半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体集積回路に関する。

【背景技術】

【0002】

従来、任意の論理を実現可能な半導体集積回路(IC)の一例として、FPGA(Field-Programmable Gate Array)が知られている。一般的なFPGAは、特定の論理を実現可能な論理ブロックと、各論理ブロック間の接続に用いられる複数の配線の接続を、プログラム可能な制御データに応じて切り替える複数のスイッチを含むスイッチブロックと、をそれぞれが有する複数のタイルがマトリクス状に配列される。そして、各スイッチブロックに対して、制御データを外部から供給する(書き込む)ことによって、様々な論理を実現することができる。

【0003】

FPGAは、様々な論理を実現することが可能であるが、各論理を実現する際に、全てのタイルが使用されることは殆ど無いので、未使用のタイルに対しては電力の供給を停止することが望ましい。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】T. Tuan, et al. IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, VOL. 26, NO.2, FEBRUARY 2007

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特定の論理を実現可能な単位を示すタイルごとに、電源制御回路を個別に設けると、電源制御回路の設置に必要な回路面積や配線等の周辺回路が増大する。すなわち、回路規模が増大してしまうという問題がある。本発明が解決しようとする課題は、回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供することである。

【課題を解決するための手段】

【0006】

実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1スイッチブロックは、第1論理ブロックまたは第2論理ブロックと入出力部との接続、第1論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2スイッチブロックは、第1論理ブロックまたは第2論理ブロックと入出力部との接続、第2論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

【図面の簡単な説明】

【0007】

【図1】第1実施形態のFPGAの概略構成例を示す図。

【図2】第1実施形態の論理ブロックから入出力部までの経路例を示す図。

【図3】フェルミ−ディラックの統計分布の平均値を示す図。

【図4】第1実施形態の電源制御回路の配置例を示す図。

【図5】第1実施形態の電源制御回路の構成例を示す図。

【図6】第1実施形態の変形例の電源制御回路の配置例を示す図。

【図7】第2実施形態の電源制御回路の配置例を示す図。

【図8】第2実施形態の変形例の電源制御回路の配置例を示す図。

【図9】第3実施形態の電源制御回路の配置例を示す図。

【図10】第3実施形態の変形例の電源制御回路の配置例を示す図。

【図11】第4実施形態の電源制御回路の配置例を示す図。

【図12】第4実施形態の変形例1における組分けの例を示す図。

【図13】第4実施形態の変形例2における組分けの例を示す図。

【図14】第4実施形態の変形例3における組分けの例を示す図。

【図15】第4実施形態の変形例4における組分けの例を示す図。

【図16】第5実施形態の電源制御回路の配置例を示す図。

【図17】第5実施形態の変形例の電源制御回路の配置例を示す図。

【図18】第5実施形態の変形例の組分けの例を示す図。

【図19】第5実施形態の変形例の組分けの例を示す図。

【図20】変形例の組分けの例を示す図。

【図21】変形例の電源制御回路の構成例を示す図。

【図22】変形例の電源制御回路の構成例を示す図。

【図23】変形例の電源制御回路の構成例を示す図。

【図24】変形例の電源制御回路の構成例を示す図。

【図25】変形例の電源制御回路の構成例を示す図。

【発明を実施するための形態】

【0008】

以下、添付図面を参照しながら、本発明に係る半導体集積回路の実施の形態を詳細に説明する。なお、以下の実施形態では、半導体集積回路として、FPGAを例に挙げて説明するが、これに限定されるものではない。

【0009】

(第1実施形態)

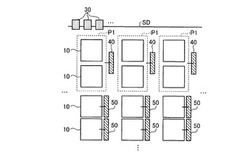

図1は、本実施形態のFPGA100の概略構成例を示す図である。図1に示すように、FPGA100は、複数のタイル10がマトリクス状に配列されたアレイ部20と、アレイ部20を囲むように配置される複数の入出力部(I/O)30とを含む。

【0010】

本実施形態の各タイル10は、それぞれ特定の論理を実現可能な単位であり、論理ブロックLBと、スイッチブロックSBとを含む。論理ブロックLBは、少なくとも1つの論理演算回路を含み、当該論理演算回路の論理演算により特定の論理が実現される。なお、各タイル10が実現可能な論理は、タイル10ごとに個別に設定可能である。

【0011】

スイッチブロックSBは、論理ブロックLBと入出力部30、あるいは、論理ブロックLB同士を接続するのに用いられる複数の配線(不図示)の接続を、プログラム可能な(任意に設定可能な)制御データに応じて切り替える複数のスイッチを含む。例えば、各スイッチは電界効果トランジスタで構成され、そのゲートは、外部から書き込まれるビットデータ(制御データ)を記憶するメモリと接続されてもよい。この場合、メモリに記憶されるビットデータは書き換え可能であり、各スイッチのオンオフは、メモリに書き込まれたビットデータに応じて切り替わる。

【0012】

複数の入出力部30の各々は、入力データを論理ブロックLBへ入力する機能、および、論理ブロックLBから出力された出力データを外部へ出力する機能を有する。

【0013】

ここで、FPGA100の構造上、あるタイル10の論理ブロックLBから出力される出力データが入出力部30へ到達するには、当該タイル10から当該入出力部30までの間に介在する全てのスイッチブロックSBを通過しなければならないので、例えば図2に示すように、出力データの出力を行う入出力部30Bから離れたタイル10Aが使用されるように配置配線されると、データ伝送の遅延量が増加してしまう。そのため、入力データの入力または出力データの出力を行う入出力部30(以下では、「使用される入出力部30」と呼ぶ)に近い位置のタイル10が使用されるように、配置配線される。

【0014】

したがって、使用される入出力部30に近いタイル10ほど、動作する可能性を示す動作確率の値は高くなる。タイル10の動作確率は、以下の式1で表すことができる。

f(D)=1/[exp{(D−μ)/C}+1] (1)

上記式1において、f(D)は、使用される入出力部30から距離Dの位置に配置されたタイル10の動作確率を示す。μは、論理ブロックLBが、使用される入出力部30に近い順から使用された場合の当該入出力部30からの距離を示す。さらに言えば、μは、FPGA(例えば150×150のタイル10を含むFPGAなど)の大きさ(例えばタイル10の数)と、ユーザーが使用する論理によって決まる固定値(定数)である。一方、上述のDは、タイル10の動作確率f(D)を求める関数の変数であり、変数Dに応じて動作確率f(D)の値は可変に設定される。Cは、使用される入出力部30からの論理ブロックLBの離れやすさを示す定数である。すなわち、動作確率f(D)は、フェルミ−ディラックの統計分布に従う。なお、上記タイル10の動作確率は、当該タイル10に含まれる論理ブロックLBが動作する可能性を示すと捉えることもできる。

【0015】

図3は、MCNCベンチマーク回路から抜粋した20回路について、FPGAの幅を150タイルとした場合に計算したフェルミ−ディラックの統計分布の平均値を示す図である。各タイル内の論理ブロックは、4入力のルックアップテーブル(LUT)で構成されることを想定している。図3からも理解されるように、使用される入出力部(I/O)からの距離が近いタイルほど、動作確率の値が高くなる。

【0016】

以上のように、FPGAでは、使用される入出力部30の付近のタイル10ほど、動作確率の値が高くなる。タイル10がマトリクス状に配列されたアレイ部20のうち、動作確率の高い領域では、当該領域に含まれる複数のタイル10が同時に使用されると考えられるため、複数のタイル10に対して、共通の電源制御回路を配置すればよいと考えられる。

【0017】

そこで、本実施形態では、図4に示すように、使用される複数の入出力部30で構成される辺SDに近い位置に配置されるタイル10については、複数のタイル10ごとにグルーピング(組分け)される。図4の例では、辺SDの延在方向(行方向)に直交する方向(列方向)において、当該辺SDに近い方から数えて第1番目と第2番目のタイル10で1つの組P1が構成される。そして、組P1ごとに、当該組P1に属する2つのタイル10の各々に対する電力の供給および停止を制御する共通の電源制御回路40が設けられる。一方、組P1に含まれるタイル10以外の他のタイル10については、当該タイル10に対する電力の供給および停止を制御する電源制御回路50が個別に設けられる。見方を変えれば、組P1に含まれるタイル10よりも辺SDから遠い位置に配置される他のタイル10については、ひとつのタイル10ごとに組分けされ、その組分けされた組ごとに、当該組に属する1つのタイル10に対して電力の供給および停止を制御する電源制御回路50が個別に設けられていると捉えることもできる。

【0018】

すなわち、本実施形態のFPGA100は、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(この例では、1つのタイル10ごとに組分けされた単位、つまりはひとつのタイル10そのもの)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30に近い位置に配置される第2回路群(この例では組P1)とを備えると捉えることができる。

【0019】

そして、第1回路群は、第1論理ブロックまたは第2論理ブロックと入出力部30との接続、第1論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、ひとつのタイル10に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、ひとつのタイル10に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路50)を有する。また、第2回路群は、第1論理ブロックまたは第2論理ブロックと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P1に含まれる2つのタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P1に含まれる2つのタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路40)を有すると捉えることができる。

【0020】

図5は、電源制御回路40の構成例を示す図である。ここでは、ひとつの組P1に対応して設けられる電源制御回路40(ひとつの組P1に含まれる電源制御回路40と捉えることができる)を例に挙げて説明するが、他の組P1に対応して設けられる電源制御回路40も同様の構成である。図5に示すように、電源制御回路40は、スイッチ素子41と、制御回路42とを含む。スイッチ素子41は、電源電位VDが供給される電源線101と組P1との間に配置される。図5の例では、スイッチ素子41は、Pチャネル型の電界効果トランジスタ(P型のMOSFET)で構成される。スイッチ素子41のゲートは制御回路42に接続され、制御回路42から供給されるスイッチ制御信号に応じて、スイッチ素子41のオンオフが切り替わる。例えばスイッチ制御信号は1ビットのデジタルデータであり、そのデジタルデータに応じてスイッチ素子41のオンオフが切り替わる構成であってもよい。また、制御回路42は、スイッチ素子41のオンオフを制御可能な手段であればよく、その構成は任意である。例えば制御回路42は、外部から書き込まれるスイッチ制御信号を記憶可能なメモリ素子で構成されてもよい。

【0021】

スイッチ素子41がオン状態に遷移した場合は、電源線101から、組P1に含まれる2つのタイル10の各々に至る電源経路が形成され、当該2つのタイル10の各々に対して電源電位VDが供給される。一方、スイッチ素子41がオフ状態に遷移した場合は、電源線101から、組P1に含まれる2つのタイル10の各々に至る電源経路は形成されないので、当該2つのタイル10の各々に対する電源電位VDの供給は行われない。なお、電源制御回路50の基本的な構成は、図5に示す電源制御回路40の構成と同様であるが、電源制御回路50は、組P1に含まれるタイル10以外の他のタイル10ごとに個別に設けられるので、他のタイル10と同数のスイッチ素子および制御回路が必要になる。

【0022】

以上に説明したように、本実施形態では、使用される入出力部30(辺SD)に近い位置に配置されるタイル10については、2つのタイル10ごとに組分けされ、組分けされた単位ごとに(組P1ごとに)共通の電源制御回路40が設けられるので、全てのタイル10に対して電源制御回路50が個別に設けられる構成に比べて、回路規模を低減できる。一方、使用される入出力部30から遠い位置に配置されるタイル10、つまりは、使用される可能性が低い(動作確率の値が小さい)タイル10については、複数のタイル10ごとに共通の電源制御回路を設けるよりも、電力の供給および停止を制御する単位を細かくした方が電力削減の効果は大きい。本実施形態では、組P1に含まれるタイル10よりも、使用される入出力部30から遠い位置に配置されるタイル10については、電源制御回路50が個別に設けられるので、タイル10単位で電力の供給および停止を制御することができる。すなわち、電力の供給および停止を制御する単位を細かくできるので、複数のタイル10ごとに共通の電源制御回路が設けられる場合に比べて、電力削減の効果が大きくなる。

【0023】

(第1実施形態の変形例)

前述のアレイ部20においては、辺SDの延在方向(行方向)と平行に配列された複数のタイル10の集合Gが並列に配列されていると捉えることができる。図6に示すように、辺SDに近い方から数えて第1行目の集合Gに含まれる複数のタイル10については、2つのタイル10ごとに1つの組P2が構成されてもよい。図6の例では、組P2ごとに、共通の電源制御回路40が設けられる。一方、第1行目の集合Gに含まれる複数のタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0024】

(第2実施形態)

次に、第2実施形態について説明する。第2実施形態では、使用される入出力部30(辺SD)の付近に形成される組に属するタイル10の数が2よりも大きい点で上述の第1実施形態と相違するが、その他の構成は第1実施形態と同様である。以下では、第1実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0025】

前述したように、アレイ部20には、辺SDの延在方向(行方向)と平行に配列された複数のタイル10の集合Gが並列に配列されていると捉えることができる。そして、本実施形態では、図7に示すように、辺SDに近い方から数えて第1行目および第2行目の集合Gの各々に含まれる複数のタイル10については、2行×2列の4つのタイル10ごとに1つの組P3が構成される。そして、組P3ごとに、共通の電源制御回路400が設けられる。電源制御回路400の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路400は、組P3に含まれる4つのタイル10の各々に対する電源電位VDの供給および停止を制御する。一方、第1行目および第2行目の集合Gの各々に含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0026】

本実施形態では、使用される入出力部30(辺SD)に近い位置に配置されるタイル10については、4つのタイル10ごとに組分けされ、組分けされた単位ごとに(組P3ごとに)共通の電源制御回路400が設けられるので、上述の第1実施形態に比べて、回路規模を一層低減できる。

【0027】

(第2実施形態の変形例)

例えば図8に示すように、辺SDに近い方から数えて第1行目および第2行目の集合Gの各々に含まれる複数のタイル10については、3つのタイル10ごとに1つの組P4が構成されてもよい。図8の例では、組P4ごとに、共通の電源制御回路410が設けられている。電源制御回路410の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路410は、組P4に含まれる3つのタイル10の各々に対する電源電位VDの供給および停止を制御する。一方、組P4に含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0028】

(第3実施形態)

次に、第3実施形態について説明する。第3実施形態では、使用される入出力部30(辺SD)の付近に形成される組に属するタイル10の数が、組ごとに可変に設定される点で上述の各実施形態と相違する。以下では、上述の各実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0029】

図9において、辺SDの付近に形成される3つの組(P51、P52、P53)に着目して説明する。図9に示す3つの組(P51、P52、P53)の各々に含まれるタイル10の数は、個別に設定される。組P51は、上述の第2実施形態と同様に、辺SDに近い方から数えて第1行目および第2行目の集合Gの各々に含まれる複数のタイル10のうちの何れか4つのタイル10(2行×2列の4つのタイル10)で構成される。その右隣に形成される組P52は、上述の第1実施形態と同様に、辺SDの延在方向に直交する方向(列方向)において、当該辺SDに近い方から数えて第1番目と第2番目のタイル10で構成される。その右隣に形成される組P53は、上述の第1実施形態の変形例と同様に、辺SDに近い方から数えて第1行目の集合Gに含まれる複数のタイル10のうちの何れか2つのタイル10で構成される。そして、組(P51、P52、P53)ごとに、当該組に含まれるタイル10に対する電力の供給および停止を制御する電源制御回路が設けられる。本実施形態では、辺SDの付近においては、上述の3種類の組(P51、P52、P53)が繰り返し形成され、上述の3種類の組(P51、P52、P53)のうちの何れかに含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0030】

図9の例では、組P51については、組P51に含まれる4つのタイル10に対する電力の供給および停止を制御する電源制御回路420が設けられる。電源制御回路420の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路420は、組P51に含まれる4つのタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P52については、組P52に含まれる2つのタイル10に対する電力の供給および停止を制御する電源制御回路430が設けられる。電源制御回路430の基本的な構成は、図5に示す電源制御回路40と同様である。さらに、組P53については、組P53に含まれる2つのタイル10に対する電力の供給および停止を制御する電源制御回路440が設けられる。電源制御回路440の基本的な構成は、図5に示す電源制御回路40と同様である。

【0031】

(第3実施形態の変形例)

上述した内容に限らず、辺SDの付近に形成される組に含まれるタイル10の数は任意に設定可能である。例えば図10に示すように、辺SDの付近に配置されたタイル10(動作確率が所定値以上のタイル10)のうち、E(E≧2)個のタイル10でひとつの組P54が形成され、当該組P54の右隣には、F個(FはEとは異なる2以上の整数)のタイル10でひとつの組P55が形成されてもよい。なお、組P54または組P55に含まれるタイル10は、第1行目の集合Gおよび第2行目の集合Gの各々に含まれるタイル10に限定されず、第3行目以降の集合Gに含まれるタイル10であってもよい。

【0032】

図10の例でも、組(P54、P55)ごとに、当該組に含まれるタイル10に対する電力の供給および停止を制御する電源制御回路が設けられる。本実施形態では、辺SDの付近においては、上述の2種類の組(P54、P55)が繰り返し形成され、上述の2種類の組(P54、P55)のうちの何れかに含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0033】

図10の例では、組P54については、組P54に含まれるE個のタイル10に対する電力の供給および停止を制御する電源制御回路450が設けられる。電源制御回路450の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路450は、組P54に含まれるE個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P55については、組P55に含まれるF個のタイル10に対する電力の供給および停止を制御する電源制御回路460が設けられる。電源制御回路460の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路460は、組P55に含まれるF個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0034】

例えばFPGA100全体で実現される論理が限定的であれば、使用される頻度が高い領域(動作確率が高いタイル10が属する領域)も限定されるので、その使用される頻度が高い領域に、タイル数が多い組を形成し、当該組に対応する電源制御回路を設けることで、回路規模を一層低減できる。一方、使用される頻度が低い領域については、タイル数が少ない組(タイル数が1つの組であってもよい)を形成し、当該組に対応する電源制御回路を設けることで、効率よく電力を削減することができる。

【0035】

(第4実施形態)

次に、第4実施形態について説明する。第4実施形態では、電源制御回路が共通化されるタイル10の組分けが段階的に行われ、使用される入出力部30(辺SD)に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、使用される入出力部30(辺SD)から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされる点で上述の各実施形態と相違する。以下では、上述の各実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0036】

図11において、辺SDに近いタイル10ほど、同じ組に含まれるタイル10の数が多く、辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされた3つの組(P61、P62、P63)に着目して説明する。組P61は、動作確率が第1基準値以上の複数のタイル10のうちの何れかN個(N>1)のタイル10で構成される。組P62は、動作確率が第2基準値以上であって、かつ第1基準値未満の複数のタイルのうちの何れかM個(M>1、M<N)のタイル10で構成される。組P63は、動作確率が第2基準値未満の複数のタイルのうちの何れかL個(L≧1、L<M)のタイル10で構成される。

【0037】

図11の例では、組P61については、組P61に含まれるN個のタイル10に対する電力の供給および停止を制御する電源制御回路470が設けられる。電源制御回路470の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路470は、組P61に含まれるN個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P62については、組P62に含まれるM個のタイル10に対する電力の供給および停止を制御する電源制御回路480が設けられる。電源制御回路480の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路480は、組P62に含まれるM個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。さらに、組P63については、組P63に含まれるL個のタイル10に対する電力の供給および停止を制御する電源制御回路490が設けられる。電源制御回路490の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路490は、組P63に含まれるL個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0038】

すなわち、本実施形態のFPGAは、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(例えば組P63)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30に近い位置に配置される第2回路群(例えば組P61)と、第1論理ブロックよりも多く、第2論理ブロックよりも少ない数の論理ブロックLB(「第3論理ブロック」)を含み、第2回路群よりも当該入出力部30から遠い位置に配置され、第1回路群よりも当該入出力部30に近い位置に配置される第3回路群(例えば組P62)と、を備えると捉えることができる。

【0039】

そして、第1回路群は、第1論理ブロック、第2論理ブロックおよび第3論理ブロックのうちの何れかと入出力部30との接続、第1論理ブロック同士の接続、第2論理ブロックまたは第3論理ブロックと第1論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、組P63に含まれるL個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、組P63に含まれるL個のタイル10の各々に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路490)を有する。また、第2回路群は、第1論理ブロック、第2論理ブロックおよび第3論理ブロックのうちの何れかと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックまたは第3論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P61に含まれるN個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P61に含まれるN個のタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路470)を有する。さらに、第3回路群は、第1論理ブロック、第2論理ブロックおよび第3論理ブロックのうちの何れかと入出力部30との接続、第3論理ブロック同士の接続、第1論理ブロックまたは第2論理ブロックと第3論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第3スイッチブロック(この例では、組P62に含まれるM個のタイル10の各々に含まれるスイッチブロックSB)と、当該第3回路群に含まれる第3論理ブロック(この例では、組P62に含まれるM個のタイル10の各々に含まれる論理ブロックLB)および第3スイッチブロックに対して電力の供給および停止を共通に制御する第3電源制御回路(この例では、電源制御回路480)を有すると捉えることができる。以上の構成でも、全てのタイル10に対して電源制御回路50が個別に設けられる構成に比べて、回路規模を低減できる。

【0040】

(第4実施形態の変形例1)

例えばユーザーが、使用される入出力部30を自由に指定可能な場合は、図12に示すように、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、4つの辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされてもよい。すなわち、組が形成される領域の大きさが点対称となるように組が形成されてもよい。図12の例では、略矩形状のアレイ部20の4隅の付近に配置される入出力部30が使用され、当該入出力部30に近いタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0041】

(第4実施形態の変形例2)

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)のうち、互いに対向する2つの辺SD1および辺SD3が使用される場合を想定する。この場合は、図13に示すように、2つの辺SD1および辺SD3に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、2つの辺SD1および辺SD3から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされるので、辺SD1および辺SD3の付近に配置されたタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0042】

(第4実施形態の変形例3)

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)のうち、辺SD1が使用される場合を想定する。この場合は、図14に示すように、辺SD1に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、辺SD1から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされるので、辺SD1の付近に配置されたタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0043】

(第4実施形態の変形例4)

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)のうち、辺SD1と辺SD4との角C1の近くの入出力部30が使用される場合を想定する。この場合は、図15に示すように、角C1に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、角C1から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされるので、角C1の付近に配置されたタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0044】

(第5実施形態)

次に、第5実施形態について説明する。第5実施形態では、使用される入出力部30に近い位置に形成される組に含まれるタイルの数は、当該組よりも、使用される入出力部30から遠い位置に形成される組に含まれるタイルの数よりも少ない点で上述の各実施形態と相違する。以下では、上述の各実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0045】

図16において、使用される複数の入出力部30で構成される辺SDに近いタイル10ほど、同じ組に含まれるタイル10の数が少なく、当該辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が多くなるように組分けされた2つの組(P71、P72)に着目して説明する。組P71は、動作確率が第1基準値以上の複数のタイルのうちの何れかi個(i≧1)のタイル10で構成される。組P72は、動作確率が第1基準値未満の複数のタイルのうちの何れかj個(j>1、j>i)のタイル10で構成される。

【0046】

図16の例では、組P71については、組P71に含まれるi個のタイル10に対する電力の供給および停止を制御する電源制御回路4000が設けられる。電源制御回路4000の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4000は、組P71に含まれるi個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P72については、組P72に含まれるj個のタイル10に対する電力の供給および停止を制御する電源制御回路4010が設けられる。電源制御回路4010の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4010は、組P72に含まれるj個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0047】

すなわち、本実施形態のFPGAは、少なくとも1つの論理ブロックLBを含む第1回路群(例えば組P71)と、第1回路群よりも多い数の論理ブロックLBを含み、第1回路群よりも、使用される入出力部30から遠い位置に配置される第2回路群(例えば組P72)とを備えると捉えることができる。そして、第1回路群は、第1スイッチブロック(この例では、組P71に含まれるi個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる論理ブロックLBおよび第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路4000)とを有する。また、第2回路群は、第2スイッチブロック(この例では、組P72に含まれるj個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる論理ブロックLBおよび第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路4010)とを有すると捉えることができる。

【0048】

(第5実施形態の変形例)

例えば使用される入出力部30に最も近い位置に形成される第1の組(当該入出力部30と第1の組との間には他の組(回路群)は存在しないと捉えることができる)に含まれるタイル10の数は、第1の組よりも入出力部30から遠い位置に形成される第2の組に含まれるタイル10の数よりも少なく、第2の組よりも入出力部30から遠い位置に形成される第3の組に含まれるタイル10の数は、第2の組に含まれるタイル10の数よりも少なくなるように、組分けすることもできる。つまりは、上述の第1の組に含まれるタイル10以外のタイル10については、辺SDに近いタイル10ほど、同じ組に含まれるタイル10の数が多く、辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされてもよい。

【0049】

図17において、使用される複数の入出力部30で構成される辺SDに最も近い位置に形成された組P73、辺SDの直交方向において組P73と隣接するとともに当該組P73よりも辺SDから遠い位置に形成された組P74、および、辺SDの直交方向において組P74と隣接するとともに当該組P74よりも辺SDから遠い位置に形成された組P75に着目して説明する。組P73は、動作確率が第1基準値以上の複数のタイル10のうちの何れかq個のタイル10で構成される。組P74は、動作確率が第2基準値以上であって、かつ第1基準値未満の複数のタイル10のうちの何れかr個のタイル10で構成される。組P75は、動作確率が第2基準値未満の複数のタイル10のうちの何れかs個のタイル10で構成される。組P73に含まれるタイル10の数qは、1以上であって、かつ、組P74に含まれるタイル10の数rよりも小さい。組P74に含まれるタイル10の数rは、1よりも大きい。組P75に含まれるタイルの数sは、1以上であって、かつ、組P74に含まれるタイル10の数rよりも小さい。

【0050】

図17の例では、組P73については、組P73に含まれるq個のタイル10に対する電力の供給および停止を制御する電源制御回路4020が設けられる。電源制御回路4020の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4020は、組P73に含まれるq個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P74については、組P74に含まれるr個のタイル10に対する電力の供給および停止を制御する電源制御回路4030が設けられる。電源制御回路4030の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4030は、組P74に含まれるr個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。さらに、組P75については、組P75に含まれるs個のタイル10に対する電力の供給を制御する電源制御回路4040が設けられる。電源制御回路4040の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4040は、組P75に含まれるs個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0051】

すなわち、本実施形態のFPGAは、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(例えば組P73)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30から遠い位置に配置される第2回路群(例えば組P74)と、第2論理ブロックよりも少ない数の論理ブロックLB(「第3論理ブロック」)を含み、第2回路群よりも、使用される入出力部30から遠い位置に配置される第4回路群(例えば組P75)とを備えると捉えることができる。

【0052】

そして、第1回路群は、第1論理ブロック、第2論理ブロックおよび第4論理ブロックのうちの何れかと入出力部30との接続、第1論理ブロック同士の接続、第2論理ブロックまたは第4論理ブロックと第1論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路4020)を有する。また、第2回路群は、第1論理ブロック、第2論理ブロックおよび第4論理ブロックのうちの何れかと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックまたは第4論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路4030)を有する。さらに、第4回路群は、第1論理ブロック、第2論理ブロック、および、第4論理ブロックのうちの何れかと入出力部30との接続、第4論理ブロック同士の接続、第1論理ブロックまたは第2論理ブロックと第4論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第4スイッチブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれるスイッチブロックSB)と、当該第4回路群に含まれる第4論理ブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれる論理ブロックLB)および第4スイッチブロックに対して電力の供給および停止を共通に制御する第4電源制御回路(この例では、電源制御回路4040)を有すると捉えることができる。

【0053】

また、本実施形態のFPGA100は、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(例えば組P75)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30に近い位置に配置される第2回路群(例えば組P74)と、第2論理ブロックよりも少ない数の論理ブロックLB(「第5論理ブロック」)を含み、第2回路群よりも、使用される入出力部30に近い位置に配置される第5回路群(例えば組P73)とを備えると捉えることもできる。

【0054】

そして、第1回路群は、第1論理ブロック、第2論理ブロック、および、第5論理ブロックのうちの何れかと入出力部30との接続、第1論理ブロック同士の接続、第2論理ブロックまたは第5論理ブロックと第1論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路4040)を有する。また、第2回路群は、第1論理ブロック、第2論理ブロック、および、第5論理ブロックのうちの何れかと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックまたは第5論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路4030)を有する。さらに、第5回路群は、第1論理ブロック、第2論理ブロック、および、第5論理ブロックのうちの何れかと入出力部30との接続、第5論理ブロック同士の接続、第1論理ブロックまたは第2論理ブロックと第5論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第5スイッチブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれるスイッチブロックSB)と、第5回路群に含まれる第5論理ブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれる論理ブロックLB)および第5スイッチブロックに対する電力の供給および停止を共通に制御する第5電源制御回路(この例では、電源制御回路4020)を有すると捉えることができる。

【0055】

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)が使用される場合は、図18のように、組が形成されてもよい(組分けが行われてもよい)。

【0056】

また、例えば、辺SD1、辺SD2および辺SD4が使用される場合は、図19のように組が形成されてもよい。図19の例において、辺SD1の付近の矩形領域Tx内に含まれる論理ブロックLBが使用され、辺SD2のうち、辺SD1と辺SD2との角C2から、辺SD2に沿って所定距離だけ延在する部分PSD2が使用され、辺SD4のうち、辺SD1と辺SD4との角C1から、辺SD4に沿って所定距離だけ延在する部分PSD4が使用される場合を想定する。より具体的には、辺SD1に加え、PSD2およびPSD4を構成する入出力部30が使用される一方、使用される論理ブロックLBは、領域Tx内の論理ブロックLBのみである場合を想定する。つまりは、この例では、PSD2およびPSD4は配線として使用され、領域Tx内の論理ブロックLBから部分PSD2へ至る配線経路が形成されるように、部分PSD2に最も近い位置に形成される複数の組の各々に含まれるタイル10(スイッチブロックSB)が動作する。同様に、領域Tx内の論理ブロックLBから部分PSD4へ至る配線経路が形成されるように、部分PSD4に最も近い位置に形成される複数の組の各々に含まれるタイル10が動作する。

【0057】

図19の例では、使用される入出力部30に最も近い位置に形成される組(「第1の組」と呼ぶ)に含まれるタイル10の数は、当該第1の組と隣接するとともに当該第1の組よりも当該入出力部30から遠い位置に形成される第2の組に含まれるタイル10の数よりも少ないので、第1の組に含まれるタイル10の数が他の組に含まれるタイル10の数よりも多くなるように組分けされる場合(第1の組に含まれるタイル10の数が最も多くなるように組分けされる場合)に比べて、消費電力量を削減できる。すなわち、図19の例では、配線として使用されるPSD2(PSD4)に最も近い位置に形成される第1の組に含まれるタイル10の数を少なくすることで、配線として使用されるタイル10の数を減らしている。これにより、消費電力量を削減できる。

【0058】

以上、本発明の各実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【0059】

要するに、本発明が適用されるFPGAは、電源制御回路が共通化されるタイル10の数(特定の論理を実現可能な論理ブロックLBの数)が相違する2つの組(「第1回路群」、「第2回路群」)を少なくとも備えていればよい。これにより、特定の論理を実現可能な単位ごとに電源制御回路が個別に設けられる場合に比べて、回路規模を低減できる。

【0060】

また、上述の各実施形態および変形例では、FPGA内に形成される各組は、行方向に延在する複数の直線と、列方向に延在する複数の直線とで区切られているが、これに限らず、例えば図20のように、隣の組との境界線が一致しないように組分けすることもできる。

【0061】

また、上述の図5の例では、スイッチ素子41は、P型のMOSFETで構成されているが、これに限らず、スイッチ素子41の構成は任意である。要するに、電源制御回路40は、対応する組P1に対する電力の供給および停止を制御可能な構成であればよく、その構成は図5の構成に限られない。以下のバリエーションの例では、スイッチ素子41に対応する組P1に含まれるタイル10の数が3つである場合を例に挙げて説明する。

【0062】

例えば図21に示すように、スイッチ素子41は、N型のMOSFETで構成されてもよい。また、スイッチ素子41がN型のMOSFETで構成される場合、例えば図22に示すように、電源電位VDが供給される電源線(不図示)と、接地電位GND(例えば0V)が供給される接地線102との間に組P1が配置され、組P1と接地線102との間に電源制御回路40が配置される構成であってもよい。

【0063】

また、例えば図23および図24に示すように、P型のMOSFETあるいはN型のMOSFETで構成されるスイッチ素子41が、組P1に含まれる3つのタイル10の各々と、電源線101との間に個別に設けられる構成であってもよい。この構成では、3つのスイッチ素子41の各々のゲートは制御回路42に共通に接続され、3つのスイッチ素子41のオンオフは、制御回路42からのスイッチ制御信号に応じて一斉に制御される。この構成であっても、組P1に対応して設けられる制御回路42はひとつで済むので、タイル10ごとに制御回路42が個別に設けられる場合に比べて、回路規模を低減できる。ただし、上述の各実施形態および変形例のように、組P1に含まれる3つのタイル10の各々に対する電力の供給および停止を切り替えるスイッチ素子41を共通化することにより、さらなる回路規模の低減を図ることが可能になる。

【0064】

さらに、例えば図25に示すように、N型のMOSFETで構成されるスイッチ素子41が、組P1に含まれる3つのタイル10の各々と、接地線102との間に個別に設けられる構成であってもよい。

【符号の説明】

【0065】

10 タイル

20 アレイ部

30 入出力部

40 電源制御回路

41 スイッチ素子

42 制御回路

50 電源制御回路

101 電源線

102 接地線

【技術分野】

【0001】

本発明の実施形態は、半導体集積回路に関する。

【背景技術】

【0002】

従来、任意の論理を実現可能な半導体集積回路(IC)の一例として、FPGA(Field-Programmable Gate Array)が知られている。一般的なFPGAは、特定の論理を実現可能な論理ブロックと、各論理ブロック間の接続に用いられる複数の配線の接続を、プログラム可能な制御データに応じて切り替える複数のスイッチを含むスイッチブロックと、をそれぞれが有する複数のタイルがマトリクス状に配列される。そして、各スイッチブロックに対して、制御データを外部から供給する(書き込む)ことによって、様々な論理を実現することができる。

【0003】

FPGAは、様々な論理を実現することが可能であるが、各論理を実現する際に、全てのタイルが使用されることは殆ど無いので、未使用のタイルに対しては電力の供給を停止することが望ましい。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】T. Tuan, et al. IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, VOL. 26, NO.2, FEBRUARY 2007

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特定の論理を実現可能な単位を示すタイルごとに、電源制御回路を個別に設けると、電源制御回路の設置に必要な回路面積や配線等の周辺回路が増大する。すなわち、回路規模が増大してしまうという問題がある。本発明が解決しようとする課題は、回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供することである。

【課題を解決するための手段】

【0006】

実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1スイッチブロックは、第1論理ブロックまたは第2論理ブロックと入出力部との接続、第1論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2スイッチブロックは、第1論理ブロックまたは第2論理ブロックと入出力部との接続、第2論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

【図面の簡単な説明】

【0007】

【図1】第1実施形態のFPGAの概略構成例を示す図。

【図2】第1実施形態の論理ブロックから入出力部までの経路例を示す図。

【図3】フェルミ−ディラックの統計分布の平均値を示す図。

【図4】第1実施形態の電源制御回路の配置例を示す図。

【図5】第1実施形態の電源制御回路の構成例を示す図。

【図6】第1実施形態の変形例の電源制御回路の配置例を示す図。

【図7】第2実施形態の電源制御回路の配置例を示す図。

【図8】第2実施形態の変形例の電源制御回路の配置例を示す図。

【図9】第3実施形態の電源制御回路の配置例を示す図。

【図10】第3実施形態の変形例の電源制御回路の配置例を示す図。

【図11】第4実施形態の電源制御回路の配置例を示す図。

【図12】第4実施形態の変形例1における組分けの例を示す図。

【図13】第4実施形態の変形例2における組分けの例を示す図。

【図14】第4実施形態の変形例3における組分けの例を示す図。

【図15】第4実施形態の変形例4における組分けの例を示す図。

【図16】第5実施形態の電源制御回路の配置例を示す図。

【図17】第5実施形態の変形例の電源制御回路の配置例を示す図。

【図18】第5実施形態の変形例の組分けの例を示す図。

【図19】第5実施形態の変形例の組分けの例を示す図。

【図20】変形例の組分けの例を示す図。

【図21】変形例の電源制御回路の構成例を示す図。

【図22】変形例の電源制御回路の構成例を示す図。

【図23】変形例の電源制御回路の構成例を示す図。

【図24】変形例の電源制御回路の構成例を示す図。

【図25】変形例の電源制御回路の構成例を示す図。

【発明を実施するための形態】

【0008】

以下、添付図面を参照しながら、本発明に係る半導体集積回路の実施の形態を詳細に説明する。なお、以下の実施形態では、半導体集積回路として、FPGAを例に挙げて説明するが、これに限定されるものではない。

【0009】

(第1実施形態)

図1は、本実施形態のFPGA100の概略構成例を示す図である。図1に示すように、FPGA100は、複数のタイル10がマトリクス状に配列されたアレイ部20と、アレイ部20を囲むように配置される複数の入出力部(I/O)30とを含む。

【0010】

本実施形態の各タイル10は、それぞれ特定の論理を実現可能な単位であり、論理ブロックLBと、スイッチブロックSBとを含む。論理ブロックLBは、少なくとも1つの論理演算回路を含み、当該論理演算回路の論理演算により特定の論理が実現される。なお、各タイル10が実現可能な論理は、タイル10ごとに個別に設定可能である。

【0011】

スイッチブロックSBは、論理ブロックLBと入出力部30、あるいは、論理ブロックLB同士を接続するのに用いられる複数の配線(不図示)の接続を、プログラム可能な(任意に設定可能な)制御データに応じて切り替える複数のスイッチを含む。例えば、各スイッチは電界効果トランジスタで構成され、そのゲートは、外部から書き込まれるビットデータ(制御データ)を記憶するメモリと接続されてもよい。この場合、メモリに記憶されるビットデータは書き換え可能であり、各スイッチのオンオフは、メモリに書き込まれたビットデータに応じて切り替わる。

【0012】

複数の入出力部30の各々は、入力データを論理ブロックLBへ入力する機能、および、論理ブロックLBから出力された出力データを外部へ出力する機能を有する。

【0013】

ここで、FPGA100の構造上、あるタイル10の論理ブロックLBから出力される出力データが入出力部30へ到達するには、当該タイル10から当該入出力部30までの間に介在する全てのスイッチブロックSBを通過しなければならないので、例えば図2に示すように、出力データの出力を行う入出力部30Bから離れたタイル10Aが使用されるように配置配線されると、データ伝送の遅延量が増加してしまう。そのため、入力データの入力または出力データの出力を行う入出力部30(以下では、「使用される入出力部30」と呼ぶ)に近い位置のタイル10が使用されるように、配置配線される。

【0014】

したがって、使用される入出力部30に近いタイル10ほど、動作する可能性を示す動作確率の値は高くなる。タイル10の動作確率は、以下の式1で表すことができる。

f(D)=1/[exp{(D−μ)/C}+1] (1)

上記式1において、f(D)は、使用される入出力部30から距離Dの位置に配置されたタイル10の動作確率を示す。μは、論理ブロックLBが、使用される入出力部30に近い順から使用された場合の当該入出力部30からの距離を示す。さらに言えば、μは、FPGA(例えば150×150のタイル10を含むFPGAなど)の大きさ(例えばタイル10の数)と、ユーザーが使用する論理によって決まる固定値(定数)である。一方、上述のDは、タイル10の動作確率f(D)を求める関数の変数であり、変数Dに応じて動作確率f(D)の値は可変に設定される。Cは、使用される入出力部30からの論理ブロックLBの離れやすさを示す定数である。すなわち、動作確率f(D)は、フェルミ−ディラックの統計分布に従う。なお、上記タイル10の動作確率は、当該タイル10に含まれる論理ブロックLBが動作する可能性を示すと捉えることもできる。

【0015】

図3は、MCNCベンチマーク回路から抜粋した20回路について、FPGAの幅を150タイルとした場合に計算したフェルミ−ディラックの統計分布の平均値を示す図である。各タイル内の論理ブロックは、4入力のルックアップテーブル(LUT)で構成されることを想定している。図3からも理解されるように、使用される入出力部(I/O)からの距離が近いタイルほど、動作確率の値が高くなる。

【0016】

以上のように、FPGAでは、使用される入出力部30の付近のタイル10ほど、動作確率の値が高くなる。タイル10がマトリクス状に配列されたアレイ部20のうち、動作確率の高い領域では、当該領域に含まれる複数のタイル10が同時に使用されると考えられるため、複数のタイル10に対して、共通の電源制御回路を配置すればよいと考えられる。

【0017】

そこで、本実施形態では、図4に示すように、使用される複数の入出力部30で構成される辺SDに近い位置に配置されるタイル10については、複数のタイル10ごとにグルーピング(組分け)される。図4の例では、辺SDの延在方向(行方向)に直交する方向(列方向)において、当該辺SDに近い方から数えて第1番目と第2番目のタイル10で1つの組P1が構成される。そして、組P1ごとに、当該組P1に属する2つのタイル10の各々に対する電力の供給および停止を制御する共通の電源制御回路40が設けられる。一方、組P1に含まれるタイル10以外の他のタイル10については、当該タイル10に対する電力の供給および停止を制御する電源制御回路50が個別に設けられる。見方を変えれば、組P1に含まれるタイル10よりも辺SDから遠い位置に配置される他のタイル10については、ひとつのタイル10ごとに組分けされ、その組分けされた組ごとに、当該組に属する1つのタイル10に対して電力の供給および停止を制御する電源制御回路50が個別に設けられていると捉えることもできる。

【0018】

すなわち、本実施形態のFPGA100は、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(この例では、1つのタイル10ごとに組分けされた単位、つまりはひとつのタイル10そのもの)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30に近い位置に配置される第2回路群(この例では組P1)とを備えると捉えることができる。

【0019】

そして、第1回路群は、第1論理ブロックまたは第2論理ブロックと入出力部30との接続、第1論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、ひとつのタイル10に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、ひとつのタイル10に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路50)を有する。また、第2回路群は、第1論理ブロックまたは第2論理ブロックと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P1に含まれる2つのタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P1に含まれる2つのタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路40)を有すると捉えることができる。

【0020】

図5は、電源制御回路40の構成例を示す図である。ここでは、ひとつの組P1に対応して設けられる電源制御回路40(ひとつの組P1に含まれる電源制御回路40と捉えることができる)を例に挙げて説明するが、他の組P1に対応して設けられる電源制御回路40も同様の構成である。図5に示すように、電源制御回路40は、スイッチ素子41と、制御回路42とを含む。スイッチ素子41は、電源電位VDが供給される電源線101と組P1との間に配置される。図5の例では、スイッチ素子41は、Pチャネル型の電界効果トランジスタ(P型のMOSFET)で構成される。スイッチ素子41のゲートは制御回路42に接続され、制御回路42から供給されるスイッチ制御信号に応じて、スイッチ素子41のオンオフが切り替わる。例えばスイッチ制御信号は1ビットのデジタルデータであり、そのデジタルデータに応じてスイッチ素子41のオンオフが切り替わる構成であってもよい。また、制御回路42は、スイッチ素子41のオンオフを制御可能な手段であればよく、その構成は任意である。例えば制御回路42は、外部から書き込まれるスイッチ制御信号を記憶可能なメモリ素子で構成されてもよい。

【0021】

スイッチ素子41がオン状態に遷移した場合は、電源線101から、組P1に含まれる2つのタイル10の各々に至る電源経路が形成され、当該2つのタイル10の各々に対して電源電位VDが供給される。一方、スイッチ素子41がオフ状態に遷移した場合は、電源線101から、組P1に含まれる2つのタイル10の各々に至る電源経路は形成されないので、当該2つのタイル10の各々に対する電源電位VDの供給は行われない。なお、電源制御回路50の基本的な構成は、図5に示す電源制御回路40の構成と同様であるが、電源制御回路50は、組P1に含まれるタイル10以外の他のタイル10ごとに個別に設けられるので、他のタイル10と同数のスイッチ素子および制御回路が必要になる。

【0022】

以上に説明したように、本実施形態では、使用される入出力部30(辺SD)に近い位置に配置されるタイル10については、2つのタイル10ごとに組分けされ、組分けされた単位ごとに(組P1ごとに)共通の電源制御回路40が設けられるので、全てのタイル10に対して電源制御回路50が個別に設けられる構成に比べて、回路規模を低減できる。一方、使用される入出力部30から遠い位置に配置されるタイル10、つまりは、使用される可能性が低い(動作確率の値が小さい)タイル10については、複数のタイル10ごとに共通の電源制御回路を設けるよりも、電力の供給および停止を制御する単位を細かくした方が電力削減の効果は大きい。本実施形態では、組P1に含まれるタイル10よりも、使用される入出力部30から遠い位置に配置されるタイル10については、電源制御回路50が個別に設けられるので、タイル10単位で電力の供給および停止を制御することができる。すなわち、電力の供給および停止を制御する単位を細かくできるので、複数のタイル10ごとに共通の電源制御回路が設けられる場合に比べて、電力削減の効果が大きくなる。

【0023】

(第1実施形態の変形例)

前述のアレイ部20においては、辺SDの延在方向(行方向)と平行に配列された複数のタイル10の集合Gが並列に配列されていると捉えることができる。図6に示すように、辺SDに近い方から数えて第1行目の集合Gに含まれる複数のタイル10については、2つのタイル10ごとに1つの組P2が構成されてもよい。図6の例では、組P2ごとに、共通の電源制御回路40が設けられる。一方、第1行目の集合Gに含まれる複数のタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0024】

(第2実施形態)

次に、第2実施形態について説明する。第2実施形態では、使用される入出力部30(辺SD)の付近に形成される組に属するタイル10の数が2よりも大きい点で上述の第1実施形態と相違するが、その他の構成は第1実施形態と同様である。以下では、第1実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0025】

前述したように、アレイ部20には、辺SDの延在方向(行方向)と平行に配列された複数のタイル10の集合Gが並列に配列されていると捉えることができる。そして、本実施形態では、図7に示すように、辺SDに近い方から数えて第1行目および第2行目の集合Gの各々に含まれる複数のタイル10については、2行×2列の4つのタイル10ごとに1つの組P3が構成される。そして、組P3ごとに、共通の電源制御回路400が設けられる。電源制御回路400の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路400は、組P3に含まれる4つのタイル10の各々に対する電源電位VDの供給および停止を制御する。一方、第1行目および第2行目の集合Gの各々に含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0026】

本実施形態では、使用される入出力部30(辺SD)に近い位置に配置されるタイル10については、4つのタイル10ごとに組分けされ、組分けされた単位ごとに(組P3ごとに)共通の電源制御回路400が設けられるので、上述の第1実施形態に比べて、回路規模を一層低減できる。

【0027】

(第2実施形態の変形例)

例えば図8に示すように、辺SDに近い方から数えて第1行目および第2行目の集合Gの各々に含まれる複数のタイル10については、3つのタイル10ごとに1つの組P4が構成されてもよい。図8の例では、組P4ごとに、共通の電源制御回路410が設けられている。電源制御回路410の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路410は、組P4に含まれる3つのタイル10の各々に対する電源電位VDの供給および停止を制御する。一方、組P4に含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0028】

(第3実施形態)

次に、第3実施形態について説明する。第3実施形態では、使用される入出力部30(辺SD)の付近に形成される組に属するタイル10の数が、組ごとに可変に設定される点で上述の各実施形態と相違する。以下では、上述の各実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0029】

図9において、辺SDの付近に形成される3つの組(P51、P52、P53)に着目して説明する。図9に示す3つの組(P51、P52、P53)の各々に含まれるタイル10の数は、個別に設定される。組P51は、上述の第2実施形態と同様に、辺SDに近い方から数えて第1行目および第2行目の集合Gの各々に含まれる複数のタイル10のうちの何れか4つのタイル10(2行×2列の4つのタイル10)で構成される。その右隣に形成される組P52は、上述の第1実施形態と同様に、辺SDの延在方向に直交する方向(列方向)において、当該辺SDに近い方から数えて第1番目と第2番目のタイル10で構成される。その右隣に形成される組P53は、上述の第1実施形態の変形例と同様に、辺SDに近い方から数えて第1行目の集合Gに含まれる複数のタイル10のうちの何れか2つのタイル10で構成される。そして、組(P51、P52、P53)ごとに、当該組に含まれるタイル10に対する電力の供給および停止を制御する電源制御回路が設けられる。本実施形態では、辺SDの付近においては、上述の3種類の組(P51、P52、P53)が繰り返し形成され、上述の3種類の組(P51、P52、P53)のうちの何れかに含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0030】

図9の例では、組P51については、組P51に含まれる4つのタイル10に対する電力の供給および停止を制御する電源制御回路420が設けられる。電源制御回路420の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路420は、組P51に含まれる4つのタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P52については、組P52に含まれる2つのタイル10に対する電力の供給および停止を制御する電源制御回路430が設けられる。電源制御回路430の基本的な構成は、図5に示す電源制御回路40と同様である。さらに、組P53については、組P53に含まれる2つのタイル10に対する電力の供給および停止を制御する電源制御回路440が設けられる。電源制御回路440の基本的な構成は、図5に示す電源制御回路40と同様である。

【0031】

(第3実施形態の変形例)

上述した内容に限らず、辺SDの付近に形成される組に含まれるタイル10の数は任意に設定可能である。例えば図10に示すように、辺SDの付近に配置されたタイル10(動作確率が所定値以上のタイル10)のうち、E(E≧2)個のタイル10でひとつの組P54が形成され、当該組P54の右隣には、F個(FはEとは異なる2以上の整数)のタイル10でひとつの組P55が形成されてもよい。なお、組P54または組P55に含まれるタイル10は、第1行目の集合Gおよび第2行目の集合Gの各々に含まれるタイル10に限定されず、第3行目以降の集合Gに含まれるタイル10であってもよい。

【0032】

図10の例でも、組(P54、P55)ごとに、当該組に含まれるタイル10に対する電力の供給および停止を制御する電源制御回路が設けられる。本実施形態では、辺SDの付近においては、上述の2種類の組(P54、P55)が繰り返し形成され、上述の2種類の組(P54、P55)のうちの何れかに含まれるタイル10以外の他のタイル10については、電源制御回路50が個別に設けられる。

【0033】

図10の例では、組P54については、組P54に含まれるE個のタイル10に対する電力の供給および停止を制御する電源制御回路450が設けられる。電源制御回路450の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路450は、組P54に含まれるE個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P55については、組P55に含まれるF個のタイル10に対する電力の供給および停止を制御する電源制御回路460が設けられる。電源制御回路460の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路460は、組P55に含まれるF個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0034】

例えばFPGA100全体で実現される論理が限定的であれば、使用される頻度が高い領域(動作確率が高いタイル10が属する領域)も限定されるので、その使用される頻度が高い領域に、タイル数が多い組を形成し、当該組に対応する電源制御回路を設けることで、回路規模を一層低減できる。一方、使用される頻度が低い領域については、タイル数が少ない組(タイル数が1つの組であってもよい)を形成し、当該組に対応する電源制御回路を設けることで、効率よく電力を削減することができる。

【0035】

(第4実施形態)

次に、第4実施形態について説明する。第4実施形態では、電源制御回路が共通化されるタイル10の組分けが段階的に行われ、使用される入出力部30(辺SD)に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、使用される入出力部30(辺SD)から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされる点で上述の各実施形態と相違する。以下では、上述の各実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0036】

図11において、辺SDに近いタイル10ほど、同じ組に含まれるタイル10の数が多く、辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされた3つの組(P61、P62、P63)に着目して説明する。組P61は、動作確率が第1基準値以上の複数のタイル10のうちの何れかN個(N>1)のタイル10で構成される。組P62は、動作確率が第2基準値以上であって、かつ第1基準値未満の複数のタイルのうちの何れかM個(M>1、M<N)のタイル10で構成される。組P63は、動作確率が第2基準値未満の複数のタイルのうちの何れかL個(L≧1、L<M)のタイル10で構成される。

【0037】

図11の例では、組P61については、組P61に含まれるN個のタイル10に対する電力の供給および停止を制御する電源制御回路470が設けられる。電源制御回路470の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路470は、組P61に含まれるN個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P62については、組P62に含まれるM個のタイル10に対する電力の供給および停止を制御する電源制御回路480が設けられる。電源制御回路480の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路480は、組P62に含まれるM個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。さらに、組P63については、組P63に含まれるL個のタイル10に対する電力の供給および停止を制御する電源制御回路490が設けられる。電源制御回路490の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路490は、組P63に含まれるL個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0038】

すなわち、本実施形態のFPGAは、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(例えば組P63)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30に近い位置に配置される第2回路群(例えば組P61)と、第1論理ブロックよりも多く、第2論理ブロックよりも少ない数の論理ブロックLB(「第3論理ブロック」)を含み、第2回路群よりも当該入出力部30から遠い位置に配置され、第1回路群よりも当該入出力部30に近い位置に配置される第3回路群(例えば組P62)と、を備えると捉えることができる。

【0039】

そして、第1回路群は、第1論理ブロック、第2論理ブロックおよび第3論理ブロックのうちの何れかと入出力部30との接続、第1論理ブロック同士の接続、第2論理ブロックまたは第3論理ブロックと第1論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、組P63に含まれるL個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、組P63に含まれるL個のタイル10の各々に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路490)を有する。また、第2回路群は、第1論理ブロック、第2論理ブロックおよび第3論理ブロックのうちの何れかと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックまたは第3論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P61に含まれるN個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P61に含まれるN個のタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路470)を有する。さらに、第3回路群は、第1論理ブロック、第2論理ブロックおよび第3論理ブロックのうちの何れかと入出力部30との接続、第3論理ブロック同士の接続、第1論理ブロックまたは第2論理ブロックと第3論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第3スイッチブロック(この例では、組P62に含まれるM個のタイル10の各々に含まれるスイッチブロックSB)と、当該第3回路群に含まれる第3論理ブロック(この例では、組P62に含まれるM個のタイル10の各々に含まれる論理ブロックLB)および第3スイッチブロックに対して電力の供給および停止を共通に制御する第3電源制御回路(この例では、電源制御回路480)を有すると捉えることができる。以上の構成でも、全てのタイル10に対して電源制御回路50が個別に設けられる構成に比べて、回路規模を低減できる。

【0040】

(第4実施形態の変形例1)

例えばユーザーが、使用される入出力部30を自由に指定可能な場合は、図12に示すように、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、4つの辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされてもよい。すなわち、組が形成される領域の大きさが点対称となるように組が形成されてもよい。図12の例では、略矩形状のアレイ部20の4隅の付近に配置される入出力部30が使用され、当該入出力部30に近いタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0041】

(第4実施形態の変形例2)

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)のうち、互いに対向する2つの辺SD1および辺SD3が使用される場合を想定する。この場合は、図13に示すように、2つの辺SD1および辺SD3に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、2つの辺SD1および辺SD3から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされるので、辺SD1および辺SD3の付近に配置されたタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0042】

(第4実施形態の変形例3)

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)のうち、辺SD1が使用される場合を想定する。この場合は、図14に示すように、辺SD1に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、辺SD1から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされるので、辺SD1の付近に配置されたタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0043】

(第4実施形態の変形例4)

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)のうち、辺SD1と辺SD4との角C1の近くの入出力部30が使用される場合を想定する。この場合は、図15に示すように、角C1に近いタイル10ほど、同じ組に含まれるタイル10の数が多く、角C1から遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされるので、角C1の付近に配置されたタイル10が使用されるように配置配線される論理を実現する場合において特に有効であり、回路規模を低減しつつ電力量を削減できる。

【0044】

(第5実施形態)

次に、第5実施形態について説明する。第5実施形態では、使用される入出力部30に近い位置に形成される組に含まれるタイルの数は、当該組よりも、使用される入出力部30から遠い位置に形成される組に含まれるタイルの数よりも少ない点で上述の各実施形態と相違する。以下では、上述の各実施形態と共通する部分については、同一の符号を付して適宜に説明を省略する。

【0045】

図16において、使用される複数の入出力部30で構成される辺SDに近いタイル10ほど、同じ組に含まれるタイル10の数が少なく、当該辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が多くなるように組分けされた2つの組(P71、P72)に着目して説明する。組P71は、動作確率が第1基準値以上の複数のタイルのうちの何れかi個(i≧1)のタイル10で構成される。組P72は、動作確率が第1基準値未満の複数のタイルのうちの何れかj個(j>1、j>i)のタイル10で構成される。

【0046】

図16の例では、組P71については、組P71に含まれるi個のタイル10に対する電力の供給および停止を制御する電源制御回路4000が設けられる。電源制御回路4000の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4000は、組P71に含まれるi個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P72については、組P72に含まれるj個のタイル10に対する電力の供給および停止を制御する電源制御回路4010が設けられる。電源制御回路4010の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4010は、組P72に含まれるj個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0047】

すなわち、本実施形態のFPGAは、少なくとも1つの論理ブロックLBを含む第1回路群(例えば組P71)と、第1回路群よりも多い数の論理ブロックLBを含み、第1回路群よりも、使用される入出力部30から遠い位置に配置される第2回路群(例えば組P72)とを備えると捉えることができる。そして、第1回路群は、第1スイッチブロック(この例では、組P71に含まれるi個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる論理ブロックLBおよび第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路4000)とを有する。また、第2回路群は、第2スイッチブロック(この例では、組P72に含まれるj個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる論理ブロックLBおよび第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路4010)とを有すると捉えることができる。

【0048】

(第5実施形態の変形例)

例えば使用される入出力部30に最も近い位置に形成される第1の組(当該入出力部30と第1の組との間には他の組(回路群)は存在しないと捉えることができる)に含まれるタイル10の数は、第1の組よりも入出力部30から遠い位置に形成される第2の組に含まれるタイル10の数よりも少なく、第2の組よりも入出力部30から遠い位置に形成される第3の組に含まれるタイル10の数は、第2の組に含まれるタイル10の数よりも少なくなるように、組分けすることもできる。つまりは、上述の第1の組に含まれるタイル10以外のタイル10については、辺SDに近いタイル10ほど、同じ組に含まれるタイル10の数が多く、辺SDから遠いタイル10ほど、同じ組に含まれるタイル10の数が少なくなるように組分けされてもよい。

【0049】

図17において、使用される複数の入出力部30で構成される辺SDに最も近い位置に形成された組P73、辺SDの直交方向において組P73と隣接するとともに当該組P73よりも辺SDから遠い位置に形成された組P74、および、辺SDの直交方向において組P74と隣接するとともに当該組P74よりも辺SDから遠い位置に形成された組P75に着目して説明する。組P73は、動作確率が第1基準値以上の複数のタイル10のうちの何れかq個のタイル10で構成される。組P74は、動作確率が第2基準値以上であって、かつ第1基準値未満の複数のタイル10のうちの何れかr個のタイル10で構成される。組P75は、動作確率が第2基準値未満の複数のタイル10のうちの何れかs個のタイル10で構成される。組P73に含まれるタイル10の数qは、1以上であって、かつ、組P74に含まれるタイル10の数rよりも小さい。組P74に含まれるタイル10の数rは、1よりも大きい。組P75に含まれるタイルの数sは、1以上であって、かつ、組P74に含まれるタイル10の数rよりも小さい。

【0050】

図17の例では、組P73については、組P73に含まれるq個のタイル10に対する電力の供給および停止を制御する電源制御回路4020が設けられる。電源制御回路4020の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4020は、組P73に含まれるq個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。また、組P74については、組P74に含まれるr個のタイル10に対する電力の供給および停止を制御する電源制御回路4030が設けられる。電源制御回路4030の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4030は、組P74に含まれるr個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。さらに、組P75については、組P75に含まれるs個のタイル10に対する電力の供給を制御する電源制御回路4040が設けられる。電源制御回路4040の基本的な構成は、図5に示す電源制御回路40と同様であるが、電源制御回路4040は、組P75に含まれるs個のタイル10の各々に対する電源電位VDの供給および停止を共通に制御する。

【0051】

すなわち、本実施形態のFPGAは、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(例えば組P73)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30から遠い位置に配置される第2回路群(例えば組P74)と、第2論理ブロックよりも少ない数の論理ブロックLB(「第3論理ブロック」)を含み、第2回路群よりも、使用される入出力部30から遠い位置に配置される第4回路群(例えば組P75)とを備えると捉えることができる。

【0052】

そして、第1回路群は、第1論理ブロック、第2論理ブロックおよび第4論理ブロックのうちの何れかと入出力部30との接続、第1論理ブロック同士の接続、第2論理ブロックまたは第4論理ブロックと第1論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路4020)を有する。また、第2回路群は、第1論理ブロック、第2論理ブロックおよび第4論理ブロックのうちの何れかと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックまたは第4論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路4030)を有する。さらに、第4回路群は、第1論理ブロック、第2論理ブロック、および、第4論理ブロックのうちの何れかと入出力部30との接続、第4論理ブロック同士の接続、第1論理ブロックまたは第2論理ブロックと第4論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第4スイッチブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれるスイッチブロックSB)と、当該第4回路群に含まれる第4論理ブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれる論理ブロックLB)および第4スイッチブロックに対して電力の供給および停止を共通に制御する第4電源制御回路(この例では、電源制御回路4040)を有すると捉えることができる。

【0053】

また、本実施形態のFPGA100は、少なくとも1つの論理ブロックLB(「第1論理ブロック」)を含む第1回路群(例えば組P75)と、第1論理ブロックよりも多い数の論理ブロックLB(「第2論理ブロック」)を含み、第1回路群よりも、使用される入出力部30に近い位置に配置される第2回路群(例えば組P74)と、第2論理ブロックよりも少ない数の論理ブロックLB(「第5論理ブロック」)を含み、第2回路群よりも、使用される入出力部30に近い位置に配置される第5回路群(例えば組P73)とを備えると捉えることもできる。

【0054】

そして、第1回路群は、第1論理ブロック、第2論理ブロック、および、第5論理ブロックのうちの何れかと入出力部30との接続、第1論理ブロック同士の接続、第2論理ブロックまたは第5論理ブロックと第1論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第1スイッチブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれるスイッチブロックSB)と、当該第1回路群に含まれる第1論理ブロック(この例では、組P75に含まれるs個のタイル10の各々に含まれる論理ブロックLB)および第1スイッチブロックに対して電力の供給および停止を共通に制御する第1電源制御回路(この例では、電源制御回路4040)を有する。また、第2回路群は、第1論理ブロック、第2論理ブロック、および、第5論理ブロックのうちの何れかと入出力部30との接続、第2論理ブロック同士の接続、第1論理ブロックまたは第5論理ブロックと第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第2スイッチブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれるスイッチブロックSB)と、当該第2回路群に含まれる第2論理ブロック(この例では、組P74に含まれるr個のタイル10の各々に含まれる論理ブロックLB)および第2スイッチブロックに対して電力の供給および停止を共通に制御する第2電源制御回路(この例では、電源制御回路4030)を有する。さらに、第5回路群は、第1論理ブロック、第2論理ブロック、および、第5論理ブロックのうちの何れかと入出力部30との接続、第5論理ブロック同士の接続、第1論理ブロックまたは第2論理ブロックと第5論理ブロックとの接続のうちの少なくとも1つに用いられる配線(単数でも複数でもよい)の接続を、プログラム可能な制御データに応じて切り替えるスイッチ(単数でも複数でもよい)を含む第5スイッチブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれるスイッチブロックSB)と、第5回路群に含まれる第5論理ブロック(この例では、組P73に含まれるq個のタイル10の各々に含まれる論理ブロックLB)および第5スイッチブロックに対する電力の供給および停止を共通に制御する第5電源制御回路(この例では、電源制御回路4020)を有すると捉えることができる。

【0055】

例えば、アレイ部20を取り囲むように配列された複数の入出力部30で構成される4つの辺(SD1〜SD4)が使用される場合は、図18のように、組が形成されてもよい(組分けが行われてもよい)。

【0056】

また、例えば、辺SD1、辺SD2および辺SD4が使用される場合は、図19のように組が形成されてもよい。図19の例において、辺SD1の付近の矩形領域Tx内に含まれる論理ブロックLBが使用され、辺SD2のうち、辺SD1と辺SD2との角C2から、辺SD2に沿って所定距離だけ延在する部分PSD2が使用され、辺SD4のうち、辺SD1と辺SD4との角C1から、辺SD4に沿って所定距離だけ延在する部分PSD4が使用される場合を想定する。より具体的には、辺SD1に加え、PSD2およびPSD4を構成する入出力部30が使用される一方、使用される論理ブロックLBは、領域Tx内の論理ブロックLBのみである場合を想定する。つまりは、この例では、PSD2およびPSD4は配線として使用され、領域Tx内の論理ブロックLBから部分PSD2へ至る配線経路が形成されるように、部分PSD2に最も近い位置に形成される複数の組の各々に含まれるタイル10(スイッチブロックSB)が動作する。同様に、領域Tx内の論理ブロックLBから部分PSD4へ至る配線経路が形成されるように、部分PSD4に最も近い位置に形成される複数の組の各々に含まれるタイル10が動作する。

【0057】

図19の例では、使用される入出力部30に最も近い位置に形成される組(「第1の組」と呼ぶ)に含まれるタイル10の数は、当該第1の組と隣接するとともに当該第1の組よりも当該入出力部30から遠い位置に形成される第2の組に含まれるタイル10の数よりも少ないので、第1の組に含まれるタイル10の数が他の組に含まれるタイル10の数よりも多くなるように組分けされる場合(第1の組に含まれるタイル10の数が最も多くなるように組分けされる場合)に比べて、消費電力量を削減できる。すなわち、図19の例では、配線として使用されるPSD2(PSD4)に最も近い位置に形成される第1の組に含まれるタイル10の数を少なくすることで、配線として使用されるタイル10の数を減らしている。これにより、消費電力量を削減できる。

【0058】

以上、本発明の各実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【0059】

要するに、本発明が適用されるFPGAは、電源制御回路が共通化されるタイル10の数(特定の論理を実現可能な論理ブロックLBの数)が相違する2つの組(「第1回路群」、「第2回路群」)を少なくとも備えていればよい。これにより、特定の論理を実現可能な単位ごとに電源制御回路が個別に設けられる場合に比べて、回路規模を低減できる。

【0060】

また、上述の各実施形態および変形例では、FPGA内に形成される各組は、行方向に延在する複数の直線と、列方向に延在する複数の直線とで区切られているが、これに限らず、例えば図20のように、隣の組との境界線が一致しないように組分けすることもできる。

【0061】

また、上述の図5の例では、スイッチ素子41は、P型のMOSFETで構成されているが、これに限らず、スイッチ素子41の構成は任意である。要するに、電源制御回路40は、対応する組P1に対する電力の供給および停止を制御可能な構成であればよく、その構成は図5の構成に限られない。以下のバリエーションの例では、スイッチ素子41に対応する組P1に含まれるタイル10の数が3つである場合を例に挙げて説明する。

【0062】

例えば図21に示すように、スイッチ素子41は、N型のMOSFETで構成されてもよい。また、スイッチ素子41がN型のMOSFETで構成される場合、例えば図22に示すように、電源電位VDが供給される電源線(不図示)と、接地電位GND(例えば0V)が供給される接地線102との間に組P1が配置され、組P1と接地線102との間に電源制御回路40が配置される構成であってもよい。

【0063】

また、例えば図23および図24に示すように、P型のMOSFETあるいはN型のMOSFETで構成されるスイッチ素子41が、組P1に含まれる3つのタイル10の各々と、電源線101との間に個別に設けられる構成であってもよい。この構成では、3つのスイッチ素子41の各々のゲートは制御回路42に共通に接続され、3つのスイッチ素子41のオンオフは、制御回路42からのスイッチ制御信号に応じて一斉に制御される。この構成であっても、組P1に対応して設けられる制御回路42はひとつで済むので、タイル10ごとに制御回路42が個別に設けられる場合に比べて、回路規模を低減できる。ただし、上述の各実施形態および変形例のように、組P1に含まれる3つのタイル10の各々に対する電力の供給および停止を切り替えるスイッチ素子41を共通化することにより、さらなる回路規模の低減を図ることが可能になる。

【0064】

さらに、例えば図25に示すように、N型のMOSFETで構成されるスイッチ素子41が、組P1に含まれる3つのタイル10の各々と、接地線102との間に個別に設けられる構成であってもよい。

【符号の説明】

【0065】

10 タイル

20 アレイ部

30 入出力部

40 電源制御回路

41 スイッチ素子

42 制御回路

50 電源制御回路

101 電源線

102 接地線

【特許請求の範囲】

【請求項1】

第1論理ブロックを少なくとも1つ含む第1回路群と、

前記第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、

入力データを前記第1論理ブロックまたは前記第2論理ブロックへ入力する機能、および、前記第1論理ブロックまたは前記第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部と、を含み、

前記第1回路群は、

前記第1論理ブロックまたは前記第2論理ブロックと前記入出力部との接続、前記第1論理ブロック同士の接続、前記第1論理ブロックと前記第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第1スイッチブロックと、

前記第1回路群に含まれる前記第1論理ブロックおよび前記第1スイッチブロックに対する電力の供給および停止を共通に制御する第1電源制御回路と、を有し、

前記第2回路群は、

前記第1論理ブロックまたは前記第2論理ブロックと前記入出力部との接続、前記第2論理ブロック同士の接続、前記第1論理ブロックと前記第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第2スイッチブロックと、

前記第2回路群に含まれる前記第2論理ブロックおよび前記第2スイッチブロックに対する電力の供給および停止を共通に制御する第2電源制御回路と、を有する、

半導体集積回路。

【請求項2】

前記第2回路群は、前記第1回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される、

請求項1の半導体集積回路。

【請求項3】

前記第1論理ブロックよりも多く、前記第2論理ブロックよりも少ない数の第3論理ブロックを含み、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部から遠い位置に配置され、前記第1回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される第3回路群をさらに備え、

前記第3回路群は、

前記第1論理ブロック、前記第2論理ブロックおよび前記第3論理ブロックのうちの何れかと前記入出力部との接続、前記第3論理ブロック同士の接続、前記第1論理ブロックまたは前記第2論理ブロックと前記第3論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第3スイッチブロックと、

前記第3回路群に含まれる前記第3論理ブロックおよび前記第3スイッチブロックに対する電力の供給および停止を共通に制御する第3電源制御回路と、を有する、

請求項2の半導体集積回路。

【請求項4】

前記第1回路群は、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される、

請求項1の半導体集積回路。

【請求項5】

前記入力データの入力または前記出力データの出力を行う前記入出力部と前記第1回路群との間には他の論理ブロックを含む回路群は存在しない、

請求項4の半導体集積回路。

【請求項6】

前記第2論理ブロックよりも少ない数の第4論理ブロックを含み、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部から遠い位置に配置される第4回路群をさらに備え、

前記第4回路群は、

前記第1論理ブロック、前記第2論理ブロック、および、前記第4論理ブロックのうちの何れかと前記入出力部との接続、前記第4論理ブロック同士の接続、前記第1論理ブロックまたは前記第2論理ブロックと前記第4論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第4スイッチブロックと、

前記第4回路群に含まれる前記第4論理ブロックおよび前記第4スイッチブロックに対する電力の供給および停止を共通に制御する第4電源制御回路と、を有する、

請求項5の半導体集積回路。

【請求項7】

前記第2論理ブロックよりも少ない数の第5論理ブロックを含み、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される第5回路群をさらに備え、

前記第5回路群は、

前記第1論理ブロック、前記第2論理ブロック、および、前記第5論理ブロックのうちの何れかと前記入出力部との接続、前記第5論理ブロック同士の接続、前記第1論理ブロックまたは前記第2論理ブロックと前記第5論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第5スイッチブロックと、

前記第5回路群に含まれる前記第5論理ブロックおよび前記第5スイッチブロックに対する電力の供給および停止を共通に制御する第5電源制御回路と、を有する、

請求項2または請求項3の半導体集積回路。

【請求項8】

前記第2回路群に含まれる前記論理ブロックは、前記第1回路群に含まれる論理ブロックよりも、電力が供給されて動作する可能性を示す動作確率が高い、

請求項2の半導体集積回路。

【請求項9】

前記動作確率は、以下の式で表される、

請求項7の半導体集積回路。

f(D)=1/[exp{(D−μ)/C}+1]

ただし、f(D)は、前記入力データの入力または前記出力データの出力を行う前記入出力部から距離Dの位置に配置された前記論理ブロックの動作確率を示し、μは、前記論理ブロックが、当該入出力部に近い順から使用された場合の当該入出力部からの距離を示し、Cは、前記論理ブロックの当該入出力部からの離れやすさを示す定数である。

【請求項1】

第1論理ブロックを少なくとも1つ含む第1回路群と、

前記第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、

入力データを前記第1論理ブロックまたは前記第2論理ブロックへ入力する機能、および、前記第1論理ブロックまたは前記第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部と、を含み、

前記第1回路群は、

前記第1論理ブロックまたは前記第2論理ブロックと前記入出力部との接続、前記第1論理ブロック同士の接続、前記第1論理ブロックと前記第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第1スイッチブロックと、

前記第1回路群に含まれる前記第1論理ブロックおよび前記第1スイッチブロックに対する電力の供給および停止を共通に制御する第1電源制御回路と、を有し、

前記第2回路群は、

前記第1論理ブロックまたは前記第2論理ブロックと前記入出力部との接続、前記第2論理ブロック同士の接続、前記第1論理ブロックと前記第2論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第2スイッチブロックと、

前記第2回路群に含まれる前記第2論理ブロックおよび前記第2スイッチブロックに対する電力の供給および停止を共通に制御する第2電源制御回路と、を有する、

半導体集積回路。

【請求項2】

前記第2回路群は、前記第1回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される、

請求項1の半導体集積回路。

【請求項3】

前記第1論理ブロックよりも多く、前記第2論理ブロックよりも少ない数の第3論理ブロックを含み、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部から遠い位置に配置され、前記第1回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される第3回路群をさらに備え、

前記第3回路群は、

前記第1論理ブロック、前記第2論理ブロックおよび前記第3論理ブロックのうちの何れかと前記入出力部との接続、前記第3論理ブロック同士の接続、前記第1論理ブロックまたは前記第2論理ブロックと前記第3論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第3スイッチブロックと、

前記第3回路群に含まれる前記第3論理ブロックおよび前記第3スイッチブロックに対する電力の供給および停止を共通に制御する第3電源制御回路と、を有する、

請求項2の半導体集積回路。

【請求項4】

前記第1回路群は、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される、

請求項1の半導体集積回路。

【請求項5】

前記入力データの入力または前記出力データの出力を行う前記入出力部と前記第1回路群との間には他の論理ブロックを含む回路群は存在しない、

請求項4の半導体集積回路。

【請求項6】

前記第2論理ブロックよりも少ない数の第4論理ブロックを含み、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部から遠い位置に配置される第4回路群をさらに備え、

前記第4回路群は、

前記第1論理ブロック、前記第2論理ブロック、および、前記第4論理ブロックのうちの何れかと前記入出力部との接続、前記第4論理ブロック同士の接続、前記第1論理ブロックまたは前記第2論理ブロックと前記第4論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第4スイッチブロックと、

前記第4回路群に含まれる前記第4論理ブロックおよび前記第4スイッチブロックに対する電力の供給および停止を共通に制御する第4電源制御回路と、を有する、

請求項5の半導体集積回路。

【請求項7】

前記第2論理ブロックよりも少ない数の第5論理ブロックを含み、前記第2回路群よりも、前記入力データの入力または前記出力データの出力を行う前記入出力部に近い位置に配置される第5回路群をさらに備え、

前記第5回路群は、

前記第1論理ブロック、前記第2論理ブロック、および、前記第5論理ブロックのうちの何れかと前記入出力部との接続、前記第5論理ブロック同士の接続、前記第1論理ブロックまたは前記第2論理ブロックと前記第5論理ブロックとの接続のうちの少なくとも1つに用いられる配線の接続を、プログラム可能な制御データに応じて切り替えるスイッチを含む第5スイッチブロックと、

前記第5回路群に含まれる前記第5論理ブロックおよび前記第5スイッチブロックに対する電力の供給および停止を共通に制御する第5電源制御回路と、を有する、

請求項2または請求項3の半導体集積回路。

【請求項8】

前記第2回路群に含まれる前記論理ブロックは、前記第1回路群に含まれる論理ブロックよりも、電力が供給されて動作する可能性を示す動作確率が高い、

請求項2の半導体集積回路。

【請求項9】

前記動作確率は、以下の式で表される、

請求項7の半導体集積回路。

f(D)=1/[exp{(D−μ)/C}+1]

ただし、f(D)は、前記入力データの入力または前記出力データの出力を行う前記入出力部から距離Dの位置に配置された前記論理ブロックの動作確率を示し、μは、前記論理ブロックが、当該入出力部に近い順から使用された場合の当該入出力部からの距離を示し、Cは、前記論理ブロックの当該入出力部からの離れやすさを示す定数である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図14】

【図15】

【図16】

【図17】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図12】

【図13】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図14】

【図15】

【図16】

【図17】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図12】

【図13】

【図18】

【図19】

【公開番号】特開2013−115109(P2013−115109A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257559(P2011−257559)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]