半導体集積回路

【課題】半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させる。

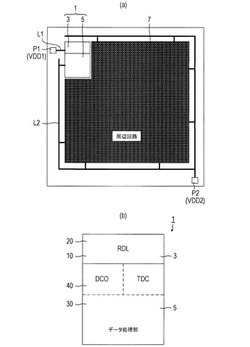

【解決手段】ICチップは周辺部を除く部位に位置する回路形成部位が、パルス遅延回路10からなる第1回路ブロック3と、時間/数値変換回路20及びデータ処理部30,デジタル制御発振回路40からなる第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。また、第1回路ブロック3は、電源パッドP1及び電源ラインL1を介して供給される第1の電源VDD1により駆動され、第2回路ブロック5及び第3回路ブロック7は、電源パッドP2及び電源ラインL2を介して供給される第2の電源VDD2により駆動されるように、レイアウトされている。

【解決手段】ICチップは周辺部を除く部位に位置する回路形成部位が、パルス遅延回路10からなる第1回路ブロック3と、時間/数値変換回路20及びデータ処理部30,デジタル制御発振回路40からなる第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。また、第1回路ブロック3は、電源パッドP1及び電源ラインL1を介して供給される第1の電源VDD1により駆動され、第2回路ブロック5及び第3回路ブロック7は、電源パッドP2及び電源ラインL2を介して供給される第2の電源VDD2により駆動されるように、レイアウトされている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基準信号の周波数を逓倍又は分周したクロック信号を発生させる回路を実現する半導体集積回路に関する。

【背景技術】

【0002】

従来、水晶発振子などを用いて生成された周波数の安定した基準信号に基づき、その基準信号の周期を、基準信号より十分に高い周波数を有する高速クロック信号でカウントし、そのカウント値に基づいて、基準信号の周期を逓倍又は分周したクロック信号を得るデジタル制御発振装置が知られている(例えば、特許文献1参照)。

【0003】

このデジタル制御発振装置101は、図4に示すように、リング状に連結したm個の遅延ユニットDUからなり、パルス信号を順次遅延して周回させるパルス遅延回路10と、このパルス遅延回路10を構成する各遅延ユニットDUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの立ち上がりから次の立ち上がりまでの位相差を2進デジタル値に変換してなる周期データDPを生成する時間/数値変換回路(TDC)20と、TDC20にて得られた周期データDPを被除数又は被乗数とし、外部より入力され逓倍数又は分周数を表す設定値Nを除数又は乗数とした演算を行うことで、クロック信号の出力周期を表す制御データDCを生成するデータ処理部30と、データ処理部30から出力される制御データDCと、パルス遅延回路10から順次出力される通過信号P1〜Pmとに基づき、基準信号CKIを逓倍又は分周したクロック信号CKOを出力するデジタル制御発振回路(DCO)40とを備えている。

【0004】

つまり、TDC20は、遅延ユニットDUの遅延時間を単位時間として、基準信号CKIの周期を周期データDPに変換(数値化)し、また、DCO40は、遅延ユニットDUの遅延時間を単位時間として、制御データDCに応じた周期を有するクロック信号CKOを発生させるように構成されている(例えば、特許文献1参照。)。

【0005】

なお、このようなデジタル制御発振装置101は、デジタル回路だけで構成されているため、半導体集積回路によって実現するのに好適である。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平7−183800号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、TDC20では、基準クロックCKIの立ち上がりエッジ又は立ち下がりエッジのいずれか一方を測定タイミングとして、測定タイミング毎にパルス遅延回路10の出力をラッチすることで、最初の測定タイミングから今回の測定タイミングまでにパルスが通過した遅延ユニットDUの段数を求め、更に、前回の測定タイミングで得られた段数との差分を求めることで、周期データDPを算出しているため、測定タイミングから周期データDPが出力されるまでに基準クロックCKIで少なくとも1クロック分の遅延が生じる。また、データ処理部30でも除算又は乗算のための演算時間が必要であり少なくとも1クロック分の遅延が生じる。

【0008】

つまり、TDC20が周期データDPを生成するタイミングと、その周期データDPから算出される制御データDCに基づいて、DCO40がクロック信号CKOを発生させるタイミングとでは、基準クロックCKIで少なくとも2〜3クロック分の時間差(ずれ)が生じることになる。従って、その時間差の間に電源電圧が変動して、遅延ユニットDUの遅延時間が変化すると、TDC20が制御データDCを生成する際に用いた単位時間と、DCO40がクロック信号CKOを発生させる際に用いる単位時間とが異なったものとなる。その結果、クロック信号CKOの周波数変動(ゆらぎ)やジッタが増大して、クロック信号CKOの品質を低下させてしまうため、クロック信号CKOの品質を保持するには、大きな電流が流れても安定した電源電圧を維持することができる高価な電源回路を用いる必要があった。

【0009】

また、半導体集積回路の回路製造プロセスの高度化(微細化プロセスの採用)に伴い、回路ブロックのレイアウトの自由度が向上する一方で、電源パターン幅の微細化による配線抵抗が増大する傾向にあるだけでなく、デジタル制御発振装置と共に同一IC(半導体集積回路)チップに搭載される周辺回路の規模の増大により電源パターンを流れる電流も増大する傾向にある。

【0010】

このため、ICチップ内の配線パターンで生じる電圧降下の影響が大きくなり、上述のような高価な電源回路を用いたとしても、パルス遅延回路10を駆動する電源電圧を一定に保持することが困難な状況になりつつあるという問題があった。

【0011】

ここで、ICチップに搭載されたデジタル制御発振装置について考える。但し、遅延ユニットは、図5に示すような、電源電圧対遅延時間特性を有するものとする。

また、ICチップでのアルミ配線のシート抵抗値50mΩ、アルミ配線幅100μmであり、電源パッドからパルス遅延回路までの電源パターンの配線長を1mmと想定する。

【0012】

この場合、電源パターンの配線抵抗は0.5Ωとなり、電源電流が100mA流れると、電源電圧は0.05V降下する。

つまり、ICチップの電源パッドに印加される電源電圧を1.5Vとすると、電源パターンに100mAの電流が流れたとすると、パルス遅延回路に印加される電源電圧は、1.45Vに低下する。すると、図5からわかるように、遅延ユニットの遅延時間は4.5%程度変化し、これに伴って、デジタル制御発振装置が出力するクロック信号の周波数も同程度揺らぐことになる。

【0013】

仮に、ICチップ内において、デジタル制御発振装置を電源パッドの直近に配置できたとしても、配線長を0.3mm以下にすることは困難であり、この場合でも、電源電流が100mA流れると15mVの電圧降下が生じ、遅延ユニットの遅延時間、ひいてはクロック信号の周波数が1.3%程度揺らぐことになる。

【0014】

なお、このような問題は、回路製造プロセスの微細化が進むに従って、より顕著なものとなる。

本発明は、上記問題点を解決するために、半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させることを目的とする。

【課題を解決するための手段】

【0015】

上記目的を達成するためになされた発明である請求項1に記載の半導体集積回路は、入力電圧に応じた遅延時間でパルス信号を遅延させる遅延ユニットを複数段接続してなるパルス遅延回路と、予め設定された基準信号を入力し、該基準信号の1周期の間に、前記パルス遅延回路にて前記パルス信号が通過した前記遅延ユニットの段数を検出して符号化することにより、前記遅延ユニットの平均遅延時間を単位として、前記基準信号の周期を表した周期データを生成する周期測定部と、逓倍数又は分周数を表す設定値を除数又は乗数とし、前記周期データを被除数又は被定数とした演算を実行することにより、前記基準信号の周波数を逓倍又は分周することで得られる信号の周期を表した制御データを生成するデータ処理部と、前記パルス遅延回路を構成する各遅延ユニットからの出力である通過信号に基づいて、前記制御データに示された周期を有するクロック信号を生成する出力部とを備えている。なお、パルス遅延回路、周期測定部、データ処理部、出力部は、設定値によって設定される任意の周期を有したクロック信号を発生させる、いわゆるデジタル制御発振装置を構成している。

【0016】

そして、少なくともパルス遅延回路を含む第1回路ブロックを第1の電源で駆動し、少なくともデータ処理部を含む第2回路ブロックを第1の電源とは異なる第2の電源で駆動するように電源パターンが配線されている。

【0017】

このように構成された本発明の半導体集積回路によれば、第1回路ブロックの電源電圧が、第2ブロックで消費される動作電流の影響を受けることがないため、第1の電源の電圧変動を抑制すること、ひいてはパルス遅延回路を構成する遅延ユニットの遅延時間の変動を抑制することができる。

【0018】

その結果、基準信号の周期を周期データに変換する際の単位時間と、制御データからクロック信号を生成する際の単位時間とが異なることによって生じるクロック信号の周波数のゆらぎやジッタを抑制することができ、出力部から出力されるクロック信号の品質を向上させることができる。

【0019】

また、第1の電源は、第1回路ブロックを駆動できるだけの駆動能力があればよいため、大きな電流が流れても安定した電源電圧を維持するために必要であった構成を省略することができ、装置を簡略化することができる。

【0020】

なお、周期測定部及び出力部については、請求項2に記載のように、これらのうち少なくとも一方が第2回路ブロックに含まれ、残りが第1回路ブロックに含まれていてもよい。

【0021】

つまり、パルス遅延回路だけで構成されていることが望ましいが、第1回路ブロックに流れる電流の変動に基づく遅延ユニットの遅延時間の変動が許容範囲内に納まっていればよいため、その条件を満たすのであれば、第1回路ブロックに、周期測定部又は出力部のいずれか一方が含まれていてもよい。

【0022】

ところで、本発明の半導体集積回路が、出力部が生成するクロック信号を利用して動作する後段処理部を備えている場合、請求項3に記載のように、第2の電源で後段処理部を駆動するように電源パターンが配線されていてもよいし、請求項4に記載のように、第1の電源及び第2の電源とは異なる第3の電源で後段処理部を駆動するように電源パターンが配線されていてもよい。

【0023】

いずれにしてもパルス遅延回路を、後段処理部に流れる電流の影響を受けることなく動作させることができる。

【図面の簡単な説明】

【0024】

【図1】実施形態におけるデジタル制御発振装置の全体構成及び電源系統を示すブロック図である。

【図2】デジタル制御発振装置を搭載したICチップのレイアウト及び電源パターンを模式的に示した説明図である。

【図3】変形例におけるレイアウト及び電源パターンを模式的に示した説明図である。

【図4】従来装置におけるデジタル制御発振装置の構成を示すブロック図である。

【図5】遅延ユニットの電源電圧対遅延時間の特性を示すグラフである。

【発明を実施するための形態】

【0025】

以下に本発明の実施形態を図面と共に説明する。

<全体構成>

図1は、デジタル制御発振装置1の全体構成及び電源系統を示すブロック図である。

【0026】

デジタル制御発振装置1は、従来装置で説明いたデジタル制御発振装置101と同様に、パルス遅延回路10、時間/数値変換回路(TDC)20、データ処理部30、デジタル制御発振回路(DCO)40により構成されている。

【0027】

但し、デジタル制御発振装置1では、パルス遅延回路10を第1回路ブロック3、TDC20及びデータ処理部30,DCO40を第2回路ブロック5として、第1回路ブロック3は、第1の電源VDD1により駆動され、第2回路ブロック5は、第1の電源CDD1とは異なる第2の電源VDD2により駆動されるように構成されている。

【0028】

なお、デジタル制御発振装置1各部の具体的な構成は、例えば、特開平7−183800号公報や特開2000−152886号公報等に詳述された周知のものであるため、ここでは説明を省略する。

【0029】

<レイアウト>

図2は、デジタル制御発振装置1を搭載したIC(半導体集積回路)チップのレイアウト及び電源パターンを模式的に示した説明図である。

【0030】

図2に示すように、ICチップは周辺部を除く部位に位置する回路形成部位が、第1回路ブロック3と、第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。

【0031】

但し、第1回路ブロック3は回路形成部位の角部四隅のうち一隅(図では左上隅)を占めるように形成され、第2回路ブロック5は、第1回路ブロック3に隣接して(図では下側に)設けられている。

【0032】

また、ICチップの周辺部には、第1の電源VDD1に接続される電源パッドP1,第2の電源VDD2に接続される電源パッドP2が設けられていると共に、電源パッドP1から第1回路ブロック3に至る電源パターンL1,電源パッドP2から第2回路ブロック5及び第3回路ブロック7に至る電源パターンL2が配線されている。

【0033】

但し、電源パッドP1は、第1回路ブロック3との間を接続する電源パターンL1が最短となる位置に設けられ、電源パッドP2は、電源パッドP1が設けられた隅とは対角に位置する隅に設けられている。

【0034】

<効果>

上述のようにICチップ上でレイアウトされたデジタル制御発振装置1によれば、第1回路ブロック3を駆動する第1の電源VDD1の電圧が、第2回路ブロック5や第3回路ブロック7に流れる動作電流の影響を受けることがないだけでなく、電源パターンL1による電圧降下が必要最小限に抑えられるため、第1の電源VDD1の電圧変動を抑制することができ、ひいてはパルス遅延回路10を構成する遅延ユニットDUの遅延時間の変動を抑制することができる。

【0035】

その結果、基準信号CKIの周期を周期データDPに変換する際の単位時間と、制御データDCからクロック信号CKOを生成する際の単位時間とが異なることによって生じるクロック信号CKOの周波数のゆらぎやジッタを抑制することができ、DCO40から出力されるクロック信号CKOの品質を向上させることができる。

【0036】

また、第1の電源VDD1は、第1回路ブロック3を駆動できるだけの駆動能力があればよく、電源電圧を安定化させるために高性能な電源回路を用いる必要がないため、装置を簡略化することができる。

【0037】

なお、本実施形態において、時間/数値変換回路(TDC)20が周期測定部、デジタル制御発振回路(DCO)40が出力部、第3回路ブロック3を構成する周辺回路が後段処理部に相当する。

【0038】

<他の実施形態>

以上本発明の一実施形態について説明したが、本発明は上記実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において様々な態様にて実施することができる。

【0039】

例えば、上記実施形態では、第2回路ブロック5及び第3回路ブロック7を、電源パッドP2,電源パターンL2を介して第2の電源VDD2によって駆動するように構成されているが、図3に示すように、第2回路ブロック5を電源パッドP2,電源パターンL2を介して第2の電源VDD2によって駆動し、第3回路ブロック7を電源パッドP3及び電源ラインL3を介して第3の電源VDD3によって駆動するように構成されていてもよい。

【0040】

また、上記実施形態では、パルス遅延回路10だけで第1回路ブロック3が構成されているがこれに限るものではなく、第1回路ブロック3を、パルス遅延回路10とTDC20とで構成したり、パルス遅延回路10とDCO40とで構成したりしてもよい。この場合、デジタル制御発振装置1のうち第1回路ブロック3に含まれる構成以外を第2回路ブロック5として構成すればよい。

【0041】

更に上記実施形態では、DCO40を、基準信号CKIの周期と設定値Nとで決まる周期を有したクロック信号CKOを生成するように構成されているが、例えば、予め設定されたタイミングから基準信号CKIの周期と設定値Nとで決まる時間だけ経過した時点でパルス信号を1回だけ発生させるように構成されていてもよい。

【符号の説明】

【0042】

1…デジタル制御発振装置 3…第1回路ブロック 5…第2回路ブロック 7…第3回路ブロック 10…パルス遅延回路 20…時間/数値変換回路(TDC) 30…データ処理部 40…デジタル制御発振回路(DCO) L1〜L3…電源パターン P1〜P3…電源パッド

【技術分野】

【0001】

本発明は、基準信号の周波数を逓倍又は分周したクロック信号を発生させる回路を実現する半導体集積回路に関する。

【背景技術】

【0002】

従来、水晶発振子などを用いて生成された周波数の安定した基準信号に基づき、その基準信号の周期を、基準信号より十分に高い周波数を有する高速クロック信号でカウントし、そのカウント値に基づいて、基準信号の周期を逓倍又は分周したクロック信号を得るデジタル制御発振装置が知られている(例えば、特許文献1参照)。

【0003】

このデジタル制御発振装置101は、図4に示すように、リング状に連結したm個の遅延ユニットDUからなり、パルス信号を順次遅延して周回させるパルス遅延回路10と、このパルス遅延回路10を構成する各遅延ユニットDUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの立ち上がりから次の立ち上がりまでの位相差を2進デジタル値に変換してなる周期データDPを生成する時間/数値変換回路(TDC)20と、TDC20にて得られた周期データDPを被除数又は被乗数とし、外部より入力され逓倍数又は分周数を表す設定値Nを除数又は乗数とした演算を行うことで、クロック信号の出力周期を表す制御データDCを生成するデータ処理部30と、データ処理部30から出力される制御データDCと、パルス遅延回路10から順次出力される通過信号P1〜Pmとに基づき、基準信号CKIを逓倍又は分周したクロック信号CKOを出力するデジタル制御発振回路(DCO)40とを備えている。

【0004】

つまり、TDC20は、遅延ユニットDUの遅延時間を単位時間として、基準信号CKIの周期を周期データDPに変換(数値化)し、また、DCO40は、遅延ユニットDUの遅延時間を単位時間として、制御データDCに応じた周期を有するクロック信号CKOを発生させるように構成されている(例えば、特許文献1参照。)。

【0005】

なお、このようなデジタル制御発振装置101は、デジタル回路だけで構成されているため、半導体集積回路によって実現するのに好適である。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平7−183800号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、TDC20では、基準クロックCKIの立ち上がりエッジ又は立ち下がりエッジのいずれか一方を測定タイミングとして、測定タイミング毎にパルス遅延回路10の出力をラッチすることで、最初の測定タイミングから今回の測定タイミングまでにパルスが通過した遅延ユニットDUの段数を求め、更に、前回の測定タイミングで得られた段数との差分を求めることで、周期データDPを算出しているため、測定タイミングから周期データDPが出力されるまでに基準クロックCKIで少なくとも1クロック分の遅延が生じる。また、データ処理部30でも除算又は乗算のための演算時間が必要であり少なくとも1クロック分の遅延が生じる。

【0008】

つまり、TDC20が周期データDPを生成するタイミングと、その周期データDPから算出される制御データDCに基づいて、DCO40がクロック信号CKOを発生させるタイミングとでは、基準クロックCKIで少なくとも2〜3クロック分の時間差(ずれ)が生じることになる。従って、その時間差の間に電源電圧が変動して、遅延ユニットDUの遅延時間が変化すると、TDC20が制御データDCを生成する際に用いた単位時間と、DCO40がクロック信号CKOを発生させる際に用いる単位時間とが異なったものとなる。その結果、クロック信号CKOの周波数変動(ゆらぎ)やジッタが増大して、クロック信号CKOの品質を低下させてしまうため、クロック信号CKOの品質を保持するには、大きな電流が流れても安定した電源電圧を維持することができる高価な電源回路を用いる必要があった。

【0009】

また、半導体集積回路の回路製造プロセスの高度化(微細化プロセスの採用)に伴い、回路ブロックのレイアウトの自由度が向上する一方で、電源パターン幅の微細化による配線抵抗が増大する傾向にあるだけでなく、デジタル制御発振装置と共に同一IC(半導体集積回路)チップに搭載される周辺回路の規模の増大により電源パターンを流れる電流も増大する傾向にある。

【0010】

このため、ICチップ内の配線パターンで生じる電圧降下の影響が大きくなり、上述のような高価な電源回路を用いたとしても、パルス遅延回路10を駆動する電源電圧を一定に保持することが困難な状況になりつつあるという問題があった。

【0011】

ここで、ICチップに搭載されたデジタル制御発振装置について考える。但し、遅延ユニットは、図5に示すような、電源電圧対遅延時間特性を有するものとする。

また、ICチップでのアルミ配線のシート抵抗値50mΩ、アルミ配線幅100μmであり、電源パッドからパルス遅延回路までの電源パターンの配線長を1mmと想定する。

【0012】

この場合、電源パターンの配線抵抗は0.5Ωとなり、電源電流が100mA流れると、電源電圧は0.05V降下する。

つまり、ICチップの電源パッドに印加される電源電圧を1.5Vとすると、電源パターンに100mAの電流が流れたとすると、パルス遅延回路に印加される電源電圧は、1.45Vに低下する。すると、図5からわかるように、遅延ユニットの遅延時間は4.5%程度変化し、これに伴って、デジタル制御発振装置が出力するクロック信号の周波数も同程度揺らぐことになる。

【0013】

仮に、ICチップ内において、デジタル制御発振装置を電源パッドの直近に配置できたとしても、配線長を0.3mm以下にすることは困難であり、この場合でも、電源電流が100mA流れると15mVの電圧降下が生じ、遅延ユニットの遅延時間、ひいてはクロック信号の周波数が1.3%程度揺らぐことになる。

【0014】

なお、このような問題は、回路製造プロセスの微細化が進むに従って、より顕著なものとなる。

本発明は、上記問題点を解決するために、半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させることを目的とする。

【課題を解決するための手段】

【0015】

上記目的を達成するためになされた発明である請求項1に記載の半導体集積回路は、入力電圧に応じた遅延時間でパルス信号を遅延させる遅延ユニットを複数段接続してなるパルス遅延回路と、予め設定された基準信号を入力し、該基準信号の1周期の間に、前記パルス遅延回路にて前記パルス信号が通過した前記遅延ユニットの段数を検出して符号化することにより、前記遅延ユニットの平均遅延時間を単位として、前記基準信号の周期を表した周期データを生成する周期測定部と、逓倍数又は分周数を表す設定値を除数又は乗数とし、前記周期データを被除数又は被定数とした演算を実行することにより、前記基準信号の周波数を逓倍又は分周することで得られる信号の周期を表した制御データを生成するデータ処理部と、前記パルス遅延回路を構成する各遅延ユニットからの出力である通過信号に基づいて、前記制御データに示された周期を有するクロック信号を生成する出力部とを備えている。なお、パルス遅延回路、周期測定部、データ処理部、出力部は、設定値によって設定される任意の周期を有したクロック信号を発生させる、いわゆるデジタル制御発振装置を構成している。

【0016】

そして、少なくともパルス遅延回路を含む第1回路ブロックを第1の電源で駆動し、少なくともデータ処理部を含む第2回路ブロックを第1の電源とは異なる第2の電源で駆動するように電源パターンが配線されている。

【0017】

このように構成された本発明の半導体集積回路によれば、第1回路ブロックの電源電圧が、第2ブロックで消費される動作電流の影響を受けることがないため、第1の電源の電圧変動を抑制すること、ひいてはパルス遅延回路を構成する遅延ユニットの遅延時間の変動を抑制することができる。

【0018】

その結果、基準信号の周期を周期データに変換する際の単位時間と、制御データからクロック信号を生成する際の単位時間とが異なることによって生じるクロック信号の周波数のゆらぎやジッタを抑制することができ、出力部から出力されるクロック信号の品質を向上させることができる。

【0019】

また、第1の電源は、第1回路ブロックを駆動できるだけの駆動能力があればよいため、大きな電流が流れても安定した電源電圧を維持するために必要であった構成を省略することができ、装置を簡略化することができる。

【0020】

なお、周期測定部及び出力部については、請求項2に記載のように、これらのうち少なくとも一方が第2回路ブロックに含まれ、残りが第1回路ブロックに含まれていてもよい。

【0021】

つまり、パルス遅延回路だけで構成されていることが望ましいが、第1回路ブロックに流れる電流の変動に基づく遅延ユニットの遅延時間の変動が許容範囲内に納まっていればよいため、その条件を満たすのであれば、第1回路ブロックに、周期測定部又は出力部のいずれか一方が含まれていてもよい。

【0022】

ところで、本発明の半導体集積回路が、出力部が生成するクロック信号を利用して動作する後段処理部を備えている場合、請求項3に記載のように、第2の電源で後段処理部を駆動するように電源パターンが配線されていてもよいし、請求項4に記載のように、第1の電源及び第2の電源とは異なる第3の電源で後段処理部を駆動するように電源パターンが配線されていてもよい。

【0023】

いずれにしてもパルス遅延回路を、後段処理部に流れる電流の影響を受けることなく動作させることができる。

【図面の簡単な説明】

【0024】

【図1】実施形態におけるデジタル制御発振装置の全体構成及び電源系統を示すブロック図である。

【図2】デジタル制御発振装置を搭載したICチップのレイアウト及び電源パターンを模式的に示した説明図である。

【図3】変形例におけるレイアウト及び電源パターンを模式的に示した説明図である。

【図4】従来装置におけるデジタル制御発振装置の構成を示すブロック図である。

【図5】遅延ユニットの電源電圧対遅延時間の特性を示すグラフである。

【発明を実施するための形態】

【0025】

以下に本発明の実施形態を図面と共に説明する。

<全体構成>

図1は、デジタル制御発振装置1の全体構成及び電源系統を示すブロック図である。

【0026】

デジタル制御発振装置1は、従来装置で説明いたデジタル制御発振装置101と同様に、パルス遅延回路10、時間/数値変換回路(TDC)20、データ処理部30、デジタル制御発振回路(DCO)40により構成されている。

【0027】

但し、デジタル制御発振装置1では、パルス遅延回路10を第1回路ブロック3、TDC20及びデータ処理部30,DCO40を第2回路ブロック5として、第1回路ブロック3は、第1の電源VDD1により駆動され、第2回路ブロック5は、第1の電源CDD1とは異なる第2の電源VDD2により駆動されるように構成されている。

【0028】

なお、デジタル制御発振装置1各部の具体的な構成は、例えば、特開平7−183800号公報や特開2000−152886号公報等に詳述された周知のものであるため、ここでは説明を省略する。

【0029】

<レイアウト>

図2は、デジタル制御発振装置1を搭載したIC(半導体集積回路)チップのレイアウト及び電源パターンを模式的に示した説明図である。

【0030】

図2に示すように、ICチップは周辺部を除く部位に位置する回路形成部位が、第1回路ブロック3と、第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。

【0031】

但し、第1回路ブロック3は回路形成部位の角部四隅のうち一隅(図では左上隅)を占めるように形成され、第2回路ブロック5は、第1回路ブロック3に隣接して(図では下側に)設けられている。

【0032】

また、ICチップの周辺部には、第1の電源VDD1に接続される電源パッドP1,第2の電源VDD2に接続される電源パッドP2が設けられていると共に、電源パッドP1から第1回路ブロック3に至る電源パターンL1,電源パッドP2から第2回路ブロック5及び第3回路ブロック7に至る電源パターンL2が配線されている。

【0033】

但し、電源パッドP1は、第1回路ブロック3との間を接続する電源パターンL1が最短となる位置に設けられ、電源パッドP2は、電源パッドP1が設けられた隅とは対角に位置する隅に設けられている。

【0034】

<効果>

上述のようにICチップ上でレイアウトされたデジタル制御発振装置1によれば、第1回路ブロック3を駆動する第1の電源VDD1の電圧が、第2回路ブロック5や第3回路ブロック7に流れる動作電流の影響を受けることがないだけでなく、電源パターンL1による電圧降下が必要最小限に抑えられるため、第1の電源VDD1の電圧変動を抑制することができ、ひいてはパルス遅延回路10を構成する遅延ユニットDUの遅延時間の変動を抑制することができる。

【0035】

その結果、基準信号CKIの周期を周期データDPに変換する際の単位時間と、制御データDCからクロック信号CKOを生成する際の単位時間とが異なることによって生じるクロック信号CKOの周波数のゆらぎやジッタを抑制することができ、DCO40から出力されるクロック信号CKOの品質を向上させることができる。

【0036】

また、第1の電源VDD1は、第1回路ブロック3を駆動できるだけの駆動能力があればよく、電源電圧を安定化させるために高性能な電源回路を用いる必要がないため、装置を簡略化することができる。

【0037】

なお、本実施形態において、時間/数値変換回路(TDC)20が周期測定部、デジタル制御発振回路(DCO)40が出力部、第3回路ブロック3を構成する周辺回路が後段処理部に相当する。

【0038】

<他の実施形態>

以上本発明の一実施形態について説明したが、本発明は上記実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において様々な態様にて実施することができる。

【0039】

例えば、上記実施形態では、第2回路ブロック5及び第3回路ブロック7を、電源パッドP2,電源パターンL2を介して第2の電源VDD2によって駆動するように構成されているが、図3に示すように、第2回路ブロック5を電源パッドP2,電源パターンL2を介して第2の電源VDD2によって駆動し、第3回路ブロック7を電源パッドP3及び電源ラインL3を介して第3の電源VDD3によって駆動するように構成されていてもよい。

【0040】

また、上記実施形態では、パルス遅延回路10だけで第1回路ブロック3が構成されているがこれに限るものではなく、第1回路ブロック3を、パルス遅延回路10とTDC20とで構成したり、パルス遅延回路10とDCO40とで構成したりしてもよい。この場合、デジタル制御発振装置1のうち第1回路ブロック3に含まれる構成以外を第2回路ブロック5として構成すればよい。

【0041】

更に上記実施形態では、DCO40を、基準信号CKIの周期と設定値Nとで決まる周期を有したクロック信号CKOを生成するように構成されているが、例えば、予め設定されたタイミングから基準信号CKIの周期と設定値Nとで決まる時間だけ経過した時点でパルス信号を1回だけ発生させるように構成されていてもよい。

【符号の説明】

【0042】

1…デジタル制御発振装置 3…第1回路ブロック 5…第2回路ブロック 7…第3回路ブロック 10…パルス遅延回路 20…時間/数値変換回路(TDC) 30…データ処理部 40…デジタル制御発振回路(DCO) L1〜L3…電源パターン P1〜P3…電源パッド

【特許請求の範囲】

【請求項1】

入力電圧に応じた遅延時間でパルス信号を遅延させる遅延ユニットを複数段接続してなるパルス遅延回路と、

予め設定された基準信号を入力し、該基準信号の1周期の間に、前記パルス遅延回路にて前記パルス信号が通過した前記遅延ユニットの段数を検出して符号化することにより、前記遅延ユニットの平均遅延時間を単位として、前記基準信号の周期を表した周期データを生成する周期測定部と、

逓倍数又は分周数を表す設定値を除数又は乗数とし、前記周期データを被除数又は被定数とした演算を実行することにより、前記基準信号の周波数を逓倍又は分周することで得られる信号の周期を表した制御データを生成するデータ処理部と、

前記パルス遅延回路を構成する各遅延ユニットからの出力である通過信号に基づいて、前記制御データに示された周期を有するクロック信号を生成する出力部と、

を備え、

少なくとも前記パルス遅延回路を含む第1回路ブロックを第1の電源で駆動し、少なくとも前記データ処理部を含む第2回路ブロックを前記第1の電源とは異なる第2の電源で駆動するように電源パターンが配線されていることを特徴とする半導体集積回路。

【請求項2】

前記周期測定部及び前記出力部のうち少なくとも一方が前記第2回路ブロックに含まれ、残りが前記第1回路ブロックに含まれることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記出力部が生成するクロック信号を利用して動作する後段処理部を備え、

前記第2の電源で前記後段処理部を駆動するように前記電源パターンが配線されていることを特徴とする請求項1又は請求項2に記載の半導体集積回路。

【請求項4】

前記出力部が生成するクロック信号を利用して動作する後段処理部を備え、

前記第1の電源及び前記第2の電源とは異なる第3の電源で前記後段処理部を駆動するように、前記電源パターンが配線されていることを特徴とする請求項1ないし請求項3のいずれか一項に記載の半導体集積回路。

【請求項1】

入力電圧に応じた遅延時間でパルス信号を遅延させる遅延ユニットを複数段接続してなるパルス遅延回路と、

予め設定された基準信号を入力し、該基準信号の1周期の間に、前記パルス遅延回路にて前記パルス信号が通過した前記遅延ユニットの段数を検出して符号化することにより、前記遅延ユニットの平均遅延時間を単位として、前記基準信号の周期を表した周期データを生成する周期測定部と、

逓倍数又は分周数を表す設定値を除数又は乗数とし、前記周期データを被除数又は被定数とした演算を実行することにより、前記基準信号の周波数を逓倍又は分周することで得られる信号の周期を表した制御データを生成するデータ処理部と、

前記パルス遅延回路を構成する各遅延ユニットからの出力である通過信号に基づいて、前記制御データに示された周期を有するクロック信号を生成する出力部と、

を備え、

少なくとも前記パルス遅延回路を含む第1回路ブロックを第1の電源で駆動し、少なくとも前記データ処理部を含む第2回路ブロックを前記第1の電源とは異なる第2の電源で駆動するように電源パターンが配線されていることを特徴とする半導体集積回路。

【請求項2】

前記周期測定部及び前記出力部のうち少なくとも一方が前記第2回路ブロックに含まれ、残りが前記第1回路ブロックに含まれることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記出力部が生成するクロック信号を利用して動作する後段処理部を備え、

前記第2の電源で前記後段処理部を駆動するように前記電源パターンが配線されていることを特徴とする請求項1又は請求項2に記載の半導体集積回路。

【請求項4】

前記出力部が生成するクロック信号を利用して動作する後段処理部を備え、

前記第1の電源及び前記第2の電源とは異なる第3の電源で前記後段処理部を駆動するように、前記電源パターンが配線されていることを特徴とする請求項1ないし請求項3のいずれか一項に記載の半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−85143(P2013−85143A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−224189(P2011−224189)

【出願日】平成23年10月11日(2011.10.11)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月11日(2011.10.11)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]