半導体集積装置

【構成】 水晶発振器用半導体集積装置において発振部と出力バッファ部の電源系をそれぞれ別々の独立した電源パッドで供給する。また発振部と出力バッファ部をデジタル部で分離して配置する。また発振部自体も基板より回り込むノイズを到達しにくい様基盤と反対電位のウェルをデジタル部側及び出力バッファ側になる様レイアウトする。

【効果】 出力バッファからの電源電圧の変動等の悪影響を発振部に与えない。また出力バッファ部のノイズをデジタル部で吸収し発振部に到達しない。これらのレイアウトにより帰還発振及び異常発振を回避した性能の安定した発振器を提供する。

【効果】 出力バッファからの電源電圧の変動等の悪影響を発振部に与えない。また出力バッファ部のノイズをデジタル部で吸収し発振部に到達しない。これらのレイアウトにより帰還発振及び異常発振を回避した性能の安定した発振器を提供する。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は発振器用半導体集積装置のレイアウトに関する。

【0002】

【従来の技術】従来、発振器用半導体集積回路において発振部に代表されるアナログ領域と分周部に代表されるデジタル領域が混在し、それぞれの領域は(1)まったく分離しないか(2)分離するも電源系は同一の配線系をもちいていた。図5は従来の発振器用ICのレイアウトの一例である。501は発振部、502は出力バッファ部、503はデジタル部で504はVDD、505はVSSパッドを示す。506はVDDパッドより配線される電源ライン(VDDライン)で507はVSSパッドより配線される電源ライン(VSSライン)である。ここで発振部501、出力バッファ502とデジタル部はVDD及びVSSラインは共通である。また発振部の隣に出力バッファが配置されている。

【0003】

【発明が解決しようとする課題】しかし、この様なレイアウトでは発振部と出力バッファの電源ラインが共通のため出力バッファに瞬時的に大電流(ショート電流)が流れることによる電圧のドロップで発振部の電源もドロップする。このため発振部は本質的な発振ではない帰還発振や異常発振等を引き起こす。この様なレイアウトによる異常発振等は簡単に対策がたてられないため開発納期に著しい遅延が生じたり、最終的に要求仕様を満たすことができないこともある。本発明の目的はかかる欠点を除去し安定した性能の発振器を供給することにある。

【0004】

【課題を解決するための手段】発振部と分周部と出力バッファ部を具備した水晶発振器用半導体集積装置において同一電位の電源パッドを複数有し少なくとも1つの電源パッドを前記発振部専用とすることを特徴とする。

【0005】発振部と分周部と出力バッファ部を具備した水晶発振器用半導体集積装置において前記発振部と前記出力バッファ部を前記分周部で分離して配置したことを特徴とする。

【0006】半導体集積装置において発振部の基盤と反対の極性を持つウェルを分周部及び出力バッファ部側に配置することを特徴とする。

【0007】

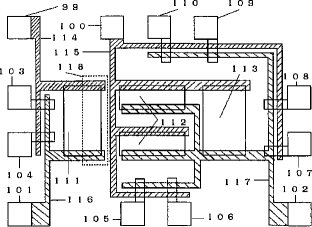

【実施例】本発明の一実施例を図1に示す。これは発振器用ICのレイアウト例で、99・100は電源用パッド(VDD)、101・102はもう一方の電源用パッド(VSS)である。103〜110は入出力用のパッドでどのパッドも静電気保護ダイオードをもっている。ここでは103は水晶振動子接続用のパッドでゲートパッド、104はドレインパッドである。111は発振部、112は分周部、113は出力バッファを示している。114は99の電源パッドより配線されるVDDラインを示し115は100の電源パッドより配線されるVDDラインである。VDDライン114とVDDライン115は同電位であるがパターン的には完全に分離され別の配線ラインとなっている。また116と117も同様で116は101の電源パッドより配線されるVSSライン、117は102の電源パッドより配線されるVSSラインで116、117は完全に別の配線となっている。また118は発振部のウェルを示し発振部のウェルは出力バッファ側に配置している。この様に電源パッドを分けた場合のパッケージへのボンディングの一例を図2に示す。ここで99、100は図1の電源パッドに対応する。201はICチップを示し、205はリードフレーム、202・203・204はリード端子で特に202はVDD電源用である。206・207はボンディング・ワイヤである。出力バッファ等でショート電流等に起因する電圧変動はボンディング・ワイヤ207から206を経て発振部に影響を与えることになる。ここで202のリード端子からIC外部の電源までのインピーダンスはボンディング・ワイヤ206のインダクタンスを含むインピーダンスと比較するとかなり小さいため出力バッファからの電圧変動は外部電源に吸収され発振部には大きな影響を与えない。この様に同電位の電源ラインにおいても発振部とデジタル部(分周部+出力バッファ部)とでまったく別の配線ラインを用いることで出力バッファ部でのショート電流等に起因する電圧変動による発振部への悪影響を防ぐことが可能となる。

【0008】本発明の別の実施例を図3に示す。301は発振部302〜305はデジタル部で306は出力バッファである。また307〜312は各々のウェルでここではN基盤のICであるためにPウェルである。なおP基盤のICであればNウェルとなる。電源ライン及びパッド配置は特に示してないが図1と同様の考え方によってレイアウトされているものとする。この実施例は電源が完全に分離されていても基盤を介して電源変動の影響を受ける可能性がある。このため大きな電源変動の要因である出力バッファをIC内部で発振部と可能な限り遠ざけかつ他のそれほど電圧変動の原因とならないデジタル部を発振部と出力バッファ部の間にはさんでいる。また発振部においても基盤と反対の電位をもつウェルを出力バッファ側及びデジタル部側に配置し電圧変動に対するインピーダンスをあげている。図4に発振部とデジタル部の接近部分の断面図を示しさらに説明する。401は基盤でここではN基盤である。402はデジタル部のPウェル、403は発振部のPウェルである。404・405は発振部のN基盤側のサブコンタクト、406・407はデジタル部の基盤サブコンタクト。408・409は発振部のウェルサブコンタクト、410・411はデジタル部のウェルサブコンタクトである。412〜419はトランジスタを構成するそれぞれの拡散である。420・421はそれぞれデジタル部のP・N両トランジスタでインバータを構成する。422・423は発振インバータを構成している。424〜427は基盤抵抗を等価的に表した物で407のサブコンタクトから404のサブコンタクトへ向かうほど404からみたインピーダンスが高くなることを視覚的に分かりやすく表している。ここでデジタル部のインバータによるショート電流が流れるとAから420のトランジスタを介しBを経て421のトランジスタを通ってVDDとVSSがショート状態となる。VDD側に着目するとショート電流はVDDライン及び407・406のサブコンタクトを介し基盤を流れる。これにより基盤の電位は低下の方向に変動する。この変動の影響は抵抗424・425・426・427を経るに従って減衰する。あるいは406・407のサブコンタクトと同様のサブコンタクトが406・407の周囲に多くあればインピーダンスの低いそちらのサブコンタクトに吸収されインピーダンスの高い発振部の方向へは影響が行きにくくなる可能性がある。またデジタル部自身も出力バッファに対して低インピーダンスの電圧変動吸収経路となる。この様な考え方から抵抗425と426の間よりも405や404のサブコンタクトの近くのほうが電圧変動の影響をうけにくいのは当然である。

【0009】

【発明の効果】前述した様なレイアウトを用いることにより出力バッファ等の大電流を流して電源に変動を与える部分に対しても発振部の様な非常に敏感な部分は特に影響を受けにくい。発振起動時の様な不安定な状態においては通常電源変動の影響をうけ帰還発振や異常発振を起こしやすい。しかし本発明のレイアウトは電源電圧の変動の発振部への影響をシャットアウトしているため、発振起動時においても安定した発振の起動を行うことが可能となる。したがって帰還発振や異常発振に対し非常に強い安定した性能の発振器を提供することができる。またICにおいてこの様なレイアウトを用いることにより水晶の特性にICからの帰還的影響を比較的与えにくくすることができるため水晶自体の特性のバラツキに対しても広い対応性がある。したがって発振器トータルとしての歩留まりを向上することができコストダウンすることができる。

【図面の簡単な説明】

【図1】 本発明の実施例のレイアウト図。

【図2】 本発明の一例のボンディング図。

【図3】 本発明の第二の実施例のレイアウト図。

【図4】 構造断面図。

【図5】 従来のレイアウト図。

【符号の説明】

99・100 電源パッド(VDD)

101・102 電源パッド(VSS)

103・104・105・106・107・108・109・110 入出力パッド

111 発振部

112 デジタル部

113 出力バッファ部

114・115 電源配線(VDD)

116・117 電源配線(VSS)

118 Pウェル

【0001】

【産業上の利用分野】本発明は発振器用半導体集積装置のレイアウトに関する。

【0002】

【従来の技術】従来、発振器用半導体集積回路において発振部に代表されるアナログ領域と分周部に代表されるデジタル領域が混在し、それぞれの領域は(1)まったく分離しないか(2)分離するも電源系は同一の配線系をもちいていた。図5は従来の発振器用ICのレイアウトの一例である。501は発振部、502は出力バッファ部、503はデジタル部で504はVDD、505はVSSパッドを示す。506はVDDパッドより配線される電源ライン(VDDライン)で507はVSSパッドより配線される電源ライン(VSSライン)である。ここで発振部501、出力バッファ502とデジタル部はVDD及びVSSラインは共通である。また発振部の隣に出力バッファが配置されている。

【0003】

【発明が解決しようとする課題】しかし、この様なレイアウトでは発振部と出力バッファの電源ラインが共通のため出力バッファに瞬時的に大電流(ショート電流)が流れることによる電圧のドロップで発振部の電源もドロップする。このため発振部は本質的な発振ではない帰還発振や異常発振等を引き起こす。この様なレイアウトによる異常発振等は簡単に対策がたてられないため開発納期に著しい遅延が生じたり、最終的に要求仕様を満たすことができないこともある。本発明の目的はかかる欠点を除去し安定した性能の発振器を供給することにある。

【0004】

【課題を解決するための手段】発振部と分周部と出力バッファ部を具備した水晶発振器用半導体集積装置において同一電位の電源パッドを複数有し少なくとも1つの電源パッドを前記発振部専用とすることを特徴とする。

【0005】発振部と分周部と出力バッファ部を具備した水晶発振器用半導体集積装置において前記発振部と前記出力バッファ部を前記分周部で分離して配置したことを特徴とする。

【0006】半導体集積装置において発振部の基盤と反対の極性を持つウェルを分周部及び出力バッファ部側に配置することを特徴とする。

【0007】

【実施例】本発明の一実施例を図1に示す。これは発振器用ICのレイアウト例で、99・100は電源用パッド(VDD)、101・102はもう一方の電源用パッド(VSS)である。103〜110は入出力用のパッドでどのパッドも静電気保護ダイオードをもっている。ここでは103は水晶振動子接続用のパッドでゲートパッド、104はドレインパッドである。111は発振部、112は分周部、113は出力バッファを示している。114は99の電源パッドより配線されるVDDラインを示し115は100の電源パッドより配線されるVDDラインである。VDDライン114とVDDライン115は同電位であるがパターン的には完全に分離され別の配線ラインとなっている。また116と117も同様で116は101の電源パッドより配線されるVSSライン、117は102の電源パッドより配線されるVSSラインで116、117は完全に別の配線となっている。また118は発振部のウェルを示し発振部のウェルは出力バッファ側に配置している。この様に電源パッドを分けた場合のパッケージへのボンディングの一例を図2に示す。ここで99、100は図1の電源パッドに対応する。201はICチップを示し、205はリードフレーム、202・203・204はリード端子で特に202はVDD電源用である。206・207はボンディング・ワイヤである。出力バッファ等でショート電流等に起因する電圧変動はボンディング・ワイヤ207から206を経て発振部に影響を与えることになる。ここで202のリード端子からIC外部の電源までのインピーダンスはボンディング・ワイヤ206のインダクタンスを含むインピーダンスと比較するとかなり小さいため出力バッファからの電圧変動は外部電源に吸収され発振部には大きな影響を与えない。この様に同電位の電源ラインにおいても発振部とデジタル部(分周部+出力バッファ部)とでまったく別の配線ラインを用いることで出力バッファ部でのショート電流等に起因する電圧変動による発振部への悪影響を防ぐことが可能となる。

【0008】本発明の別の実施例を図3に示す。301は発振部302〜305はデジタル部で306は出力バッファである。また307〜312は各々のウェルでここではN基盤のICであるためにPウェルである。なおP基盤のICであればNウェルとなる。電源ライン及びパッド配置は特に示してないが図1と同様の考え方によってレイアウトされているものとする。この実施例は電源が完全に分離されていても基盤を介して電源変動の影響を受ける可能性がある。このため大きな電源変動の要因である出力バッファをIC内部で発振部と可能な限り遠ざけかつ他のそれほど電圧変動の原因とならないデジタル部を発振部と出力バッファ部の間にはさんでいる。また発振部においても基盤と反対の電位をもつウェルを出力バッファ側及びデジタル部側に配置し電圧変動に対するインピーダンスをあげている。図4に発振部とデジタル部の接近部分の断面図を示しさらに説明する。401は基盤でここではN基盤である。402はデジタル部のPウェル、403は発振部のPウェルである。404・405は発振部のN基盤側のサブコンタクト、406・407はデジタル部の基盤サブコンタクト。408・409は発振部のウェルサブコンタクト、410・411はデジタル部のウェルサブコンタクトである。412〜419はトランジスタを構成するそれぞれの拡散である。420・421はそれぞれデジタル部のP・N両トランジスタでインバータを構成する。422・423は発振インバータを構成している。424〜427は基盤抵抗を等価的に表した物で407のサブコンタクトから404のサブコンタクトへ向かうほど404からみたインピーダンスが高くなることを視覚的に分かりやすく表している。ここでデジタル部のインバータによるショート電流が流れるとAから420のトランジスタを介しBを経て421のトランジスタを通ってVDDとVSSがショート状態となる。VDD側に着目するとショート電流はVDDライン及び407・406のサブコンタクトを介し基盤を流れる。これにより基盤の電位は低下の方向に変動する。この変動の影響は抵抗424・425・426・427を経るに従って減衰する。あるいは406・407のサブコンタクトと同様のサブコンタクトが406・407の周囲に多くあればインピーダンスの低いそちらのサブコンタクトに吸収されインピーダンスの高い発振部の方向へは影響が行きにくくなる可能性がある。またデジタル部自身も出力バッファに対して低インピーダンスの電圧変動吸収経路となる。この様な考え方から抵抗425と426の間よりも405や404のサブコンタクトの近くのほうが電圧変動の影響をうけにくいのは当然である。

【0009】

【発明の効果】前述した様なレイアウトを用いることにより出力バッファ等の大電流を流して電源に変動を与える部分に対しても発振部の様な非常に敏感な部分は特に影響を受けにくい。発振起動時の様な不安定な状態においては通常電源変動の影響をうけ帰還発振や異常発振を起こしやすい。しかし本発明のレイアウトは電源電圧の変動の発振部への影響をシャットアウトしているため、発振起動時においても安定した発振の起動を行うことが可能となる。したがって帰還発振や異常発振に対し非常に強い安定した性能の発振器を提供することができる。またICにおいてこの様なレイアウトを用いることにより水晶の特性にICからの帰還的影響を比較的与えにくくすることができるため水晶自体の特性のバラツキに対しても広い対応性がある。したがって発振器トータルとしての歩留まりを向上することができコストダウンすることができる。

【図面の簡単な説明】

【図1】 本発明の実施例のレイアウト図。

【図2】 本発明の一例のボンディング図。

【図3】 本発明の第二の実施例のレイアウト図。

【図4】 構造断面図。

【図5】 従来のレイアウト図。

【符号の説明】

99・100 電源パッド(VDD)

101・102 電源パッド(VSS)

103・104・105・106・107・108・109・110 入出力パッド

111 発振部

112 デジタル部

113 出力バッファ部

114・115 電源配線(VDD)

116・117 電源配線(VSS)

118 Pウェル

【特許請求の範囲】

【請求項1】発振部と論理部と出力バッファ部を具備した水晶発振器用半導体集積装置において同一電位の電源パッドを複数有し少なくとも1つの電源パッドを前記発振部専用とすることを特徴とする半導体集積装置。

【請求項2】発振部と論理部と出力バッファ部を具備した水晶発振器用半導体集積装置において前記発振部と前記出力バッファ部を前記論理部で分離して配置したことを特徴とする半導体集積装置。

【請求項3】請求項2記載の半導体集積装置において発振部の基盤と反対の導電性を持つウェルを前記論理部及び前記出力バッファ部側に配置することを特徴とする半導体集積装置。

【請求項1】発振部と論理部と出力バッファ部を具備した水晶発振器用半導体集積装置において同一電位の電源パッドを複数有し少なくとも1つの電源パッドを前記発振部専用とすることを特徴とする半導体集積装置。

【請求項2】発振部と論理部と出力バッファ部を具備した水晶発振器用半導体集積装置において前記発振部と前記出力バッファ部を前記論理部で分離して配置したことを特徴とする半導体集積装置。

【請求項3】請求項2記載の半導体集積装置において発振部の基盤と反対の導電性を持つウェルを前記論理部及び前記出力バッファ部側に配置することを特徴とする半導体集積装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開平5−48003

【公開日】平成5年(1993)2月26日

【国際特許分類】

【出願番号】特願平3−200731

【出願日】平成3年(1991)8月9日

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【公開日】平成5年(1993)2月26日

【国際特許分類】

【出願日】平成3年(1991)8月9日

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

[ Back to top ]