協調検証方法及び協調検証装置

【課題】 本発明の課題は、設計回路が性能要件を満たしているか否かを判定することを目的とする。

【解決手段】 上記課題は、コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行うことにより達成される。

【解決手段】 上記課題は、コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行うことにより達成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、設計回路のソフトウェア及びハードウェアによる協調検証を行なう協調検証方法及び協調検証装置に関する。

【背景技術】

【0002】

ソフトウェアの開発において、そのソフトウェアが動作するハードウェアのモデルを用いて、ソフトウェアとハードウェアとを協調動作させて検証することが行なわれている。マルチメディア向け等のLSI(Large Scale Integration)で実行されるプログラム(ソフトウェア)では、リアルタイム性が要求されるものが多く、それらのプログラムで繰り返し実行される処理単位は、常に規定時間以内で実行されなければならないという強い制約が要求される場合が多い。

【0003】

検証を行なう際に、プログラムを実行した際の処理単位に係る処理時間を監視することが考えられる。処理時間を監視するという観点において、所定処理に対して処理時間を監視し、所定時間を経過した際にはタイムアウトを通知する技術や、ソフトウェア・ハードウェア協調検証において、ソフトウェアモデルの処理時間を検証用プラットフォームにおける検証時刻から算出したタイマの値に基づき、予め設定されたタイマ間隔でシミュレーション時刻を監視する技術などが提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平04−239341号公報

【特許文献2】特開平04−279940号公報

【特許文献3】特開2010−009113号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来の技術は、何らかの要因で処理が決められた時間に終了しない、処理がループしてしまい終了しない等の状態を監視する技術であるため、検証対象のプログラムが正常に機能する場合には、そのような機能的には問題の無いプログラムを、制約で規定された性能に基づいて、精度良く評価することができない。

【0006】

マルチメディア用のプログラムでは、機能の制約を満たしていたとしても、例えば、グラフィック処理、オーディオ処理等で、ある処理単位の実行が規定時間を越えた場合、ノイズの混入などにより品質が問題となる場合がある。

【0007】

LSI設計においてシミュレータ及びエミュレータによるソフトウェア・ハードウェア協調検証を実施する際に、論理的に正しいことを検証するだけでなく、全体の処理時間を測定し、なおかつ、プログラムの個々の部分の処理に関して、規定時間内に実行されていることを同時に検証することができない。そのため、オーディオ処理において、ある瞬間のサンプリングに処理が間に合わないためのノイズが発生するケースなどを検出すること、即ち、機能に問題はないが、性能に問題がある処理の検出は困難であった。

【0008】

よって、本発明の目的は、LSI製造前の段階のソフトウェア・ハードウェア協調検証において、ソフトウェア及びハードウェアの機能のみならず性能上の制約を検証可能とすることである。

【課題を解決するための手段】

【0009】

開示の技術は、コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う。

【0010】

また、上記課題を解決するための手段として、協調検証装置、コンピュータに上記協調検証方法として行わせるためのプログラム、及び、そのプログラムを記録した記録媒体とすることもできる。

【発明の効果】

【0011】

開示の技術では、性能要件に基づく計数可能な規定値を用いて性能測定することによって、設計回路が性能要件を満たしているか否かを判定することができる。

【図面の簡単な説明】

【0012】

【図1】基本構成を示す図である。

【図2】規定値算出方法の第1例を説明するための図である。

【図3】規定値算出方法の第2例を説明するための図である。

【図4】測定用付加回路の機能構成例を示す図である。

【図5】検証システムのハードウェア構成を示す図である。

【図6】性能測定処理のみをシミュレータで実施する第1実施例を説明するための図である。

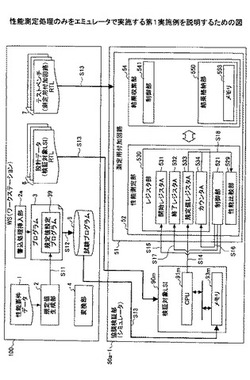

【図7】性能測定処理のみをエミュレータを用いて実施する第2実施例を説明するための図である。

【図8】機能検証処理のみをシミュレータで実施する第3実施例を説明するための図である。

【図9】機能検証処理のみをエミュレータで実施する第4実施例を説明するための図である。

【図10】性能測定処理及び機能検証処理を実施する第5実施例を説明するための図である。

【図11】性能測定処理及び機能検証処理を実施する第6実施例を説明するための図である。

【図12】周波数を探索する第1の探索例を説明するための図である。

【図13】図12の第1の探索例での処理概要を説明するためのフローチャート図である。

【図14】機能の組み合せを探索する第2の探索例を説明するための図である。

【図15】図14の第2の探索例での処理概要を説明するためのフローチャート図である。

【図16】同一の機能の組み合せにおいて性能要件を満たす条件を探索する第3の探索例を説明するための図である。

【図17】バス占有率に基づく性能測定について説明するための図である。

【図18】第5実施例の変形例を説明するための図である。

【図19】第6実施例の変形例を説明するための図である。

【図20】図19の第6実施例の変形例での処理概要を説明するためのフローチャート図である。

【図21】マルチメディア対応LSIの回路モデル構成の例を示す図である。

【図22】図21に示すマルチメディア対応LSIの性能限界の探索例を示す図である。

【図23】データフロー例を示す図である。

【図24】バスモニタの結果表示のためのフローチャート図である。

【図25】ボトルネック解析の例を説明するための図である。

【図26】バス占有率を用いた性能余裕度の検証例を説明するための図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態を図面に基づいて説明する。本実施の形態では、LSIで実行される個々の部分処理について、シミュレータ及びエミュレータを用いたソフトウェア・ハードウェア協調検証(以下、協調検証と言う)において、論理的に正しいことを検証するのに加えて、予め指定された性能要件内で実行されていることを監視することによって、性能又は/及び機能面の処理違反を検出可能とし、また、解析のためにその検証結果を提供する。

【0014】

図1は、基本構成を示す図である。図1中、本実施の形態に係る構成部のみを示し、他構成部を省略している。図1に例示される基本構成において、検証システム1000は、主に、規定値生成部2と、変換部4と、協調検証部50とを有する。更に、性能要件データ1と、プログラム3と、試験プログラム5と、設計データ6と、テストベンチ7とが記憶部に格納されている。

【0015】

後述されるように、規定値生成部2と、変換部4と、協調検証部50とは、ワークステーションなどのコンピュータ装置において、対応するプログラムをCPUが実行することによって実現される処理部である。或いは、規定値生成部2と変換部4とは、一つのワークステーションで実現され、協調検証部50は、エミュレータで実現されてもよい。

【0016】

性能要件データ1は、制約によって規定される性能要件を示し、検証対象の部分処理に要求される処理時間、バスの占有率などのデータを含む。

【0017】

規定値生成部2は、性能要件データ1を読み込んで、性能検証用の規定値を生成する。性能要件データ1によって規定される性能要件に係る値から、協調検証部50での処理において計数可能な規定値を算出する処理部である。規定値生成部2は、検証対象の部分処理が開始される際に、算出された規定値を協調検証部50の所定のレジスタに書き込むための規定値設定プログラム39を検証対象のプログラム3に埋め込む。

【0018】

変換部4は、プログラム3を、検証対象LSI90mを試験するための試験プログラム5に変換する処理部である。プログラム3は、各部分処理の性能又は/及び機能を検証するために、検証対象LSI90mで実行させるプログラムである。試験プログラム5は、変換部4によって、検証対象LSI90mで実行可能なプログラムコードに変換される。

【0019】

設計データ6は、RTL(Register Transfer Level)などのハードウェア記述言語によってハードウェアの動作を抽象化して表現したデータである。

【0020】

テストベンチ7は、試験プログラム5によって動作する検証対象LSI90mの性能又は/及び機能を検証するためのRTL(Register Transfer Level)などのハードウェア記述言語で作成した回路モデルを含み、協調検証部50に実装される。本実施の形態では、テストベンチ7は、測定用に付加されるRTL(Register Transfer Level)などのハードウェア記述言語で作成された回路モデルである測定用付加回路51を有する。

【0021】

協調検証部50は、シミュレータ又はエミュレータ上で協調検証を行なう処理部であり、検証対象LSI90mと、測定用付加回路51とを有する。

【0022】

検証対象LSI90mは、設計データ6が協調検証部50にロードされることによって実装される、設計されたLSIの動作を表す回路モデルであり、少なくともCPU91mとメモリ93mとを有する。CPU91mとメモリ93mとも、回路モデルとして実装される。試験プログラム5がメモリ93mにロードされ、CPU91mが試験プログラム5を実行することによって、協調検証が開始される。

【0023】

所定の部分処理の開始の際に、CPU91mは、規定値生成部2によって埋め込まれた規定値設定プログラム39に従って、規定値を測定用付加回路51の所定レジスタに書き込んで所定の部分処理を実行し、所定の部分処理の実行中に測定用付加回路51が検証対象LSI90mの性能又は/及び機能を測定することによって収集した結果を取得して、試験結果を判定する。

【0024】

測定用付加回路51は、テストベンチ7が協調検証部50にロードされることによって実装される回路モデルであり、性能測定部52と、機能検証部54と、結果収集部54とを有する。

【0025】

性能測定部52は、試験プログラム5によって起動され、検証対象LSI90mの動作が開始されると、CPU91mが設定した規定値に基づいて性能測定を行う処理部である。その結果は結果収集部54によって収集されて、検証対象LSI90mに通知される。

【0026】

機能検証部56は、試験プログラム5によって起動され、検証対象LSI90mの動作の機能測定を行う処理部である。その結果は結果収集部54によって収集されて、検証対象LSI90mに通知される。

【0027】

結果収集部54は、性能測定部52又は/及び56からの結果を収集して、CPU91mに通知する。CPU91mが実行している試験プログラム5によって、結果が判定される。

【0028】

次に、規定値生成部2によって行われる規定値算出方法の例について、図2、図3で説明する。図2は、規定値算出方法の第1例を説明するための図である。図2において、性能を満たすための処理時間「33ms」が指定されている性能要件データ1aと、規定値を算出するために使用される規定値算出データ8aとが、規定値生成部2に読み込まれる。

【0029】

この第1例では、規定値算出データ8aによって、設計データ6から得られるクロック周波数「100MHz」が指定される。

【0030】

規定値生成部2は、読み込んだ性能要件データ1aで指定される性能要件と規定値算出データ8aで指定されるクロック周波数とに基づいて、規定値となる設計データ6に対するサイクル数を算出する。

【0031】

規定値生成部2は、クロック周波数「100MHz」から設計データ6の1サイクル「10ns」を求め、設計データ6の1サイクル「10ns」で処理時間「33ms」を除算することにより、処理時間「33ms」を満たすための、設計データ6において処理を終えなければならない「3,300,000」サイクルを取得する。

【0032】

規定値生成部2は、算出結果のサイクル数「3,300,000」を性能測定時の規定値として所定レジスタに書き込むための規定値設定プログラム39をプログラム3に埋め込む。

【0033】

図3は、規定値算出方法の第2例を説明するための図である。図3において、性能を満たすためのバス占有率「50%」以下が指定されている性能要件データ1bと、規定値を算出するために使用される規定値算出データ8bとが、規定値生成部2に読み込まれる。

【0034】

この第2例では、規定値算出データ8bによって、設計データ6から得られるバス動作周波数「100MHz」及びバス幅「64bit」と、1コマンドの転送量としてreadコマンド「64bit」及びwriteコマンド「64bit」、分解能「1秒」が指定される。

【0035】

規定値生成部2は、読み込んだ性能要件データ1bで指定される性能要件と規定値算出データ8bで指定されるクロック周波数とに基づいて、規定値となる設計データ6に対するサイクル数を算出する。

【0036】

規定値生成部2は、読み込んだ性能要件データ1bで指定される性能要件と規定値算出データ8bで指定される設計データ6のバス動作周波数「100MHz」及びバス幅「64bit」と、1コマンドの転送量とに基づいて、規定値となるコマンド発行可能最大数を算出する。

【0037】

規定値生成部2は、バス動作周波数「100MHz」にバス幅「64bit」を乗算することにより最大転送量(理論値)「6400Mbps」を求める。read及びwriteとも64bitの1コマンドの転送量を考慮すると、性能要件バス占有率「50%」以下を満たすには、最大転送量(理論値)「6400Mbps」を1コマンド分の「64bit」で除算し、更に、性能要件バス占有率「50%」を乗算することによって、性能として要求される、1秒間あたりコマンド発行可能最大回数「50M回」を取得する。この場合、分解能は「1秒」であるので、分解能1秒当たりのコマンド発行可能最大回数は「50M回」となる。分解能が「2秒」の場合は、分解能2秒当たりのコマンド発行可能最大回数は「100M回」となる。

【0038】

規定値生成部2は、算出結果のコマンド発行可能最大回数「50M回」を性能測定時の規定値として所定レジスタに書き込むための規定値設定プログラム39をプログラム3に埋め込む。

【0039】

図4は、測定用付加回路の機能構成例を示す図である。図4において、RTLで記述された回路モデルである測定用付加回路51は、性能測定部52と、結果収集部54と、機能検証部56とを有する。

【0040】

性能測定部52は、検証対象LSI90mの性能を測定し、制御部521と、性能比較部529と、レジスタ部530とを有する。

【0041】

制御部521は、性能測定の開始と終了とを監視し、性能測定部52での処理を制御する。

【0042】

図2に示す規定値算出方法の第1例の場合、処理の開始からサイクル毎にカウントする。また、カウント値が規定値を超えた場合、制御部521は、結果収集部54に通知し、性能測定の結果を、結果格納部550を介してメモリ553に記憶する。

【0043】

また、図3に示す規定値算出方法の第2例の場合、制御部521は、検証対象LSI91mに対して、バスモニタを組み込んで、処理の開始からコマンド発行毎にカウントを行う。制御部521は、指定された分解能を変換したサイクル数分を経過するとカウンタをリセットする。カウント値が規定値を超えた場合、制御部521は、結果収集部54に通知し、性能測定の結果を、結果格納部550を介してメモリ553に記憶する。

【0044】

性能比較部529は、検証対象LSI90mが処理開始時に設定した規定値と処理中にカウントしたカウント値とを比較することによって性能測定を行う。レジスタ部530は、性能測定に必要な複数のレジスタを有する。

【0045】

結果収集部54は、性能測定部52から出力される比較結果を収集し、制御部541と、結果格納部550とを有する。制御部541は、性能測定部52及び機能検証部56からの結果を受信し、結果格納部550のメモリ553に格納する。また、制御部541は、性能測定部52及び機能検証部56からの結果を検証対象LSI90mに通知する。即ち、性能測定部52及び機能検証部56からの結果は、検証対象LSI90mで実行されている試験プログラム5に通知される。一方、性能又は機能に問題があった場合には、制御部541は、測定用付加回路51を停止させる。

【0046】

機能検証部56は、検証対象LSI90mの機能を測定し、入力部560と、制御部561と、期待値生成部562と、期待値格納メモリ563と、期待値比較部564と、レジスタ部570とを有する。機能の測定には、検証対象LSI90mが正しく機能しているか否かに関する測定を含む。

【0047】

入力部560は、内部メモリや外部メモリへの入力データを機能検証部56に取り込む。制御部561は、入力データとの比較開始条件を判断し、期待値比較部564によって期待値との比較を行わせる。

【0048】

期待値生成部562は、期待値データ58を生成し、期待値格納メモリ563に格納する。期待値比較部564は、入力部560から取り込まれた入力データと、期待値データ58とを比較する。制御部561によって、比較結果に応じたデータが結果収集部54に提供される。結果収集部54は、機能検証部56の制御部561から期待値データ58との比較不一致が通知されると、測定用付加回路51を停止させる。

【0049】

上述した機能構成に基づく協調検証における処理パターンとして、

処理パターンA:性能測定処理のみ

処理パターンB:機能検証処理のみ

処理パターンC:性能測定処理及び機能検証処理(処理パターンA+B)

このように、3種類の処理パターンがある。これら処理パターンA、B、及びC毎に、エミュレータを使用しないシミュレータのみの実施例、及びエミュレータを使用する場合の実施例の各々について、処理概要を説明する。

【0050】

上述した機能実装A、B、及びCの説明にあたり、先ず、検証システム1000のハードウェア構成について説明する。図5は、検証システム1000のハードウェア構成を示す図である。図5において、検証システム1000は、少なくともWS(ワークステーション)100を有する。

【0051】

WS100は、シミュレータとして機能するようにコンピュータによって制御される装置であって、CPU(Central Processing Unit)11と、メモリユニット12と、表示ユニット13と、出力ユニット14と、入力ユニット15と、通信ユニット16と、記憶装置17と、ドライブ18とを有し、バスBに接続される。

【0052】

CPU11は、メモリユニット12に格納されたプログラムに従ってWS100を制御する。メモリユニット12には、RAM(Random Access Memory)及びROM(Read-Only Memory)等が用いられ、CPU11にて実行されるプログラム、CPU11での処理に必要なデータ、CPU11での処理にて得られたデータ等を格納する。また、メモリユニット12の一部の領域が、CPU11での処理に利用されるワークエリアとして割り付けられている。

【0053】

表示ユニット13は、CPU11の制御のもとに必要な各種情報を表示する。出力ユニット14は、プリンタ等を有し、利用者からの指示に応じて各種情報を出力するために用いられる。入力ユニット15は、マウス、キーボード等を有し、LSIの開発者等のユーザがWS100が処理を行なうための必要な各種情報を入力するために用いられる。通信ユニット16は、例えばインターネット、LAN(Local Area Network)等に接続し、外部装置との間の通信制御をするための装置である。

【0054】

記憶装置17には、例えば、ハードディスクユニットが用いられ、各種処理を実行する規定値生成部2、変換部4、協調検証部50での処理を実現するためのプログラム等、また、検証対象LSI90mで実行される検証対象の処理を行わせるためのプログラム3、メモリ93mの形式に変換された試験プログラム5、設計データ6、テストベンチ7等のデータを格納する。

【0055】

メモリユニット12又は/及び記憶装置17などによって、本実施の形態において必要なプログラム及びデータを記憶する記憶部が形成される。

【0056】

WS100によって行われる処理を実現するプログラムは、例えば、CD−ROM(Compact Disc Read-Only Memory)等の記憶媒体19によってWS100に提供される。即ち、プログラムが保存された記憶媒体19がドライブ18にセットされると、ドライブ18が記憶媒体19からプログラムを読み出し、その読み出されたプログラムがバスBを介して記憶装置17にインストールされる。そして、プログラムが起動されると、記憶装置17にインストールされたプログラムに従ってCPU11がその処理を開始する。尚、プログラムを格納する媒体としてCD−ROMに限定するものではなく、コンピュータが読み取り可能な媒体であればよい。コンピュータ読取可能な記憶媒体として、CD−ROMの他に、DVDディスク、USBメモリ等の可搬型記録媒体、フラッシュメモリ等の半導体メモリであっても良い。

【0057】

また、WS100によって行われる処理を実現するプログラムが、通信ユニット16を介して外部装置から提供されてもよい。或いは、外部装置へ該プログラムを提供し、後述される各処理は外部装置で実現されるように構成してもよい。通信ユニット16による通信は無線又は有線に限定されるものではない。

【0058】

また、検証システム1000は、更に、エミュレータI/F20を有することにより、エミュレータ200との通信によって、エミュレータ200を用いた協調検証を行なうこともできる。

【0059】

以下に、性能測定処理のみの処理パターンAに係る機能構成及び処理手順について、シミュレータ(WS100)で実施する場合と、エミュレータ200を用いて実施する場合とで、夫々説明する。

【0060】

性能測定処理のみの処理パターンAをシミュレータ(WS100)で実施する第1実施例に係る処理手順について、図6で説明する。図6は、性能測定処理のみをシミュレータで実施する第1実施例を説明するための図である。図6において、WS100は、書込処理挿入部2aを有し、測定用付加回路51の性能測定部52のレジスタ部530は、開始レジスタA531と、終了レジスタA532と、規定値レジスタA533と、カウンタA534とを有する。

【0061】

図6に示す第1実施例において、書込処理挿入部2aは、性能測定の対象処理(以下、処理Aという。例えば、オーディオ処理などである。)の開始時点で開始レジスタA531に書き込む処理、及び終了時点て終了レジスタA532に書き込む処理を行うプログラムをプログラム3に挿入し、また、規定値生成部2は、性能要件データ1に基づいて、規定値を規定値レジスタA533に設定する処理を行う規定値設定プログラム39をプログラム3に挿入する(ステップS11)。

【0062】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS12)。

【0063】

そして、CPU11が、メモリユニット12にロードされた、設計データ6と、テストベンチ7とを実行することによって、シミュレータである協調検証部50a−1として機能し、試験プログラム5がメモリ93mにロードされることによって、シミュレーションを開始する(ステップS13)。

【0064】

シミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って性能測定部51を起動し、処理Aに対する性能測定処理の開始の際に、処理Aに係る規定値(サイクル数)を規定値レジスタA533に設定する(ステップS14)。

【0065】

制御部521は、検証対象LSI91mによる処理Aの開始で、開始レジスタA531に書き込む(ステップS15)。また、制御部521は、カウンタA534をリセットする(ステップS16)。その後、カウンタA534は、サイクル毎にカウントアップされる。

【0066】

検証対象LSI91mによる処理Aの終了で、制御部521は、終了レジスタA532に書き込む(ステップS17)。

【0067】

性能比較部529は、カウンタA534のカウンタ値と規定値レジスタA533に設定された規定値とを比較する(ステップS18)。性能比較部529による比較結果がカウンタA534のカウンタ値が規定値レジスタA533の規定値より大きいことを示す場合、制御部521は、性能に問題があると判定して、結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553で管理されるエラーフラグを1に設定する。

【0068】

エラーフラグが「1」を示す場合、性能に問題があると判定されたことを示し、「0」を示す場合、性能は規定内であり問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、シミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、シミュレーションを停止する。シミュレーションを停止するかどうかは選択することが出来る。

【0069】

一方、シミュレーションを停止せず、性能が規定内であり問題ない場合、上述したステップS15からS18を繰り返す。

【0070】

性能測定処理のみの処理パターンAをエミュレータ200を用いて実施する第2実施例に係る処理手順について、図7で説明する。図7は、性能測定処理のみをエミュレータを用いて実施する第2実施例を説明するための図である。図7に示す第2実施例では、WS100がコンパイラ8とコンパイルDB9とを更に有する点で第1実施例と異なる。測定用付加回路51の性能測定部52のレジスタ部530は、図6と同様である。

【0071】

図7に示す第2実施例において、書込処理挿入部2aは、性能測定の対象処理(以下、処理Aという。例えば、オーディオ処理などである。)の開始時点で開始レジスタA531に書き込む処理、及び終了時点て終了レジスタA532に書き込む処理を行うプログラムをプログラム3に挿入し、また、規定値生成部2は、性能要件データ1に基づいて、規定値を規定値レジスタA533に設定する処理を行う規定値設定プログラム39をプログラム3に挿入する(ステップS21)。

【0072】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS22)。

【0073】

コンパイラ8は、設計データ6と、テストベンチ7とを、エミュレータである協調検証部50a−2用にコンパイルして、記憶部内のコンパイルDB9に格納する(ステップS23)。このステップS23での処理は、ステップS21での処理前に行ってもよい。

【0074】

そして、エミュレータI/F20を介して、コンパイルされた設計データ6とテストベンチ7とを含むコンパイルDB9が協調検証部50a−2にロードされ実行されることにより、検証対象LSI90mと測定用付加回路51とが回路モデルとして実現され、更に、試験プログラム5がメモリ93mにロードされ実行されることによって、エミュレーションが開始される(ステップS24)。

【0075】

エミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って性能測定部51を起動し、処理Aに対する性能測定処理の開始の際に、処理Aに係る規定値(サイクル数)を規定値レジスタA533に設定する(ステップS25)。

【0076】

制御部521は、検証対象LSI91mによる処理Aの開始で、開始レジスタA531に書き込む(ステップS26)。また、制御部521は、カウンタA534をリセットする(ステップS27)。その後、カウンタA534は、サイクル毎にカウントアップされる。

【0077】

検証対象LSI91mによる処理Aの終了で、制御部521は、終了レジスタA532に書き込む(ステップS28)。

【0078】

性能比較部529は、カウンタA534のカウンタ値と規定値レジスタA533に設定された規定値とを比較する(ステップS29)。性能比較部529による比較結果がカウンタA534のカウンタ値が規定値レジスタA533の規定値より大きいことを示す場合、制御部521は、性能に問題があると判定して、結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553で管理されるエラーフラグを1に設定する。

【0079】

エラーフラグが「1」を示す場合、性能に問題があると判定されたことを示し、「0」を示す場合、性能は規定内であり問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、エミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、エミュレーションを停止する。エミュレーションを停止するかどうかは選択することが出来る。

【0080】

一方、エミュレーションを停止せず、性能が規定内であり問題ない場合、上述したステップS26からS29を繰り返す。

【0081】

以下に、機能検証処理のみの処理パターンBに係る機能構成及び処理手順について、シミュレータ(WS100)で実施する場合と、エミュレータ200を用いて実施する場合とで、夫々説明する。

【0082】

機能検証処理のみの処理パターンBをシミュレータ(WS100)で実施する第3実施例に係る処理手順について、図8で説明する。図8は、機能検証処理のみをシミュレータで実施する第3実施例を説明するための図である。図8において、WS100は、更に、記述追加部10を有する。また、測定用付加回路51の機能検証部56のレジスタ部570は、期待値生成用データレジスタ571と、比較モードレジスタB572と、比較開始レジスタB573と、期待値比較エラーレジスタB574とを有する。

【0083】

図8に示す第3実施例において、書込処理挿入部2bは、機能検証の対象処理(以下、処理Bという。例えば、グラフィック処理などである。)の開始時点で、比較モードレジスタB572と、比較開始レジスタB573と、期待値生成データレジスタB571とに書き込みする処理を行うプログラムをプログラム3に挿入する(ステップS31)。

【0084】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS32)。

【0085】

記述追加部10は、テストベンチ7に内部メモリや外部メモリへの入力データを機能検証部56の入力部560に取り込む処理の記述を追加する(ステップS33)。このステップS33での処理は、ステップS31での処理前に行ってもよい。

【0086】

そして、CPU11が、メモリユニット12にロードされた、設計データ6と、テストベンチ7とを実行することによって、シミュレータである協調検証部50b−1として機能し、試験プログラム5がメモリ93mにロードされることによって、シミュレーションを開始する(ステップS34)。

【0087】

シミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って機能検証部56を起動し、処理Bに対する機能検証処理を開始する(ステップS35)。

【0088】

制御部561は、比較開始レジスタB573と、入力部560に取り込まれた入力データとを監視し、比較開始条件になると期待値比較部564によって、期待値との比較を行わせる(ステップS36)。そして、制御部561は、期待値比較部564による比較結果を期待値比較エラーレジスタB574に書き込む(ステップS37)。

【0089】

比較結果が不一致を示す場合、制御部561は、不一致となったアドレス及び入力データを結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553に格納し、また、結果収集部54に、結果格納部550で管理されるエラーフラグを1に設定させる(ステップS38)。

【0090】

エラーフラグが「1」を示す場合、機能に問題があると判定されたことを示し、「0」を示す場合、機能に問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、シミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、シミュレーションを停止する。シミュレーションを停止するかどうかは選択することが出来る。

【0091】

一方、シミュレーションを停止せず、機能に問題ない場合、上述したステップS35からS38を繰り返す。

【0092】

機能検証処理のみの処理パターンBをエミュレータ200を用いて実施する第4実施例に係る処理手順について、図9で説明する。図9は、機能検証処理のみをエミュレータで実施する第4実施例を説明するための図である。図9に示す第4実施例では、WS100がコンパイラ8とコンパイルDB9とを更に有する点で第3実施例と異なる。測定用付加回路51の性能測定部52のレジスタ部530は、図8と同様である。

【0093】

図9に示す第4実施例において、書込処理挿入部2bは、機能検証の対象処理(以下、処理Bという。例えば、グラフィック処理などである。)の開始時点で、比較モードレジスタB572と、比較開始レジスタB573と、期待値生成データレジスタB571とに書き込みする処理を行うプログラムをプログラム3に挿入する(ステップS41)。

【0094】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS42)。

【0095】

記述追加部10は、テストベンチ7に内部メモリや外部メモリへの入力データを機能検証部56の入力部560に取り込む処理の記述を追加する(ステップS43)。このステップS43での処理は、ステップS41での処理前に行ってもよい。

【0096】

コンパイラ8は、設計データ6と、テストベンチ7とを、エミュレータである協調検証部50a−2用にコンパイルして、記憶部内のコンパイルDB9に格納する(ステップS44)。このステップS44での処理は、ステップS41での処理前に行ってもよい。

【0097】

そして、エミュレータI/F20を介して、コンパイルされた設計データ6とテストベンチ7とを含むコンパイルDB9が協調検証部50a−2にロードされ実行されることにより、検証対象LSI90mと測定用付加回路51とが回路モデルとして実現され、更に、試験プログラム5がメモリ93mにロードされ実行されることによって、エミュレーションが開始される(ステップS45)。

【0098】

エミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って機能検証部56を起動し、処理Bに対する機能検証処理を開始する(ステップS46)。

【0099】

制御部561は、比較開始レジスタB573と、入力部560に取り込まれた入力データとを監視し、比較開始条件になると期待値比較部564によって、期待値との比較を行わせる(ステップS47)。そして、制御部561は、期待値比較部564による比較結果を期待値比較エラーレジスタB574に書き込む(ステップS48)。

【0100】

比較結果が不一致を示す場合、制御部561は、不一致となったアドレス及び入力データを結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553に格納し、また、結果収集部54に、結果格納部550で管理されるエラーフラグを1に設定させる(ステップS49)。

【0101】

エラーフラグが「1」を示す場合、機能に問題があると判定されたことを示し、「0」を示す場合、機能に問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、エミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、エミュレーションを停止する。エミュレーションを停止するかどうかは選択することが出来る。

【0102】

一方、エミュレーションを停止せず、機能に問題ない場合、上述したステップS46からS49を繰り返す。

【0103】

以下に、性能測定処理及び機能検証処理による処理パターンCに係る第5及び第6実施例について説明する。第5及び第6実施例において、各回路モデルの構成は、第1から第4実施例で説明した通りである。また、第1から第4実施例より、性能測定処理及び機能検証処理による処理パターンCにおいても、シミュレータ(WS100)で実施することも可能であるし、エミュレータ200を用いて実施することも可能である。

【0104】

性能測定処理と機能検証処理との同時実施では、図6に示す第1実施例と図8に示す第3実施例における機能構成を含み、即ち、検証対象LSI90mと図4に示す測定用付加回路51全体とをWS100で実現する構成A、又は、図7に示す第2実施例と図9に示す第4実施例における機能構成を含み、即ち、検証対象LSI90mと図4に示す測定用付加回路51全体とをエミュレータ200で実現する構成B、のいずれかである。

【0105】

以下に、上記構成A又は構成Bを問わず、性能測定処理と機能検証処理との組み合わせを実現する基本構成50C―1と、更に、現状の性能で性能要件を満たす条件を探索する構成50C―2とを、夫々、第5実施例及び第6実施例として説明する。

【0106】

第5及び第6実施例に共通して、性能に問題があった場合は機能検証部56を停止し、機能に問題があった場合は性能測定部52を停止することが可能である。また、性能又は機能に問題があった場合、結果収集部54を介してその状態をCPU91mに通知することができ、WS100によるシミュレーション又はエミュレータ200によるエミュレーションの実行を停止することが出来る。

【0107】

現状の性能が性能要件を満たすための条件を探索する構成50C―2に係る第6実施例では、クロック周波数を徐々に下げ、性能要件を満たす周波数を探索することができる。また、性能に問題があった場合、機能を選択し、性能要件を満たす機能の組み合わせを探索することができる。更に、性能要件を満たすバス占有率を探索することができる。

【0108】

先ず、第5実施例について図10で説明する。図10は、性能測定処理及び機能検証処理を実施する第5実施例を説明するための図である。図10中、回路モデルの構成は、図6及び図8で例示される通りであるので、協調検証部50c−1では処理構成を示して、性能測定処理と機能検証処理との組み合わせに係る処理手順で第5実施例を説明する。

【0109】

図10において、試験プログラム5が検証対象LSI90mのメモリ93mにロードされると(ステップS71)、検証対象LSI90mのCPU91mによって試験処理98pが開始される(ステップS72)。

【0110】

試験処理98pの開始によって、性能測定部52が起動され(ステップS73)、機能検証部56が起動される(ステップS74)。性能測定部52及び機能検証部56の起動する順は問わない。そして、オーディオ処理などの処理A及びグラフィック処理などの処理Bに係る検証対象処理が開始される。検証対象処理に関して、リアルタイムに測定用付加回路51によって、性能測定及び機能検証が行なわれる。

【0111】

上述したステップS73の性能測定部52の起動によって、図6のステップS14、S15、及びS16、又は、図7のステップS25、S26、及びS27が行われ、性能測定処理52pが開始される。性能測定処理52pでは、サイクル毎にカウントアップされるカウンタA534の値と、規定値レジスタA533の規定値とを比較する(ステップS731)。その比較結果がカウンタA534の値が規定値レジスタA533の規定値を超えることを示す場合(NG)、エラーフラグ「1」の設定が結果収集部54に通知される。エラーフラグ「1」の設定を受けた結果収集部54は、シミュレーション又はエミュレーションを停止する(ステップS76−2)。シミュレーション又はエミュレーションを停止するかどうかは選択することが出来る。

【0112】

一方、その比較結果がカウンタA534の値が規定値レジスタA533の規定値以下であることを示す場合(OK)、処理が終了したか否かが判断される(ステップS735)。処理が終了していない場合(NO)、性能測定処理52pは、ステップS731へ戻り、次のサイクルで上述した同様の比較処理を行う。一方、処理終了である場合(YES)、処理が終了したことが結果収集部54に通知される。

【0113】

上述したステップS74の機能検証部56の起動によって、図8のステップS35又は図9のステップS46が行われ、機能検証処理56pが開始される。機能検証処理56pでは、入力データと期待値とを比較する(ステップS741)。その比較結果が不一致を示す場合(NG)、図8のステップS37又は図9のステップS48が実行され、エラーフラグ「1」の設定が結果収集部54に通知される。エラーフラグ「1」の設定を受けた結果収集部54は、シミュレーション又はエミュレーションを停止する(ステップS76−2)。シミュレーション又はエミュレーションを停止するかどうかは選択することが出来る。

【0114】

一方、その比較結果が一致を示す場合(OK)、処理が終了したか否かが判断される(ステップS735)。処理が終了していない場合(NO)、機能検証処理56pは、ステップS743へ戻り、次の入力データで上述した同様の比較処理を行う。一方、処理終了である場合(YES)、処理が終了したことが結果収集部54に通知される。

【0115】

結果収集部54は、性能測定部52及び機能検証部56からの通知によって収集された比較結果を試験処理98pに通知する(試験処理98pにおける結果収集:ステップS76)。

【0116】

試験処理98pにおいて、測定用付加回路51の結果収集部54から収集した比較結果を参照して、性能測定部52及び機能検証部56による比較結果の判定を行う(比較判定:ステップS77)。比較結果の判定によって、性能又は/及び機能に問題があると判定した場合(NG)、性能又は/及び機能に問題があることを示す試験結果を表示ユニット13に表示させて(ステップS78−1)、この試験処理98pは終了する(ステップS79)。

【0117】

一方、性能又は/及び機能に問題がないと判定した場合(OK)、性能又は/及び機能に問題がないことを示す試験結果を表示ユニット13に表示させて(ステップS78−2)、この試験処理98pは終了する(ステップS79)。

【0118】

次に、現状の性能が性能要件を満たすための条件を探索する構成50C―2に係る第6実施例について、図11で説明する。図11は、性能測定処理及び機能検証処理を実施する第6実施例を説明するための図である。図11中、図10と同一ステップには同一符号を付し、その説明を省略する。また、回路モデルの構成は、図7及び図9で例示される通りであるので、協調検証部50c−2では処理構成を示して、性能測定処理と機能検証処理との組み合わせに係る処理手順で第6実施例を説明する。

【0119】

第6実施例において、試験処理98pでは、現状の性能が性能要件を満たすための条件を探索するために、異なる性能要件に対応した複数のパターンを用いて試験が行われる。各パターンは、ステップS73による性能測定部52の起動及びステップS74による機能検証部56の起動によって開始される。

【0120】

そして、パターン毎に、図10で説明したようにステップS77までの処理が実行され、ステップS78−1又はS78−2による試験結果の表示ユニット13への表示後に、全パターンを実施したか否かが判断される(ステップS78−3)。未だ実施していないパターンがある場合(NO)、次のパターンを実施するためにステップS73へと戻り、上述同様の処理を繰り返す。

【0121】

一方、全パターンを実施した場合(YES)、この試験処理98pは終了する(ステップS79)。

【0122】

現状の性能が性能要件を満たすための条件の探索では、規定値生成部2によって試験プログラム98p中に複数の規定値が準備される。シミュレータ(WS100)による、又は、エミュレータ200を用いた協調検証の実行中に、試験処理98pが規定値を自動で変更することによって、性能が性能要件を満たすための条件を探索する。条件として周波数があり、異なる周波数毎に、規定値算出方法の第1例によって性能要件をサイクル数で示す規定値が算出される。

【0123】

性能要件を満たす周波数を探索する第1の探索例について図12で説明する。図12は、周波数を探索する第1の探索例を説明するための図である。図12において、1回目の周波数「100MHz」及び性能要件「33ms」に基づく規定値1による判定1が、規定値1内で検証対象処理が終了しなかったことを示す場合(S733でNG)、LSIの開発者は、条件となる周波数又は性能要件について再考することとなる。

【0124】

一方、規定値1による判定1が、規定値1内で検証対象処理が終了したことを示す場合(S735でOK)、規定値2のパターンで判定される。2回目の周波数「90MHz」及び性能要件「33ms」に基づく規定値2による判定2が、規定値2内で検証対象処理が終了しなかったことを示す場合(S733でNG)、LSIの開発者は、1回目の規定値1による条件が限界であると判断する。

【0125】

一方、規定値2による判定2が、規定値2内で検証対象処理が終了したことを示す場合(S735でOK)、規定値3のパターンで判定される。このような処理が各規定値1、2、・・・毎に繰り返されることによって、性能要件を満たす条件が探索される。

【0126】

規定値1は、図2に示す規定値算出方法の第1例に従って算出されたサイクル数「3,300,000」を示す。規定値2も同様に算出されたサイクル数「2,970,000」を示す。

【0127】

図13は、図12の第1の探索例での処理概要を説明するためのフローチャート図である。図13において、試験プログラム5によって行われる試験処理98pにおいて、プログラム構成DB71からパターンが選択される(ステップS81)。

【0128】

選択されたパターンのプログラムがCPU91mによって実行される(ステップS82)。実行開始時に、パターンに対応する規定値が性能測定部52に設定される。具体的には、性能測定部52のレジスタ部530内の規定値レジスタA533(図6又は図7)に設定される。

【0129】

そして、性能測定部52による規定値との比較結果が結果収集部54の結果格納部550に書き込まれる(ステップS83)。

【0130】

その後、試験処理98pにおいて、全パターンを実施したか否かが判断される(ステップS84)。全パターンの実施を終了していない場合、ステップS81へ戻り、試験処理98pにおいて、次のパターンが選択され、上述した同様の処理が繰り返される。一方、全パターンを実施した場合、試験処理98pは終了する。

【0131】

プログラム構成DB71は、試験プログラム5に含まれている探索用のパターンに対応したプログラムを含んでいる。この例では、探索用にパターン1、2、3、・・・が含まれていることを示している。パターンの選択は厳しい条件から実施されるようにし、比較結果がNGの場合、即時にシミュレーションを終了させる。パターン毎の比較判定は、表示ユニット13に表示されることにより、LSIの開発者は、周波数の探索結果を知ることができる。

【0132】

パターン1が選択されると、性能測定処理52pにおいて、周波数「100MHz」及び性能要件「33ms」に基づいて算出された規定値1との比較が行われる。次に、パターン2が選択されると、性能測定処理52pにおいて、周波数「90MHz」及び性能要件「33ms」に基づいて算出された規定値2との比較が行われる。更に、パターン3が選択されると、性能測定処理52pにおいて、周波数「80MHz」及び性能要件「33ms」に基づいて算出された規定値3との比較が行われる。

【0133】

次に、図11に示す構成50C―2において、試験プログラム5に、複数の機能の組み合せを準備し、組み合せ毎に性能測定処理52pを行い、性能要件を満たす組み合わせを探索する第2の探索例について説明する。

【0134】

図14は、機能の組み合せを探索する第2の探索例を説明するための図である。図14に示す第2の探索例では、試験プログラム5の中に、機能の組み合せ「A1、A2、及びA3」、「A1及びA2」、及び「A1及びA3」が準備され、シミュレーション(又はエミュレーション)の実行中に、機能の組み合せを選択して、性能要件を満たす組み合せを探索する。

【0135】

機能の組み合せの例として、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大が示されている。

【0136】

性能要件「33ms」の制約において、機能A1、機能A2、及び機能A3の組み合せを1回目で行う。その結果、機能検証ではOKであったが、性能測定では機能A1からA3までを終了するのにかかる所要時間が40msとなり、性能要件の処理時間33msを超えてNGであった。

【0137】

同一の制約において、機能A1及び機能A2の組み合せを2回目で行う。1回目と異なり、機能A3は実行されない。その結果、機能検証がOKであると共に、性能測定では所要時間が33msであり性能要件の処理時間33msを超えることなくOKの判定となった。この例の場合では、1回目の機能の組み合せでは性能要件を満たすことができないが、2回目の機能の組み合わせでは性能要件を満たすことが判る。このように、どの組み合せであれば性能要件を満たすのかを探索することができる。

【0138】

図15は、図14の第2の探索例での処理概要を説明するためのフローチャート図である。図15において、試験プログラム5によって行われる試験処理98pにおいて、プログラム構成DB72からパターンが選択される(ステップS91)。

【0139】

選択されたパターンのプログラムがCPU91mによって実行される(ステップS92)。実行開始時に、規定値が性能測定部52に設定される。この機能の組み合せによる第2の探索例では、性能測定部52に設定される規定値は、周波数に変化はないので、どのパターンが選択されても一律である。

【0140】

そして、性能測定部52による規定値との比較結果が結果収集部54の結果格納部550に書き込まれる(ステップS93)。

【0141】

その後、試験処理98pにおいて、全パターンを実施したか否かが判断される(ステップS94)。全パターンの実施を終了していない場合、ステップS91へ戻り、試験処理98pにおいて、次のパターンが選択され、上述した同様の処理が繰り返される。一方、全パターンを実施した場合、試験処理98pは終了する。

【0142】

プログラム構成DB72は、試験プログラム5に含まれている探索用のパターンに対応したプログラムを含んでいる。この例では、探索用にパターン1(シリアル)、パターン2(シリアル)、パターン3(パラレル)、・・・が含まれていることを示している。

【0143】

パターン1(シリアル)は、機能A1、機能A2、そして機能A3の順に行うパターンである。パターン2(シリアル)は、機能A1、そして機能A2の順に行うパターンである。パターン3(パラレル)は、機能A1及び機能A3を並列で行い、そして機能A2を行うパターンである。

【0144】

選択されたパターンのプログラムが終了するまでに要した所要時間と規定値との比較が行われ、その比較結果が結果収集部54を介して試験処理98pに通知される。

【0145】

第3の探索例として、機能の組み合せは同一であるが、入力画像サイズを変更して、性能要件を満たす条件(入力画像サイズ)を探索する場合について説明する。図16は、同一の機能の組み合せにおいて性能要件を満たす条件を探索する第3の探索例を説明するための図である。

【0146】

図16に示す第3の探索例では、試験プログラム5の中に、複数の入力画像サイズの入力画像データが準備され、シミュレーション(又はエミュレーション)の実行中に、入力画像サイズを変更して、組み合せ機能が性能要件を満たす条件「入力画像サイズ」を探索する。

【0147】

機能の組み合せの例として、機能A1、A2、及びA3が示され、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大である。

【0148】

性能要件「33ms」の制約において、機能A1、機能A2、及び機能A3の組み合せで、入力画像サイズ「1024×768」の入力画像データを用いて1回目を行う。その結果、機能検証ではOKであったが、性能測定では機能A1からA3までを終了するのにかかる所要時間が40msとなり、性能要件の処理時間33msを超えてNGであった。

【0149】

同一の性能要件及び同一の機能の組み合せにおいて、入力画像サイズを「800×600」に変更して、2回目を行う。その結果、機能検証がOKであると共に、性能測定では所要時間が33msであり性能要件の処理時間33msを超えることなくOKの判定となった。この例の場合では、1回目の入力画像サイズ「1024×768」では性能要件を満たすことができないが、2回目の入力画像サイズ「800×600」では性能要件を満たすことが判る。このように、機能の組み合せにおいて、どの条件であれば性能要件を満たすのかを探索することができる。

【0150】

次に、性能要件として、所要時間の代わりに、バス占有率を指定した場合について説明する。性能要件であるバス占有率は、図3の規定値算出方法の第2例で示されるように、規定値生成部2によって、計数可能な規定値で示される。図17は、バス占有率に基づく性能測定について説明するための図である。図17において、CPU96mと、Codec97mと、MEMC98mとを有する検証対象LSI95mと、MEMC98mでコントロールされるSDRAM99mとが試験される各回路モデルである場合を示す。各回路モデルに対して検証対象処理量を監視するためにバスモニタ6a、6b、6c、及び6dを組み込んで、所定時間毎にバス占有率を取得する。

【0151】

このようなバスモニタ6a、6b、6c、及び6dを組み込むことで、検証対象LSI90m内のバス占有率17aと、検証対象LSI90m外のバス占有率17bとを夫々検証することが可能となる。例えば、バス占有率「50%」を規定値とした場合、規定値を超える期間17tが判るため、検証対象LSIの性能に係る設計の見直しを効果的に行うことができる。

【0152】

性能要件をバス占有率「50%」以下とした場合の、性能測定処理及び機能検証処理を実施する第5実施例の変形例について図18で説明する。図18は、第5実施例の変形例を説明するための図である。

【0153】

図18に示す変形例では、試験プログラム5によって、機能の組み合せ「A1、A2、及びA3」が実行され、バス占有率「50%」以下が指定された性能要件に従って、機能検証処理56p及び性能測定処理52pが実行された場合を示している。

【0154】

機能の組み合せの例として、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大が示されている。

【0155】

この例では、バス占有率50%以下の制約において、機能検証ではOKであったが、性能測定ではバス占有率が最大で「60%」となる期間があり、性能要件のバス占有率50%を超えてNGであった。性能測定では機能A1からA3までを実行中に性能要件のバス占有率50%を超えた時刻が存在したことが示されている。

【0156】

所定時間毎のバス占有率を結果収集部54で収集し蓄積するようにし、プログラム実行後の試験結果を表示ユニット13に表示させることで、時刻110msでバス占有率の最大値「60%」を示した結果となったことが判る。このように、どの期間で性能要件を満たすことができなかったのかを知ることができる。

【0157】

次に、同一の機能の組み合せで、性能要件のバス占有率50%以下を満たす条件「入力画像サイズ」を探索する第6実施例の変形例について説明する。図19は、第6実施例の変形例を説明するための図である。

【0158】

図19に示す第6実施例の変形例では、試験プログラム5の中に、複数の入力画像サイズの入力画像データが準備され、シミュレーション(又はエミュレーション)の実行中に、入力画像サイズを変更して、組み合せ機能が性能要件を満たす条件「入力画像サイズ」を探索する。図16に示す第3の探索例との違いは、性能要件として「バス占有率50%」以下が指定される。

【0159】

機能の組み合せの例として、機能A1、A2、及びA3が示され、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大である。

【0160】

バス占有率50%以下の制約において、機能A1、機能A2、及び機能A3の組み合せで、入力画像サイズ「1024×768」の入力画像データを用いて1回目を行う。その結果、機能検証ではOKであったが、性能測定では機能A1からA3を終了するまでの所定時間毎のバス占有率において「50%」を超える期間が存在したためNGであった。

【0161】

同一の性能要件及び同一の機能の組み合せにおいて、入力画像サイズを「800×600」に変更して、2回目を行う。その結果、機能検証がOKであると共に、性能測定では所定時間毎のバス占有率において「50%」以下であったためOKの判定となった。この例の場合では、1回目の入力画像サイズ「1024×768」では性能要件を満たすことができないが、2回目の入力画像サイズ「800×600」では性能要件を満たすことが判る。このように、機能の組み合せにおいて、どの条件であれば性能要件を満たすのか、を探索することができる。

【0162】

また、どの期間で性能要件を満たさないのかを知ることができ、機能を組み合わせた場合に性能が落ちる箇所を検証することができる。この1回目及び2回目の結果例を参照することにより、機能A1−>機能A2−>機能A3のシリアルな処理において、入力画像サイズ「1024×768」の場合に、機能A2で性能要件を満たさない期間が存在する等の検証が容易となる。

【0163】

図20は、図19の第6実施例の変形例での処理概要を説明するためのフローチャート図である。図20において、試験プログラム5によって行われる試験処理98pにおいて、入力画像サイズDB73からパターンが選択される(ステップS101)。

【0164】

所定プログラムがCPU91mによって実行される(ステップS102)。実行開始時に、規定値が性能測定部52に設定される。この変形例では、性能測定部52に設定される規定値は、パターンの選択に影響されないため、どのパターンが選択されてもバス占有率50%以下で一律である。

【0165】

そして、性能測定部52による規定値との比較結果が結果収集部54の結果格納部550に書き込まれる(ステップS103)。

【0166】

その後、試験処理98pにおいて、全パターンを実施したか否かが判断される(ステップS104)。全パターンの実施を終了していない場合、ステップS101へ戻り、試験処理98pにおいて、次のパターンが選択され、上述した同様の処理が繰り返される。一方、全パターンを実施した場合、試験処理98pは終了する。

【0167】

入力画像サイズDB73は、性能要件を満たす条件の探索用のパターンを含んでいる。入力画像サイズDB73によって、パターン毎に、異なる入力画像サイズの入力画像データが管理される。この例では、探索される条件として、入力画像サイズ「1024×768」のパターン1、入力画像サイズ「800×600」のパターン2、・・・が含まれていることを示している。

【0168】

次に、バス占有率を性能要件とした図11に示す第6実施例の構成50C―2による性能測定結果の種々の使用例について説明する。第6実施例の構成50C―2を用いて、車両等に搭載されるようなナビゲーションと、映像再生と、音楽再生とが可能な種々のマルチメディア対応のLSIを検証する場合にについて説明する。

【0169】

図21は、マルチメディア対応LSIの回路モデル構成の例を示す図である。図21には、検証対象となる回路モデルが例示されている。種々のマルチメディア対応のLSI300mは、CPU301mと、DMAC302mと、MEMC303mと、画像処理回路305mと、ディスプレイコントローラ306mと、CD/BD/DVD I/F307mと、HDD I/F308mと、オーディオI/F309mとを有し、バス330mを介して互いに接続される。

【0170】

また、MEMC303mには、SDRAM313mが接続される。ディスプレイコントローラ306mには、ディスプレイ315m及び316mが接続される。CD/BD/DVD I/F307mには、CD/BD/DVD317mが接続される。HDD I/F308mには、HDD318が接続される。オーディオI/F309mには、スピーカー319mが接続される。このような検証対象となる回路モデルにおいて、検証対象処理量を監視するためにバスモニタ9aから9kを組み込んで、所定時間毎にバス占有率を取得する。

【0171】

図22は、図21に示すマルチメディア対応LSIの性能限界の探索例を示す図である。図22では、性能要件をバス占有率50%以下とした場合の性能測定により性能限界を探索する例を示している。1回目のパターンAでは、ナビゲーション、DVD映像再生、再生を含むCDリッピングの3つの機能の組み合わせが行われる。性能測定処理52pにより、全てのバスモニタの総和結果22aを得る。このような総和結果22aから、性能要件のバス占有率50%以下を超える期間が60msから90msと、170msとに存在することが示され、3つの機能を同時に動作させることができないことが判明する。

【0172】

2回目のパターンBでは、ナビゲーション、DVD映像再生、HDD再生のパターンAとは異なる3つの機能の組み合わせが行われる。この機能の組み合せにおいて、HDD再生は、CDリッピングしたデータを予めHDD318mに格納しておき、HDD318mから音楽を再生する。性能測定処理52pにより、全てのバスモニタの総和結果22bを得る。このような総和結果22bから、HDD318mから音楽を再生するようにした機能の組み合せでは、性能要件のバス占有率50%以下を満たすことができ、性能に問題ないことが判明する。

【0173】

例えば、図23に例示されるように、パターンAにおけるCPU301mとMEMC303mを介したSDRAM313mとの間、及び、MEMC303mを介したSDRAM313mとHDD318mとの音楽再生に係る検証対象処理が、パターンBでは削減されることにより、性能要件のバス占有率50%以下を満たすことができたと考えられる。

【0174】

図24は、バスモニタの結果表示のためのフローチャート図である。図24において、シミュレーションが開始されると(ステップS121)、所定プログラムを実行する(ステップS122)。性能測定部52はバスモニタによって測定した測定データ24aを所定時間毎に結果収集部54へ通知して、結果格納部550のメモリ553に書き込む(ステップS123)。

【0175】

シミュレーションが終了すると(ステップS124)、結果格納部550のメモリ553に書き込まれたデータ24aを加工してcsvファイル24bを得る(ステップS125)。そして、csvファイル24bを用いて作成した測定結果を示すグラフ24cを表示ユニット13に表示させる(ステップS126)。

【0176】

測定データ24aは、結果格納部550のメモリ553に16進数で記録され、read回数データ25aと、write回数データ25bとを含む。read回数データ25aは、所定時間毎にreadされた回数が示される。同様に、write回数データ25bは、所定時間毎にwriteされた回数が示される。

【0177】

測定データ24aは、10進数で表されたcsvファイル24bに加工される。csvファイル24bには、所定時間間隔を表す番号0、1、2、・・・毎にread回数及びwrite回数とが対応付けられて記録される。csvファイル24bへの加工は、図10に示す試験処理98pにおいて、試験結果表示(NG)を行うS78−1又は試験結果表示(OK)を行うS78−2などで行うようにすればよい。

【0178】

測定結果を示すグラフ24cは、縦軸にSDRAM用のバス占有率を示し、横軸に時間軸を示している。測定結果を示すグラフ24cが表示ユニット13に表示されることによって、開発者は、制約要件のバス占有率50%を満たしていない期間を視覚的に容易に確認することができる。

【0179】

図21の回路モデル構成例では、測定データ24aを、バスモニタ9aから9kの各々に対して記録することで、開発者は、より詳細な解析を行うことができる。各バスモニタ9a〜9kから得られた測定結果をグラフで表示されることにより、ボトルネック解析により性能改善を行うことができる。

【0180】

図25は、ボトルネック解析の例を説明するための図である。図25において、図21の回路モデル構成例において各バスモニタ9a〜9kから得られた全ての測定結果からボトルネック解析を行った結果、SDRAM313mのバス占有率を示すグラフ25cからSDRAM313mのバス占有率に問題があることが判明した例が示されている。

【0181】

グラフ25cを参照すると、SDRAM313mのバス占有率が、性能要件のバス占有率50%を超えている期間が存在することが判る。従って、開発者は、MEMC303mの改善、SDRAM313mの種類の変更、SDRAM313mの周波数を上げる等の性能改善を行う必要があると判断できる。

【0182】

また、バス占有率の測定結果を用いて、LSI300mの性能に余裕があるか否かを判断することも可能である。性能の余裕度を判定することにより、消費電力をより削減したLSI開発を検討することができる。例えば、ナビゲーションの機能と、HDD再生の機能のみが行えればよい場合に、この組み合せによる性能の余裕度を、バス占有率を性能要件として設定することにより検証することができる。

【0183】

図26は、バス占有率を用いた性能余裕度の検証例を説明するための図である。図26に例示されるバス占有率の測定結果を示すグラフ26cを参照することにより、バス占有率が最大となる時間70msにおいても、性能要件のバス占有率50%までその2割以上の余裕があることが判る。

【0184】

従って、設計者は、周波数を下げることにより、消費電力の削減が可能であると判断することができる。その結果、省エネ対応のLSI300mとなるように周波数の変更に関する設計変更を行うことができる。

【0185】

上述したように、本実施例に係る検証システムでは、LSI設計において、シミュレータ又はエミュレータによるソフトウェア及びハードウェアによる協調検証の実施において、LSIの設計が論理的に正しいことを検証するのみならず、全体の処理時間を測定し、なおかつ、プログラムの個々の部分(機能)の処理を測定し、また、プログラムの個々の部分(機能)の処理に関して、性能要件を満たしているか否かを検証することができる。

【0186】

性能要件を満たす、クロック周波数、機能の組み合せ、入力画像サイズなどを探索することができ、設計改善のための情報を得ることが可能となり、LSI製造前に性能改善を行うことが可能となる。

【0187】

本発明は、具体的に開示された実施例に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【0188】

以上の第1から第6実施例等を含む実施形態に関し、更に以下の付記を開示する。

(付記1)

コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、

前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、

前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う

ことを特徴とする協調検証方法。

(付記2)

前記規定値は、前記性能要件で指定される処理時間と、前記設計回路の設計データで示されるクロック周波数とに基づいて算出されたサイクル数であることを特徴とする付記1記載の協調検証方法。

(付記3)

前記設計回路にロードされるプログラムに異なるクロック周波数に基づく複数の規定値を含み、前記協調検証の実施中に、規定値を変更することによって、前記性能要件を満たす該クロック周波数を探索することを特徴とする付記2記載の協調検証方法。

(付記4)

前記規定値は、前記性能要件で指定されるバス占有率と、前記設計回路の設計データで示されるバス動作周波数及び分解能で指定された単位時間あたりのバスサイクル数であることを特徴とする付記1記載の協調検証方法。

(付記5)

前記設計回路にロードされるプログラムに複数の機能の組み合せを含み、前記協調検証の実施中に、該機能の組み合せを変更することによって、前記性能要件を満たす該機能の組み合せを探索することを特徴とする付記1記載の協調検証方法。

(付記6)

前記設計回路にロードされるプログラムに一の機能の組み合せと複数の入力画像サイズとを含み、前記協調検証の実施中に、該入力画像サイズを変更することによって、前記性能要件を満たす該入力画像サイズを探索することを特徴とする付記1記載の協調検証方法。

(付記7)

前記機能の組み合せは、シリアル又はパラレルで実行する組み合せを含むことを特徴とする付記5又は6記載の協調検証方法。

(付記8)

所定時間毎に、前記設計回路におけるバスモニタによる該設計回路のメモリへのread回数及びwrite回数とを結果格納部に格納し、

16進数で示される前記read回数及びwrite回数を10進数で示すデータファイルに加工し、

時系列にバス占有状態を表すグラフ図を表示ユニットに表示させる

ことを特徴とする付記1又は4記載の協調検証方法。

(付記9)

設計回路のソフトウェア及びハードウェアによる協調検証を行なう協調検証装置であって、

性能測定部と、結果収集部とを少なくとも有する測定用付加回路を有し、

性能測定部は、

前記設計回路の性能要件に基づく計数可能な規定値が設定される規定値レジスタと、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントするカウンタレジスタと、

前記カウンタレジスタの値と前記規定値レジスタに設定された前記規定値とを比較する性能比較部とを有し、

前記結果収集部は、前記性能比較部による結果を格納する結果格納部を有する

ことを特徴とする協調検証装置。

(付記10)

前記測定用付加回路は、更に、機能検証部を有し、

前記機能検証部は、

前記設計回路によって処理されたデータを入力する入力部と、

前記入力部が入力したデータと期待値データとを比較する機能比較部とを有し、

前記結果収集部は、前記結果格納部に前記機能比較部による結果を格納することを特徴とする付記9記載の協調検証装置。

(付記11)

前記結果収集部は、前記性能測定部又は前記機能検証部にエラーを検出した場合、前記協調検証を停止させることを特徴とする付記9又は10記載の協調検証装置。

(付記12)

前記測定付加回路は、ハードウェア記述言語で記述された回路であることを特徴とする付記9乃至11記載の協調検証装置。

(付記13)

前記協調検証装置は、シミュレータ又はエミュレータであることを特徴とする付記9乃至12記載の協調検証装置。

(付記14)

前記設計回路のソフトウェア及びハードウェアによる協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、

前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う

処理をコンピュータに実行させることを特徴とするプログラム。

【符号の説明】

【0189】

1 性能要件データ

2 規定値生成部

2a 書込処理挿入部

3 プログラム

4 変換部

5 試験プログラム

6 設計データ(検証対象LSI)

7 テストベンチ

8 コンパイラ

8a 規定値算出データ

8b 規定値算出データ

9 コンパイルDB

11 CPU

12 メモリユニット

13 表示ユニット

14 出力ユニット

15 入力ユニット

16 通信ユニット

17 記憶装置

18 ドライバ

19 記憶媒体

39 規定値設定プログラム

50 協調検証部

50a−1、50b−1 協調検証部(シミュレータ)

50a−2、50b−2 協調検証部(エミュレータ)

50c−1、50c−2 協調検証部(シミュレータ又はエミュレータ)

51 測定用付加回路

52 性能測定部

54 結果収集部

56 機能検証部

58 期待値データ

90m 検証対象LSI

91m CPU

93m メモリ

521 制御部

529 性能比較部

530 レジスタ部

531 開始レジスタA

532 終了レジスタA

533 規定値レジスタA

534 カウンタA

541 制御部

550 結果格納部

553 メモリ

560 入力部

561 制御部

562 期待値生成部

563 期待値格納メモリ

564 期待値比較部

570 レジスタ部

571 期待値生成用データレジスタB

572 比較モードレジスタB

573 比較開始レジスタB

574 期待値比較エラーレジスタB

1000 検証システム

【技術分野】

【0001】

本発明は、設計回路のソフトウェア及びハードウェアによる協調検証を行なう協調検証方法及び協調検証装置に関する。

【背景技術】

【0002】

ソフトウェアの開発において、そのソフトウェアが動作するハードウェアのモデルを用いて、ソフトウェアとハードウェアとを協調動作させて検証することが行なわれている。マルチメディア向け等のLSI(Large Scale Integration)で実行されるプログラム(ソフトウェア)では、リアルタイム性が要求されるものが多く、それらのプログラムで繰り返し実行される処理単位は、常に規定時間以内で実行されなければならないという強い制約が要求される場合が多い。

【0003】

検証を行なう際に、プログラムを実行した際の処理単位に係る処理時間を監視することが考えられる。処理時間を監視するという観点において、所定処理に対して処理時間を監視し、所定時間を経過した際にはタイムアウトを通知する技術や、ソフトウェア・ハードウェア協調検証において、ソフトウェアモデルの処理時間を検証用プラットフォームにおける検証時刻から算出したタイマの値に基づき、予め設定されたタイマ間隔でシミュレーション時刻を監視する技術などが提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平04−239341号公報

【特許文献2】特開平04−279940号公報

【特許文献3】特開2010−009113号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来の技術は、何らかの要因で処理が決められた時間に終了しない、処理がループしてしまい終了しない等の状態を監視する技術であるため、検証対象のプログラムが正常に機能する場合には、そのような機能的には問題の無いプログラムを、制約で規定された性能に基づいて、精度良く評価することができない。

【0006】

マルチメディア用のプログラムでは、機能の制約を満たしていたとしても、例えば、グラフィック処理、オーディオ処理等で、ある処理単位の実行が規定時間を越えた場合、ノイズの混入などにより品質が問題となる場合がある。

【0007】

LSI設計においてシミュレータ及びエミュレータによるソフトウェア・ハードウェア協調検証を実施する際に、論理的に正しいことを検証するだけでなく、全体の処理時間を測定し、なおかつ、プログラムの個々の部分の処理に関して、規定時間内に実行されていることを同時に検証することができない。そのため、オーディオ処理において、ある瞬間のサンプリングに処理が間に合わないためのノイズが発生するケースなどを検出すること、即ち、機能に問題はないが、性能に問題がある処理の検出は困難であった。

【0008】

よって、本発明の目的は、LSI製造前の段階のソフトウェア・ハードウェア協調検証において、ソフトウェア及びハードウェアの機能のみならず性能上の制約を検証可能とすることである。

【課題を解決するための手段】

【0009】

開示の技術は、コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う。

【0010】

また、上記課題を解決するための手段として、協調検証装置、コンピュータに上記協調検証方法として行わせるためのプログラム、及び、そのプログラムを記録した記録媒体とすることもできる。

【発明の効果】

【0011】

開示の技術では、性能要件に基づく計数可能な規定値を用いて性能測定することによって、設計回路が性能要件を満たしているか否かを判定することができる。

【図面の簡単な説明】

【0012】

【図1】基本構成を示す図である。

【図2】規定値算出方法の第1例を説明するための図である。

【図3】規定値算出方法の第2例を説明するための図である。

【図4】測定用付加回路の機能構成例を示す図である。

【図5】検証システムのハードウェア構成を示す図である。

【図6】性能測定処理のみをシミュレータで実施する第1実施例を説明するための図である。

【図7】性能測定処理のみをエミュレータを用いて実施する第2実施例を説明するための図である。

【図8】機能検証処理のみをシミュレータで実施する第3実施例を説明するための図である。

【図9】機能検証処理のみをエミュレータで実施する第4実施例を説明するための図である。

【図10】性能測定処理及び機能検証処理を実施する第5実施例を説明するための図である。

【図11】性能測定処理及び機能検証処理を実施する第6実施例を説明するための図である。

【図12】周波数を探索する第1の探索例を説明するための図である。

【図13】図12の第1の探索例での処理概要を説明するためのフローチャート図である。

【図14】機能の組み合せを探索する第2の探索例を説明するための図である。

【図15】図14の第2の探索例での処理概要を説明するためのフローチャート図である。

【図16】同一の機能の組み合せにおいて性能要件を満たす条件を探索する第3の探索例を説明するための図である。

【図17】バス占有率に基づく性能測定について説明するための図である。

【図18】第5実施例の変形例を説明するための図である。

【図19】第6実施例の変形例を説明するための図である。

【図20】図19の第6実施例の変形例での処理概要を説明するためのフローチャート図である。

【図21】マルチメディア対応LSIの回路モデル構成の例を示す図である。

【図22】図21に示すマルチメディア対応LSIの性能限界の探索例を示す図である。

【図23】データフロー例を示す図である。

【図24】バスモニタの結果表示のためのフローチャート図である。

【図25】ボトルネック解析の例を説明するための図である。

【図26】バス占有率を用いた性能余裕度の検証例を説明するための図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態を図面に基づいて説明する。本実施の形態では、LSIで実行される個々の部分処理について、シミュレータ及びエミュレータを用いたソフトウェア・ハードウェア協調検証(以下、協調検証と言う)において、論理的に正しいことを検証するのに加えて、予め指定された性能要件内で実行されていることを監視することによって、性能又は/及び機能面の処理違反を検出可能とし、また、解析のためにその検証結果を提供する。

【0014】

図1は、基本構成を示す図である。図1中、本実施の形態に係る構成部のみを示し、他構成部を省略している。図1に例示される基本構成において、検証システム1000は、主に、規定値生成部2と、変換部4と、協調検証部50とを有する。更に、性能要件データ1と、プログラム3と、試験プログラム5と、設計データ6と、テストベンチ7とが記憶部に格納されている。

【0015】

後述されるように、規定値生成部2と、変換部4と、協調検証部50とは、ワークステーションなどのコンピュータ装置において、対応するプログラムをCPUが実行することによって実現される処理部である。或いは、規定値生成部2と変換部4とは、一つのワークステーションで実現され、協調検証部50は、エミュレータで実現されてもよい。

【0016】

性能要件データ1は、制約によって規定される性能要件を示し、検証対象の部分処理に要求される処理時間、バスの占有率などのデータを含む。

【0017】

規定値生成部2は、性能要件データ1を読み込んで、性能検証用の規定値を生成する。性能要件データ1によって規定される性能要件に係る値から、協調検証部50での処理において計数可能な規定値を算出する処理部である。規定値生成部2は、検証対象の部分処理が開始される際に、算出された規定値を協調検証部50の所定のレジスタに書き込むための規定値設定プログラム39を検証対象のプログラム3に埋め込む。

【0018】

変換部4は、プログラム3を、検証対象LSI90mを試験するための試験プログラム5に変換する処理部である。プログラム3は、各部分処理の性能又は/及び機能を検証するために、検証対象LSI90mで実行させるプログラムである。試験プログラム5は、変換部4によって、検証対象LSI90mで実行可能なプログラムコードに変換される。

【0019】

設計データ6は、RTL(Register Transfer Level)などのハードウェア記述言語によってハードウェアの動作を抽象化して表現したデータである。

【0020】

テストベンチ7は、試験プログラム5によって動作する検証対象LSI90mの性能又は/及び機能を検証するためのRTL(Register Transfer Level)などのハードウェア記述言語で作成した回路モデルを含み、協調検証部50に実装される。本実施の形態では、テストベンチ7は、測定用に付加されるRTL(Register Transfer Level)などのハードウェア記述言語で作成された回路モデルである測定用付加回路51を有する。

【0021】

協調検証部50は、シミュレータ又はエミュレータ上で協調検証を行なう処理部であり、検証対象LSI90mと、測定用付加回路51とを有する。

【0022】

検証対象LSI90mは、設計データ6が協調検証部50にロードされることによって実装される、設計されたLSIの動作を表す回路モデルであり、少なくともCPU91mとメモリ93mとを有する。CPU91mとメモリ93mとも、回路モデルとして実装される。試験プログラム5がメモリ93mにロードされ、CPU91mが試験プログラム5を実行することによって、協調検証が開始される。

【0023】

所定の部分処理の開始の際に、CPU91mは、規定値生成部2によって埋め込まれた規定値設定プログラム39に従って、規定値を測定用付加回路51の所定レジスタに書き込んで所定の部分処理を実行し、所定の部分処理の実行中に測定用付加回路51が検証対象LSI90mの性能又は/及び機能を測定することによって収集した結果を取得して、試験結果を判定する。

【0024】

測定用付加回路51は、テストベンチ7が協調検証部50にロードされることによって実装される回路モデルであり、性能測定部52と、機能検証部54と、結果収集部54とを有する。

【0025】

性能測定部52は、試験プログラム5によって起動され、検証対象LSI90mの動作が開始されると、CPU91mが設定した規定値に基づいて性能測定を行う処理部である。その結果は結果収集部54によって収集されて、検証対象LSI90mに通知される。

【0026】

機能検証部56は、試験プログラム5によって起動され、検証対象LSI90mの動作の機能測定を行う処理部である。その結果は結果収集部54によって収集されて、検証対象LSI90mに通知される。

【0027】

結果収集部54は、性能測定部52又は/及び56からの結果を収集して、CPU91mに通知する。CPU91mが実行している試験プログラム5によって、結果が判定される。

【0028】

次に、規定値生成部2によって行われる規定値算出方法の例について、図2、図3で説明する。図2は、規定値算出方法の第1例を説明するための図である。図2において、性能を満たすための処理時間「33ms」が指定されている性能要件データ1aと、規定値を算出するために使用される規定値算出データ8aとが、規定値生成部2に読み込まれる。

【0029】

この第1例では、規定値算出データ8aによって、設計データ6から得られるクロック周波数「100MHz」が指定される。

【0030】

規定値生成部2は、読み込んだ性能要件データ1aで指定される性能要件と規定値算出データ8aで指定されるクロック周波数とに基づいて、規定値となる設計データ6に対するサイクル数を算出する。

【0031】

規定値生成部2は、クロック周波数「100MHz」から設計データ6の1サイクル「10ns」を求め、設計データ6の1サイクル「10ns」で処理時間「33ms」を除算することにより、処理時間「33ms」を満たすための、設計データ6において処理を終えなければならない「3,300,000」サイクルを取得する。

【0032】

規定値生成部2は、算出結果のサイクル数「3,300,000」を性能測定時の規定値として所定レジスタに書き込むための規定値設定プログラム39をプログラム3に埋め込む。

【0033】

図3は、規定値算出方法の第2例を説明するための図である。図3において、性能を満たすためのバス占有率「50%」以下が指定されている性能要件データ1bと、規定値を算出するために使用される規定値算出データ8bとが、規定値生成部2に読み込まれる。

【0034】

この第2例では、規定値算出データ8bによって、設計データ6から得られるバス動作周波数「100MHz」及びバス幅「64bit」と、1コマンドの転送量としてreadコマンド「64bit」及びwriteコマンド「64bit」、分解能「1秒」が指定される。

【0035】

規定値生成部2は、読み込んだ性能要件データ1bで指定される性能要件と規定値算出データ8bで指定されるクロック周波数とに基づいて、規定値となる設計データ6に対するサイクル数を算出する。

【0036】

規定値生成部2は、読み込んだ性能要件データ1bで指定される性能要件と規定値算出データ8bで指定される設計データ6のバス動作周波数「100MHz」及びバス幅「64bit」と、1コマンドの転送量とに基づいて、規定値となるコマンド発行可能最大数を算出する。

【0037】

規定値生成部2は、バス動作周波数「100MHz」にバス幅「64bit」を乗算することにより最大転送量(理論値)「6400Mbps」を求める。read及びwriteとも64bitの1コマンドの転送量を考慮すると、性能要件バス占有率「50%」以下を満たすには、最大転送量(理論値)「6400Mbps」を1コマンド分の「64bit」で除算し、更に、性能要件バス占有率「50%」を乗算することによって、性能として要求される、1秒間あたりコマンド発行可能最大回数「50M回」を取得する。この場合、分解能は「1秒」であるので、分解能1秒当たりのコマンド発行可能最大回数は「50M回」となる。分解能が「2秒」の場合は、分解能2秒当たりのコマンド発行可能最大回数は「100M回」となる。

【0038】

規定値生成部2は、算出結果のコマンド発行可能最大回数「50M回」を性能測定時の規定値として所定レジスタに書き込むための規定値設定プログラム39をプログラム3に埋め込む。

【0039】

図4は、測定用付加回路の機能構成例を示す図である。図4において、RTLで記述された回路モデルである測定用付加回路51は、性能測定部52と、結果収集部54と、機能検証部56とを有する。

【0040】

性能測定部52は、検証対象LSI90mの性能を測定し、制御部521と、性能比較部529と、レジスタ部530とを有する。

【0041】

制御部521は、性能測定の開始と終了とを監視し、性能測定部52での処理を制御する。

【0042】

図2に示す規定値算出方法の第1例の場合、処理の開始からサイクル毎にカウントする。また、カウント値が規定値を超えた場合、制御部521は、結果収集部54に通知し、性能測定の結果を、結果格納部550を介してメモリ553に記憶する。

【0043】

また、図3に示す規定値算出方法の第2例の場合、制御部521は、検証対象LSI91mに対して、バスモニタを組み込んで、処理の開始からコマンド発行毎にカウントを行う。制御部521は、指定された分解能を変換したサイクル数分を経過するとカウンタをリセットする。カウント値が規定値を超えた場合、制御部521は、結果収集部54に通知し、性能測定の結果を、結果格納部550を介してメモリ553に記憶する。

【0044】

性能比較部529は、検証対象LSI90mが処理開始時に設定した規定値と処理中にカウントしたカウント値とを比較することによって性能測定を行う。レジスタ部530は、性能測定に必要な複数のレジスタを有する。

【0045】

結果収集部54は、性能測定部52から出力される比較結果を収集し、制御部541と、結果格納部550とを有する。制御部541は、性能測定部52及び機能検証部56からの結果を受信し、結果格納部550のメモリ553に格納する。また、制御部541は、性能測定部52及び機能検証部56からの結果を検証対象LSI90mに通知する。即ち、性能測定部52及び機能検証部56からの結果は、検証対象LSI90mで実行されている試験プログラム5に通知される。一方、性能又は機能に問題があった場合には、制御部541は、測定用付加回路51を停止させる。

【0046】

機能検証部56は、検証対象LSI90mの機能を測定し、入力部560と、制御部561と、期待値生成部562と、期待値格納メモリ563と、期待値比較部564と、レジスタ部570とを有する。機能の測定には、検証対象LSI90mが正しく機能しているか否かに関する測定を含む。

【0047】

入力部560は、内部メモリや外部メモリへの入力データを機能検証部56に取り込む。制御部561は、入力データとの比較開始条件を判断し、期待値比較部564によって期待値との比較を行わせる。

【0048】

期待値生成部562は、期待値データ58を生成し、期待値格納メモリ563に格納する。期待値比較部564は、入力部560から取り込まれた入力データと、期待値データ58とを比較する。制御部561によって、比較結果に応じたデータが結果収集部54に提供される。結果収集部54は、機能検証部56の制御部561から期待値データ58との比較不一致が通知されると、測定用付加回路51を停止させる。

【0049】

上述した機能構成に基づく協調検証における処理パターンとして、

処理パターンA:性能測定処理のみ

処理パターンB:機能検証処理のみ

処理パターンC:性能測定処理及び機能検証処理(処理パターンA+B)

このように、3種類の処理パターンがある。これら処理パターンA、B、及びC毎に、エミュレータを使用しないシミュレータのみの実施例、及びエミュレータを使用する場合の実施例の各々について、処理概要を説明する。

【0050】

上述した機能実装A、B、及びCの説明にあたり、先ず、検証システム1000のハードウェア構成について説明する。図5は、検証システム1000のハードウェア構成を示す図である。図5において、検証システム1000は、少なくともWS(ワークステーション)100を有する。

【0051】

WS100は、シミュレータとして機能するようにコンピュータによって制御される装置であって、CPU(Central Processing Unit)11と、メモリユニット12と、表示ユニット13と、出力ユニット14と、入力ユニット15と、通信ユニット16と、記憶装置17と、ドライブ18とを有し、バスBに接続される。

【0052】

CPU11は、メモリユニット12に格納されたプログラムに従ってWS100を制御する。メモリユニット12には、RAM(Random Access Memory)及びROM(Read-Only Memory)等が用いられ、CPU11にて実行されるプログラム、CPU11での処理に必要なデータ、CPU11での処理にて得られたデータ等を格納する。また、メモリユニット12の一部の領域が、CPU11での処理に利用されるワークエリアとして割り付けられている。

【0053】

表示ユニット13は、CPU11の制御のもとに必要な各種情報を表示する。出力ユニット14は、プリンタ等を有し、利用者からの指示に応じて各種情報を出力するために用いられる。入力ユニット15は、マウス、キーボード等を有し、LSIの開発者等のユーザがWS100が処理を行なうための必要な各種情報を入力するために用いられる。通信ユニット16は、例えばインターネット、LAN(Local Area Network)等に接続し、外部装置との間の通信制御をするための装置である。

【0054】

記憶装置17には、例えば、ハードディスクユニットが用いられ、各種処理を実行する規定値生成部2、変換部4、協調検証部50での処理を実現するためのプログラム等、また、検証対象LSI90mで実行される検証対象の処理を行わせるためのプログラム3、メモリ93mの形式に変換された試験プログラム5、設計データ6、テストベンチ7等のデータを格納する。

【0055】

メモリユニット12又は/及び記憶装置17などによって、本実施の形態において必要なプログラム及びデータを記憶する記憶部が形成される。

【0056】

WS100によって行われる処理を実現するプログラムは、例えば、CD−ROM(Compact Disc Read-Only Memory)等の記憶媒体19によってWS100に提供される。即ち、プログラムが保存された記憶媒体19がドライブ18にセットされると、ドライブ18が記憶媒体19からプログラムを読み出し、その読み出されたプログラムがバスBを介して記憶装置17にインストールされる。そして、プログラムが起動されると、記憶装置17にインストールされたプログラムに従ってCPU11がその処理を開始する。尚、プログラムを格納する媒体としてCD−ROMに限定するものではなく、コンピュータが読み取り可能な媒体であればよい。コンピュータ読取可能な記憶媒体として、CD−ROMの他に、DVDディスク、USBメモリ等の可搬型記録媒体、フラッシュメモリ等の半導体メモリであっても良い。

【0057】

また、WS100によって行われる処理を実現するプログラムが、通信ユニット16を介して外部装置から提供されてもよい。或いは、外部装置へ該プログラムを提供し、後述される各処理は外部装置で実現されるように構成してもよい。通信ユニット16による通信は無線又は有線に限定されるものではない。

【0058】

また、検証システム1000は、更に、エミュレータI/F20を有することにより、エミュレータ200との通信によって、エミュレータ200を用いた協調検証を行なうこともできる。

【0059】

以下に、性能測定処理のみの処理パターンAに係る機能構成及び処理手順について、シミュレータ(WS100)で実施する場合と、エミュレータ200を用いて実施する場合とで、夫々説明する。

【0060】

性能測定処理のみの処理パターンAをシミュレータ(WS100)で実施する第1実施例に係る処理手順について、図6で説明する。図6は、性能測定処理のみをシミュレータで実施する第1実施例を説明するための図である。図6において、WS100は、書込処理挿入部2aを有し、測定用付加回路51の性能測定部52のレジスタ部530は、開始レジスタA531と、終了レジスタA532と、規定値レジスタA533と、カウンタA534とを有する。

【0061】

図6に示す第1実施例において、書込処理挿入部2aは、性能測定の対象処理(以下、処理Aという。例えば、オーディオ処理などである。)の開始時点で開始レジスタA531に書き込む処理、及び終了時点て終了レジスタA532に書き込む処理を行うプログラムをプログラム3に挿入し、また、規定値生成部2は、性能要件データ1に基づいて、規定値を規定値レジスタA533に設定する処理を行う規定値設定プログラム39をプログラム3に挿入する(ステップS11)。

【0062】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS12)。

【0063】

そして、CPU11が、メモリユニット12にロードされた、設計データ6と、テストベンチ7とを実行することによって、シミュレータである協調検証部50a−1として機能し、試験プログラム5がメモリ93mにロードされることによって、シミュレーションを開始する(ステップS13)。

【0064】

シミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って性能測定部51を起動し、処理Aに対する性能測定処理の開始の際に、処理Aに係る規定値(サイクル数)を規定値レジスタA533に設定する(ステップS14)。

【0065】

制御部521は、検証対象LSI91mによる処理Aの開始で、開始レジスタA531に書き込む(ステップS15)。また、制御部521は、カウンタA534をリセットする(ステップS16)。その後、カウンタA534は、サイクル毎にカウントアップされる。

【0066】

検証対象LSI91mによる処理Aの終了で、制御部521は、終了レジスタA532に書き込む(ステップS17)。

【0067】

性能比較部529は、カウンタA534のカウンタ値と規定値レジスタA533に設定された規定値とを比較する(ステップS18)。性能比較部529による比較結果がカウンタA534のカウンタ値が規定値レジスタA533の規定値より大きいことを示す場合、制御部521は、性能に問題があると判定して、結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553で管理されるエラーフラグを1に設定する。

【0068】

エラーフラグが「1」を示す場合、性能に問題があると判定されたことを示し、「0」を示す場合、性能は規定内であり問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、シミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、シミュレーションを停止する。シミュレーションを停止するかどうかは選択することが出来る。

【0069】

一方、シミュレーションを停止せず、性能が規定内であり問題ない場合、上述したステップS15からS18を繰り返す。

【0070】

性能測定処理のみの処理パターンAをエミュレータ200を用いて実施する第2実施例に係る処理手順について、図7で説明する。図7は、性能測定処理のみをエミュレータを用いて実施する第2実施例を説明するための図である。図7に示す第2実施例では、WS100がコンパイラ8とコンパイルDB9とを更に有する点で第1実施例と異なる。測定用付加回路51の性能測定部52のレジスタ部530は、図6と同様である。

【0071】

図7に示す第2実施例において、書込処理挿入部2aは、性能測定の対象処理(以下、処理Aという。例えば、オーディオ処理などである。)の開始時点で開始レジスタA531に書き込む処理、及び終了時点て終了レジスタA532に書き込む処理を行うプログラムをプログラム3に挿入し、また、規定値生成部2は、性能要件データ1に基づいて、規定値を規定値レジスタA533に設定する処理を行う規定値設定プログラム39をプログラム3に挿入する(ステップS21)。

【0072】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS22)。

【0073】

コンパイラ8は、設計データ6と、テストベンチ7とを、エミュレータである協調検証部50a−2用にコンパイルして、記憶部内のコンパイルDB9に格納する(ステップS23)。このステップS23での処理は、ステップS21での処理前に行ってもよい。

【0074】

そして、エミュレータI/F20を介して、コンパイルされた設計データ6とテストベンチ7とを含むコンパイルDB9が協調検証部50a−2にロードされ実行されることにより、検証対象LSI90mと測定用付加回路51とが回路モデルとして実現され、更に、試験プログラム5がメモリ93mにロードされ実行されることによって、エミュレーションが開始される(ステップS24)。

【0075】

エミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って性能測定部51を起動し、処理Aに対する性能測定処理の開始の際に、処理Aに係る規定値(サイクル数)を規定値レジスタA533に設定する(ステップS25)。

【0076】

制御部521は、検証対象LSI91mによる処理Aの開始で、開始レジスタA531に書き込む(ステップS26)。また、制御部521は、カウンタA534をリセットする(ステップS27)。その後、カウンタA534は、サイクル毎にカウントアップされる。

【0077】

検証対象LSI91mによる処理Aの終了で、制御部521は、終了レジスタA532に書き込む(ステップS28)。

【0078】

性能比較部529は、カウンタA534のカウンタ値と規定値レジスタA533に設定された規定値とを比較する(ステップS29)。性能比較部529による比較結果がカウンタA534のカウンタ値が規定値レジスタA533の規定値より大きいことを示す場合、制御部521は、性能に問題があると判定して、結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553で管理されるエラーフラグを1に設定する。

【0079】

エラーフラグが「1」を示す場合、性能に問題があると判定されたことを示し、「0」を示す場合、性能は規定内であり問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、エミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、エミュレーションを停止する。エミュレーションを停止するかどうかは選択することが出来る。

【0080】

一方、エミュレーションを停止せず、性能が規定内であり問題ない場合、上述したステップS26からS29を繰り返す。

【0081】

以下に、機能検証処理のみの処理パターンBに係る機能構成及び処理手順について、シミュレータ(WS100)で実施する場合と、エミュレータ200を用いて実施する場合とで、夫々説明する。

【0082】

機能検証処理のみの処理パターンBをシミュレータ(WS100)で実施する第3実施例に係る処理手順について、図8で説明する。図8は、機能検証処理のみをシミュレータで実施する第3実施例を説明するための図である。図8において、WS100は、更に、記述追加部10を有する。また、測定用付加回路51の機能検証部56のレジスタ部570は、期待値生成用データレジスタ571と、比較モードレジスタB572と、比較開始レジスタB573と、期待値比較エラーレジスタB574とを有する。

【0083】

図8に示す第3実施例において、書込処理挿入部2bは、機能検証の対象処理(以下、処理Bという。例えば、グラフィック処理などである。)の開始時点で、比較モードレジスタB572と、比較開始レジスタB573と、期待値生成データレジスタB571とに書き込みする処理を行うプログラムをプログラム3に挿入する(ステップS31)。

【0084】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS32)。

【0085】

記述追加部10は、テストベンチ7に内部メモリや外部メモリへの入力データを機能検証部56の入力部560に取り込む処理の記述を追加する(ステップS33)。このステップS33での処理は、ステップS31での処理前に行ってもよい。

【0086】

そして、CPU11が、メモリユニット12にロードされた、設計データ6と、テストベンチ7とを実行することによって、シミュレータである協調検証部50b−1として機能し、試験プログラム5がメモリ93mにロードされることによって、シミュレーションを開始する(ステップS34)。

【0087】

シミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って機能検証部56を起動し、処理Bに対する機能検証処理を開始する(ステップS35)。

【0088】

制御部561は、比較開始レジスタB573と、入力部560に取り込まれた入力データとを監視し、比較開始条件になると期待値比較部564によって、期待値との比較を行わせる(ステップS36)。そして、制御部561は、期待値比較部564による比較結果を期待値比較エラーレジスタB574に書き込む(ステップS37)。

【0089】

比較結果が不一致を示す場合、制御部561は、不一致となったアドレス及び入力データを結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553に格納し、また、結果収集部54に、結果格納部550で管理されるエラーフラグを1に設定させる(ステップS38)。

【0090】

エラーフラグが「1」を示す場合、機能に問題があると判定されたことを示し、「0」を示す場合、機能に問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、シミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、シミュレーションを停止する。シミュレーションを停止するかどうかは選択することが出来る。

【0091】

一方、シミュレーションを停止せず、機能に問題ない場合、上述したステップS35からS38を繰り返す。

【0092】

機能検証処理のみの処理パターンBをエミュレータ200を用いて実施する第4実施例に係る処理手順について、図9で説明する。図9は、機能検証処理のみをエミュレータで実施する第4実施例を説明するための図である。図9に示す第4実施例では、WS100がコンパイラ8とコンパイルDB9とを更に有する点で第3実施例と異なる。測定用付加回路51の性能測定部52のレジスタ部530は、図8と同様である。

【0093】

図9に示す第4実施例において、書込処理挿入部2bは、機能検証の対象処理(以下、処理Bという。例えば、グラフィック処理などである。)の開始時点で、比較モードレジスタB572と、比較開始レジスタB573と、期待値生成データレジスタB571とに書き込みする処理を行うプログラムをプログラム3に挿入する(ステップS41)。

【0094】

次に、変換部4は、プログラム3をシミュレーション用のメモリ形式に変換することによって、試験プログラム5を生成する(ステップS42)。

【0095】

記述追加部10は、テストベンチ7に内部メモリや外部メモリへの入力データを機能検証部56の入力部560に取り込む処理の記述を追加する(ステップS43)。このステップS43での処理は、ステップS41での処理前に行ってもよい。

【0096】

コンパイラ8は、設計データ6と、テストベンチ7とを、エミュレータである協調検証部50a−2用にコンパイルして、記憶部内のコンパイルDB9に格納する(ステップS44)。このステップS44での処理は、ステップS41での処理前に行ってもよい。

【0097】

そして、エミュレータI/F20を介して、コンパイルされた設計データ6とテストベンチ7とを含むコンパイルDB9が協調検証部50a−2にロードされ実行されることにより、検証対象LSI90mと測定用付加回路51とが回路モデルとして実現され、更に、試験プログラム5がメモリ93mにロードされ実行されることによって、エミュレーションが開始される(ステップS45)。

【0098】

エミュレーションの開始によって、検証対象LSI90mのCPU91mは、メモリ93mにロードされた試験プログラム5に従って機能検証部56を起動し、処理Bに対する機能検証処理を開始する(ステップS46)。

【0099】

制御部561は、比較開始レジスタB573と、入力部560に取り込まれた入力データとを監視し、比較開始条件になると期待値比較部564によって、期待値との比較を行わせる(ステップS47)。そして、制御部561は、期待値比較部564による比較結果を期待値比較エラーレジスタB574に書き込む(ステップS48)。

【0100】

比較結果が不一致を示す場合、制御部561は、不一致となったアドレス及び入力データを結果収集部54に通知することにより、結果収集部54の結果格納部550のメモリ553に格納し、また、結果収集部54に、結果格納部550で管理されるエラーフラグを1に設定させる(ステップS49)。

【0101】

エラーフラグが「1」を示す場合、機能に問題があると判定されたことを示し、「0」を示す場合、機能に問題はないと判定されたことを示す。エラーフラグ「1」の設定を受信すると、結果収集部54は、エミュレーション結果を結果格納部550のメモリ553に格納し、メモリ553内のエラーフラグに「1」を設定して、エミュレーションを停止する。エミュレーションを停止するかどうかは選択することが出来る。

【0102】

一方、エミュレーションを停止せず、機能に問題ない場合、上述したステップS46からS49を繰り返す。

【0103】

以下に、性能測定処理及び機能検証処理による処理パターンCに係る第5及び第6実施例について説明する。第5及び第6実施例において、各回路モデルの構成は、第1から第4実施例で説明した通りである。また、第1から第4実施例より、性能測定処理及び機能検証処理による処理パターンCにおいても、シミュレータ(WS100)で実施することも可能であるし、エミュレータ200を用いて実施することも可能である。

【0104】

性能測定処理と機能検証処理との同時実施では、図6に示す第1実施例と図8に示す第3実施例における機能構成を含み、即ち、検証対象LSI90mと図4に示す測定用付加回路51全体とをWS100で実現する構成A、又は、図7に示す第2実施例と図9に示す第4実施例における機能構成を含み、即ち、検証対象LSI90mと図4に示す測定用付加回路51全体とをエミュレータ200で実現する構成B、のいずれかである。

【0105】

以下に、上記構成A又は構成Bを問わず、性能測定処理と機能検証処理との組み合わせを実現する基本構成50C―1と、更に、現状の性能で性能要件を満たす条件を探索する構成50C―2とを、夫々、第5実施例及び第6実施例として説明する。

【0106】

第5及び第6実施例に共通して、性能に問題があった場合は機能検証部56を停止し、機能に問題があった場合は性能測定部52を停止することが可能である。また、性能又は機能に問題があった場合、結果収集部54を介してその状態をCPU91mに通知することができ、WS100によるシミュレーション又はエミュレータ200によるエミュレーションの実行を停止することが出来る。

【0107】

現状の性能が性能要件を満たすための条件を探索する構成50C―2に係る第6実施例では、クロック周波数を徐々に下げ、性能要件を満たす周波数を探索することができる。また、性能に問題があった場合、機能を選択し、性能要件を満たす機能の組み合わせを探索することができる。更に、性能要件を満たすバス占有率を探索することができる。

【0108】

先ず、第5実施例について図10で説明する。図10は、性能測定処理及び機能検証処理を実施する第5実施例を説明するための図である。図10中、回路モデルの構成は、図6及び図8で例示される通りであるので、協調検証部50c−1では処理構成を示して、性能測定処理と機能検証処理との組み合わせに係る処理手順で第5実施例を説明する。

【0109】

図10において、試験プログラム5が検証対象LSI90mのメモリ93mにロードされると(ステップS71)、検証対象LSI90mのCPU91mによって試験処理98pが開始される(ステップS72)。

【0110】

試験処理98pの開始によって、性能測定部52が起動され(ステップS73)、機能検証部56が起動される(ステップS74)。性能測定部52及び機能検証部56の起動する順は問わない。そして、オーディオ処理などの処理A及びグラフィック処理などの処理Bに係る検証対象処理が開始される。検証対象処理に関して、リアルタイムに測定用付加回路51によって、性能測定及び機能検証が行なわれる。

【0111】

上述したステップS73の性能測定部52の起動によって、図6のステップS14、S15、及びS16、又は、図7のステップS25、S26、及びS27が行われ、性能測定処理52pが開始される。性能測定処理52pでは、サイクル毎にカウントアップされるカウンタA534の値と、規定値レジスタA533の規定値とを比較する(ステップS731)。その比較結果がカウンタA534の値が規定値レジスタA533の規定値を超えることを示す場合(NG)、エラーフラグ「1」の設定が結果収集部54に通知される。エラーフラグ「1」の設定を受けた結果収集部54は、シミュレーション又はエミュレーションを停止する(ステップS76−2)。シミュレーション又はエミュレーションを停止するかどうかは選択することが出来る。

【0112】

一方、その比較結果がカウンタA534の値が規定値レジスタA533の規定値以下であることを示す場合(OK)、処理が終了したか否かが判断される(ステップS735)。処理が終了していない場合(NO)、性能測定処理52pは、ステップS731へ戻り、次のサイクルで上述した同様の比較処理を行う。一方、処理終了である場合(YES)、処理が終了したことが結果収集部54に通知される。

【0113】

上述したステップS74の機能検証部56の起動によって、図8のステップS35又は図9のステップS46が行われ、機能検証処理56pが開始される。機能検証処理56pでは、入力データと期待値とを比較する(ステップS741)。その比較結果が不一致を示す場合(NG)、図8のステップS37又は図9のステップS48が実行され、エラーフラグ「1」の設定が結果収集部54に通知される。エラーフラグ「1」の設定を受けた結果収集部54は、シミュレーション又はエミュレーションを停止する(ステップS76−2)。シミュレーション又はエミュレーションを停止するかどうかは選択することが出来る。

【0114】

一方、その比較結果が一致を示す場合(OK)、処理が終了したか否かが判断される(ステップS735)。処理が終了していない場合(NO)、機能検証処理56pは、ステップS743へ戻り、次の入力データで上述した同様の比較処理を行う。一方、処理終了である場合(YES)、処理が終了したことが結果収集部54に通知される。

【0115】

結果収集部54は、性能測定部52及び機能検証部56からの通知によって収集された比較結果を試験処理98pに通知する(試験処理98pにおける結果収集:ステップS76)。

【0116】

試験処理98pにおいて、測定用付加回路51の結果収集部54から収集した比較結果を参照して、性能測定部52及び機能検証部56による比較結果の判定を行う(比較判定:ステップS77)。比較結果の判定によって、性能又は/及び機能に問題があると判定した場合(NG)、性能又は/及び機能に問題があることを示す試験結果を表示ユニット13に表示させて(ステップS78−1)、この試験処理98pは終了する(ステップS79)。

【0117】

一方、性能又は/及び機能に問題がないと判定した場合(OK)、性能又は/及び機能に問題がないことを示す試験結果を表示ユニット13に表示させて(ステップS78−2)、この試験処理98pは終了する(ステップS79)。

【0118】

次に、現状の性能が性能要件を満たすための条件を探索する構成50C―2に係る第6実施例について、図11で説明する。図11は、性能測定処理及び機能検証処理を実施する第6実施例を説明するための図である。図11中、図10と同一ステップには同一符号を付し、その説明を省略する。また、回路モデルの構成は、図7及び図9で例示される通りであるので、協調検証部50c−2では処理構成を示して、性能測定処理と機能検証処理との組み合わせに係る処理手順で第6実施例を説明する。

【0119】

第6実施例において、試験処理98pでは、現状の性能が性能要件を満たすための条件を探索するために、異なる性能要件に対応した複数のパターンを用いて試験が行われる。各パターンは、ステップS73による性能測定部52の起動及びステップS74による機能検証部56の起動によって開始される。

【0120】

そして、パターン毎に、図10で説明したようにステップS77までの処理が実行され、ステップS78−1又はS78−2による試験結果の表示ユニット13への表示後に、全パターンを実施したか否かが判断される(ステップS78−3)。未だ実施していないパターンがある場合(NO)、次のパターンを実施するためにステップS73へと戻り、上述同様の処理を繰り返す。

【0121】

一方、全パターンを実施した場合(YES)、この試験処理98pは終了する(ステップS79)。

【0122】

現状の性能が性能要件を満たすための条件の探索では、規定値生成部2によって試験プログラム98p中に複数の規定値が準備される。シミュレータ(WS100)による、又は、エミュレータ200を用いた協調検証の実行中に、試験処理98pが規定値を自動で変更することによって、性能が性能要件を満たすための条件を探索する。条件として周波数があり、異なる周波数毎に、規定値算出方法の第1例によって性能要件をサイクル数で示す規定値が算出される。

【0123】

性能要件を満たす周波数を探索する第1の探索例について図12で説明する。図12は、周波数を探索する第1の探索例を説明するための図である。図12において、1回目の周波数「100MHz」及び性能要件「33ms」に基づく規定値1による判定1が、規定値1内で検証対象処理が終了しなかったことを示す場合(S733でNG)、LSIの開発者は、条件となる周波数又は性能要件について再考することとなる。

【0124】

一方、規定値1による判定1が、規定値1内で検証対象処理が終了したことを示す場合(S735でOK)、規定値2のパターンで判定される。2回目の周波数「90MHz」及び性能要件「33ms」に基づく規定値2による判定2が、規定値2内で検証対象処理が終了しなかったことを示す場合(S733でNG)、LSIの開発者は、1回目の規定値1による条件が限界であると判断する。

【0125】

一方、規定値2による判定2が、規定値2内で検証対象処理が終了したことを示す場合(S735でOK)、規定値3のパターンで判定される。このような処理が各規定値1、2、・・・毎に繰り返されることによって、性能要件を満たす条件が探索される。

【0126】

規定値1は、図2に示す規定値算出方法の第1例に従って算出されたサイクル数「3,300,000」を示す。規定値2も同様に算出されたサイクル数「2,970,000」を示す。

【0127】

図13は、図12の第1の探索例での処理概要を説明するためのフローチャート図である。図13において、試験プログラム5によって行われる試験処理98pにおいて、プログラム構成DB71からパターンが選択される(ステップS81)。

【0128】

選択されたパターンのプログラムがCPU91mによって実行される(ステップS82)。実行開始時に、パターンに対応する規定値が性能測定部52に設定される。具体的には、性能測定部52のレジスタ部530内の規定値レジスタA533(図6又は図7)に設定される。

【0129】

そして、性能測定部52による規定値との比較結果が結果収集部54の結果格納部550に書き込まれる(ステップS83)。

【0130】

その後、試験処理98pにおいて、全パターンを実施したか否かが判断される(ステップS84)。全パターンの実施を終了していない場合、ステップS81へ戻り、試験処理98pにおいて、次のパターンが選択され、上述した同様の処理が繰り返される。一方、全パターンを実施した場合、試験処理98pは終了する。

【0131】

プログラム構成DB71は、試験プログラム5に含まれている探索用のパターンに対応したプログラムを含んでいる。この例では、探索用にパターン1、2、3、・・・が含まれていることを示している。パターンの選択は厳しい条件から実施されるようにし、比較結果がNGの場合、即時にシミュレーションを終了させる。パターン毎の比較判定は、表示ユニット13に表示されることにより、LSIの開発者は、周波数の探索結果を知ることができる。

【0132】

パターン1が選択されると、性能測定処理52pにおいて、周波数「100MHz」及び性能要件「33ms」に基づいて算出された規定値1との比較が行われる。次に、パターン2が選択されると、性能測定処理52pにおいて、周波数「90MHz」及び性能要件「33ms」に基づいて算出された規定値2との比較が行われる。更に、パターン3が選択されると、性能測定処理52pにおいて、周波数「80MHz」及び性能要件「33ms」に基づいて算出された規定値3との比較が行われる。

【0133】

次に、図11に示す構成50C―2において、試験プログラム5に、複数の機能の組み合せを準備し、組み合せ毎に性能測定処理52pを行い、性能要件を満たす組み合わせを探索する第2の探索例について説明する。

【0134】

図14は、機能の組み合せを探索する第2の探索例を説明するための図である。図14に示す第2の探索例では、試験プログラム5の中に、機能の組み合せ「A1、A2、及びA3」、「A1及びA2」、及び「A1及びA3」が準備され、シミュレーション(又はエミュレーション)の実行中に、機能の組み合せを選択して、性能要件を満たす組み合せを探索する。

【0135】

機能の組み合せの例として、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大が示されている。

【0136】

性能要件「33ms」の制約において、機能A1、機能A2、及び機能A3の組み合せを1回目で行う。その結果、機能検証ではOKであったが、性能測定では機能A1からA3までを終了するのにかかる所要時間が40msとなり、性能要件の処理時間33msを超えてNGであった。

【0137】

同一の制約において、機能A1及び機能A2の組み合せを2回目で行う。1回目と異なり、機能A3は実行されない。その結果、機能検証がOKであると共に、性能測定では所要時間が33msであり性能要件の処理時間33msを超えることなくOKの判定となった。この例の場合では、1回目の機能の組み合せでは性能要件を満たすことができないが、2回目の機能の組み合わせでは性能要件を満たすことが判る。このように、どの組み合せであれば性能要件を満たすのかを探索することができる。

【0138】

図15は、図14の第2の探索例での処理概要を説明するためのフローチャート図である。図15において、試験プログラム5によって行われる試験処理98pにおいて、プログラム構成DB72からパターンが選択される(ステップS91)。

【0139】

選択されたパターンのプログラムがCPU91mによって実行される(ステップS92)。実行開始時に、規定値が性能測定部52に設定される。この機能の組み合せによる第2の探索例では、性能測定部52に設定される規定値は、周波数に変化はないので、どのパターンが選択されても一律である。

【0140】

そして、性能測定部52による規定値との比較結果が結果収集部54の結果格納部550に書き込まれる(ステップS93)。

【0141】

その後、試験処理98pにおいて、全パターンを実施したか否かが判断される(ステップS94)。全パターンの実施を終了していない場合、ステップS91へ戻り、試験処理98pにおいて、次のパターンが選択され、上述した同様の処理が繰り返される。一方、全パターンを実施した場合、試験処理98pは終了する。

【0142】

プログラム構成DB72は、試験プログラム5に含まれている探索用のパターンに対応したプログラムを含んでいる。この例では、探索用にパターン1(シリアル)、パターン2(シリアル)、パターン3(パラレル)、・・・が含まれていることを示している。

【0143】

パターン1(シリアル)は、機能A1、機能A2、そして機能A3の順に行うパターンである。パターン2(シリアル)は、機能A1、そして機能A2の順に行うパターンである。パターン3(パラレル)は、機能A1及び機能A3を並列で行い、そして機能A2を行うパターンである。

【0144】

選択されたパターンのプログラムが終了するまでに要した所要時間と規定値との比較が行われ、その比較結果が結果収集部54を介して試験処理98pに通知される。

【0145】

第3の探索例として、機能の組み合せは同一であるが、入力画像サイズを変更して、性能要件を満たす条件(入力画像サイズ)を探索する場合について説明する。図16は、同一の機能の組み合せにおいて性能要件を満たす条件を探索する第3の探索例を説明するための図である。

【0146】

図16に示す第3の探索例では、試験プログラム5の中に、複数の入力画像サイズの入力画像データが準備され、シミュレーション(又はエミュレーション)の実行中に、入力画像サイズを変更して、組み合せ機能が性能要件を満たす条件「入力画像サイズ」を探索する。

【0147】

機能の組み合せの例として、機能A1、A2、及びA3が示され、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大である。

【0148】

性能要件「33ms」の制約において、機能A1、機能A2、及び機能A3の組み合せで、入力画像サイズ「1024×768」の入力画像データを用いて1回目を行う。その結果、機能検証ではOKであったが、性能測定では機能A1からA3までを終了するのにかかる所要時間が40msとなり、性能要件の処理時間33msを超えてNGであった。

【0149】

同一の性能要件及び同一の機能の組み合せにおいて、入力画像サイズを「800×600」に変更して、2回目を行う。その結果、機能検証がOKであると共に、性能測定では所要時間が33msであり性能要件の処理時間33msを超えることなくOKの判定となった。この例の場合では、1回目の入力画像サイズ「1024×768」では性能要件を満たすことができないが、2回目の入力画像サイズ「800×600」では性能要件を満たすことが判る。このように、機能の組み合せにおいて、どの条件であれば性能要件を満たすのかを探索することができる。

【0150】

次に、性能要件として、所要時間の代わりに、バス占有率を指定した場合について説明する。性能要件であるバス占有率は、図3の規定値算出方法の第2例で示されるように、規定値生成部2によって、計数可能な規定値で示される。図17は、バス占有率に基づく性能測定について説明するための図である。図17において、CPU96mと、Codec97mと、MEMC98mとを有する検証対象LSI95mと、MEMC98mでコントロールされるSDRAM99mとが試験される各回路モデルである場合を示す。各回路モデルに対して検証対象処理量を監視するためにバスモニタ6a、6b、6c、及び6dを組み込んで、所定時間毎にバス占有率を取得する。

【0151】

このようなバスモニタ6a、6b、6c、及び6dを組み込むことで、検証対象LSI90m内のバス占有率17aと、検証対象LSI90m外のバス占有率17bとを夫々検証することが可能となる。例えば、バス占有率「50%」を規定値とした場合、規定値を超える期間17tが判るため、検証対象LSIの性能に係る設計の見直しを効果的に行うことができる。

【0152】

性能要件をバス占有率「50%」以下とした場合の、性能測定処理及び機能検証処理を実施する第5実施例の変形例について図18で説明する。図18は、第5実施例の変形例を説明するための図である。

【0153】

図18に示す変形例では、試験プログラム5によって、機能の組み合せ「A1、A2、及びA3」が実行され、バス占有率「50%」以下が指定された性能要件に従って、機能検証処理56p及び性能測定処理52pが実行された場合を示している。

【0154】

機能の組み合せの例として、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大が示されている。

【0155】

この例では、バス占有率50%以下の制約において、機能検証ではOKであったが、性能測定ではバス占有率が最大で「60%」となる期間があり、性能要件のバス占有率50%を超えてNGであった。性能測定では機能A1からA3までを実行中に性能要件のバス占有率50%を超えた時刻が存在したことが示されている。

【0156】

所定時間毎のバス占有率を結果収集部54で収集し蓄積するようにし、プログラム実行後の試験結果を表示ユニット13に表示させることで、時刻110msでバス占有率の最大値「60%」を示した結果となったことが判る。このように、どの期間で性能要件を満たすことができなかったのかを知ることができる。

【0157】

次に、同一の機能の組み合せで、性能要件のバス占有率50%以下を満たす条件「入力画像サイズ」を探索する第6実施例の変形例について説明する。図19は、第6実施例の変形例を説明するための図である。

【0158】

図19に示す第6実施例の変形例では、試験プログラム5の中に、複数の入力画像サイズの入力画像データが準備され、シミュレーション(又はエミュレーション)の実行中に、入力画像サイズを変更して、組み合せ機能が性能要件を満たす条件「入力画像サイズ」を探索する。図16に示す第3の探索例との違いは、性能要件として「バス占有率50%」以下が指定される。

【0159】

機能の組み合せの例として、機能A1、A2、及びA3が示され、機能A1は画像の縮小、機能A2は画像の一部を白黒化、そして、機能A3は画像の拡大である。

【0160】

バス占有率50%以下の制約において、機能A1、機能A2、及び機能A3の組み合せで、入力画像サイズ「1024×768」の入力画像データを用いて1回目を行う。その結果、機能検証ではOKであったが、性能測定では機能A1からA3を終了するまでの所定時間毎のバス占有率において「50%」を超える期間が存在したためNGであった。

【0161】

同一の性能要件及び同一の機能の組み合せにおいて、入力画像サイズを「800×600」に変更して、2回目を行う。その結果、機能検証がOKであると共に、性能測定では所定時間毎のバス占有率において「50%」以下であったためOKの判定となった。この例の場合では、1回目の入力画像サイズ「1024×768」では性能要件を満たすことができないが、2回目の入力画像サイズ「800×600」では性能要件を満たすことが判る。このように、機能の組み合せにおいて、どの条件であれば性能要件を満たすのか、を探索することができる。

【0162】

また、どの期間で性能要件を満たさないのかを知ることができ、機能を組み合わせた場合に性能が落ちる箇所を検証することができる。この1回目及び2回目の結果例を参照することにより、機能A1−>機能A2−>機能A3のシリアルな処理において、入力画像サイズ「1024×768」の場合に、機能A2で性能要件を満たさない期間が存在する等の検証が容易となる。

【0163】

図20は、図19の第6実施例の変形例での処理概要を説明するためのフローチャート図である。図20において、試験プログラム5によって行われる試験処理98pにおいて、入力画像サイズDB73からパターンが選択される(ステップS101)。

【0164】

所定プログラムがCPU91mによって実行される(ステップS102)。実行開始時に、規定値が性能測定部52に設定される。この変形例では、性能測定部52に設定される規定値は、パターンの選択に影響されないため、どのパターンが選択されてもバス占有率50%以下で一律である。

【0165】

そして、性能測定部52による規定値との比較結果が結果収集部54の結果格納部550に書き込まれる(ステップS103)。

【0166】

その後、試験処理98pにおいて、全パターンを実施したか否かが判断される(ステップS104)。全パターンの実施を終了していない場合、ステップS101へ戻り、試験処理98pにおいて、次のパターンが選択され、上述した同様の処理が繰り返される。一方、全パターンを実施した場合、試験処理98pは終了する。

【0167】

入力画像サイズDB73は、性能要件を満たす条件の探索用のパターンを含んでいる。入力画像サイズDB73によって、パターン毎に、異なる入力画像サイズの入力画像データが管理される。この例では、探索される条件として、入力画像サイズ「1024×768」のパターン1、入力画像サイズ「800×600」のパターン2、・・・が含まれていることを示している。

【0168】

次に、バス占有率を性能要件とした図11に示す第6実施例の構成50C―2による性能測定結果の種々の使用例について説明する。第6実施例の構成50C―2を用いて、車両等に搭載されるようなナビゲーションと、映像再生と、音楽再生とが可能な種々のマルチメディア対応のLSIを検証する場合にについて説明する。

【0169】

図21は、マルチメディア対応LSIの回路モデル構成の例を示す図である。図21には、検証対象となる回路モデルが例示されている。種々のマルチメディア対応のLSI300mは、CPU301mと、DMAC302mと、MEMC303mと、画像処理回路305mと、ディスプレイコントローラ306mと、CD/BD/DVD I/F307mと、HDD I/F308mと、オーディオI/F309mとを有し、バス330mを介して互いに接続される。

【0170】

また、MEMC303mには、SDRAM313mが接続される。ディスプレイコントローラ306mには、ディスプレイ315m及び316mが接続される。CD/BD/DVD I/F307mには、CD/BD/DVD317mが接続される。HDD I/F308mには、HDD318が接続される。オーディオI/F309mには、スピーカー319mが接続される。このような検証対象となる回路モデルにおいて、検証対象処理量を監視するためにバスモニタ9aから9kを組み込んで、所定時間毎にバス占有率を取得する。

【0171】

図22は、図21に示すマルチメディア対応LSIの性能限界の探索例を示す図である。図22では、性能要件をバス占有率50%以下とした場合の性能測定により性能限界を探索する例を示している。1回目のパターンAでは、ナビゲーション、DVD映像再生、再生を含むCDリッピングの3つの機能の組み合わせが行われる。性能測定処理52pにより、全てのバスモニタの総和結果22aを得る。このような総和結果22aから、性能要件のバス占有率50%以下を超える期間が60msから90msと、170msとに存在することが示され、3つの機能を同時に動作させることができないことが判明する。

【0172】

2回目のパターンBでは、ナビゲーション、DVD映像再生、HDD再生のパターンAとは異なる3つの機能の組み合わせが行われる。この機能の組み合せにおいて、HDD再生は、CDリッピングしたデータを予めHDD318mに格納しておき、HDD318mから音楽を再生する。性能測定処理52pにより、全てのバスモニタの総和結果22bを得る。このような総和結果22bから、HDD318mから音楽を再生するようにした機能の組み合せでは、性能要件のバス占有率50%以下を満たすことができ、性能に問題ないことが判明する。

【0173】

例えば、図23に例示されるように、パターンAにおけるCPU301mとMEMC303mを介したSDRAM313mとの間、及び、MEMC303mを介したSDRAM313mとHDD318mとの音楽再生に係る検証対象処理が、パターンBでは削減されることにより、性能要件のバス占有率50%以下を満たすことができたと考えられる。

【0174】

図24は、バスモニタの結果表示のためのフローチャート図である。図24において、シミュレーションが開始されると(ステップS121)、所定プログラムを実行する(ステップS122)。性能測定部52はバスモニタによって測定した測定データ24aを所定時間毎に結果収集部54へ通知して、結果格納部550のメモリ553に書き込む(ステップS123)。

【0175】

シミュレーションが終了すると(ステップS124)、結果格納部550のメモリ553に書き込まれたデータ24aを加工してcsvファイル24bを得る(ステップS125)。そして、csvファイル24bを用いて作成した測定結果を示すグラフ24cを表示ユニット13に表示させる(ステップS126)。

【0176】

測定データ24aは、結果格納部550のメモリ553に16進数で記録され、read回数データ25aと、write回数データ25bとを含む。read回数データ25aは、所定時間毎にreadされた回数が示される。同様に、write回数データ25bは、所定時間毎にwriteされた回数が示される。

【0177】

測定データ24aは、10進数で表されたcsvファイル24bに加工される。csvファイル24bには、所定時間間隔を表す番号0、1、2、・・・毎にread回数及びwrite回数とが対応付けられて記録される。csvファイル24bへの加工は、図10に示す試験処理98pにおいて、試験結果表示(NG)を行うS78−1又は試験結果表示(OK)を行うS78−2などで行うようにすればよい。

【0178】

測定結果を示すグラフ24cは、縦軸にSDRAM用のバス占有率を示し、横軸に時間軸を示している。測定結果を示すグラフ24cが表示ユニット13に表示されることによって、開発者は、制約要件のバス占有率50%を満たしていない期間を視覚的に容易に確認することができる。

【0179】

図21の回路モデル構成例では、測定データ24aを、バスモニタ9aから9kの各々に対して記録することで、開発者は、より詳細な解析を行うことができる。各バスモニタ9a〜9kから得られた測定結果をグラフで表示されることにより、ボトルネック解析により性能改善を行うことができる。

【0180】

図25は、ボトルネック解析の例を説明するための図である。図25において、図21の回路モデル構成例において各バスモニタ9a〜9kから得られた全ての測定結果からボトルネック解析を行った結果、SDRAM313mのバス占有率を示すグラフ25cからSDRAM313mのバス占有率に問題があることが判明した例が示されている。

【0181】

グラフ25cを参照すると、SDRAM313mのバス占有率が、性能要件のバス占有率50%を超えている期間が存在することが判る。従って、開発者は、MEMC303mの改善、SDRAM313mの種類の変更、SDRAM313mの周波数を上げる等の性能改善を行う必要があると判断できる。

【0182】

また、バス占有率の測定結果を用いて、LSI300mの性能に余裕があるか否かを判断することも可能である。性能の余裕度を判定することにより、消費電力をより削減したLSI開発を検討することができる。例えば、ナビゲーションの機能と、HDD再生の機能のみが行えればよい場合に、この組み合せによる性能の余裕度を、バス占有率を性能要件として設定することにより検証することができる。

【0183】

図26は、バス占有率を用いた性能余裕度の検証例を説明するための図である。図26に例示されるバス占有率の測定結果を示すグラフ26cを参照することにより、バス占有率が最大となる時間70msにおいても、性能要件のバス占有率50%までその2割以上の余裕があることが判る。

【0184】

従って、設計者は、周波数を下げることにより、消費電力の削減が可能であると判断することができる。その結果、省エネ対応のLSI300mとなるように周波数の変更に関する設計変更を行うことができる。

【0185】

上述したように、本実施例に係る検証システムでは、LSI設計において、シミュレータ又はエミュレータによるソフトウェア及びハードウェアによる協調検証の実施において、LSIの設計が論理的に正しいことを検証するのみならず、全体の処理時間を測定し、なおかつ、プログラムの個々の部分(機能)の処理を測定し、また、プログラムの個々の部分(機能)の処理に関して、性能要件を満たしているか否かを検証することができる。

【0186】

性能要件を満たす、クロック周波数、機能の組み合せ、入力画像サイズなどを探索することができ、設計改善のための情報を得ることが可能となり、LSI製造前に性能改善を行うことが可能となる。

【0187】

本発明は、具体的に開示された実施例に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【0188】

以上の第1から第6実施例等を含む実施形態に関し、更に以下の付記を開示する。

(付記1)

コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、

前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、

前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う

ことを特徴とする協調検証方法。

(付記2)

前記規定値は、前記性能要件で指定される処理時間と、前記設計回路の設計データで示されるクロック周波数とに基づいて算出されたサイクル数であることを特徴とする付記1記載の協調検証方法。

(付記3)

前記設計回路にロードされるプログラムに異なるクロック周波数に基づく複数の規定値を含み、前記協調検証の実施中に、規定値を変更することによって、前記性能要件を満たす該クロック周波数を探索することを特徴とする付記2記載の協調検証方法。

(付記4)

前記規定値は、前記性能要件で指定されるバス占有率と、前記設計回路の設計データで示されるバス動作周波数及び分解能で指定された単位時間あたりのバスサイクル数であることを特徴とする付記1記載の協調検証方法。

(付記5)

前記設計回路にロードされるプログラムに複数の機能の組み合せを含み、前記協調検証の実施中に、該機能の組み合せを変更することによって、前記性能要件を満たす該機能の組み合せを探索することを特徴とする付記1記載の協調検証方法。

(付記6)

前記設計回路にロードされるプログラムに一の機能の組み合せと複数の入力画像サイズとを含み、前記協調検証の実施中に、該入力画像サイズを変更することによって、前記性能要件を満たす該入力画像サイズを探索することを特徴とする付記1記載の協調検証方法。

(付記7)

前記機能の組み合せは、シリアル又はパラレルで実行する組み合せを含むことを特徴とする付記5又は6記載の協調検証方法。

(付記8)

所定時間毎に、前記設計回路におけるバスモニタによる該設計回路のメモリへのread回数及びwrite回数とを結果格納部に格納し、

16進数で示される前記read回数及びwrite回数を10進数で示すデータファイルに加工し、

時系列にバス占有状態を表すグラフ図を表示ユニットに表示させる

ことを特徴とする付記1又は4記載の協調検証方法。

(付記9)

設計回路のソフトウェア及びハードウェアによる協調検証を行なう協調検証装置であって、

性能測定部と、結果収集部とを少なくとも有する測定用付加回路を有し、

性能測定部は、

前記設計回路の性能要件に基づく計数可能な規定値が設定される規定値レジスタと、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントするカウンタレジスタと、

前記カウンタレジスタの値と前記規定値レジスタに設定された前記規定値とを比較する性能比較部とを有し、

前記結果収集部は、前記性能比較部による結果を格納する結果格納部を有する

ことを特徴とする協調検証装置。

(付記10)

前記測定用付加回路は、更に、機能検証部を有し、

前記機能検証部は、

前記設計回路によって処理されたデータを入力する入力部と、

前記入力部が入力したデータと期待値データとを比較する機能比較部とを有し、

前記結果収集部は、前記結果格納部に前記機能比較部による結果を格納することを特徴とする付記9記載の協調検証装置。

(付記11)

前記結果収集部は、前記性能測定部又は前記機能検証部にエラーを検出した場合、前記協調検証を停止させることを特徴とする付記9又は10記載の協調検証装置。

(付記12)

前記測定付加回路は、ハードウェア記述言語で記述された回路であることを特徴とする付記9乃至11記載の協調検証装置。

(付記13)

前記協調検証装置は、シミュレータ又はエミュレータであることを特徴とする付記9乃至12記載の協調検証装置。

(付記14)

前記設計回路のソフトウェア及びハードウェアによる協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、

前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う

処理をコンピュータに実行させることを特徴とするプログラム。

【符号の説明】

【0189】

1 性能要件データ

2 規定値生成部

2a 書込処理挿入部

3 プログラム

4 変換部

5 試験プログラム

6 設計データ(検証対象LSI)

7 テストベンチ

8 コンパイラ

8a 規定値算出データ

8b 規定値算出データ

9 コンパイルDB

11 CPU

12 メモリユニット

13 表示ユニット

14 出力ユニット

15 入力ユニット

16 通信ユニット

17 記憶装置

18 ドライバ

19 記憶媒体

39 規定値設定プログラム

50 協調検証部

50a−1、50b−1 協調検証部(シミュレータ)

50a−2、50b−2 協調検証部(エミュレータ)

50c−1、50c−2 協調検証部(シミュレータ又はエミュレータ)

51 測定用付加回路

52 性能測定部

54 結果収集部

56 機能検証部

58 期待値データ

90m 検証対象LSI

91m CPU

93m メモリ

521 制御部

529 性能比較部

530 レジスタ部

531 開始レジスタA

532 終了レジスタA

533 規定値レジスタA

534 カウンタA

541 制御部

550 結果格納部

553 メモリ

560 入力部

561 制御部

562 期待値生成部

563 期待値格納メモリ

564 期待値比較部

570 レジスタ部

571 期待値生成用データレジスタB

572 比較モードレジスタB

573 比較開始レジスタB

574 期待値比較エラーレジスタB

1000 検証システム

【特許請求の範囲】

【請求項1】

コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、

前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、

前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う

ことを特徴とする協調検証方法。

【請求項2】

前記規定値は、前記性能要件で指定される処理時間と、前記設計回路の設計データで示されるクロック周波数とに基づいて算出されたサイクル数であることを特徴とする請求項1記載の協調検証方法。

【請求項3】

前記設計回路にロードされるプログラムに異なるクロック周波数に基づく複数の規定値を含み、前記協調検証の実施中に、規定値を変更することによって、前記性能要件を満たす該クロック周波数を探索することを特徴とする請求項2記載の協調検証方法。

【請求項4】

前記規定値は、前記性能要件で指定されるバス占有率と、前記設計回路の設計データで示されるバス動作周波数及び分解能で指定された単位時間あたりのバスサイクル数であることを特徴とする請求項1記載の協調検証方法。

【請求項5】

設計回路のソフトウェア及びハードウェアによる協調検証を行なう協調検証装置であって、

性能測定部と、結果収集部とを少なくとも有する測定用付加回路を有し、

性能測定部は、

前記設計回路の性能要件に基づく計数可能な規定値が設定される規定値レジスタと、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントするカウンタレジスタと、

前記カウンタレジスタの値と前記規定値レジスタに設定された前記規定値とを比較する性能比較部とを有し、

前記結果収集部は、前記性能比較部による結果を格納する結果格納部を有する

ことを特徴とする協調検証装置。

【請求項1】

コンピュータによって実行される設計回路のソフトウェア及びハードウェアによる協調検証方法であって、

前記設計回路の協調検証の開始時に性能要件に基づく計数可能な規定値を規定値レジスタに設定し、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントし、

前記カウントしたカウント値と前記規定値レジスタに設定された前記規定値とを比較することによって性能測定を行う

ことを特徴とする協調検証方法。

【請求項2】

前記規定値は、前記性能要件で指定される処理時間と、前記設計回路の設計データで示されるクロック周波数とに基づいて算出されたサイクル数であることを特徴とする請求項1記載の協調検証方法。

【請求項3】

前記設計回路にロードされるプログラムに異なるクロック周波数に基づく複数の規定値を含み、前記協調検証の実施中に、規定値を変更することによって、前記性能要件を満たす該クロック周波数を探索することを特徴とする請求項2記載の協調検証方法。

【請求項4】

前記規定値は、前記性能要件で指定されるバス占有率と、前記設計回路の設計データで示されるバス動作周波数及び分解能で指定された単位時間あたりのバスサイクル数であることを特徴とする請求項1記載の協調検証方法。

【請求項5】

設計回路のソフトウェア及びハードウェアによる協調検証を行なう協調検証装置であって、

性能測定部と、結果収集部とを少なくとも有する測定用付加回路を有し、

性能測定部は、

前記設計回路の性能要件に基づく計数可能な規定値が設定される規定値レジスタと、

前記協調検証の実施中、前記性能要件に係る前記設計回路の動作をカウントするカウンタレジスタと、

前記カウンタレジスタの値と前記規定値レジスタに設定された前記規定値とを比較する性能比較部とを有し、

前記結果収集部は、前記性能比較部による結果を格納する結果格納部を有する

ことを特徴とする協調検証装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図17】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図14】

【図16】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図17】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図14】

【図16】

【図18】

【図19】

【公開番号】特開2013−69174(P2013−69174A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−208182(P2011−208182)

【出願日】平成23年9月22日(2011.9.22)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月22日(2011.9.22)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]