印刷可能な半導体構造、並びに関連する製造方法及び組立方法

【課題】選択された物理的寸法、形状、組成、及び、空間的配置を有する高品質印刷可能半導体素子の製造、転写、組み立てのための高歩留りの経路を与える。

【解決手段】大面積基板及び/又はフレキシブル基板を含む基板上へのミクロサイズ及び/又はナノサイズの半導体構造の配列の高精度の位置合わせ転写及び集積を行なう。また、バルクシリコンウエハ等の低コストバルク材料から印刷可能半導体素子を形成する方法、及び、広範囲の機能的な半導体デバイスを形成するための多目的で商業的に魅力的な印刷ベースの製造ブラットフォームを可能にするスマート材料処理を行う。

【解決手段】大面積基板及び/又はフレキシブル基板を含む基板上へのミクロサイズ及び/又はナノサイズの半導体構造の配列の高精度の位置合わせ転写及び集積を行なう。また、バルクシリコンウエハ等の低コストバルク材料から印刷可能半導体素子を形成する方法、及び、広範囲の機能的な半導体デバイスを形成するための多目的で商業的に魅力的な印刷ベースの製造ブラットフォームを可能にするスマート材料処理を行う。

【発明の詳細な説明】

【関連出願の相互参照】

【0001】

[001]本出願は、2005年6月2日に出願された米国特許出願11/145,542号、2005年6月2日に出願された米国特許出願11/145,574号、及び、2005年6月2日に出願された国際PCT出願PCT/US05/19354号の利益を主張するものであり、これらの出願の全てを、その全体を参照することによって本明細書の開示内容と矛盾しない範囲で援用するものである。

【発明の背景】

【0002】

[002]1994年における印刷された全ての高分子トランジスタの最初のデモンストレーション以来、プラスチック基板上にフレキシブル集積電子デバイスを備える可能性に満ちた新たな種類の電子システムに多大な興味が向けられてきた[Garnier,F.,Hajlaoui,R.,Yassar,A.Srivastava,P.,Science,第265刊、1684−1686頁]。最近では、かなりの研究が、フレキシブルプラスチック電子デバイスにおける導体素子、誘電体素子、半導体素子のための新たな溶解処理可能な材料の開発へと向けられてきている。しかしながら、フレキシブルエレクトロニクス分野における進歩は、新たな溶解処理可能な材料の開発によってのみならず、新たなデバイス部品の幾何学的配置、効率的なデバイス及びデバイス部品処理方法、並びに、プラスチック基板に適用できる高分解能パターニング技術によっても促進されるものである。そのような材料、デバイス構成、及び製造方法は、急速に出現する新たな種類のフレキシブル集積電子デバイス、システム、及び回路に欠くことができない役割を果たすことが期待されている。

【0003】

[003]フレキシブルエレクトロニクスの分野における関心は、主に、この技術によって与えられる幾つかの重要な利点に起因している。第1に、プラスチック基板材料の機械的な耐久性は、機械的な応力によって引き起こされる損傷及び/又は電子的性能劣化を受け難い電子デバイスをもたらす。第2に、これらの基板材料の固有の可撓性により、これらの基板材料を、脆弱な従来のシリコン系電子デバイスでは不可能な多数の有用なデバイス構造を与える多くの形状へと統合することができる。例えば、屈曲可能なフレキシブルエレクトロニクスデバイスは、従来のシリコンベースの技術では容易に達成されない電子ペーパー、装着型コンピュータ、及び、大面積高分解能ディスプレイといった新たなデバイスの製造を可能にすると期待されている。最後に、溶解処理可能な部品材料とプラスチック基板とを組み合わせると、大きな基板面積にわたって低コストで電子デバイスを形成できる連続高速印刷技術による製造が可能となる。

【0004】

[004]しかしながら、良好な電子的性能を示すフレキシブル電子デバイスの設計及び製造は、多くの重大な難問を与える。第1に、従来のシリコン系電子デバイスを形成する十分に開発された方法は、殆どのプラスチック材料に適合しない。例えば、単結晶シリコン又はゲルマニウム半導体等の従来の高品質な無機半導体部品は、一般に、殆どのプラスチック基板の融解温度又は分解温度を大幅に超える温度(>1000℃)で薄膜を成長させることにより処理される。また、殆どの無機半導体は、本来、溶液ベースの処理及び供給を可能にする従来の溶媒に溶けることができない。第2に、多くのアモルファスシリコン、有機又はハイブリッド無機−有機半導体は、プラスチック基板への組み込みに適合しており、比較的低い温度で処理することができるが、これらの材料は、良好な電子的性能を得ることができる集積電子デバイスを提供可能な電子的特性を有していない。例えば、これらの材料から生成される半導体素子を有する薄膜トラジスタは、相補的な単結晶シリコン系デバイスよりも大きさが約3桁規模小さい電界効果移動度を示す。これらの制限の結果、フレキシブル電子デバイスは、現在、非放射性ピクセルを有するアクティブマトリクスフラットパネルディスプレイ用のスイッチング素子や発光ダイオードでの使用等、高い性能を必要としない特定の用途に限られている。

【0005】

[005]最近、プラスチック基板上の集積電子デバイスの更に幅広い範囲のエレクトロニクス用途へと適用性を拡大するべく、当該集積電子デバイスの電子的性能を向上させることにおいて進展が見られている。例えば、プラスチック基板材料における処理に適合し、アモルファスシリコン、有機又はハイブリッド無機−有機半導体素子を有する薄膜トランジスタよりも相当に高いデバイス性能特性を示す幾つかの新規な薄膜トランジスタ(TFT)構造が出現してきている。一つの種類の高性能フレキシブル電子デバイスは、アモルファスシリコン薄膜のパルスレーザアニーリングにより製造される多結晶シリコン薄膜半導体素子に基づいている。この種のフレキシブル電子デバイスは高いデバイス電子性能特性を与えるが、パルスレーザアニーリングの使用は、そのようなデバイスの製造の簡易性及び自由度を制限し、それによって、コストが大幅に増大してしまう。他の有望な新たな種類の高性能フレキシブル電子デバイスは、ナノワイヤ、ナノリボン、ナノ粒子、カーボンナノチューブといった溶解処理可能なナノスケール材料を、多数のマクロ電子デバイス及びマイクロ電子デバイスにおける能動機能素子として使用するデバイスである。

【0006】

[006]別個の単結晶ナノワイヤ又はナノリボンの使用は、高いデバイス性能特性を示すプラスチック基板上の印刷可能電子デバイスをもたらす可能な手段として評価されている。Duan等は、複数の選択方位性単結晶シリコンナノワイヤ又はCdSナノリボンを半導体チャネルとして有する薄膜トランジスタ構成について記載している[Duan,X.,Niu,C.,Sahl,V.,Chen,J.,Parce,J.,Empedocles,S.,Goldman,J.,Nature,第425刊、274−278頁]。この著者は、プラスチック基板上での溶解処理に適合するとされる製造プロセスについて報告しており、この製造プロセスでは、流れ方向付けアライメント(flow−directed alignment)方法を使用して、150ナノメートル以下の厚さを有する単結晶シリコンナノワイヤ又はCdSナノリボンを溶液中に分散して、基板の表面上に組み立てて、薄膜トランジスタにおける半導体素子を形成する。この著者によって提供された光学顕微鏡写真は、開示された製造プロセスが、略平行な方向で、且つ、約500ナノメートル〜約1000ナノメートルだけ離間した単層のナノワイヤ又はナノリボンを形成することを示唆している。この著者は、個々のナノワイヤ又はナノリボンに関して比較的高い固有の電界効果移動度(約119cm2V−1s−1)を報告しているが、全体のデバイス電界効果移動度は、最近、Duan等により報告された固有の電界効果移動度値よりも「大きさが約2桁規模低い」ものであると判断されている[Mitzi,D.B,Kosbar,L.L,Murray,C.E.,Copel,M.Afzali,A.,Nature,第428刊、299〜303頁]。このデバイス電界効果移動度は、従来の単結晶無機薄膜トランジスタのデバイス電界効果移動度よりも数桁規模大きさが低く、恐らくは、Duan等において開示された方法及びデバイス構成を使用して別個のナノワイヤ又はナノリボンをアライメントし、高密度で実装し、電気的に接触させることの

実際の難しさに起因している。

【0007】

[007]また、多結晶無機半導体薄膜に対する前駆物質としてナノ結晶溶液を使用することも、高いデバイス性能特性を示すプラスチック基板上の印刷可能電子デバイスを設ける可能な手段として検討されてきた。Ridley等は、約2ナノメートルの寸法を有する溶液カドミウムセレナイドナノ結晶をプラスチック適合温度で処理して電界効果トランジスタ用の半導体素子を提供する溶解処理製造方法について開示している[Ridley,B.A.,Nivi,B.and Jacobson,J.M.,Science,第286刊、746〜749頁(1999)]。この著者は、セレン化カドミウムのナノ結晶溶液中での低温粒子成長が数百個のナノ結晶を含む単結晶領域を形成する方法について報告している。Ridley等は、有機半導体素子をもった比較可能なデバイスに対して向上した電気的特性を報告しているが、これら技術によって得られるデバイス移動度(約1cm2V−1s−1)は、従来の単結晶無機薄膜トランジスタのデバイス電界効果移動度よりも数桁規模大きさが低い。Ridley等のデバイス構成及び製造方法により達成される電界効果移動度における限界は、恐らくは、個々のナノ粒子間で成される電気的な接触に起因している。特に、ナノ結晶溶液を安定化させ凝集を防止するために有機末端基を使用すると、高いデバイス電界効果移動度をもたらすために必要な隣接ナノ粒子間の良好な電気接触の形成が妨げられることがある。

【0008】

[008]Duan等及びRidley等は、プラスチック基板上に薄膜トランジスタを製造するための方法を提供しているが、説明されたデバイス構成は、電極、半導、体及び/又は誘電体等の機械的に堅牢なデバイス部品を備えるトランジスタを使用している。良好な機械的特性を有するプラスチック基板の選択は、屈曲方向性又は歪曲方向性を成して機能し得る電子デバイスをもたらすことができる。しかしながら、そのような動きは、個々の硬質トランジスタデバイス部品上に機械的な歪みを生み出すことが予期される。この機械的な歪みは、例えばクラッキングにより個々の部品に損傷を引き起こす場合があるとともに、デバイス部品間の電気的な接触を低下させ、或いは妨げる場合もある。

【0009】

[009]何れも2005年6月2日に出願された米国特許11/145,574及び11/145,542は、多目的で低コストな高面積印刷技術によって電子デバイス、光電子デバイス及び他の機能素子アセンブリを製造するための印刷可能半導体素子を使用する高歩留りの製造プラットフォームを開示している。開示された方法及び構成は、大きな基板面積にわたって良好な配置精度、位置合わせ精度、及びパターン忠実度をもたらす乾式転写コンタクト印刷技術及び/又はソリューション印刷技術を使用してミクロサイズ及び/又はナノサイズの半導体構造の転写、組み立て及び/又は集積を行なう。開示された方法は、フレキシブルプラスチック基板を含む種々の有用な基板材料に適合する比較的低温(<約400℃)で独立に行なわれてもよい印刷技術によって、従来の高温処理方法を使用して基板上に形成される高品質半導体材料の集積を可能にする重要な処理上の利点をもたらす。印刷可能半導体材料を使用して形成されるフレキシブルな薄膜トランジスタは、300cm2V−1s−1よりも大きいデバイス電界効果移動度及び103よりも大きいON/OFF比等の良好な電子特性を示す。

【0010】

[010]以上から分かるように、低コストバルク出発材料から高品質印刷可能半導体素子を形成する方法は、大面積のフレキシブルな電子デバイス及び光電子デバイス並びにデバイス配列を形成するための印刷技術の商業的魅力を高める。また、基板上に印刷される半導体素子の物理的寸法、空間的方位、位置合わせにわたって高い制御性を可能にする印刷可能半導体構成及び印刷ベースの組み立て方法も、幅広い範囲の機能デバイスを製造するためのこれら方法の適用可能性を高める。

【発明の概要】

【0011】

[011]本発明は、選択された物理的寸法、形状、組成、及び、空間的配置を有する高品質印刷可能半導体素子の製造、転写、組み立てに関する高歩留りの筋道を与える。本発明の構成及び方法は、大面積基板及び/又はフレキシブル基板を含む基板上へのミクロサイズ及び/又はナノサイズの半導体構造の配列の高精度の位置合わせ転写及び集積を行なう。また、本発明は、バルクシリコンウエハ等の低コストバルク材料から印刷可能半導体素子を形成する方法、及び、広範囲の機能的な半導体デバイスを形成するための多目的で商業的に魅力的な印刷ベースの製造ブラットフォームを可能にするスマート材料の処理方策を提供する。この半導体製造・転写・集積プラットフォームは、幾何学的形状、相対的な空間的配置、及び編成、ドーピングレベル、印刷可能半導体構造の材料純度にわたる非常に高度な制御を含む多くの利点をもたらす。

【0012】

[012]本方法及び構成は、大面積の可撓性の高性能マクロ電子デバイスを含む種々の複雑な集積電子デバイス又は光電子デバイス、若しくはデバイス配列の製造を可能にし、これらデバイス及びデバイス配列を、従来の高温処理方法を使用して製造される単結晶半導体系デバイスに匹敵する性能特性を示すものとする。基板上に又は基板中へ印刷可能半導体素子を組み立て、位置決めし、編成し、転写し、パターニングし、及び/又は、集積する本構成及び関連方法は、一以上の半導体素子を備える略任意の構造体を製造するために使用され得る。しかしながら、これらの方法は、複雑な集積電子デバイス又は光電子デバイス、若しくは、ダイオード、発光ダイオード、太陽電池及びトランジスタ(例えば、薄膜トランジスタ(TFT)、金属半導体電界効果トランジスタ(MESFET)FET及びバイポーラ)の配列といったデバイス配列を製造するのに特に有用である。また、本構成及び関連方法は、NOA及びNAND論理ゲートや相補論理回路等のシステムレベル集積電気回路を製造するのに有用である。この場合、印刷可能半導体素子は、良好な空間的配置で基板上に印刷されるとともに、所望の回路構造を形成するように互いに接続される。

【0013】

[013]一態様では、本発明は、繰り返し処理できるバルクシリコンウエハ出発材料を使用して、高い精度をもって選択される物理的寸法、形状、空間的配置を有する高歩留りの印刷可能半導体素子を形成する処理方法を提供する。本発明のこの態様の一実施形態では、(111)方位を有し且つ外面を有するシリコンウエハが設けられる。商業的に魅力的な実施形態では、ウエハは低コストなバルク(111)シリコンウエハである。(111)シリコンウエハの外面上には複数の凹状形態部が形成され、各凹状形態部は、露出したシリコンウエハの底面及び側面を有する。凹状形態部の側面の少なくとも一部はマスキングされる。この説明では、「マスキングされた」との表現は、エッチングを防止し又は妨げることができ、或いはマスク表面のエッチング速度を減少させることができる耐エッチング性マスク材料等のマスク材料を供給することを指す。凹状形態部の間の領域は、(111)シリコンウエハの<110>方位に沿ってエッチングが起こるようにエッチングされ、それにより、部分的に又は完全にアンダーカットされたシリコン構造を備える一以上の印刷可能半導体素子が製造される。有益な実施形態では、隣接して配置された凹状形態部間の領域が、シリコンウエハの<110>方位に沿ってエッチングすることによってアンダーカットされ、それにより、印刷可能半導体素子が形成される。オプションとして、凹状形態部の位置、形状、及び、空間的配置は、印刷可能半導体素子をウエハに対して接続するブリッジ素子のようなアライメント維持素子を形成するように選択される。

【0014】

[014]一実施形態では、凹状形態部の側面の全てではなく一部がマスキングされ、それにより、側面のマスキングされた領域及びマスキングされない領域が形成される。側面のマスキングされていない領域は、例えば異方性エッチング法によってエッチングされ、それにより、凹状形態部間に位置する(111)シリコンウエハの領域がアンダーカットされる。本発明のこの実施形態では、エッチングは、シリコンウエハの<110>方位に沿って凹状形態部間で生じ、それにより、部分的に又は完全にアンダーカットされたシリコン構造を備える印刷可能半導体素子が製造される。

【0015】

[015]他の実施形態では、凹状形態部の側面が完全にマスキングされ、凹状形態部間の領域は、例えばマスキングされた領域の下側の材料をエッチングすることによって、シリコンウエハの<110>方位に沿ってエッチングが生じるようにエッチングされ、それにより、凹状形態部間に位置する(111)シリコンウエハがアンダーカットされる。この処理は、部分的にあるいは完全にアンダーカットされたシリコン構造を備える印刷可能半導体素子を製造する。幾つかの実施形態では、凹状形態部の床部の下側の材料が、例えば異方性エッチング法によって除去される。オプションとして、凹状形態部の床部が部分的にマスキングされ、それにより、エッチング液のための入口が残される。この場合、入口は、凹状形態部の底面上に位置する。凹状形態部の側面が完全にマスキングされる製造方法により、側面の部分的マスキングを使用する一部の方法よりも正確に印刷可能素子の厚さを規定して選択することができる。

【0016】

[016]オプションとして、本方法は、印刷可能半導体素子の製造前に、凹状形態部の形状、物理的寸法、及び、形態を精緻化するステップを更に含んでいてもよい。ここでの精緻化とは、凹状形態部の側面及び床部のような凹状形態部の表面の材料除去処理のことである。精緻化は、凹状形態部のより滑らかな表面をもたらす処理及び/又はより均一な物理的寸法及び表面形態を有する凹状形態部をもたらす処理を含んでおり、それにより、より滑らかな表面及び外観を有し、並びに/若しくは、より均一な物理的寸法及び形態を有する印刷可能半導体素子が得られる。一実施形態では、幾何学的形状、物理的寸法及び/又は形態は、異方性エッチング技術によって、例えば高温KOH溶液を使用するエッチングによって、精緻化される。凹状形態部の幾何学的形状、物理的寸法、及び形態を精緻化することに関する処理ステップを含む本発明の方法は、マイクロ電気機械システム(MEMS)及びナノ電気機械システム(NEMS)を形成するための製造経路にとって有用である。

【0017】

[017]選択された物理的寸法、位置、相対的な空間的方位を有する複数の凹状形態部を有する(111)ウエハの外面のパターニングは、デバイスシステム中への印刷可能半導体素子の最終的な組み立て及び集積を容易にするよう、高い精度で選択された位置及び空間的方位で設けられる多数(例えば、約1×103〜約1.0×1010)の印刷可能半導体素子の配列を同時に製造するための本方法のこの態様において有用である。本発明の方法は、シリコンウエハの外面の大部分(例えば、約75%−約95%)に対応する印刷可能半導体素子の配列を形成することができる。

【0018】

[018]本発明は、(111)シリコンウエハの<110>方位に沿うエッチングが進行して隣接する凹状形態部間で完了し、それにより、凹状形態部間の(111)シリコンウエハの領域を全体的にアンダーカットし、その結果、印刷可能半導体素子を形成する方法を含む。或いは、本発明は、隣接する凹状形態部間でのシリコンウエハの<110>方位に沿うエッチングが完全になされず、それにより、凹状形態部間の(111)シリコンウエハの領域が部分的にアンダーカットされ、したがって、部分的にアンダーカットされた印刷可能半導体素子が形成される方法を含む。このエッチング処理ステップによって印刷可能半導体素子が完全にアンダーカットされる幾つかの方法では、ウエハの外面上の凹状形態部の空間的配置及び物理的寸法は、製造される印刷可能半導体素子が当該印刷可能半導体素子の一以上の端部でシリコンウエハに対して接続されたまま、場合によっては一体に接続されたままの状態となるように選択される。幾つかの実施形態では、印刷可能半導体素子は、シリコンウエハに対して直接に接続し、他の実施形態では、印刷可能半導体素子は、ブリッジ素子といった一以上のアライメント維持素子によってシリコンウエハに対して接続される。

【0019】

[019](111)方位を有するシリコンウエハを本発明のエッチングシステムと組み合わせて使用すると、印刷可能半導体素子及びオプションとしてのブリッジ素子のようなアライメント維持素子を少なくとも部分的に又は完全にアンダーカットするのに有用である固有のエッチストップが与えられる。幾つかの実施形態では、例えば、シリコンウエハの<110>方位に沿って選択的エッチングを行なう異方性エッチングシステムが選択される。これらの実施形態では、エッチングは、シリコンウエハの<111>方位よりも速い速度でシリコンウエハの<110>方位に沿って進行し、また、幾つかの用途においては、エッチングは、シリコンウエハの<111>方位よりも少なくとも100倍速い速度でシリコンウエハの<110>方位に沿って選択的に進行し、また、幾つかの実施形態では、エッチングは、シリコンウエハの<111>方位よりも少なくとも600倍速い速度でシリコンウエハの<110>方位に沿って進行する。幾つかの処理条件下では、異方性エッチングシステムは、エッチングがシリコンウエハの<111>方位に沿って実質的に進行しないように使用される。この説明では、「エッチングが<111>方位に沿って実質的に進行しない」との表現は、典型的な印刷可能半導体素子製造プロセスの場合の約数パーセント未満のエッチングの程度を指す。このアンダーカット処理ステップにとって有用なエッチングシステムは、滑らかにアンダーカットされた底面、例えば0.5ナノメートル以下の表面粗さをもつアンダーカット底面を有する印刷可能半導体素子を形成する。本方法に有用な異方性エッチング液システムは、室温又は298Kよりも高い温度で、KOH、水酸化アルカリ液、EDP(エチレンジアミンピロカテコール)、TMAH(水酸化テトラメチルアンモニウム)、アミンガレート(没食子酸、エタノールアミン、ピラジン、界面活性剤水溶液)、及びヒドラジンといった塩基性溶液を使用する湿式化学エッチングを含むが、これらに限定されない。

【0020】

[020]凹状形態部の側面をマスキングするための有用な方法としては、一つの金属又は金属の組み合わせといったマスク材料の傾斜型電子ビーム蒸着(angled electron beam deposition)、化学気相堆積、熱酸化、及び、マスク材料の溶液堆積が挙げられる。例示的な方法としては、凹状形態部の側面の部分的な被覆を行なうTi/Auの二金属傾斜型電子ビーム蒸着が挙げられる。傾斜型蒸着中に作られる「陰」は、本実施形態では、印刷可能半導体素子の厚さを少なくとも部分的に規定する。本方法は、凹状形態部の側面を完全にマスキングする処理ステップを含み、或いは凹状形態部の側面の一部だけをマスキングする処理ステップを含み、例えば、側面の選択された部分、領域、面積又は深さをマスキングするプロセスステップを含む。

【0021】

[021]本発明のこの態様の一実施形態では、選択された物理的寸法、方向、及び位置を有する凹状形態部のパターンが外面に対して与えられる。この実施形態では、外面上の凹状形態部は、印刷可能半導体素子及び場合によりブリッジ素子の物理的寸法、形状、位置、及び空間的方向を少なくとも部分的に規定するように選択された物理的寸法(すなわち、長さ、幅及び深さ)、形状、位置、及び、相対的な空間的方向を有する。隣接する凹状形態部の相対的位置(例えば間隔)、形状、空間的方向は、印刷可能半導体素子の形状、幅、又は長さを規定するように選択される。例えば、隣接する凹状形態部間の間隔は、印刷可能半導体素子の幅又は長さを規定し、また、凹状形態部の深さは、印刷可能半導体素子の厚さを少なくとも部分的に決定するように選択されてもよい。幾つかの実施形態では、一以上の均一な物理的寸法、例えば均一な厚さ、幅、又は長さを有する印刷可能半導体素子を形成するために、一以上の略均一(すなわち、約5%の範囲内)な物理的寸法を有する凹状形態部が好ましい。凹状形態部は、技術的に知られた任意の手段によって形成され得るものであり、当該手段には、近接場位相シフトフォトリソグラフィのようなフォトリソグラフィ処理、ソフトリソグラフィ処理、リフトオフ法、乾式化学エッチング、プラズマエッチング、湿式化学エッチング、微細加工、電子ビーム書き込み、及び、反応性イオンエッチングがあるが、これらに限定されない。選択された物理的寸法及び相対的な空間的配置を有する凹状形態部のパターンを形成することができる一つの有用な実施形態では、シリコンウエハの外面上に一以上の凹状形態部を形成するステップは、(i)マスクを与えることによって外面の一以上の領域をマスキングし、それにより、外面のマスキングされた領域とマスキングされない領域とを形成するステップと、(ii)ウエハの外面のマスキングされない領域の少なくとも一部をエッチングするステップ、例えば、異方性ドライエッチングを行い又は等方性ドライエッチングを行なうステップと、を備える。

【0022】

[022]本発明のこの態様の一実施形態では、凹状形態部は、選択された物理的寸法、位置及び相対的な空間的方向を有する複数のチャネル(溝)をウエハの外面に構成する。例えば、第1及び第2のチャネルを含む凹状形態部は、それらが互いに物理的に離間されるようにシリコンウエハ上にパターニングされてもよい。この実施形態の凹状形態部間をエッチングするステップは、シリコンウエハの<110>方向に沿って第1のチャネルから第2のチャネルへと進行し、それにより、隣接するチャネル間に位置するシリコンウエハの領域の少なくとも一部がアンダーカットされて、第1及び第2のチャネル間に(111)シリコンウエハから印刷可能半導体素子及びオプションとしてブリッジ素子が形成される。この処理は、第1及び第2のチャネル間に位置する部分的に又は完全にアンダーカットされたシリコン構造を備える印刷可能半導体素子を形成する。印刷可能半導体素子の配列を形成するための有用な実施形態では、良好な位置及び寸法を有する多数のチャネルを備えるパターンがシリコンウエハの外面上に形成され、それにより、単一の処理プロトコルで多数の印刷可能半導体素子を同時に製造することができる。

【0023】

[023]一実施形態では、ウエハの外面上の第1及び第2のチャネルは、略平行に長手方向に向けられる。この実施形態では、凹状形態部間をエッチングするステップは、第1及び第2のチャネル間に位置する部分的に又は完全にアンダーカットされた印刷可能半導体リボンを形成する。好ましくは、幾つかの実施形態の場合に、第1及び第2のチャネルの位置及び物理的寸法は、転写デバイスとの接触を伴う処理ステップのような更なる処理まで印刷可能半導体リボンがシリコンウエハに対して一体に接続されたままの状態となるように選択される。なお、この転写デバイスは、エラストマスタンプを含むがこれに限定されない。一実施形態では、例えば、第1のチャネルが第1の端部で終端し、第2のチャネルが第2の端部で終端し、印刷可能半導体リボンは、直接的に、或いは、ブリッジ素子のようなアライメント維持素子を介して、第1のチャネルの第1の端部とチャネルの第2の端部との間の領域でシリコンウエハに対して接続された状態を維持する。また、第1のチャネル及び第2のチャネルが第3及び第4の端部でそれぞれ終端していてもよく、また、場合により、印刷可能半導体リボンは、第3の端部と第4の端部との間の領域でシリコンウエハに対して直接的に接続してもよく、又は、ブリッジ素子のようなアライメント維持素子によって接続されてもよい。

【0024】

[024]本発明のこの態様の方法は、多数のオプションの処理ステップを含んでいてもよく、当該オプションの処理ステップとしては、電気接点のような導電構造、絶縁構造、及び/又は更なる半導体構造を印刷可能半導体素子上に形成するための材料堆積及び/又はパターニング、アニーリングステップ、ウエハ洗浄、表面処理、例えば外面の粗さを減少させるための表面研磨、材料ドーピング処理、エラストマスタンプといった転写デバイス又はソリューション印刷技術を使用する印刷可能半導体素子の転写、パターニング、組み立て及び/又は集積、ウエハ表面仕上げ、例えば親水基又は疎水基を形成することによって印刷可能半導体素子の表面を機能化すること、例えばエッチングによる材料除去、印刷可能半導体素子上での熱酸化物層の成長及び/又は除去、並びに、これらオプションの処理ステップの任意の組み合わせがあるが、これらに限定されるものではない。

【0025】

[025]本発明の印刷可能半導体素子を形成する方法は、シリコンウエハから印刷可能半導体素子を切り離すステップを更に含んでいてもよい。この説明では、「切り離す」とは、印刷可能半導体素子がシリコンウエハから分離されるプロセスのことである。本発明における切り離し処理は、印刷可能半導体素子の一以上の端部をマザー基板に対して接続するブリッジ素子のような一以上のアライメント維持素子を破壊することを伴ってもよい。シリコンウエハからの印刷可能半導体素子の切り離しは、乾式転写コンタクト印刷(dry transfer contact printing)のようなコンタクト印刷転写処理に有用なエラストマスタンプといった転写デバイスと印刷可能半導体素子を接触させることによって行なわれてもよい。幾つかの実施形態では、半導体素子の外面が、形状適合可能な(Conformable)エラストマスタンプといった転写デバイスの接触面と接触し、場合により形状適合して(Conformally)接触し、半導体素子が接触面に結合する。オプションとして、本発明のこの態様の方法は、印刷可能半導体素子を転写デバイスに対して位置合わせ転写するステップを更に含む。オプションとして、本発明のこの態様の方法は、動力学的に制御される分離速度を使用して、エラストマスタンプに対する印刷可能半導体素子の位置合わせ転写を容易にすることを更に含む。

【0026】

[026]印刷可能半導体素子を製造するための本方法の利点は、バルク(111)シリコンウエハといった所定の(111)シリコンウエハ出発材料を使用して複数回行なうことができるという点である。本方法の反復処理能力は、単一の出発ウエハを使用して本方法の複数の繰り返しを可能にし、それにより、数十又は数百平方フィートもの印刷可能半導体素子を1平方フィートのバルクシリコンウエハ出発材料から形成できるので、有益である。一実施形態では、本方法は、印刷可能半導体素子の切り離し及び転写後にシリコンウエハの外面を再仕上げするステップを更に含む。この説明では、「シリコンウエハを再仕上げする」との表現は、例えば一以上の印刷可能半導体素子の切り離し及び/又は転写の後に、平坦な、場合により滑らかなシリコンウエハの外面を形成する処理ステップを指す。再仕上げは、技術的に公知の任意の技術によって行なわれ得るものであり、研磨、エッチング、研削、微細加工、化学機械研磨、異方性ウェットエッチングを含むものであるが、これらに限定されない。有用な実施形態では、(i)シリコンウエハの外面上に複数の凹状形態部を形成する処理ステップと、(ii)凹状形態部の側面の少なくとも一部及び場合により側面の全体をマスキングする処理ステップと、(iii)側面間をエッチングし、それにより、更なる印刷可能半導体素子を形成する処理ステップとが、外面の再仕上げ後に繰り返される。切り離し処理ステップ及び再仕上げ処理ステップを含む本発明の方法は、単一のシリコンウエハ出発材料を使用して多数回繰り返して行なわれてもよい。

【0027】

[027]他の態様において、本発明は、受容基板上に対する高精度の位置合わせ転写、位置合わせ組み立て、及び/又は、位置合わせ集積を可能にする印刷可能半導体構成(組成)及び構造を提供する。この説明において、「位置合わせ転写」、「位置合わせ組み立て」、「位置合わせ集積」との表現は、転写された素子の相対的な空間的方向(配置)を好ましくは約5ミクロンの範囲内に、更に好ましくは何らかの用途では約0.1ミクロンの範囲内に維持する協調プロセスを指す。また、本発明の位置合わせプロセスとは、5ミクロンの範囲で、好ましくは何らかの実施形態では500ナノメートルの範囲で、予め選択された受容基板の特定の領域に対して印刷可能半導体素子を転写し、組み立て、及び/又は、集積することができる本発明の方法の能力のことであってもよい。本発明のこの態様の印刷可能半導体構成及び構造は、転写印刷組み立て技術及び集積技術の正確さ、精度、及び、再現性を高め、それにより、高性能電子デバイス及び電気光学デバイスを製造するための堅牢で商業的に実施可能な製造プラットフォームを与える。本発明における位置合わせ処理は、様々な転写デバイスを使用して行なわれてもよく、当該転写デバイスには、乾式転写コンタクト印刷のようなコンタクト印刷転写処理において有用なエラストマスタンプ又は非エラストマスタンプといったスタンピング転写デバイスがあるが、これに限定されるものではない。

【0028】

[028]この態様の一実施形態では、本発明は、印刷可能半導体素子を備える印刷可能半導体構造と、印刷可能半導体構造及びマザーウエハに対して接続し、場合により一体に接続される一つ以上のブリッジ素子と、を提供する。印刷可能半導体素子及びブリッジ素子の物理的寸法、構成、形状、幾何学的構成は、エラストマスタンプのような転写デバイスと印刷可能半導体との接触によってブリッジ素子を破断でき、それにより、制御された方式でマザーウエハから印刷可能半導体構造が切り離されるように選択される。

【0029】

[029]一実施形態では、ブリッジ素子、印刷可能半導体素子、及びマザーウエハは、単一構造を構成するように一体に接続される。この説明では、「単一構造」とは、マザーウエハ、ブリッジ素子、印刷可能半導体素子がモノリシック構造を備える構成のことである。例えば、一実施形態では、単一構造は、一以上のブリッジ素子がマザーウエハ及び印刷可能半導体素子に対して一体に接続される単一の連続した半導体構造を備える。しかしながら、本発明は、ブリッジ素子、印刷可能半導体素子及びマザーウエハが単一構造を構成せず、共有結合、接着剤、及び/又は、分子間力(例えば、ファンデルワールス力、水素結合、双極子−双極子相互作用、ロンドン分散力)等の結合機構によって互いに接続される印刷可能半導体構造も含む。

【0030】

[030]本発明のこの態様の印刷可能半導体構造は、印刷可能半導体素子及びマザーウエハに対して接続され、場合により一体に接続された単一の又は複数のブリッジ素子を備えていてもよい。本発明のブリッジ素子は、印刷可能半導体素子の表面をマザーウエハに対して接続する構造を含む。一実施形態では、一以上のブリッジ素子が、印刷可能半導体素子の端部及び/又は底部をマザーウエハに対して接続する。一実施形態では、ブリッジ素子は、印刷可能半導体リボンの長さを終端させる一端又は両端をマザーウエハに対して接続する。幾つかの実施形態では、印刷可能半導体素子及びブリッジ素子がマザーウエハから少なくとも部分的にアンダーカットされる。高精度の位置合わせ転写を可能にする一実施形態では、印刷可能半導体素子及びブリッジ素子がマザーウエハから完全にアンダーカットされる。しかしながら、本発明は、印刷可能半導体素子をマザーウエハに対して接続するアンダーカットされた構造ではないブリッジ素子も含む。そのようなアンダーカットされない形態の一例は、印刷可能半導体素子の底部をマザーウエハに対して接続する及び/又は固定するブリッジ素子である。

【0031】

[031]本発明は、ブリッジ素子が印刷可能半導体素子の少なくとも二つの異なる端部又は表面をマザーウエハに対して接続する実施形態を含む。複数のブリッジ素子を有する印刷可能半導体構造は、それらが転写デバイス及び/又は受容基板の接触面に対する接触及び転写中に半導体素子のアライメント、空間的方向及び位置の大きな安定性を与えるため、高度な高精度の位置合わせ転写を必要とする用途において有用である。

【0032】

[032]本発明のこの態様のブリッジ素子は、印刷可能半導体素子を半導体ウエハといったマザー基板に対して接続する及び/又は固定するアライメント維持素子である。ブリッジ素子は、転写、組み立て及び/又は集積処理ステップ中に印刷可能半導体素子の選択された方向及び/又は位置を維持するのに有用である。また、ブリッジ素子は、転写、組み立て及び/又は集積処理ステップ中に印刷可能半導体素子のパターン又は配列の相対的な位置及び方向を維持するのにも有用である。本発明の方法において、ブリッジ素子は、コンフォーマブルエラストマスタンプのような転写デバイスの接触面に関連する接触、結合、転写及び集積プロセス中に印刷可能半導体素子の位置及び空間的方向を保ち、それにより、マザーウエハから転写デバイスへの位置合わせ転写を可能にする。

【0033】

[033]本発明のこの態様におけるブリッジ素子は、転写デバイスの接触及び/又は移動時に印刷可能半導体素子の位置及び方向を大きく変えることなく印刷可能半導体素子から引き離すことができる。この引き離しは、転写デバイスの接触及び/又は移動中、例えば乾式転写コンタクト印刷中におけるブリッジ素子の破断及び/又は切断によって達成されてもよい。破断に伴う引き離しは、エラストマスタンプのような形状適合可能な転写デバイスの使用及び/又は転写デバイスの接触面に対する転写を容易にする動力学的に制御された分離速度の使用によって促進されてもよい。

【0034】

[034]本発明のこの態様の一実施形態では、ブリッジ素子の空間的配置、幾何学的形状、構成、及び物理的寸法は、高精度の位置合わせ転写を行なうように選択される。この説明では、「高精度の位置合わせ転写」との表現は、印刷可能半導体素子の相対的な空間的方向及び相対的位置の変化が約10%未満である印刷可能半導体素子の転写を指す。また、高精度の位置合わせ転写とは、マサー基板から転写デバイス及び/又は受容基板への印刷可能半導体素子の良好な配置精度を伴う転写のことでもある。また、高精度の位置合わせ転写とは、転写デバイス及び/又は受容基板への印刷可能半導体素子のパターンの良好なパターン忠実度を伴う転写のことでもある。

【0035】

[035]本発明のブリッジ素子は、部分的に又は完全にアンダーカットされた構造を備えていてもよい。本発明において有用なブリッジ素子は、均一な幅、又は、破断による切り離しを容易にする体系的に可変の幅、例えば狭い首部へと先細る幅を有していてもよい。幾つかの実施形態では、ブリッジ素子は、約100ナノメートル〜約1000ミクロンの範囲から選択される平均幅と、約1ナノメートル〜約1000ミクロンの範囲から選択される平均厚さと、約100ナノメートル〜約1000ミクロンの範囲から選択される平均長さとを有する。幾つかの実施形態では、ブリッジ素子の物理的寸法及び形状は、マザーウエハに接続する印刷可能半導体素子の物理的寸法に対して規定される。位置合わせ転写は、例えば、印刷可能半導体素子の平均幅よりも少なくとも2倍小さい、好ましくは幾つかの用途では10倍小さい平均幅、及び/又は、印刷可能半導体素子の平均厚さよりも1.5倍小さい平均厚さを有するブリッジ素子を使用して達成されてもよい。また、ブリッジ素子には、それらの破断を容易にし、且つ、マザーウエハから転写デバイス及び/又は受容基板への印刷可能半導体素子の位置合わせ転写を容易にするために、鋭角な形態部が設けられていてもよい。

【0036】

[036]この態様の一実施形態では、印刷可能半導体素子は、第1の端部及び第2の端部で終端する長手方向主軸線に沿って所定の長さで延びる印刷可能半導体リボンを備える。第1のブリッジ素子は、印刷可能半導体リボンの第1の端部をマザーウエハに対して接続し、また、第2のブリッジ素子は、半導体リボンの第2の端部をマザーウエハに対して接続する。オプションとして、印刷可能半導体リボン、第1のブリッジ素子、及び第2のブリッジ素子は、完全にアンダーカットされた構造である。一実施形態では、第1のブリッジ素子、第2のブリッジ素子、印刷可能半導体リボン、及びマザーウエハは、単一半導体構造を備える。一実施形態では、第1及び第2のブリッジ素子は、印刷可能半導体リボンの平均幅よりも約1〜約20倍小さい平均幅を有する。一実施形態では、第1及び第2のブリッジ素子は各々、印刷可能半導体リボンの第1の端部及び第2の端部の各々の断面積の1〜約100%未満の断面積に対して接続される。本発明は、第1及び第2のブリッジ素子が互いに基端又は先端に空間的構成を有する実施形態を含む。

【0037】

[037]本発明において、印刷可能半導体素子及び/又はブリッジ素子の外面は、エラストマスタンプのような転写デバイスへの位置合わせ転写を高めるように機能化されていてもよい。位置合わせ転写にとって有用な機能化手法は、親水基及び/又は疎水基を、印刷可能半導体素子の表面に対して加えて、転写デバイスの接触面に対する結合を向上することを含む。他の化学手法は、接触面(印刷可能素子上及び/又は受容面上の面)のうちの一以上を、金属でコーティングすることであり、当該金属としては、金が挙げられるが、これに限定されない。これらの金属は、受容面を印刷可能素子に対して化学的に架橋することができる自己組織構成した単層で処理されてもよい。また、二つの名目上露出した金表面が、接触時に(例えば冷間溶接によって)金属溶接結合を形成してもよい。

【0038】

[038]本発明の印刷可能半導体素子は幅広い範囲の材料から形成されてもよい。印刷可能半導体素子を形成するための有用な前駆材料としては、単結晶シリコンウエハ、多結晶シリコンウエハ、ゲルマニウムウエハといったバルク半導体ウエハ、超薄シリコンウエハのような超薄半導体ウエハ、P型又はN型ドープウエハや選択された空間的分布のドーパントを有するウエハといったドープ半導体ウエハ(絶縁体上のシリコン(例えば、Si−SiO2、SiGe)といった絶縁体ウエハ上の半導体)、及び、基板ウエハ上のシリコンや絶縁体上のシリコンといった基板ウエハ上の半導体を含む半導体ウエハソースが挙げられる。また、本発明の印刷可能半導体素子は、従来の方法を使用する半導体デバイス処理からの使い残しである使い古しの又は未使用の高品質な又は再処理された半導体材料から形成されてもよい。また、本発明の印刷可能半導体素子は、犠牲層又は基板(例えば、SiN又はSiO2)上に堆積され、且つ、その後にアニールされるアモルファスの薄膜、多結晶半導体材料及び単結晶半導体材料(例えば、多結晶シリコン、アモルファスシリコン、多結晶GaAs及びアモルファスGaAs)のような種々のナノウエハソース、及び、グラファイト、MoSe2、他の遷移金属カルコゲニドを含むがこれらに限定されない他のバルク結晶、並びに、イットリウムバリウム酸化銅から形成されてもよい。

【0039】

[039]本発明の典型的な転写デバイスは、エラストマ転写スタンプのような乾式転写スタンプ、複合転写スタンプ、形状適合可能なエラストマスタンプのような形状適合可能な転写デバイス、多層エラストマスタンプのような多層転写デバイスを含む。エラストマスタンプといった転写デバイスは、乾式転写コンタクト印刷等のコンタクト印刷処理にとって有用である。本発明の転写デバイスは場合により、形状適合可能である。本発明において有用な転写デバイスは、2005年4月27日に米国特許商標局に出願された“Composite Patterning Devices for Soft Lithography”と題する米国特許出願第11/115,954号に記載されるような複数の高分子層を備える転写デバイスを含む。なお、この米国特許出願を、その全体を参照することによって、本願に援用する。本発明の方法に使用できる例示的なパターニングデバイスは、ポリ(ジメチルシロキサン)(PDMS)層のような低いヤング率を有する高分子層であり、好ましくは幾つかの用途では約1ミクロン〜約100ミクロンの範囲から選択される厚さを有するものである。ヤング率が低い高分子の使用は、一以上の印刷可能半導体素子、特に湾曲した露出面、粗い露出面、平坦な露出面、滑らかな露出面及び/又は輪郭を成す露出面を有する印刷可能半導体素子との良好な形状適合接触(ConformalContact)を形成することができ、且つ、湾曲した基板表面、粗い基板表面、平坦な基板表面、滑らかな基板表面及び/又は輪郭を成す基板表面のような種々の表面形態を有する基板表面との良好な形状適合接触を形成できる転写デバイスを提供するので、有益である。

【0040】

[040]また、本発明は、高精度の位置合わせ転写を含むエラストマスタンプといった転写デバイスに対する印刷可能半導体素子の転写方法、並びに/若しくは、高精度の位置合わせ組み立て及び/又は集積を含む受容基板上における印刷可能半導体素子の組み立て及び/又は集積方法も含む。本発明の印刷方法及び構成の利点は、印刷可能半導体素子のパターンを、当該パターンを規定する印刷可能半導体素子の選択された空間的配置を保つ方式で基板表面上に転写して組み立てることができるという点である。本発明のこの態様は、選択されたデバイス構造又はデバイス構造の配列に直接に対応する良好な位置及び相対的な空間的方向で複数の印刷可能半導体素子が製造される用途において特に有益である。本発明の転写印刷方法は、印刷可能半導体素子及び/又は印刷可能機能デバイスを転写し、位置決めし、組み立てることを可能とするものであり、当該素子及びデバイスには、トランジスタ、光導波管、マイクロ電気機械システム、ナノ電気機械システム、レーザダイオード、又は完全に形成された回路があるが、これらに限定されない。

【0041】

[041]本処理方法及び構成は、半導体材料に加えて、バルク半金属材料に適用できる。例えば、本方法、構成及び構造は、グラファイトやグラフェン等の炭素質材料及び雲母等の他の層状材料と共に使用されてもよい。

【0042】

[042]一実施形態では、本発明は、印刷可能半導体素子を転写デバイスに対して転写する方法であって、(i)印刷可能半導体素子を備える印刷可能半導体素子構造と、印刷可能半導体構造に接続され且つマザーウエハに接続される少なくとも一つのブリッジ素子とを設けるステップであって、印刷可能半導体素子及びブリッジ素子がマザーウエハから少なくとも部分的にアンダーカットされる、当該ステップと、(ii)印刷可能半導体素子を、接触面を有する転写デバイスと接触させるステップであって、接触面と印刷可能半導体素子との間の接触が印刷可能半導体素子を接触面に結合させる、当該ステップと、(iii)ブリッジ素子の破断をもたらすように転写デバイスを移動させるステップであって、それにより、印刷可能半導体構造をマザーウエハから上記転写デバイスへと転写させる、当該ステップと、を含む方法を提供する。

【0043】

[043]一実施形態では、本発明は、基板の受容面上に印刷可能半導体素子を組み立てるための方法であって、(i)印刷可能半導体素子と、印刷可能半導体構造に接続され且つマザーウエハに接続される少なくとも一つのブリッジ素子とを設けるステップであって、印刷可能半導体素子及びブリッジ素子がマザーウエハから少なくとも部分的にアンダーカットされる、当該ステップと、(ii)印刷可能半導体素子を、接触面を有する転写デバイスと接触させるステップであって、接触面と印刷可能半導体素子との間の接触が印刷可能半導体素子を接触面に結合させる、当該ステップと、(iii)ブリッジ素子の破断をもたらすように転写デバイスを移動させるステップであって、それにより、印刷可能半導体構造をマザーウエハから転写デバイスへと転写することによって、その上に印刷可能半導体素子が配置された接触面を形成するステップと、(iv)接触面上に配置された印刷可能半導体素子を基板の受容面と接触させるステップと、(v)形状適合可能な転写デバイスの接触面と印刷可能半導体素子とを分離するステップであって、印刷可能半導体素子を受容面上へ転写することによって、基板の受容面上に印刷可能半導体素子を組み立てるステップと、を含む方法を提供する。

【0044】

一実施形態では、本発明は、印刷可能半導体素子を製造するための方法であって、(1)(111)方位を有し、且つ、外面を有するシリコンウエハを設けるステップと、(2)シリコンウエハの外面上に複数の凹状形態部を形成するステップであって、凹状形態部の各々が、露出したシリコンウエハの底面及び側面を有する、当該ステップと、(3)凹状形態部の側面の少なくとも一部をマスキングするステップと、(4)凹状形態部間をエッチングするステップであって、当該エッチングが上記シリコンウエハの<110>方位に沿って行なわれ、それにより、印刷可能半導体素子が製造される、当該ステップと、を含む方法を提供する。

【発明の詳細な説明】

【0045】

[070]図面を参照すると、同様の参照符号は同様の要素を指しており、また、複数の図面に現れる同じ参照符号は同じ要素を示している。また、以降の説明には、以下の定義が当てはまる。

【0046】

[071]「印刷可能」とは、基板を高温(すなわち、約摂氏400度以下の温度)に晒すことなく基板上にあるいは基板中に転写、組み立て、パターニング、編成、及び/又は、集積化することができる材料、構造、デバイス部品、及び/又は、集積機能デバイスに関連している。本発明の一実施形態では、印刷可能な材料、素子、デバイス部品、及びデバイスは、溶液印刷(solution printing)、又は乾式転写コンタクト印刷(dry transfer contact printing)によって基板上にあるいは基板中に転写、組み立て、パターニング、編成、及び/又は、集積化することができる。

【0047】

[072]本発明の「印刷可能半導体素子」は、例えば乾式転写コンタクト印刷法及び/又はソリューション印刷法を使用することによって基板表面上に組み立てることができ及び/又は集積化することができる半導体構造を備える。一実施形態では、本発明の印刷可能半導体素子は、単一単結晶半導体構造、多結晶半導体構造、微結晶性無機半導体構造である。一実施形態では、印刷可能半導体素子は、マザーウエハのような基板に、一以上のブリッジ素子を介して接続される。本説明においては、単一構造は、機械的に接続される特徴形態を有するモノリシック素子である。本発明の半導体素子は、ドーピングされていなくてもよく、あるいはドーピングされていてもよく、ドーパントの選択された空間分布を有していてもよく、また、P型ドーパント及びN型ドーパントを含む複数の異なるドーパント材料がドーピングされていてもよい。本発明は、約1ミクロン以上の少なくとも一つの断面寸法を有する微細構造の印刷可能半導体素子と、約1ミクロン以下の少なくとも一つの断面寸法を有するナノ構造の印刷可能半導体素子とを含む。多くの用途で有用である印刷可能半導体素子は、従来の高温処理技術を使用して形成される高純度結晶半導体ウエハといった高純度バルク材料の「トップダウン」処理から得られる素子を備える。一実施形態では、本発明の印刷可能半導体素子は、導電層、誘電体層、電極、更なる半導体構造、又はこれらの任意の組み合わせといった少なくとも一つの更なるデバイス部品又は構造に動作可能に接続された半導体を有する複合構造を備える。一実施形態では、本発明の印刷可能半導体素子は、伸縮可能な半導体素子及び/又は異種半導体素子を備える。

【0048】

[073]「断面寸法」とは、デバイス、デバイス部品、又は材料の断面の寸法のことである。断面寸法としては、幅、厚さ、半径、直径が挙げられる。例えば、リボン形状を有する印刷可能半導体素子は、長さと、厚さ及び幅の二つの断面寸法とによって特徴付けられる。例えば、円筒形状を有する印刷可能半導体素子は、長さと断面寸法直径(あるいは半径)とによって特徴付けられる。

【0049】

[074]「略平行に長手方向に向けられた」とは、印刷可能半導体素子といった素子群の長手方向軸が選択されたアライメント軸と略平行に向けられるような方向性のことである。この定義では、選択された軸と略平行とは、完全に平行な方向から10度の範囲内にある方向、より好ましくは完全に平行な方向から5度の範囲内にある方向のことである。

【0050】

[075]「可撓性の」及び「屈曲(湾曲)可能な」との用語は、本説明においては同意語として使用されており、材料、構造、デバイス又はデバイス部品の破壊点を特徴付ける歪み等の著しい歪みをもたらす変形を受けることなく湾曲形状へ変形される材料、構造、デバイス又はデバイス部品の性能を示している。例示的な実施形態では、可撓性の材料、構造、デバイス又はデバイス部品は、約5%以上の歪みをもたらすことなく、好ましくは一部の用途においては約1%以上の歪みをもたらすことなく、更に好ましくは一部の用途においては約0.5%以上の歪みをもたらすことなく湾曲形状へ変形され得る。

【0051】

[076]「半導体」とは、非常に低い温度で絶縁体であるが約300ケルビンの温度で相当の導電率を有する材料である任意の材料のことである。本説明において、半導体という用語の使用は、マイクロエレクトロニクス及び電気デバイスの技術でのこの用語の使用と整合させようとするものである。本発明において有用な半導体は、シリコン、ゲルマニウム、ダイヤモンド等の元素半導体や、SiC及びSiGe等のIV族化合物半導体、AlSb、AlAs、Aln、AlP、BN、GaSb、GaAs、GaN、GaP、InSb、InAs、InN、InP等のIII−V族半導体、AlXGa1−XAs等のIII−V族三元半導体合金、CsSe、CdS、CdTe、ZnO、ZnSe、ZnS、ZnTe等のII−IV族半導体、CuCl等のI−VII族半導体、PbS、PbTe、SnS等のIV−VI族半導体、PbI2、MoS2、GaSe等の層半導体、CuO、Cu2O等の酸化物半導体、等といった化合物半導体を備えていてもよい。半導体という用語は、真性半導体と、所定の用途又はデバイスのために有用である有益な電気的特性を与えるためにp型ドーピング材料及びn型ドーピング材料を有する半導体を含む一つ以上の選択された材料がドーピングされた不純物半導体とを含む。半導体という用語は、半導体及び/又はドーパントの混合物を備える複合材料を含む。本発明の一部の用途に有用な特定の半導体材料としては、Si、Ge、SiC、AIP、AlAs、AlSb、GaN、GaP、GaAs、GaSb、InP、InAs、GaSb、InP、InAs、InSb、ZnO、ZnSe、ZnTe、CdS、CdSe、ZnSe、ZnTe、CdS、CdSe、CdTe、HgS、PbS、PbSe、PbTe、AlGaAs、AlInAs、AlInP、GaAsP、GaInAs、GaInP、AlGaAsSb、AlGaInP、GaInAsPが挙げられるが、これらに限定されない。多孔質シリコン半導体材料は、センサや発光ダイオード(LED)及び固体レーザ等の発光材料の分野における本発明の用途においては有用である。半導体材料の不純物は、半導体材料自体以外の原子、元素、イオン及び/又は分子又は半導体材料に対して与えられる任意のドーパントである。不純物は、半導体材料中に存在し且つ半導体材料の電気的特性に悪影響を与えることがある望ましくない材料であり、酸素、炭素、重金属を含む金属を含むがこれらに限定されない。重金属不純物としては、周期表の銅と鉛との間にある元素のグループ、カルシウム、ナトリウム、並びに、全てのイオン、化合物及び/又はそれらの複合体が挙げられるが、これらに限定されない。

【0052】

[077]「良好な電子的性能」及び「高性能」は、本説明においては同意語として使用されており、電子信号スイッチング及び/又は増幅のような所望の機能を提供する電界効果移動度、閾値電圧、on−off比等の電子的特性を有するデバイス及びデバイス部品を示している。良好な電子的性能を示す本発明の典型的な印刷可能半導体素子は、100cm2V−1s−1以上、好ましくは一部の用途においては約300cm2V−1s−1以上の固有の電界効果移動度を有し得る。良好な電子的性能を示す本発明の典型的なトランジスタは、約100cm2V−1s−1以上、好ましくは一部の用途においては約300cm2V−1s−1以上、更に好ましくは一部の用途においては約800cm2V−1s−1以上のデバイス電界効果移動度を有し得る。良好な電子的性能を示す本発明の典型的なトランジスタは、約5ボルト未満の閾値電圧及び/又は約1×104を超えるon−off比を有していてもよい。

【0053】

[078]「プラスチック」とは、一般に加熱時にモールド又は成形でき、且つ、所望の形状へと硬化できる任意の合成材料又は天然に生じる材料、若しくはこれらの材料の組み合わせを指す。本発明のデバイス及び方法において有用な典型的なプラスチックとしては、高分子、樹脂、セルロース誘導体が挙げられるが、これらに限定されない。本説明において、プラスチックとの用語は、構造増強材、充填剤、繊維、可塑剤、安定剤、若しくは、所望の化学的又は物理的な特性を与えることができる添加物のような一以上の添加物を有する一以上のプラスチックを備える複合プラスチック材料を含むものを意味している。

【0054】

[079]「エラストマ」とは、伸長又は変形させることができ、且つ、実質的な永久歪みを伴うことなく、その当初の形状に戻すことができる高分子材料のことである。エラストマは、一般に、略弾性的な変形を受ける。本発明において有用な典型的なエラストマは、ポリマ、コポリマ、複合材料、又は、ポリマとコポリマとの混合物を含み得る。エラストマ層とは、少なくとも一つのエラストマを含む層のことである。また、エラストマ層は、ドーパント及び他の非エラストマ材料を含むことがある。本発明において有用なエラストマとしては、熱可塑性エラストマ、スチレン材料、オレフィン材料、ポリオレフィン、ポリウレタン熱可塑性エラストマ、ポリアミド、合成ゴム、PDMS、ポリブタジエン、ポリイソブチレン、ポリ(スチレン−ブタジエン−スチレン)、ポリウレタン、ポリクロロプレン、シリコーンを挙げることができるが、これらに限定されない。エラストマは、本方法において有用であるエラストマスタンプを与える。

【0055】

[080]「転写デバイス」とは、印刷可能半導体素子のような素子又は素子の配列を受けることができ及び/又は再配置することができるデバイス又はデバイス部品のことである。本発明において有用な転写デバイスは、転写を受ける素子と形状適合接触を確立できる一以上の接触面を有する形状適合可能な転写デバイスを含む。本方法及び構成は、コンタクトプリント処理にとって有用であるエストラマスタンプを備える転写デバイスに関する使用に特に良く適している。

【0056】

[081]「大面積」とは、デバイス製造のために使用される基板の受容面の面積のような、約36平方インチ以上の面積のことである。

【0057】

[082]「デバイス電界効果移動度」とは、トランジスタのような電気デバイスの電界効果移動度のことであり、電気デバイスに対応する出力電流データを使用して計算されるようなものである。

【0058】

[083]「形状適合接触(conformal contact)」とは、表面、コーティングされた表面、及び/又は、基板表面上に(印刷可能半導体素子等の)構造体を転写し、組み立て、編成し、集積するために有用となり得る材料がその上に堆積された表面の間で成される接触のことである。一態様では、形状適合接触は、基板表面又は印刷可能半導体素子等の物体の表面の形状全体に対する形状適合可能な転写デバイスの一以上の接触面の巨視的な適合(順応)に関する。他の態様では、形状適合接触は、基板表面に対する形状適合可能な転写デバイスの一以上の接触面の微視的な適合に関するものであり、外側空隙(outvoids)との密着をもたらすものである。形状適合接触という用語は、ソフトリソグラフィの技術におけるこの用語の使用と整合させようとするものである。形状適合接触は、形状適合可能な転写デバイスの一以上の露出した接触面と基板表面との間で成されてもよい。或いは、形状適合接触は、一以上のコーティングされた接触面、例えばその上に転写材料、印刷可能半導体素子、デバイス部品及び/又はデバイスが堆積された形状適合可能な転写デバイスの接触面と基板表面との間で行なわれてもよい。或いは、形状適合接触は、形状適合可能な転写デバイスの一以上の露出した、或いは、コーティングされた接触面と、転写材料、固体フォトレジスト層、プレポリマ層、液体、薄膜又は流体等の材料でコーティングされた基板表面との間で行なわれてもよい。

【0059】

[084]「配置精度」とは、電極等の他のデバイス部品の位置に対する、又は、受容面の選択された領域に対する選択された位置へと印刷可能半導体素子等の印刷可能素子を転写することができる転写方法又は転写デバイスの能力のことである。「良好な配置」精度とは、他のデバイス又はデバイス部品に対する選択された位置へと、又は、受容面の選択された領域に対する選択された位置へと、絶対的に正確な位置からの50μm以下の空間的偏り、好ましくは一部の用途においては20μm以下の空間的偏り、更に好ましくは一部の用途においては5μm以下の空間的偏りで、印刷可能素子を転写できる方法及びデバイスを指している。本発明は、良好な配置精度をもって転写される少なくとも一つの印刷可能素子を備えるデバイスを提供する。

【0060】

[085]「忠実度」とは、印刷可能半導体素子のパターンのような素子の選択されたパターンが、基板の受容面に対してどの程度うまく転写されるかについての尺度(指標)のことである。良好な忠実度とは、個々の素子の相対位置及び方位が転写中に保たれる、素子の選択されたパターンの転写のことであり、例えば、個々の素子の選択されたパターン内でのそれらの位置からの空間的な偏りが500nm以下、好ましくは100nm以下となる。

【0061】

[086]「アンダーカット」とは、印刷可能半導体素子、ブリッジ素子又はこれらの双方の素子のような素子の底面が、少なくとも部分的にマザーウエハ又はバルク材料のような他の構造体から引き離されているか、又は、固定されていない構造的形態のことである。完全なアンダーカットとは、印刷可能半導体素子、ブリッジ素子又はこれらの双方の素子のような素子の底面がマザーウエハ又はバルク材料等の他の構造体から完全に引き離されている構造的形態のことである。アンダーカット構造は、部分的又は完全な独立構造であってもよい。アンダーカット構造は、それらが引き離されるマザーウエハ又はバルク材料等の他の構造体によって部分的に又は完全に支持されていてもよい。アンダーカット構造は、底面以外の表面で、ウエハ又は他のバルク材料等の他の構造体に対して付着され、貼り付けられ、及び/又は、接続されていてもよい。例えば、本発明は、印刷可能半導体素子及び/又はブリッジ素子がそれらの底面以外の表面上に位置する端部でウエハに対して接続される(例えば図2A及び図2B参照)方法及び構造を含む。

【0062】

[087]以下の説明では、本発明の正確な本質を十分に説明するために、本発明のデバイス、デバイス部品、及び方法の多数の特定の詳細を示す。しかしながら、これらの特定の詳細が無くとも本発明を実施できることは、当業者には明らかであろう。

【0063】

[088]本発明は、印刷可能半導体素子を製造し、印刷可能半導体素子及び印刷可能半導体素子のパターンを基板表面上に組み立てるための方法及びデバイスを提供する。高品質な印刷可能半導体素子を低コストのバルク半導体材料から製造するための方法を提供する。また、本発明は、マザーウエハから転写デバイス及び/又は受容基板への印刷可能半導体素子の高精度の位置合わせ転写(registered transfer)を行なう半導体構造及び方法も提供する。本発明の方法、デバイス、及びデバイス部品は、高性能な電子デバイス及び光電子デバイス、並びにデバイスのアレイを、可撓性のプラスチック基板上に形成することを可能とする。

【0064】

[089]図1Aは、単結晶シリコンの印刷可能半導体リボンを有する印刷可能半導体素子を、(111)方位をもつバルクシリコンウエハから形成するための本発明の例示的な方法を示す概略断面図である。図1Bは、バルクシリコンウエハから印刷可能半導体素子を形成するための本方法における、繰り返し可能な処理ステップを含む処理ステップを示すフロー図である。

【0065】

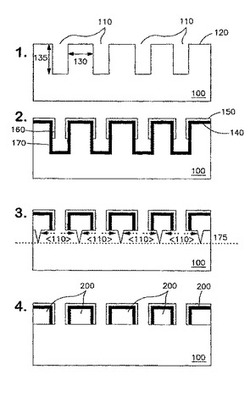

[090]図1A(パネル1)及び図1Bに示すように、まず、(111)方位を有するシリコンウエハ100を提供する。(111)方位を有するシリコンウエハ100は、バルクシリコンウエハであってもよい。次いで、予め選択された物理的寸法、間隔、空間的配置を有する複数のチャネル(溝)110を、例えば、近接場フォトリソグラフィ技術、リフトオフ技術、ドライエッチング技術を組み合わせて使用して、シリコンウエハ100の外面120にエッチングする。本実施形態では、チャネル間の間隔130は、本方法を使用して製造される印刷可能半導体リボンの幅を規定する。

【0066】

[091]図1A(パネル2)及び図1Bに示すように、オプションとして、熱酸化物層140を、例えば(111)シリコンウエハ100を加熱することにより、チャネル110上及び外面120上に成長させる。次に、マスク150を、例えば、金属又は金属の組み合わせ等の一以上のマスク材料の傾斜型電子ビーム蒸着(angled electron beam evaporation)を使用して、チャネル110の側面上及び外面120上に堆積し、これによって、マスク領域及び非マスク領域をシリコンウエハ100に形成する。このマスキングステップは、チャネル110の側面のマスク領域160及び同側面の非マスク領域170を形成する。本発明は、深さ135に沿うチャネル110の側面全体がマスキングされる実施形態を含む(例えば、図1D参照)。幾つかの実施形態では、マスク領域が側面の下方へと延びる範囲は、マスク材料の蒸着角度、ウエハ100の外面120上の表面特徴によって作られる「陰」、マスク材料の流束(flux)のコリメーションの程度によって制御される。チャネル110の深さ135及び側面のマスク領域160の範囲は、少なくとも部分的に、これらの方法によって形成される印刷可能半導体リボンの厚さを規定する。そして、オプションとして、熱酸化物層140の露出領域を、更なる処理の前に、例えば乾式化学エッチング技術を使用して除去する。

【0067】

[092]次に、図1A(パネル3)及び図1Bに示すように、チャネル110の側面の非マスク領域170をエッチングする。例示的な実施形態では、チャネル110の側面の非マスク領域170を、チャネル間のエッチングがシリコンウエハ100の<110>方位に沿って優先的(選択的)に生じるように、異方性エッチングし、これによって、隣接するチャネル110間の(111)シリコンウエハ100の領域をアンダーカットする。エッチフロント<110>方位を、図1Bのパネル3に破線矢印で概略的に示す。一実施形態では、異方性エッチングシステムを選択して、エッチングがシリコンウエハ100の<111>方位に沿って実質的に生じないようにする。異方性エッチングシステムの選択性、及び、シリコンウエハ100の(111)方位は、破線175として概略的に示す固有のエッチストップをもたらす。本発明のこの態様にとって有用な異方性エッチングシステムとしては、高温塩基性溶液を使用する湿式化学エッチングシステムが挙げられる。幾つかの実施形態では、この処理ステップのために、比較的滑らかな底面(例えば、1ナノメートル未満の粗さ)を有する印刷可能半導体リボンを形成するエッチングシステムが選択される。

【0068】

[093]図1A(パネル4)及び図1Bに示すように、チャネル間のエッチングは、シリコンウエハ100から完全にアンダーカットされる印刷可能半導体リボン200を形成する。一実施形態では、チャネル110の物理的寸法、形状、空間的配置は、エッチング処理ステップが一以上の端部でシリコンウエハ100に対して接続される印刷可能半導体リボン200を形成するように、選択される。本方法によって形成される印刷可能半導体リボン200は、平坦で、薄く、機械的に可撓性である。次いで、オプションとして、例えば湿式化学エッチング技術によってマスク150を除去する。

【0069】

[094]以下、図1Bのフローチャートを参照する。オプションとして、本方法は、印刷可能半導体素子を、例えばエラストマスタンプとの接触によってシリコンウエハから切り離すステップを含む。例示的な方法では、印刷可能半導体素子をエラストマスタンプと接触させることにより、印刷可能半導体素子をシリコンウエハ100に対して接続する一以上のブリッジ素子を破壊し、これにより、シリコンウエハ100からエラストマスタンプへの印刷可能半導体素子の位置合わせ転写を行なう。本発明の方法は、シリコンウエハ100からエラストマスタンプ転写デバイスへの位置合わせ転写を容易にするために、動力学的に制御された剥離速度の使用を含む。

【0070】

[095]オプションとして、本発明は、シリコンウエハ100の平坦な及び/又は滑らかな外面を形成する例えば表面処理ステップ(例えば、研磨、研削、エッチング、微細加工等)によって、シリコンウエハの外面を再仕上げするステップを更に含む歩留りの高い製造方法を含む。図1Bに示すように、シリコンウエハ100を再仕上げすることにより、製造プロセスを複数回繰り返すことができ、それにより、単一のシリコンウエハ出発材料からの印刷可能半導体リボンの歩留りが高められる。

【0071】

[096]図1の(c)は、凹状形態部の側面が完全ではなく部分的にマスキングされる製造方法を示す概略断面処理図を示している。図1の(d)は、凹状形態部の側面が完全にマスキングされる製造方法を示す概略断面処理図を示している。図1の(d)に示すように、凹状形態部の床部は、全てではなくその一部がマスキングされる。本実施形態では、本方法は、凹状形態部のマスキングされた側面の下側の材料をエッチングする処理ステップを含む。部分的にマスキングされた床部の構成がエッチング液のための入口を形成し、これにより、エッチングが、凹状形態部間、例えば隣接する凹状形態部間で起こり得るようになる。凹状形態部の側面の完全マスキングを使用する本発明の方法は、印刷可能半導体素子の厚さの選択及び規定における高い正確さ及び精度をもたらすのに有益である。一実施形態では、側面は、不動態化の境界が凹状形態部の床部で発生するように完全にマスキングされる。これらの方法において、リボンの厚さは、不動態化の境界によって規定されず、代わりに、溝の床部(底面)及びウエハの上面の高さによって規定される。

【0072】

[097]本発明の印刷可能半導体素子を製造する方法は、凹状形態部の幾何学的形状、物理的寸法、及び形態を精緻化するステップを更に含んでいてもよい。凹状形態部の精緻化は、凹状形態部を形成した後であって、印刷可能半導体素子の形成及び/又は切り離しの前における製造プロセス中の任意の時点で行なわれてもよい。有用な実施形態では、凹状形態部の精緻化は、凹状形態部の側面を部分的に又は完全にマスキングすることを含む処理ステップの前に行なわれる。図1Eは、側面の精緻化を伴うことなく形成された溝構造を有するSi(111)における凹状形態部の画像を示している。図1Eに示す凹状形態部は、位相シフトフォトリソグラフィ、金属リフトオフ、反応性イオンエッチング、及び、その後の金属エッチングマスクの除去によって形成されたものである。図1Fは、側面の精緻化を伴って形成された溝構造を有するSi(111)における凹状形態部の画像を示している。図1Fに示す凹状形態部は、位相シフトフォトリソグラフィ、金属リフトオフ、反応性イオンエッチング、高温KOH溶液中での異方性エッチングによる精緻化、及び、その後の金属エッチングマスクの除去によって形成されたものである。また、このサンプルは、傾斜型金属蒸着によって処理されている。これら図の比較によって示されるように、図1Fにおける溝の床部及び側面は、図1Eにおける溝の床部及び側面よりも滑らかに形成されている。

【0073】

[098]ここでの精緻化とは、凹状形態部の表面、例えば凹状形態部の側面及び床部の材料除去処理のことである。精緻化は、凹状形態部のより滑らかな表面をもたらす処理、並びに/若しくは、より均一な物理的寸法及び表面形態を有する凹状形態部をもたらす処理を含む。一実施形態では、幾何学的形状、物理的寸法及び/又は形態は、異方性エッチング技術によって、例えば高温KOH溶液を使用するエッチングによって精緻化される。溝の異方性ウェットエッチング精緻化は、位置合わせ転写が可能な(111)シリコンリボンの形成に特に有用である。精緻化処理ステップの利点には、(i)マザーウエハの結晶軸から決定される溝床部の改良された形成を可能とすること、及び、(2)マザーウエハの結晶軸によって溝の側面の改良された形成を可能とすることがある。

【0074】

[099]図2A及び図2Bは、印刷可能半導体素子と二つのブリッジ素子とを備える本発明の印刷可能半導体構造の概略平面図である。ブリッジ素子は、図2Aに示す構造では、互いに先端に配置されており、また、ブリッジ素子は、図2Bに示す構造では、互いに基端に配置されている。図2A及び図2Bに示すように、印刷可能半導体構造290は、印刷可能半導体素子300とブリッジ素子310とを備えている。ブリッジ素子310は、アライメント維持素子であり、半導体素子300をマザーウエハ320に対して接続し、オプションとして一体に接続する。一実施形態では、印刷可能半導体素子300及びブリッジ素子310は、マザーウエハ320から部分的に、又は、完全にアンダーカットされる。一実施形態では、印刷可能半導体素子300、ブリッジ素子310、及び、マザーウエハ320は、単一の連続する半導体構造のような単一構造である。

【0075】

[0100]印刷可能半導体素子300は、長手方向軸340に沿う長さ330で長手方向に延びており、幅350で延在している。長さ330は、ブリッジ素子310に接続される第1及び第2の端部400で終端している。ブリッジ素子310は、長さ360で延びており、幅370で延在している。図1A及び図1Bに示す実施形態では、ブリッジ素子が印刷可能半導体素子300の端部400の全体の幅及び/又は断面積よりも小さい幅及び/又は断面積で接続している。図2A及び図2Bに示すように、ブリッジ素子310の幅370は、位置合わせ転写を容易にするために、印刷可能半導体素子300の幅350よりも小さい。また、半導体素子300は、ブリッジ素子310の露出外面の表面積よりも大きい表面積の露出外面を有する。本発明の一部の処理方法及び転写方法において、ブリッジ素子310及び印刷可能半導体素子300のこれら寸法特性は、印刷可能半導体素子300の高精度の位置合わせ転写、組み立て、及び/又は、集積化を容易にする。

【0076】

[0101]ブリッジ素子310によって行なわれる構造支持は、例えばエラストマスタンプ転写デバイスを使用するウエハ320からの転写前及び/又は転写中に、予め選択された空間的方位に半導体素子300を保持する。ブリッジ素子310の固定機能は、一つ以上の印刷可能半導体素子の相対位置、間隔、空間的方位が所望の機能デバイス、及び/又は、回路構造に対応する多くの製造用途において望ましい。ブリッジ素子の物理的寸法、空間的方向、及び幾何学的形状は、半導体素子300を転写デバイスとの接触時に切り離せるように選択される。幾つかの実施形態において、切り離しは、例えば図2B及び図2Bに示す破線に沿う破断によって達成される。一部の用途においては、ブリッジ素子310を破断するために必要な力が十分に小さく、それにより、転写中に半導体素子300の位置及び空間的方位が実質的に乱されないことが重要である。

【0077】

[0102]ブリッジ素子又はブリッジ素子の任意の組み合わせの空間的配置、幾何学的形状、構成、及び物理的寸法は、本発明では、高精度の位置合わせ転写を行なうように選択される。図2C及び図2Dは、印刷可能半導体素子をマザーウエハに対して接続するブリッジ素子の画像を示している。図2は、印刷可能シリコン素子と、印刷可能素子をマザー(SOI)ウエハに対して接続する(狭い)ブリッジ素子とを示している。印刷可能半導体素子及びブリッジ素子の幾何学的形状は、SF6エッチングによって規定される。図2Cに示すように、印刷可能半導体素子及びブリッジ素子は、丸みを帯びた角部を有することが確認される。これらの角部の丸み及びこれらの素子の全体の幾何学的形状は、PDMS転写デバイスで印刷可能半導体素子を切り離す能力を低下させる。また、図2Dは、印刷可能シリコン素子及び印刷可能素子をマザー(SOI)ウエハに対して接続する(狭い)ブリッジ素子を示している。幾何学的形状は、高温KOH異方性エッチングによって形成されている。図2Dに示すように、印刷可能半導体素子及びブリッジ素子は、鋭い角部を有するのが確認される。これらの角部の鋭さは、明確な破壊点で応力を集中させ、したがって、PDMS転写デバイスでこれらの素子を切り離す能力を高める。

【実施例1】

【0078】

プラスチック基板上のフレキシブルトランジスタ、ダイオード、及び回路におけるアライメントされたGaAsワイヤの印刷配列

【0079】

[0103]フォトリソグラフィ及び異方性化学エッチングの使用によって高品質な単結晶ウエハから形成される集積オーム接点を有するGaAsワイヤのアライメントされた配列は、フレキシブルプラスチック基板上のトランジスタ、ショットキーダイオード、論理ゲート、及び、より一層複雑な回路のための将来有望な種類の材料を与える。これらデバイスは、優れた電子的特性及び機械的特性を示し、これらの双方の特性は、マクロエレクトロニクスと称されることの多い新たな分野の低コストな大面積フレキシブルエレクトロニクスにとって重要である。

【0080】

[0104]単結晶無機半導体のミクロンワイヤ及びナノスケールワイヤ、リボン、プレートレット等は、多くの用途で使用できる機能デバイス(例えば、光学素子、オプトエレクトロニクス、エレクトロニクス、センシング等)のための魅力的な構成要素である。例えば、「ボトムアップ」手法によって合成されたSiナノワイヤは、Langmuir/Blodgett技術(又はマイクロ流体工学)を使用してアライメント配列へと組み付けることができ、プラスチック基板上のフレキシブル薄膜トランジスタ(TFT)のためのトランスポートチャネルとして使用することができる。異なる手法では、約100nmの厚さ及び数ミクロン〜数百ミクロンの範囲の幅を有するリボンの形態を成すSi(微細構造シリコン;μs−Si)のマイクロ/ナノスケール素子は、「トップダウン」手法にもかかわらず、高品質な単結晶バルクソース(例えば、シリコンオンインシュレータ、SOIウエハ、又は、バルクウエハ)から形成することができる。この種の材料を使用して、300cm2V−1s−1程度のデバイス移動度を有するプラスチック上のフレキシブルTFTを製造することができる。高い品質のウエハベースの原材料(良好に規定されたドーピングレベル、ドーピングの均一性、低い表面粗さ、表面欠陥の密度に関して)は、同様に良好な特性を有するシリコンベース半導体材料をもたらし、信頼できる高性能デバイス動作にとって有利である。「トップダウン」製造プロセスも魅力的である。その理由は、この製造プロセスは、最終的な(例えば、プラスチックあるいは他のもの)デバイス基板への「乾式転写印刷」中にウエハレベルで形成された高度に順序付けられた組織ナノ/微細構造を保つ可能性をもたらすためである。Siを用いると高い性能が可能であるが、例えばGaAsを用いると、約8500cm2V−1s−1というその高い固有の電子移動度に起因して、更に良好な特性(例えば、動作速度)が得られる。先の研究は、「トップダウン」製造ステップを用いて、GaAsウエハから三角形断面を有するナノ/マイクロワイヤを、異方性化学エッチングを使用して形成するための技術を明らかにしている。これらのGaAsワイヤがウエハ上に依然として拘束されている間に当該GaAsワイヤ上にオーム接点を形成し、次いで、それらをプラスチック基板へ転写印刷することにより、機械的に可撓性の金属半導体電界効果トランジスタ(MESFET)が優れた特性をもって形成される。これらのトランジスタは、ギガヘルツ範囲で1の小さい信号利得を示す。この例は、組み立て/集積方法として転写印刷を用いて、インバータや論理ゲートのような機能回路の種々の基本ユニットを、これらタイプのMESFET及びGaAsワイヤベースのダイオードを能動部品として使用して、プラスチック基板上に形成できる能力を明らかにしている。これらタイプのシステムは、可動アンテナのための大面積電子回路、構造ヘルスモニタ、及び他のデバイス、軽量プラスチック基板上の高速高性能フレキシブルデバイスに対する厳しい要件を有する他のデバイスにおいて重要である。

【0081】

[0105]図3の(a)は、GaAsトランジスタ、ダイオード、論理ゲートをプラスチック上に形成するための主要なステップを示している。基本的な手法は、バルク単結晶GaAsウエハから高純度且つ周知のドーピングプロファイルを有するマイクロ/ナノワイヤを形成するための「トップダウン」製造技術に依存している。オーム接点は、ワイヤを製造する前にウエハ上に形成されるものであり、120nm AuGe/20nm Ni/120nm Auから成り、(100)半絶縁GaAs(Sl−GaAs)基板上のn−GaAsの150nmエピタキシャル層上に堆積され、(N2を流した状態で石英チューブ内において450℃で1分間)アニールされる。接点ストライプは、(0−1−1)結晶方位に沿って位置しており、2μmの幅を有する。トランジスタの場合には、オームストライプ間の隙間がチャネル長さを規定する。フォトリソグラフィ及び異方性化学エッチングは、三角形断面(図3の(b)の挿入画)及び約2μmの幅を有し、且つ、ウエハに接続する端部(図3の(b))を有するGaAsワイヤの配列を形成する。これらの接続は、各マスクのレイアウト(すなわち、フォトレジストパターン)によって規定されるように、良好に規定された方向及び空間的位置をもつワイヤを維持するための「アンカー」としての機能を果たす。エッチングマスクを除去し、Ti(2nm)/SiO2(50nm)の二重層を堆積させると、転写印刷のためのワイヤの表面が形成される。三角形の断面により、ワイヤの表面上のTi/SiO2膜はマザーウエハ上の膜に接続せず、したがって、転写印刷の歩留まり促進を確実にする。僅かに酸化されたポリ(ジメチルシロキサン)(PDMS)スタンプをウエハの表面上に積層すると、PDMSスタンプの表面と新たなSiO2膜との間で縮合反応により化学結合が引き起こされる。これについては、図3の(a)の一番上のフレームを参照されたい。PDMSスタンプを剥離すると、ワイヤがウエハから引き離され、これらワイヤがスタンプに結合されたままの状態となる。この「インク」スタンプを液体ポリウレタン(PU)の薄層でコーティングされたポリ(エチレンテレフタレート)(PET)シートに接触させて、PUを硬化させ、スタンプから剥離した後、1:10HF溶液中でTi/SiO2層を除去すると、図3の(a)の真中のフレームに示すように、GaAsワイヤの順序付けられた配列がPU/PET基板上に残る。Ti/SiO2膜は、GaAsワイヤをPDMSに対して結合するための接着層としての機能を果たすだけでなく、処理中に(例えば溶媒及びPUによる)想定し得る汚染物からGaAsワイヤの表面も保護する。

【0082】

[0106]この形式では、ワイヤの汚れのない露出した表面及びオームストライプは、ワイヤ上に集積されたオーム接点を接続するソース電極及びドレイン電極(250nmAu)を形成するために、更なるリソグラフィ処理及びメタライゼーションに晒される。トランジスタでは、これらの電極がソース及びドレインを形成し、ダイオードでは、これらの電極がオーム電極をとなる。ワイヤの露出部分上にフォトリソグラフィ及びリフトオフによって形成される接点(150nm Ti/150nm Au)は、これらがプラスチック基板と一体化される一方、ダイオード用のショットキー接点及びMESFET用のゲート電極を形成する。プラスチック基板上での全ての処理は、110℃を下回る温度で行なわれる。熱膨張係数の不一致又は他の想定し得る効果に起因する基板からのGaAsワイヤの剥離は、全く観察されなかった。トランジスタでは、ゲート電極の幅は、動作速度を制御する重大な寸法である。ソースとドレインとの間でのこの電極の位置は、この作業においては比較的重要ではない。低い位置合わせ精度に対するこの許容範囲は、セルフアライメントされない高速MOSFET(金属酸化膜半導体電界効果トランジスタ)型デバイスでは存在しないものであり、精密な位置合わせが処理中にプラスチックに起こり得る僅かな制御されない変形のために困難か又は不可能なことの多いプラスチック基板上で、高速動作を確実に達成するためには極めて重要である。適切な幾何学的構成で複数のトランジスタ及びダイオードを互いに接続すると、機能的な論理回路が形成される。図3の(a)の方式はNORゲートを示している。

【0083】

[0107]走査型電子顕微鏡(SEM)画像(図3の(c))は、トランジスタの半導体部品を形成する10本の平行なワイヤを示している。このデバイスのチャネル長及びゲート長はそれぞれ、各々50μm及び5μmである。これらの幾何学的構成は、簡単な集積回路、すなわち、論理ゲートを形成するために使用される。ソース電極とドレイン電極との間の隙間内のTi/Auストライプは、n−GaAs表面を有するショットキー接点を形成する。この電極は、ソースとのドレインとの間での電流の流れを変調するためのゲートとしての機能を果たす。ダイオード(図3の(d))は、一端にオームストライプを有し他端にショットキー接点を有するワイヤを使用する。図3の(e)及び図3の(f)は、PET基板上のGaAsトランジスタ、ダイオード、及び簡単な回路の集まりの画像を示している。図3の(f)では、回路を有するPETシートはホワイトマーカーの軸の周りで曲げられており、このことは、これら電子ユニットの可撓性を示している。

【0084】

[0108]プラスチック上のワイヤベースMESFET(図3の(c))のDC特性は、ウエハ上に形成されるワイヤベースMESFETと同じ定性的挙動(図4の(a))を示す。ソースとドレインとの間の電流(IDS)は、ゲートに対して印加されるバイアス(VGS)によって十分に変調される。すなわち、IDSはVGSの減少に伴って減少する。この場合には、負のVGSは、チャネル領域内の有効キャリア(すなわち、n−GaAsのための電子)を奪い、チャネル厚を減少させる。VGSが十分に負になると、空乏層がn−GaAs層の厚さと等しくなり、ソースとドレインとの間での電流の流れが途切れる(すなわち、IDSがほぼゼロになる)。図4の(a)に示すように、IDSは、VGSが−2.5V未満のときにほぼゼロまで降下する。ドレイン−ソース電圧(VDS)が0.1Vのとき(すなわち、直線領域)のピンチオフ電圧(すなわち、ゲート電圧VGS)は2.7Vである。飽和領域(VDS=4V)において、このトランジスタの伝達曲線を図4の(b)に示す。ON/OFF電流比及び最大相互コンダクタンスは、図4の(b)から、各々約106μS及び約880μSであるものと求められる。全体のソース−ドレイン電流は、ワイヤの数(すなわち、有効チャネル幅)及びソースとドレインとの間の距離(すなわち、チャネル長さ)の関数である。一定のチャネル幅では、短いチャネルを有するトランジスタは比較的高い電流を供給することができる。例えば、VGS=0.5VでVDS=4Vのときの飽和IDSは、50μmのチャネル長を有するトランジスタでの1.75mAから、25μmのチャネル長を有するトランジスタでの3.8mAまで増大する(図4の(c))。短いチャネルを有するトランジスタは特定の用途において高電流を供給することができるが、電流を完全に途切れさせることは難しいため、ON/OFF電流比は減少する傾向にある。図4の(c)に示すように、25μmのチャネル長を有するトランジスタのIDSは、VGSが−5Vの場合であっても依然として数マイクロアンペア程度である。

【0085】

[0109]プラスチック上のGaAsワイヤショットキーダイオードは、整流器の典型的な挙動を示す(図4の(d))。すなわち、順方向バイアス電圧(V)の増大に伴って順方向電流(I)が急速に増大し、一方、逆方向電流は、逆バイアスが5V程度の大きさのときであっても小さく保たれる。これらのショットキーダイオードのI−V特性は、熱イオン放射モデルによって記述することができ、V>>3kT/qのときに以下のように表現される。

【数1】

この場合、以下の通りである。

【数2】

ここで、Jは、印加バイアス電圧(V)での順方向ダイオード電流密度を表わしており、kはボルツマン定数であり、Tは絶対温度(すなわち、実験では298K)であり、ψBはショットキーバリア高さであり、A**はGaAsにおける有効リチャードソン定数(すなわち、8.64A・cm−2・K−2)である。InJとバイアス(V)との間の関係をプロットすることにより(挿入図)、直線(一次)関係(挿入図の直線)の切片及び傾きから飽和電流J0及び理想ファクタnが決定される。ψBの量は方程式(2)を用いて概算される。ψB及びnはショットキー界面特性の評価基準として一般に使用される。これらの双方は、金属とGaAsとの間の界面帯電状態に大きく依存している。すなわち、帯電状態の増大は、ψBの減少及びn値の増大を引き起こす。この作業で製造されるダイオードの場合、ψB及びnは、図4の(d)の挿入画から、各々512meV及び1.21であると求められる。これらデバイスは、ウエハ上に形成されるダイオードと比べて幾分低いショットキーバリア(約800meVに対して512meV)及び大きい理想ファクタ(約1.10に対して1.21)を有する。

【0086】

[0110]これらGaAsワイヤデバイス(すなわち、MESFET及びダイオード)は、複雑な回路のための論理ゲート中に組み込むことができる。例えば、異なる飽和電流を有するチャネル長が異なる二つのMESFETを接続すると、インバータ(論理NOTゲート)が形成される(図5の(a)及び図5の(b))。負荷(上)及びスイッチングトランジスタ(下)は、100μm及び50μmのチャネル長を各々有し、150μmのチャネル幅及び5μmのゲート長を有する。この構造により、スイッチングトランジスタの飽和電流の約50%の飽和電流が負荷トランジスタから得られ、それにより、負荷ラインは、ターンオン電圧が小さい線形領域でスイッチングトランジスタのVGS=0曲線と交わる。インバータは飽和領域で測定される。すなわち、Vddは5Vでバイアスされる。大きなマイナス電圧(論理0)がスイッチングトランジスタ(140)のゲートに対して印加されて(Vin)、当該スイッチングトランジスタがOFFされると、出力ノードの電圧(Vout)がVdd(論理1、高いプラスの電圧)と等しくなる。これは負荷トランジスタが常にONだからである。Vinが増大すると、スイッチングトランジスタがONとなり、スイッチングトランジスタ及び負荷トランジスタの双方を通じて大きな電流が供給される。スイッチングトランジスタが完全にONになると、すなわち、Vinが大きなプラス電圧(論理1)になると、Voutが低いプラス電圧(論理0)まで減少する。図5の(c)は伝達曲線を示している。インバータは、1よりも高い最大電圧利得(すなわち、(dVout/dVin)max=1.52)を示す。Voutの論理状態は、ショットキーダイオードから成るレベルシフトブランチを加えることにより、更なる回路集積に適する電圧へとシフトされる(図3の(d)に示すように)。

【0087】

[0111]このタイプの幾つかのデバイスを並列に又は直列に組み合わせると、NORゲートやNANDゲートのような更に複雑な論理機能が得られる。図6の(a)及び図6の(b)に示すNOAゲートにおいては、並列の二つの同じMESFETがスイッチングトランジスタとしての機能を果たす。高いプラスの電圧(論理1)を印加することによっていずれかのスイッチングトランジスタ(VA又はVB)をONすると、負荷トランジスタのドレイン(Vdd)を通じて大きな電流をグランド(GND)へと供給することができ、それにより、低いレベル(論理0)の出力電圧(Vo)を得ることができる。双方の入力が高いマイナス電圧(論理0)にある場合にのみ、高いプラスの出力電圧(論理1)を得ることができる。NORゲートの入力に対する出力の依存度を図6の(c)に示す。NANDゲートの構造(図6の(d)及び図6の(e))では、電流は、高いプラス電圧(論理1)を印加することにより双方のスイッチングトランジスタがONにされる場合にのみ、全てのトランジスタにわたって大きい。この構造では、出力電圧が比較的低い値(論理0)を示す。他の入力の組み合わせを用いるとトランジスタを通じて電流が流れなくなり、Vddに相当する高いプラスの出力電圧(論理1)が得られる(図6の(f))。このタイプの論理ゲート及び/又は他の受動素子(例えば、レジスタ、キャパシタ、インダクタ等)を更に集積させると、プラスチック上に高速大面積電子システムを設けられる見込みが与えられる。

【0088】

[0112]要約すると、高品質なバルク単結晶ウエハを用いた「トップダウン」処理を使用して製造される集積オーム接点を有するGaAsワイヤは、高性能「印刷可能」半導体材料を与え、フレキシブルプラスチック基板上のトランジスタ、ダイオード及び集積論理ゲートへの比較的容易な経路を与える。高温処理ステップ(例えば、オーム接点の形成)をプラスチック基板から分離すること、及び、GaAsワイヤの良好に順序付けられた配列を転写印刷するためのPDMSスタンプを使用することは、本明細書で説明する手法の重要な特徴である。半導体としてGaAsワイヤを使用することは、動作速度に対する要件が厳しい大面積印刷エレクトロニクスにとって魅力的である。その理由は、(i)GaA

sが高い固有の電子移動度(約8500cm2V−1s−1)を有し、従来の高周波回路において確立された用途を有するためであり、(ii)MESFETがゲート誘電体を必要としないため、GaAsを用いて形成されたMESFETがMOSFETよりも簡単な処理を与えるためであり、(iii)GaAsMESFETがセルフアライメントされないMOSFETで起こる寄生オーバーラップキャパシタンスをもたないためであり、(iv)大面積プラスチック基板上で容易に得ることができる分解能及びパターニング位置合わせの適度なレベルであっても、GaAsMESFETにおける高速動作が可能だからである。GaAsの(Siと比べた)比較的高いコスト、及び、GaAsワイヤデバイスを用いて相補回路を形成することの困難性が欠点である。それにもかかわらず、比較的容易に高性能トランジスタ及びダイオードをプラスチック基板上に形成できること、及び、これらの部品を機能回路へ組み込むことができることは、機械的な可撓性、軽量構造、及び、大面積印刷のような処理との適合性が必要とされる電子システムへのこの経路においてある展望を示している。

【0089】

[0113]実験セクション:GaAsウエハ(IQE社、ペンシルベニア州のベスレヘム)は、高真空チャンバ内で分子ビームエピタキシャル(MBE)蒸着によって(100)半絶縁GaAsウエハ上に成長したエピタキシャルSi−ドープn型GaAs層(キャリア濃度が4.0×1017cm−3)を有する。リソグラフィプロセスは、AZフォトレジスト(ポジ画像化及びネガ画像化の各々のためのAZ5214及びAZnLOF2020)を使用し、プラスチック基板、すなわち、硬化ポリウレタン(PU、NEA 121、ニュージャージー州CranburyのNorland Producs社)の薄層でコーティングされたポリ(エチレンテレフタレート)(約175μm厚のPET、Mylar膜、カリフォルニア州パロアルトのSouthwall Technologies)シートと適合する温度(<110℃)で行なう。フォトレジストマスクパターンを有するGaAsウエハを、氷水槽内で冷却されたエッチング液(4mL H3PO4(85重量%)、52mL H2O2(30重量%)、48mL脱イオン水)中で異方性エッチングする。全ての金属を、電子ビーム蒸着器(Temescal)によって約4Å/sの速度で蒸発させる。蒸発は、50nm厚の金属が堆積されると、サンプルを(5分間)冷却してプラスチック基板が溶けるのを防止するべく停止させる。サンプルが冷却された後、更に多くの金属を堆積させるために蒸着(蒸発)/冷却サイクルを繰り返す。

【実施例2】

【0090】

フレキシブルプラスチック基板上の機械的に可撓性のトランジスタにおけるギガヘルツ動作

【0091】

[0114]バルクウエハから形成されたオーム接点を有するGaAsワイヤと、ソフトリソグラフィ転写印刷技術と、最適化されたデバイス構造とを組み合わせて使用すると、個々のデバイス速度がギガヘルツ範囲で、高度な機械的曲げ性を有する機械的に可撓性のトランジスタを低コストプラスチック基板上に形成することができる。本明細書に開示する手法は、適度なリソグラフィパターニング分解能及び位置合わせ精度をもって製造される簡単なレイアウトの材料を組み入れている。この実施例は、高性能トランジスタの電気的及び機械的な特性について説明する。結果は、高速通信及び計算、並びに、新規な種類の大面積電子システム(「マクロエレクトロニクス」)含むがこれらに限定されない特定の用途において重要である。

【0092】

[0115]高移動度半導体で形成された大面積フレキシブル電子システム(すなわち、マクロエレクトロニクス)は、これらタイプの回路の幾つかの潜在的な用途が高速通信及び/又は計算能力を必要とするため、興味深いものである。アモルファス/多結晶酸化物やカルコゲニド、多結晶及び単結晶シリコンナノワイヤ、並びに微細構造リボンのような種々の無機材料を用いて形成される可撓性の薄膜トランジスタ(TFT)は、多結晶有機薄膜の移動度(一般に、<1cm2V−1s−1)よりも相当に高い移動度(10〜300cm2V−1s−1)を示す。先の研究は、非常に高い固有電子移動度(約8500cm2V−1s−1)を有する単結晶GaAsのワイヤ配列が金属半導体電界効果トランジスタ(MESFET)の幾何学的構造においてTFTの用のトランスポートチャネルとしての機能を果たすことができることを明らかにした。この実施例は、最適化された構造を用いて、同様のデバイスが、適度なリソグラフィ分解能及び良好な曲げ性であっても、GHz範囲の周波数で動作できることを示している。特に、実験結果によれば、プラスチック基板上のGaAsワイヤベースのMESFETは、約200nm厚の基板が使用されるときに約1cmまでの曲げ半径において僅かな電気的特性の変化を伴って、ゲート長が2μmのトランジスタにおける1.5GHzよりも高いカットオフ周波数を示す。デバイス挙動の簡単なシミュレーションは実験観察と良く一致し、また、S帯域(5GHz)における動作周波数が得られる。

【0093】

[0116]基本的な製造指針は、他の部分で説明した方法と同様であるが、高速動作を可能にする最適化されたデバイス構造及び処理方法を用いている。ここでは、集積オームストライプ(N2雰囲気中で1分間にわたって450℃で、120nm AuGe/20nm Ni/120nm Auをアニールすることによって形成されたもの)を有するGaAsワイヤ(約2μm幅)の配列を、フォトリソグラフィ及び異方性化学エッチングにより、150nm n−GaAsのエピタキシャル層を有する(100)半絶縁GaAs(Sl−GaAs)ウエハから形成する。Ti(2nm)/SiO2(50nm)の薄い二重層を、アンダーカットされたGaASワイヤ上に堆積して、接着層としての機能を果たさせ、転写印刷プロセスを容易にし、また、本プロセスに関与する有機物(主に、スタンプの表面から移る有機物)による汚染からワイヤの平坦な表面及びオーム接点を保護する。この層を、サンプルを1:10HF溶液中に浸漬することによって、除去し、一連のステップでのデバイス製造のためにGaAsワイヤのクリーンな表面を露出させる。また、このTi/SiO2層の(本発明者の先の作業における転写印刷において接着層として使用されるフォトレジスト層の厚さと比較して)薄い厚さによって、プラスチックポリ(エチレンテレフタレート)(PET)シートの比較的平坦な表面が得られ、この表面上に、スピンキャストされたポリウレタン(PU)の薄層を用いてGaAsワイヤ配列を印刷する。高い表面平坦性により、幅狭のゲート電極を、それらの長手方向に沿ってクラックを生じさせることなく堆積させることができ、それにより、デバイスの動作速度を高めるための有効なルートを与えることができる。

【0094】

[0117]PET基板上に得られるMESFET(図7の(a)に示すゲート長が2μmの典型的なトランジスタのSEM画像参照)は、マザーウエハ上に形成されたトランジスタの輸送特性と同様のDC輸送特性を示す。図7の(b)は、ゲート長が2μmのデバイスについて、ソース・ドレイン間の電流(IDS)を、ゲート電圧(VGS)(挿入図)の関数として、また、異なるVGSにおけるソース/ドレイン電圧の関数として示している。VDSが0.1Vのとき(すなわち、線形領域)のピンチオフ電圧は−2.7Vである。多くのデバイスに関する平均測定値から決定されるON/OFF電流比は約106である。デバイスは極僅かなヒステリシスを示し(挿入図)、このことは高速応答において特に重要である。デバイスは良好なデバイス間均一性を示す。表1は、チャネル長さが50μmで、ゲート長が異なるMESFETの統計結果(デバイス数>50)を示している。DC特性は、大きなゲート長を有するデバイスが幾分低いON/OFF比を示す点を除き、ゲート長とは略無関係である。しかしながら、ゲート長は、以下に示す動作周波数を決定する際に重大な役割を果たす

【表1】

【0095】

[0118]図8の(a)の挿入画は、マイクロ波検査用に形成されたデバイスのレイアウトを示している。検査構造の各ユニットは、一つの共通のゲートを有し、且つ、ゲート長が2μmでチャネル長が50μmの二つの同じMESFETと、RFプローブのレイアウトと一致するように構成されたプロービングパッドとを有している。測定時には、ドレイン(D)端子が(ソース(S)に対して)4Vに保たれ、また、ゲート(G)は、50Ωで224mVの等価電圧振幅を有する0dBmのRF電源と結合された0.5Vのバイアスによって駆動される。測定は、エラー修正用のWinCal3.2によりCascadeMicrotech 101−190B ISS基板(レーザトリミングされた金パターンで覆われたセラミックチップの断片)に対して標準的なSOLT(Short−Open−Load−Through)技術を用いて50MHzから1GHzまでの範囲で較正されたHP8510C Network Analyzerを使用して行なわれる。すなわち、短絡較正は完全な短絡であると考えられ、また、開路較正は完全な開放であると考えられる。更なる組み外しを伴うことなく較正が行なわれるため、測定の基準面は入力プローブと出力プローブとの間に設定される。すなわち、接触パッドの寄生成分が測定に含められる。しかしながら、接触パッドに対するこれらの寄生成分の影響は、1GHzの周波数を有するRF信号の波長が300mmであるのに対して接触パッドの長さが200μmであるという事実を考慮すると無視できる。接触パッドは波長の1/1500にすぎないため、インピーダンス変換のその影響は無視できる。

【0096】

[0119]デバイスの測定されたSパラメータから小信号電流増幅率(h21)を抽出することができる。この量は、入力RF信号の周波数に対する対数依存性を示している(図9の(a))。単位電流利得周波数(unity current gain frequency)(fT)は、短絡電流利得が1になるときの周波数として規定される。この量は、20dB/decadeラインの最小二乗適合によって図9の(a)の曲線を外挿し、且つ、そのx切片の場所を見つけることによって決定できる。このようにして決定された値はfT=1.55GHzである。このデバイスは、本発明者の知る限りでは、最も速い機械的に可撓性のプラスチック上のトランジスタであり、ギガヘルツ範囲のfTを有する第1のものである。また、測定されたDCパラメータと電極間の計算された容量とを使用して、小信号等価回路モデルにしたがってGaAs MESFETのRF応答を評価した。シミュレーション結果からのプロットは、fT=1.68GHzをもたらす実験結果と良く一致する。また、このモデルは、異なるゲート長を有するトランジスタにおいて良好に機能し、例えば、ゲート長が5μmのMESFETの実験のfT(730MHz)は、そのシミュレートされた量(795MHz)に近い(図9の(b)。このモデルにおいては、MESFETの固有パラメータだけが考慮されている。これは、外因性パラメータ(すなわち、プロービングパッドに関連するインダクタンス及び抵抗)が無視できると見なされるためである。相互コンダクタンス(gm)、出力抵抗(RDS)、及び、充電抵抗(Ri:チャネル上の電荷がVDSの変化に同時に応答できないという事実を考慮したもの)は、DC測定から得られる。MESFETに関連する固有キャパシタンスは、空乏層、エッジフリンジング、幾何学的フリンジングキャパシタンスからの寄与を含む。これらは各々、個々のGaAsワイヤの幅の総和に等しいチャネル幅を有する従来のデバイスにおける標準的な方程式を使用して計算される。空乏層キャパシタンスは、ゲート長(LG)、有効デバイス幅(W)、及び、以下の空乏高さをもって特徴付けられる。

【数3】

この方程式では、空乏層が平行板コンデンサとして機能すると仮定して、

【数4】

である。エッジフリンジングキャパシタンス及び幾何学的フリンジングキャパシタンスは各々以下によって決定される。

【数5】

【数6】

ここで、150μm及び200μmは、ソースパッド又はドレインパッドの何れかの幅及び長さである。K(k)は第1種の楕円積分であり、

【数7】

【数8】

であり、CGS、すなわち、ゲートとソースとの間のキャパシタンスは、三つの全ての種類のキャパシタンスを含んでおり、一方、CDS及びCDGは、エッジフリンジングキャパシタンス及び幾何学的フリンジングキャパシタンスだけを含でいる。Cedge及びCgeometricの寄与は、殆どの場合、シミュレーション結果に対する著しい影響無く無視し得る。これは、それらの寄与がゲート長に適したCdepletionよりもかなり小さいためである。このモデルは、ゲート長に伴うfTの変化を含むプラスチック上のワイヤ配列デバイスの挙動を考慮している。図8の(c)は、ゲート長が異なり、且つ、チャネル長が50μmのGaAsワイヤMESFETの測定された(記号)fTと計算された(破線)fTとを比較している。このモデリングは、ゲート長を減少させることによって、或いは、GaAsマザーウエハ中の層の構造を更に最適化することによってfTを大きく増大させることができることを示唆している。

【0097】

[0120]本発明者は、ゲート長が15μmのワイヤベースのMESFETに対する引張り歪みの影響の初期測定を報告した。この実施例では、圧縮及び引張りの双方における高速デバイスの破壊点までの挙動について検討する。本測定は、曲率半径が異なる凹形状及び凸形状への基板の曲げ(図9の(a)参照)に応じた全DC電気特性から成る。曲げ半径は、曲げられたサンプルの側面画像の幾何学的なフィッティングによって得られる。凹状及び凸状の曲げ面は、デバイス上に引張り歪み(プラス値が割り当てられる)及び圧縮歪み(マイナス値が割り当てられる)をもたらす。図8の(a)の挿入画に示すデバイスと同様のデバイスを、性能に対する曲げ誘発歪みの影響を評価するために使用している。飽和電流(すなわち、VDS=4V、VGS=0V)は、引張り歪みの0.71%(この研究で使用された200μm厚基板における14mmの曲げ半径に対応する)への増大に伴って約10%増大し、また、圧縮歪みの0.71%への増大に伴って約20%減少する(図9の(b))。基板が何れかの方向に曲げられた後に解放されると電流が回復するが、これは、プラスチック基板及びデバイスの他の部品の変形が、この形態では弾性的であることを示唆している(PET及びPUは、約2%の歪みで塑性変形すると思われる)。(100)GaAsウエハ上のGaxIn1−xAs又はGaxIn1−xAsから成る歪みエピ層に関する研究は、二軸応力及び外的に加えられた一軸応力(この実施例と同様のケース)がバンドギャップエネルギの著しい変化及びエピ層における価電子帯分裂をもたらし得ることを明らかにしている。引張り歪みは、バンドギャップエネルギを減少させ、それにより、全体のキャリア濃度(電子及び正孔)を増大させ、電流を増大させ。これに対し、圧縮歪みは、バンドギャップエネルギを増大させて電流を減少させる。これらの現象は、本発明者のデバイスの観察と一致する。SEM顕微鏡を用いた結合プロセスのIn Situイメージングは、GaAsワイヤのいずれもが<±0.71%の歪みで破壊しないことを裏付けている。約1%を越える引張り歪みでは、一部のワイヤの破断(又は、ゲート電極のクラッキング)に起因してデバイス劣化が起こる。ここで使用したワイヤよりもかなり幅広い(例えば、10μm幅)ワイヤの場合、ワイヤは、プラスチックから剥離し、それらの比較的高い曲げ剛性により破断することなく引張り曲げ応力が解放される。

【0098】

[0121]曲げ歪みは飽和電流を20%未満だけ変化させるので、ON/OFF比の変化は、主に、OFF電流の変化によって決定される。価電子帯における正孔濃度の変化や、歪みによって引き起こされるn−GaAs層の表面欠陥及び転位数は、トランジスタのOFF電流の変化に寄与する。引張り歪み及び圧縮歪みはいずれも、転位数及び表面欠陥を増大させる可能性があり、それにより、デバイスのOFF電流を増大させる。引張り歪みは、OFF電流を増大させる更なる電子及び正孔を形成する。一方、圧縮歪みは、正孔濃度を下げる。その結果、引張り時のMESFETのOFF電流は、歪みのないデバイスのそれよりも高くなると思われる。圧縮歪みは、デバイスのOFF電流に対して大きな影響を与えない。したがって、対応するON/OFF電流比は、引張りに伴って減少し、圧縮に伴って略同じ値を維持する。図9の(c)は、前述した説明との質的な一致を示す、歪み時の飽和領域における測定されたON/OFF電流比の依存度を与えている。

【0099】

[0122]要約すると、この実施例の結果は、曲げに伴う表面歪み(0.71%程度の引張り及び圧縮)がこの変更された処理によって形成されるMESFETの性能を著しく低下させないことを示している。更に重要なことには、サンプルのその曲げ状態を解放すると、デバイス性能はその当初の状態へ戻る。これらの観察は、PU/PET基板上のGaAsワイヤベースのMESFETがマクロエレクトロニクスの多くの想定される用途の要件を満たす機械的特性を有することを示している。また、これらのタイプのTFTは、RF通信デバイスに適しており、且つ、機械的な可撓性、軽量構造、及び、大面積印刷のような処理との適合性が要求される他の用途に適した速度に近づく高い速度を示す。従来の集積回路におけるSiと比べたGaAsの欠点の幾つか(すなわち、高いウエハコスト、信頼できるコンプリメンタリ回路を形成できないこと、機械的な脆弱性等)は、薄い、屈曲可能な、適度な密度のクラスのワイヤ又はリボン及びこの研究の焦点となる大面積回路を使用するデバイスにおける重要性を減らした。

【実施例3】

【0100】

バルクウエハから得られるシリコンの超薄リボンを使用する機械的に可撓性の薄膜トランジスタ

【0101】

[0123]この実施例は、バルクシリコン(111)ウエハのリソグラフィパターニング及び異方性エッチングによって形成された単結晶シリコンの薄い(サブミクロン)リボンのアライメントされた配列を使用する一種の薄膜トランジスタをもたらす。薄いプラスチック基板上に印刷されたこのようなリボンを組み込んだデバイスは良好な電気的特性及び機械的可撓性を示す。線形領域で評価される有効デバイス移動度は360cm2V−1s−1であり、ON/OFF比は>103である。これらの結果は、構造ヘルスモニタ、センサ、ディスプレイ及び他の用途のための大面積の高性能な機械的可撓性の電子システムへの低コストなアプローチへ向かう重要なステップを表わしている。

【0102】

[0124]限定関連特性及び幅広く使用できる形状因子は、エレクトロニクス、フォトニクス、マイクロ電気機械システム及び他の分野における新たな用途にとって興味深い低次元材料を形成する。例えば、プラスチック基板上に成形され、塗られ、又は、印刷されるマイクロ/ナノワイヤ、リボン又はチューブを使用して、高性能フレキシブル電子デバイス(例えば、トランジスタ、簡単な回路素子等)を構成することができる。薄い高アスペクト比の材料構造は、バルク状態で本質的に脆弱で壊れ易い材料製の単結晶半導体において曲げ性を可能にし、特定の構造形態では伸縮性を可能にする。その結果、これらのタイプの半導体は、通常はキャリア移動度に関して相当に低い性能を示す真空処理可能及び溶解処理可能なポリ/非結晶有機材料に対して興味深い代替物を与える。最近説明されたトップダウン手法は、材料のウエハベースソースから半導体ワイヤ、リボン、及び、シートを形成する。この手法は、得られる構造の幾何学的形状、空間的配置、ドーピングレベル、及び、材料純度にわたって高レベルの制御を行なう。しかしながら、この手法の経済的魅力は、特に大面積カバレージを求める用途においては、ウエハ(絶縁体上のシリコン、成長基板上のエピタキシャル層等)の単位面積当たりのコストによって制限される。

【0103】

[0125]この実施例では、異なる手法を報告する。特に、低コストバルクSi(111)ウエハから得られるサブミクロン厚のシリコンリボンのアライメントされた配列を使用する一種の薄膜トランジスタ(TFT)を提示する。始めに、これらの構造を形成して当該構造をエラストマスタンプによってプラスチック基板上に転写するための処理について説明する。また、リボンの形状、リボンの厚さ及び表面形態の構造的特性を提示する。これらの印刷されたリボンが形成されたショットキーバリアTFTに対して行なわれた電気測定値は、360cm2V−1s−1のn型電界効果移動度及び4000のON/OFF比を示す。

【0104】

[0126]図10は、Si(111)ウエハ(Montco社、n型、0.8−1.8Ωcm)の表面から薄い(<1μm)リボンを形成するトップダウン方法を示している。プロセスは近接場位相シフトフォトリソグラフィ13から始まり、その後、金属リフトオフ及びSF6プラズマエッチング(Plasmatherm RIEシステム、45秒間にわたり、40sccmSF6、30mTorr、200WRF電源)を行い、約1μm深さで且つ1μm幅の溝の配列をSi表面に形成する(図1の(a))。溝間の間隔はリボンの幅(一般的には10μm)を規定する。次に、100nmの熱酸化物を1100℃でウエハ上に成長させる。Ti/Au(3/30nm)の傾斜型電子ビーム蒸着によって行なう二つの金属堆積ステップによって、溝側面の部分的な被覆を行なう(図10の(b))。これらの傾斜型蒸着中に作られる「陰」はリボンの厚さを規定する。溝エッチングの状態、蒸着の角度、金属の流束のコリメーションの度合いが、この陰影付けの程度、したがって、リボンの厚さを制御する。次に、CF4プラズマエッチング(5分間にわたり、40sccmCF4、2sccmO2、50mTorrベース圧力、150WRF電源)によって、露出した酸化物を除去する。最後に、高温KOH溶液(質量比が3:1:1 H2O:KOH:IPA、100℃)によってリボンをアンダーカットする。エッチングフロントは、(111)平面を保ちつつ<110>方位に進み(図10C)、当初のウエハの大部分(75−90%)を覆う自立リボンを形成する。エッチングマスクは、各リボンを溝の端部でウエハに対して固定されたままの状態とするように設計されている(図12の(a)及び図12の(b))。このマスクを水中でKl/I2(2.67/0.67重量%)を用いて、その後HFにより除去すると、製造が完了する。このようにして形成されたリボンは、高価なシリコンオンインシュレータウエハを用いた前述の手法を使用して形成されるリボンと同様、薄く、平坦で、機械的に可撓性である5−7,11。原子間力顕微鏡検査(図11の(a))は、典型的なリボンにわたって厚さが約115〜約130nmの範囲であることを示している。これらの変動は、光学顕微鏡写真における僅かな色変化として現れている(図12の(e))。これらのリボンのうちの一つの下面の5×5μm部位のAFMにより測定された粗さは、図12の(b)に示されており、0.5nmである。この値は、上端の研磨された表面(0.12nm)よりも大きく、又、同じ方法によって測定されたSOIウエハから形成されたリボンの下面(0.18nm)よりも大きい。この粗さを低下させるための他の異方性エッチング液の使用も興味深い。厚さの源は、また、その程度までのものではなくとも、粗さは、部分的に溝内のエッジ粗さであり、このエッジ粗さは、傾斜型蒸着中に側面不動態化において粗さを引き起こす。側面の質を高めると、リボン厚の変動を抑えることができる。しかしながら、以下で示すように、良好な性能を有するトランジスタデバイスは、本明細書中で説明する処理を使用して製造されるリボンを用いて構成することができる。

【0105】

[0127]リボンは、図12に概略的に示すように、高歩留り(>95%)印刷プロセスによって他の(フレキシブルな)基板に対して転写することができる。印刷プロセスを行なうため、PDMSスタンプをウエハに対して重ね合わせ、その後、PDMSスタンプを急速に引き剥がして、リボンを回収する。このタイプのプロセスは、スタンプに対する接着の動力学的な制御に依存している。このように「インク付けされた」スタンプ(図12の(b)及び図12の(e))は、リボンを接触によって他の基板に対して印刷できる。ITOコーティングされた0.2nm厚のPET基板上に印刷されたリボンは、ゲート電極としてITOを有する高性能フレキシブルボトム−ゲートTFTをプラスチック上に形成するために使用できる。印刷の前にITOゲート上に堆積されたSU−8の層は、ゲート誘電体としての機能及びリボン転写を容易にするための接着剤としての機能を果たす。印刷中、リボンは硬化されていないSU−8中に沈み、それにより、リボンの上端が接着剤の表面と面一になり、その結果、リボンの底面とITOとの間に約2μmの誘電体が残る。フォトリソグラフィ(100μm長×100μm幅)及びHF/H2O2を用いるウェットエッチングによって形成された厚い(約0.2μm)Tiソース接点及びドレイン接点は、ソース電極及びドレイン電極のためのショットキーバリア接点を形成する。これらのボトム−ゲートデバイスは、特徴的なn型エンハンスメントモードMOSFETゲート変調を示す。トランジスタは約103のON/OFF比を得る。この場合、金属酸化膜半導体電界効果トランジスタの動作のための標準的な方程式を使用して決定されるデバイスレベル移動度は、約360cm2V−1s−1(線形)及び100cm2V−1s−1(飽和、Vd=5Vで評価される)程度の大きさの14である。リボン自体の移動度は、デバイスレベル移動度(440cm2V−1s−1線形及び120cm2V−1s−1飽和)よりも約20%高くなければならない。これは、これらのリボンがそれらの間の空間に起因してチャネルの約83%だけを満たすためである。リボンデバイスは、基板が適度な(15mm)半径まで曲げられるときには耐え抜くが、0.2mm厚基板における更に鋭い(5mm)曲げでは著しく劣化する。

【0106】

[0128]要約すると、この実施例は、バルクシリコン(111)ウエハから印刷可能な単結晶シリコンリボンを形成するための高歩留り製造方法を示している。製造後にバルクウエハの表面を再仕上げすると、複数の繰り返しが可能となり、それにより、1平方フィートの出発材料から数十あるいは数百平方フィートのリボンを形成することができる。プラスチック上にこれらのリボンから形成されたTFTは、高性能フレキシブル半導体としてのそれらの使用を示している。これらのデバイス及び当該デバイスを製造する方法は、大面積フレキシブルエレクトロニクスにおいてのみならず、3次元集積又は不均一集積を必要とするあるいは従来のシリコン微細加工手法を使用して得ることが難しい他の特徴を必要とする用途においても有用である。

【実施例4】

【0107】

プラスチック基板上の湾曲可能なGaN高電子移動度トランジスタ(HEMT)

【0108】

[0129]フレキシブルで大面積なエレクトロニクス、すなわち、マクロエレクトロニクスの新興分野内に包含される技術は、過去数年にわたって顕著な進歩を遂げてきており、幾らかの有力な民生用途及び軍事的用途で近い将来に商品化されるものと期待される。新規な形状因子を有するマイクロ電子回路は、これらのシステムの重要な部品であり、また、新たな製造方法−特に印刷−がこれらの電子回路を製造するためにおそらく必要とされる。このため、印刷可能な形態の半導体に対してかなりの注意が払われてきており、また、有機材料(例えば、ペンタセン、ポリチオフェン等)及び無機材料(例えば、ポリシリコン、無機ナノワイヤ)の双方が試験されてきた。この研究は、プラスチック基板上に集積されたデバイスに関して幾つかの有望な結果を示した。しかしながら、それらの現在の用途範囲は、これらの半導体から形成されるデバイスの固有の低い性能、例えばそれらの低い有効デバイス移動度及び動作周波数によって大きく制限された範囲である。本発明者は、従来の及び有機高分子基板の双方の基板上に非常に高性能のデバイスを形成することができる微細構造半導体(μs−Sc)と呼ばれる新たな形態の印刷可能な無機半導体を検討した。また、本発明者は、μs−Scを基本として、十分に開発されたデバイスを半導体ウエハ上に形成でき、その後、そのデバイスをそれらの性能を低下させることなくフレキシブル基板に対して転写できることを明らかにした。この手法は、高品質なウエハスケール半導体を利用する一方で、当該半導体を印刷ベースの製造方法に適合させる。これらの材料のうち、単結晶μs−GaNが最も興味深い。なぜなら、単結晶μs−GaNは、高い破壊電界(GaAsの0.4MVcm−1に対して3MVcm−1)、高い飽和キャリア速度(GaAsの107cms−1に対して2.5×107cms−1)及び良好な熱伝導率(GaAsの0.5Wcm−1に対して1.3Wcm−1)をもたらす幅広いバンドギャップ(GaAsの1.4eVに対して3.4eV)を含む優れた材料特性を有するためである。また、AlGaN/GaNヘテロ構造の形態の不均一集積は、高い伝導バンドオフセット及び1.0×1013cm−2の範囲にあるシートキャリア密度との圧電応答性を有するデバイスグレード材料もたらす。これらの魅力的な特性は、無線通信用の電子デバイス、フルカラー発光デバイス、及び、光電気システムのためのUV光検出器等の高周波及び高出力性能を必要とするのに適するGaNを形成した。

【0109】

[0130]AlGaN/GaN高電子移動度トランジスタ(HEMT)の最初のデモンストレーション以来、かなりの研究活動がこの分野に焦点を合わしてきた。これらの努力は、サファイア、SiC、Si及びAlNを含む様々な基板上に集積されるデバイスをもたらしてきた。この実施例では、フレキシブルAlGaN/GaNヘテロ構造高電子移動度トランジスタ(HEMT、図14に要約されるプロセスに示す)の製造について説明する。この場合、トランジスタは、処理された後、それらのSi(111)成長基板からコンタクト印刷ベースのプロトコルによってブラスチックシート上へと転写される。この研究は、ヘテロ構造III−V半導体材料に基づく高性能HEMTデバイスをプラスチック基板上へ集積するための処理の説明を提供する。

【0110】

[0131]図15は、HEMTデバイスの製造において使用されるステップを概略的に示している。このプロセスは、標準的なシーケンスフォトリソグラフィステップ及びリフトオフステップを使用して、バルクGaNヘテロ構造ウエハ上にオーム接点(Ti/Al/Mo/Au)を形成することから始まる(図15の(a))。次に、PECVD酸化物層及びCr金属を堆積させて、その後のドライエッチングのためのマスクとしての機能を果たさせる。Cr及びPECVD酸化物のフォトリソグラフィ及びエッチングは、その後の印刷のためのソリッドインクとしての機能を果たすGaNリボンにとって望ましい幾何学的形状を規定する(図15の(b))。上端のフォトレジストを剥ぎ取った後、ICPドライエッチングを使用して、露出したGaNを除去する(図15の(c))。Cr層は、このICPエッチングによって除去されるが、厚いPECVD酸化物層をGaNの上端に略無傷のまま残す。水酸化テトラメチルアンモニウム(TMAH)を用いる異方性ウェットエッチング(図15の(d))は、下側に位置するSiを除去し、GaNリボンをマザー基板から引き離す。この強力なアルカリエッチング中、PECVD酸化物は、オーム接点を劣化から保護するよう機能する。プラズマエッチングステップ及びウェットエッチングステップによって顕著に粗面化された残存するPECVD酸化物を、次いで、BOE(バッファード酸化物エッチング液)プロセスステップを使用して除去する。その後、新たな滑らかな犠牲シリコン酸化物層を、電子ビーム蒸着によってGaNリボンの上部に堆積させる。GaNリボンの印刷のため、ウエハをポリジメチルシロキサン(PDMS)スラブと接触させた(図15の(e))。また、マザー基板からの高速除去時に、PDMSに対するμs−GaNの完全な転写を得る。次いで、この「インク付けされた」スラブを、ポリウレタン(PU)でコーティングされたポリ(エチレンテレフタレート)シート(PET)と重ね合わせ(図15の(f))、また、上側からUV光を使用して、PUを硬化させる(図15の(h))。また、PDMSを引き剥がすことにより、プラスチック基板に対してμs−GaN素子を転写する。この転写により、GaNリボン上にはPU残留物が残る。そして、この残留物を、図15の(e)のステップで蒸着された電子ビーム蒸着SiO2層を、BOEを用いて剥ぎ取る際に除去する。プロセスの最後のステップは、ソース/ドレイン相互接続部及びショットキーゲート金属接点(Ni/Au)の形成、電子ビーム蒸着により堆積され且つ標準的なリフトオフプロセスを使用してパターニングされる層の形成を含む(図15の(f))。

【0111】

[0132]下側に位置するSi(図1d)の除去後に自立μs−GaNの当初の位置を維持するため、図14Cに概説したプロセスに示すような微細構造半導体(μs−Sc)の新規な幾何学的構成を採用する。μs−GaNリボンは、PDMS印刷ツールに対するそれらの位置合わせ転写(図15の(e))を容易にするために、GaNリボンの端部に二つの幅の狭いブリッジ(すなわち、図14Cに矢印で示す二つの破壊点)を有する。この構造は、先に報告された「ピーナッツ」構成を超える著しい改善を示す。転写プロセスを仲介する破断は、この構成を伴って非常に効率的であることが分かった。先の「ピーナッツ」構成は、印刷に適したμs−Scリボンを形成するために、エッチング時間の厳格な最適化及び非常に均一なエッチング速度を大面積にわたって必要とする。この「幅狭ブリッジ」構造は、エッチング速度の差に殆ど影響されない。この後者の点を示すために、図16の(a)及び図16の(b)は、TMAH異方性エッチングステップの前後に各々取得されたGaNウエハの光学画像を示している。これらの画像では、独立且つ支持されたGaN微細構造の異なる色を容易に識別できる。図16の(c)及び図16の(d)は、下側に位置するSiをカットするTMAHのエッチングステップの中間段階で取得された走査電子顕微鏡写真(SEM)画像を示している。図16の(d)の拡大画像及び図16の(b)の破線領域は、Siエッチングプロセス、即ち、GaNリボンの方向に対して垂直な方向にのみ本質的に伝搬することを示す、この異方性の高い性質を強力に表している。この特定のシステムでは、選択エッチングは(110)方位に沿って生じ、Si(111)表面は、図14Cに示すように、固有のエッチングブロックマスクとしての機能を果たした。図16の(e)は、インク付けされたPDMSスラブのSEM画像を示しており、ここでは、μs−GaNがそのウエハ上位置合わせの全張力をもって転写された。図16の(f)の画像は、印刷された構造体のSEM顕微鏡写真を示しており、この最後のステップでは、μs−GaNヘテロ構造デバイスがPUコーティングされたPET基板に対して転写される。これらの画像は、「幅狭ブリッジ」μs−GaNモチーフに基づく転写がヘテロ構造リボンを損傷させないことを実証している。

【0112】

[0133]図17の(a)及び図17の(b)は、PET基板に対する転写後のμs−GaN系HEMTの代表的な光学画像を示している。様々なコントラストは、図14Bに示すこれらデバイスの断面概略図の様々なレンド(lends)に対応している。この幾何学的構成では、二つのオーム接点(Ti/Al/Mo/Au)間に活性電子チャネルが形成され、また、電子流量(又は電流)がショットキー(Ni/Au)ゲート接点によって制御される。図17の(b)に示すデバイスのチャネル長、チャネル幅、及び、ゲート幅は各々20、170、5μmである。側面ウェットエッチングによって引き起こされる小さな充填率という必然的な限界を持った先のμs−GaAsプロセスとは異なり、これらのデバイスにおける充填率は、印刷されたIII−V構造における先の報告と比べて非常に高い(μs−GaAsにおける13%に対して67%)。図17の(c)は、プラスチック支持されたGaN HEMTデバイスの典型的ドレイン電流−電圧(I−V)特性を示している。ここでは、ゲートは、−3Vから1Vまで1Vのステップでバイアスされた。このデバイスは、1Vのゲートバイアス及び5Vのドレインバイアスで約5mAの最大ドレイン電流を示す。図17の(d)は、一定のドレイン電圧(Vd=2V)で測定された伝達特性を示している。このデバイスは、−2.7Vの閾値電圧(Vth)、103のON/OFF比、及び、1.5mSの相互コンダクタンスを示す。同じデバイス構成を有するが転写前のGaN HEMTの相互コンダクタンスは、2.6mSの相互コンダクタンスを有する。転写プロセスは、この値を約38%減少させるようである。

【0113】

[0134]GaN HEMTの機械的な可撓性を、図18の(a)に示す曲げステージを使用して調査した。図18の(b)は、曲げ半径(及びその対応する歪み)に応じて測定された一連の伝達曲線を示している。1.1cmまでの曲げ半径(0.46%程度の歪みに対応する)の場合、測定された相互コンダクタンス、閾値電圧、及び、ON/OFF比において非常に安定した応答が観察されている。図18の(c)は、最大歪みの位置及びその切り離し後の双方で測定された一連の電流−電圧(I−V)曲線を示している。前述したように、見出される影響は比較的小さく、図17の(b)及び図18の(b)の三つのI−V曲線間で見られる僅かな差は、過酷な曲げサイクルによってμs−GaN HEMTデバイスが損傷されないことを示唆している。

【0114】

[0135]要約すると、この実施例は、プラスチック基板上に可撓性の高性能GaN HEMTを印刷するのに適したプロセスについて説明している。また、転写印刷プロトコルを容易にするμs−Scの効率的な幾何学的構成、及び、異方性ウェットエッチングによって犠牲層を除去するためのスマート材料方策を明らかにしている。本結果は、μs−GaN技術が高性能モバイル計算システム及び高速通信システム等の次世代のマクロ電子デバイスを開発する興味深い機会を与えることを示唆している。

【0115】

[0136]方法:GaN微細構造を、シリコン(100)ウエハ(Nitronex)上のヘテロ構造GaNで製造する。この構造は、III−V半導体の三つの層、すなわち、AlGaN層(18nm、ドーピングされていない)と、GaNバッファ層(0.6μm、ドーピングされていない)と、AlN転位層(0.6μm)とを備えている。AZ5214フォトレジストを使用して、オーム接点領域を開放し、この露出した領域を、O2プラズマ(Plasmatherm、50mTorr、20sccm、300W、30秒)を用して洗浄する。低い接触抵抗を得るため、メタライゼーションステップの前に、RIEシステム内でのSiCl4プラズマを使用したオーム接点領域の前処理を行なう。その後、Ti/Al/Mo/Au(上から下に向かって15/60/35/50nm)金属層を堆積させる。電子ビーム蒸着を使用して、Ti、Al、Moを堆積し、一方、熱蒸着によってAuを堆積させた。また、接点を、リフトオフプロセスを使用して形成する。この接点を、N2環境を使用する急速熱アニーリングシステム内で30秒間にわたって850℃でアニールする。その後のICPエッチングのためのマスク材料として、PECVD酸化物(Plasmatherm、400nm、900mTorr、350sccm2%SiH4/He、795sccmNO2、250℃)層及びCr金属(電子ビーム蒸着、150nm)層を堆積させる。フォトリソグラフィ、ウェットエッチング(Cyantek Crエッチング液)及びRIE処理(50mTorr、40sccmCH4、100W、14分)が、GaNのリボン形状を規定する。アセトンを用いてフォトレジストを除去した後、ICPドライエッチング(3.2mTorr、15sccmCl2、5sccmAr、−100Vバイアス、14分)を使用して露出したGaNを除去し、その後、TMAHウェットエッチング溶液を使用して下側のSiをエッチング除去する(Aldrich、5分間にわたって160℃)。このサンプルを、90秒にわたってBOE(6:1、NH4F:HF)中に浸漬して、PECVD酸化物を除去し、また、新たな50nmの電子ビーム蒸着されたSiO2層をGaNリボン上に堆積させる。その後、GaNウエハをPDMSスラブ(Sylgard 184、Dow corning)と接触させ、PDMSスラブを、その後、μs−GaN素子を取得するために>0.01ms−1の剥離速度で引き剥がす。μs−GaNでインク付けされたPDMSスラブを、その後、ポリウレタン(PU、Norland光学接着剤、No. 73)でコーティングされたポリ(エチレンテレフタレート)シート(PET、100μm厚、Glafix Plastics)に対して重ね合わせる。サンプルを、上側からのUV光に晒し、これによりPUを硬化させる。PDMSを引き剥がし、30分間にわたってBOE中に浸漬することによって、電子ビーム酸化物を除去することにより、プラスチック基板上に対してμs−GaN素子を転写する。ショットキー接点領域をパターニングするためにネガフォトレジスト(AZnLOF2020)を使用し、また、その後、Ni/Au(80/100nm)層を電子ビーム蒸着によって堆積させる。AZストリッパーと併せてリフトオフプロセスを使用してPRを除去する(5時間にわたりKWIK)。

【実施例5】

【0116】

複数のエピタキシャル層を有するGaAsのバルクウエハから得られる印刷可能半導体素子

【0117】

[0137]本発明は、GaAsのバルクウエハを出発材料として使用して、印刷可能半導体リボンを形成する方法を含む。一実施形態では、リボンを、複数のエピタキシャル層を有するGaAsの高品質バルクウエハから形成する。このウエハは、(100)半絶縁GaAs(Sl−GaAs)ウエハ上に200nm厚AlAs層を成長させた後、150nmの厚さを有するSl−GaAs層と厚さが120nmで且つキャリア濃度が4×1017cm−3のSiドープされたn型GaAs層とを連続的に堆積させることによって形成される。(0TT)結晶方位に対して平行に規定されたフォトレジストラインのパターンは、エピ層(GaAs及びAlAsの両方を含む)の化学エッチングのためのマスクとしての機能を果たす。H3PO4及びH2O2の水溶性エッチング液を用いた異方性エッチングは、これらの最上層を、フォトレジストによって規定される長さ及び方向を有しかつウエハ表面に対して鋭角を成す側面を有する個々のバーへと分離させた。異方性エッチング後にフォトレジストを除去し、その後、HFのエタノール溶液(エタノールと49%HF水溶液との間の体積比が2:1)中にウエハを浸すことにより、AlAs層とGaAsの切り離されたリボン(n−GaAs/Sl−GaAs)とを除去する。このステップにおいて水の代わりにエタノールを使用すると、乾燥中に毛管力の作用に起因して脆弱なリボンに生じ得るクラッキングが減少される。また、水と比べて低いエタノールの表面張力は、GaAsリボンの空間的レイアウトの乾燥に伴う乱れを最小限に抑える。

【0118】

[0138]顧客設計のエピタキシャル層を有するGaAsウエハは、ペンシルベニア州のベスレヘムにあるIQE社から販売されている。リソグラフィプロセスは、AZフォトレジスト、すなわち、ポジ画像化及びネガ画像化のためのAZ5214及びAZnLOF2020を各々使用した。フォトレジストマスクパターンを有するGaAsウエハは、氷水槽内で冷却されるエッチング液(4mL H3PO4(85重量%)、52mL H2O2(30重量%)、及び、48mL脱イオン水)中で異方性エッチングする。AlAs層は、エタノール中に希釈されたHF溶液(Fisher(登録商標) Chemicals)(体積比1:2)を用いて溶解する。マザー基板上の切り離されたリボンを有するサンプルは、ドラフト内で乾燥させる。乾燥されたサンプルを、電子ビーム蒸着器(Temescal FC−1800)のチャンバ内に配置し、2nmTi及び28nmSiO2の一連の層でコーティングする。

【実施例6】

【0119】

Si(111)ウエハから得られる多層配列印刷可能半導体素子

【0120】

[0139]また、本発明は、Si(111)ウエハ前駆材料から得られる多層配列印刷可能半導体素子を与える方法及び構成も含む。図19は、印刷可能半導体素子の多層配列を形成するための本発明の方法を示すプロセスフローの概略図を示している。図19のパネル1に示すように、(111)方位を有するシリコンウエハを設ける。ウエハの外面を、耐エッチング性マスクを用いてパターニングし、それにより、多層配列の印刷可能半導体リボンの長さ及び幅を規定するように選択された寸法を有するマスキングされた領域を形成する。図19に示す実施例において、耐エッチング性マスクは熱成長するSiO2層である。

【0121】

[0140]パネル2に示すように、シリコンウエハを、主に、パターニングされた外面に対して垂直な方向でエッチングする。使用したエッチングシステムは、輪郭を成す側面を有する凹状形態部を形成する。有用な実施形態では、凹状形態部の側面は、周期的な凹凸状の輪郭形状を有する側面及び/又は凹状形態部の側面上に存在する深い隆起を有する輪郭形状をもつ側面のような複数の輪郭形態部を有する選択された空間的に変化する輪郭形状を成している。選択された輪郭形状を有する凹状形態部を形成するための例示的な手段としては、反応性イオンエッチング液ガス及びエッチレジスト材料に対してシリコンウエハを周期的に晒すSTS−ICPRIEエッチングシステム及びBOEエッチングシステムが挙げられる。図19のパネル3に示すように、この処理ステップは、凹状形態部に隣接して位置されかつ選択的に輪郭付けられた側面を有する複数のシリコン構造を形成する。

【0122】

[0141]図19のパネル3に示すように、凹状形態部及びシリコン構造を有する処理済みのシリコンウエハに、耐エッチング性マスク材料を堆積し、それにより、凹状形態部の輪郭を成す側面の一部のみを堆積材料によってコーティングする。本発明のこの態様において、凹状形態部の側面の選択された輪郭形状は、少なくとも部分的に、側面上におけるマスク材料の空間的分布を決定する。したがって、この処理ステップは、多層積層体中の印刷可能半導体素子の厚さを規定する。例えば、ウエハが、金属又は金属の組み合わせの傾斜型蒸着に晒され、それにより、主に凹状形態部の輪郭表面中に存在する隆起上に材料が堆積され、例えば側壁の凹状領域に存在する隆起の「陰(シャドウ)」にある輪郭表面の領域上には実質的に堆積されないようになっていてもよい。隆起、波状部、凹凸形態部のような選択された輪郭形状の特徴形態により成形された「陰」は、少なくとも部分的に、多層配列の印刷可能半導体素子の厚さを規定する。金堆積材料の使用は、露出したシリコン表面に対するその良好な接着性により有益である。

【0123】

[0142]図19のパネル4に示すように、次に、ウエハを、例えばKOH等の塩基性溶液に晒すことにより、異方性エッチングする。凹状形態部間の領域を、シリコンウエハの<110>方位に沿ってエッチングが生じるようにエッチングし、それにより、各々が部分的に又は完全にアンダーカットされた構造を備える印刷可能半導体素子の多層配列を形成する。本発明は、シリコンウエハの<110>方位に沿うエッチングが隣接する凹状形態部間で終了するように進行し、それにより、印刷可能半導体素子が完全にアンダーカットされる方法を含む。先に詳しく説明したように、シリコンウエハの(111)方位と組み合わせて選択されるエッチングシステムにより、ウエハの<111>方位に沿うエッチング速度よりも<110>方位に沿うエッチング速度の方が速くなる。オプションとして、凹状形態部の位置、形状、及び空間的方向は、印刷可能半導体素子をウエハに対して接続するブリッジ素子等のアライメント維持素子を形成するように選択される。パネル4に示す多層構造においては、多層配列の半導体リボンの端部をシリコンウエハに対して接続するブリッジ素子が設けられている。

【0124】

[0143]図19のパネル5は、例えば洗浄、エッチング又は他の材料除去プロセスによってブリッジ素子がシリコンウエハから除去され、それにより、印刷可能半導体素子の多層積層体が形成されるオプションの処理ステップを示している。或いは、配列状の印刷可能半導体素子をコンタクト印刷方法によって切り離すことができる。一実施形態では、例えば、多層配列の印刷可能半導体素子は、印刷可能半導体素子をエラストマスタンプ等の転写デバイスに対して繰り返し接触させることにより、シリコンウエハから連続的に切り離されて転写される。

【0125】

[0144]図20は、Si(111)の斜視(a、c、e、g)及び断面(b、d、f、h)のSEM画像を示している。図中、(a)及び(b)は、STS−ICPRIEエッチング及びBOEエッチング後のSEM画像、(c)及び(d)は側面上での金属保護後のSEM画像、(e)〜(h)はその後に金属クリーニングが行なわれる、2分間(e及びf)及び5分間(g及びh)のKOHエッチング後のSEM画像である。

【0126】

[0145]図21は、(a)に4層Si(111)リボンの大型アライメント配列の写真を示している。(b)及び(c)は、(a)に示す4層Si(111)の上面SEM画像であり、(d)及び(e)は、(a)に示す4層Si(111)の斜視SEM画像である。

【0127】

[0146]図22は、(a)に切り離されたフレキシブルSi(111)リボンの写真、(b)及び(c)にOM画像を示している。(d〜f)は、(a)に示すリボンのSEM画像である。

【0128】

[0147]図23は、(a)にPDMS基板上に転写されたアライメントされたSi(111)リボンの光学画像を示している。(b)は、(a)に示す配列からの4つのリボンのAFM画像である。(c)は、単一のSiチップから転写する4サイクルからのSi(111)配列の四つのパターンを収容するフレキシブルポリエステルフィルムの写真である。

【0129】

[0148]以下の文献は、コンタクト印刷技術及び/又はソリューション印刷技術により印刷可能半導体素子を転写し、組み立て、相互に接続するために本発明の方法で使用され得る自己組織構成技術に関するものである。これら文献を、その全体を参照することによって、本明細書に援用する。

(1)“Guided molecular self−assembly:a review of recent effort”, Jiyun C Huie Smart Mater.Struct.(2003) 12,264−271

(2)“Large−Scale Hierarchical Organization of Nanowire Arrays for Integrated Nanosystems”, Whang,D.; Jin,S.; Wu,Y.; Lieber,C.M.Nano Lett.(2003) 3(9),1255−1259

(3)“Directed Assembly of One−Dimensional Nanostructures into Functional Networks”, Yu Huang,Xiangfeng Duan,Qingqiao Wei,and Charles M.Lieber,Science (2001) 291,630−633

(4)“Electric−field assisted assembly and alignment of metallic nanowires”, Peter A.Smithら,Appl.Phys.Lett.(2000) 77(9),1399−1401

【0130】

[0149]本出願の全体にわたる全参照文献、例えば、発行され又は許可された特許、若しくは、その等価物を含む特許文献、特許出願公報、未公開特許出願、及び、非特許文献又は他の原資料を、各文献がこの出願の開示内容と少なくとも部分的に矛盾しない程度において、参照することによって個々に援用するが如く、それらの全体を本明細書で参照することによって、援用する(例えば、部分的に矛盾する文献は、文献の部分的に矛盾する部分を除き、参照することによって援用する)。

【0131】

[0150]本明細書に添付された任意の1又は複数の付録は、明細書及び/又は図面の一部として参照することによって本願に援用する。

【0132】

[0151]本明細書中において「備える(comprise)」、「備える(comprises)」、「備えられた(comprised)」、又は、「備える(comprising)」との用語が使用される場合、これらの用語は、述べられた特徴、整数、ステップ、又は、部品の存在を特定するが、一つ以上の他の特徴、整数、ステップ、部品、又は、それらのグループの存在又は付加を排除しないように解釈されなければならない。また、「備える(comprising)」又は「備える(comprise(s))」又は「備えられた(comprised)」との用語が場合により文法的に類似の用語、例えば「から成る(consisting/consist(s))」又は「から本質的に成る(onsisting essentially of/consist(s) essentially of)」に置き換えて、これによって、必ずしも同一の広がりを持たない更なる実施形態を説明する本発明の別個の実施形態も包含されることを意図している。

【0133】

[0152]様々な特定の好ましい実施形態及び技術を参照して本発明を説明してきた。しかしながら、本発明の思想及び範囲内に留めつつ多くの変形及び変向を成すことができることは言うまでもない。当業者であれば分かるように、本明細書中で具体的に記載された構成、方法、デバイス、デバイス素子、材料、処理、及び、技術以外の構成、方法、デバイス、デバイス素子、材料、処理、及び、技術は、必要以上の実験に頼ることなく本明細書中に広く開示されるように本発明の実施に適用することができる。本明細書中に記載された構成、方法、デバイス、デバイス素子、材料、処理及び技術の技術的に知られた全ての機能的な均等物は、この発明に包含されるものである。一つの範囲が開示されるときには如何なるときでも、全ての部分的範囲及び個々の値があたかも別個に述べられているかのように包含されるものである。本発明は、図面に示し又は明細書中に例示した任意のものを含む、開示した実施形態によって限定されるものではなく、当該実施形態は、例示及び説明のために提示したものであって、限定するものではない。本発明の範囲は、請求項によってのみ限定されるべきである。

【0134】

参考文献

[1] a) Y. Xia, P. Yang,Y. Sun, Y. Wu, B.Mayers, B. Gates, Y. Yin, F. Kim, H. Yan, Adv. Mater. 2003,15, 353. b) C. M.Lieber, Mater. Res. Soc. Bull. 2003, 28, 486. c) M. C.McAlpine, R. S.Friedman, C. M. Lieber, Proc. IEEE 2005, 93, 1357. d) M. Law, J.Goldberger, P.Yang, Ann. Rev. Mater. Res. 2004, 34, 83. e) P. Yang, Mater. Res.Soc. Bull.2005, 30, 85. f) Z. R. Dai, Z. W. Pan, Z. L. Wang, Adv. F

unct Mater. 2003, 13,9.g) special issue on nanostructured advanced materials, Pure Appl. Chem.2002,74(9).

[2] a) Y. Yin, A. P.Alivisatos, Nature,2005, 437, 664. b) I. Gur, N. A. Fromer, M. L. Geier,A. P.Alivisatos, Science, 2005, 310, 462. c) L. Samuelson, M. T. Bjork, K.Depper, M.Larsson, B. J. Ohlsson, N. Panev, A. I. Persson, N. Skold, C. Thelander, L. R.Wallenberg, Physica E 2004, 21, 560.

[3] a) L. A. Bauer, N.S. Birenbaum, G. J.Meyer, J. Mater. Chem. 2004, 14, 517.b) Y. Cui, Q. Wei, H.Park, C. M. Lieber,Science 2001, 293, 1289.

[4] Z. Tang, N. A.Kotov, Adv. Mater. 2005,17, 951.

[5] X. Duan, C. Niu, V.Sahi, J. Chen, J. W.Parce, S. Empedocles, J. L. Goldman, Nature 2003, 425, 274.

[6] R. S. Friedman, M.C. McAlpine, D. S. Ricketts, D. Ham, C. M. Lieber, Nature 2005, 434, 1085.

[7] E. Menard, K. J.Lee, D.-Y. Khang, R. G.Nuzzo, J. A. Rogers, Appl. Phys. Lett. 2004, 84, 5398.

[8] a) S. Mack, M. A.Meitl, A. Baca, inpreparation. b) Y. Sun, S. Mack, J. A. Rogers,Proc. Intl.Electron DeviceMeeting(IEEE), 2005, in press.

[9] a) E. Menard, R. G.Nuzzo, J. A. Rogers,Appl. Phys. Lett. 2005, 86, 093507.b) Z.-T. Zhu, E. Menard,K. Hurley, R. G. Nuzzo, J. A.Rogers, Appl. Phys. Lett. 2005, 86, 133507.

[10] a) Y. Sun, J. A.Rogers, Nano Lett.2004, 4, 1953. b) Y. Sun, D.-Y. Khang, F. Hua, K. Hurley, R.G. Nuzzo, J. A. Rogers, Adv.Fund Mater. 2005, 15, 30.

[11] Y. Sun, S. Kim, I.Adesida, J. A. Rogers, Appl. Phys. Lett. 2005, 87, 083501.

[12] Y. Sun, H.-S. Kim,E. Menard, S. Kim, G.Chen, I. Adesida, R. Dettmer, R. Cortez, A. Tewksbury, J.A. Rogers, Appl.Phys. Lett., submitted.

[13] R. H. Reuss, B. R.Chalamala, A.Moussessian, M. G. Kane, A. Kumar, D. C. Zhang, J. A. Rogers, M.Hatalis, D.Temple, G. Moddel, B. J. Eliasson, M. J. Estes, J. Kunze, E. S.Handy, E. S.Harmon, D. B. Salzman, J. M. Woodall, M. A. Alam, J. Y.

Murthy, S. C. Jacobsen,M. Olivier, D.Markus, P. M. Campbell, E. Snow, Proc. IEEE 2005, 39, 1239.

[14] D. C. Duffy, C.McDonald, O. J. A.Schueller, G. M. Whitesides, Anal. Chem. 1998, 70, 4974.

[15] S. M. Sze,Semiconductor Devices,Physics and Technology (Wiley, New York, 1985).

[16] G. Eftekhari,Phys. Status SolidiA-Appl. Res. 1993, 140, 189.

[17] H.-l. Chen, C.-K.Hsiung, Y.-l Chou,Semicond. Sci. Technol. 2003, 18, 620.

[18] S. Forment, M.Biber, R. L. vanMeirhaeghe, W. P. Leroy, A. Turut, Semicond. Sci Technol. 2004,19, 1391.

[19] L. Stephen, S. E.Butner, GalliumArsenide Digital lntergrated Circuit Design. (McGraw-Hill, NewYork, 1990).

1R. H. Reuss, B. R. Chalamala, A. Moussessian,M.G. Kane, A. Kumar, D. C. Zhang, J. A. Rogers, M. Hatalis, D. Temple, G.Moddel,B. J. Eliasson, M. J. Estes, J. Kunze, E. S.

Handy, E. S. Harmon, D.B. Salzman, J. M.Woodall, M. A. Alam, J. Y. Murthy, S. C.Jacobsen, M. Olivier,D. Markus, P. M.Campbell, and E. Snow, Proc. IEEE 39, 1209 (2005).

2K. Nomura, H. Ohta, A. Takagi, T. Kamiya,M.Hirano, and H. Hosono, Nature 432, 488 (2004).

3D. B. Mitzi, L. L. Kosbar, C. E. Murray, M.Copel,and A. Afzali, Nature 428, 299 (2004).

4S. Ucjikoga, MRS Bull. 27, 881 (2002).

5X. Duang, C. Niu, V. Sahi, J. Chen, J. W.Parce,S. Empedocies, and J. L. Goldman,Nature 425, 274 (2003).

6R. S. Friedman, M. C. McAlpine, D. S. Ricketts,D. Ham, and C. M. Lieber, Nature434,1085 (2005).

7E. Menard, K. J. Lee, D.-Y. Khang, R. G.Nuzzo,and J. A. Rogers, Appl. Phys. Lett. 84,5398 (2004).

8E. Menard, R. G. Nuzzo, and J. A. Rogers,Appl.Phys. Lett. 86, 093507 (2005).

9Z.-T. Zhu, E. Menard, K. Hurley, R. G. Nuzzo,andJ. A. Rogers, Appl. Phys. Lett. 86,133507 (2005).

10Y. Sun, S. Kim, I. Adesida, and J. A. Rogers,Appl. Phys. Lett. 87, 083501 (2005).

11Y. Sun, and J. A. Rogers, J. A. Nano Lett.4,1953 (2004).

12Y. Sun, D.-Y. Khang, F. Hua, K. Hurley, R.G.Nuzzo, and J. A. Rogers, Adv. Funct. Mater. 15, 30 (2005).

13A. S. Sedra,and K. C. Smith, MicroelectronicCircuits (Oxford University Press, New York,1998).

14L. Stephen, and S. E. Butner, GalliumArsenideDigital lntergrated Circuit Design (McGraw-Hill, New York, 1990).

15M. C, Lau, Small Signal EquivalentCircuitExtraction from a Gallium Arsenide MESFET device (M.S. thesis,VirginiaPolytechnic Institution and State University, Blacksburg, VA, 1997).

16L. B. Freund, Intl. J. Solids Struct. 37,185(2000).

17C. P. Kuo, S. K. Vong, R. M. Cohen, and G.B.Stringfellow, J. Appl. Phys. 57, 5428 (1985).

1X. Duan, C. Niu, V. Sahi, J. Chen, J. W.Parce,S. Empedocles, J. L. Goldman, Nature 425, 274 (2003).

2Y. Huang, X. Duan, Q. Wei, C. M. Lieber,Science291, 630 (2001).

3M. A. Meitl, Y. Zhou, A. Gaur, S. Jeon, M.L.Usrey, M. S. Strano, J. A. Rogers, Nano Lett. 4, No. 9 1643 (2004).

4R. S. Friedman, Nature 434, 1085 (2005).

5E. Menard, K. J. Lee, D.-Y. Khang, R. G.Nuzzoand J. A. Rogers, Appl. Phys. Lett. 84,5398 (2004).

6E. Menard, R.G. Nuzzo and J.A. Rogers,Appl.Phys. Lett. 86, (2005).

7Z.-T. Zhu, E. Menard, K. Hurley, R. G. Nuzzo,J.A. Rogers, Appl. Phys. Lett. 86,133507 (2005).

8Y. Sun, S. Kim, I. Adesida, J. A. Rogers, Appl.Phys. Lett. 87, 083501 (2005).

9K. J. Lee, M. J. Motala, M. A. Meitl, W.R.Childs, E. Menard, A. K. Shim, J. A. Rogers,R. G. Nuzzo, Adv. Mater. 17,2332(2005).

10M. A. Meitl, Z.-T. Zhu, V. Kumar, K. J. Lee,X.Feng, Y. Y. Huang, I. Adesida, R. G. Nuzzo, and J. A. Rogers, Nat. Mater. 5,33(2006).

11D.Y. Khang, H. Jiang, Y. Huang and J.A.Rogers,Science 311, 208 (2006).

12S. R. Forrest, Nature 428, 911 (2004).

13J. A. Rogers, K. E. Paul, R. J. Jackman, G.M.Whitesides, Appl. Phys. Lett. 70, 2658 (1997).

14S. Sze., Semiconductor Devices: PhysicsandTechnology 2nd ed. (Wiley, New York, 2002), pp.190-192.

[1] R. Reuss et al.Proc. IEEE. 2005, 39,1239.

[2] J. A. Rogers, Z.Bao, K. Baldwin, A.Dodabalapur, B. Crone, V. R. Raju, V. Kuck, H. Katz, K.Amundson, J. Ewing, P.Drzaic, Proc. Nat. Acad. Sci. 2001, 98, 4835.

[3] (a) J. H. Schon, S.Berg, C. Kloc, B.Batlogg, Science 2000, 287, 1022. (b) A. Dodabalapur, L.Torsi, H. E. Katz,Science 1995, 268, 270.

[4] B. S. Ong, Y. Wu,P. Liu, S. Gardner, J.Am. Chem. Soc. 2004, 126, 3378.

[5] S. R. Forrest,Nature, 2004, 428, 911.

[6] C. R. Kagan, D. B.Mitzi, C. D.Dimitrakopoulos, Science 1999, 286, 945.

[7] X. Duan, C. Niu, V.Sahi, J. Chen, J. W.Parce, S. Empedocles, J. L. Goldman, Nature, 2003, 425,274.

[8] J. Kwon, D. Kim, H.Cho, K. Park, J.Jung, J. Kim, Y. Park, T. Noguchi, IEEE Trans.Electron. 2005,466, 7.

[9] K. Lee, M. J.Motala, M. A. Meitl, W. R.Childs, E. Menard, A. K. Shim, J. A. Rogers,R. G.Nuzzo, Adv. Mater. 2005, 17,2336.

[10] Z. Zhu, E. Menard,K. Hurley, R. G.Nuzzo, J. A. Rogers, App. Phys. Lett. 2005, 86,133507.

[11] M. A. Meitl, Z.Zhu, V. Kumar, K. Lee,X. Feng, Y. Huang, R. G. Nuzzo, J. A. Rogers, NatureMater. 2006, 5, 33.

[12] D. Khang, H.Jiang, Y. Huang, J. A.Rogers, Science, 2006, 311, 208.

[13] Y. Sun, S. Kim, I.Adesida, J. A. Rogers, App. Phys. Lett. 2005, 87, 083501.

[14] K. Lee, Dr. J.Lee, H. Hwang, J. A.Rogers, R. G. Nuzzo, Small 2005, 1, 1164.

[15] (a) GaN andrelated Materials (Eds.: S.J. Pearton), Gordon and Breach, NewYork,1997.(b)Group III Nitride Semiconductor Compounds (Eds.: B. Gil), Clarendon,Oxford,1998.

[16] (a) U. Mishra, P.Parikh, Y. Wu, Proc.IEEE. 2002, 90, 1022. (b) S. J. Pearton, J. C. Zolper, R.J. Shul, F. Ren, J.Appl. Phys. 1999, 86, 1. (c) S. C. Jain, M. Willander, J.Narayan, R. Van Overstraeten, J. Appl. Phys. 2000, 87, 965.

[17] M. A. Khan, A.Bhattari, J. N. Kuznia,and D. T. Olson, App. Phys. Lett. 1993, 63,1214.

[18] Typical Sianisotropic etch ratios inTMAH and H2O mixtures are reported from 12to 50 in the direction<110>/<111>. Please see to the followingreferences; (a) Fundamentals of Microfabrication, (Ed: M.Madou), CRC Press, NewYork, 1997. (b) D.L. Kendall, Ann. Rev. Mater. Sci 1979, 9, 373.

[19] V. Kumar, L Zhou,D. Selvanathan, and I. Adesida, J. Appl. Phys. 2002, 92, 1712.

[20] Silicon Processingfor the VLSI Era, Vol. 1 : Process Technology, (Ed: S. Wolf, R.N. Tauber)Lattice Press, 1999.

【図面の簡単な説明】

【0135】

【図1A】単結晶シリコンのリボンを有する印刷可能半導体素子を、(111)方位を有するバルクシリコンウエハから形成するための本発明の例示的な方法を示す概略断面図である。

【図1B】バルクシリコンウエハから印刷可能半導体素子を形成するための本方法の処理ステップを示すフロー図である。

【図1】(c)及び(d)は、凹状形態部の側面が完全ではなく部分的にマスキングされる製造方法を示す概略断面処理図である。

【図1E】側面の精緻化を伴うことなく形成されたチャネル(溝)構造であって、位相シフトフォトリソグラフィ、金属リフトオフ、反応性イオンエッチング、及び、その後の金属エッチングマスクの除去によって形成された溝構造を有するSi(111)における凹状形態部の画像である。

【図1F】側面の精緻化を伴って形成されたチャネル構造を有するSi(111)における凹状形態部の画像を示している。

【図2A】印刷可能半導体素子と二つのブリッジ素子とを備える本発明の印刷可能半導体構造の概略平面図であり、二つのブリッジ素子は同図に示す構造において互いに先端に設けられている。

【図2B】印刷可能半導体素子と二つのブリッジ素子とを備える本発明の印刷可能半導体構造の概略平面図であり、二つのブリッジ素子は同図に示す構造において互いに基端に設けられている。

【図2C】印刷可能半導体素子をマザーウエハに対して接続するブリッジ素子の画像を示している。

【図2D】印刷可能半導体素子をマザーウエハに対して接続するブリッジ素子の画像を示している。

【図3】(a)は単結晶GaAsウエハから形成されたオームストライプと一体の転写印刷されたGaAsワイヤを使用してプラスチック上にトランジスタ、ダイオード及び論理回路を形成するためのプロセスの概略図であり、(b)はGaAsワイヤの端部がマザーウエハに対して接続した状態のGaAsワイヤ(オームストライプを有する)の配列のSEM画像であり、矢印によって示した一部のワイヤは、配列されたワイヤの下側に位置しており、このことは、GaAsワイヤがバルクウエハから分離されていることを示しており、挿入画は、自立した個々のワイヤを表わしており、その三角形断面を明確に示している。(c)は50μmのチャネル長及び5μmのゲート長を有し、PET基板上に転写印刷された(b)に示すGaAsワイヤ配列が形成された個々のMESFETのSEM画像である。(d)は、PETシート上のTi/n−GaAsショットキーダイオードの光学顕微鏡写真であり、挿入画は、一方の電極パッドがワイヤの一端上にオームストライプを接続し、ショットキー接点を形成するために他方の電極(150nm Ti/150nm Au)パッドがGaAsワイヤに対して直接に接続されていることを示している。(e)及び(f)は、(e)では平坦な表面上、(f)では湾曲シャフト上に実装された様々な論理ゲート及び個々のMESFETを有するPET基板の光学画像である。

【図4】5μmのゲート長及び異なるチャネル長((a)及び(b)では50μm、(c)では25μm)を有するPU/PET基板上のGaAsワイヤMESFETの特性を示す図である。(a)は、異なるゲート電圧(VGS)での図3Cに示すトランジスタの電流−電圧(すなわち、IDS対VDS)曲線を示しており、上から下に向けて、VGSは0.5から−3.0Vへと0.5Vのステップで減少している。(b)は、VDS=4Vの飽和領域における同じトランジスタの伝達特性曲線を示しており、挿入図は、ゲート電圧に対する相互コンダクタンスの依存度を明らかにする伝達特性曲線の導関数を示している。(c)は、25μmのチャネル長のトランジスタにおける異なるVGSでのソース−ドレイン電流を示しており、上から下に向けて、VGSは0.5から−5.0Vへと0.5Vのステップで減少している。(d)は、良好な整流性能を示す製造時のAu/Ti−GaAsショットキーダイオードのI−V特性を示している。

【図5】インバータの(a)回路図、(b)光学画像、(c)出力−入力特性を示す図であり、全てのMESFETは5μmのゲート長を有しており、Vddはグランド(GND)に対して5Vでバイアスされたものである。

【図6】異なる論理ゲート、即ち、即ち、(a、b、c)NORゲート及び(d、e、f)NANDゲートの回路図、光学画像、出力−入力特性を示す図であり、全てのMESFETは5μmのゲート長を有しており、スケールバーは100μmであり、これらの論理ゲートに対して印加されるVddはグランド(GND)に対して5Vであり、NORゲート及びNANDゲートの論理“0”及び“1”の入力信号はそれぞれ、−5V及び2Vで駆動されており、NORゲートの論理“0”及び“1”の出力はそれぞれ、1.58−1.67V及び4.1Vであり、NANDゲートの論理“0”及び“1”の出力はそれぞれ、2.90V及び4.83−4.98Vである。

【図7】(a)は、50μmのチャネル長及び2μmのゲート長をもつPU/PET基板上における個々のGaAsワイヤMESFETのSEM画像であり、各トランジスタに10個の整列されたGaAsワイヤが形成されていることを示している。(b)は、(a)に示すトランジスタの電流−電圧(すなわち、IDS対VDS)曲線であり、上から下に向けて、VGSは0.5から−3.0Vへと0.5Vのステップで減少しており、挿入図は、VDS=4Vの飽和領域におけるこのトランジスタの伝達特性曲線を示している。

【図8】(a)及び(b)は、ゲート長が異なる((a)では2μm及び(b)では5μm)GaAsワイヤMESFETのRF応答の実験結果(青)及びシミュレーション結果(赤)を示す図であり、測定は、(a)の挿入画に示すプロービング構成で行なわれたものである。(c)は、ゲート長に対するfTの依存度を示す図であり、異なる記号は異なるデバイスに対する測定値を表わしており、破線はシミュレーションに対応している。

【図9】PU/PET基板上の高速GaAsワイヤMESFET(ゲート長が2μm)の機械的柔軟性の特性を示す図である。図中、(a)は、測定用の設備の光学画像である。(b)及び(c)は、表面歪みの影響(プラス値及びマイナス値が引張歪み及び圧縮歪みの各々に対応している)を示しており、(b)は、VDS=4V及びVGS=0Vにおいてソース−ドレインを通じて流れる飽和電流を示しており、(c)は、VDS=4Vの飽和領域におけるON/OFF電流比を示している。

【図10】単結晶シリコンリボン製造の概略的プロセスフローを示す図である。図中、(a)は、(111)Si表面におけるSF6プラズマエッチング溝を示している。(b)では、Ti/Au層の熱酸化及び傾斜型蒸着が側面を不動態化している。(c)では、最後に、高温KOH/IPA/H2O溶液がSiリボンをアンダーカットしている。(d)は、部分的にアンダーカットされたリボンの断面SEM画像である。(e)は、切り離されたフレキシブルリボンを示している。

【図11】異方性ウェットエッチングのアンダーカットにより形成された微細構造シリコンの原子間力顕微鏡検査写真であり、(a)は、底面が露出したPDMSスタンプ上のリボンのAFM高さ画像であり、リボンは、それらの縁部で測定された厚さが115〜130nmであり、中央で下方へと湾曲している。(b)は、550nm厚のリボンの底面のAFM画像であり、KOH/IPA/H2Oアンダーカットによってもたらされたナノスケールの粗さを示している。

【図12】微細構造シリコンを「ドナー」ウエハからプラスチック基板へと転写するための概略的プロセスフローを示す図である。図中、(a)では、ウエハに対して固定されるアンダーカットリボンを有するチップに対してPDMSスタンプが重なり合う。(b)では、リボンがスタンプに結合し、スタンプを引き剥がすことによりリボンをウエハから除去することができる。(c)では、次いで、リボンがスタンプからプラスチック基板へと印刷される。(d)は、ドナーウエハに対して固定される略完全にアンダーカットされたリボンのSEM画像である。(e)は、ドナーから除去されかつスタンプに固定されたリボンの光学顕微鏡写真である。(f)は、転写されたシリコンリボンから形成されるTFTを収容するフレキシブルプラスチック「チップ」の写真である。

【図13】PET/ITO基板上の単結晶シリコンボトム−ゲートトランジスタの電気的特性を示す図であり、L=100μ、W=100μm、線形移動度360cm2V−1s−1、飽和移動度100cm2V−1s−1であり、図中、(a)は、デバイスの挿入画上面図を伴う約4000ON/OFF比を示す伝達特性(VD=0.1V)を示しており、(b)は電流−電圧(I−V)特性を示している。

【図14A】高電子移動度トランジスタを製造するためのヘテロ構造GaNウエハ(HEMT、AlGaNとGaNとの間の界面に形成される2次元電子ガス(2DEG))の概略図である。

【図14B】プラスチック基板上のHEMT形状の概略図である。

【図14C】Ws−GaNリボンの端部で二つの「幅狭ブリッジ」によって支持されたWs−GaN構造の概略図であり、自立Ws−GaN素子を形成するためにスマート異方性エッチング方向が使用される。

【図15】プラスチック基板上にWs−GaN HEMTを形成するためのステップの概略図である。

【図16】(a)は、下側に位置するSiのTMAHウェットエッチング前のGaNウエハを示す図である。(b)は、TMAHエッチング後の自立GaNリボンを示す図である(犠牲Si層のエッチングされた領域とエッチングされていない領域との間の色の違いに留意されたい)。(c)及び(d)は、下側に位置するSiのTMAH異方性エッチングの中間ステップのSEM画像である。(e)は、μs−GaN物体を用いてファンデルワールス力によってインク付けされたODMSスラブのSEM画像である。(f)は、PUコーティングされたPETへ転写されたμs−GaNのSEM画像である。容易に視認できるように、金属領域及び高分子領域が人為的に色付けされている。

【図17】プラスチック基板上にWs−GaNから形成された高性能HEMTを示す図である。図中、(a)及び(b)は、実際のフレキシブルWs−GaNデバイスの光学顕微鏡写真であり、断面デバイス形状の概略図が図14Bに示されている。(c)は、一連のゲート電圧(Vg=−4V〜1V)におけるWs−GaN系HEMTのI−V曲線を示しており、デバイスのチャネル長、チャネル幅及びゲート幅は各々、20Wm、170Wm及び5Wmであった。(d)は、一定のソース−ドレイン電圧(Vds=2V)で測定された伝達特性であり、1.5mSの相互コンダクタンスを示している。

【図18】(a)は、実際の曲げステージ及びプラスチックデバイスの光学画像であり、(b)は、異なる曲げ半径(及びその対応する歪み)で得られた伝達曲線であり、(c)は、プラスチックシートが最大曲げ半径で曲げられるとき(オレンジ)及び曲げサイクル後に平らにされるとき(青)に得られたI−V曲線である。

【図19】印刷可能半導体素子の多層配列を形成するための本発明の方法を示すプロセスフロー概略図である。