印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイス、及び伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを提供する。

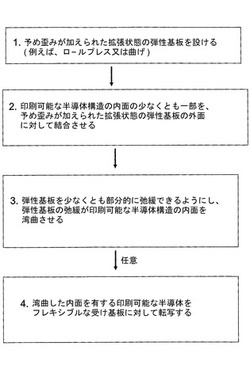

【解決手段】予め歪みが加えられた拡張状態の弾性基板が与えられる。印刷可能な半導体構造の内面の少なくとも一部を、予め歪みが加えられた拡張状態の弾性基板の外面に対して結合される。半導体構造の内面を湾曲させることにより弾性基板を少なくとも部分的に緩和状態へと弛緩させる。湾曲した内面を有する半導体構造が弾性基板から他の基板、好ましくはフレキシブル基板へと転写される。

【解決手段】予め歪みが加えられた拡張状態の弾性基板が与えられる。印刷可能な半導体構造の内面の少なくとも一部を、予め歪みが加えられた拡張状態の弾性基板の外面に対して結合される。半導体構造の内面を湾曲させることにより弾性基板を少なくとも部分的に緩和状態へと弛緩させる。湾曲した内面を有する半導体構造が弾性基板から他の基板、好ましくはフレキシブル基板へと転写される。

Notice: Undefined index: DEJ in /mnt/www/gzt_disp.php on line 298

【特許請求の範囲】

【請求項1】

支持面を有する予め歪みが加えられた弾性基板と、

少なくとも1つの凹領域及び少なくとも1つの凸領域を有する湾曲した表面を有する印刷可能な結晶半導体構造と、

を備え、

前記湾曲した表面の少なくとも一部は、前記予め歪みが加えられた弾性基板の前記支持面に対して結合されており、

前記半導体構造は、歪を受けている湾曲構造を備える、伸縮可能な半導体素子。

【請求項2】

前記湾曲した表面は、複数の凸領域、複数の凹領域、又は、複数の凸領域並びに複数の凹領域の両方を有する、請求項1に記載の伸縮可能な半導体素子。

【請求項3】

前記湾曲した表面は、周期的な波又は非周期的な波によって特徴づけられる輪郭形状を有している、請求項1に記載の伸縮可能な半導体素子。

【請求項4】

前記結晶半導体構造は、湾曲したリボンを有し、当該リボンは、当該リボンの長さを拡張する周期的な波によって特徴付けられる輪郭形状を有する、請求項1に記載の伸縮可能な半導体素子。

【請求項5】

前記湾曲リボンは、5ミクロン〜50ミクロンの範囲にわたって選択される幅と、50ナノメートル〜500ナノメートルにわたって選択された厚さと、を有している、請求項4に記載の伸縮可能な半導体素子。

【請求項6】

前記予め歪みが加えられた弾性基板は、ポリ(ジメチルシロキサン)を備えている、請求項1に記載の伸縮可能な半導体素子。

【請求項7】

前記結晶半導体構造は、単結晶無機半導体材料である、請求項1に記載の伸縮可能な半導体素子。

【請求項8】

前記湾曲した表面は、前記支持面に対して連続的に結合されている、又は、前記湾曲した表面は、前記湾曲した表面に沿う選択された点で前記支持面に対して結合されている、請求項1に記載の伸縮可能な半導体素子。

【請求項9】

前記結晶半導体構造は、Si、Ge、ダイヤモンド、SiC、SiGe、AlSb、AlAs、Aln、AlP、BN、GaSb、GaAs、GaN、GaP、InSb、InAs、InN、InP、AlxGa1−xAs、CsSe、CdS、CdSe、CdTe、ZnO、ZnSe、ZnS、HgS、PbS、ZnTe、CuCl、PbS、PbTe、SnS、PbI2、MoS2、GaSe、CuO、Cu2O、AlGaAs、AlInAs、AlInP、GaAsP、GaInAs、GaInP、AlGaAsSb、AlGaInP、及び、GaInAsPからなる群から選択される材料である、請求項1に記載の伸縮可能な半導体素子。

【請求項10】

前記歪は0.5%よりも大きい、請求項1に記載の伸縮可能な半導体素子。

【請求項11】

前記歪は30%よりも小さい、請求項1に記載の伸縮可能な半導体素子。

【請求項12】

伸縮可能な半導体素子を形成するための方法であって、

内面を有する印刷可能な結晶半導体構造を準備するステップと、

予め歪みが加えられた拡張状態の弾性基板を設けるステップであって、前記弾性基板が外面を有しているステップと、

前記印刷可能な半導体構造の前記内面の少なくとも一部を、前記予め歪みが加えられた拡張状態の弾性基板の前記外面に対して結合させるステップと、

前記弾性基板を緩和状態まで少なくとも部分的に弛緩できるようにするステップであって、前記弾性基板の弛緩が前記印刷可能な半導体構造の前記内面を湾曲させ、それにより、湾曲した内面を有する前記伸縮可能な半導体素子を形成する、ステップと、

を備える方法。

【請求項13】

前記予め歪みが加えられた弾性基板は、第1の軸に沿って拡張される、又は、前記第1の軸並びに前記第1の軸と直交する第2の軸に沿って拡張される、請求項12に記載の方法。

【請求項14】

前記結晶半導体構造は、単結晶無機半導体材料である、請求項12に記載の方法。

【請求項15】

前記予め歪みが加えられた拡張状態の弾性基板は、前記弾性基板を曲げること、又は、前記弾性基板を圧延することにより形成される、請求項12に記載の方法。

【請求項16】

前記湾曲した内面を有する前記半導体をフレキシブルな受け基板に転写するステップをさらに備える、請求項12に記載の方法。

【請求項17】

支持面を有する予め歪みが加えられた弾性基板と、

複数の集積デバイス部品を備える電気デバイスと、

を備え、

前記電気デバイスは、少なくとも1つの凹領域及び少なくとも1つの凸領域を含む湾曲した表面を有する湾曲形状に設けられ、

前記湾曲した表面の少なくとも一部は、前記予め歪みが加えられた弾性基板の前記支持面に対して結合され、

前記複数の集積デバイス部品は、歪を受けている湾曲構造を備え、

前記複数の集積デバイス部品は、前記湾曲構造に設けられた結晶半導体構造を含む、伸縮可能な電気回路。

【請求項18】

前記集積デバイス部品は、

半導体素子と、

誘電体素子と、

電極と、

導体素子と、

ドープ半導体素子と、

から成るグループから選択される、請求項17に記載の伸縮可能な電気回路。

【請求項19】

前記湾曲した表面は、周期的な波又は非周期的な波によって特徴づけられる輪郭形状を有している請求項17に記載の伸縮可能な電気回路。

【請求項20】

前記歪を受けている湾曲構造は、薄膜トランジスタ、又は、薄膜トランジスタの配列を備える、請求項17に記載の伸縮可能な電気回路。

【請求項21】

前記電気デバイスの前記結晶半導体構造は、単結晶無機半導体材料である、請求項17に記載の伸縮可能な電気回路。

【請求項22】

前記結晶半導体構造は、Si、Ge、ダイヤモンド、SiC、SiGe、AlSb、AlAs、Aln、AlP、BN、GaSb、GaAs、GaN、GaP、InSb、InAs、InN、InP、AlxGa1−xAs、CsSe、CdS、CdSe、CdTe、ZnO、ZnSe、ZnS、HgS、PbS、ZnTe、CuCl、PbS、PbTe、SnS、PbI2、MoS2、GaSe、CuO、Cu2O、AlGaAs、AlInAs、AlInP、GaAsP、GaInAs、GaInP、AlGaAsSb、AlGaInP、及び、GaInAsPからなる群から選択される材料である、請求項17に記載の伸縮可能な電気回路。

【請求項23】

前記電気デバイスは、10ミクロン未満の正味の厚さを有する、請求項17に記載の伸縮可能な電気回路。

【請求項24】

前記電気デバイスは、トランジスタ、ダイオード、発光ダイオード、レーザ、有機発光ダイオード、マイクロ電子機械システム、及び、ナノ電子機械システムからなる群から選択される、請求項17に記載の伸縮可能な電気回路。

【請求項25】

前記歪は、0.5%よりも大きい、請求項17に記載の伸縮可能な電気回路。

【請求項26】

前記歪は30%よりも小さい、請求項17に記載の伸縮可能な電気回路。

【請求項27】

伸縮可能な電気回路を形成するための方法であって、

内面を有する印刷可能な電気回路を準備するステップと、

予め歪みが加えられた拡張状態の弾性基板を設けるステップであって、前記弾性基板が外面を有している、ステップと、

前記印刷可能な電気回路の前記内面の少なくとも一部を、前記予め歪みが加えられた拡張状態の弾性基板の前記外面に対して結合させるステップと、

前記弾性基板を緩和状態まで少なくとも部分的に弛緩できるようにするステップであって、前記弾性基板の弛緩が前記印刷可能な電気回路の前記内面を湾曲させ、それにより、前記内面の少なくとも1つの湾曲が形成され、それにより、湾曲した内面を有する前記伸縮可能な電気回路を形成するステップと、

を備える方法。

【請求項28】

前記電気回路は、複数の集積デバイス部品を備えており、

前記複数の集積デバイス部品は、

半導体素子と、

誘電体素子と、

電極と、

導体素子と、

ドープ半導体素子と、

から成るグループから選択される、請求項27に記載の方法。

【請求項29】

前記印刷可能な電気回路は、薄膜トランジスタを備える、請求項27に記載の方法。

【請求項30】

前記予め歪みが加えられた弾性基板は、第1の軸に沿って拡張される、又は、前記第1の軸並びに前記第1の軸と直交する第2の軸に沿って拡張される、請求項27に記載の方法。

【請求項31】

前記印刷可能な電気回路は、単結晶無機半導体構造を備える、請求項30に記載の方法。

【請求項32】

前記予め歪みが加えられた拡張状態の弾性基板は、前記弾性基板を曲げること、又は、前記弾性基板を圧延することにより形成される、請求項27に記載の方法。

【請求項33】

前記湾曲した内面を有する前記印刷可能な電気回路をフレキシブルな受け基板に転写するステップをさらに備える、請求項27に記載の方法。

【請求項34】

基板の受け面上に印刷可能半導体素子を組み立てるための方法であって、

単一無機半導体構造を備える前記印刷可能半導体素子を準備するステップと、

前記印刷可能半導体素子を、接触面を有するコンフォーマブルな転写デバイスと接触させるステップであって、前記接触面と前記印刷可能半導体素子との間の接触が前記印刷可能半導体素子を前記接触面に対して結合させ、それにより、前記印刷可能半導体素子がその上に配置された前記接触面が形成されるステップと、

前記接触面上に配置された前記印刷可能半導体素子を前記基板の前記受け面と接触させるステップと、

前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子とを分離させるステップであって、前記印刷可能半導体素子が前記受け面上に転写され、それにより、前記基板の前記受け面上に前記印刷可能半導体素子を組み立てるステップと、

を備える方法。

【請求項35】

前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子の外面との間でコンフォーマル接触が成される、請求項34に記載の方法。

【請求項36】

その上に配置された前記印刷可能半導体素子を有する前記接触面と、前記基板の前記受け面との間でコンフォーマル接触が成される、請求項34に記載の方法。

【請求項37】

前記コンフォーマブルな転写デバイスがエラストマースタンプを備えている、請求項34に記載の方法。

【請求項38】

前記印刷可能半導体素子をコンフォーマブルな転写デバイスと接触させる前記ステップ、前記接触面上に配置された前記印刷可能半導体素子を前記基板の前記受け面と接触させる前記ステップ、及び、前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子とを分離させる前記ステップが、前記印刷可能半導体素子を前記受け面上に乾式転写印刷するステップを備える、請求項34に記載の方法。

【請求項39】

それぞれが単一無機半導体構造を備える更なる複数の印刷可能半導体素子を準備するステップと、

前記印刷可能半導体素子を、接触面を有するコンフォーマブルな転写デバイスと接触させるステップであって、前記接触面と前記印刷可能半導体素子との間の接触が前記印刷可能半導体素子を前記接触面に対して結合させるとともに、前記印刷可能半導体素子の選択されたパターンを備える相対的な方向で、その上に配置された前記印刷可能半導体素子を有する前記接触面を形成するステップと、

前記接触面上に配置された前記印刷可能半導体素子を前記基板の前記受け面と接触させるステップと、

前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子とを分離させるステップであって、前記選択されたパターンを備える前記相対的な方向で前記印刷可能半導体素子が前記受け面上に転写されるステップと、

をさらに備える、請求項34に記載の方法。

【請求項40】

前記印刷可能半導体素子が、前記選択されたパターンを備える前記相対的な方向でマザー基板上に設けられ、前記相対的な方向が前記受け面に対する転写中に維持される、請求項39に記載の方法。

【請求項41】

前記印刷可能半導体素子は、単結晶無機半導体を備える、請求項34に記載の方法。

【請求項42】

前記印刷可能半導体素子は、ダイオード、LED、トランジスタ、及び、太陽電池からなる群から選択される、請求項34に記載の方法。

【請求項43】

前記印刷可能半導体素子は、50nm〜1mmの範囲から選択される幅と、1μm〜1mmの範囲から選択される長さと、10nm〜100μmの範囲から選択される厚さを有する、請求項34に記載の方法。

【請求項44】

前記印刷可能半導体素子の少なくとも1つは、幅に対する厚さの比が0.1以下である、請求項34に記載の方法。

【請求項45】

前記印刷可能半導体素子を準備する前記ステップが、マザー基板上に選択された方向で前記半導体素子を設ける工程を備え、前記半導体素子の前記選択された方向が、前記マザー基板と前記印刷可能半導体素子とを結合するアライメント維持要素により、前記接触面との接触中に維持される、請求項34に記載の方法

【請求項46】

トランジスタと、

太陽電池と、

フォトダイオードと、

発光ダイオードと、

マイクロ電子機械デバイスと、

ナノ電子機械デバイスと、

レーザと、

P − N 接合と、

相補型論理回路と、

から成るグループから選択される電気デバイスを製造するための方法を備える、請求項34に記載の方法。

【請求項47】

印刷可能半導体素子を製造するための方法であって、

外面を有するウエハを準備するステップであって、前記ウエハが無機半導体材料を備えるステップと、

マスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングすることにより、レリーフ構造と前記ウエハの少なくとも1つの露出面とを形成するステップであって、前記レリーフ構造が1つのマスキングされた側と1つ以上のマスキングされていない側とを有するステップと、

前記レリーフ構造の前記マスキングされていない側の少なくとも一部に対してマスクを適用するステップと、

前記ウエハの前記露出面を少なくとも部分的にエッチングすることにより、前記印刷可能半導体素子を製造するステップと、

を備える方法。

【請求項48】

印刷可能半導体素子を製造するための方法であって、

外面を有するウエハを準備するステップであって、前記ウエハが無機半導体を備えるステップと、

第1のマスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングすることにより、複数のレリーフ構造を形成するステップと、

前記ウエハをアニールすることにより、アニール外面を形成するステップと、

第2のマスクを適用することにより前記アニール外面の選択された領域をマスキングするステップと、

前記アニール外面をエッチングすることにより、前記印刷可能半導体素子を形成するステップと、

を備える方法。

【請求項49】

印刷可能半導体素子を製造するための方法であって、

外面を有する超薄ウエハを準備するステップであって、前記ウエハが無機半導体を備え且つ前記外面と直交する軸に沿って選択された厚さを有するステップと、

マスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングするステップであって、前記ウエハが前記外面と直交する前記軸に沿った前記厚さの全体にわたってエッチングされ、それにより、前記印刷可能半導体素子を形成するステップと、

を備える、方法。

【請求項50】

1つ以上のアライメント維持要素を介してマザーウエハに対して接続される印刷可能半導体素子を製造するための方法であって、

外面を有する前記マザーウエハを準備するステップであって、前記ウエハが無機半導体材料を備えるステップと、

マスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングすることにより、レリーフ構造と前記ウエハの少なくとも1つの露出面とを形成するステップであって、前記レリーフ構造が1つのマスキングされた側と1つ以上のマスキングされていない側とを有するステップと、

前記ウエハの前記露出面をエッチングするステップと、

前記レリーフ構造の完全な解放が妨げられるように前記露出面のエッチングを停止させ、それにより、1つ以上のアライメント維持要素を介してマザーウエハに対して接続される前記印刷可能半導体素子を製造するステップと、

を備える方法。

【請求項51】

基板の受け面上に印刷可能半導体素子を組み立てるための方法であって、

単一無機半導体構造を備える前記印刷可能半導体素子を準備するステップであって、前記印刷可能半導体素子が500ナノメートル以上の少なくとも1つの断面寸法を有するステップと、

前記半導体素子を溶媒中に分散させ、それにより、前記溶媒中に前記半導体素子を備える懸濁液を形成するステップと、

前記懸濁液を前記受け面上にソリューション印刷することにより前記半導体素子を前記基板へ供給し、それにより、前記受け面上に前記半導体素子を組み立てるステップと、

を備える方法。

【請求項52】

基板の受け面上に印刷可能半導体素子を組み立てるための方法であって、

単一結晶無機半導体構造及びハンドル素子を備える前記半導体素子を準備するステップと、

溶媒中に前記半導体素子を分散させることにより、前記溶媒中に前記半導体素子を備える懸濁液を形成するステップと、

前記懸濁液を前記受け面上に分散させることにより前記半導体素子を前記基板に対して供給するステップと、

磁場、電場、又は、これらの両方を与えることにより前記受け面上で前記半導体素子をアライメントするステップであって、前記磁場、電場、又は、これらの両方が前記ハンドル素子と相互に作用することにより、前記半導体素子を選択された位置及び方向へ移動させる力が形成され、それにより、前記受け面上に前記半導体素子を組み立てるステップと、

を備える方法。

【請求項53】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置されるとともに、それぞれが500ナノメートル以上の少なくとも1つの断面寸法を有する単一無機半導体構造を備える複数の印刷可能半導体素子と、

を備える電気デバイス。

【請求項54】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置されるとともに、それぞれが単一無機半導体構造を備え、前記各無機半導体構造中の重金属不純物の濃度が原子100万個につき1以下である複数の印刷可能半導体素子と、

を備える電気デバイス。

【請求項55】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置されるとともに、前記第1の電極、前記第2の電極又はこれらの両方に対するそれぞれの位置が50ミクロンの範囲内となるように選択される複数の印刷可能半導体素子と、

を備える電気デバイス。

【請求項56】

500ナノメートル以上の少なくとも1つの断面寸法を有する単一結晶無機半導体構造を備える印刷可能なP−N接合であって、前記結晶無機半導体構造がNドープ領域と電気的に接触するPドープ領域を備えているP−N接合。

【請求項57】

プラスチック基板により支持されるトランジスタにおいて、

単一結晶無機半導体構造を備える印刷可能半導体素子と電気的に接触するソース電極と、

前記印刷可能半導体素子と電気的に接触するドレイン電極と、

前記ソース電極及びドレイン電極から分離されるゲート電極であって、前記ゲート電極に対する電位の印加が、前記印刷可能半導体素子を介したソース電極とドレイン電極との間の電子の流れに影響を与えるゲート電極と、

を備え、

100cm2V−1s−1以上のデバイス電界効果移動度を有しているトランジスタ。

【請求項58】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置される複数の印刷可能半導体素子と、

を備え、

前記印刷可能半導体素子の少なくとも1つの物理的寸法が10%未満変化する電気デバイスの配列。

【請求項59】

単一結晶無機半導体構造と、

前記結晶無機半導体構造に接続された少なくとも1つのハンドル素子と、

を備える印刷可能半導体素子。

【請求項1】

支持面を有する予め歪みが加えられた弾性基板と、

少なくとも1つの凹領域及び少なくとも1つの凸領域を有する湾曲した表面を有する印刷可能な結晶半導体構造と、

を備え、

前記湾曲した表面の少なくとも一部は、前記予め歪みが加えられた弾性基板の前記支持面に対して結合されており、

前記半導体構造は、歪を受けている湾曲構造を備える、伸縮可能な半導体素子。

【請求項2】

前記湾曲した表面は、複数の凸領域、複数の凹領域、又は、複数の凸領域並びに複数の凹領域の両方を有する、請求項1に記載の伸縮可能な半導体素子。

【請求項3】

前記湾曲した表面は、周期的な波又は非周期的な波によって特徴づけられる輪郭形状を有している、請求項1に記載の伸縮可能な半導体素子。

【請求項4】

前記結晶半導体構造は、湾曲したリボンを有し、当該リボンは、当該リボンの長さを拡張する周期的な波によって特徴付けられる輪郭形状を有する、請求項1に記載の伸縮可能な半導体素子。

【請求項5】

前記湾曲リボンは、5ミクロン〜50ミクロンの範囲にわたって選択される幅と、50ナノメートル〜500ナノメートルにわたって選択された厚さと、を有している、請求項4に記載の伸縮可能な半導体素子。

【請求項6】

前記予め歪みが加えられた弾性基板は、ポリ(ジメチルシロキサン)を備えている、請求項1に記載の伸縮可能な半導体素子。

【請求項7】

前記結晶半導体構造は、単結晶無機半導体材料である、請求項1に記載の伸縮可能な半導体素子。

【請求項8】

前記湾曲した表面は、前記支持面に対して連続的に結合されている、又は、前記湾曲した表面は、前記湾曲した表面に沿う選択された点で前記支持面に対して結合されている、請求項1に記載の伸縮可能な半導体素子。

【請求項9】

前記結晶半導体構造は、Si、Ge、ダイヤモンド、SiC、SiGe、AlSb、AlAs、Aln、AlP、BN、GaSb、GaAs、GaN、GaP、InSb、InAs、InN、InP、AlxGa1−xAs、CsSe、CdS、CdSe、CdTe、ZnO、ZnSe、ZnS、HgS、PbS、ZnTe、CuCl、PbS、PbTe、SnS、PbI2、MoS2、GaSe、CuO、Cu2O、AlGaAs、AlInAs、AlInP、GaAsP、GaInAs、GaInP、AlGaAsSb、AlGaInP、及び、GaInAsPからなる群から選択される材料である、請求項1に記載の伸縮可能な半導体素子。

【請求項10】

前記歪は0.5%よりも大きい、請求項1に記載の伸縮可能な半導体素子。

【請求項11】

前記歪は30%よりも小さい、請求項1に記載の伸縮可能な半導体素子。

【請求項12】

伸縮可能な半導体素子を形成するための方法であって、

内面を有する印刷可能な結晶半導体構造を準備するステップと、

予め歪みが加えられた拡張状態の弾性基板を設けるステップであって、前記弾性基板が外面を有しているステップと、

前記印刷可能な半導体構造の前記内面の少なくとも一部を、前記予め歪みが加えられた拡張状態の弾性基板の前記外面に対して結合させるステップと、

前記弾性基板を緩和状態まで少なくとも部分的に弛緩できるようにするステップであって、前記弾性基板の弛緩が前記印刷可能な半導体構造の前記内面を湾曲させ、それにより、湾曲した内面を有する前記伸縮可能な半導体素子を形成する、ステップと、

を備える方法。

【請求項13】

前記予め歪みが加えられた弾性基板は、第1の軸に沿って拡張される、又は、前記第1の軸並びに前記第1の軸と直交する第2の軸に沿って拡張される、請求項12に記載の方法。

【請求項14】

前記結晶半導体構造は、単結晶無機半導体材料である、請求項12に記載の方法。

【請求項15】

前記予め歪みが加えられた拡張状態の弾性基板は、前記弾性基板を曲げること、又は、前記弾性基板を圧延することにより形成される、請求項12に記載の方法。

【請求項16】

前記湾曲した内面を有する前記半導体をフレキシブルな受け基板に転写するステップをさらに備える、請求項12に記載の方法。

【請求項17】

支持面を有する予め歪みが加えられた弾性基板と、

複数の集積デバイス部品を備える電気デバイスと、

を備え、

前記電気デバイスは、少なくとも1つの凹領域及び少なくとも1つの凸領域を含む湾曲した表面を有する湾曲形状に設けられ、

前記湾曲した表面の少なくとも一部は、前記予め歪みが加えられた弾性基板の前記支持面に対して結合され、

前記複数の集積デバイス部品は、歪を受けている湾曲構造を備え、

前記複数の集積デバイス部品は、前記湾曲構造に設けられた結晶半導体構造を含む、伸縮可能な電気回路。

【請求項18】

前記集積デバイス部品は、

半導体素子と、

誘電体素子と、

電極と、

導体素子と、

ドープ半導体素子と、

から成るグループから選択される、請求項17に記載の伸縮可能な電気回路。

【請求項19】

前記湾曲した表面は、周期的な波又は非周期的な波によって特徴づけられる輪郭形状を有している請求項17に記載の伸縮可能な電気回路。

【請求項20】

前記歪を受けている湾曲構造は、薄膜トランジスタ、又は、薄膜トランジスタの配列を備える、請求項17に記載の伸縮可能な電気回路。

【請求項21】

前記電気デバイスの前記結晶半導体構造は、単結晶無機半導体材料である、請求項17に記載の伸縮可能な電気回路。

【請求項22】

前記結晶半導体構造は、Si、Ge、ダイヤモンド、SiC、SiGe、AlSb、AlAs、Aln、AlP、BN、GaSb、GaAs、GaN、GaP、InSb、InAs、InN、InP、AlxGa1−xAs、CsSe、CdS、CdSe、CdTe、ZnO、ZnSe、ZnS、HgS、PbS、ZnTe、CuCl、PbS、PbTe、SnS、PbI2、MoS2、GaSe、CuO、Cu2O、AlGaAs、AlInAs、AlInP、GaAsP、GaInAs、GaInP、AlGaAsSb、AlGaInP、及び、GaInAsPからなる群から選択される材料である、請求項17に記載の伸縮可能な電気回路。

【請求項23】

前記電気デバイスは、10ミクロン未満の正味の厚さを有する、請求項17に記載の伸縮可能な電気回路。

【請求項24】

前記電気デバイスは、トランジスタ、ダイオード、発光ダイオード、レーザ、有機発光ダイオード、マイクロ電子機械システム、及び、ナノ電子機械システムからなる群から選択される、請求項17に記載の伸縮可能な電気回路。

【請求項25】

前記歪は、0.5%よりも大きい、請求項17に記載の伸縮可能な電気回路。

【請求項26】

前記歪は30%よりも小さい、請求項17に記載の伸縮可能な電気回路。

【請求項27】

伸縮可能な電気回路を形成するための方法であって、

内面を有する印刷可能な電気回路を準備するステップと、

予め歪みが加えられた拡張状態の弾性基板を設けるステップであって、前記弾性基板が外面を有している、ステップと、

前記印刷可能な電気回路の前記内面の少なくとも一部を、前記予め歪みが加えられた拡張状態の弾性基板の前記外面に対して結合させるステップと、

前記弾性基板を緩和状態まで少なくとも部分的に弛緩できるようにするステップであって、前記弾性基板の弛緩が前記印刷可能な電気回路の前記内面を湾曲させ、それにより、前記内面の少なくとも1つの湾曲が形成され、それにより、湾曲した内面を有する前記伸縮可能な電気回路を形成するステップと、

を備える方法。

【請求項28】

前記電気回路は、複数の集積デバイス部品を備えており、

前記複数の集積デバイス部品は、

半導体素子と、

誘電体素子と、

電極と、

導体素子と、

ドープ半導体素子と、

から成るグループから選択される、請求項27に記載の方法。

【請求項29】

前記印刷可能な電気回路は、薄膜トランジスタを備える、請求項27に記載の方法。

【請求項30】

前記予め歪みが加えられた弾性基板は、第1の軸に沿って拡張される、又は、前記第1の軸並びに前記第1の軸と直交する第2の軸に沿って拡張される、請求項27に記載の方法。

【請求項31】

前記印刷可能な電気回路は、単結晶無機半導体構造を備える、請求項30に記載の方法。

【請求項32】

前記予め歪みが加えられた拡張状態の弾性基板は、前記弾性基板を曲げること、又は、前記弾性基板を圧延することにより形成される、請求項27に記載の方法。

【請求項33】

前記湾曲した内面を有する前記印刷可能な電気回路をフレキシブルな受け基板に転写するステップをさらに備える、請求項27に記載の方法。

【請求項34】

基板の受け面上に印刷可能半導体素子を組み立てるための方法であって、

単一無機半導体構造を備える前記印刷可能半導体素子を準備するステップと、

前記印刷可能半導体素子を、接触面を有するコンフォーマブルな転写デバイスと接触させるステップであって、前記接触面と前記印刷可能半導体素子との間の接触が前記印刷可能半導体素子を前記接触面に対して結合させ、それにより、前記印刷可能半導体素子がその上に配置された前記接触面が形成されるステップと、

前記接触面上に配置された前記印刷可能半導体素子を前記基板の前記受け面と接触させるステップと、

前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子とを分離させるステップであって、前記印刷可能半導体素子が前記受け面上に転写され、それにより、前記基板の前記受け面上に前記印刷可能半導体素子を組み立てるステップと、

を備える方法。

【請求項35】

前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子の外面との間でコンフォーマル接触が成される、請求項34に記載の方法。

【請求項36】

その上に配置された前記印刷可能半導体素子を有する前記接触面と、前記基板の前記受け面との間でコンフォーマル接触が成される、請求項34に記載の方法。

【請求項37】

前記コンフォーマブルな転写デバイスがエラストマースタンプを備えている、請求項34に記載の方法。

【請求項38】

前記印刷可能半導体素子をコンフォーマブルな転写デバイスと接触させる前記ステップ、前記接触面上に配置された前記印刷可能半導体素子を前記基板の前記受け面と接触させる前記ステップ、及び、前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子とを分離させる前記ステップが、前記印刷可能半導体素子を前記受け面上に乾式転写印刷するステップを備える、請求項34に記載の方法。

【請求項39】

それぞれが単一無機半導体構造を備える更なる複数の印刷可能半導体素子を準備するステップと、

前記印刷可能半導体素子を、接触面を有するコンフォーマブルな転写デバイスと接触させるステップであって、前記接触面と前記印刷可能半導体素子との間の接触が前記印刷可能半導体素子を前記接触面に対して結合させるとともに、前記印刷可能半導体素子の選択されたパターンを備える相対的な方向で、その上に配置された前記印刷可能半導体素子を有する前記接触面を形成するステップと、

前記接触面上に配置された前記印刷可能半導体素子を前記基板の前記受け面と接触させるステップと、

前記コンフォーマブルな転写デバイスの前記接触面と前記印刷可能半導体素子とを分離させるステップであって、前記選択されたパターンを備える前記相対的な方向で前記印刷可能半導体素子が前記受け面上に転写されるステップと、

をさらに備える、請求項34に記載の方法。

【請求項40】

前記印刷可能半導体素子が、前記選択されたパターンを備える前記相対的な方向でマザー基板上に設けられ、前記相対的な方向が前記受け面に対する転写中に維持される、請求項39に記載の方法。

【請求項41】

前記印刷可能半導体素子は、単結晶無機半導体を備える、請求項34に記載の方法。

【請求項42】

前記印刷可能半導体素子は、ダイオード、LED、トランジスタ、及び、太陽電池からなる群から選択される、請求項34に記載の方法。

【請求項43】

前記印刷可能半導体素子は、50nm〜1mmの範囲から選択される幅と、1μm〜1mmの範囲から選択される長さと、10nm〜100μmの範囲から選択される厚さを有する、請求項34に記載の方法。

【請求項44】

前記印刷可能半導体素子の少なくとも1つは、幅に対する厚さの比が0.1以下である、請求項34に記載の方法。

【請求項45】

前記印刷可能半導体素子を準備する前記ステップが、マザー基板上に選択された方向で前記半導体素子を設ける工程を備え、前記半導体素子の前記選択された方向が、前記マザー基板と前記印刷可能半導体素子とを結合するアライメント維持要素により、前記接触面との接触中に維持される、請求項34に記載の方法

【請求項46】

トランジスタと、

太陽電池と、

フォトダイオードと、

発光ダイオードと、

マイクロ電子機械デバイスと、

ナノ電子機械デバイスと、

レーザと、

P − N 接合と、

相補型論理回路と、

から成るグループから選択される電気デバイスを製造するための方法を備える、請求項34に記載の方法。

【請求項47】

印刷可能半導体素子を製造するための方法であって、

外面を有するウエハを準備するステップであって、前記ウエハが無機半導体材料を備えるステップと、

マスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングすることにより、レリーフ構造と前記ウエハの少なくとも1つの露出面とを形成するステップであって、前記レリーフ構造が1つのマスキングされた側と1つ以上のマスキングされていない側とを有するステップと、

前記レリーフ構造の前記マスキングされていない側の少なくとも一部に対してマスクを適用するステップと、

前記ウエハの前記露出面を少なくとも部分的にエッチングすることにより、前記印刷可能半導体素子を製造するステップと、

を備える方法。

【請求項48】

印刷可能半導体素子を製造するための方法であって、

外面を有するウエハを準備するステップであって、前記ウエハが無機半導体を備えるステップと、

第1のマスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングすることにより、複数のレリーフ構造を形成するステップと、

前記ウエハをアニールすることにより、アニール外面を形成するステップと、

第2のマスクを適用することにより前記アニール外面の選択された領域をマスキングするステップと、

前記アニール外面をエッチングすることにより、前記印刷可能半導体素子を形成するステップと、

を備える方法。

【請求項49】

印刷可能半導体素子を製造するための方法であって、

外面を有する超薄ウエハを準備するステップであって、前記ウエハが無機半導体を備え且つ前記外面と直交する軸に沿って選択された厚さを有するステップと、

マスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングするステップであって、前記ウエハが前記外面と直交する前記軸に沿った前記厚さの全体にわたってエッチングされ、それにより、前記印刷可能半導体素子を形成するステップと、

を備える、方法。

【請求項50】

1つ以上のアライメント維持要素を介してマザーウエハに対して接続される印刷可能半導体素子を製造するための方法であって、

外面を有する前記マザーウエハを準備するステップであって、前記ウエハが無機半導体材料を備えるステップと、

マスクを適用することにより前記外面の選択された領域をマスキングするステップと、

前記ウエハの前記外面をエッチングすることにより、レリーフ構造と前記ウエハの少なくとも1つの露出面とを形成するステップであって、前記レリーフ構造が1つのマスキングされた側と1つ以上のマスキングされていない側とを有するステップと、

前記ウエハの前記露出面をエッチングするステップと、

前記レリーフ構造の完全な解放が妨げられるように前記露出面のエッチングを停止させ、それにより、1つ以上のアライメント維持要素を介してマザーウエハに対して接続される前記印刷可能半導体素子を製造するステップと、

を備える方法。

【請求項51】

基板の受け面上に印刷可能半導体素子を組み立てるための方法であって、

単一無機半導体構造を備える前記印刷可能半導体素子を準備するステップであって、前記印刷可能半導体素子が500ナノメートル以上の少なくとも1つの断面寸法を有するステップと、

前記半導体素子を溶媒中に分散させ、それにより、前記溶媒中に前記半導体素子を備える懸濁液を形成するステップと、

前記懸濁液を前記受け面上にソリューション印刷することにより前記半導体素子を前記基板へ供給し、それにより、前記受け面上に前記半導体素子を組み立てるステップと、

を備える方法。

【請求項52】

基板の受け面上に印刷可能半導体素子を組み立てるための方法であって、

単一結晶無機半導体構造及びハンドル素子を備える前記半導体素子を準備するステップと、

溶媒中に前記半導体素子を分散させることにより、前記溶媒中に前記半導体素子を備える懸濁液を形成するステップと、

前記懸濁液を前記受け面上に分散させることにより前記半導体素子を前記基板に対して供給するステップと、

磁場、電場、又は、これらの両方を与えることにより前記受け面上で前記半導体素子をアライメントするステップであって、前記磁場、電場、又は、これらの両方が前記ハンドル素子と相互に作用することにより、前記半導体素子を選択された位置及び方向へ移動させる力が形成され、それにより、前記受け面上に前記半導体素子を組み立てるステップと、

を備える方法。

【請求項53】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置されるとともに、それぞれが500ナノメートル以上の少なくとも1つの断面寸法を有する単一無機半導体構造を備える複数の印刷可能半導体素子と、

を備える電気デバイス。

【請求項54】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置されるとともに、それぞれが単一無機半導体構造を備え、前記各無機半導体構造中の重金属不純物の濃度が原子100万個につき1以下である複数の印刷可能半導体素子と、

を備える電気デバイス。

【請求項55】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置されるとともに、前記第1の電極、前記第2の電極又はこれらの両方に対するそれぞれの位置が50ミクロンの範囲内となるように選択される複数の印刷可能半導体素子と、

を備える電気デバイス。

【請求項56】

500ナノメートル以上の少なくとも1つの断面寸法を有する単一結晶無機半導体構造を備える印刷可能なP−N接合であって、前記結晶無機半導体構造がNドープ領域と電気的に接触するPドープ領域を備えているP−N接合。

【請求項57】

プラスチック基板により支持されるトランジスタにおいて、

単一結晶無機半導体構造を備える印刷可能半導体素子と電気的に接触するソース電極と、

前記印刷可能半導体素子と電気的に接触するドレイン電極と、

前記ソース電極及びドレイン電極から分離されるゲート電極であって、前記ゲート電極に対する電位の印加が、前記印刷可能半導体素子を介したソース電極とドレイン電極との間の電子の流れに影響を与えるゲート電極と、

を備え、

100cm2V−1s−1以上のデバイス電界効果移動度を有しているトランジスタ。

【請求項58】

第1の電極と、

第2の電極と、

それぞれが前記第1及び第2の電極と電気的に接触した状態で位置される複数の印刷可能半導体素子と、

を備え、

前記印刷可能半導体素子の少なくとも1つの物理的寸法が10%未満変化する電気デバイスの配列。

【請求項59】

単一結晶無機半導体構造と、

前記結晶無機半導体構造に接続された少なくとも1つのハンドル素子と、

を備える印刷可能半導体素子。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図4A1】

【図4A2】

【図4B1】

【図4B2】

【図5A】

【図5B】

【図5C】

【図6】

【図7】

【図8】

【図9】

【図10A】

【図10B】

【図10C】

【図10D】

【図10E】

【図10F】

【図10G】

【図10H】

【図11A】

【図11B】

【図11C】

【図11D】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18A】

【図18B】

【図18C】

【図18D】

【図18E】

【図18F】

【図18G】

【図18H】

【図18I】

【図18J】

【図18K】

【図19】

【図20A】

【図20B】

【図20C】

【図20D】

【図20E】

【図20F】

【図21A】

【図21B】

【図21C】

【図21D】

【図21E】

【図21F】

【図21G】

【図22A】

【図22B】

【図22C】

【図23】

【図24】

【図25】

【図26A】

【図26B】

【図27A】

【図27B】

【図27C】

【図28A】

【図28B】

【図29A】

【図29B】

【図30A】

【図30B】

【図31A】

【図31B】

【図31C】

【図31D】

【図32A】

【図32B】

【図33】

【図34A】

【図34B】

【図34C】

【図35A】

【図35B】

【図35C】

【図35D】

【図35E】

【図36A】

【図36B】

【図37B】

【図38】

【図39A】

【図39B】

【図39C】

【図39D】

【図40A】

【図40B】

【図40C】

【図41】

【図42A】

【図42B】

【図42C】

【図43A】

【図43B】

【図43C】

【図44A】

【図44B】

【図44C】

【図44D】

【図46】

【図47】

【図37A】

【図45】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図4A1】

【図4A2】

【図4B1】

【図4B2】

【図5A】

【図5B】

【図5C】

【図6】

【図7】

【図8】

【図9】

【図10A】

【図10B】

【図10C】

【図10D】

【図10E】

【図10F】

【図10G】

【図10H】

【図11A】

【図11B】

【図11C】

【図11D】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18A】

【図18B】

【図18C】

【図18D】

【図18E】

【図18F】

【図18G】

【図18H】

【図18I】

【図18J】

【図18K】

【図19】

【図20A】

【図20B】

【図20C】

【図20D】

【図20E】

【図20F】

【図21A】

【図21B】

【図21C】

【図21D】

【図21E】

【図21F】

【図21G】

【図22A】

【図22B】

【図22C】

【図23】

【図24】

【図25】

【図26A】

【図26B】

【図27A】

【図27B】

【図27C】

【図28A】

【図28B】

【図29A】

【図29B】

【図30A】

【図30B】

【図31A】

【図31B】

【図31C】

【図31D】

【図32A】

【図32B】

【図33】

【図34A】

【図34B】

【図34C】

【図35A】

【図35B】

【図35C】

【図35D】

【図35E】

【図36A】

【図36B】

【図37B】

【図38】

【図39A】

【図39B】

【図39C】

【図39D】

【図40A】

【図40B】

【図40C】

【図41】

【図42A】

【図42B】

【図42C】

【図43A】

【図43B】

【図43C】

【図44A】

【図44B】

【図44C】

【図44D】

【図46】

【図47】

【図37A】

【図45】

【公開番号】特開2012−235133(P2012−235133A)

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−139132(P2012−139132)

【出願日】平成24年6月20日(2012.6.20)

【分割の表示】特願2007−515549(P2007−515549)の分割

【原出願日】平成17年6月2日(2005.6.2)

【出願人】(506175840)ザ ボード オブ トラスティーズ オブ ザ ユニヴァーシティー オブ イリノイ (30)

【Fターム(参考)】

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願番号】特願2012−139132(P2012−139132)

【出願日】平成24年6月20日(2012.6.20)

【分割の表示】特願2007−515549(P2007−515549)の分割

【原出願日】平成17年6月2日(2005.6.2)

【出願人】(506175840)ザ ボード オブ トラスティーズ オブ ザ ユニヴァーシティー オブ イリノイ (30)

【Fターム(参考)】

[ Back to top ]