双方向シリアルバスの通信制御方法および双方向シリアルバススイッチ

【課題】双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる双方向シリアルバスの通信制御方法および双方向シリアルバススイッチを提供する。

【解決手段】双方向シリアルバススイッチ(100)は、マスタデバイス(101)とスレーブデバイス(102)との間の双方向信号を単方向信号に変換するスイッチ(103,104)と、マスタデバイスが出力する信号に従って単方向信号の方向を決定しスイッチを制御するデコード部(105)と、を有する。

【解決手段】双方向シリアルバススイッチ(100)は、マスタデバイス(101)とスレーブデバイス(102)との間の双方向信号を単方向信号に変換するスイッチ(103,104)と、マスタデバイスが出力する信号に従って単方向信号の方向を決定しスイッチを制御するデコード部(105)と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は少数の配線で多数のデバイスを制御するため双方向シリアル通信システムに係り、特に複数のデバイスを接続した双方向シリアルバスの通信制御方法および双方向シリアルバススイッチに関する。

【背景技術】

【0002】

双方向シリアル通信方式はI2C(Inter-Integrated Circuit)やMDIO(Management Data Input/Output)などで使用されている。双方向シリアル通信方式では、たとえばバスを1つのデバイスが占有してしまったり、どれか1つのデバイスがハングアップしてしまったり、デバイスの電源がおちたり、あるいは省エネ制御のために意図的にデバイスの電源を落としたり、という原因によりバスの論理が固定されると、バス自体が使用できなくなるという問題がある。そこで、バスが使用できなくなる事態を避けるために、バスを切り離す手段が提案されている(特許文献1参照)。

【0003】

また、接続されるデバイス数が多くなると浮遊容量が増えるために接続デバイス数が制限されるという問題に対しては、マスタデバイス側のバスと複数のスレーブデバイス側のバスとの間を選択的に接続するスイッチを設け、アドレスデコーダによりデータ転送の対象となるスレーブデバイスが接続されるようにスイッチを制御する方法が提案されている(たとえば特許文献2参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−295069号公報

【特許文献2】特開2000−165421号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献に記載されたようなバススイッチは、FPGA(Field Programmable Gate Array)などのゲートアレイにそのまま組み込むことができない。なぜならばゲートアレイの内部では双方向信号を使用できないからである。また、双方向シリアル通信方式では、マスタデバイスがクロックをドライブするが、ある決まったタイミングで通信方向を切り替えることが必要である。例えば、MDIOではアドレスのフレームの受信からデータの送信までを2クロック以内に完了しなければならない。

【0006】

そこで、本発明の目的は、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる双方向シリアルバスの通信制御方法および双方向シリアルバススイッチを提供することにある。

【課題を解決するための手段】

【0007】

本発明による双方向シリアルバススイッチは、複数のデバイスを双方向シリアル通信可能に接続する双方向シリアルバススイッチであって、第1デバイスと第2デバイスとの間の双方向信号を単方向信号に変換するスイッチ手段と、前記第1デバイスが出力する信号に従って前記単方向信号の方向を決定し前記スイッチ手段を制御する解析手段と、を有することを特徴とする。

【0008】

本発明による双方向シリアルバスの通信制御方法は、第1デバイスが出力する信号に従って、前記第1デバイスと第2デバイスとの間の双方向信号の伝送方向を決定する制御信号を生成し、前記制御信号に従って前記第1デバイスと前記第2デバイスとの間の双方向信号を単方向信号に変換する、ことを特徴とする。

【発明の効果】

【0009】

本発明によれば、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる

【図面の簡単な説明】

【0010】

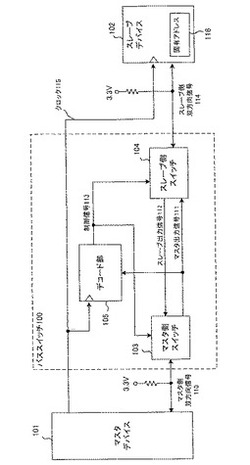

【図1】図1は本発明の第1実施形態によるバススイッチを含む双方向シリアルバスシステムの構成を示すブロック図である。

【図2】図2(A)は図1におけるマスタ側スイッチの構成例を示すブロック図、図2(B)は図1におけるスレーブ側スイッチの構成例を示すブロック図である。

【図3】図3は本実施形態によるバススイッチの動作を説明するためのMDIOリードシーケンスを示す信号波形図である。

【図4】図4は本実施形態によるバススイッチの動作を説明するためのMDIOライトシーケンスを示す信号波形図である。

【図5】図5は本実施形態によるバススイッチの動作を説明するためのI2Cリードシーケンスを示す信号波形図である。

【図6】図6は本実施形態によるバススイッチの動作を説明するためのI2Cライトシーケンスを示す信号波形図である。

【図7】図7は本発明の第2実施形態によるバススイッチを含む双方向シリアルバスシステムの構成を示すブロック図である。

【図8】図8は本発明の他の適用例である双方向シリアルバスシステムの構成を示すブロック図である。

【発明を実施するための形態】

【0011】

本発明によれば、アドレスデコーダの解析結果に応じて信号の転送方向を切り替えるスイッチを設けることで送信中に信号の方向を切り替えることができ、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることが可能となる。たとえばゲートアレイの内部にアドレスを解析するデコーダを設け、マスタデバイスからの出力信号を解析することで、スレーブデバイスからの送信タイミングでスイッチの切替を行なうようにする。

【0012】

以下、本発明の実施形態について図面を参照しながら詳細に説明する。なお、以下の実施形態において、マスタデバイスはCPU(Central Processing Unit)などの演算機能を持ちスレーブデバイスに主導的にアクセスするデバイスのことであり、スレーブデバイスは、EEPROM(Electrically Erasable Programmable Read-Only Memory)やPHY(イーサネット物理層チップ(「イーサネット」は登録商標、以下同じ。))などの機能を持ちマスタデバイスに従属的に接続されるデバイスのことである。

【0013】

1.第1実施形態

1.1)構成

図1において、本発明の第1実施形態による双方向シリアルバススイッチ100は、マスタデバイス101とスレーブデバイス102との間で転送される双方向シリアル信号を単方向信号に変換する機能を有する。より具体的には、双方向シリアルバススイッチ100は、マスタ側スイッチ103、スレーブ側スイッチ104およびデコード部105を有し、マスタ側スイッチ103およびスレーブ側スイッチ104を切り替え制御することで、双方向信号を単方向信号に変換する。

【0014】

マスタ側スイッチ103は、デコード部105から入力する制御信号113に従って、マスタデバイス101から受けたマスタ側双方向信号110をマスタ出力信号111として出力するか、あるいはスレーブ側スイッチ104から入力するスレーブ出力信号112をマスタ側双方向信号110として出力するか切り替える。

【0015】

スレーブ側スイッチ104は、同じく制御信号113に従って、スレーブデバイス102から受けたスレーブ側双方向信号114をスレーブ出力信号112として出力するか、あるいはマスタ側スイッチ103から入力するマスタ出力信号111をスレーブ側双方向信号114として出力するか切り替える。

【0016】

デコード部105は、マスタ出力信号111を入力して動作およびアドレスをデコードし、デコード結果に従ってマスタ側スイッチ103およびスレーブ側スイッチ104へそれぞれ切替制御のための制御信号113を出力する。なお、デコード部105には予め各スレーブデバイスの固有アドレスが記憶されている。またデコード部105にはマスタデバイス101からクロック115が供給され、そのクロック115はさらにスレーブデバイス102にも供給される。

【0017】

図2(A)に示すように、マスタ側スイッチ103は、スレーブからマスタの方向に信号を出力するバッファアンプ103aと、マスタからスレーブの方向に信号を出力するバッファアンプ103bとを有する。バッファアンプ103aの制御端子には制御信号113がそのまま入力し、バッファアンプ103bの制御端子には制御信号113がインバータ103cを通して入力する。したがって、制御信号113が0/1であれば、バッファアンプ103aとバッファアンプ103bの一方が信号を出力するとき(ON)、他方は信号を出力しない(OFF)という切替制御が行われる。ここでは、通常、バッファアンプ103aがOFF、バッファアンプ103bがONとなっているものとする。

【0018】

図2(B)に示すように、スレーブ側スイッチ104は、スレーブからマスタの方向に信号を出力するバッファアンプ104aと、マスタからスレーブの方向に信号を出力するバッファアンプ104bとを有する。バッファアンプ104aの制御端子には制御信号113がそのまま入力し、バッファアンプ104bの制御端子には制御信号113がインバータ104cを通して入力する。したがって、制御信号113が0/1であれば、バッファアンプ104aとバッファアンプ104bの一方が信号を出力するとき(ON)、他方は信号を出力しない(OFF)という切替制御が行われる。ここでは、通常、バッファアンプ104aがOFF、バッファアンプ104bがONとなっているものとする。

【0019】

図2(A)および図2(B)において、制御信号113が通常‘0’であるとすれば、マスタデバイス101がドライブすると、マスタ側スイッチ103はマスタ側双方向信号110を受けてマスタ出力信号111をドライブし、スレーブ側スイッチ104はマスタ出力信号111を受けてスレーブ側双方向信号114をドライブする。逆に、スレーブデバイス102がドライブをする場合には、後述するように制御信号113が‘1’となり、スレーブ側スイッチ104はスレーブ側双方向信号114を受けてスレーブ出力信号112をドライブし、マスタ側スイッチ103はスレーブ出力信号112を受けてマスタ側双方向信号110をドライブする。このようにして、双方向シリアルバススイッチ100の双方向信号と単方向信号との間の変換を実現することができる。

【0020】

1.2)動作(MDIO適用例)

A)MDIOリードフレーム

図3を参照しながら、MDIOインタフェースを一例として、スレーブデバイス102からのデータ読み出し時のリードフレームにおける切替動作を説明する。ここで、MDIOリードフレームは、プリアンブル201、スタートオブフレーム202、オペレーションコード203、PHYアドレス204、レジスタアドレス205、ターンアラウンド206、およびデータ207による区間で区切られている。

【0021】

プリアンブル201では、フレームの先頭を表すために32ビット分で連続して‘1’が出力される(ただし、図3では省略している。)。スタートオブフレーム202では、プリアンブル201で‘1’が連続して続いた後に‘0’→‘1’と変化することでフレームの開始を表す。オペレーションコード203では、リードとライトのどちらのフレームであるかを表し、リードフレームの場合は‘10’が出力される。PHYアドレス204はアクセスするスレーブデバイス102の固有アドレス116を指定し、レジスタアドレス205はスレーブ内部のレジスタのアドレスを指定する。ターンアラウンド206では、マスタデバイス101からスレーブデバイス102への出力切替を行なうため2クロックの間を空ける。リードフレームではスレーブデバイス102からデータがドライブされ、ライトフレームではマスタデバイス101からデータがドライブされる。

【0022】

制御信号113は通常‘0’にセットされているので、マスタ側スイッチ103およびスレーブ側スイッチ104はマスタ出力信号111を選択し、スレーブ出力信号112側は高インピーダンス状態となっている。デコード部105は、マスタ側双方向信号110から出力されたマスタ出力信号111を解析し、リードフレームでPHYアドレス204が予め記憶されたスレーブの固有アドレス116と一致する場合には、ターンアラウンド206からデータの出力が終わるまで制御信号113を‘0’から‘1’にする。

制御信号113が‘1’になることで、マスタ側スイッチ103およびスレーブ側スイッチ104はスレーブ出力信号112を選択し、マスタ出力信号111側は高インピーダンス状態となる。これによって、スレーブデバイス102から出力されたデータがスレーブ出力信号112としてマスタ側へ読みだされる。

【0023】

B)MDIOライトフレーム

図4を参照しながら、スレーブデバイス102へのデータ書き込み時のMDIOライトフレームにおける切替動作を説明する。MDIOライトフレームも、リードフレームと同様に、プリアンブル201、スタートオブフレーム202、オペレーションコード203、PHYアドレス204、レジスタアドレス205、ターンアラウンド206、およびデータ207による区間で区切られている。ただし、オペレーションコード203はライトフレームを表す‘01’となる。また、ライトフレームではマスタデバイス101からデータがドライブされる。

【0024】

デコード部105は、マスタ出力信号111を解析し、ライトフレームでPHYアドレス204がスレーブの固有アドレス116と一致する場合には、制御信号113を変化させず、ターンアラウンド206以降も‘0’のまま維持する。したがって、マスタ側スイッチ103おおびスレーブ側スイッチ104はマスタ出力を選択した状態であり、マスタ側双方向信号110からの書き込みデータはマスタ出力信号111としてスレーブ側へ転送される。

【0025】

1.3)動作(I2C適用例)

図5および図6に本実施形態をI2Cに適用した場合のデコード処理(ライトシーケンスおよびリードシーケンス)を示す。図5および図6に示すように、リード/ライトシーケンスでは、スタート301に続くデバイスアドレス302によってスレーブデバイス102の固有アドレス116と一致する否かが判別され、R/W303によってリードかライトかが判別される。続いて、読み出し/書き込みデータ305が出力されるが、I2Cでは仕様上、8ビット送信完了毎にACK304を返す必要があるために、このタイミングで制御信号113が‘1’となる。

【0026】

図5に示すライトシーケンスでは、デコード部105でスレーブデバイス102がもつ固有アドレス116であるデバイスアドレス302を判別し、スレーブデバイス102に該当する場合には、デバイスアドレス302とR/W303を送信後、すなわち8ビット送信の完了後である9クロック目のタイミングで、制御信号113を‘1’にする。以下同様に8ビット送信完了毎に制御信号113を‘1’にする。

【0027】

図6に示すリードシーケンスでは、途中でスレーブデバイス102側からのドライブに切り替わるので、最初のACK304のタイミングから制御信号を‘1’にし、マスタがACK304を返すタイミングで制御信号を‘0’に切り替える。以上の方法により双方向シリアルバススイッチをI2Cバスに適用することができる。

【0028】

1.4)効果

上述したように、本発明の第1実施形態によるバススイッチ100は、デコード部105の解析結果に応じてマスタ側スイッチ103およびスレーブ側スイッチ104を制御することで、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる。双方向シリアル信号を単方向信号に変換するので、バススイッチ100をゲートアレイにそのまま組み込むことができる。

【0029】

さらに、マスタデバイス101の出力信号からスレーブデバイスのアドレスとオペレーションを解析することで単方向信号の方向を即座に切り替えることができるので、双方向シリアル通信方式で要求される通信方向の切替条件を容易に満たすことができる。

【0030】

2.第2実施形態

上述した第1実施形態では、図1に示すように1つのスレーブデバイスを接続した場合を例示したが、本発明による双方向シリアル通信システムはこれに限定されるものではなく、複数のスレーブデバイスを接続可能である。以下、本発明の第2実施形態として複数のスレーブデバイスを接続したバススイッチについて説明する。

【0031】

2.1)構成

図7に示すように、本実施形態による双方向シリアルバスバススイッチ400は、マスタデバイス401と複数のスレーブデバイス(ここでは2つのスレーブ1デバイス402とスレーブ2デバイス403)の各々との間で転送される双方向シリアル信号を単方向信号に変換する機能を有する。

【0032】

基本的な構成は図1の第1実施形態と同様であるが、図1に示す第1実施形態との比較では、複数のスレーブデバイスにそれぞれ対応したスレーブスイッチ(ここでは2つのスレーブ1スイッチ405とスレーブ2スイッチ406)が設けられ、それらからのスレーブ出力信号がデコード部408からの制御信号414に従ってセレクタ407により選択される構成が追加されている。なお、双方向シリアルバススイッチ400におけるマスタ側スイッチ404、スレーブ1スイッチ405およびスレーブ2スイッチ406については、図2に示す構成と基本的に同じであるから説明は省略する。

【0033】

また、スレーブスイッチの数が増加しているので、それに合わせて制御信号414の論理が追加されている。図7の構成では、マスタデバイス401がドライブする場合には制御信号414が‘0’、スレーブ1デバイス402がドライブする場合には制御信号414が‘1’、スレーブ2デバイス403がドライブする場合には制御信号414が‘2’となる。

【0034】

デコード部408は、図3および図4に示すMDIOの場合、マスタ側から送信されるフレームのPHYアドレスが、スレーブ1デバイス402の固有アドレスかスレーブ2デバイス403の固有アドレスかを判別する。そのために、それぞれのスレーブデバイスの固有アドレスが予め記憶されている。

【0035】

2.2)動作

ライトを行なう場合、どちらのスレーブデバイスにアクセスする場合でもスイッチの切替は不要で制御信号414は‘0’固定になる。

【0036】

スレーブ1デバイス402からリードを行なう場合、マスタデバイス401からリードフレームが送信され、デコード部408でスレーブ1デバイス402の固有アドレスを検出し、ターンアラウンドのタイミングで制御信号414を‘1’にセットする。このとき、セレクタ407はスレーブ1出力信号413を選択した状態となるので、スレーブ1スイッチ405がスレーブ1側の双方向信号415を受けてスレーブ1出力信号413をドライブすると、スレーブ1出力信号413はセレクタ407を通してスレーブ出力信号412としてマスタ側スイッチ404へ転送され、マスタ側スイッチ404がスレーブ出力信号412を入力してマスタ側双方向信号410をドライブする。

【0037】

スレーブ2デバイス403からリードを行なう場合、マスタデバイス401からリードフレームが送信され、デコード部408でスレーブ2デバイス403の固有アドレスを検出し、ターンアラウンドのタイミングで制御信号414を‘2’にセットする。このとき、セレクタ407はスレーブ2出力信号417を選択した状態となるので、スレーブ2スイッチ406がスレーブ2側の双方向信号416を受けてスレーブ2出力信号417をドライブすると、スレーブ2出力信号417はセレクタ407を通してスレーブ出力信号412としてマスタ側スイッチ404へ転送され、マスタ側スイッチ404がスレーブ出力信号412を入力してマスタ側双方向信号410をドライブする。

【0038】

2.3)効果

本実施形態によれば、上述した第1実施形態の効果に加えて、スレーブデバイスを2つ以上接続する場合でも、スレーブ側スイッチと制御信号をスレーブデバイスにあわせて増やすことにより容易に対応できるという効果を有する。

【0039】

このようにハードウェアにより自動的にバスの分離を行なうことで、バスを1つのデバイスが占有してしまったり、どれか1つのデバイスがハングアップしてしまったり、デバイスの電源がおちたり、もしくは省エネ制御のために意図的にデバイスの電源を落としたりということがあってもバス自体が使用できなくなるという事態を回避できる。また、ゲートアレイで分離することで、スレーブデバイスの接続数が増えることによる浮遊容量の影響を受けない。また、デバイスを追加することによるマスタおよびスレーブデバイスのハードウェア変更やアクセスタイミングにあわせた特殊なスイッチ制御を行なうことなく、バスの分離が可能なゲートアレイを提供することができる。

【0040】

3.その他適用例

図8に示すように、双方向シリアルバスバススイッチ500は、上記第2実施形態と同様の構成とした場合、マスタデバイス501と複数のスレーブデバイス(ここでは3つのスレーブデバイス502−504)の各々との間で転送される双方向シリアル信号を単方向信号に変換する機能を有し、さらにマスタデバイス501のマスタ側双方向シリアルバスに直接スレーブデバイス505を接続することもできる。

【産業上の利用可能性】

【0041】

本発明はI2CやMDIOなどの双方向シリアルバスに適用可能である。

【符号の説明】

【0042】

100、400、500 双方向シリアルバススイッチ

101、401、501 マスタデバイス

102、402,403,502−505 スレーブデバイス

103、404 マスタ側スイッチ

104、405,406 スレーブ側スイッチ

105、408 デコード部

110、410 マスタ側双方向信号

111、411 マスタ出力信号

112、412,413,417 スレーブ出力信号

113、414 制御信号

114、415,416 スレーブ側双方向信号

【技術分野】

【0001】

本発明は少数の配線で多数のデバイスを制御するため双方向シリアル通信システムに係り、特に複数のデバイスを接続した双方向シリアルバスの通信制御方法および双方向シリアルバススイッチに関する。

【背景技術】

【0002】

双方向シリアル通信方式はI2C(Inter-Integrated Circuit)やMDIO(Management Data Input/Output)などで使用されている。双方向シリアル通信方式では、たとえばバスを1つのデバイスが占有してしまったり、どれか1つのデバイスがハングアップしてしまったり、デバイスの電源がおちたり、あるいは省エネ制御のために意図的にデバイスの電源を落としたり、という原因によりバスの論理が固定されると、バス自体が使用できなくなるという問題がある。そこで、バスが使用できなくなる事態を避けるために、バスを切り離す手段が提案されている(特許文献1参照)。

【0003】

また、接続されるデバイス数が多くなると浮遊容量が増えるために接続デバイス数が制限されるという問題に対しては、マスタデバイス側のバスと複数のスレーブデバイス側のバスとの間を選択的に接続するスイッチを設け、アドレスデコーダによりデータ転送の対象となるスレーブデバイスが接続されるようにスイッチを制御する方法が提案されている(たとえば特許文献2参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−295069号公報

【特許文献2】特開2000−165421号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献に記載されたようなバススイッチは、FPGA(Field Programmable Gate Array)などのゲートアレイにそのまま組み込むことができない。なぜならばゲートアレイの内部では双方向信号を使用できないからである。また、双方向シリアル通信方式では、マスタデバイスがクロックをドライブするが、ある決まったタイミングで通信方向を切り替えることが必要である。例えば、MDIOではアドレスのフレームの受信からデータの送信までを2クロック以内に完了しなければならない。

【0006】

そこで、本発明の目的は、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる双方向シリアルバスの通信制御方法および双方向シリアルバススイッチを提供することにある。

【課題を解決するための手段】

【0007】

本発明による双方向シリアルバススイッチは、複数のデバイスを双方向シリアル通信可能に接続する双方向シリアルバススイッチであって、第1デバイスと第2デバイスとの間の双方向信号を単方向信号に変換するスイッチ手段と、前記第1デバイスが出力する信号に従って前記単方向信号の方向を決定し前記スイッチ手段を制御する解析手段と、を有することを特徴とする。

【0008】

本発明による双方向シリアルバスの通信制御方法は、第1デバイスが出力する信号に従って、前記第1デバイスと第2デバイスとの間の双方向信号の伝送方向を決定する制御信号を生成し、前記制御信号に従って前記第1デバイスと前記第2デバイスとの間の双方向信号を単方向信号に変換する、ことを特徴とする。

【発明の効果】

【0009】

本発明によれば、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる

【図面の簡単な説明】

【0010】

【図1】図1は本発明の第1実施形態によるバススイッチを含む双方向シリアルバスシステムの構成を示すブロック図である。

【図2】図2(A)は図1におけるマスタ側スイッチの構成例を示すブロック図、図2(B)は図1におけるスレーブ側スイッチの構成例を示すブロック図である。

【図3】図3は本実施形態によるバススイッチの動作を説明するためのMDIOリードシーケンスを示す信号波形図である。

【図4】図4は本実施形態によるバススイッチの動作を説明するためのMDIOライトシーケンスを示す信号波形図である。

【図5】図5は本実施形態によるバススイッチの動作を説明するためのI2Cリードシーケンスを示す信号波形図である。

【図6】図6は本実施形態によるバススイッチの動作を説明するためのI2Cライトシーケンスを示す信号波形図である。

【図7】図7は本発明の第2実施形態によるバススイッチを含む双方向シリアルバスシステムの構成を示すブロック図である。

【図8】図8は本発明の他の適用例である双方向シリアルバスシステムの構成を示すブロック図である。

【発明を実施するための形態】

【0011】

本発明によれば、アドレスデコーダの解析結果に応じて信号の転送方向を切り替えるスイッチを設けることで送信中に信号の方向を切り替えることができ、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることが可能となる。たとえばゲートアレイの内部にアドレスを解析するデコーダを設け、マスタデバイスからの出力信号を解析することで、スレーブデバイスからの送信タイミングでスイッチの切替を行なうようにする。

【0012】

以下、本発明の実施形態について図面を参照しながら詳細に説明する。なお、以下の実施形態において、マスタデバイスはCPU(Central Processing Unit)などの演算機能を持ちスレーブデバイスに主導的にアクセスするデバイスのことであり、スレーブデバイスは、EEPROM(Electrically Erasable Programmable Read-Only Memory)やPHY(イーサネット物理層チップ(「イーサネット」は登録商標、以下同じ。))などの機能を持ちマスタデバイスに従属的に接続されるデバイスのことである。

【0013】

1.第1実施形態

1.1)構成

図1において、本発明の第1実施形態による双方向シリアルバススイッチ100は、マスタデバイス101とスレーブデバイス102との間で転送される双方向シリアル信号を単方向信号に変換する機能を有する。より具体的には、双方向シリアルバススイッチ100は、マスタ側スイッチ103、スレーブ側スイッチ104およびデコード部105を有し、マスタ側スイッチ103およびスレーブ側スイッチ104を切り替え制御することで、双方向信号を単方向信号に変換する。

【0014】

マスタ側スイッチ103は、デコード部105から入力する制御信号113に従って、マスタデバイス101から受けたマスタ側双方向信号110をマスタ出力信号111として出力するか、あるいはスレーブ側スイッチ104から入力するスレーブ出力信号112をマスタ側双方向信号110として出力するか切り替える。

【0015】

スレーブ側スイッチ104は、同じく制御信号113に従って、スレーブデバイス102から受けたスレーブ側双方向信号114をスレーブ出力信号112として出力するか、あるいはマスタ側スイッチ103から入力するマスタ出力信号111をスレーブ側双方向信号114として出力するか切り替える。

【0016】

デコード部105は、マスタ出力信号111を入力して動作およびアドレスをデコードし、デコード結果に従ってマスタ側スイッチ103およびスレーブ側スイッチ104へそれぞれ切替制御のための制御信号113を出力する。なお、デコード部105には予め各スレーブデバイスの固有アドレスが記憶されている。またデコード部105にはマスタデバイス101からクロック115が供給され、そのクロック115はさらにスレーブデバイス102にも供給される。

【0017】

図2(A)に示すように、マスタ側スイッチ103は、スレーブからマスタの方向に信号を出力するバッファアンプ103aと、マスタからスレーブの方向に信号を出力するバッファアンプ103bとを有する。バッファアンプ103aの制御端子には制御信号113がそのまま入力し、バッファアンプ103bの制御端子には制御信号113がインバータ103cを通して入力する。したがって、制御信号113が0/1であれば、バッファアンプ103aとバッファアンプ103bの一方が信号を出力するとき(ON)、他方は信号を出力しない(OFF)という切替制御が行われる。ここでは、通常、バッファアンプ103aがOFF、バッファアンプ103bがONとなっているものとする。

【0018】

図2(B)に示すように、スレーブ側スイッチ104は、スレーブからマスタの方向に信号を出力するバッファアンプ104aと、マスタからスレーブの方向に信号を出力するバッファアンプ104bとを有する。バッファアンプ104aの制御端子には制御信号113がそのまま入力し、バッファアンプ104bの制御端子には制御信号113がインバータ104cを通して入力する。したがって、制御信号113が0/1であれば、バッファアンプ104aとバッファアンプ104bの一方が信号を出力するとき(ON)、他方は信号を出力しない(OFF)という切替制御が行われる。ここでは、通常、バッファアンプ104aがOFF、バッファアンプ104bがONとなっているものとする。

【0019】

図2(A)および図2(B)において、制御信号113が通常‘0’であるとすれば、マスタデバイス101がドライブすると、マスタ側スイッチ103はマスタ側双方向信号110を受けてマスタ出力信号111をドライブし、スレーブ側スイッチ104はマスタ出力信号111を受けてスレーブ側双方向信号114をドライブする。逆に、スレーブデバイス102がドライブをする場合には、後述するように制御信号113が‘1’となり、スレーブ側スイッチ104はスレーブ側双方向信号114を受けてスレーブ出力信号112をドライブし、マスタ側スイッチ103はスレーブ出力信号112を受けてマスタ側双方向信号110をドライブする。このようにして、双方向シリアルバススイッチ100の双方向信号と単方向信号との間の変換を実現することができる。

【0020】

1.2)動作(MDIO適用例)

A)MDIOリードフレーム

図3を参照しながら、MDIOインタフェースを一例として、スレーブデバイス102からのデータ読み出し時のリードフレームにおける切替動作を説明する。ここで、MDIOリードフレームは、プリアンブル201、スタートオブフレーム202、オペレーションコード203、PHYアドレス204、レジスタアドレス205、ターンアラウンド206、およびデータ207による区間で区切られている。

【0021】

プリアンブル201では、フレームの先頭を表すために32ビット分で連続して‘1’が出力される(ただし、図3では省略している。)。スタートオブフレーム202では、プリアンブル201で‘1’が連続して続いた後に‘0’→‘1’と変化することでフレームの開始を表す。オペレーションコード203では、リードとライトのどちらのフレームであるかを表し、リードフレームの場合は‘10’が出力される。PHYアドレス204はアクセスするスレーブデバイス102の固有アドレス116を指定し、レジスタアドレス205はスレーブ内部のレジスタのアドレスを指定する。ターンアラウンド206では、マスタデバイス101からスレーブデバイス102への出力切替を行なうため2クロックの間を空ける。リードフレームではスレーブデバイス102からデータがドライブされ、ライトフレームではマスタデバイス101からデータがドライブされる。

【0022】

制御信号113は通常‘0’にセットされているので、マスタ側スイッチ103およびスレーブ側スイッチ104はマスタ出力信号111を選択し、スレーブ出力信号112側は高インピーダンス状態となっている。デコード部105は、マスタ側双方向信号110から出力されたマスタ出力信号111を解析し、リードフレームでPHYアドレス204が予め記憶されたスレーブの固有アドレス116と一致する場合には、ターンアラウンド206からデータの出力が終わるまで制御信号113を‘0’から‘1’にする。

制御信号113が‘1’になることで、マスタ側スイッチ103およびスレーブ側スイッチ104はスレーブ出力信号112を選択し、マスタ出力信号111側は高インピーダンス状態となる。これによって、スレーブデバイス102から出力されたデータがスレーブ出力信号112としてマスタ側へ読みだされる。

【0023】

B)MDIOライトフレーム

図4を参照しながら、スレーブデバイス102へのデータ書き込み時のMDIOライトフレームにおける切替動作を説明する。MDIOライトフレームも、リードフレームと同様に、プリアンブル201、スタートオブフレーム202、オペレーションコード203、PHYアドレス204、レジスタアドレス205、ターンアラウンド206、およびデータ207による区間で区切られている。ただし、オペレーションコード203はライトフレームを表す‘01’となる。また、ライトフレームではマスタデバイス101からデータがドライブされる。

【0024】

デコード部105は、マスタ出力信号111を解析し、ライトフレームでPHYアドレス204がスレーブの固有アドレス116と一致する場合には、制御信号113を変化させず、ターンアラウンド206以降も‘0’のまま維持する。したがって、マスタ側スイッチ103おおびスレーブ側スイッチ104はマスタ出力を選択した状態であり、マスタ側双方向信号110からの書き込みデータはマスタ出力信号111としてスレーブ側へ転送される。

【0025】

1.3)動作(I2C適用例)

図5および図6に本実施形態をI2Cに適用した場合のデコード処理(ライトシーケンスおよびリードシーケンス)を示す。図5および図6に示すように、リード/ライトシーケンスでは、スタート301に続くデバイスアドレス302によってスレーブデバイス102の固有アドレス116と一致する否かが判別され、R/W303によってリードかライトかが判別される。続いて、読み出し/書き込みデータ305が出力されるが、I2Cでは仕様上、8ビット送信完了毎にACK304を返す必要があるために、このタイミングで制御信号113が‘1’となる。

【0026】

図5に示すライトシーケンスでは、デコード部105でスレーブデバイス102がもつ固有アドレス116であるデバイスアドレス302を判別し、スレーブデバイス102に該当する場合には、デバイスアドレス302とR/W303を送信後、すなわち8ビット送信の完了後である9クロック目のタイミングで、制御信号113を‘1’にする。以下同様に8ビット送信完了毎に制御信号113を‘1’にする。

【0027】

図6に示すリードシーケンスでは、途中でスレーブデバイス102側からのドライブに切り替わるので、最初のACK304のタイミングから制御信号を‘1’にし、マスタがACK304を返すタイミングで制御信号を‘0’に切り替える。以上の方法により双方向シリアルバススイッチをI2Cバスに適用することができる。

【0028】

1.4)効果

上述したように、本発明の第1実施形態によるバススイッチ100は、デコード部105の解析結果に応じてマスタ側スイッチ103およびスレーブ側スイッチ104を制御することで、双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる。双方向シリアル信号を単方向信号に変換するので、バススイッチ100をゲートアレイにそのまま組み込むことができる。

【0029】

さらに、マスタデバイス101の出力信号からスレーブデバイスのアドレスとオペレーションを解析することで単方向信号の方向を即座に切り替えることができるので、双方向シリアル通信方式で要求される通信方向の切替条件を容易に満たすことができる。

【0030】

2.第2実施形態

上述した第1実施形態では、図1に示すように1つのスレーブデバイスを接続した場合を例示したが、本発明による双方向シリアル通信システムはこれに限定されるものではなく、複数のスレーブデバイスを接続可能である。以下、本発明の第2実施形態として複数のスレーブデバイスを接続したバススイッチについて説明する。

【0031】

2.1)構成

図7に示すように、本実施形態による双方向シリアルバスバススイッチ400は、マスタデバイス401と複数のスレーブデバイス(ここでは2つのスレーブ1デバイス402とスレーブ2デバイス403)の各々との間で転送される双方向シリアル信号を単方向信号に変換する機能を有する。

【0032】

基本的な構成は図1の第1実施形態と同様であるが、図1に示す第1実施形態との比較では、複数のスレーブデバイスにそれぞれ対応したスレーブスイッチ(ここでは2つのスレーブ1スイッチ405とスレーブ2スイッチ406)が設けられ、それらからのスレーブ出力信号がデコード部408からの制御信号414に従ってセレクタ407により選択される構成が追加されている。なお、双方向シリアルバススイッチ400におけるマスタ側スイッチ404、スレーブ1スイッチ405およびスレーブ2スイッチ406については、図2に示す構成と基本的に同じであるから説明は省略する。

【0033】

また、スレーブスイッチの数が増加しているので、それに合わせて制御信号414の論理が追加されている。図7の構成では、マスタデバイス401がドライブする場合には制御信号414が‘0’、スレーブ1デバイス402がドライブする場合には制御信号414が‘1’、スレーブ2デバイス403がドライブする場合には制御信号414が‘2’となる。

【0034】

デコード部408は、図3および図4に示すMDIOの場合、マスタ側から送信されるフレームのPHYアドレスが、スレーブ1デバイス402の固有アドレスかスレーブ2デバイス403の固有アドレスかを判別する。そのために、それぞれのスレーブデバイスの固有アドレスが予め記憶されている。

【0035】

2.2)動作

ライトを行なう場合、どちらのスレーブデバイスにアクセスする場合でもスイッチの切替は不要で制御信号414は‘0’固定になる。

【0036】

スレーブ1デバイス402からリードを行なう場合、マスタデバイス401からリードフレームが送信され、デコード部408でスレーブ1デバイス402の固有アドレスを検出し、ターンアラウンドのタイミングで制御信号414を‘1’にセットする。このとき、セレクタ407はスレーブ1出力信号413を選択した状態となるので、スレーブ1スイッチ405がスレーブ1側の双方向信号415を受けてスレーブ1出力信号413をドライブすると、スレーブ1出力信号413はセレクタ407を通してスレーブ出力信号412としてマスタ側スイッチ404へ転送され、マスタ側スイッチ404がスレーブ出力信号412を入力してマスタ側双方向信号410をドライブする。

【0037】

スレーブ2デバイス403からリードを行なう場合、マスタデバイス401からリードフレームが送信され、デコード部408でスレーブ2デバイス403の固有アドレスを検出し、ターンアラウンドのタイミングで制御信号414を‘2’にセットする。このとき、セレクタ407はスレーブ2出力信号417を選択した状態となるので、スレーブ2スイッチ406がスレーブ2側の双方向信号416を受けてスレーブ2出力信号417をドライブすると、スレーブ2出力信号417はセレクタ407を通してスレーブ出力信号412としてマスタ側スイッチ404へ転送され、マスタ側スイッチ404がスレーブ出力信号412を入力してマスタ側双方向信号410をドライブする。

【0038】

2.3)効果

本実施形態によれば、上述した第1実施形態の効果に加えて、スレーブデバイスを2つ以上接続する場合でも、スレーブ側スイッチと制御信号をスレーブデバイスにあわせて増やすことにより容易に対応できるという効果を有する。

【0039】

このようにハードウェアにより自動的にバスの分離を行なうことで、バスを1つのデバイスが占有してしまったり、どれか1つのデバイスがハングアップしてしまったり、デバイスの電源がおちたり、もしくは省エネ制御のために意図的にデバイスの電源を落としたりということがあってもバス自体が使用できなくなるという事態を回避できる。また、ゲートアレイで分離することで、スレーブデバイスの接続数が増えることによる浮遊容量の影響を受けない。また、デバイスを追加することによるマスタおよびスレーブデバイスのハードウェア変更やアクセスタイミングにあわせた特殊なスイッチ制御を行なうことなく、バスの分離が可能なゲートアレイを提供することができる。

【0040】

3.その他適用例

図8に示すように、双方向シリアルバスバススイッチ500は、上記第2実施形態と同様の構成とした場合、マスタデバイス501と複数のスレーブデバイス(ここでは3つのスレーブデバイス502−504)の各々との間で転送される双方向シリアル信号を単方向信号に変換する機能を有し、さらにマスタデバイス501のマスタ側双方向シリアルバスに直接スレーブデバイス505を接続することもできる。

【産業上の利用可能性】

【0041】

本発明はI2CやMDIOなどの双方向シリアルバスに適用可能である。

【符号の説明】

【0042】

100、400、500 双方向シリアルバススイッチ

101、401、501 マスタデバイス

102、402,403,502−505 スレーブデバイス

103、404 マスタ側スイッチ

104、405,406 スレーブ側スイッチ

105、408 デコード部

110、410 マスタ側双方向信号

111、411 マスタ出力信号

112、412,413,417 スレーブ出力信号

113、414 制御信号

114、415,416 スレーブ側双方向信号

【特許請求の範囲】

【請求項1】

複数のデバイスを双方向シリアル通信可能に接続する双方向シリアルバススイッチであって、

第1デバイスと第2デバイスとの間の双方向信号を単方向信号に変換するスイッチ手段と、

前記第1デバイスが出力する信号に従って前記単方向信号の方向を決定し前記スイッチ手段を制御する解析手段と、

を有することを特徴とする双方向シリアルバススイッチ。

【請求項2】

前記第1デバイスが出力する信号のデバイスアドレスおよびオペレーションに従って前記単方向信号の方向を決定することを特徴とする請求項1に記載の双方向シリアルバススイッチ。

【請求項3】

前記第1デバイスが出力する信号に従って複数の第2デバイスから出力される単方向信号のいずれか1つを選択する選択手段をさらに有することを特徴とする請求項1または2に記載の双方向シリアルバススイッチ。

【請求項4】

請求項1−3のいずれか1項に記載の双方向シリアルバススイッチが構成されたゲートアレイ。

【請求項5】

請求項1−3のいずれか1項に記載の双方向シリアルバススイッチを有する双方向シリアルバスシステム。

【請求項6】

複数のデバイスを双方向シリアル通信可能に接続する双方向シリアルバスの通信制御方法であって、

第1デバイスが出力する信号に従って、前記第1デバイスと第2デバイスとの間の双方向信号の伝送方向を決定する制御信号を生成し、

前記制御信号に従って前記第1デバイスと前記第2デバイスとの間の双方向信号を単方向信号に変換する、

ことを特徴とする双方向シリアルバスの通信制御方法。

【請求項7】

前記第1デバイスが出力する信号のデバイスアドレスおよびオペレーションに従って前記単方向信号の方向を決定することを特徴とする請求項6に記載の双方向シリアルバスの通信制御方法。

【請求項8】

前記第1デバイスが出力する信号に従って複数の第2デバイスから出力される単方向信号のいずれか1つを選択することを特徴とする請求項6または7に記載の双方向シリアルバスの通信制御方法。

【請求項1】

複数のデバイスを双方向シリアル通信可能に接続する双方向シリアルバススイッチであって、

第1デバイスと第2デバイスとの間の双方向信号を単方向信号に変換するスイッチ手段と、

前記第1デバイスが出力する信号に従って前記単方向信号の方向を決定し前記スイッチ手段を制御する解析手段と、

を有することを特徴とする双方向シリアルバススイッチ。

【請求項2】

前記第1デバイスが出力する信号のデバイスアドレスおよびオペレーションに従って前記単方向信号の方向を決定することを特徴とする請求項1に記載の双方向シリアルバススイッチ。

【請求項3】

前記第1デバイスが出力する信号に従って複数の第2デバイスから出力される単方向信号のいずれか1つを選択する選択手段をさらに有することを特徴とする請求項1または2に記載の双方向シリアルバススイッチ。

【請求項4】

請求項1−3のいずれか1項に記載の双方向シリアルバススイッチが構成されたゲートアレイ。

【請求項5】

請求項1−3のいずれか1項に記載の双方向シリアルバススイッチを有する双方向シリアルバスシステム。

【請求項6】

複数のデバイスを双方向シリアル通信可能に接続する双方向シリアルバスの通信制御方法であって、

第1デバイスが出力する信号に従って、前記第1デバイスと第2デバイスとの間の双方向信号の伝送方向を決定する制御信号を生成し、

前記制御信号に従って前記第1デバイスと前記第2デバイスとの間の双方向信号を単方向信号に変換する、

ことを特徴とする双方向シリアルバスの通信制御方法。

【請求項7】

前記第1デバイスが出力する信号のデバイスアドレスおよびオペレーションに従って前記単方向信号の方向を決定することを特徴とする請求項6に記載の双方向シリアルバスの通信制御方法。

【請求項8】

前記第1デバイスが出力する信号に従って複数の第2デバイスから出力される単方向信号のいずれか1つを選択することを特徴とする請求項6または7に記載の双方向シリアルバスの通信制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−105284(P2013−105284A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−248094(P2011−248094)

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000197366)NECアクセステクニカ株式会社 (1,236)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000197366)NECアクセステクニカ株式会社 (1,236)

【Fターム(参考)】

[ Back to top ]