双方向スイッチの駆動電源回路

【課題】絶縁電源の個数を減少させて装置全体の小型軽量化、低コスト化を可能にした双方向スイッチの駆動電源回路を提供する。

【解決手段】逆阻止IGBT1,2が逆並列接続された双方向スイッチを駆動するために、各IGBT1,2の駆動回路に電源を供給する双方向スイッチの駆動電源回路に関する。逆阻止IGBT1の駆動回路23に電源を供給する直流電源19と、逆阻止IGBT2の駆動回路24に電源を供給するコンデンサ22と、直流電源19とコンデンサ22との間に直列に接続され、かつ、そのオン時に逆阻止IGBT1を介して直流電源19によりコンデンサ22を充電する駆動電源用半導体スイッチとしてのPチャンネルMOSFET20と、を備える。

【解決手段】逆阻止IGBT1,2が逆並列接続された双方向スイッチを駆動するために、各IGBT1,2の駆動回路に電源を供給する双方向スイッチの駆動電源回路に関する。逆阻止IGBT1の駆動回路23に電源を供給する直流電源19と、逆阻止IGBT2の駆動回路24に電源を供給するコンデンサ22と、直流電源19とコンデンサ22との間に直列に接続され、かつ、そのオン時に逆阻止IGBT1を介して直流電源19によりコンデンサ22を充電する駆動電源用半導体スイッチとしてのPチャンネルMOSFET20と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えばIGBT等の電力用半導体スイッチング素子を逆並列に接続して構成される双方向スイッチに駆動用の電源を供給するための駆動電源回路に関するものである。

【背景技術】

【0002】

図6は、電力用半導体スイッチング素子として逆耐圧を有するIGBT(以下、逆阻止IGBTという)1,2を逆並列に接続して構成した双方向性の電力用半導体スイッチ(以下、単に双方向スイッチと言う)を示している。また、図7は、図6に示した双方向スイッチを9個用いて構成した三相のマトリクスコンバータの回路構成図であり、R,S,Tは三相電源に接続される三相入力端子、U,V,Wは三相負荷に接続される三相出力端子を示す。

【0003】

従来、この種の双方向スイッチをマトリクスコンバータに適用した場合、逆阻止IGBTを駆動するための絶縁電源は、下記の非特許文献1の表4.1に記載されているように6個必要であることが知られている。

図7を例に挙げれば、エミッタ同士が同電位となる逆阻止IGBTの駆動電源に各々絶縁電源を設ける必要があるため、逆阻止IGBT1,3,5、同7,9,11、同13,15,17、同2,8,14、同4,10,16、同6,12,18の6つの逆阻止IGBT群に対して、それぞれ絶縁電源が設けられることになる。

【0004】

【非特許文献1】原 英則 他5名、「マトリクスコンバータドライブの性能改善」、平成14年電気学会産業応用部門大会論文集、社団法人電気学会、pp.931−pp.934、図4.1、表4.1

【発明の開示】

【発明が解決しようとする課題】

【0005】

一般に、絶縁電源を確保するためには、変圧器を用いたDC/DCコンバータが用いられる。前述したマトリクスコンバータの例では、絶縁電源の個数に相当する6個のDC/DCコンバータが必要になり、これらのDC/DCコンバータの構成部品である変圧器等が装置全体の小型化を妨げ、また、コストを上昇させる原因となっている。

そこで本発明の解決課題は、絶縁電源の個数を減少させて装置全体の小型軽量化、低コスト化を可能にした電力用半導体スイッチの駆動電源回路を提供することにある。

【課題を解決するための手段】

【0006】

上記課題を解決するため、請求項1に記載した発明は、第1の半導体スイッチと第2の半導体スイッチとが逆並列接続されてなる双方向スイッチを駆動するために、第1の半導体スイッチの駆動回路及び第2の半導体スイッチの駆動回路に電源を供給する双方向スイッチの駆動電源回路において、

第1の半導体スイッチの駆動回路に電源を供給する直流電源と、第2の半導体スイッチの駆動回路に電源を供給するコンデンサと、前記直流電源と前記コンデンサとの間に直列に接続され、かつ、そのオン時に第1または第2の半導体スイッチを介して前記直流電源により前記コンデンサを充電するための駆動電源用半導体スイッチと、を備えたものである。

【0007】

請求項2に記載した発明は、請求項1において、第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したものである。

【0008】

請求項3に記載した発明は、請求項1において、第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したものである。

【0009】

請求項4に記載した発明は、請求項1〜3の何れか1項において、前記駆動電源用半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したものである。

【0010】

請求項5に記載した発明は、請求項1〜3の何れか1項において、前記駆動電源用半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したものである。

【0011】

請求項6に記載した発明は、請求項5において、前記駆動電源用半導体スイッチを構成する半導体スイッチング素子が、PチャンネルMOSFETまたはPチャンネルIGBTもしくはPNPトランジスタであることを特徴とする。

【0012】

請求項7に記載した発明は、請求項1〜6の何れか1項において、第1の半導体スイッチ、第2の半導体スイッチ及び前記駆動電源用半導体スイッチを、同時にオンオフさせるものである。

【0013】

請求項8に記載した発明は、請求項1〜6の何れか1項において、前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方または一方がオンしているときにオンさせるものである。

【0014】

請求項9に記載した発明は、請求項1〜6の何れか1項において、前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方がオンしてから一定時間経過後にオンさせるものである。

【発明の効果】

【0015】

本発明は、双方向スイッチを構成する一方の半導体スイッチを、直流電源が接続される駆動回路により駆動し、他方の半導体スイッチについては、前記直流電源に駆動電源用半導体スイッチを介して接続されたコンデンサを駆動電圧源とする駆動回路により駆動するものである。

このため、DC/DCコンバータ等を有する絶縁電源の数を従来に比べて低減することができ、例えば三相のマトリクスコンバータに本発明を適用した場合には、絶縁電源の数を半減することが可能であり、装置全体の小型軽量化、低価格化を図ることができる。

【発明を実施するための最良の形態】

【0016】

以下、図に沿って本発明の実施形態を説明する。

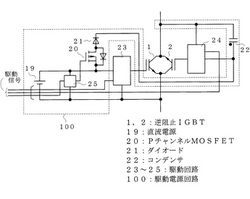

図1は、本発明の第1実施形態を示す構成図であり、半導体スイッチング素子としての逆阻止IGBT1と逆阻止IGBT2とを逆並列に接続して構成した双方向スイッチに本発明の駆動電源回路100(点線により囲まれた部分)を適用した例である。この実施形態は、請求項1〜6の発明に相当している。

なお、上記逆阻止IGBT1,2は、請求項における第1の半導体スイッチ、第2の半導体スイッチにそれぞれ相当する。

【0017】

図1において、23は逆阻止IGBT1の駆動回路、24は逆阻止IGBT2の駆動回路であり、これらの駆動回路23,24の出力端子は逆阻止IGBT1,2のゲートにそれぞれ接続されている。また、19は逆阻止IGBT1を駆動するための直流電源であり、その正極は駆動回路23及び後述の駆動回路25の各一方の電源端子に接続され、負極は駆動回路23,25の各他方の電源端子及び逆阻止IGBT1のエミッタ(逆阻止IGBT2のコレクタ)に接続されている。更に、22は逆阻止IGBT2の駆動電圧源となるコンデンサであり、その一端は駆動回路24の一方の電源端子に接続され、他端は駆動回路24の他方の電源端子及び逆阻止IGBT2のエミッタ(逆阻止IGBT1のコレクタ)に接続されている。

【0018】

20は駆動電源用半導体スイッチとしてのPチャンネルMOSFETであり、そのソースは直流電源19の正極に接続されていると共に、ドレインはダイオード21を介して前記コンデンサ22の一端に接続されている。

また、25はMOSFET20の駆動回路であり、その出力端子はMOSFET20のゲートに接続されており、この駆動回路25及び前記駆動回路23,24には、外部の制御回路から駆動信号が入力されるように構成されている。

上記構成において、直流電源19、コンデンサ22、駆動回路25、PチャンネルMOSFET20及びダイオード21によって本実施形態に係る駆動電源回路100が構成される。

【0019】

以下、図1及び図2を参照しながら本実施形態の動作について説明する。

図1に示した双方向スイッチにおいて、逆阻止IGBT1と逆阻止IGBT2とは、基本的に同時にオンオフされるが、本実施形態では、PチャンネルMOSFET20も逆阻止IGBT1,2と同時にオンオフさせる。

すなわち、直流電源19により電源が供給されている駆動回路23,25と、MOSFET20及びダイオード21を介して直流電源19により充電されているコンデンサ22を駆動電圧源とする駆動回路24とには、外部から駆動信号がそれぞれ入力され、逆阻止IGBT1、MOSFET20、逆阻止IGBT2を同時にオン、及び同時にオフさせるものである。

【0020】

ここで、逆阻止IGBT1の駆動電源としての直流電源19は、安定した電源電圧を出力するものであるとする。また、PチャンネルMOSFET20は、ソースの電位に対してゲート端子の電位が低くなるとオンする特性を持つため、PチャンネルMOSFET20は、逆阻止IGBT1,2の駆動信号と反転した信号を駆動回路25から入力することにより駆動するものとする。

【0021】

図2は、逆阻止IGBT2の駆動電圧源としてのコンデンサ22の充電電流が流れる経路を示している。逆阻止IGBT1がオンしている状態でPチャンネルMOSFET20をオンすると、逆阻止IGBT1のエミッタと逆阻止IGBT2のエミッタとが同電位となるため、図中の矢印で示した経路で電流が流れ、コンデンサ22が図示の極性で直流電源19の電圧とほぼ等しい電圧に充電される。

【0022】

また、逆阻止IGBT1,2がオフしていて、逆阻止IGBT1のエミッタに対してコレクタ側に正の電圧が印加されている場合は、ダイオード21が電圧を担い、主回路電流が駆動電源回路100を介して流れるのを防ぐ。また、逆阻止IGBT1,2がオフしているときはPチャンネルMOSFET20もオフしているため、逆阻止IGBT1のエミッタに対してコレクタ側に負の電圧が印加されている場合は、MOSFET20が電圧を担い、主回路電流が駆動電源回路100を介して流れるのを防いでいる。

【0023】

本実施形態において、逆阻止IGBT1,2がオフしている期間はコンデンサ22を充電することができず、その期間中にコンデンサ22の電圧が低下する恐れがあるが、コンデンサ22の容量を必要に応じて大きくしておけば、実用上問題はなく、上述した逆阻止IGBT1,2及びPチャンネルMOSFET20のオン動作により、コンデンサ22の電圧を直流電源19の電圧とほぼ等しい一定の電圧値に保つことができる。

【0024】

なお、請求項4に記載するように、駆動電源用半導体スイッチとしてのPチャンネルMOSFET20が逆耐圧を有するのであれば、ダイオード21は不要となる。また、請求項6に記載する如く、PチャンネルMOSFET20の代わりに、PチャンネルIGBTやPNP形トランジスタを用いても同様な効果が得られる。

更に、PチャンネルMOSFET20の代わりに、例えば、NチャンネルMOSFETを用いても、同様な動作をさせることが可能であるが、この場合、NチャンネルMOSFET用の駆動電源を別途用意する必要がある。

【0025】

次に、図3は本発明の第2実施形態の主要部を示したものであり、請求項7〜9の発明に相当する。

先の第1実施形態では、逆阻止IGBT1及び逆阻止IGBT2を基本的に同時にオンオフさせるものとし、また、PチャンネルMOSFET20もこれらの逆阻止IGBT1,2と同時にオンオフさせるものとした。しかし、用途によっては、逆阻止IGBT1と逆阻止IGBT2とのオンオフタイミングを意図的にずらすことがある。

【0026】

また、PチャンネルMOSFET20は、逆阻止IGBT1,2の電流定格に比べて非常に小さい電流定格で十分であるが、一般に定格電流が小さいほどスイッチング速度が速いため、逆阻止IGBT1,2よりも先にPチャンネルMOSFET20がオンする可能性がある。このため、逆阻止IGBT1,2の何れか一方と同じタイミングのオンオフ信号をMOSFET20に入力しても、逆阻止IGBT1または逆阻止IGBT2よりも先にMOSFET20がオンしてしまい、本来であれば逆阻止IGBT1,2の何れか一方を流れるべき主回路電流がMOSFET20を流れてしまう結果、MOSFET20を破壊する恐れがある。

【0027】

そこで、第2実施形態は上記問題点を解決するためのものであり、図3はPチャンネルMOSFET20の駆動信号を発生する駆動回路25Aを示している。

図示するように、この駆動回路25Aは、逆阻止IGBT1,2の駆動信号が入力されるアンド回路26と、その出力信号を遅延させてPチャンネルMOSFET20がオンするタイミングを遅らせるオンディレイ回路27とから構成されている。

【0028】

図4は、この第2実施形態における逆阻止IGBT1,2及びPチャンネルMOSFET20の駆動信号のタイミングチャートである。

時刻t1で逆阻止IGBT1,2の両方がオン状態となり、アンド回路26の出力信号がオンディレイ回路27に加えられてから一定の時間が経過した時刻t2でPチャンネルMOSFET20をオンさせる。

【0029】

また、MOSFET20をオフする信号のタイミングは、逆阻止IGBT1,2のうち、先にオフする信号と同じタイミングとするものとし、図示例では逆阻止IGBT1のオフ時刻t3に一致させている。前述した如く、PチャンネルMOSFET20は逆阻止IGBTに比べてスイッチング速度が速いため、オフ信号のタイミングがPチャンネルMOSFET20と逆阻止IGBT1,2の何れかと同じタイミングでも特に問題はない。

図3の制御回路25Aによって上記のタイミングでPチャンネルMOSFET20をオンオフすることにより、MOSFET20への主回路電流の流入による破壊を防止することができる。

【0030】

なお、逆阻止IGBT1,2がオフするより前の時刻で、PチャンネルMOSFET20を意図的にオフさせてもよい。

また、逆阻止IGBT1,2の何れか一方がオンしているときにPチャンネルMOSFET20をオフさせてもよい。

【0031】

更に、上記第1実施形態及び第2実施形態は、例えば図5に示すように、逆耐圧を有さないIGBT28,29と、これらにそれぞれ順接続されるダイオード30,31とを用いて構成した双方向スイッチにも適用することができる。

なお、この構成は請求項3の発明に相当するものである。

この場合、IGBT28とダイオード30との直列回路が各請求項における第1の半導体スイッチに相当し、IGBT29とダイオード31との直列回路が各請求項における第2の半導体スイッチに相当する。

【0032】

前述したように、従来では、図7に示したようなマトリクスコンバータにおいて、絶縁電源を確保するためにDC/DCコンバータが6個必要であったのに対し、本発明の実施形態では、例えば、逆阻止IGBT1,3,5、同7,9,11、同13,15,17という3つの逆阻止IGBT群にそれぞれ絶縁電源を設ければよいことになり、絶縁電源の個数の削減によって装置全体の小型軽量化、低価格化に寄与するものである。

【図面の簡単な説明】

【0033】

【図1】本発明の第1実施形態を示す構成図である。

【図2】第1実施形態におけるコンデンサの充電経路を示す図である。

【図3】本発明の第2実施形態の主要部を示す構成図である。

【図4】第2実施形態における各スイッチの駆動信号のタイミングチャートである。

【図5】IGBT及びダイオードを用いた双方向スイッチの構成図である。

【図6】逆阻止IGBTを用いた双方向スイッチの構成図である。

【図7】マトリクスコンバータの回路構成図である。

【符号の説明】

【0034】

1〜18:逆阻止IGBT

19:直流電源

20:PチャンネルMOSFET

21:ダイオード

22:コンデンサ

23〜25,25A:駆動回路

26:アンド回路

27:オンディレイ回路

28,29:IGBT

30,31:ダイオード

100:駆動電源回路

【技術分野】

【0001】

本発明は、例えばIGBT等の電力用半導体スイッチング素子を逆並列に接続して構成される双方向スイッチに駆動用の電源を供給するための駆動電源回路に関するものである。

【背景技術】

【0002】

図6は、電力用半導体スイッチング素子として逆耐圧を有するIGBT(以下、逆阻止IGBTという)1,2を逆並列に接続して構成した双方向性の電力用半導体スイッチ(以下、単に双方向スイッチと言う)を示している。また、図7は、図6に示した双方向スイッチを9個用いて構成した三相のマトリクスコンバータの回路構成図であり、R,S,Tは三相電源に接続される三相入力端子、U,V,Wは三相負荷に接続される三相出力端子を示す。

【0003】

従来、この種の双方向スイッチをマトリクスコンバータに適用した場合、逆阻止IGBTを駆動するための絶縁電源は、下記の非特許文献1の表4.1に記載されているように6個必要であることが知られている。

図7を例に挙げれば、エミッタ同士が同電位となる逆阻止IGBTの駆動電源に各々絶縁電源を設ける必要があるため、逆阻止IGBT1,3,5、同7,9,11、同13,15,17、同2,8,14、同4,10,16、同6,12,18の6つの逆阻止IGBT群に対して、それぞれ絶縁電源が設けられることになる。

【0004】

【非特許文献1】原 英則 他5名、「マトリクスコンバータドライブの性能改善」、平成14年電気学会産業応用部門大会論文集、社団法人電気学会、pp.931−pp.934、図4.1、表4.1

【発明の開示】

【発明が解決しようとする課題】

【0005】

一般に、絶縁電源を確保するためには、変圧器を用いたDC/DCコンバータが用いられる。前述したマトリクスコンバータの例では、絶縁電源の個数に相当する6個のDC/DCコンバータが必要になり、これらのDC/DCコンバータの構成部品である変圧器等が装置全体の小型化を妨げ、また、コストを上昇させる原因となっている。

そこで本発明の解決課題は、絶縁電源の個数を減少させて装置全体の小型軽量化、低コスト化を可能にした電力用半導体スイッチの駆動電源回路を提供することにある。

【課題を解決するための手段】

【0006】

上記課題を解決するため、請求項1に記載した発明は、第1の半導体スイッチと第2の半導体スイッチとが逆並列接続されてなる双方向スイッチを駆動するために、第1の半導体スイッチの駆動回路及び第2の半導体スイッチの駆動回路に電源を供給する双方向スイッチの駆動電源回路において、

第1の半導体スイッチの駆動回路に電源を供給する直流電源と、第2の半導体スイッチの駆動回路に電源を供給するコンデンサと、前記直流電源と前記コンデンサとの間に直列に接続され、かつ、そのオン時に第1または第2の半導体スイッチを介して前記直流電源により前記コンデンサを充電するための駆動電源用半導体スイッチと、を備えたものである。

【0007】

請求項2に記載した発明は、請求項1において、第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したものである。

【0008】

請求項3に記載した発明は、請求項1において、第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したものである。

【0009】

請求項4に記載した発明は、請求項1〜3の何れか1項において、前記駆動電源用半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したものである。

【0010】

請求項5に記載した発明は、請求項1〜3の何れか1項において、前記駆動電源用半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したものである。

【0011】

請求項6に記載した発明は、請求項5において、前記駆動電源用半導体スイッチを構成する半導体スイッチング素子が、PチャンネルMOSFETまたはPチャンネルIGBTもしくはPNPトランジスタであることを特徴とする。

【0012】

請求項7に記載した発明は、請求項1〜6の何れか1項において、第1の半導体スイッチ、第2の半導体スイッチ及び前記駆動電源用半導体スイッチを、同時にオンオフさせるものである。

【0013】

請求項8に記載した発明は、請求項1〜6の何れか1項において、前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方または一方がオンしているときにオンさせるものである。

【0014】

請求項9に記載した発明は、請求項1〜6の何れか1項において、前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方がオンしてから一定時間経過後にオンさせるものである。

【発明の効果】

【0015】

本発明は、双方向スイッチを構成する一方の半導体スイッチを、直流電源が接続される駆動回路により駆動し、他方の半導体スイッチについては、前記直流電源に駆動電源用半導体スイッチを介して接続されたコンデンサを駆動電圧源とする駆動回路により駆動するものである。

このため、DC/DCコンバータ等を有する絶縁電源の数を従来に比べて低減することができ、例えば三相のマトリクスコンバータに本発明を適用した場合には、絶縁電源の数を半減することが可能であり、装置全体の小型軽量化、低価格化を図ることができる。

【発明を実施するための最良の形態】

【0016】

以下、図に沿って本発明の実施形態を説明する。

図1は、本発明の第1実施形態を示す構成図であり、半導体スイッチング素子としての逆阻止IGBT1と逆阻止IGBT2とを逆並列に接続して構成した双方向スイッチに本発明の駆動電源回路100(点線により囲まれた部分)を適用した例である。この実施形態は、請求項1〜6の発明に相当している。

なお、上記逆阻止IGBT1,2は、請求項における第1の半導体スイッチ、第2の半導体スイッチにそれぞれ相当する。

【0017】

図1において、23は逆阻止IGBT1の駆動回路、24は逆阻止IGBT2の駆動回路であり、これらの駆動回路23,24の出力端子は逆阻止IGBT1,2のゲートにそれぞれ接続されている。また、19は逆阻止IGBT1を駆動するための直流電源であり、その正極は駆動回路23及び後述の駆動回路25の各一方の電源端子に接続され、負極は駆動回路23,25の各他方の電源端子及び逆阻止IGBT1のエミッタ(逆阻止IGBT2のコレクタ)に接続されている。更に、22は逆阻止IGBT2の駆動電圧源となるコンデンサであり、その一端は駆動回路24の一方の電源端子に接続され、他端は駆動回路24の他方の電源端子及び逆阻止IGBT2のエミッタ(逆阻止IGBT1のコレクタ)に接続されている。

【0018】

20は駆動電源用半導体スイッチとしてのPチャンネルMOSFETであり、そのソースは直流電源19の正極に接続されていると共に、ドレインはダイオード21を介して前記コンデンサ22の一端に接続されている。

また、25はMOSFET20の駆動回路であり、その出力端子はMOSFET20のゲートに接続されており、この駆動回路25及び前記駆動回路23,24には、外部の制御回路から駆動信号が入力されるように構成されている。

上記構成において、直流電源19、コンデンサ22、駆動回路25、PチャンネルMOSFET20及びダイオード21によって本実施形態に係る駆動電源回路100が構成される。

【0019】

以下、図1及び図2を参照しながら本実施形態の動作について説明する。

図1に示した双方向スイッチにおいて、逆阻止IGBT1と逆阻止IGBT2とは、基本的に同時にオンオフされるが、本実施形態では、PチャンネルMOSFET20も逆阻止IGBT1,2と同時にオンオフさせる。

すなわち、直流電源19により電源が供給されている駆動回路23,25と、MOSFET20及びダイオード21を介して直流電源19により充電されているコンデンサ22を駆動電圧源とする駆動回路24とには、外部から駆動信号がそれぞれ入力され、逆阻止IGBT1、MOSFET20、逆阻止IGBT2を同時にオン、及び同時にオフさせるものである。

【0020】

ここで、逆阻止IGBT1の駆動電源としての直流電源19は、安定した電源電圧を出力するものであるとする。また、PチャンネルMOSFET20は、ソースの電位に対してゲート端子の電位が低くなるとオンする特性を持つため、PチャンネルMOSFET20は、逆阻止IGBT1,2の駆動信号と反転した信号を駆動回路25から入力することにより駆動するものとする。

【0021】

図2は、逆阻止IGBT2の駆動電圧源としてのコンデンサ22の充電電流が流れる経路を示している。逆阻止IGBT1がオンしている状態でPチャンネルMOSFET20をオンすると、逆阻止IGBT1のエミッタと逆阻止IGBT2のエミッタとが同電位となるため、図中の矢印で示した経路で電流が流れ、コンデンサ22が図示の極性で直流電源19の電圧とほぼ等しい電圧に充電される。

【0022】

また、逆阻止IGBT1,2がオフしていて、逆阻止IGBT1のエミッタに対してコレクタ側に正の電圧が印加されている場合は、ダイオード21が電圧を担い、主回路電流が駆動電源回路100を介して流れるのを防ぐ。また、逆阻止IGBT1,2がオフしているときはPチャンネルMOSFET20もオフしているため、逆阻止IGBT1のエミッタに対してコレクタ側に負の電圧が印加されている場合は、MOSFET20が電圧を担い、主回路電流が駆動電源回路100を介して流れるのを防いでいる。

【0023】

本実施形態において、逆阻止IGBT1,2がオフしている期間はコンデンサ22を充電することができず、その期間中にコンデンサ22の電圧が低下する恐れがあるが、コンデンサ22の容量を必要に応じて大きくしておけば、実用上問題はなく、上述した逆阻止IGBT1,2及びPチャンネルMOSFET20のオン動作により、コンデンサ22の電圧を直流電源19の電圧とほぼ等しい一定の電圧値に保つことができる。

【0024】

なお、請求項4に記載するように、駆動電源用半導体スイッチとしてのPチャンネルMOSFET20が逆耐圧を有するのであれば、ダイオード21は不要となる。また、請求項6に記載する如く、PチャンネルMOSFET20の代わりに、PチャンネルIGBTやPNP形トランジスタを用いても同様な効果が得られる。

更に、PチャンネルMOSFET20の代わりに、例えば、NチャンネルMOSFETを用いても、同様な動作をさせることが可能であるが、この場合、NチャンネルMOSFET用の駆動電源を別途用意する必要がある。

【0025】

次に、図3は本発明の第2実施形態の主要部を示したものであり、請求項7〜9の発明に相当する。

先の第1実施形態では、逆阻止IGBT1及び逆阻止IGBT2を基本的に同時にオンオフさせるものとし、また、PチャンネルMOSFET20もこれらの逆阻止IGBT1,2と同時にオンオフさせるものとした。しかし、用途によっては、逆阻止IGBT1と逆阻止IGBT2とのオンオフタイミングを意図的にずらすことがある。

【0026】

また、PチャンネルMOSFET20は、逆阻止IGBT1,2の電流定格に比べて非常に小さい電流定格で十分であるが、一般に定格電流が小さいほどスイッチング速度が速いため、逆阻止IGBT1,2よりも先にPチャンネルMOSFET20がオンする可能性がある。このため、逆阻止IGBT1,2の何れか一方と同じタイミングのオンオフ信号をMOSFET20に入力しても、逆阻止IGBT1または逆阻止IGBT2よりも先にMOSFET20がオンしてしまい、本来であれば逆阻止IGBT1,2の何れか一方を流れるべき主回路電流がMOSFET20を流れてしまう結果、MOSFET20を破壊する恐れがある。

【0027】

そこで、第2実施形態は上記問題点を解決するためのものであり、図3はPチャンネルMOSFET20の駆動信号を発生する駆動回路25Aを示している。

図示するように、この駆動回路25Aは、逆阻止IGBT1,2の駆動信号が入力されるアンド回路26と、その出力信号を遅延させてPチャンネルMOSFET20がオンするタイミングを遅らせるオンディレイ回路27とから構成されている。

【0028】

図4は、この第2実施形態における逆阻止IGBT1,2及びPチャンネルMOSFET20の駆動信号のタイミングチャートである。

時刻t1で逆阻止IGBT1,2の両方がオン状態となり、アンド回路26の出力信号がオンディレイ回路27に加えられてから一定の時間が経過した時刻t2でPチャンネルMOSFET20をオンさせる。

【0029】

また、MOSFET20をオフする信号のタイミングは、逆阻止IGBT1,2のうち、先にオフする信号と同じタイミングとするものとし、図示例では逆阻止IGBT1のオフ時刻t3に一致させている。前述した如く、PチャンネルMOSFET20は逆阻止IGBTに比べてスイッチング速度が速いため、オフ信号のタイミングがPチャンネルMOSFET20と逆阻止IGBT1,2の何れかと同じタイミングでも特に問題はない。

図3の制御回路25Aによって上記のタイミングでPチャンネルMOSFET20をオンオフすることにより、MOSFET20への主回路電流の流入による破壊を防止することができる。

【0030】

なお、逆阻止IGBT1,2がオフするより前の時刻で、PチャンネルMOSFET20を意図的にオフさせてもよい。

また、逆阻止IGBT1,2の何れか一方がオンしているときにPチャンネルMOSFET20をオフさせてもよい。

【0031】

更に、上記第1実施形態及び第2実施形態は、例えば図5に示すように、逆耐圧を有さないIGBT28,29と、これらにそれぞれ順接続されるダイオード30,31とを用いて構成した双方向スイッチにも適用することができる。

なお、この構成は請求項3の発明に相当するものである。

この場合、IGBT28とダイオード30との直列回路が各請求項における第1の半導体スイッチに相当し、IGBT29とダイオード31との直列回路が各請求項における第2の半導体スイッチに相当する。

【0032】

前述したように、従来では、図7に示したようなマトリクスコンバータにおいて、絶縁電源を確保するためにDC/DCコンバータが6個必要であったのに対し、本発明の実施形態では、例えば、逆阻止IGBT1,3,5、同7,9,11、同13,15,17という3つの逆阻止IGBT群にそれぞれ絶縁電源を設ければよいことになり、絶縁電源の個数の削減によって装置全体の小型軽量化、低価格化に寄与するものである。

【図面の簡単な説明】

【0033】

【図1】本発明の第1実施形態を示す構成図である。

【図2】第1実施形態におけるコンデンサの充電経路を示す図である。

【図3】本発明の第2実施形態の主要部を示す構成図である。

【図4】第2実施形態における各スイッチの駆動信号のタイミングチャートである。

【図5】IGBT及びダイオードを用いた双方向スイッチの構成図である。

【図6】逆阻止IGBTを用いた双方向スイッチの構成図である。

【図7】マトリクスコンバータの回路構成図である。

【符号の説明】

【0034】

1〜18:逆阻止IGBT

19:直流電源

20:PチャンネルMOSFET

21:ダイオード

22:コンデンサ

23〜25,25A:駆動回路

26:アンド回路

27:オンディレイ回路

28,29:IGBT

30,31:ダイオード

100:駆動電源回路

【特許請求の範囲】

【請求項1】

第1の半導体スイッチと第2の半導体スイッチとが逆並列接続されてなる双方向スイッチを駆動するために、第1の半導体スイッチの駆動回路及び第2の半導体スイッチの駆動回路に電源を供給する双方向スイッチの駆動電源回路において、

第1の半導体スイッチの駆動回路に電源を供給する直流電源と、

第2の半導体スイッチの駆動回路に電源を供給するコンデンサと、

前記直流電源と前記コンデンサとの間に直列に接続され、かつ、そのオン時に第1または第2の半導体スイッチを介して前記直流電源により前記コンデンサを充電するための駆動電源用半導体スイッチと、

を備えたことを特徴とする双方向スイッチの駆動電源回路。

【請求項2】

請求項1に記載した双方向スイッチの駆動電源回路において、

第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項3】

請求項1に記載した双方向スイッチの駆動電源回路において、

第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項4】

請求項1〜3の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項5】

請求項1〜3の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項6】

請求項5に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを構成する半導体スイッチング素子が、PチャンネルMOSFETまたはPチャンネルIGBTもしくはPNPトランジスタであることを特徴とする双方向スイッチの駆動電源回路。

【請求項7】

請求項1〜6の何れか1項に記載した双方向スイッチの駆動電源回路において、

第1の半導体スイッチ、第2の半導体スイッチ及び前記駆動電源用半導体スイッチを、同時にオンオフさせることを特徴とする双方向スイッチの駆動電源回路。

【請求項8】

請求項1〜6の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方または一方がオンしているときにオンさせることを特徴とする双方向スイッチの駆動電源回路。

【請求項9】

請求項1〜6の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方がオンしてから一定時間経過後にオンさせることを特徴とする双方向スイッチの駆動電源回路。

【請求項1】

第1の半導体スイッチと第2の半導体スイッチとが逆並列接続されてなる双方向スイッチを駆動するために、第1の半導体スイッチの駆動回路及び第2の半導体スイッチの駆動回路に電源を供給する双方向スイッチの駆動電源回路において、

第1の半導体スイッチの駆動回路に電源を供給する直流電源と、

第2の半導体スイッチの駆動回路に電源を供給するコンデンサと、

前記直流電源と前記コンデンサとの間に直列に接続され、かつ、そのオン時に第1または第2の半導体スイッチを介して前記直流電源により前記コンデンサを充電するための駆動電源用半導体スイッチと、

を備えたことを特徴とする双方向スイッチの駆動電源回路。

【請求項2】

請求項1に記載した双方向スイッチの駆動電源回路において、

第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項3】

請求項1に記載した双方向スイッチの駆動電源回路において、

第1の半導体スイッチ及び第2の半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項4】

請求項1〜3の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、逆耐圧を有する半導体スイッチング素子により構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項5】

請求項1〜3の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、逆耐圧を有しない半導体スイッチング素子と、この半導体スイッチング素子に順接続されたダイオードとによって構成したことを特徴とする双方向スイッチの駆動電源回路。

【請求項6】

請求項5に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを構成する半導体スイッチング素子が、PチャンネルMOSFETまたはPチャンネルIGBTもしくはPNPトランジスタであることを特徴とする双方向スイッチの駆動電源回路。

【請求項7】

請求項1〜6の何れか1項に記載した双方向スイッチの駆動電源回路において、

第1の半導体スイッチ、第2の半導体スイッチ及び前記駆動電源用半導体スイッチを、同時にオンオフさせることを特徴とする双方向スイッチの駆動電源回路。

【請求項8】

請求項1〜6の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方または一方がオンしているときにオンさせることを特徴とする双方向スイッチの駆動電源回路。

【請求項9】

請求項1〜6の何れか1項に記載した双方向スイッチの駆動電源回路において、

前記駆動電源用半導体スイッチを、第1の半導体スイッチ及び第2の半導体スイッチの両方がオンしてから一定時間経過後にオンさせることを特徴とする双方向スイッチの駆動電源回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2006−14549(P2006−14549A)

【公開日】平成18年1月12日(2006.1.12)

【国際特許分類】

【出願番号】特願2004−191253(P2004−191253)

【出願日】平成16年6月29日(2004.6.29)

【出願人】(000005234)富士電機ホールディングス株式会社 (3,146)

【Fターム(参考)】

【公開日】平成18年1月12日(2006.1.12)

【国際特許分類】

【出願日】平成16年6月29日(2004.6.29)

【出願人】(000005234)富士電機ホールディングス株式会社 (3,146)

【Fターム(参考)】

[ Back to top ]