可変インダクタ及びこれを用いた半導体装置

【課題】占有面積を大きくすることなく、インダクタンス値を変更できる可変インダクタを提供する。

【解決手段】本発明の可変インダクタ1は、スパイラルインダクタ2と、ループ導体5と、前記ループ導体5の一端を開放/短絡するスイッチ7と、を含む可変インダクタであって、前記ループ導体5は前記スパイラルインダクタ2に対して垂直方向に形成され、前記スイッチ7により前記ループ導体5の一端を開放/短絡することによって前記スパイラルインダクタ2のインダクタンス値を調整する機能を有する。

【解決手段】本発明の可変インダクタ1は、スパイラルインダクタ2と、ループ導体5と、前記ループ導体5の一端を開放/短絡するスイッチ7と、を含む可変インダクタであって、前記ループ導体5は前記スパイラルインダクタ2に対して垂直方向に形成され、前記スイッチ7により前記ループ導体5の一端を開放/短絡することによって前記スパイラルインダクタ2のインダクタンス値を調整する機能を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、可変インダクタ及びこれを用いた半導体装置に係り、例えばCMOSプロセスを用いて形成され、ミリ波帯を含む超高周波数帯において用いられる半導体装置において、整合回路を構成するインダクタのインダクタンス値を調整する技術に関するものである。

【背景技術】

【0002】

ミリ波帯を用いた無線通信分野においてCMOSプロセスを用いたMMIC(monolithic microwave integrated circuit)の開発が進められており、整合回路の集中定数化によるチップ面積の小型化も進められている。

一般に、整合回路を集中定数化すると、インダクタンス又は容量の自己共振周波数によって、狭帯域化するという課題がある。

集中定数化された素子を用いた整合回路では、狭帯域特性を改善するために、整合回路を可変にすることが一般的である。整合回路内の容量を可変とするためには、バラクタを用いるか、容量を並列化してスイッチのON/OFFによって制御することが考えられる。しかしながら、ミリ波帯ではバラクタ又はスイッチを用いることによって整合回路における損失が大きくなるという課題がある。

【0003】

このような課題を解決する方法として、例えばインダクタのインダクタンス値を調整する構成が提案されている(例えば特許文献1、特許文献2参照)。

図13は特許文献1に記載された可変インダクタの概略構成図である。図13において、インダクタンス可変素子101は、渦巻き状のスパイラル電極102と、スパイラル電極102の周回部分を短絡することにより、入出力電極103、104間を流れる電流を、短絡させるためのスイッチ105、106とを有している。

スイッチ105、106は、ゲート電極107、108と、ゲート電極107、108を挟んで形成された拡散領域109、110、111とを用いて構成されている。これらインダクタンス可変素子101、スイッチ105、106は、絶縁層112を介して、シリコン基板113上に形成されている。

拡散領域109、110、111のそれぞれは、p型不純物を熱拡散あるいはイオン打ち込みにより、n型シリコン基板113表面に形成される。

【0004】

可変インダクタにおいては、インダクタンス値は入出力電極103、104の間のスパイラル電極102の長さによって決定される。可変インダクタは、スイッチ105をONすることにより、入出力電極103、104間のスパイラル電極102の長さを短くでき、さらにスイッチ106をONすることによって、スパイラル電極102の長さをさらに短くできる。

【0005】

また、図14に、特許文献2に記載された可変インダクタの概略構成図を示す。図14において、スパイラルコイル201、スパイラルコイルの第1層202、スパイラルコイルの第2層203、制御回路204、スイッチ205、シリコン基板206、周囲配線207、周囲配線の第1層208、周囲配線の第2層209を含む構成である。

【0006】

特許文献2の可変インダクタは以下のように構成される。スパイラルコイル201の周囲に周囲配線207を設け、周囲配線207の一端にスイッチ205を接続した構成において、制御回路204からの制御信号によってスイッチをON/OFFさせ、周囲配線207の一端を開放/短絡させる。

周囲配線207の一端を開放させた状態に比べて、周囲配線207の一端を短絡させた状態では、スパイラルコイル201において発生する磁束が周囲配線207を貫通することによって周囲配線207に誘導電流が流れ、スパイラルコイル201の磁束を打ち消し、スパイラルコイル201のインダクタンス値は低下する。すなわち、スイッチ205をON/OFFすることによって周囲配線207の一端を開放/短絡し、インダクタンス値を可変とする。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3318086号公報

【特許文献2】特開2008−16703号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記特許文献1のインダクタ構成では、スイッチのON/OFFによってインダクタンス値を変更できるが、インダクタに直列にスイッチが配置さるため、ミリ波帯ではスイッチの影響によって損失が大きくなるという課題がある。

また、上記特許文献2のようなインダクタ構成では、周囲配線207の状況によってインダクタンス値を変更できるが、インダクタンス値を変更するにはインダクタ周囲に配線領域が必要となり、インダクタの占める面積が大きくなるという課題がある。

また、インダクタ周囲に周囲配線を設けることにより、インダクタの入出力ラインの下部が配線領域となるため、インダクタの入出力ラインが長くなり、損失が大きくなるという課題がある。

【0009】

本発明は、前記実情に鑑みてなされたものであり、インダクタの占有面積を拡大させずに、また調整可能な周波数帯域が広く、損失の小さい可変インダクタを提供することを目的とする。

【課題を解決するための手段】

【0010】

上記の課題を解決するための本発明の可変インダクタは、半導体基板上に形成された、スパイラルインダクタと、ループ導体と、前記ループ導体の一端を開放/短絡するスイッチと、を含む可変インダクタであって、前記ループ導体は前記スパイラルインダクタの下層に配置され、前記スイッチを用いて前記ループ導体の一端を開放/短絡することによって、前記スパイラルインダクタのインダクタンス値を変更可能としたものである。

上記構成によれば、可変インダクタの占有面積を拡大させずに、インダクタンス値を調整できる。

【0011】

また、本発明は、前記可変インダクタであって、前記ループ導体は前記スパイラルインダクタに対して垂直方向に形成されたものを含む。

この構成によれば、ループ導体がスパイラルインダクタに対して垂直方向に形成されているため、占有面積を小さくでき、MOSFETを含むトランジスタを用いてスイッチを形成する場合にも、スパイラルインダクタの形成領域下に収まめることが可能となる。

【0012】

また、本発明は、前記可変インダクタであって、前記スパイラルインダクタが、前記半導体基板の一表面に形成されており、前記ループ導体は、前記スパイラルインダクタより下層に形成された第1層導体と、前記第1層導体よりも下層に形成された第2層導体と、前記半導体基板の少なくとも一部を、前記表面に垂直な方向に形成されたビア内に形成され、前記第1及び第2層導体間を接続する垂直導体と、前記ループ導体の一端を開放/短絡するためのスイッチと、を用いて構成される。

上記構成によれば、ループ導体を半導体基板の一表面に対して垂直なループを構成することによって、半導体基板上における占有面積を拡大することなく、ループ面積を大きくとることができる。そして、ループ導体を流れる誘導電流により、結果的にスパイラルインダクタにより発生する磁束の影響を、より大きく受けられるため、可変インダクタのインダクタンス値を大きく変えることができる。また、発振回路としての半導体集積回路装置において、製造プロセスにおける配線のための導体パターン形成工程において、マスクパターンの変更によって、工数の増大なしにループ導体を形成できる。

【0013】

また、本発明は、前記可変インダクタであって、前記半導体基板はシリコン基板であり、前記スパイラルインダクタは、前記シリコン基板の最表層に形成された表面導体において構成され、前記第1の導体は、前記表面導体に対し、層間絶縁膜を介して下層側に配置された内層導体であり、前記第2の導体は、前記シリコン基板の裏面に形成された裏面導体であり、前記ループ導体は、前記内層導体と、前記シリコン基板を貫通する貫通ビア内に形成された垂直導体と、前記裏面導体と、前記ループ導体の一端を開放/短絡するためのスイッチとを含む。

上記構成によれば、ループ導体のループ面積を大きくとることができ、結果的にスパイラルインダクタにおいて発生する磁束の影響をより大きく受けるため、可変インダクタのインダクタンス値の可変範囲を大きくできる。また裏面導体を用いているため、より大きなループを形成でき、インダクタンス値の可変範囲を広くできる。

【0014】

また、本発明は、前記可変インダクタであって、前記ループ導体は、前記スパイラルインダクタを構成する最外周ラインにより囲まれた領域下、あるいは内側に配置される。

上記構成によれば、ループ導体に起因する占有面積の増大なしに、前記可変インダクタのインダクタンスを効率よく変更できる。

【0015】

また、本発明は、前記可変インダクタであって、前記スイッチは、前記ループ導体の一端に接続された可変抵抗を含み、前記可変抵抗の抵抗値を調整することにより、スパイラルインダクタのインダクタンス値を調整する。

上記構成によれば、ループ導体に接続された可変抵抗の抵抗値を調整することによって、ループ導体に流れる誘起電流量を調整でき、結果的に可変インダクタのインダクタンス値を精度良く調整できる。

【0016】

また、本発明は、前記可変インダクタであって、前記スパイラルインダクタの下部に、前記ループ導体が複数設けられるものを含む。

上記構成によれば、複数のループ導体に流れる誘起電流量をそれぞれ調整できるため、結果として可変インダクタのインダクタンス値を精度良く調整でき、かつ調整範囲を大きくできる。

【0017】

また、本発明は、前記可変インダクタであって、前記ループ導体は、前記スパイラルインダクタの形成された前記半導体基板の表面に垂直な方向において複数回巻回されたスパイラル状であり、前記スイッチは、前記ループ導体の一端を開放/短絡することによって前記ループ導体の巻数が変更可能に構成される。

上記構成によれば、複数のループ導体に流れる誘起電流量をそれぞれ調整できるため、結果として可変インダクタのインダクタンス値を精度良く調整でき、かつ調整範囲を大きくできる。また、ループの巻回回数を大きくすることによって、誘導電流の変化による磁束変化を拡大でき、インダクタンスの調整範囲を増大できる。

【0018】

また、本発明の半導体装置は、前記可変インダクタを含む構成である。

このような構成とすることによって、発振回路等のCMOS回路を構成する半導体基板上において可変インダクタを構成できるため、整合回路等に用いることにより高周波回路の周波数を調整できる。

【発明の効果】

【0019】

本発明の可変インダクタによれば、シリコン基板を貫通する貫通ビア等を用いたループ導体を、スパイラルインダクタの下層にループ導体を配置し、スイッチによりループ導体の一端を開放/短絡することによって、ループ導体に流れる誘起電流を調整する。これにより高周波数帯域において、インダクタンス値を効率よく変更できる。従って、ミリ波帯のように、広帯域において整合を調整する必要がある場合に用いる可変整合回路を構成できる。

【図面の簡単な説明】

【0020】

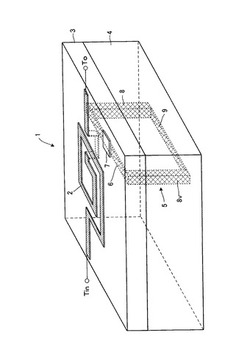

【図1】本発明の実施の形態1に係る可変インダクタの概略構成図

【図2】本発明の実施の形態1に係る可変インダクタを示す図、(a)は上面図、(b)は(a)のA−A断面図、(c)は(a)のB−B断面図

【図3】本発明の実施の形態1に係る可変インダクタを用いた半導体装置を示す図、(a)は等価回路、(b)は概略ブロック図

【図4】本発明の実施の形態2に係る可変インダクタの概略構成図

【図5】本発明の実施の形態2に係る可変インダクタを示す図、(a)は上面図、(b)は断面図

【図6】本発明の実施の形態3に係る可変インダクタの上面図

【図7】本発明の実施の形態4に係る可変インダクタのループ導体を示す斜視図

【図8】本発明の実施の形態4に係る可変インダクタを示す図、(a)は上面図、(b)は(a)のA−A断面図

【図9】本発明の実施の形態5に係る可変インダクタのループ導体を示す斜視図

【図10】本発明の実施の形態5に係る可変インダクタを示す図、(a)は可変インダクタのスパイラルインダクタ2の上面図、(b)はループ導体の上面図、(c)は(a)のA−A断面図

【図11】本発明の実施の形態5の変形例1に係る可変インダクタのループ導体を示す図、(a)は上面図、(b)は(a)のA−A断面図

【図12】本発明の実施の形態5の変形例2に係る可変インダクタのループ導体を示す図、(a)は上面図、(b)は(a)のA−A断面図

【図13】従来の可変インダクタの概略構成図

【図14】従来の可変インダクタの概略構成図

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について、図面を用いて説明する。

(実施の形態1)

次に、本発明の実施の形態1について図面を参照しつつ説明する。

図1は実施の形態1に係る可変インダクタの概略構成図である。図2(a)は可変インダクタ1の上面図、図2(b)はA−A断面図、図2(c)はB−B断面図)である。図3は可変インダクタ1を含む半導体集積回路装置100の概略構成図であり、図3(a)は半導体集積回路装置の等価回路を示す図、図3(b)は半導体集積回路装置の概略ブロック図である。

可変インダクタ1は、図3(a)および(b)に示すようにトランジスタ20、又は、キャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する。図1および図2(a)乃至(c)では可変インダクタについて示し、他の素子領域については省略する。

可変インダクタ1は、図1および図2に示すように、半導体基板としてのシリコン基板4表面に形成されたスパイラルインダクタ2と、スパイラルインダクタ2に対して垂直方向に形成されたループ導体5と、スイッチ7とを含む構成であり、スイッチ7によりループ導体5の一端を開放/短絡することによって、スパイラルインダクタ2のインダクタンス値を変更可能とした。

なお、可変インダクタ1の占有面積とは、図2(a)のループ導体5とスイッチ7とでしめされた領域であり、シリコン基板4表面に対しての面積である。

【0022】

スパイラルインダクタ2は、半導体基板としてのシリコン基板4の表面に層間絶縁膜3を介して最表層に形成されたスパイラル状の金層パターンを用いた表面導体において構成されている。

ループ導体5は、内層導体6としてのアルミニウム層パターンと、裏面導体9としてのアルミニウム層パターンと、垂直導体8と、スイッチ7とを用いて構成される。

なお、図1におけるスイッチ7と内層導体6としてのアルミニウム層パターンとの配置関係は、図の記載を簡略化している。より詳しい配置関係は、図2(b)、(c)に示す。

内層導体6としてのアルミニウム層パターンは、表面導体に対し、層間絶縁膜3を介して下層側に配置される。裏面導体9としてのアルミニウム層パターンは、シリコン基板4の裏面に形成される。垂直導体8は、シリコン基板4を貫通する貫通ビア8v内に形成される。スイッチ7は、ループ導体の一端を開放/短絡する。

スイッチ7は、図2(c)に示すように、ゲート電極7Gとゲート電極7Gを挟んで形成されたソース領域7S及びドレイン領域7Dとによって形成される。なお、ソース領域7S及びドレイン領域7Dが、ループ導体5に接続され、ループ導体5の一端の開放する、又は、短絡する。

【0023】

上記の構成をもつ可変インダクタを用いて、発振回路としての半導体集積回路装置の整合を調整する動作を以下に説明する。

可変インダクタ1は、層間絶縁膜3内に形成されたスパイラルインダクタ2と層間絶縁膜3とシリコン基板4内に構成されたループ導体5とを含む構成である。スパイラルインダクタ2は導体損を小さくするため、一般的なCMOSプロセスにおけるトップメタルである金層パターンを用いて構成される。

【0024】

ループ導体5は、層間絶縁膜3の内部配線である内層導体6と、層間絶縁膜3とシリコン基板4を貫通する貫通ビア8vに形成された垂直導体8と、シリコン基板4の裏面に配置される裏面導体9と、を用いて環状の導体を形成する。また、ループ導体5は、内層導体からなるループ導体5の一部をスイッチ7により開放/短絡できる。これらの各導体はアルミニウムを含む導体により形成される。

【0025】

ループ導体5は、スイッチ7を開放した場合には、スパイラルインダクタ2において発生する磁束がループ導体5の内側を貫いてもループ導体5に誘起電流が生じないためスパイラルインダクタ2のインダクタンス値は変わらない。

ループ導体5は、スイッチ7を短絡した場合、閉ループとなる。このため、スパイラルインダクタ2において発生磁束が、ループ導体5を貫くために、ループ導体5に誘起電流が流れ、スパイラルインダクタ2の磁束を打ち消すような磁束が発生する。そのため、スパイラルインダクタ2のインダクタンス値は減少する。

【0026】

スイッチ7の開放/短絡を制御することによって、ループ導体5に発生する誘起電流を調整し、スパイラルインダクタ2のインダクタンス値を調整できる。

次に、スパイラルインダクタ2とループ導体5との位置関係について説明する。図2は可変インダクタ1の上面図(a)、およびA−Aにおける断面図(b)をそれぞれ示す。ループ導体5はスパイラルインダクタ2の構成するライン下部に位置しており、ループ導体5を構成する内層導体6はスパイラルインダクタ2において使用する配線層より下部の配線層において構成されている。

【0027】

また、スイッチ7はトランジスタを用いて構成される。一般的なシリコン基板4上面(シリコン基板4と層間絶縁膜3の間)において構成され、内層導体6とスイッチ7は層間絶縁膜3内に形成されるビアにより接続される。ループ導体5を構成するために貫通ビア8vを用いているが、貫通ビア8vを用いずに、ループ導体5を層間絶縁膜3内において形成できる。

しかしながら、一般的なCMOSプロセスにおける層間膜厚は数μm程度と薄いため、ループ導体5の高さ方向の長さを十分に取ることが困難であり、ループ導体5により囲まれる面積が小さくなる。このため、スパイラルインダクタ2の磁束の影響を受けにくくなるので、インダクタンス値の調整幅も小さくなる。したがって、ループ導体5の形成では、貫通ビア8vを用いることが望ましい。

【0028】

以上のような構成によって、スパイラルインダクタ2のインダクタンス値を調整するループ導体5をスパイラルインダクタ2の下部に、スパイラルインダクタ2に対して垂直方向に配置することによって、可変インダクタ1とした場合の占有面積を拡大することなくインダクタンス値を調整でき、またスパイラルインダクタ2の入出力ラインを必要以上に伸ばす必要がなくなり、インダクタとしての損失を少なくできる。

【0029】

次に、図3に可変インダクタ1を含む半導体集積回路装置100の概略構成図を示す。(a)は半導体集積回路装置の等価回路の一例、(b)は半導体集積回路装置の概略ブロック図である。図3(a)および(b)に示すように、半導体集積回路装置100は可変インダクタ1の他に、トランジスタ20、キャパシタ21を含む構成であり、可変インダクタ1の周囲にはその他の素子が近接して配置されることが一般的である。

【0030】

図3の構成においても、ループ導体5をスパイラルインダクタ2の下部または内側に配置することによって、トランジスタ20又はキャパシタ21への影響を低減できる。これに対し、ループ導体5をスパイラルインダクタ2の下部より外側に配置する場合、スパイラルインダクタ2の占有面積が増大し、更に、トランジスタ20又はキャパシタ21に与える影響が大きくなる。

【0031】

以上のように、本発明の実施の形態によれば、スパイラルインダクタ2の下部に、スパイラルインダクタ2に対して垂直方向にループ導体5を形成し、ループ導体5を構成する内層導体6の一部をスイッチ7のON/OFFによって開放/短絡を制御するため、ループ導体5において発生する誘起電流を調整できる。その結果、可変インダクタ1の占有面積を小型化しながらインダクタンス値を調整できる。

【0032】

さらに、ループ導体5のサイズは、スパイラルインダクタ2のサイズに影響なく変更できるため、例えば内層導体6あるいは裏面導体9のパターン長を伸縮することによって、ループ導体5の周囲長(ループ導体5により囲まれる領域の面積)を調整できる。

また、貫通ビアではなく、所望の深さまでビアを形成することにより、貫通ビア8v内の垂直導体8の長さの調整でき、ループ導体5の周囲長(ループ導体5により囲まれる領域の面積)を調整できる。なお、中間層までのビアによりループ導体を形成できるが、ループ内面積が小さくなるため、相互インダクタンスは小さくなり、インダクタンスの調整範囲は小さくなる。

【0033】

本発明の実施の形態によれば、可変インダクタ1のインダクタンス値調整量に合わせて、ループ導体5の形状を決定できる。

【0034】

さらに、ループ導体5をスパイラルインダクタ2の下部に配置する場合には、配置する場所によってスパイラルインダクタ2の磁束の影響が変わるため、可変インダクタ1のインダクタンス値調整量に合わせて、ループ導体5の配置位置を決定できる。

【0035】

導体集積回路装置の製造プロセスにおける配線のための導体パターン形成工程において、表面導体及び裏面導体形成のためのマスクパターンを変更することによって、工数の増大なしにループ導体を形成できる。あるいは貫通ビアを形成する工程についても、半導体集積回路装置において貫通ビアを形成する場合には同一プロセスによって形成すればよい。

あるいは途中工程において貫通ビアが形成される場合は、後続工程において、貫通ビア内に形成された垂直導体に接続するビアを更に形成し、垂直方向に接続してもよい。

以上のように、本発明によれば、ループ導体を半導体基板の一表面に対して垂直なループを構成することによって、半導体基板上における占有面積を増大することなく、ループ面積を大きくとることができる。

そして、ループ導体を流れる誘導電流により、スパイラルインダクタにおいて発生する磁束の影響を、より大きく受けられるため、可変インダクタのインダクタンス値を大きく変えることができる。また、発振回路としての半導体集積回路装置において、製造プロセスにおける配線のための導体パターン形成工程において、マスクパターンの変更によって工数の増大なしにループ導体を形成できる。

【0036】

なお、本実施の形態では、ループ導体5を開放/短絡するためにスイッチ7を用いているが、例えばスイッチ7に代えて、抵抗を並列接続し、可変抵抗として、抵抗値の調整によってループ導体5に流れる誘起電流を調整しても良い。前述の構成によって、可変インダクタ1のインダクタンス値を精度良く調整できる。

【0037】

また、前述したように、ループ導体5を、スパイラルインダクタ2を構成するライン直下またはライン直下より内側に形成することによって、可変インダクタ1の占有面積を拡大することなく、インダクタンス値を調整できる。

しかしながら、ループ導体は、スパイラルインダクタの内側に限定されることなく外側にはみ出してもよいし、内側から外側にわたって形成されてもよい。

【0038】

また、本実施の形態において説明した可変インダクタを高周波回路の整合回路に用いることによって、整合回路の整合状態を調整でき、広い周波数帯にわたって整合を調整できる。

【0039】

(実施の形態2)

次に、本発明の実施の形態2について図面を参照しつつ説明する。

図4は実施の形態2に係る可変インダクタの概略構成図である。図5(a)は可変インダクタ1の上面図、図5(b)はA−A断面図である。

可変インダクタ1は、前記実施の形態1と同様、トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する(図3(a)および(b)参照)。ここでは可変インダクタについて示し、他の素子領域については省略する。

可変インダクタ1は、図5に示すように、半導体基板としてのシリコン基板4表面に形成されたスパイラルインダクタ2と、スパイラルインダクタ2に対して垂直方向に形成された2つのループ導体すなわち第1及び第2のループ導体5a、5bと、第1及び第2のスイッチ7a,7bとを用いて構成される。

第1及び第2のループ導体5a、5bは、スパイラルインダクタ2の最外周の相対向する2辺2o1,2o2に沿って形成される。それぞれのループ導体は前記実施の形態1のループ導体5と同様である。可変インダクタ1は、相対向して同様のループ導体が一つ追加されている。

可変インダクタ1は、各ループ導体は同様に形成され、それぞれスイッチを用いて構成され、第1及び第2のスイッチ7a、7bにより第1及び第2のループ導体5a、5bの一端を開放/短絡することによって、スパイラルインダクタ2のインダクタンス値を変更可能とした。

その他の構成は実施の形態1の可変インダクタと同様であるためここでは説明を省略する。同一部位には同一符号を付した。

【0040】

以下、可変インダクタの動作について説明する。基本的な動作は実施の形態1において説明したとおりであるため省略する。可変インダクタは、第1および第2のループ導体5a、5bを設け、第1および第2のスイッチ7a、7bをON/OFFさせて第1および第2のループ導体5a、5bを構成する内層導体6の一端を開放/短絡する。これにより、可変インダクタは、第1および第2のループ導体5a、5bに流れる誘起電流を調整でき、スパイラルインダクタ2のインダクタンス値を変更できる。

【0041】

すなわち、スパイラルインダクタ2に対して、第1のループ導体5aと第2のループ導体5bを設け、第1のスイッチ7aと第2のスイッチ7bを同時にONすれば、第1のループ導体5aと第2のループ導体5bのいずれにも誘起電流が生じる。その結果、スパイラルインダクタ2のインダクタンス値を大きく変えることができる。

【0042】

この構成においても、図5(a)および図5(b)に示すように、第1のループ導体5a及び第2のループ導体5bをそれぞれスパイラルインダクタ2の下部に垂直方向に形成できるため、可変インダクタ1の半導体基板の一表面における占有面積を大きくすることなく、インダクタンス値の可変幅を大きくできる。

【0043】

本発明の実施の形態によれば、半導体集積回路装置は、スパイラルインダクタ2の下部に、スパイラルインダクタ2に対して垂直方向に第1のループ導体5aおよび第2のループ導体5bを形成し、第1のループ導体5aを構成する内層導体6の一部を第1のスイッチ7aのON/OFFによって開放/短絡し、第2のループ導体5bを構成する内層導体6の一部を第2のスイッチ7bのON/OFFによって開放/短絡を制御するため、第1のループ導体5a及び第2のループ導体5bにおいて発生する誘起電流を調整でき、結果的に可変インダクタ1の占有面積を小型化しながらインダクタンス値を大きく調整できる。

【0044】

第1及び第2のループ導体5a及び5bをスパイラルインダクタ2下部に配置する場合に、配置する場所によってスパイラルインダクタ2の磁束の影響が変わるため、可変インダクタ1のインダクタンス値調整量に合わせて、第1及び第2のループ導体5a及び5bの配置位置を決定できる。例えば、第1及び第2のループ導体5a及び5bを、スパイラルインダクタ2を構成する導体パターン(ライン)直下または導体パターン直下より内側に形成することによって、可変インダクタ1の占有面積を大きくすることなく、インダクタンス値を調整できる。

【0045】

なお、本実施の形態では、第1及び第2のループ導体5a及び5bを開放/短絡するために第1及び第2のスイッチ7a及び7bを用いているが、例えばスイッチに代えて、抵抗を並列化した可変抵抗として、抵抗値の調整によって、第1及び第2のループ導体5a及び5bに流れる誘起電流を調整しても良い。このため、可変インダクタ1のインダクタンス値を精度良く調整できる。

【0046】

(実施の形態3)

次に、本発明の実施の形態3について図面を参照しつつ説明する。図6は実施の形態3に係る可変インダクタの概略構成図である。

可変インダクタ1は、実施の形態1と同様、トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する(図3(a)および(b)参照)。図6では、可変インダクタについて示し、他の素子領域については省略する。

可変インダクタ1は、図6に示すように、半導体基板としてのシリコン基板4表面に形成されたスパイラルインダクタ2と、スパイラルインダクタ2に対して垂直方向に形成された4つのループ導体、すなわち第1乃至第4のループ導体5a乃至5dと、第1乃至第4のスイッチ7a乃至7dとを用いて構成される。

第1及び第2のループ導体5a、5bは、スパイラルインダクタ2の最外周の相対向する2辺2o1,2o2に沿って形成される。また第3及び第4のループ導体5c、5dは、スパイラルインダクタ2の最外周の相対向するもう1組の2辺2o3,2o4に沿って形成される。

それぞれのループ導体は前記実施の形態1のループ導体5と同様であり、相対向して同様のループ導体が一つ追加された可変インダクタ1である。各ループ導体は、同じ形状であり、それぞれにスイッチ7を含む構成である。第1乃至第4のスイッチ7a、7b、7c、7dが、第1乃至第4のループ導体5a、5b、5c、5dの一端を開放/短絡することによって、スパイラルインダクタ2のインダクタンス値を変更可能とした。

その他の構成は実施の形態1および2の可変インダクタと同様であるためここでは説明を省略する。同一部位には同一符号を付した。

【0047】

図6に示すように、スパイラルインダクタ2の下部の最外周の4辺2o1,2o2,2o3,2o4に沿って形成される。4方向に対して、垂直方向にループ導体が形成されるよう、第1乃至第4のループ導体5a、5b、5c、5dを設け、それぞれ第1乃至第4のスイッチ7a、7b、7c、7dによりON/OFFするため、4つのループ導体に流れる誘起電流を調整できるため、インダクタンス値をより大きく調整できる。

なお、本実施の形態の構成では、第1乃至第4のループ導体5a、5b、5c、5dをスパイラルインダクタ2の最外周の相対向する2組の辺2o1,2o2、2o3,2o4の幅になるべく等しく形成するのが望ましい。これは磁束の漏れを防ぐためであり、この構成によれば、相互インダクタンスを最大限に大きく出来、インダクタンスの調整範囲を大きく出来る。

【0048】

また、本実施の形態において説明した可変インダクタを高周波回路の整合回路に用いることにより、整合回路の整合状態をさらに大きな範囲において調整でき、広い周波数帯において整合を調整できる。

【0049】

(実施の形態4)

次に、本発明の実施の形態4について図面を参照しつつ説明する。

図7は実施の形態4に係る可変インダクタのループ導体を示す斜視図、図8(a)は上面図、図8(b)は図8(a)のA−A断面図である。

前記実施の形態1乃至3ではループ導体は、巻き数1回であったが、本実施の形態では、巻き数を3回にした。

この構成においても、各ループは前記実施の形態1乃至3と同様に、内層導体6としての平行な3本のアルミニウム層パターンと、裏面導体9としての平行な3本のアルミニウム層パターンと、平行な6本の垂直導体8と、を含む構成であり、ループ導体もスパイラル状のループを構成している。

内層導体6としての平行な3本のアルミニウム層パターンは、スパイラルインダクタ2を構成する表面導体に対し、層間絶縁膜3を介して下層側に配置される。裏面導体9としての平行な3本のアルミニウム層パターンは、シリコン基板4の裏面に形成される。平行な6本の垂直導体8は、シリコン基板4を貫通する貫通ビア内に形成される。

そしてループ導体の一端を開放/短絡するためのスイッチ(図示せず)が設けられている。

【0050】

その他の構成は実施の形態1および2の可変インダクタと同様であるためここでは説明を省略する。同一部位には同一符号を付した。

【0051】

可変インダクタ1についても、占有面積の増大を招くことなく、前記実施の形態1と同様トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成するが、より、効率よく調整が可能となり、整合回路の整合状態をさらに大きな範囲において調整でき、広い周波数帯において整合を調整できる。

【0052】

(実施の形態5)

次に、本発明の実施の形態5について図面を参照しつつ説明する。

図9は実施の形態5に係る可変インダクタを示す斜視図、図10(a)は可変インダクタのスパイラルインダクタ2の上面図、図10(b)はループ導体5の上面図、図10(c)は、(a)のA−A断面図である。

前記実施の形態1乃至4ではループ導体は、基板表面に対して垂直に配されたが、本実施の形態の可変インダクタは、スパイラルインダクタ2に沿って層間絶縁膜3を介して平行にループ導体15を設けた。

【0053】

ループ導体15は、スパイラルインダクタ2と同様のパターンを用いて構成され、層間絶縁膜3を介して平行に形成されている。したがって磁束の漏れはほとんどなく、しかもループ導体15と、スパイラルインダクタ2との相互の距離は近接しているため相互インダクタンスを大きくできる。したがってインダクタンスの調整範囲を最大限に大きく出来る。

【0054】

この構成においては、ループ導体15は、スパイラルインダクタ2を構成する表面導体に対し、層間絶縁膜3を介して平行に、下層側に配置された内層導体6としてのスパイラル上のアルミニウム層パターン6sを用いて構成されている。

【0055】

この構成によれば、ループ導体15は、ループを形成するためにビア18によって内層導体6のアルミニウム層パターン6sを接続する以外は、平面パターンを用いて構成されるため、製造がさらに容易となる。なおループ導体は1周のループであってもよい。

【0056】

その他の構成は実施の形態1乃至4の可変インダクタと同じであるためここでは説明を省略する。同一部位には同一符号を付した。

【0057】

可変インダクタ1についても、占有面積の増大を招くことなく、前記実施の形態1と同様トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する。

このため、より効率よく調整でき、整合回路の整合状態をさらに大きな範囲において調整できる。従って、広い周波数帯にわたって整合を調整できる。

【0058】

(変形例1)

また、図11(a)および(b)に図10の変形例としてループ導体の上面図および断面図を示すように、同心体を構成するように複数周、例えば3周のループを持つループ導体を用いて構成しても良い。この構成によればパターン形成が1つの層により完了するため、製造が容易である。1周ごとに閉ループを形成してもよいが、1周ごとに閉ループを形成するパターン長は少なくてすむが、スイッチ7を1ループ毎に形成する必要がある。図11(b)は図11(a)のA−A断面図である。

【0059】

(変形例2)

さらにまた、図12(a)および(b)に図11(a)および(b)に示した同心体を構成する複数周のループを持つループ導体を構成した例の変形例としてループ導体の上面図および断面図を示すように、2層構造を用いて2周のループ導体25を形成してもよい。

そしてループ導体の一端を開放/短絡するためのスイッチ7が設けられている。

【0060】

なお、上述した実施の形態では、ループ導体としては、アルミニウムおよび金を用いたが、他の金属導体でもよく、表面導体あるいは裏面導体と、貫通ビアなどのビア内側に形成される導体とは別の導体材料を用いてもよい。

【0061】

また、前記実施の形態では、シリコンデバイスを構成するシリコン基板に可変インダクタンスを集積化して形成した例について説明したが、シリコン基板以外にも、HEMT又はHBTを含む化合物半導体デバイス、GaAsデバイス、InPデバイス、又はGaNデバイスにも集積化可能である。化合物半導体デバイスでは、アルミニウム又は金以外にも、仕事関数を含む所定の条件を満たす導体材料を用いればよく、単層金属あるいは多層金属を用いてもよい。

【産業上の利用可能性】

【0062】

本発明に係る可変インダクタは、例えばシリコン基板を貫通する貫通ビアを含むビアを用いたループ導体をスパイラルインダクタの下部に垂直方向に形成し、ループ導体の一部をスイッチを用いて開放/短絡してループ導体に流れる誘起電流を調整することによって、インダクタンス値を可変に出来るという有利な効果を有するため、ミリ波帯の整合回路のように、容量が小さく、調整が難しい整合回路における可変インダクタとして有効である。

本発明の可変インダクタは、CMOSデバイスを含むシリコンデバイス、HEMT又はHBTを含む化合物半導体デバイス、GaAsデバイス、InPデバイス又はGaNデバイスにも集積化可能である。

【符号の説明】

【0063】

1 可変インダクタ

2 スパイラルインダクタ

3 層間絶縁膜

4 シリコン基板

5,5s、15,25 ループ導体

5a 第1のループ導体

5b 第2のループ導体

5c 第3のループ導体

5d 第4のループ導体

6 内層導体

7 スイッチ

7G ゲート電極

7S ソース領域

7D ドレイン領域

7a 第1のスイッチ

7b 第2のスイッチ

7c 第3のスイッチ

7d 第4のスイッチ

8 垂直導体

8v 貫通ビア

9 裏面導体

18 ビア

20 トランジスタ

21 キャパシタ

100 半導体集積回路装置

101 インダクタンス可変素子

102 スパイラル電極

103、104 入出力電極

105、106 スイッチ

107、108 ゲート電極

109、110、111 拡散領域

112 絶縁層

113 Si基板

201 スパイラルコイル

202 スパイラルコイルの第1層

203 スパイラルコイルの第2層

204 制御回路

205 スイッチ

206 シリコン基板

207 周囲配線

208 周囲配線の第1層

209 周囲配線の第2層

【技術分野】

【0001】

本発明は、可変インダクタ及びこれを用いた半導体装置に係り、例えばCMOSプロセスを用いて形成され、ミリ波帯を含む超高周波数帯において用いられる半導体装置において、整合回路を構成するインダクタのインダクタンス値を調整する技術に関するものである。

【背景技術】

【0002】

ミリ波帯を用いた無線通信分野においてCMOSプロセスを用いたMMIC(monolithic microwave integrated circuit)の開発が進められており、整合回路の集中定数化によるチップ面積の小型化も進められている。

一般に、整合回路を集中定数化すると、インダクタンス又は容量の自己共振周波数によって、狭帯域化するという課題がある。

集中定数化された素子を用いた整合回路では、狭帯域特性を改善するために、整合回路を可変にすることが一般的である。整合回路内の容量を可変とするためには、バラクタを用いるか、容量を並列化してスイッチのON/OFFによって制御することが考えられる。しかしながら、ミリ波帯ではバラクタ又はスイッチを用いることによって整合回路における損失が大きくなるという課題がある。

【0003】

このような課題を解決する方法として、例えばインダクタのインダクタンス値を調整する構成が提案されている(例えば特許文献1、特許文献2参照)。

図13は特許文献1に記載された可変インダクタの概略構成図である。図13において、インダクタンス可変素子101は、渦巻き状のスパイラル電極102と、スパイラル電極102の周回部分を短絡することにより、入出力電極103、104間を流れる電流を、短絡させるためのスイッチ105、106とを有している。

スイッチ105、106は、ゲート電極107、108と、ゲート電極107、108を挟んで形成された拡散領域109、110、111とを用いて構成されている。これらインダクタンス可変素子101、スイッチ105、106は、絶縁層112を介して、シリコン基板113上に形成されている。

拡散領域109、110、111のそれぞれは、p型不純物を熱拡散あるいはイオン打ち込みにより、n型シリコン基板113表面に形成される。

【0004】

可変インダクタにおいては、インダクタンス値は入出力電極103、104の間のスパイラル電極102の長さによって決定される。可変インダクタは、スイッチ105をONすることにより、入出力電極103、104間のスパイラル電極102の長さを短くでき、さらにスイッチ106をONすることによって、スパイラル電極102の長さをさらに短くできる。

【0005】

また、図14に、特許文献2に記載された可変インダクタの概略構成図を示す。図14において、スパイラルコイル201、スパイラルコイルの第1層202、スパイラルコイルの第2層203、制御回路204、スイッチ205、シリコン基板206、周囲配線207、周囲配線の第1層208、周囲配線の第2層209を含む構成である。

【0006】

特許文献2の可変インダクタは以下のように構成される。スパイラルコイル201の周囲に周囲配線207を設け、周囲配線207の一端にスイッチ205を接続した構成において、制御回路204からの制御信号によってスイッチをON/OFFさせ、周囲配線207の一端を開放/短絡させる。

周囲配線207の一端を開放させた状態に比べて、周囲配線207の一端を短絡させた状態では、スパイラルコイル201において発生する磁束が周囲配線207を貫通することによって周囲配線207に誘導電流が流れ、スパイラルコイル201の磁束を打ち消し、スパイラルコイル201のインダクタンス値は低下する。すなわち、スイッチ205をON/OFFすることによって周囲配線207の一端を開放/短絡し、インダクタンス値を可変とする。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3318086号公報

【特許文献2】特開2008−16703号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記特許文献1のインダクタ構成では、スイッチのON/OFFによってインダクタンス値を変更できるが、インダクタに直列にスイッチが配置さるため、ミリ波帯ではスイッチの影響によって損失が大きくなるという課題がある。

また、上記特許文献2のようなインダクタ構成では、周囲配線207の状況によってインダクタンス値を変更できるが、インダクタンス値を変更するにはインダクタ周囲に配線領域が必要となり、インダクタの占める面積が大きくなるという課題がある。

また、インダクタ周囲に周囲配線を設けることにより、インダクタの入出力ラインの下部が配線領域となるため、インダクタの入出力ラインが長くなり、損失が大きくなるという課題がある。

【0009】

本発明は、前記実情に鑑みてなされたものであり、インダクタの占有面積を拡大させずに、また調整可能な周波数帯域が広く、損失の小さい可変インダクタを提供することを目的とする。

【課題を解決するための手段】

【0010】

上記の課題を解決するための本発明の可変インダクタは、半導体基板上に形成された、スパイラルインダクタと、ループ導体と、前記ループ導体の一端を開放/短絡するスイッチと、を含む可変インダクタであって、前記ループ導体は前記スパイラルインダクタの下層に配置され、前記スイッチを用いて前記ループ導体の一端を開放/短絡することによって、前記スパイラルインダクタのインダクタンス値を変更可能としたものである。

上記構成によれば、可変インダクタの占有面積を拡大させずに、インダクタンス値を調整できる。

【0011】

また、本発明は、前記可変インダクタであって、前記ループ導体は前記スパイラルインダクタに対して垂直方向に形成されたものを含む。

この構成によれば、ループ導体がスパイラルインダクタに対して垂直方向に形成されているため、占有面積を小さくでき、MOSFETを含むトランジスタを用いてスイッチを形成する場合にも、スパイラルインダクタの形成領域下に収まめることが可能となる。

【0012】

また、本発明は、前記可変インダクタであって、前記スパイラルインダクタが、前記半導体基板の一表面に形成されており、前記ループ導体は、前記スパイラルインダクタより下層に形成された第1層導体と、前記第1層導体よりも下層に形成された第2層導体と、前記半導体基板の少なくとも一部を、前記表面に垂直な方向に形成されたビア内に形成され、前記第1及び第2層導体間を接続する垂直導体と、前記ループ導体の一端を開放/短絡するためのスイッチと、を用いて構成される。

上記構成によれば、ループ導体を半導体基板の一表面に対して垂直なループを構成することによって、半導体基板上における占有面積を拡大することなく、ループ面積を大きくとることができる。そして、ループ導体を流れる誘導電流により、結果的にスパイラルインダクタにより発生する磁束の影響を、より大きく受けられるため、可変インダクタのインダクタンス値を大きく変えることができる。また、発振回路としての半導体集積回路装置において、製造プロセスにおける配線のための導体パターン形成工程において、マスクパターンの変更によって、工数の増大なしにループ導体を形成できる。

【0013】

また、本発明は、前記可変インダクタであって、前記半導体基板はシリコン基板であり、前記スパイラルインダクタは、前記シリコン基板の最表層に形成された表面導体において構成され、前記第1の導体は、前記表面導体に対し、層間絶縁膜を介して下層側に配置された内層導体であり、前記第2の導体は、前記シリコン基板の裏面に形成された裏面導体であり、前記ループ導体は、前記内層導体と、前記シリコン基板を貫通する貫通ビア内に形成された垂直導体と、前記裏面導体と、前記ループ導体の一端を開放/短絡するためのスイッチとを含む。

上記構成によれば、ループ導体のループ面積を大きくとることができ、結果的にスパイラルインダクタにおいて発生する磁束の影響をより大きく受けるため、可変インダクタのインダクタンス値の可変範囲を大きくできる。また裏面導体を用いているため、より大きなループを形成でき、インダクタンス値の可変範囲を広くできる。

【0014】

また、本発明は、前記可変インダクタであって、前記ループ導体は、前記スパイラルインダクタを構成する最外周ラインにより囲まれた領域下、あるいは内側に配置される。

上記構成によれば、ループ導体に起因する占有面積の増大なしに、前記可変インダクタのインダクタンスを効率よく変更できる。

【0015】

また、本発明は、前記可変インダクタであって、前記スイッチは、前記ループ導体の一端に接続された可変抵抗を含み、前記可変抵抗の抵抗値を調整することにより、スパイラルインダクタのインダクタンス値を調整する。

上記構成によれば、ループ導体に接続された可変抵抗の抵抗値を調整することによって、ループ導体に流れる誘起電流量を調整でき、結果的に可変インダクタのインダクタンス値を精度良く調整できる。

【0016】

また、本発明は、前記可変インダクタであって、前記スパイラルインダクタの下部に、前記ループ導体が複数設けられるものを含む。

上記構成によれば、複数のループ導体に流れる誘起電流量をそれぞれ調整できるため、結果として可変インダクタのインダクタンス値を精度良く調整でき、かつ調整範囲を大きくできる。

【0017】

また、本発明は、前記可変インダクタであって、前記ループ導体は、前記スパイラルインダクタの形成された前記半導体基板の表面に垂直な方向において複数回巻回されたスパイラル状であり、前記スイッチは、前記ループ導体の一端を開放/短絡することによって前記ループ導体の巻数が変更可能に構成される。

上記構成によれば、複数のループ導体に流れる誘起電流量をそれぞれ調整できるため、結果として可変インダクタのインダクタンス値を精度良く調整でき、かつ調整範囲を大きくできる。また、ループの巻回回数を大きくすることによって、誘導電流の変化による磁束変化を拡大でき、インダクタンスの調整範囲を増大できる。

【0018】

また、本発明の半導体装置は、前記可変インダクタを含む構成である。

このような構成とすることによって、発振回路等のCMOS回路を構成する半導体基板上において可変インダクタを構成できるため、整合回路等に用いることにより高周波回路の周波数を調整できる。

【発明の効果】

【0019】

本発明の可変インダクタによれば、シリコン基板を貫通する貫通ビア等を用いたループ導体を、スパイラルインダクタの下層にループ導体を配置し、スイッチによりループ導体の一端を開放/短絡することによって、ループ導体に流れる誘起電流を調整する。これにより高周波数帯域において、インダクタンス値を効率よく変更できる。従って、ミリ波帯のように、広帯域において整合を調整する必要がある場合に用いる可変整合回路を構成できる。

【図面の簡単な説明】

【0020】

【図1】本発明の実施の形態1に係る可変インダクタの概略構成図

【図2】本発明の実施の形態1に係る可変インダクタを示す図、(a)は上面図、(b)は(a)のA−A断面図、(c)は(a)のB−B断面図

【図3】本発明の実施の形態1に係る可変インダクタを用いた半導体装置を示す図、(a)は等価回路、(b)は概略ブロック図

【図4】本発明の実施の形態2に係る可変インダクタの概略構成図

【図5】本発明の実施の形態2に係る可変インダクタを示す図、(a)は上面図、(b)は断面図

【図6】本発明の実施の形態3に係る可変インダクタの上面図

【図7】本発明の実施の形態4に係る可変インダクタのループ導体を示す斜視図

【図8】本発明の実施の形態4に係る可変インダクタを示す図、(a)は上面図、(b)は(a)のA−A断面図

【図9】本発明の実施の形態5に係る可変インダクタのループ導体を示す斜視図

【図10】本発明の実施の形態5に係る可変インダクタを示す図、(a)は可変インダクタのスパイラルインダクタ2の上面図、(b)はループ導体の上面図、(c)は(a)のA−A断面図

【図11】本発明の実施の形態5の変形例1に係る可変インダクタのループ導体を示す図、(a)は上面図、(b)は(a)のA−A断面図

【図12】本発明の実施の形態5の変形例2に係る可変インダクタのループ導体を示す図、(a)は上面図、(b)は(a)のA−A断面図

【図13】従来の可変インダクタの概略構成図

【図14】従来の可変インダクタの概略構成図

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について、図面を用いて説明する。

(実施の形態1)

次に、本発明の実施の形態1について図面を参照しつつ説明する。

図1は実施の形態1に係る可変インダクタの概略構成図である。図2(a)は可変インダクタ1の上面図、図2(b)はA−A断面図、図2(c)はB−B断面図)である。図3は可変インダクタ1を含む半導体集積回路装置100の概略構成図であり、図3(a)は半導体集積回路装置の等価回路を示す図、図3(b)は半導体集積回路装置の概略ブロック図である。

可変インダクタ1は、図3(a)および(b)に示すようにトランジスタ20、又は、キャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する。図1および図2(a)乃至(c)では可変インダクタについて示し、他の素子領域については省略する。

可変インダクタ1は、図1および図2に示すように、半導体基板としてのシリコン基板4表面に形成されたスパイラルインダクタ2と、スパイラルインダクタ2に対して垂直方向に形成されたループ導体5と、スイッチ7とを含む構成であり、スイッチ7によりループ導体5の一端を開放/短絡することによって、スパイラルインダクタ2のインダクタンス値を変更可能とした。

なお、可変インダクタ1の占有面積とは、図2(a)のループ導体5とスイッチ7とでしめされた領域であり、シリコン基板4表面に対しての面積である。

【0022】

スパイラルインダクタ2は、半導体基板としてのシリコン基板4の表面に層間絶縁膜3を介して最表層に形成されたスパイラル状の金層パターンを用いた表面導体において構成されている。

ループ導体5は、内層導体6としてのアルミニウム層パターンと、裏面導体9としてのアルミニウム層パターンと、垂直導体8と、スイッチ7とを用いて構成される。

なお、図1におけるスイッチ7と内層導体6としてのアルミニウム層パターンとの配置関係は、図の記載を簡略化している。より詳しい配置関係は、図2(b)、(c)に示す。

内層導体6としてのアルミニウム層パターンは、表面導体に対し、層間絶縁膜3を介して下層側に配置される。裏面導体9としてのアルミニウム層パターンは、シリコン基板4の裏面に形成される。垂直導体8は、シリコン基板4を貫通する貫通ビア8v内に形成される。スイッチ7は、ループ導体の一端を開放/短絡する。

スイッチ7は、図2(c)に示すように、ゲート電極7Gとゲート電極7Gを挟んで形成されたソース領域7S及びドレイン領域7Dとによって形成される。なお、ソース領域7S及びドレイン領域7Dが、ループ導体5に接続され、ループ導体5の一端の開放する、又は、短絡する。

【0023】

上記の構成をもつ可変インダクタを用いて、発振回路としての半導体集積回路装置の整合を調整する動作を以下に説明する。

可変インダクタ1は、層間絶縁膜3内に形成されたスパイラルインダクタ2と層間絶縁膜3とシリコン基板4内に構成されたループ導体5とを含む構成である。スパイラルインダクタ2は導体損を小さくするため、一般的なCMOSプロセスにおけるトップメタルである金層パターンを用いて構成される。

【0024】

ループ導体5は、層間絶縁膜3の内部配線である内層導体6と、層間絶縁膜3とシリコン基板4を貫通する貫通ビア8vに形成された垂直導体8と、シリコン基板4の裏面に配置される裏面導体9と、を用いて環状の導体を形成する。また、ループ導体5は、内層導体からなるループ導体5の一部をスイッチ7により開放/短絡できる。これらの各導体はアルミニウムを含む導体により形成される。

【0025】

ループ導体5は、スイッチ7を開放した場合には、スパイラルインダクタ2において発生する磁束がループ導体5の内側を貫いてもループ導体5に誘起電流が生じないためスパイラルインダクタ2のインダクタンス値は変わらない。

ループ導体5は、スイッチ7を短絡した場合、閉ループとなる。このため、スパイラルインダクタ2において発生磁束が、ループ導体5を貫くために、ループ導体5に誘起電流が流れ、スパイラルインダクタ2の磁束を打ち消すような磁束が発生する。そのため、スパイラルインダクタ2のインダクタンス値は減少する。

【0026】

スイッチ7の開放/短絡を制御することによって、ループ導体5に発生する誘起電流を調整し、スパイラルインダクタ2のインダクタンス値を調整できる。

次に、スパイラルインダクタ2とループ導体5との位置関係について説明する。図2は可変インダクタ1の上面図(a)、およびA−Aにおける断面図(b)をそれぞれ示す。ループ導体5はスパイラルインダクタ2の構成するライン下部に位置しており、ループ導体5を構成する内層導体6はスパイラルインダクタ2において使用する配線層より下部の配線層において構成されている。

【0027】

また、スイッチ7はトランジスタを用いて構成される。一般的なシリコン基板4上面(シリコン基板4と層間絶縁膜3の間)において構成され、内層導体6とスイッチ7は層間絶縁膜3内に形成されるビアにより接続される。ループ導体5を構成するために貫通ビア8vを用いているが、貫通ビア8vを用いずに、ループ導体5を層間絶縁膜3内において形成できる。

しかしながら、一般的なCMOSプロセスにおける層間膜厚は数μm程度と薄いため、ループ導体5の高さ方向の長さを十分に取ることが困難であり、ループ導体5により囲まれる面積が小さくなる。このため、スパイラルインダクタ2の磁束の影響を受けにくくなるので、インダクタンス値の調整幅も小さくなる。したがって、ループ導体5の形成では、貫通ビア8vを用いることが望ましい。

【0028】

以上のような構成によって、スパイラルインダクタ2のインダクタンス値を調整するループ導体5をスパイラルインダクタ2の下部に、スパイラルインダクタ2に対して垂直方向に配置することによって、可変インダクタ1とした場合の占有面積を拡大することなくインダクタンス値を調整でき、またスパイラルインダクタ2の入出力ラインを必要以上に伸ばす必要がなくなり、インダクタとしての損失を少なくできる。

【0029】

次に、図3に可変インダクタ1を含む半導体集積回路装置100の概略構成図を示す。(a)は半導体集積回路装置の等価回路の一例、(b)は半導体集積回路装置の概略ブロック図である。図3(a)および(b)に示すように、半導体集積回路装置100は可変インダクタ1の他に、トランジスタ20、キャパシタ21を含む構成であり、可変インダクタ1の周囲にはその他の素子が近接して配置されることが一般的である。

【0030】

図3の構成においても、ループ導体5をスパイラルインダクタ2の下部または内側に配置することによって、トランジスタ20又はキャパシタ21への影響を低減できる。これに対し、ループ導体5をスパイラルインダクタ2の下部より外側に配置する場合、スパイラルインダクタ2の占有面積が増大し、更に、トランジスタ20又はキャパシタ21に与える影響が大きくなる。

【0031】

以上のように、本発明の実施の形態によれば、スパイラルインダクタ2の下部に、スパイラルインダクタ2に対して垂直方向にループ導体5を形成し、ループ導体5を構成する内層導体6の一部をスイッチ7のON/OFFによって開放/短絡を制御するため、ループ導体5において発生する誘起電流を調整できる。その結果、可変インダクタ1の占有面積を小型化しながらインダクタンス値を調整できる。

【0032】

さらに、ループ導体5のサイズは、スパイラルインダクタ2のサイズに影響なく変更できるため、例えば内層導体6あるいは裏面導体9のパターン長を伸縮することによって、ループ導体5の周囲長(ループ導体5により囲まれる領域の面積)を調整できる。

また、貫通ビアではなく、所望の深さまでビアを形成することにより、貫通ビア8v内の垂直導体8の長さの調整でき、ループ導体5の周囲長(ループ導体5により囲まれる領域の面積)を調整できる。なお、中間層までのビアによりループ導体を形成できるが、ループ内面積が小さくなるため、相互インダクタンスは小さくなり、インダクタンスの調整範囲は小さくなる。

【0033】

本発明の実施の形態によれば、可変インダクタ1のインダクタンス値調整量に合わせて、ループ導体5の形状を決定できる。

【0034】

さらに、ループ導体5をスパイラルインダクタ2の下部に配置する場合には、配置する場所によってスパイラルインダクタ2の磁束の影響が変わるため、可変インダクタ1のインダクタンス値調整量に合わせて、ループ導体5の配置位置を決定できる。

【0035】

導体集積回路装置の製造プロセスにおける配線のための導体パターン形成工程において、表面導体及び裏面導体形成のためのマスクパターンを変更することによって、工数の増大なしにループ導体を形成できる。あるいは貫通ビアを形成する工程についても、半導体集積回路装置において貫通ビアを形成する場合には同一プロセスによって形成すればよい。

あるいは途中工程において貫通ビアが形成される場合は、後続工程において、貫通ビア内に形成された垂直導体に接続するビアを更に形成し、垂直方向に接続してもよい。

以上のように、本発明によれば、ループ導体を半導体基板の一表面に対して垂直なループを構成することによって、半導体基板上における占有面積を増大することなく、ループ面積を大きくとることができる。

そして、ループ導体を流れる誘導電流により、スパイラルインダクタにおいて発生する磁束の影響を、より大きく受けられるため、可変インダクタのインダクタンス値を大きく変えることができる。また、発振回路としての半導体集積回路装置において、製造プロセスにおける配線のための導体パターン形成工程において、マスクパターンの変更によって工数の増大なしにループ導体を形成できる。

【0036】

なお、本実施の形態では、ループ導体5を開放/短絡するためにスイッチ7を用いているが、例えばスイッチ7に代えて、抵抗を並列接続し、可変抵抗として、抵抗値の調整によってループ導体5に流れる誘起電流を調整しても良い。前述の構成によって、可変インダクタ1のインダクタンス値を精度良く調整できる。

【0037】

また、前述したように、ループ導体5を、スパイラルインダクタ2を構成するライン直下またはライン直下より内側に形成することによって、可変インダクタ1の占有面積を拡大することなく、インダクタンス値を調整できる。

しかしながら、ループ導体は、スパイラルインダクタの内側に限定されることなく外側にはみ出してもよいし、内側から外側にわたって形成されてもよい。

【0038】

また、本実施の形態において説明した可変インダクタを高周波回路の整合回路に用いることによって、整合回路の整合状態を調整でき、広い周波数帯にわたって整合を調整できる。

【0039】

(実施の形態2)

次に、本発明の実施の形態2について図面を参照しつつ説明する。

図4は実施の形態2に係る可変インダクタの概略構成図である。図5(a)は可変インダクタ1の上面図、図5(b)はA−A断面図である。

可変インダクタ1は、前記実施の形態1と同様、トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する(図3(a)および(b)参照)。ここでは可変インダクタについて示し、他の素子領域については省略する。

可変インダクタ1は、図5に示すように、半導体基板としてのシリコン基板4表面に形成されたスパイラルインダクタ2と、スパイラルインダクタ2に対して垂直方向に形成された2つのループ導体すなわち第1及び第2のループ導体5a、5bと、第1及び第2のスイッチ7a,7bとを用いて構成される。

第1及び第2のループ導体5a、5bは、スパイラルインダクタ2の最外周の相対向する2辺2o1,2o2に沿って形成される。それぞれのループ導体は前記実施の形態1のループ導体5と同様である。可変インダクタ1は、相対向して同様のループ導体が一つ追加されている。

可変インダクタ1は、各ループ導体は同様に形成され、それぞれスイッチを用いて構成され、第1及び第2のスイッチ7a、7bにより第1及び第2のループ導体5a、5bの一端を開放/短絡することによって、スパイラルインダクタ2のインダクタンス値を変更可能とした。

その他の構成は実施の形態1の可変インダクタと同様であるためここでは説明を省略する。同一部位には同一符号を付した。

【0040】

以下、可変インダクタの動作について説明する。基本的な動作は実施の形態1において説明したとおりであるため省略する。可変インダクタは、第1および第2のループ導体5a、5bを設け、第1および第2のスイッチ7a、7bをON/OFFさせて第1および第2のループ導体5a、5bを構成する内層導体6の一端を開放/短絡する。これにより、可変インダクタは、第1および第2のループ導体5a、5bに流れる誘起電流を調整でき、スパイラルインダクタ2のインダクタンス値を変更できる。

【0041】

すなわち、スパイラルインダクタ2に対して、第1のループ導体5aと第2のループ導体5bを設け、第1のスイッチ7aと第2のスイッチ7bを同時にONすれば、第1のループ導体5aと第2のループ導体5bのいずれにも誘起電流が生じる。その結果、スパイラルインダクタ2のインダクタンス値を大きく変えることができる。

【0042】

この構成においても、図5(a)および図5(b)に示すように、第1のループ導体5a及び第2のループ導体5bをそれぞれスパイラルインダクタ2の下部に垂直方向に形成できるため、可変インダクタ1の半導体基板の一表面における占有面積を大きくすることなく、インダクタンス値の可変幅を大きくできる。

【0043】

本発明の実施の形態によれば、半導体集積回路装置は、スパイラルインダクタ2の下部に、スパイラルインダクタ2に対して垂直方向に第1のループ導体5aおよび第2のループ導体5bを形成し、第1のループ導体5aを構成する内層導体6の一部を第1のスイッチ7aのON/OFFによって開放/短絡し、第2のループ導体5bを構成する内層導体6の一部を第2のスイッチ7bのON/OFFによって開放/短絡を制御するため、第1のループ導体5a及び第2のループ導体5bにおいて発生する誘起電流を調整でき、結果的に可変インダクタ1の占有面積を小型化しながらインダクタンス値を大きく調整できる。

【0044】

第1及び第2のループ導体5a及び5bをスパイラルインダクタ2下部に配置する場合に、配置する場所によってスパイラルインダクタ2の磁束の影響が変わるため、可変インダクタ1のインダクタンス値調整量に合わせて、第1及び第2のループ導体5a及び5bの配置位置を決定できる。例えば、第1及び第2のループ導体5a及び5bを、スパイラルインダクタ2を構成する導体パターン(ライン)直下または導体パターン直下より内側に形成することによって、可変インダクタ1の占有面積を大きくすることなく、インダクタンス値を調整できる。

【0045】

なお、本実施の形態では、第1及び第2のループ導体5a及び5bを開放/短絡するために第1及び第2のスイッチ7a及び7bを用いているが、例えばスイッチに代えて、抵抗を並列化した可変抵抗として、抵抗値の調整によって、第1及び第2のループ導体5a及び5bに流れる誘起電流を調整しても良い。このため、可変インダクタ1のインダクタンス値を精度良く調整できる。

【0046】

(実施の形態3)

次に、本発明の実施の形態3について図面を参照しつつ説明する。図6は実施の形態3に係る可変インダクタの概略構成図である。

可変インダクタ1は、実施の形態1と同様、トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する(図3(a)および(b)参照)。図6では、可変インダクタについて示し、他の素子領域については省略する。

可変インダクタ1は、図6に示すように、半導体基板としてのシリコン基板4表面に形成されたスパイラルインダクタ2と、スパイラルインダクタ2に対して垂直方向に形成された4つのループ導体、すなわち第1乃至第4のループ導体5a乃至5dと、第1乃至第4のスイッチ7a乃至7dとを用いて構成される。

第1及び第2のループ導体5a、5bは、スパイラルインダクタ2の最外周の相対向する2辺2o1,2o2に沿って形成される。また第3及び第4のループ導体5c、5dは、スパイラルインダクタ2の最外周の相対向するもう1組の2辺2o3,2o4に沿って形成される。

それぞれのループ導体は前記実施の形態1のループ導体5と同様であり、相対向して同様のループ導体が一つ追加された可変インダクタ1である。各ループ導体は、同じ形状であり、それぞれにスイッチ7を含む構成である。第1乃至第4のスイッチ7a、7b、7c、7dが、第1乃至第4のループ導体5a、5b、5c、5dの一端を開放/短絡することによって、スパイラルインダクタ2のインダクタンス値を変更可能とした。

その他の構成は実施の形態1および2の可変インダクタと同様であるためここでは説明を省略する。同一部位には同一符号を付した。

【0047】

図6に示すように、スパイラルインダクタ2の下部の最外周の4辺2o1,2o2,2o3,2o4に沿って形成される。4方向に対して、垂直方向にループ導体が形成されるよう、第1乃至第4のループ導体5a、5b、5c、5dを設け、それぞれ第1乃至第4のスイッチ7a、7b、7c、7dによりON/OFFするため、4つのループ導体に流れる誘起電流を調整できるため、インダクタンス値をより大きく調整できる。

なお、本実施の形態の構成では、第1乃至第4のループ導体5a、5b、5c、5dをスパイラルインダクタ2の最外周の相対向する2組の辺2o1,2o2、2o3,2o4の幅になるべく等しく形成するのが望ましい。これは磁束の漏れを防ぐためであり、この構成によれば、相互インダクタンスを最大限に大きく出来、インダクタンスの調整範囲を大きく出来る。

【0048】

また、本実施の形態において説明した可変インダクタを高周波回路の整合回路に用いることにより、整合回路の整合状態をさらに大きな範囲において調整でき、広い周波数帯において整合を調整できる。

【0049】

(実施の形態4)

次に、本発明の実施の形態4について図面を参照しつつ説明する。

図7は実施の形態4に係る可変インダクタのループ導体を示す斜視図、図8(a)は上面図、図8(b)は図8(a)のA−A断面図である。

前記実施の形態1乃至3ではループ導体は、巻き数1回であったが、本実施の形態では、巻き数を3回にした。

この構成においても、各ループは前記実施の形態1乃至3と同様に、内層導体6としての平行な3本のアルミニウム層パターンと、裏面導体9としての平行な3本のアルミニウム層パターンと、平行な6本の垂直導体8と、を含む構成であり、ループ導体もスパイラル状のループを構成している。

内層導体6としての平行な3本のアルミニウム層パターンは、スパイラルインダクタ2を構成する表面導体に対し、層間絶縁膜3を介して下層側に配置される。裏面導体9としての平行な3本のアルミニウム層パターンは、シリコン基板4の裏面に形成される。平行な6本の垂直導体8は、シリコン基板4を貫通する貫通ビア内に形成される。

そしてループ導体の一端を開放/短絡するためのスイッチ(図示せず)が設けられている。

【0050】

その他の構成は実施の形態1および2の可変インダクタと同様であるためここでは説明を省略する。同一部位には同一符号を付した。

【0051】

可変インダクタ1についても、占有面積の増大を招くことなく、前記実施の形態1と同様トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成するが、より、効率よく調整が可能となり、整合回路の整合状態をさらに大きな範囲において調整でき、広い周波数帯において整合を調整できる。

【0052】

(実施の形態5)

次に、本発明の実施の形態5について図面を参照しつつ説明する。

図9は実施の形態5に係る可変インダクタを示す斜視図、図10(a)は可変インダクタのスパイラルインダクタ2の上面図、図10(b)はループ導体5の上面図、図10(c)は、(a)のA−A断面図である。

前記実施の形態1乃至4ではループ導体は、基板表面に対して垂直に配されたが、本実施の形態の可変インダクタは、スパイラルインダクタ2に沿って層間絶縁膜3を介して平行にループ導体15を設けた。

【0053】

ループ導体15は、スパイラルインダクタ2と同様のパターンを用いて構成され、層間絶縁膜3を介して平行に形成されている。したがって磁束の漏れはほとんどなく、しかもループ導体15と、スパイラルインダクタ2との相互の距離は近接しているため相互インダクタンスを大きくできる。したがってインダクタンスの調整範囲を最大限に大きく出来る。

【0054】

この構成においては、ループ導体15は、スパイラルインダクタ2を構成する表面導体に対し、層間絶縁膜3を介して平行に、下層側に配置された内層導体6としてのスパイラル上のアルミニウム層パターン6sを用いて構成されている。

【0055】

この構成によれば、ループ導体15は、ループを形成するためにビア18によって内層導体6のアルミニウム層パターン6sを接続する以外は、平面パターンを用いて構成されるため、製造がさらに容易となる。なおループ導体は1周のループであってもよい。

【0056】

その他の構成は実施の形態1乃至4の可変インダクタと同じであるためここでは説明を省略する。同一部位には同一符号を付した。

【0057】

可変インダクタ1についても、占有面積の増大を招くことなく、前記実施の形態1と同様トランジスタ20又はキャパシタ21を含むCMOS半導体素子の搭載された半導体集積回路基板(シリコン基板4)上に搭載されて半導体集積回路装置100を構成する。

このため、より効率よく調整でき、整合回路の整合状態をさらに大きな範囲において調整できる。従って、広い周波数帯にわたって整合を調整できる。

【0058】

(変形例1)

また、図11(a)および(b)に図10の変形例としてループ導体の上面図および断面図を示すように、同心体を構成するように複数周、例えば3周のループを持つループ導体を用いて構成しても良い。この構成によればパターン形成が1つの層により完了するため、製造が容易である。1周ごとに閉ループを形成してもよいが、1周ごとに閉ループを形成するパターン長は少なくてすむが、スイッチ7を1ループ毎に形成する必要がある。図11(b)は図11(a)のA−A断面図である。

【0059】

(変形例2)

さらにまた、図12(a)および(b)に図11(a)および(b)に示した同心体を構成する複数周のループを持つループ導体を構成した例の変形例としてループ導体の上面図および断面図を示すように、2層構造を用いて2周のループ導体25を形成してもよい。

そしてループ導体の一端を開放/短絡するためのスイッチ7が設けられている。

【0060】

なお、上述した実施の形態では、ループ導体としては、アルミニウムおよび金を用いたが、他の金属導体でもよく、表面導体あるいは裏面導体と、貫通ビアなどのビア内側に形成される導体とは別の導体材料を用いてもよい。

【0061】

また、前記実施の形態では、シリコンデバイスを構成するシリコン基板に可変インダクタンスを集積化して形成した例について説明したが、シリコン基板以外にも、HEMT又はHBTを含む化合物半導体デバイス、GaAsデバイス、InPデバイス、又はGaNデバイスにも集積化可能である。化合物半導体デバイスでは、アルミニウム又は金以外にも、仕事関数を含む所定の条件を満たす導体材料を用いればよく、単層金属あるいは多層金属を用いてもよい。

【産業上の利用可能性】

【0062】

本発明に係る可変インダクタは、例えばシリコン基板を貫通する貫通ビアを含むビアを用いたループ導体をスパイラルインダクタの下部に垂直方向に形成し、ループ導体の一部をスイッチを用いて開放/短絡してループ導体に流れる誘起電流を調整することによって、インダクタンス値を可変に出来るという有利な効果を有するため、ミリ波帯の整合回路のように、容量が小さく、調整が難しい整合回路における可変インダクタとして有効である。

本発明の可変インダクタは、CMOSデバイスを含むシリコンデバイス、HEMT又はHBTを含む化合物半導体デバイス、GaAsデバイス、InPデバイス又はGaNデバイスにも集積化可能である。

【符号の説明】

【0063】

1 可変インダクタ

2 スパイラルインダクタ

3 層間絶縁膜

4 シリコン基板

5,5s、15,25 ループ導体

5a 第1のループ導体

5b 第2のループ導体

5c 第3のループ導体

5d 第4のループ導体

6 内層導体

7 スイッチ

7G ゲート電極

7S ソース領域

7D ドレイン領域

7a 第1のスイッチ

7b 第2のスイッチ

7c 第3のスイッチ

7d 第4のスイッチ

8 垂直導体

8v 貫通ビア

9 裏面導体

18 ビア

20 トランジスタ

21 キャパシタ

100 半導体集積回路装置

101 インダクタンス可変素子

102 スパイラル電極

103、104 入出力電極

105、106 スイッチ

107、108 ゲート電極

109、110、111 拡散領域

112 絶縁層

113 Si基板

201 スパイラルコイル

202 スパイラルコイルの第1層

203 スパイラルコイルの第2層

204 制御回路

205 スイッチ

206 シリコン基板

207 周囲配線

208 周囲配線の第1層

209 周囲配線の第2層

【特許請求の範囲】

【請求項1】

半導体基板上に形成された、スパイラルインダクタと、ループ導体と、前記ループ導体の一端を開放/短絡するスイッチと、を含む可変インダクタであって、

前記ループ導体は前記スパイラルインダクタの下層に配置され、

前記スイッチを用いて前記ループ導体の一端を開放/短絡することによって、前記スパイラルインダクタのインダクタンス値を変更する可変インダクタ。

【請求項2】

請求項1に記載の可変インダクタであって、

前記ループ導体は前記スパイラルインダクタに対して垂直方向に形成された可変インダクタ。

【請求項3】

請求項2に記載の可変インダクタであって、

前記スパイラルインダクタは前記半導体基板の一表面に形成されており、

前記ループ導体は、

前記スパイラルインダクタより下層に形成された第1層導体と、

前記第1層導体よりも下層に形成された第2層導体と

前記半導体基板の少なくとも一部を、前記表面に垂直な方向に形成されたビア内に形成され、前記第1及び第2層導体間を接続する垂直導体と、

前記ループ導体の一端を開放/短絡するためのスイッチと、

を含む可変インダクタ。

【請求項4】

請求項3に記載の可変インダクタであって、

前記半導体基板はシリコン基板であり、

前記スパイラルインダクタは、前記シリコン基板の最表層に形成された表面導体において構成され、

前記第1の導体は、前記表面導体に対し、層間絶縁膜を介して下層側に配置された内層導体であり、

前記第2の導体は、前記シリコン基板の裏面に形成された裏面導体であり、

前記ループ導体は、

前記内層導体と、

前記シリコン基板を貫通する貫通ビア内に形成された垂直導体と、

前記裏面導体と、

前記ループ導体の一端を開放/短絡するためのスイッチと、

を含む可変インダクタ。

【請求項5】

請求項1乃至4のいずれか1項に記載の可変インダクタであって、

前記ループ導体は、前記スパイラルインダクタを構成する最外周ラインにより囲まれた領域下、あるいは内側に配置される可変インダクタ。

【請求項6】

請求項1乃至5のいずれか1項に記載の可変インダクタであって、

前記スイッチは、前記ループ導体の一端に接続された可変抵抗を含み、前記可変抵抗の抵抗値を調整することにより、スパイラルインダクタのインダクタンス値を調整する可変インダクタ。

【請求項7】

請求項1乃至6のいずれか1項に記載の可変インダクタであって、

前記スパイラルインダクタの下部に、前記ループ導体が複数設けられた可変インダクタ。

【請求項8】

請求項1乃至7のいずれか1項に記載の可変インダクタであって、

前記ループ導体は、前記スパイラルインダクタの形成された前記半導体基板の表面に垂直な方向において複数回巻回されたスパイラル状であり、

前記スイッチは、前記ループ導体の一端を開放/短絡することによって、前記ループ導体の巻数が変更する可変インダクタ。

【請求項9】

請求項1乃至8のいずれか1項に記載の可変インダクタを含む半導体装置。

【請求項1】

半導体基板上に形成された、スパイラルインダクタと、ループ導体と、前記ループ導体の一端を開放/短絡するスイッチと、を含む可変インダクタであって、

前記ループ導体は前記スパイラルインダクタの下層に配置され、

前記スイッチを用いて前記ループ導体の一端を開放/短絡することによって、前記スパイラルインダクタのインダクタンス値を変更する可変インダクタ。

【請求項2】

請求項1に記載の可変インダクタであって、

前記ループ導体は前記スパイラルインダクタに対して垂直方向に形成された可変インダクタ。

【請求項3】

請求項2に記載の可変インダクタであって、

前記スパイラルインダクタは前記半導体基板の一表面に形成されており、

前記ループ導体は、

前記スパイラルインダクタより下層に形成された第1層導体と、

前記第1層導体よりも下層に形成された第2層導体と

前記半導体基板の少なくとも一部を、前記表面に垂直な方向に形成されたビア内に形成され、前記第1及び第2層導体間を接続する垂直導体と、

前記ループ導体の一端を開放/短絡するためのスイッチと、

を含む可変インダクタ。

【請求項4】

請求項3に記載の可変インダクタであって、

前記半導体基板はシリコン基板であり、

前記スパイラルインダクタは、前記シリコン基板の最表層に形成された表面導体において構成され、

前記第1の導体は、前記表面導体に対し、層間絶縁膜を介して下層側に配置された内層導体であり、

前記第2の導体は、前記シリコン基板の裏面に形成された裏面導体であり、

前記ループ導体は、

前記内層導体と、

前記シリコン基板を貫通する貫通ビア内に形成された垂直導体と、

前記裏面導体と、

前記ループ導体の一端を開放/短絡するためのスイッチと、

を含む可変インダクタ。

【請求項5】

請求項1乃至4のいずれか1項に記載の可変インダクタであって、

前記ループ導体は、前記スパイラルインダクタを構成する最外周ラインにより囲まれた領域下、あるいは内側に配置される可変インダクタ。

【請求項6】

請求項1乃至5のいずれか1項に記載の可変インダクタであって、

前記スイッチは、前記ループ導体の一端に接続された可変抵抗を含み、前記可変抵抗の抵抗値を調整することにより、スパイラルインダクタのインダクタンス値を調整する可変インダクタ。

【請求項7】

請求項1乃至6のいずれか1項に記載の可変インダクタであって、

前記スパイラルインダクタの下部に、前記ループ導体が複数設けられた可変インダクタ。

【請求項8】

請求項1乃至7のいずれか1項に記載の可変インダクタであって、

前記ループ導体は、前記スパイラルインダクタの形成された前記半導体基板の表面に垂直な方向において複数回巻回されたスパイラル状であり、

前記スイッチは、前記ループ導体の一端を開放/短絡することによって、前記ループ導体の巻数が変更する可変インダクタ。

【請求項9】

請求項1乃至8のいずれか1項に記載の可変インダクタを含む半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−209405(P2012−209405A)

【公開日】平成24年10月25日(2012.10.25)

【国際特許分類】

【出願番号】特願2011−73445(P2011−73445)

【出願日】平成23年3月29日(2011.3.29)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度、総務省、超高速近距離無線伝送技術等の研究開発の委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年10月25日(2012.10.25)

【国際特許分類】

【出願日】平成23年3月29日(2011.3.29)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度、総務省、超高速近距離無線伝送技術等の研究開発の委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]