可変容量回路及びこれを備える発振回路

【課題】リーク電流を少なくできる可変容量回路及びこれを備える発振回路を提供する。

【解決手段】オフ時のNMOSトランジスタ12において、ソース電圧がPMOSトランジスタ11によって電源電圧VDDになるので、基板バイアス効果によってNMOSトランジスタ12の閾値電圧が高くなる。よって、オフ時のNMOSトランジスタ12のリーク電流が流れにくくなり、可変容量回路30のリーク電流が少なくなる。NMOSトランジスタ22も同様である。

【解決手段】オフ時のNMOSトランジスタ12において、ソース電圧がPMOSトランジスタ11によって電源電圧VDDになるので、基板バイアス効果によってNMOSトランジスタ12の閾値電圧が高くなる。よって、オフ時のNMOSトランジスタ12のリーク電流が流れにくくなり、可変容量回路30のリーク電流が少なくなる。NMOSトランジスタ22も同様である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、可変容量回路及びこれを備える発振回路に関する。

【背景技術】

【0002】

従来の可変容量回路について説明する。図4は、可変容量回路を示す図である。

容量回路40において、制御端子の電圧(電圧Vc1)がハイレベルに制御されると、NMOSトランジスタ42はオンするので、容量43の一端は出力端子に接続される。よって、容量43の容量値はCであるので、容量回路40の容量値はCになる。また、制御端子の電圧(電圧Vc1)がローレベルに制御されると、NMOSトランジスタ42はオフするので、容量43の一端は出力端子に接続されない。なお、容量回路50の動作も同様である。

【0003】

可変容量回路60において、電圧Vc1はハイレベルに制御され、電圧Vc2はローレベルに制御される。すると、容量43の一端は出力端子に接続され、容量53の一端は出力端子に接続されない。よって、容量43の容量値はCであるので、可変容量回路60の容量値はCになる。また、電圧Vc1がハイレベルに制御され、電圧Vc2もハイレベルに制御される。すると、容量43の一端は出力端子に接続され、容量53の一端も出力端子に接続される。よって、容量43の容量値はCであり、容量53の容量値もCであるので、可変容量回路60の容量値は2Cになる(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−051238号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、従来の技術では、オフ時のNMOSトランジスタ42及びNMOSトランジスタ52がリーク電流を流してしまう。つまり、可変容量回路60はリーク電流を流してしまう。

【0006】

例えば、可変容量回路60の出力端子に定電流源が設けられ、定電流源が可変容量回路60に定電流を供給し、可変容量回路60は定電流及び自らの容量値によって出力電圧Voutを生成するとする。この時、容量回路40がオンし、容量回路50がオフしているとする。すると、容量回路50はオフしていてもリーク電流を流してしまうので、このリーク電流の分、容量回路40に正確な定電流が流れなくなってしまう。よって、可変容量回路60の出力電圧Voutが不正確になってしまう。

【0007】

本発明は、上記課題に鑑みてなされ、リーク電流を少なくできる可変容量回路及びこれを備える発振回路を提供する。

【課題を解決するための手段】

【0008】

本発明は、上記課題を解決するため、可変容量回路において、ゲートは制御端子に接続され、ソース及びバックゲートは第一電源端子に接続される第一導電型MOSトランジスタと、ゲートは前記制御端子に接続され、ドレインは出力端子に接続され、バックゲートは第二電源端子に接続される第二導電型MOSトランジスタと、前記第一導電型MOSトランジスタのドレインと前記第二導電型MOSトランジスタのソースとの接続点と、第二電源端子との間に、設けられる容量と、を備える複数の容量回路と、各前記容量回路の出力端子を接続される可変容量回路の出力端子と、を備えることを特徴とする可変容量回路を提供する。

【発明の効果】

【0009】

本発明では、オフ時の第二導電型MOSトランジスタにおいて、ソース電圧が第一導電型MOSトランジスタによって第一電源端子の電圧になるので、基板バイアス効果によって第二導電型MOSトランジスタの閾値電圧が高くなる。よって、オフ時の第二導電型MOSトランジスタのリーク電流が流れにくくなり、可変容量回路のリーク電流が少なくなる。

【図面の簡単な説明】

【0010】

【図1】可変容量回路を示す図である。

【図2】発振回路を示す図である。

【図3】発振回路を示す図である。

【図4】従来の可変容量回路を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態を、図面を参照して説明する。

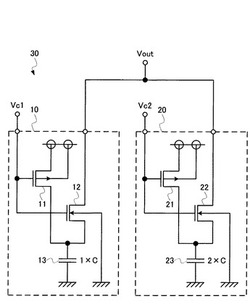

まず、可変容量回路の構成について説明する。図1は、可変容量回路を示す図である。

可変容量回路30は、容量回路10及び容量回路20を備える。また、可変容量回路30は、第一〜第二制御端子及び出力端子を備える。容量回路10は、PMOSトランジスタ11、NMOSトランジスタ12、及び、容量13を備える。また、容量回路10は、制御端子及び出力端子を備える。容量回路20は、PMOSトランジスタ21、NMOSトランジスタ22、及び、容量23を備える。また、容量回路20は、制御端子及び出力端子を備える。

【0012】

容量回路10の制御端子は、可変容量回路30の第一制御端子に接続され、出力端子は、可変容量回路30の出力端子に接続される。容量回路20の制御端子は、可変容量回路30の第二制御端子に接続され、出力端子は、可変容量回路30の出力端子に接続される。

【0013】

容量回路10において、PMOSトランジスタ11のゲートは、制御端子に接続され、ソース及びバックゲートは、電源端子に接続される。NMOSトランジスタ12のゲートは、制御端子に接続され、ドレインは、出力端子に接続され、バックゲートは、接地端子に接続される。容量13は、PMOSトランジスタ11のドレインとNMOSトランジスタ12のソースとの接続点と、接地端子との間に、設けられる。

【0014】

容量回路20において、PMOSトランジスタ21のゲートは、制御端子に接続され、ソース及びバックゲートは、電源端子に接続される。NMOSトランジスタ22のゲートは、制御端子に接続され、ドレインは、出力端子に接続され、バックゲートは、接地端子に接続される。容量23は、PMOSトランジスタ21のドレインとNMOSトランジスタ22のソースとの接続点と、接地端子との間に、設けられる。

【0015】

次に、容量回路10の動作について説明する。

容量回路10の制御端子の電圧(電圧Vc1)がハイレベルに制御される。すると、PMOSトランジスタ11はオフし、NMOSトランジスタ12はオンする。出力端子と容量13との間のNMOSトランジスタ12がオンするので、容量13の一端は出力端子に接続される。よって、容量13の容量値はCであるので、容量回路10の容量値はCになる。

【0016】

容量回路10の制御端子の電圧(電圧Vc1)がローレベルに制御される。すると、PMOSトランジスタ11はオンし、NMOSトランジスタ12はオフする。出力端子と容量13との間のNMOSトランジスタ12がオフするので、容量13の一端は出力端子に接続されない。ここで、PMOSトランジスタ11はオンするので、NMOSトランジスタ12のソース電圧は電源電圧VDDになり、基板バイアス効果によってNMOSトランジスタ12の閾値電圧が高くなる。すると、オフ時のNMOSトランジスタ12のリーク電流が流れにくくなる。

【0017】

なお、容量回路20の動作も同様であり、容量回路20のオン時、容量23の容量値は2Cであるので、容量回路20の容量値は2Cになる。

【0018】

次に、可変容量回路30の動作について説明する。

電圧Vc1はハイレベルに制御され、電圧Vc2はローレベルに制御される。すると、容量13の一端は出力端子に接続され、容量23の一端は出力端子に接続されない。よって、容量13の容量値はCであるので、可変容量回路30の容量値はCになる。

【0019】

電圧Vc1はローレベルに制御され、電圧Vc2はハイレベルに制御される。すると、容量13の一端は出力端子に接続されず、容量23の一端は出力端子に接続される。よって、容量23の容量値は2Cであるので、可変容量回路30の容量値は2Cになる。

【0020】

電圧Vc1はハイレベルに制御され、電圧Vc2もハイレベルに制御される。すると、容量13の一端は出力端子に接続され、容量23の一端も出力端子に接続される。よって、容量13の容量値はCであり、容量23の容量値は2Cであるので、可変容量回路30の容量値は3Cになる。

【0021】

このようにすると、オフ時のNMOSトランジスタ12において、ソース電圧がPMOSトランジスタ11によって電源電圧VDDになるので、基板バイアス効果によってNMOSトランジスタ12の閾値電圧が高くなる。よって、オフ時のNMOSトランジスタ12のリーク電流が流れにくくなり、可変容量回路30のリーク電流が少なくなる。NMOSトランジスタ22も同様である。

【0022】

なお、図1では、容量は接地端子に設けられているが、図示しないが、電源端子に設けられても良い。この時、容量と出力端子との間にPMOSトランジスタが設けられる。また、容量とそのPMOSトランジスタとの接続点と、接地端子との間に、NMOSトランジスタが設けられる。

【0023】

また、図1では、2つの容量回路が設けられているが、図示しないが、3つ以上の容量回路が適宜設けられても良い。

【0024】

また、複数の容量回路が設けられる場合、各容量回路の容量の容量値はC、2C、3C、・・・・、と単位容量値ごとに異なる容量値でも良い。また、C、2C、4C、・・・・、と2進数的に異なる容量値でも良い。また、任意に異なる容量値でも良い。また、同一の容量値でも良い。

【0025】

また、NMOSトランジスタ12及びNMOSトランジスタ22は、オフのときにPMOSトランジスタ11及びPMOSトランジスタ21がソースに電源電圧VDDを供給するので、基板バイアス効果によりオフ時の閾値電圧が高くなる。すなわち、NMOSトランジスタ12及びNMOSトランジスタ22の閾値電圧を通常のNMOSトランジスタの閾値電圧よりも低く設計しても、オフ時のリーク電流は増加しない。従って、可変容量回路30は、NMOSトランジスタ12及びNMOSトランジスタ22の閾値電圧を低く設計することにより、低電圧動作が可能となる、という効果もある。

【0026】

次に、本発明の可変容量回路を発振回路へ適用した例について説明する。

例えば、可変容量回路30は、図2に示すような発振回路に適用されても良い。

ここで、ローレベルの電圧V3が出力されている。NMOSトランジスタ75はオフしていて、1つの目の可変容量回路30の容量が電流源76からの定電流の供給によって充電され、定電流及び1つの目の可変容量回路30の容量値に基づき、電圧V1が徐々に高くなる。電圧V1(1つの目の容量可変回路30の出力電圧)がNMOSトランジスタ71の閾値電圧以上になると、NMOSトランジスタ71はオンする。よって、電流源77及びNMOSトランジスタ71で構成されるインバータの出力電圧はローレベルになり、インバータ72の入力電圧はローレベルになり、出力電圧はハイレベルになる。NMOSトランジスタ73はオンし、電圧V2はローレベルになる。NMOSトランジスタ74はオフし、電圧V3はハイレベルになる。つまり、ローレベルの電圧V3の出力期間が終了する。

【0027】

その後、ハイレベルの電圧V3が出力される。NMOSトランジスタ75はオンし、電圧V1はローレベルになる。つまり、定電流の供給の開始時から所定時間が経過すると、NMOSトランジスタ75はオンして可変容量回路30への電流供給を停止する。NMOSトランジスタ71がオフし、インバータ72の入力電圧はハイレベルになり、出力電圧はローレベルになる。NMOSトランジスタ73はオフし、2つの目の可変容量回路30の容量が電流源78からの定電流の供給によって充電され、定電流及び2つの目の可変容量回路30の容量値に基づき、電圧V2が徐々に高くなる。電圧V2(2つの目の容量可変回路30の出力電圧)がNMOSトランジスタ74の閾値電圧以上になると、NMOSトランジスタ74はオンする。よって、電流源79及びNMOSトランジスタ74で構成されるインバータの出力電圧はローレベルになり、電圧V3はローレベルになる。つまり、ハイレベルの電圧V3の出力期間が終了する。

【0028】

このように、電圧V3は、定電流及び可変容量回路30の容量値に基づき、ハイレベルになったりローレベルになったりして発振する。この時、可変容量回路30の容量値が可変されることにより、可変容量回路30の充放電時間が微調整されたり変更されたりし、電圧V3の発振周波数が微調整されたり変更されたりすることができる。

【0029】

また、可変容量回路30は、図3に示すような発振回路に適用されても良い。

ここで、発振回路は、増幅器81、増幅器81に並列接続する抵抗82及び圧電素子83、増幅器81の入力端子に設けられる入力側の可変容量回路30、及び、増幅器81の出力端子に設けられる出力側の可変容量回路30を備える。

【0030】

増幅器81は、電圧V1を電圧V2に増幅する。抵抗82及び圧電素子83は、増幅器81の帰還ループを形成し、電圧V1〜V2を発振させる。入力側及び出力側の可変容量回路30は、容量値を可変されることにより、充放電時間を微調整され、発振回路の発振周波数を微調整することができる。

【符号の説明】

【0031】

30 可変容量回路

10、20 容量回路

11、21 PMOSトランジスタ

12、22 NMOSトランジスタ

13、23 容量

【技術分野】

【0001】

本発明は、可変容量回路及びこれを備える発振回路に関する。

【背景技術】

【0002】

従来の可変容量回路について説明する。図4は、可変容量回路を示す図である。

容量回路40において、制御端子の電圧(電圧Vc1)がハイレベルに制御されると、NMOSトランジスタ42はオンするので、容量43の一端は出力端子に接続される。よって、容量43の容量値はCであるので、容量回路40の容量値はCになる。また、制御端子の電圧(電圧Vc1)がローレベルに制御されると、NMOSトランジスタ42はオフするので、容量43の一端は出力端子に接続されない。なお、容量回路50の動作も同様である。

【0003】

可変容量回路60において、電圧Vc1はハイレベルに制御され、電圧Vc2はローレベルに制御される。すると、容量43の一端は出力端子に接続され、容量53の一端は出力端子に接続されない。よって、容量43の容量値はCであるので、可変容量回路60の容量値はCになる。また、電圧Vc1がハイレベルに制御され、電圧Vc2もハイレベルに制御される。すると、容量43の一端は出力端子に接続され、容量53の一端も出力端子に接続される。よって、容量43の容量値はCであり、容量53の容量値もCであるので、可変容量回路60の容量値は2Cになる(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−051238号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、従来の技術では、オフ時のNMOSトランジスタ42及びNMOSトランジスタ52がリーク電流を流してしまう。つまり、可変容量回路60はリーク電流を流してしまう。

【0006】

例えば、可変容量回路60の出力端子に定電流源が設けられ、定電流源が可変容量回路60に定電流を供給し、可変容量回路60は定電流及び自らの容量値によって出力電圧Voutを生成するとする。この時、容量回路40がオンし、容量回路50がオフしているとする。すると、容量回路50はオフしていてもリーク電流を流してしまうので、このリーク電流の分、容量回路40に正確な定電流が流れなくなってしまう。よって、可変容量回路60の出力電圧Voutが不正確になってしまう。

【0007】

本発明は、上記課題に鑑みてなされ、リーク電流を少なくできる可変容量回路及びこれを備える発振回路を提供する。

【課題を解決するための手段】

【0008】

本発明は、上記課題を解決するため、可変容量回路において、ゲートは制御端子に接続され、ソース及びバックゲートは第一電源端子に接続される第一導電型MOSトランジスタと、ゲートは前記制御端子に接続され、ドレインは出力端子に接続され、バックゲートは第二電源端子に接続される第二導電型MOSトランジスタと、前記第一導電型MOSトランジスタのドレインと前記第二導電型MOSトランジスタのソースとの接続点と、第二電源端子との間に、設けられる容量と、を備える複数の容量回路と、各前記容量回路の出力端子を接続される可変容量回路の出力端子と、を備えることを特徴とする可変容量回路を提供する。

【発明の効果】

【0009】

本発明では、オフ時の第二導電型MOSトランジスタにおいて、ソース電圧が第一導電型MOSトランジスタによって第一電源端子の電圧になるので、基板バイアス効果によって第二導電型MOSトランジスタの閾値電圧が高くなる。よって、オフ時の第二導電型MOSトランジスタのリーク電流が流れにくくなり、可変容量回路のリーク電流が少なくなる。

【図面の簡単な説明】

【0010】

【図1】可変容量回路を示す図である。

【図2】発振回路を示す図である。

【図3】発振回路を示す図である。

【図4】従来の可変容量回路を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態を、図面を参照して説明する。

まず、可変容量回路の構成について説明する。図1は、可変容量回路を示す図である。

可変容量回路30は、容量回路10及び容量回路20を備える。また、可変容量回路30は、第一〜第二制御端子及び出力端子を備える。容量回路10は、PMOSトランジスタ11、NMOSトランジスタ12、及び、容量13を備える。また、容量回路10は、制御端子及び出力端子を備える。容量回路20は、PMOSトランジスタ21、NMOSトランジスタ22、及び、容量23を備える。また、容量回路20は、制御端子及び出力端子を備える。

【0012】

容量回路10の制御端子は、可変容量回路30の第一制御端子に接続され、出力端子は、可変容量回路30の出力端子に接続される。容量回路20の制御端子は、可変容量回路30の第二制御端子に接続され、出力端子は、可変容量回路30の出力端子に接続される。

【0013】

容量回路10において、PMOSトランジスタ11のゲートは、制御端子に接続され、ソース及びバックゲートは、電源端子に接続される。NMOSトランジスタ12のゲートは、制御端子に接続され、ドレインは、出力端子に接続され、バックゲートは、接地端子に接続される。容量13は、PMOSトランジスタ11のドレインとNMOSトランジスタ12のソースとの接続点と、接地端子との間に、設けられる。

【0014】

容量回路20において、PMOSトランジスタ21のゲートは、制御端子に接続され、ソース及びバックゲートは、電源端子に接続される。NMOSトランジスタ22のゲートは、制御端子に接続され、ドレインは、出力端子に接続され、バックゲートは、接地端子に接続される。容量23は、PMOSトランジスタ21のドレインとNMOSトランジスタ22のソースとの接続点と、接地端子との間に、設けられる。

【0015】

次に、容量回路10の動作について説明する。

容量回路10の制御端子の電圧(電圧Vc1)がハイレベルに制御される。すると、PMOSトランジスタ11はオフし、NMOSトランジスタ12はオンする。出力端子と容量13との間のNMOSトランジスタ12がオンするので、容量13の一端は出力端子に接続される。よって、容量13の容量値はCであるので、容量回路10の容量値はCになる。

【0016】

容量回路10の制御端子の電圧(電圧Vc1)がローレベルに制御される。すると、PMOSトランジスタ11はオンし、NMOSトランジスタ12はオフする。出力端子と容量13との間のNMOSトランジスタ12がオフするので、容量13の一端は出力端子に接続されない。ここで、PMOSトランジスタ11はオンするので、NMOSトランジスタ12のソース電圧は電源電圧VDDになり、基板バイアス効果によってNMOSトランジスタ12の閾値電圧が高くなる。すると、オフ時のNMOSトランジスタ12のリーク電流が流れにくくなる。

【0017】

なお、容量回路20の動作も同様であり、容量回路20のオン時、容量23の容量値は2Cであるので、容量回路20の容量値は2Cになる。

【0018】

次に、可変容量回路30の動作について説明する。

電圧Vc1はハイレベルに制御され、電圧Vc2はローレベルに制御される。すると、容量13の一端は出力端子に接続され、容量23の一端は出力端子に接続されない。よって、容量13の容量値はCであるので、可変容量回路30の容量値はCになる。

【0019】

電圧Vc1はローレベルに制御され、電圧Vc2はハイレベルに制御される。すると、容量13の一端は出力端子に接続されず、容量23の一端は出力端子に接続される。よって、容量23の容量値は2Cであるので、可変容量回路30の容量値は2Cになる。

【0020】

電圧Vc1はハイレベルに制御され、電圧Vc2もハイレベルに制御される。すると、容量13の一端は出力端子に接続され、容量23の一端も出力端子に接続される。よって、容量13の容量値はCであり、容量23の容量値は2Cであるので、可変容量回路30の容量値は3Cになる。

【0021】

このようにすると、オフ時のNMOSトランジスタ12において、ソース電圧がPMOSトランジスタ11によって電源電圧VDDになるので、基板バイアス効果によってNMOSトランジスタ12の閾値電圧が高くなる。よって、オフ時のNMOSトランジスタ12のリーク電流が流れにくくなり、可変容量回路30のリーク電流が少なくなる。NMOSトランジスタ22も同様である。

【0022】

なお、図1では、容量は接地端子に設けられているが、図示しないが、電源端子に設けられても良い。この時、容量と出力端子との間にPMOSトランジスタが設けられる。また、容量とそのPMOSトランジスタとの接続点と、接地端子との間に、NMOSトランジスタが設けられる。

【0023】

また、図1では、2つの容量回路が設けられているが、図示しないが、3つ以上の容量回路が適宜設けられても良い。

【0024】

また、複数の容量回路が設けられる場合、各容量回路の容量の容量値はC、2C、3C、・・・・、と単位容量値ごとに異なる容量値でも良い。また、C、2C、4C、・・・・、と2進数的に異なる容量値でも良い。また、任意に異なる容量値でも良い。また、同一の容量値でも良い。

【0025】

また、NMOSトランジスタ12及びNMOSトランジスタ22は、オフのときにPMOSトランジスタ11及びPMOSトランジスタ21がソースに電源電圧VDDを供給するので、基板バイアス効果によりオフ時の閾値電圧が高くなる。すなわち、NMOSトランジスタ12及びNMOSトランジスタ22の閾値電圧を通常のNMOSトランジスタの閾値電圧よりも低く設計しても、オフ時のリーク電流は増加しない。従って、可変容量回路30は、NMOSトランジスタ12及びNMOSトランジスタ22の閾値電圧を低く設計することにより、低電圧動作が可能となる、という効果もある。

【0026】

次に、本発明の可変容量回路を発振回路へ適用した例について説明する。

例えば、可変容量回路30は、図2に示すような発振回路に適用されても良い。

ここで、ローレベルの電圧V3が出力されている。NMOSトランジスタ75はオフしていて、1つの目の可変容量回路30の容量が電流源76からの定電流の供給によって充電され、定電流及び1つの目の可変容量回路30の容量値に基づき、電圧V1が徐々に高くなる。電圧V1(1つの目の容量可変回路30の出力電圧)がNMOSトランジスタ71の閾値電圧以上になると、NMOSトランジスタ71はオンする。よって、電流源77及びNMOSトランジスタ71で構成されるインバータの出力電圧はローレベルになり、インバータ72の入力電圧はローレベルになり、出力電圧はハイレベルになる。NMOSトランジスタ73はオンし、電圧V2はローレベルになる。NMOSトランジスタ74はオフし、電圧V3はハイレベルになる。つまり、ローレベルの電圧V3の出力期間が終了する。

【0027】

その後、ハイレベルの電圧V3が出力される。NMOSトランジスタ75はオンし、電圧V1はローレベルになる。つまり、定電流の供給の開始時から所定時間が経過すると、NMOSトランジスタ75はオンして可変容量回路30への電流供給を停止する。NMOSトランジスタ71がオフし、インバータ72の入力電圧はハイレベルになり、出力電圧はローレベルになる。NMOSトランジスタ73はオフし、2つの目の可変容量回路30の容量が電流源78からの定電流の供給によって充電され、定電流及び2つの目の可変容量回路30の容量値に基づき、電圧V2が徐々に高くなる。電圧V2(2つの目の容量可変回路30の出力電圧)がNMOSトランジスタ74の閾値電圧以上になると、NMOSトランジスタ74はオンする。よって、電流源79及びNMOSトランジスタ74で構成されるインバータの出力電圧はローレベルになり、電圧V3はローレベルになる。つまり、ハイレベルの電圧V3の出力期間が終了する。

【0028】

このように、電圧V3は、定電流及び可変容量回路30の容量値に基づき、ハイレベルになったりローレベルになったりして発振する。この時、可変容量回路30の容量値が可変されることにより、可変容量回路30の充放電時間が微調整されたり変更されたりし、電圧V3の発振周波数が微調整されたり変更されたりすることができる。

【0029】

また、可変容量回路30は、図3に示すような発振回路に適用されても良い。

ここで、発振回路は、増幅器81、増幅器81に並列接続する抵抗82及び圧電素子83、増幅器81の入力端子に設けられる入力側の可変容量回路30、及び、増幅器81の出力端子に設けられる出力側の可変容量回路30を備える。

【0030】

増幅器81は、電圧V1を電圧V2に増幅する。抵抗82及び圧電素子83は、増幅器81の帰還ループを形成し、電圧V1〜V2を発振させる。入力側及び出力側の可変容量回路30は、容量値を可変されることにより、充放電時間を微調整され、発振回路の発振周波数を微調整することができる。

【符号の説明】

【0031】

30 可変容量回路

10、20 容量回路

11、21 PMOSトランジスタ

12、22 NMOSトランジスタ

13、23 容量

【特許請求の範囲】

【請求項1】

可変容量回路において、

ゲートは制御端子に接続され、ソース及びバックゲートは第一電源端子に接続される第一導電型MOSトランジスタと、ゲートは前記制御端子に接続され、ドレインは出力端子に接続され、バックゲートは第二電源端子に接続される第二導電型MOSトランジスタと、前記第一導電型MOSトランジスタのドレインと前記第二導電型MOSトランジスタのソースとの接続点と、第二電源端子との間に、設けられる容量と、を備える複数の容量回路と、

各前記容量回路の出力端子を接続される可変容量回路の出力端子と、

を備えることを特徴とする可変容量回路。

【請求項2】

前記第二導電型MOSトランジスタは、通常の第二導電型MOSトランジスタの閾値電圧よりも低い閾値電圧を有することを特徴とする請求項1記載の可変容量回路。

【請求項3】

各前記容量回路の容量は、同一の容量値をそれぞれ有することを特徴とする請求項1または2記載の可変容量回路。

【請求項4】

各前記容量回路の容量は、異なる容量値をそれぞれ有することを特徴とする請求項1または2記載の可変容量回路。

【請求項5】

各前記容量回路の容量は、単位容量値ごとに異なる容量値をそれぞれ有することを特徴とする請求項4記載の可変容量回路。

【請求項6】

各前記容量回路の容量は、2進数的に異なる容量値をそれぞれ有することを特徴とする請求項4記載の可変容量回路。

【請求項7】

各前記容量回路の容量は、任意に異なる容量値をそれぞれ有することを特徴とする請求項4記載の可変容量回路。

【請求項8】

発振回路において、

請求項1から7のいずれかに記載の可変容量回路と、

前記可変容量回路の容量値に基づいた発振周波数で、発振する発振手段と、

を備えることを特徴とする発振回路。

【請求項9】

前記発振手段は、

前記可変容量回路に電流供給を行う電流源と、前記可変容量回路の出力電圧が所定電圧以上になると自らの出力電圧を反転させる第一インバータと、前記電流供給の開始時から所定時間が経過すると、前記電流供給が停止するよう動作するスイッチと、を備える2つの内部回路と、

一の前記内部回路の出力端子と他の前記内部回路の入力端子との間に設けられる第二インバータと、

を備えることを特徴とする請求項8記載の発振回路。

【請求項10】

前記発振手段は、

増幅器と、

前記増幅器に並列接続する抵抗及び圧電素子と、

を備えることを特徴とする請求項8記載の発振回路。

【請求項1】

可変容量回路において、

ゲートは制御端子に接続され、ソース及びバックゲートは第一電源端子に接続される第一導電型MOSトランジスタと、ゲートは前記制御端子に接続され、ドレインは出力端子に接続され、バックゲートは第二電源端子に接続される第二導電型MOSトランジスタと、前記第一導電型MOSトランジスタのドレインと前記第二導電型MOSトランジスタのソースとの接続点と、第二電源端子との間に、設けられる容量と、を備える複数の容量回路と、

各前記容量回路の出力端子を接続される可変容量回路の出力端子と、

を備えることを特徴とする可変容量回路。

【請求項2】

前記第二導電型MOSトランジスタは、通常の第二導電型MOSトランジスタの閾値電圧よりも低い閾値電圧を有することを特徴とする請求項1記載の可変容量回路。

【請求項3】

各前記容量回路の容量は、同一の容量値をそれぞれ有することを特徴とする請求項1または2記載の可変容量回路。

【請求項4】

各前記容量回路の容量は、異なる容量値をそれぞれ有することを特徴とする請求項1または2記載の可変容量回路。

【請求項5】

各前記容量回路の容量は、単位容量値ごとに異なる容量値をそれぞれ有することを特徴とする請求項4記載の可変容量回路。

【請求項6】

各前記容量回路の容量は、2進数的に異なる容量値をそれぞれ有することを特徴とする請求項4記載の可変容量回路。

【請求項7】

各前記容量回路の容量は、任意に異なる容量値をそれぞれ有することを特徴とする請求項4記載の可変容量回路。

【請求項8】

発振回路において、

請求項1から7のいずれかに記載の可変容量回路と、

前記可変容量回路の容量値に基づいた発振周波数で、発振する発振手段と、

を備えることを特徴とする発振回路。

【請求項9】

前記発振手段は、

前記可変容量回路に電流供給を行う電流源と、前記可変容量回路の出力電圧が所定電圧以上になると自らの出力電圧を反転させる第一インバータと、前記電流供給の開始時から所定時間が経過すると、前記電流供給が停止するよう動作するスイッチと、を備える2つの内部回路と、

一の前記内部回路の出力端子と他の前記内部回路の入力端子との間に設けられる第二インバータと、

を備えることを特徴とする請求項8記載の発振回路。

【請求項10】

前記発振手段は、

増幅器と、

前記増幅器に並列接続する抵抗及び圧電素子と、

を備えることを特徴とする請求項8記載の発振回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−188146(P2011−188146A)

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願番号】特願2010−49882(P2010−49882)

【出願日】平成22年3月5日(2010.3.5)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願日】平成22年3月5日(2010.3.5)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

[ Back to top ]