可変容量素子の制御装置

【課題】不良素子を含む複数のMEMS可変容量素子が集積された可変容量システムの歩留まり及び信頼性を向上させる。

【解決手段】可変容量素子の制御装置100は、複数の可変容量素子を含む可変容量システム300の制御を指示する指示手段108と、前記指示手段108の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段102と、前記第1制御手段102によって制御された可変容量素子の容量を検知する容量検知手段104と、前記容量検知手段104によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報124を記憶する記憶手段120と、前記記憶手段120に記憶された不良素子情報124に基づいて、前記可変容量素子を開状態又は閉状態に制御する第2制御手段106と、を備えている。

【解決手段】可変容量素子の制御装置100は、複数の可変容量素子を含む可変容量システム300の制御を指示する指示手段108と、前記指示手段108の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段102と、前記第1制御手段102によって制御された可変容量素子の容量を検知する容量検知手段104と、前記容量検知手段104によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報124を記憶する記憶手段120と、前記記憶手段120に記憶された不良素子情報124に基づいて、前記可変容量素子を開状態又は閉状態に制御する第2制御手段106と、を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、可変容量素子の制御装置に関し、特に、MEMS(Micro-Electro-Mechanical Systems)可変容量素子及び複数のMEMS可変容量素子が集積されたシステムを制御するための可変容量素子の制御装置に関する。

【背景技術】

【0002】

近年のデバイスの微小化技術の進展に伴い、様々な製品にMEMS可変容量素子等の微小なデバイスが用いられている。

【0003】

静電型アクチュエータを利用したMEMS可変容量素子の構造は、例えば、特許文献1に開示されている。MEMS可変容量素子の制御装置は、MEMS可変容量素子を閉状態(MEMS可変容量素子に容量が大きい状態)にするためには、静電型アクチュエータの上部電極と下部電極との間に電位差をかけ、これら電極間の静電引力が、上部電極が固着された梁のばね力を上回るようにする。

【0004】

閉状態のMEMS可変容量素子では、静電型アクチュエータの上部電極と下部電極とが絶縁膜を介して接した状態となる。このとき、FNトンネル又はプール・フレンケル機構により、絶縁膜に電荷が注入され、トラップされる。この現象を、静電型アクチュエータのダイエレクトリック・チャージングという。

【0005】

このとき、ダイエレクトリック・チャージングにより、絶縁膜にたまった電荷量が十分大きくなると、上部電極と下部電極との間の電位差を0Vとしても、絶縁膜中の電荷に上部電極が引き寄せられ、MEMS可変容量素子を閉状態から開状態(MEMS可変容量素子に容量が小さい状態)に制御することができなくなる場合がある。この現象を、ダイエレクトリック・チャージングによるスティクションという。

【0006】

また、絶縁膜に印加される電界の向きと絶縁膜に注入される電荷の符号は、絶縁膜の種類やトラップの場所により異なるので、ダイエレクトリック・チャージングによるスティクションとは逆に、絶縁膜に注入された電荷の影響でMEMS可変容量素子を閉状態に制御することができなくなる場合もある。

【0007】

また、MEMS可変容量素子の製造上のばらつき等又は経年変化による劣化に起因する不良により、MEMS可変容量素子を制御することができなくなる場合もある。

【0008】

ここで、単一のMEMS可変容量素子において、製造上のばらつき等に起因する不良素子(製造時から所望の動作をしない素子)については、不良品としてスクリーニングすることができる。しかし、ダイエレクトリック・チャージングによるスティクション又は経年変化による劣化に起因する不良素子については、スクリーニングすることができないという問題がある。

【0009】

さらに、複数のMEMS可変容量素子が集積された可変容量システムにおいて、集積されたMEMS可変容量素子の1つが不良素子であるために可変容量システム全体を不良品として扱う場合には、可変容量システムの歩留まり及び信頼性が低下するという問題がある。

【0010】

さらに、可変容量システムの製造時のテストによって不良素子を検出する場合には、不良素子の数及び位置を不揮発性メモリに蓄える必要があり、可変容量システムの製造コストが増加するという問題があった。

【特許文献1】米国特許US5578976号

【発明の開示】

【発明が解決しようとする課題】

【0011】

本発明の目的は、不良素子を含む複数のMEMS可変容量素子が集積された可変容量システムの歩留まり及び信頼性を向上させることである。

【課題を解決するための手段】

【0012】

本発明の第1態様によれば、複数の可変容量素子を含む可変容量システムの制御を指示する指示手段と、前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段と、前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を記憶する記憶手段と、前記記憶手段に記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御する第2制御手段と、を備えたことを特徴とする可変容量素子の制御装置が提供される。

【0013】

本発明の第2態様によれば、複数の可変容量素子及び前記複数の可変容量素子に対応するレジスタを有する可変容量システムを制御する可変容量素子の制御装置であって、前記可変容量素子の制御を指示する指示手段と、前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段及び第2制御手段と、前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、を備え、前記第1制御手段は、前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を前記レジスタに記憶し、前記第2制御手段は、前記レジスタに記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御することを特徴とする可変容量素子の制御装置が提供される。

【発明の効果】

【0014】

本発明によれば、不良素子を含む複数のMEMS可変容量素子が集積されたシステムの歩留まり及び信頼性を向上させることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明の実施例について図面を参照して説明する。なお、以下の実施例は、本発明の実施の一形態であって、本発明の範囲を限定するものではない。

【実施例1】

【0016】

はじめに、本発明の実施例1について説明する。本発明の実施例1では、不良素子情報として、不良素子の数を検出する例について説明する。

【0017】

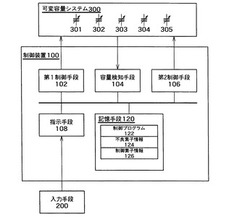

図1は、本発明の実施例1に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【0018】

本発明の実施例1に係る制御装置100は、入力装置200及び可変容量システム300に接続され、第1制御手段102、容量検知手段104、第2制御手段106、指示手段108及び記憶手段120を備えている。入力装置200は、オペレータからの指示を受け付けるハードウェア(例えば、キーボード又はマウス)である。

【0019】

本発明の実施例1に係る可変容量システム300は、複数のMEMS可変容量素子301〜305が集積されたシステムである。MEMS可変容量素子301〜305の数は、複数個であればいくつでも良い。

【0020】

第1制御手段102は、後述する不良素子検出処理において、指示手段108の指示内容に基づいて不良素子を検出するプロセッサである。

【0021】

容量検知手段104は、各MEMS可変容量素子301〜305毎に上部電極と下部電極の間の容量を検知する容量検知センサである。

【0022】

第2制御手段106は、後述する容量制御処理において、指示手段108の指示内容に基づいて、可変容量システム300が所定の容量を示すように制御するプロセッサである。

【0023】

指示手段108は、入力装置200から入力されたテストコマンドに基づいて、第1制御手段102に後述する不良素子検出処理の開始を指示するとともに、第2制御手段106に後述する容量制御処理の開始を指示する。なお、指示手段108は、制御装置100の電源が投入された場合に、同様の処理の開始を指示しても良い。ここで、指示手段108の指示内容は、制御対象となるMEMS可変容量素子301〜305の数又は所望の容量を示す指示情報を含む。

【0024】

記憶手段120は、第1制御手段102及び第2制御手段106のための制御プログラム122、各MEMS可変容量素子301〜305毎の不良を示す不良素子情報124並びに後述する制御素子情報126を記憶する。

【0025】

不良素子情報124は、不良素子の数又は不良素子の位置を記憶する不良素子レジスタに記憶される。

【0026】

次に、本発明の実施例1に係る不良素子検出処理及び容量制御処理について説明する。ここでは、可変容量システム300が常に閉状態(MEMS可変容量素子に容量が大きい状態)にある不良素子のみを含む例を説明する。

【0027】

閉状態の上部電極と下部電極の間の距離は開状態(MEMS可変容量素子に容量が小さい状態)の上部電極と下部電極の間の距離よりも短いので、閉状態の上部電極と下部電極の間の容量は開状態の上部電極と下部電極の間の容量よりも大きくなる。従って、上部電極と下部電極の間の容量を計測することにより、MEMS可変容量素子の状態(開状態又は閉状態)が分かる。

【0028】

可変容量システム300の可変容量素子の総数をy、入力装置200から入力された指示情報(閉状態にする素子の数)をnとすると、y個のうちn個の素子を閉状態にする必要がある。例えば、入力装置200から指示情報としてn=3が与えられたときには、3つのMEMS可変容量素子を閉状態に制御する必要がある。

【0029】

不良素子(常に閉状態である素子)の数をm、閉状態に制御する必要がある制御素子の数をxとすると、x=n−mである。従って、制御素子の数xを求めるためには、不良素子の数mを検出する必要がある。

【0030】

図2は、本発明の実施例1に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0031】

なお、本発明の実施例1に係る不良素子検出処理は、制御装置100の電源が投入されたとき又は入力装置200からテストコマンドが入力されたときに行われる。

【0032】

はじめに、第1制御手段102は、記憶手段120の不良素子情報124をリセットする(S201)。

【0033】

続いて、第1制御手段102は、全てのMEMS可変容量素子301〜305を開状態に制御する(S202)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0034】

続いて、容量検知手段104は、MEMS可変容量素子301〜305のうちの1つの素子の容量を検知する(S203)。

【0035】

続いて、第1制御手段102は、S203の検知結果が「閉状態」を示す場合には(S204−YES)、記憶手段120の不良素子レジスタに記憶された不良素子の数を示す不良素子情報(不良素子数m)124をインクリメントし(S205)、S206へ進む。

【0036】

一方、S203の検知結果が「開状態」を示す場合には(S204−NO)、S206へ進む。

【0037】

S203〜S205は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S206−NO)。

【0038】

全てのMEMS可変容量素子301〜305に対してS203〜S206が行われた場合には(S206−YES)、本発明の実施例1に係る不良素子検出処理が終了する。

【0039】

なお、第1制御手段102は、S202において、全ての素子を閉状態に制御し、S206において、S203の検知結果が「開状態」を示す場合に、常に開状態にある不良素子の数を示す不良素子情報(不良素子数m)124を記憶手段120の不良素子レジスタに記憶しても良い。

【0040】

図3は、本発明の実施例1に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0041】

はじめに、指示手段108は、入力装置200から入力されたオペレータの指示に基づいて、指示情報nを受け付ける(S301)。なお、入力装置200から入力された指示情報が所望の容量である場合には、所望の容量を満たすMEMS可変容量素子301〜305の数をnとする。

【0042】

続いて、第2制御手段106は、全ての素子を開状態に制御する(S302)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0043】

続いて、第2制御手段106は、制御素子数x(=n−m)を算出し、制御素子情報126として記憶手段120に記憶する(S303)。

【0044】

続いて、容量検知手段104は、各MEMS可変容量素子301〜305毎に素子容量を検知する(S304)。

【0045】

続いて、第2制御手段106は、S304の検知結果が「開状態」を示す場合には(S305−YES)、S304において検知された素子を閉状態に制御する(S306)。

【0046】

続いて、第2制御手段106は、制御素子情報(制御素子数x)126をデクリメントし(S307)、S308へ進む。

【0047】

一方、S304の検知結果が「閉状態」を示す場合には(S305−NO)、S308へ進む。

【0048】

S304〜S307は、制御素子情報(制御素子数x)126が0になるまで繰り返される(S308−NO)。

【0049】

制御素子情報(制御素子数x)126が0になった場合には(S308−YES)、本発明の実施例1に係る容量制御処理が終了する。

【0050】

なお、指示手段106は、S301において、可変容量システム300の素子数よりも所定の割合未満の数を指示情報nの上限としても良い。この場合には、指示情報nの上限は、可変容量システム300の歩留まりを考慮して定められる。例えば、可変容量システム300の素子数が5個である場合であって、可変容量システム300の歩留まりが60%である場合には、指示情報nの上限は3となる。

【0051】

また、第2制御手段106は、S302において、全ての素子を閉状態に制御し、S306において、S304の検知結果が「閉状態」を示す場合に、S304において検知された素子を開状態に制御しても良い。

【0052】

本発明の実施例1によれば、可変容量システム300の容量が外部の制御装置100によって制御されるので、プロセスに対する要求が互いに異なる可変容量システム300と他の回路システムとを分離することができ、可変容量システム300の歩留まり及び信頼性を向上させることができる。

【0053】

また、本発明の実施例1によれば、全ての素子を開状態に制御した後で閉状態である素子の数を不良素子情報124として記憶手段120に記憶するので、製造後のダイエレクトリック・チャージングによるスティクション又は経年変化による劣化に起因する不良素子の数を検出することができる。

【0054】

また、本発明の実施例1によれば、不良素子検出処理の検出結果に基づいて容量制御処理を行うので、製造後のダイエレクトリック・チャージングによるスティクション又は経年変化による劣化に起因する不良素子を含む可変容量システム300においても所望の容量に制御することができる。

【0055】

また、本発明の実施例1によれば、不良素子の数及び位置を記憶する不揮発性メモリが必要ないので、製造コストを低減させることができる。

【0056】

また、本発明の実施例1によれば、指示手段106が受付可能な指示情報nの値が可変容量システム300の歩留まりに応じて定められるので、可変容量システム300の全てのMEMS可変容量素子301〜305の正常状態を補償する必要がなく、製造コストを低減することができる。

【実施例2】

【0057】

次に、本発明の実施例2について説明する。本発明の実施例1では、不良素子情報として不良素子の数を検出する例について説明したが、本発明の実施例2では、不良素子情報として不良素子の数及び位置を検出する例について説明する。なお、本発明の実施例1と同様の内容についての説明は省略する。

【0058】

図4は、本発明の実施例2に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0059】

なお、本発明の実施例2に係る不良素子検出処理は、制御装置100の電源が投入されたとき又は入力装置200からテストコマンドが入力されたときに行われる。

【0060】

はじめに、制御装置100は、図2のS201〜S203と同様の処理を行う(S401)。このとき、不良素子は開状態であるが、その他の素子は開状態である。

【0061】

続いて、第1制御手段102は、S401(図2のS203)の検知結果が「閉状態」を示す場合には(S402−YES)、不良素子の位置を示す不良素子情報(位置情報)124を記憶手段120の不良素子レジスタに記憶し(S403)、S404へ進む。例えば、第1制御手段102は、記憶手段120の不良素子レジスタに位置情報を記憶する。ここで、記憶手段120の不良素子レジスタに記憶された位置情報の数は不良素子の数である。

【0062】

一方、S402(図2のS203)の検知結果が「開状態」を示す場合には(S402−NO)、S404へ進む。

【0063】

S401〜S405は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S404−NO)。

【0064】

全てのMEMS可変容量素子301〜305に対してS401〜S405が行われた場合には(S404−YES)、本発明の実施例2に係る不良素子検出処理が終了する。

【0065】

図5は、本発明の実施例2に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0066】

はじめに、制御装置100は、図3のS301及びS302と同様の処理を行う(S501)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0067】

続いて、第2制御手段106は、記憶手段120の不良素子レジスタに記憶された不良素子情報(位置情報)124を参照する(S502)。

【0068】

続いて、第2制御手段106は、S501(図3のS301)の指示情報(n)、S502において参照された不良素子情報(位置情報)124の数(m)及びS502において参照された不良素子情報(位置情報)124に示された素子のうち正常な素子と同じグループに属する素子の数(k)に基づいて制御素子数x(=n−m+k)を算出し、制御素子情報126として記憶手段120に記憶する(S503)。

【0069】

続いて、第2制御手段106は、不良素子情報(位置情報)124に示されない素子のうち、制御素子情報(制御素子数x)126に相当する数の素子を閉状態に制御し(S504)、本発明の実施例2に係る容量制御処理を終了する。

【0070】

本発明の実施例2によれば、常に閉状態である不良素子を含む可変容量システム300においても、実施例1と同様の効果を得ることができる。

【0071】

また、本発明の実施例2によれば、不良素子検出処理において位置情報を参照するので、不良素子の数だけでなく、不良素子の位置を特定することができる。

【0072】

また、本発明の実施例2によれば、容量制御処理において、位置情報を参照し、MEMS可変容量素子301〜305の容量を検知することなく制御するとともに、正常な素子と同じグループに属するk個の不良素子も含めて同時に制御するので、処理時間を短縮することができる。

【実施例3】

【0073】

次に、本発明の実施例3について説明する。本発明の実施例1及び2では、それぞれ、常に閉状態又は開状態にある不良素子を含む可変容量システムを制御する例について説明したが、本発明の実施例3では、常に閉状態にある不良素子及び常に開状態にある不良素子を含む可変容量システムを制御する例について説明する。なお、本発明の実施例1及び2と同様の内容についての説明は省略する。

【0074】

本発明の実施例3に係る制御装置100では、指示手段108は、閉状態への容量制御処理又は開状態への容量制御処理を指示する。

【0075】

記憶手段120は、常に閉状態にある不良素子の数及び位置を記憶する第1レジスタ及び常に開状態にある不良素子の数及び位置を記憶する第2レジスタを備えている。

【0076】

図6は、本発明の実施例3に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0077】

はじめに、制御装置100は、図2のS201〜S203と同様の処理を行う(S601)。このとき、常に閉状態にある不良素子は閉状態であるが、その他の素子は開状態である。

【0078】

続いて、第1制御手段102は、S601(図2のS203)の検知結果が「閉状態」を示す場合には(S602−YES)、常に閉状態にある不良素子の位置を示す不良素子情報(位置情報)124を記憶手段120の第1レジスタに記憶し(S603)、S604へ進む。

【0079】

一方、S601(図2のS203)の検知結果が「開状態」を示す場合には(S602−NO)、S604へ進む。

【0080】

S601〜S603は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S604−NO)。

【0081】

全てのMEMS可変容量素子301〜305に対してS601〜S603が行われた場合には(S604−YES)、第1制御手段102は、全てのMEMS可変容量素子301〜305を閉状態に制御する(S605)。このとき、常に開状態にある不良素子は開状態であるが、その他の素子は閉状態である。

【0082】

続いて、容量検知手段104は、図2のS203と同様の処理を行う(S606)。

【0083】

S606の検知結果が「開状態」を示す場合には(S607−YES)、常に開状態にある不良素子の位置を示す不良素子情報(位置情報)124を記憶手段120の第2レジスタに記憶し(S608)、S609へ進む。

【0084】

一方、S606の検知結果が「閉状態」を示す場合には(S607−NO)、S609へ進む。

【0085】

S606〜S608は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S609−NO)。

【0086】

全てのMEMS可変容量素子301〜305に対してS606〜S608が行われた場合には(S609−YES)、本発明の実施例3に係る不良素子検出処理が終了する。

【0087】

なお、制御装置100は、S601〜S604とS605〜S609を順不同に行っても良い。

【0088】

図7は、本発明の実施例3に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0089】

はじめに、制御装置100は、図3のS301及びS302と同様の処理を行う(S701)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0090】

続いて、第2制御手段106は、記憶手段120の第1レジスタの不良素子情報(位置情報)124を参照する(S702)。

【0091】

続いて、第2制御手段106は、記憶手段120の第2レジスタの不良素子情報(位置情報)124を参照する(S703)。

【0092】

S701(図3のS301)の指示情報が閉状態への容量制御処理(閉状態にする素子の数)を示す場合には(S704−YES)、第2制御手段106は、S701(図3のS301)の指示情報(n)及びS702において参照された記憶手段120の第1レジスタに記憶された不良素子情報(位置情報)124の数(m1)に基づいて制御素子数x(=n−m1)を算出し、制御素子情報(制御素子数x)126として記憶手段120に記憶する(S705)。

【0093】

続いて、第2制御手段106は、記憶手段120の第1レジスタ及び第2レジスタの不良素子情報(位置情報)124に示されない素子のうち、制御素子情報(制御素子数x)に相当する数の素子を閉状態に制御し(S706)、本発明の実施例3に係る容量制御処理を終了する。

【0094】

一方、S701(図3のS301)の指示が開状態への容量制御処理(開状態にする素子の数)を示す場合には(S704−NO)、第2制御手段106は、全ての素子を閉状態に制御する(S707)。このとき、不良素子は開状態であるが、その他の素子は閉状態である。

【0095】

続いて、S701(図3のS301)の指示情報(n)及びS703において参照された記憶手段120の第2レジスタの不良素子情報(位置情報)124の数(m2)に基づいて制御素子数x(=n−m2)を算出し、制御素子情報126として記憶手段120に記憶する(S708)。

【0096】

続いて、第2制御手段106は、記憶手段120の第1レジスタ及び第2レジスタの不良素子情報(位置情報)124に示されない素子のうち、制御素子情報(制御素子数x)に相当する数の素子を開状態に制御し(S709)、本発明の実施例3に係る容量制御処理を終了する。

【0097】

本発明の実施例3によれば、常に閉状態にある不良素子及び常に開状態にある不良素子を含む可変容量システム300においても、実施例1及び2と同様の効果を得ることができる。

【実施例4】

【0098】

次に、本発明の実施例4について説明する。本発明の実施例1〜3では、制御装置内の不良素子情報に基づいて容量制御処理を行う例について説明したが、本発明の実施例4では、可変容量システム内の不良素子情報に基づいて容量制御処理を行う例について説明する。なお、本発明の実施例1〜3と同様の内容についての説明は省略する。

【0099】

図8は、本発明の実施例4に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【0100】

本発明の実施例4に係る可変容量システム300は、複数のMEMS可変容量素子301〜305及び各MEMS可変容量素子301〜305に対応するフラグ・レジスタ311〜315を備える。

【0101】

各フラグ・レジスタ311〜315は、それぞれ、正常な状態であること、常に閉状態であること及び常に開状態であることを示すための2ビットの容量を有する。

【0102】

記憶手段120は、第1制御手段102及び第2制御手段106のための制御プログラム122並びに制御素子情報126を記憶する。

【0103】

図9は、本発明の実施例4に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0104】

はじめに、制御装置100は、図2のS201〜S203と同様の処理を行う(S901)。このとき、常に閉状態にある不良素子は閉状態であるが、その他の素子は開状態である。

【0105】

続いて、第1制御手段102は、S901(図2のS203)の検知結果が「閉状態」を示す場合には(S902−YES)、常に閉状態にある不良素子に対応するフラグ・レジスタ(例えば、MEMS可変容量素子301が「閉状態」を示す場合には、フラグ・レジスタ311)に「閉状態」を示すフラグを立て(S903)、S904へ進む。

【0106】

一方、S901(図2のS203)の検知結果が「開状態」を示す場合には(S902−NO)、S904へ進む。

【0107】

S901〜S903は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S904−NO)。

【0108】

全てのMEMS可変容量素子301〜305に対してSS901〜903が行われた場合には(S904−YES)、第1制御手段102は、全てのMEMS可変容量素子301〜305を閉状態に制御する(S905)。このとき、常に開状態にある不良素子は開状態であるが、その他の素子は閉状態である。

【0109】

続いて、容量検知手段104は、図2のS203と同様の処理を行う(S906)。

【0110】

S906の検知結果が「開状態」を示す場合には(S907−YES)、常に開状態にある不良素子に対応するフラグ・レジスタ(例えば、MEMS可変容量素子302が「開状態」を示す場合には、フラグ・レジスタ312)に「開状態」を示すフラグを立て(S903)、S904へ進む。

【0111】

一方、S906の検知結果が「閉状態」を示す場合には(S907−NO)、S909へ進む。すなわち、フラグが立てられていないフラグ・レジスタに対応する素子は正常な素子である。

【0112】

S906〜S908は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S909−NO)。

【0113】

全てのMEMS可変容量素子301〜305に対してS906〜S908が行われた場合には(S909−YES)、本発明の実施例4に係る不良素子検出処理が終了する。

【0114】

なお、制御装置100は、S901〜S904とS905〜S909を順不同に行っても良い。

【0115】

また、本発明の実施例4に係る不良素子検出処理において、第1制御手段102は、常に閉状態であることを示すフラグ又は常に開状態であることを示すフラグのいずれか一方を立てても良い。

【0116】

図10は、本発明の実施例4に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0117】

はじめに、制御装置100は、図3のS301及びS302と同様の処理を行う(S1001)。このとき、常に閉状態にある不良素子は閉状態であるが、その他の素子は開状態である。

【0118】

続いて、第2制御手段106は、フラグ・レジスタ311〜315を参照する(S1002)。

【0119】

S1001(図3のS301)の指示情報が閉状態への容量制御処理(閉状態にする素子の数)を示す場合には(S1003−YES)、第2制御手段106は、S1001(図3のS301)の指示情報(n)及びS1002において参照されたフラグ・レジスタ311〜315のうち「閉状態」を示すフラグが立てられたフラグ・レジスタの数(m1)に基づいて制御素子数x(=n−m1)を算出し、制御素子情報126として記憶手段120に記憶する(S1004)。

【0120】

続いて、第2制御手段106は、フラグが立てられていないフラグ・レジスタに対応する素子のうち、制御素子情報(制御素子数x)126に相当する数の素子を閉状態に制御し(S1005)、本発明の実施例4に係る容量制御処理を終了する。

【0121】

一方、S1001(図3のS301)の指示が開状態への容量制御処理(開状態にする素子の数)を示す場合には(S1003−NO)、第2制御手段106は、全ての素子を閉状態に制御する(S1006)。このとき、常に開状態にある不良素子は開状態であるが、その他の素子は閉状態である。

【0122】

続いて、S1001(図3のS301)の指示情報(n)及びS1002において参照されたフラグ・レジスタ311〜315のうち「開状態」を示すフラグが立てられたフラグ・レジスタの数(m2)に基づいて制御素子数x(=n−m2)を算出し、制御素子情報126として記憶手段120に記憶する(S1007)。

【0123】

続いて、第2制御手段106は、フラグが立てられていないフラグ・レジスタに対応する素子のうち、制御素子情報(制御素子数x)126に相当する数の素子を開状態に制御し(S1008)、本発明の実施例4に係る容量制御処理を終了する。

【0124】

本発明の実施例4によれば、不良素子において、可変容量システム300のフラグ・レジスタ311〜315に不良素子情報を示すフラグを立てるので、本発明の実施例1〜実施例3よりも不良素子検出処理及び容量制御処理に要する処理時間を短縮することができる。

【図面の簡単な説明】

【0125】

【図1】本発明の実施例1に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【図2】本発明の実施例1に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【図3】本発明の実施例1に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図4】本発明の実施例2に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【図5】本発明の実施例2に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図6】本発明の実施例3に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図7】本発明の実施例3に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図8】本発明の実施例4に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【図9】本発明の実施例4に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【図10】本発明の実施例4に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【符号の説明】

【0126】

100 制御装置

102 第1制御手段

104 容量検知手段

106 第2制御手段

108 指示手段

120 記憶手段

200 入力装置

300 可変容量システム

301〜305 MEMS可変容量素子

【技術分野】

【0001】

本発明は、可変容量素子の制御装置に関し、特に、MEMS(Micro-Electro-Mechanical Systems)可変容量素子及び複数のMEMS可変容量素子が集積されたシステムを制御するための可変容量素子の制御装置に関する。

【背景技術】

【0002】

近年のデバイスの微小化技術の進展に伴い、様々な製品にMEMS可変容量素子等の微小なデバイスが用いられている。

【0003】

静電型アクチュエータを利用したMEMS可変容量素子の構造は、例えば、特許文献1に開示されている。MEMS可変容量素子の制御装置は、MEMS可変容量素子を閉状態(MEMS可変容量素子に容量が大きい状態)にするためには、静電型アクチュエータの上部電極と下部電極との間に電位差をかけ、これら電極間の静電引力が、上部電極が固着された梁のばね力を上回るようにする。

【0004】

閉状態のMEMS可変容量素子では、静電型アクチュエータの上部電極と下部電極とが絶縁膜を介して接した状態となる。このとき、FNトンネル又はプール・フレンケル機構により、絶縁膜に電荷が注入され、トラップされる。この現象を、静電型アクチュエータのダイエレクトリック・チャージングという。

【0005】

このとき、ダイエレクトリック・チャージングにより、絶縁膜にたまった電荷量が十分大きくなると、上部電極と下部電極との間の電位差を0Vとしても、絶縁膜中の電荷に上部電極が引き寄せられ、MEMS可変容量素子を閉状態から開状態(MEMS可変容量素子に容量が小さい状態)に制御することができなくなる場合がある。この現象を、ダイエレクトリック・チャージングによるスティクションという。

【0006】

また、絶縁膜に印加される電界の向きと絶縁膜に注入される電荷の符号は、絶縁膜の種類やトラップの場所により異なるので、ダイエレクトリック・チャージングによるスティクションとは逆に、絶縁膜に注入された電荷の影響でMEMS可変容量素子を閉状態に制御することができなくなる場合もある。

【0007】

また、MEMS可変容量素子の製造上のばらつき等又は経年変化による劣化に起因する不良により、MEMS可変容量素子を制御することができなくなる場合もある。

【0008】

ここで、単一のMEMS可変容量素子において、製造上のばらつき等に起因する不良素子(製造時から所望の動作をしない素子)については、不良品としてスクリーニングすることができる。しかし、ダイエレクトリック・チャージングによるスティクション又は経年変化による劣化に起因する不良素子については、スクリーニングすることができないという問題がある。

【0009】

さらに、複数のMEMS可変容量素子が集積された可変容量システムにおいて、集積されたMEMS可変容量素子の1つが不良素子であるために可変容量システム全体を不良品として扱う場合には、可変容量システムの歩留まり及び信頼性が低下するという問題がある。

【0010】

さらに、可変容量システムの製造時のテストによって不良素子を検出する場合には、不良素子の数及び位置を不揮発性メモリに蓄える必要があり、可変容量システムの製造コストが増加するという問題があった。

【特許文献1】米国特許US5578976号

【発明の開示】

【発明が解決しようとする課題】

【0011】

本発明の目的は、不良素子を含む複数のMEMS可変容量素子が集積された可変容量システムの歩留まり及び信頼性を向上させることである。

【課題を解決するための手段】

【0012】

本発明の第1態様によれば、複数の可変容量素子を含む可変容量システムの制御を指示する指示手段と、前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段と、前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を記憶する記憶手段と、前記記憶手段に記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御する第2制御手段と、を備えたことを特徴とする可変容量素子の制御装置が提供される。

【0013】

本発明の第2態様によれば、複数の可変容量素子及び前記複数の可変容量素子に対応するレジスタを有する可変容量システムを制御する可変容量素子の制御装置であって、前記可変容量素子の制御を指示する指示手段と、前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段及び第2制御手段と、前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、を備え、前記第1制御手段は、前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を前記レジスタに記憶し、前記第2制御手段は、前記レジスタに記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御することを特徴とする可変容量素子の制御装置が提供される。

【発明の効果】

【0014】

本発明によれば、不良素子を含む複数のMEMS可変容量素子が集積されたシステムの歩留まり及び信頼性を向上させることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明の実施例について図面を参照して説明する。なお、以下の実施例は、本発明の実施の一形態であって、本発明の範囲を限定するものではない。

【実施例1】

【0016】

はじめに、本発明の実施例1について説明する。本発明の実施例1では、不良素子情報として、不良素子の数を検出する例について説明する。

【0017】

図1は、本発明の実施例1に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【0018】

本発明の実施例1に係る制御装置100は、入力装置200及び可変容量システム300に接続され、第1制御手段102、容量検知手段104、第2制御手段106、指示手段108及び記憶手段120を備えている。入力装置200は、オペレータからの指示を受け付けるハードウェア(例えば、キーボード又はマウス)である。

【0019】

本発明の実施例1に係る可変容量システム300は、複数のMEMS可変容量素子301〜305が集積されたシステムである。MEMS可変容量素子301〜305の数は、複数個であればいくつでも良い。

【0020】

第1制御手段102は、後述する不良素子検出処理において、指示手段108の指示内容に基づいて不良素子を検出するプロセッサである。

【0021】

容量検知手段104は、各MEMS可変容量素子301〜305毎に上部電極と下部電極の間の容量を検知する容量検知センサである。

【0022】

第2制御手段106は、後述する容量制御処理において、指示手段108の指示内容に基づいて、可変容量システム300が所定の容量を示すように制御するプロセッサである。

【0023】

指示手段108は、入力装置200から入力されたテストコマンドに基づいて、第1制御手段102に後述する不良素子検出処理の開始を指示するとともに、第2制御手段106に後述する容量制御処理の開始を指示する。なお、指示手段108は、制御装置100の電源が投入された場合に、同様の処理の開始を指示しても良い。ここで、指示手段108の指示内容は、制御対象となるMEMS可変容量素子301〜305の数又は所望の容量を示す指示情報を含む。

【0024】

記憶手段120は、第1制御手段102及び第2制御手段106のための制御プログラム122、各MEMS可変容量素子301〜305毎の不良を示す不良素子情報124並びに後述する制御素子情報126を記憶する。

【0025】

不良素子情報124は、不良素子の数又は不良素子の位置を記憶する不良素子レジスタに記憶される。

【0026】

次に、本発明の実施例1に係る不良素子検出処理及び容量制御処理について説明する。ここでは、可変容量システム300が常に閉状態(MEMS可変容量素子に容量が大きい状態)にある不良素子のみを含む例を説明する。

【0027】

閉状態の上部電極と下部電極の間の距離は開状態(MEMS可変容量素子に容量が小さい状態)の上部電極と下部電極の間の距離よりも短いので、閉状態の上部電極と下部電極の間の容量は開状態の上部電極と下部電極の間の容量よりも大きくなる。従って、上部電極と下部電極の間の容量を計測することにより、MEMS可変容量素子の状態(開状態又は閉状態)が分かる。

【0028】

可変容量システム300の可変容量素子の総数をy、入力装置200から入力された指示情報(閉状態にする素子の数)をnとすると、y個のうちn個の素子を閉状態にする必要がある。例えば、入力装置200から指示情報としてn=3が与えられたときには、3つのMEMS可変容量素子を閉状態に制御する必要がある。

【0029】

不良素子(常に閉状態である素子)の数をm、閉状態に制御する必要がある制御素子の数をxとすると、x=n−mである。従って、制御素子の数xを求めるためには、不良素子の数mを検出する必要がある。

【0030】

図2は、本発明の実施例1に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0031】

なお、本発明の実施例1に係る不良素子検出処理は、制御装置100の電源が投入されたとき又は入力装置200からテストコマンドが入力されたときに行われる。

【0032】

はじめに、第1制御手段102は、記憶手段120の不良素子情報124をリセットする(S201)。

【0033】

続いて、第1制御手段102は、全てのMEMS可変容量素子301〜305を開状態に制御する(S202)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0034】

続いて、容量検知手段104は、MEMS可変容量素子301〜305のうちの1つの素子の容量を検知する(S203)。

【0035】

続いて、第1制御手段102は、S203の検知結果が「閉状態」を示す場合には(S204−YES)、記憶手段120の不良素子レジスタに記憶された不良素子の数を示す不良素子情報(不良素子数m)124をインクリメントし(S205)、S206へ進む。

【0036】

一方、S203の検知結果が「開状態」を示す場合には(S204−NO)、S206へ進む。

【0037】

S203〜S205は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S206−NO)。

【0038】

全てのMEMS可変容量素子301〜305に対してS203〜S206が行われた場合には(S206−YES)、本発明の実施例1に係る不良素子検出処理が終了する。

【0039】

なお、第1制御手段102は、S202において、全ての素子を閉状態に制御し、S206において、S203の検知結果が「開状態」を示す場合に、常に開状態にある不良素子の数を示す不良素子情報(不良素子数m)124を記憶手段120の不良素子レジスタに記憶しても良い。

【0040】

図3は、本発明の実施例1に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0041】

はじめに、指示手段108は、入力装置200から入力されたオペレータの指示に基づいて、指示情報nを受け付ける(S301)。なお、入力装置200から入力された指示情報が所望の容量である場合には、所望の容量を満たすMEMS可変容量素子301〜305の数をnとする。

【0042】

続いて、第2制御手段106は、全ての素子を開状態に制御する(S302)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0043】

続いて、第2制御手段106は、制御素子数x(=n−m)を算出し、制御素子情報126として記憶手段120に記憶する(S303)。

【0044】

続いて、容量検知手段104は、各MEMS可変容量素子301〜305毎に素子容量を検知する(S304)。

【0045】

続いて、第2制御手段106は、S304の検知結果が「開状態」を示す場合には(S305−YES)、S304において検知された素子を閉状態に制御する(S306)。

【0046】

続いて、第2制御手段106は、制御素子情報(制御素子数x)126をデクリメントし(S307)、S308へ進む。

【0047】

一方、S304の検知結果が「閉状態」を示す場合には(S305−NO)、S308へ進む。

【0048】

S304〜S307は、制御素子情報(制御素子数x)126が0になるまで繰り返される(S308−NO)。

【0049】

制御素子情報(制御素子数x)126が0になった場合には(S308−YES)、本発明の実施例1に係る容量制御処理が終了する。

【0050】

なお、指示手段106は、S301において、可変容量システム300の素子数よりも所定の割合未満の数を指示情報nの上限としても良い。この場合には、指示情報nの上限は、可変容量システム300の歩留まりを考慮して定められる。例えば、可変容量システム300の素子数が5個である場合であって、可変容量システム300の歩留まりが60%である場合には、指示情報nの上限は3となる。

【0051】

また、第2制御手段106は、S302において、全ての素子を閉状態に制御し、S306において、S304の検知結果が「閉状態」を示す場合に、S304において検知された素子を開状態に制御しても良い。

【0052】

本発明の実施例1によれば、可変容量システム300の容量が外部の制御装置100によって制御されるので、プロセスに対する要求が互いに異なる可変容量システム300と他の回路システムとを分離することができ、可変容量システム300の歩留まり及び信頼性を向上させることができる。

【0053】

また、本発明の実施例1によれば、全ての素子を開状態に制御した後で閉状態である素子の数を不良素子情報124として記憶手段120に記憶するので、製造後のダイエレクトリック・チャージングによるスティクション又は経年変化による劣化に起因する不良素子の数を検出することができる。

【0054】

また、本発明の実施例1によれば、不良素子検出処理の検出結果に基づいて容量制御処理を行うので、製造後のダイエレクトリック・チャージングによるスティクション又は経年変化による劣化に起因する不良素子を含む可変容量システム300においても所望の容量に制御することができる。

【0055】

また、本発明の実施例1によれば、不良素子の数及び位置を記憶する不揮発性メモリが必要ないので、製造コストを低減させることができる。

【0056】

また、本発明の実施例1によれば、指示手段106が受付可能な指示情報nの値が可変容量システム300の歩留まりに応じて定められるので、可変容量システム300の全てのMEMS可変容量素子301〜305の正常状態を補償する必要がなく、製造コストを低減することができる。

【実施例2】

【0057】

次に、本発明の実施例2について説明する。本発明の実施例1では、不良素子情報として不良素子の数を検出する例について説明したが、本発明の実施例2では、不良素子情報として不良素子の数及び位置を検出する例について説明する。なお、本発明の実施例1と同様の内容についての説明は省略する。

【0058】

図4は、本発明の実施例2に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0059】

なお、本発明の実施例2に係る不良素子検出処理は、制御装置100の電源が投入されたとき又は入力装置200からテストコマンドが入力されたときに行われる。

【0060】

はじめに、制御装置100は、図2のS201〜S203と同様の処理を行う(S401)。このとき、不良素子は開状態であるが、その他の素子は開状態である。

【0061】

続いて、第1制御手段102は、S401(図2のS203)の検知結果が「閉状態」を示す場合には(S402−YES)、不良素子の位置を示す不良素子情報(位置情報)124を記憶手段120の不良素子レジスタに記憶し(S403)、S404へ進む。例えば、第1制御手段102は、記憶手段120の不良素子レジスタに位置情報を記憶する。ここで、記憶手段120の不良素子レジスタに記憶された位置情報の数は不良素子の数である。

【0062】

一方、S402(図2のS203)の検知結果が「開状態」を示す場合には(S402−NO)、S404へ進む。

【0063】

S401〜S405は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S404−NO)。

【0064】

全てのMEMS可変容量素子301〜305に対してS401〜S405が行われた場合には(S404−YES)、本発明の実施例2に係る不良素子検出処理が終了する。

【0065】

図5は、本発明の実施例2に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0066】

はじめに、制御装置100は、図3のS301及びS302と同様の処理を行う(S501)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0067】

続いて、第2制御手段106は、記憶手段120の不良素子レジスタに記憶された不良素子情報(位置情報)124を参照する(S502)。

【0068】

続いて、第2制御手段106は、S501(図3のS301)の指示情報(n)、S502において参照された不良素子情報(位置情報)124の数(m)及びS502において参照された不良素子情報(位置情報)124に示された素子のうち正常な素子と同じグループに属する素子の数(k)に基づいて制御素子数x(=n−m+k)を算出し、制御素子情報126として記憶手段120に記憶する(S503)。

【0069】

続いて、第2制御手段106は、不良素子情報(位置情報)124に示されない素子のうち、制御素子情報(制御素子数x)126に相当する数の素子を閉状態に制御し(S504)、本発明の実施例2に係る容量制御処理を終了する。

【0070】

本発明の実施例2によれば、常に閉状態である不良素子を含む可変容量システム300においても、実施例1と同様の効果を得ることができる。

【0071】

また、本発明の実施例2によれば、不良素子検出処理において位置情報を参照するので、不良素子の数だけでなく、不良素子の位置を特定することができる。

【0072】

また、本発明の実施例2によれば、容量制御処理において、位置情報を参照し、MEMS可変容量素子301〜305の容量を検知することなく制御するとともに、正常な素子と同じグループに属するk個の不良素子も含めて同時に制御するので、処理時間を短縮することができる。

【実施例3】

【0073】

次に、本発明の実施例3について説明する。本発明の実施例1及び2では、それぞれ、常に閉状態又は開状態にある不良素子を含む可変容量システムを制御する例について説明したが、本発明の実施例3では、常に閉状態にある不良素子及び常に開状態にある不良素子を含む可変容量システムを制御する例について説明する。なお、本発明の実施例1及び2と同様の内容についての説明は省略する。

【0074】

本発明の実施例3に係る制御装置100では、指示手段108は、閉状態への容量制御処理又は開状態への容量制御処理を指示する。

【0075】

記憶手段120は、常に閉状態にある不良素子の数及び位置を記憶する第1レジスタ及び常に開状態にある不良素子の数及び位置を記憶する第2レジスタを備えている。

【0076】

図6は、本発明の実施例3に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0077】

はじめに、制御装置100は、図2のS201〜S203と同様の処理を行う(S601)。このとき、常に閉状態にある不良素子は閉状態であるが、その他の素子は開状態である。

【0078】

続いて、第1制御手段102は、S601(図2のS203)の検知結果が「閉状態」を示す場合には(S602−YES)、常に閉状態にある不良素子の位置を示す不良素子情報(位置情報)124を記憶手段120の第1レジスタに記憶し(S603)、S604へ進む。

【0079】

一方、S601(図2のS203)の検知結果が「開状態」を示す場合には(S602−NO)、S604へ進む。

【0080】

S601〜S603は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S604−NO)。

【0081】

全てのMEMS可変容量素子301〜305に対してS601〜S603が行われた場合には(S604−YES)、第1制御手段102は、全てのMEMS可変容量素子301〜305を閉状態に制御する(S605)。このとき、常に開状態にある不良素子は開状態であるが、その他の素子は閉状態である。

【0082】

続いて、容量検知手段104は、図2のS203と同様の処理を行う(S606)。

【0083】

S606の検知結果が「開状態」を示す場合には(S607−YES)、常に開状態にある不良素子の位置を示す不良素子情報(位置情報)124を記憶手段120の第2レジスタに記憶し(S608)、S609へ進む。

【0084】

一方、S606の検知結果が「閉状態」を示す場合には(S607−NO)、S609へ進む。

【0085】

S606〜S608は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S609−NO)。

【0086】

全てのMEMS可変容量素子301〜305に対してS606〜S608が行われた場合には(S609−YES)、本発明の実施例3に係る不良素子検出処理が終了する。

【0087】

なお、制御装置100は、S601〜S604とS605〜S609を順不同に行っても良い。

【0088】

図7は、本発明の実施例3に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0089】

はじめに、制御装置100は、図3のS301及びS302と同様の処理を行う(S701)。このとき、不良素子は閉状態であるが、その他の素子は開状態である。

【0090】

続いて、第2制御手段106は、記憶手段120の第1レジスタの不良素子情報(位置情報)124を参照する(S702)。

【0091】

続いて、第2制御手段106は、記憶手段120の第2レジスタの不良素子情報(位置情報)124を参照する(S703)。

【0092】

S701(図3のS301)の指示情報が閉状態への容量制御処理(閉状態にする素子の数)を示す場合には(S704−YES)、第2制御手段106は、S701(図3のS301)の指示情報(n)及びS702において参照された記憶手段120の第1レジスタに記憶された不良素子情報(位置情報)124の数(m1)に基づいて制御素子数x(=n−m1)を算出し、制御素子情報(制御素子数x)126として記憶手段120に記憶する(S705)。

【0093】

続いて、第2制御手段106は、記憶手段120の第1レジスタ及び第2レジスタの不良素子情報(位置情報)124に示されない素子のうち、制御素子情報(制御素子数x)に相当する数の素子を閉状態に制御し(S706)、本発明の実施例3に係る容量制御処理を終了する。

【0094】

一方、S701(図3のS301)の指示が開状態への容量制御処理(開状態にする素子の数)を示す場合には(S704−NO)、第2制御手段106は、全ての素子を閉状態に制御する(S707)。このとき、不良素子は開状態であるが、その他の素子は閉状態である。

【0095】

続いて、S701(図3のS301)の指示情報(n)及びS703において参照された記憶手段120の第2レジスタの不良素子情報(位置情報)124の数(m2)に基づいて制御素子数x(=n−m2)を算出し、制御素子情報126として記憶手段120に記憶する(S708)。

【0096】

続いて、第2制御手段106は、記憶手段120の第1レジスタ及び第2レジスタの不良素子情報(位置情報)124に示されない素子のうち、制御素子情報(制御素子数x)に相当する数の素子を開状態に制御し(S709)、本発明の実施例3に係る容量制御処理を終了する。

【0097】

本発明の実施例3によれば、常に閉状態にある不良素子及び常に開状態にある不良素子を含む可変容量システム300においても、実施例1及び2と同様の効果を得ることができる。

【実施例4】

【0098】

次に、本発明の実施例4について説明する。本発明の実施例1〜3では、制御装置内の不良素子情報に基づいて容量制御処理を行う例について説明したが、本発明の実施例4では、可変容量システム内の不良素子情報に基づいて容量制御処理を行う例について説明する。なお、本発明の実施例1〜3と同様の内容についての説明は省略する。

【0099】

図8は、本発明の実施例4に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【0100】

本発明の実施例4に係る可変容量システム300は、複数のMEMS可変容量素子301〜305及び各MEMS可変容量素子301〜305に対応するフラグ・レジスタ311〜315を備える。

【0101】

各フラグ・レジスタ311〜315は、それぞれ、正常な状態であること、常に閉状態であること及び常に開状態であることを示すための2ビットの容量を有する。

【0102】

記憶手段120は、第1制御手段102及び第2制御手段106のための制御プログラム122並びに制御素子情報126を記憶する。

【0103】

図9は、本発明の実施例4に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【0104】

はじめに、制御装置100は、図2のS201〜S203と同様の処理を行う(S901)。このとき、常に閉状態にある不良素子は閉状態であるが、その他の素子は開状態である。

【0105】

続いて、第1制御手段102は、S901(図2のS203)の検知結果が「閉状態」を示す場合には(S902−YES)、常に閉状態にある不良素子に対応するフラグ・レジスタ(例えば、MEMS可変容量素子301が「閉状態」を示す場合には、フラグ・レジスタ311)に「閉状態」を示すフラグを立て(S903)、S904へ進む。

【0106】

一方、S901(図2のS203)の検知結果が「開状態」を示す場合には(S902−NO)、S904へ進む。

【0107】

S901〜S903は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S904−NO)。

【0108】

全てのMEMS可変容量素子301〜305に対してSS901〜903が行われた場合には(S904−YES)、第1制御手段102は、全てのMEMS可変容量素子301〜305を閉状態に制御する(S905)。このとき、常に開状態にある不良素子は開状態であるが、その他の素子は閉状態である。

【0109】

続いて、容量検知手段104は、図2のS203と同様の処理を行う(S906)。

【0110】

S906の検知結果が「開状態」を示す場合には(S907−YES)、常に開状態にある不良素子に対応するフラグ・レジスタ(例えば、MEMS可変容量素子302が「開状態」を示す場合には、フラグ・レジスタ312)に「開状態」を示すフラグを立て(S903)、S904へ進む。

【0111】

一方、S906の検知結果が「閉状態」を示す場合には(S907−NO)、S909へ進む。すなわち、フラグが立てられていないフラグ・レジスタに対応する素子は正常な素子である。

【0112】

S906〜S908は、全てのMEMS可変容量素子301〜305に対して行われるまで繰り返される(S909−NO)。

【0113】

全てのMEMS可変容量素子301〜305に対してS906〜S908が行われた場合には(S909−YES)、本発明の実施例4に係る不良素子検出処理が終了する。

【0114】

なお、制御装置100は、S901〜S904とS905〜S909を順不同に行っても良い。

【0115】

また、本発明の実施例4に係る不良素子検出処理において、第1制御手段102は、常に閉状態であることを示すフラグ又は常に開状態であることを示すフラグのいずれか一方を立てても良い。

【0116】

図10は、本発明の実施例4に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【0117】

はじめに、制御装置100は、図3のS301及びS302と同様の処理を行う(S1001)。このとき、常に閉状態にある不良素子は閉状態であるが、その他の素子は開状態である。

【0118】

続いて、第2制御手段106は、フラグ・レジスタ311〜315を参照する(S1002)。

【0119】

S1001(図3のS301)の指示情報が閉状態への容量制御処理(閉状態にする素子の数)を示す場合には(S1003−YES)、第2制御手段106は、S1001(図3のS301)の指示情報(n)及びS1002において参照されたフラグ・レジスタ311〜315のうち「閉状態」を示すフラグが立てられたフラグ・レジスタの数(m1)に基づいて制御素子数x(=n−m1)を算出し、制御素子情報126として記憶手段120に記憶する(S1004)。

【0120】

続いて、第2制御手段106は、フラグが立てられていないフラグ・レジスタに対応する素子のうち、制御素子情報(制御素子数x)126に相当する数の素子を閉状態に制御し(S1005)、本発明の実施例4に係る容量制御処理を終了する。

【0121】

一方、S1001(図3のS301)の指示が開状態への容量制御処理(開状態にする素子の数)を示す場合には(S1003−NO)、第2制御手段106は、全ての素子を閉状態に制御する(S1006)。このとき、常に開状態にある不良素子は開状態であるが、その他の素子は閉状態である。

【0122】

続いて、S1001(図3のS301)の指示情報(n)及びS1002において参照されたフラグ・レジスタ311〜315のうち「開状態」を示すフラグが立てられたフラグ・レジスタの数(m2)に基づいて制御素子数x(=n−m2)を算出し、制御素子情報126として記憶手段120に記憶する(S1007)。

【0123】

続いて、第2制御手段106は、フラグが立てられていないフラグ・レジスタに対応する素子のうち、制御素子情報(制御素子数x)126に相当する数の素子を開状態に制御し(S1008)、本発明の実施例4に係る容量制御処理を終了する。

【0124】

本発明の実施例4によれば、不良素子において、可変容量システム300のフラグ・レジスタ311〜315に不良素子情報を示すフラグを立てるので、本発明の実施例1〜実施例3よりも不良素子検出処理及び容量制御処理に要する処理時間を短縮することができる。

【図面の簡単な説明】

【0125】

【図1】本発明の実施例1に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【図2】本発明の実施例1に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【図3】本発明の実施例1に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図4】本発明の実施例2に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【図5】本発明の実施例2に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図6】本発明の実施例3に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図7】本発明の実施例3に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【図8】本発明の実施例4に係る制御装置100及び可変容量システム300の構成を示すブロック図である。

【図9】本発明の実施例4に係る不良素子検出処理における制御装置100の処理手順を示すフローチャートである。

【図10】本発明の実施例4に係る容量制御処理における制御装置100の処理手順を示すフローチャートである。

【符号の説明】

【0126】

100 制御装置

102 第1制御手段

104 容量検知手段

106 第2制御手段

108 指示手段

120 記憶手段

200 入力装置

300 可変容量システム

301〜305 MEMS可変容量素子

【特許請求の範囲】

【請求項1】

複数の可変容量素子を含む可変容量システムの制御を指示する指示手段と、

前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段と、

前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、

前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を記憶する記憶手段と、

前記記憶手段に記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御する第2制御手段と、を備えたことを特徴とする可変容量素子の制御装置。

【請求項2】

前記指示手段は、前記可変容量システムの容量を指示し、

前記第1制御手段は、前記複数の可変容量素子を開状態に制御し、

前記記憶手段は、前記容量検知手段によって容量が検知された可変容量素子の数を示す不良素子情報を記憶し、

前記第2制御手段は、前記指示手段によって指示された可変容量システムの容量及び前記記憶手段に記憶された不良素子情報に基づいて、開状態の可変容量素子を閉状態に制御する請求項1に記載の可変容量素子の制御装置。

【請求項3】

前記指示手段は、前記可変容量システムの容量を指示し、

前記第1制御手段は、前記複数の可変容量素子を開状態に制御し、

前記記憶手段は、前記容量検知手段によって容量が検知された可変容量素子を示す不良素子情報を記憶し、

前記第2制御手段は、前記指示手段によって指示された可変容量システムの容量及び前記記憶手段に記憶された不良素子情報に基づいて、開状態の可変容量素子であって前記記憶手段に記憶された不良素子情報に対応しない可変容量素子を閉状態に制御する請求項1に記載の可変容量素子の制御装置。

【請求項4】

複数の可変容量素子及び前記複数の可変容量素子に対応するレジスタを有する可変容量システムを制御する可変容量素子の制御装置であって、

前記可変容量素子の制御を指示する指示手段と、

前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段及び第2制御手段と、

前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、を備え、

前記第1制御手段は、前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を前記レジスタに記憶し、

前記第2制御手段は、前記レジスタに記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御することを特徴とする可変容量素子の制御装置。

【請求項5】

前記指示手段は、前記可変容量素子の数よりも所定の割合未満の数の前記複数の可変容量素子の制御を指示する請求項1乃至4の何れか1項に記載の可変容量素子の制御装置。

【請求項1】

複数の可変容量素子を含む可変容量システムの制御を指示する指示手段と、

前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段と、

前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、

前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を記憶する記憶手段と、

前記記憶手段に記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御する第2制御手段と、を備えたことを特徴とする可変容量素子の制御装置。

【請求項2】

前記指示手段は、前記可変容量システムの容量を指示し、

前記第1制御手段は、前記複数の可変容量素子を開状態に制御し、

前記記憶手段は、前記容量検知手段によって容量が検知された可変容量素子の数を示す不良素子情報を記憶し、

前記第2制御手段は、前記指示手段によって指示された可変容量システムの容量及び前記記憶手段に記憶された不良素子情報に基づいて、開状態の可変容量素子を閉状態に制御する請求項1に記載の可変容量素子の制御装置。

【請求項3】

前記指示手段は、前記可変容量システムの容量を指示し、

前記第1制御手段は、前記複数の可変容量素子を開状態に制御し、

前記記憶手段は、前記容量検知手段によって容量が検知された可変容量素子を示す不良素子情報を記憶し、

前記第2制御手段は、前記指示手段によって指示された可変容量システムの容量及び前記記憶手段に記憶された不良素子情報に基づいて、開状態の可変容量素子であって前記記憶手段に記憶された不良素子情報に対応しない可変容量素子を閉状態に制御する請求項1に記載の可変容量素子の制御装置。

【請求項4】

複数の可変容量素子及び前記複数の可変容量素子に対応するレジスタを有する可変容量システムを制御する可変容量素子の制御装置であって、

前記可変容量素子の制御を指示する指示手段と、

前記指示手段の指示に基づいて、前記複数の可変容量素子を開状態又は閉状態に制御する第1制御手段及び第2制御手段と、

前記第1制御手段によって制御された可変容量素子の容量を検知する容量検知手段と、を備え、

前記第1制御手段は、前記容量検知手段によって検知された容量に基づいて、前記可変容量素子の不良を示す不良素子情報を前記レジスタに記憶し、

前記第2制御手段は、前記レジスタに記憶された不良素子情報に基づいて、前記可変容量素子を開状態又は閉状態に制御することを特徴とする可変容量素子の制御装置。

【請求項5】

前記指示手段は、前記可変容量素子の数よりも所定の割合未満の数の前記複数の可変容量素子の制御を指示する請求項1乃至4の何れか1項に記載の可変容量素子の制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2008−300646(P2008−300646A)

【公開日】平成20年12月11日(2008.12.11)

【国際特許分類】

【出願番号】特願2007−145368(P2007−145368)

【出願日】平成19年5月31日(2007.5.31)

【出願人】(000003078)株式会社東芝 (54,554)

【公開日】平成20年12月11日(2008.12.11)

【国際特許分類】

【出願日】平成19年5月31日(2007.5.31)

【出願人】(000003078)株式会社東芝 (54,554)

[ Back to top ]