可変容量素子

【課題】移動後の可動電極の位置を維持して、所望の静電容量で安定に動作させることができる、外部振動に強い構造の可変容量素子を提供する。

【解決手段】ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46にV1の正電圧を印加すると、可動電極18が駆動電極14側に移動して、チューナブル・キャパシタ44の容量Cが小さくなる。ブレーキ電圧V2が印加されると、ブレーキ・キャパシタ20の下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との電極間距離が0μmになる。下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との電極間距離も0μmになる。即ち、両電極は誘電体層28を介して接触することになる。これで電極間での摩擦力によって可動電極18の位置を安定に維持することができる。

【解決手段】ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46にV1の正電圧を印加すると、可動電極18が駆動電極14側に移動して、チューナブル・キャパシタ44の容量Cが小さくなる。ブレーキ電圧V2が印加されると、ブレーキ・キャパシタ20の下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との電極間距離が0μmになる。下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との電極間距離も0μmになる。即ち、両電極は誘電体層28を介して接触することになる。これで電極間での摩擦力によって可動電極18の位置を安定に維持することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、可変容量素子に係り、特に、MEMS(Micro Electro Mechanical System)技術を適用した可変容量素子に関する。

【背景技術】

【0002】

近年、携帯電話に代表される無線通信機器は著しい進化を遂げている。次世代の携帯電話では、多数の周波数帯を利用する。このため、複数の周波数を受信可能なRF(Radio Frequency)フロントエンドの開発が進められている。この場合に問題となるのが、部品点数の増加である。特に、キャパシタやインダクター等の受動部品は共通化が難しく、周波数の数が増える分だけ部品点数が増加する。部品点数が増加すると、RFフロントエンドの体積が大きくなり、コストも高くなるという問題が生じる。

【0003】

これらの問題を解決する技術として、部品の大幅な小型化を可能にするMEMS技術が注目されている。MEMS技術とは、機械的な微小構造を作成し、超小型のデバイスを作製するものである。例えば、1つのデバイスで複数のインピーダンスを持つことが可能なMEMS・チューナブル・キャパシタを作製することができる。

【0004】

MEMS・チューナブル・キャパシタを用いて、チューナブル整合回路を構成することができる。このチューナブル整合回路をRFフロントエンドに適用することで、各周波数やシステムごとに動的に回路そのものを再構成することが可能となり、アンテナの本数や個別増幅器の個数を大幅に減らすことが期待できる。このため、種々のMEMS・チューナブル・キャパシタが提案されている。

【0005】

例えば、特許文献1には、基板上に第1電極と第2電極とを固定配置し、電圧印加によりアクチュエータで可動電極を駆動して、可動電極との接触により第1電極と第2電極との間の容量を変化させるMEMS型の可変容量素子が記載されている。

【0006】

特許文献2には、櫛型の第1電極と第2電極とが上下方向に対向配置された微小可動構造体(MEMS)が記載されている。この微小可動構造体では、第1電極と第2電極との間に電圧が印加されると静電力により駆動力が発生する。可動電極である第2電極が上下方向に移動することで、静電力が作用する面積が変化して、静電容量が変化する。

【0007】

一方、携帯電話等の小型の無線通信機器には、約3Vのバッテリーが使用されている。従って、携帯電話等に適用するためには、動作電圧が3V以下の低電圧動作が可能なMEMS・チューナブル・キャパシタが必要になる。即ち、0V〜3Vの範囲で、静電容量を大幅に変化させなければならない。特許文献2に記載された微小可動構造体のように、櫛型電極を用いた場合には、静電力が作用する面積が大きくなり、静電容量の変動幅を増大できるという利点がある。

【0008】

特許文献3には、特許文献2と同様に、固定電極と可動電極とに櫛型電極を用いた電機機械式マイクロ可変容量ダイオード(MEMS)が記載されている。このMEMS可変容量ダイオードでは、固定電極と可動電極との間に電圧が印加されると、静電力により可動電極が移動して静電容量を変化させる。また、櫛型電極は、ミラー素子等の他のMEMSデバイスにも用いられている。例えば、特許文献4には、電圧印加により基台の第1櫛型電極と可動部の第2櫛型電極との間に静電力が働き、可動部が基台の方向に移動するマイクロアクチュエータが記載されている。

【0009】

【特許文献1】特開2006−261480号公報

【特許文献2】特開2005−224934号公報

【特許文献3】特表2006−518926号公報

【特許文献4】特開2005−341788号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

上述した通り、携帯電話等に適用するために、動作電圧が3V以下の低電圧動作が可能なMEMSデバイスとして、櫛型電極を用いたMEMS・チューナブル・キャパシタ(可変容量素子)が検討されている。しかしながら、これらの可変容量素子には、移動後の可動電極の位置を安定して維持できないという問題があった。可動電極は、静電力で所定位置に維持されているためである。外部振動により可動電極の位置が変動すると、静電容量が変化して動作が不安定になるという不具合を生じる。

【0011】

また、固定電極と可動電極とは、互いの櫛歯部が噛み合うように動作する。従って、動作時に外部振動を受けて固定電極と可動電極とが接触し、短絡する恐れがある。

【0012】

本発明は、上記問題を解決すべく成されたものであり、移動後の可動電極の位置を維持して、所望の静電容量で安定に動作させることができる、外部振動に強い構造の可変容量素子を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するために請求項1に記載の可変容量素子は、支持基板と、前記支持基板の表面に形成された薄膜状の第1電極と、前記第1電極の上方に固定配置されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第2電極と、前記第1電極と前記第2電極との間に配置され、前記第2電極に対して垂直方向及び水平方向に移動可能に保持されると共に、前記第2電極の複数の櫛歯部の間隙に対向し且つ第2電極側に突出する複数の櫛歯部を備え、表面が誘電体層で被覆された平板状の第3電極であって、前記第2電極と共に可変容量を構成し、前記第1電極と該第2電極の間に印加された第1電圧に応じて垂直方向に駆動される第3電極と、前記第1電極の上方に固定配置され、前記第2電極と水平方向に接続されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第4電極であって、前記第2電極とは電気的に絶縁された第4電極と、前記第1電極と前記第4電極との間に配置され、前記第3電極と水平方向に接続されると共に、前記第4電極の複数の櫛歯部の間隙に対向し且つ第4電極側に突出する少なくとも1つの櫛歯部を備え、表面が誘電体層で被覆された平板状の第5電極であって、前記第4電極と共に前記第3電極の振動を防止する振動防止部を構成し、前記第4電極と該第5電極との間に印加された第2電圧に応じて水平方向に駆動されて、前記第4電極の櫛歯部と該第5電極の櫛歯部とが接触して静電力により前記第4電極に固定される第5電極と、を備えたことを特徴としている。

【0014】

請求項2に記載の可変容量素子は、請求項1に記載の発明において、前記第3電極及び前記第5電極の前記第1電極と対向する面に絶縁膜を介して第6電極を更に形成し、該第6電極と前記第1電極との間に印加された第1電圧に応じて前記第3電極が垂直方向に駆動されることを特徴としている。

【0015】

請求項3に記載の可変容量素子は、請求項1又は2に記載の発明において、前記第1電極と前記第3電極及び第5電極との間に、前記電極間での静電容量を調整する誘電体層が設けられたことを特徴としている。

【0016】

請求項4に記載の可変容量素子は、請求項1〜3の何れか1項に記載の発明において、前記第2電極と前記4電極とが1枚の平板として形成されたことを特徴としている。

【0017】

請求項5に記載の可変容量素子は、支持基板と、前記支持基板の表面に形成された薄膜状の第1電極と、前記第1電極の上方に固定配置されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第2電極と、前記第1電極と前記第2電極との間に配置され、前記第2電極に対して垂直方向及び水平方向に移動可能に保持されると共に、前記第2電極の複数の櫛歯部の間隙に対向し且つ第2電極側に突出する複数の櫛歯部を備え、表面が誘電体層で被覆された平板状の第3電極であって、前記第2電極と共に可変容量を構成し、前記第1電極と該第2電極の間に印加された第1電圧に応じて垂直方向に駆動される第3電極と、前記第1電極の上方に固定配置され、前記第2電極に対し左右対称となるように前記第2電極と水平方向に接続されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第4電極であって、前記第2電極とは電気的に絶縁された複数対の第4電極と、前記第1電極と前記第4電極との間に配置され、前記第3電極と水平方向に接続されると共に、前記第4電極の複数の櫛歯部の間隙に対向し且つ第4電極側に突出する少なくとも1つの櫛歯部を備え、表面が誘電体層で被覆された平板状の第5電極であって、前記複数対の第4電極の各々に対応して設けられ、前記複数対の第4電極の各々と共に前記第3電極の振動を防止する振動防止部を構成し、前記第4電極と該第5電極との間に印加された第2電圧に応じて一対の第5電極が水平方向を反対向きに駆動されて、前記第4電極の櫛歯部と該第5電極の櫛歯部とが接触して静電力により前記複数対の第4電極の各々に固定される複数対の第5電極と、を備えたことを特徴としている。

【0018】

請求項6に記載の可変容量素子は、請求項5に記載の発明において、前記第3電極及び前記第5電極の前記第1電極と対向する面に絶縁膜を介して第6電極を更に形成し、該第6電極と前記第1電極との間に印加された第1電圧に応じて前記第3電極が垂直方向に駆動されることを特徴としている。

【0019】

請求項7に記載の可変容量素子は、請求項5又は6に記載の発明において、前記第1電極と前記第3電極及び第5電極との間に、前記電極間での静電容量を調整する誘電体層が設けられたことを特徴としている。

【0020】

請求項8に記載の可変容量素子は、請求項5〜7の何れか1項に記載の発明において、前記第2電極と前記複数対の第4電極の各々とが別々の平板として形成されたことを特徴としている。

【0021】

請求項9に記載の可変容量素子は、請求項5〜8の何れか1項に記載の発明において、前記第3電極と前記複数対の第5電極の各々とは、可とう性を有する材料で形成されたU字状の接続部材で接続されたことを特徴としている。

【0022】

請求項10に記載の可変容量素子は、請求項1〜9の何れか1項に記載の発明において、前記支持基板が、半導体基板又は結晶基板であることを特徴としている。

【0023】

請求項11に記載の可変容量素子は、請求項1〜10の何れか1項に記載の発明において、前記支持基板が、シリコン基板又は酸化アルミニウム基板であることを特徴としている。

【発明の効果】

【0024】

各請求項に係る発明によれば、以下の効果がある。

【0025】

請求項1に係る発明によれば、第4電極及び第5電極から構成される振動防止部にブレーキ電圧(第2電圧)を印加することで、駆動電圧(第1電圧)を印加して移動させた後の可動電極(第3電極)の垂直方向の位置を固定し、外部振動による可動電極(第3電極)の振動を防止して、可変容量素子を所望の静電容量で安定に動作させることができる、という効果がある。

【0026】

請求項2、請求項6に係る発明によれば、可動電極(第3電極)と絶縁された可動駆動電極(第6電極)を設けることで、容量調整動作時における駆動電圧(第1電圧)による影響を低減して、可変容量素子を所望の静電容量で更に安定に動作させることができる、という効果がある。

【0027】

請求項3、請求項7に係る発明によれば、更に、可動電極(第3電極)と駆動電極(第1電極)との間に誘電体層を設けることで、誘電体層の厚さで可動電極(第3電極)を支持する梁部のばね定数を制御して、可変容量素子を所望の静電容量で動作させることができる、という効果がある。

【0028】

請求項4に係る発明によれば、上部ブレーキ電極(第4電極)及び固定電極(第2電極)を一体に形成することで、作製工程が簡単になる、という効果がある。

【0029】

請求項5に係る発明によれば、下部ブレーキ電極(第5電極)及び可動電極(第3電極)をフレキシブルな接続部材で接続した状態で振動防止部にブレーキ電圧(第2電圧)を印加することで、駆動電圧(第1電圧)を印加して移動させた後の可動電極(第3電極)の垂直方向及び水平方向の位置を固定し、外部振動による可動電極(第3電極)の振動を防止して、可変容量素子を所望の静電容量で更に安定に動作させることができる、という効果がある。

【0030】

請求項8に係る発明によれば、上部ブレーキ電極(第4電極)及び固定電極(第2電極)を別体に形成することで、下部ブレーキ電極(第5電極)及び可動電極(第3電極)を別体に形成することができる、という効果がある。

【0031】

請求項9に係る発明によれば、下部ブレーキ電極(第5電極)と可動電極(第3電極)とを、別々に動かすことが可能になる、という効果がある。

【0032】

請求項10、11に係る発明によれば、RFフロントエンドに適用するチューナブル整合回路を構成するのにより好適な可変容量素子を提供できる、という効果がある。

【発明を実施するための最良の形態】

【0033】

以下、図面を参照して本発明の実施の形態の一例を詳細に説明する。

【0034】

(第1の実施の形態)

<可変容量素子の概略構成>

まず、図1〜図3を参照して、可変容量素子の構成を簡単に説明する。図1は本発明の第1の実施の形態に係る可変容量素子の外観を示す斜視図である。図2は可変容量素子を固定電極側から見た平面図である。図3は可変容量素子の側面図である。

【0035】

可変容量素子10は、シリコン等の半導体で構成された支持基板12、支持基板12上に配置された駆動電極14、駆動電極14に対向するように離間配置された固定電極16、駆動電極14と固定電極16との間に移動可能に保持された可動電極18、及び可動電極18の移動後の振動を防止する振動防止部としてのブレーキ・キャパシタ20を備えている。ブレーキ・キャパシタ20は、上部ブレーキ電極22と、電圧印加により上部ブレーキ電極22と接触する下部ブレーキ電極24とで構成されている。

【0036】

支持基板12は平面視が矩形状の平板である。支持基板12としては、半導体プロセスで使用可能な基板であればよく、シリコン基板等の半導体基板の外、酸化アルミニウム(Al2O3)等の結晶基板を用いることができる。駆動電極14は導電性材料により形成された薄膜電極である。導電性材料としては、半導体プロセスで一般的に使用されている材料を使用することができる。駆動電極14は絶縁層(図示せず)を介して支持基板上12上に成膜されている。駆動電極14は平面視が支持基板12よりひと回り小さい矩形状とされ、支持基板上12の中央部分に形成されている。

【0037】

本実施の形態では、支持基板12の面積を400μm×400μmとし、駆動電極14の面積を300μm×300μmとしている。支持基板12としては、シリコン(Si)等の半導体基板が用いられている。また、駆動電極14用の導電性材料には、タングステンシリサイド(WSi2)が用いられている。絶縁層(図示せず)には、窒化シリコン(Si3N4)が用いられている。駆動電極14の厚さは約0.2μmである。

【0038】

固定電極16は平面視が矩形状の基板を備えている。この基板には、後述する通り、支持基板12側に突出した複数の櫛歯部16Aが設けられている(図4参照)。上部ブレーキ電極22は平面視が短冊状の基板を備えている。この基板には、後述する通り、支持基板12側に突出した単数又は複数の櫛歯部22Aが設けられている(図4参照)。上部ブレーキ電極22の長手方向の基板側面が、誘電体26を介して固定電極16の長手方向の基板側面に接合されている。即ち、固定電極16、誘電体26、及び上部ブレーキ電極22は、平面視が矩形状の部材として一体に形成されている。上部ブレーキ電極22が付設された固定電極16の面積は、対向する駆動電極14の面積とほぼ同じ大きさとされている。固定電極16及び上部ブレーキ電極22は、同じ導電性材料で形成することができる。導電性材料としては、半導体プロセスで一般的に使用されている材料を使用することができる。

【0039】

本実施の形態では、上部ブレーキ電極22が付設された固定電極16の面積を300μm×300μmとしている。固定電極16及び上部ブレーキ電極22の厚さは約1.4μmである。基板の厚さが約0.2μmで、櫛歯部の高さが約1.2μmであり、合計の厚さが約1.4μmとなる。また、固定電極16及び上部ブレーキ電極22用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。誘電体26には、窒化シリコン(Si3N4)が用いられている。

【0040】

可動電極18及び下部ブレーキ電極24は、平面視が矩形状の部材として導電性材料で一体に形成されている。導電性材料としては、半導体プロセスで一般的に使用されている材料を使用することができる。固定電極16と可動電極18とは同じ材料で形成されていることが好ましい。この部材の内、固定電極16に対向する部分が可動電極18であり、上部ブレーキ電極22に対向する部分が下部ブレーキ電極24である。この部材は平面視が矩形状の基板を備えている。この基板には、後述する通り、固定電極16側に突出した複数の櫛歯部18Aと、上部ブレーキ電極22側に突出した単数又は複数の櫛歯部24Aとが設けられている(図4参照)。櫛歯部が形成された可動電極18及び下部ブレーキ電極24の表面は、誘電体層28で被覆されている。下部ブレーキ電極24が付設された可動電極18の面積は、対向する駆動電極14の面積とほぼ同じ大きさとされている。

【0041】

本実施の形態では、下部ブレーキ電極24が付設された可動電極18の面積を300μm×300μmとしている。可動電極18及び下部ブレーキ電極24の厚さは約1.4μmである。基板の厚さが約0.2μmで、櫛歯部の高さが約1.2μmであり、合計の厚さが約1.4μmとなる。誘電体層28の厚さは約0.1μmである。また、可動電極18及び下部ブレーキ電極24用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。誘電体層28には、窒化シリコン(Si3N4)が用いられている。

【0042】

上部ブレーキ電極22が付設された固定電極16は、支持基板12上に立設された複数の支柱30により支持されて、支持基板12から所定の高さに固定配置されている。支柱30の本数は3本以上が好ましい。複数の支柱30は、固定電極16と同じ導電性材料で形成することができる。本実施の形態では、支柱30用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。固定電極16は、支持基板12から約5μmの高さに配置されている。

【0043】

支持基板12の四隅の各々には、柱状のアンカー部32が立設されている。即ち、支持基板12上には、4本のアンカー部32が立設されている。4本のアンカー部32間には、長尺状の梁部34が架け渡されている。長尺状の梁部34は、可動電極18等を取り囲むように架け渡されている。本実施の形態では、幅1.4μmの長尺状の梁部34が、支持基板12から約3.5μmの高さに架け渡されている。

【0044】

下部ブレーキ電極24が付設された可動電極18は、複数のばね部材36により梁部34に連結されている。下部ブレーキ電極24が付設された可動電極18は、ばね部材36により梁部34に連結されることで、駆動電極14と固定電極16との間において、垂直方向及び水平方向に移動可能に保持されている。

【0045】

本実施の形態では、下部ブレーキ電極24及び可動電極18は、4個のばね部材36によって、長尺状の梁部34と同じ高さ(即ち、支持基板12から約3.5μmの高さ)に保持されている。アンカー部32、梁部34、及びばね部材36は、保持される可動電極18と同じ導電性材料で形成することができる。本実施の形態では、アンカー部32、梁部34、及びばね部材36用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。

【0046】

なお、支持基板12に平行な面内方向を水平方向とし、支持基板12に垂直な方向を垂直方向とする。面内方向において、矩形状の支持基板12の一辺が延びる方向をX方向とし、これに直交する方向をY方向とする。X方向及びY方向の各々に直交する方向がZ方向である。図1に示す斜視図では、Z方向の寸法を30倍に拡大して図示している。また、図3に示す側面図では、可動電極18は梁部34の背後にあり、固定電極16と可動電極18との間に介在する誘電体層28が模式的に表されている。

【0047】

<櫛型電極の構造>

次に、図4、図5を参照して、櫛型電極の構造を説明する。図4は図2に示す可変容量素子のX−X線断面図である。図5(A)は図2に示す領域Aでの櫛歯部の嵌合状態を示す図である。図2に示す領域Aは、誘電体26の近傍の約3μm×約10μmの小領域であり、図4では領域Bに相当する。図5(B)は図2に示す領域Aでの対向電極の分解斜視図である。

【0048】

図4に示すように、固定電極16には、複数の櫛歯部16Aが設けられている。上部ブレーキ電極22には、単数又は複数の櫛歯部22Aが設けられている。図4では、3個の櫛歯部16Aと1個の櫛歯部22Aとが図示されている。また、可動電極18には、複数の櫛歯部18Aが設けられている。下部ブレーキ電極24には、単数又は複数の櫛歯部24Aが設けられている。図4では、3個の櫛歯部18Aと2個の櫛歯部24Aとが図示されている。

【0049】

図5(B)に示すように、三次元構造で表すと、櫛歯部の各々は、誘電体26の長さ方向(図2ではY方向)に対し平行に延びた長尺状の板体である。例えば、可動電極18の櫛歯部18Aであれば、長尺状の板体である櫛歯部18Aは、Y方向に対し平行に延び且つ可動電極18の基板に対し直角を成すように、基板に設けられている。本実施の形態では、櫛歯部16A、櫛歯部18A、櫛歯部22A、及び櫛歯部24Aの各々は、高さ1.2μm、幅0.5μmで基板から突出している。また、同じ基板の隣接する2個の櫛歯部の離間距離は約0.9μmである。

【0050】

また、図4及び図5(A)に示すように、電極間に電圧を印加する前の初期状態では、可動電極18側の櫛歯部18A及び櫛歯部24Aの各々が、固定電極16側の櫛歯部16A及び櫛歯部22Aの間隙(櫛歯部が設けられていない領域)に対向するように、下部ブレーキ電極24が付設された可動電極18が所定位置に保持されている。

【0051】

これにより、可動電極18が固定電極16側に向って垂直方向に移動しても、可動電極18の櫛歯部18Aは、固定電極16側の隣接する2個の櫛歯部16Aの間隙に侵入することができる。また、下部ブレーキ電極24の櫛歯部24Aは、固定電極16側の櫛歯部16A及び櫛歯部22Aの間隙に侵入することができる。本実施の形態では、例えば、櫛歯部16Aと櫛歯部18Aのように、対向電極の櫛歯部が嵌合された状態では、対向する櫛歯部間の距離は約0.1μmである。

【0052】

上述した通り、櫛歯部が形成された可動電極18及び下部ブレーキ電極24の表面は、誘電体層28で被覆されている。従って、可動電極18と固定電極16との間には誘電体層28が必ず介在し、可動電極18の移動により両電極間が短絡されることはない。同様に、上部ブレーキ電極22と下部ブレーキ電極24との間には誘電体層28が必ず介在し、下部ブレーキ電極24の移動により両電極間が短絡されることはない。

【0053】

駆動電極14と可動電極18とは、両電極間に駆動電圧V1を印加する電源40に接続されている。また、上部ブレーキ電極22と下部ブレーキ24電極とは、両電極間にブレーキ電圧V2を印加する電源42に接続されている。なお、下部ブレーキ電極24及び可動電極18は、ばね部材36、梁部34、及びアンカー部32を介して、電源42に接続されると共に接地されている。従って、下部ブレーキ電極24と可動電極18とは、共に接地されてグランド電位となる。

【0054】

<可変容量素子の動作>

(1)可変容量素子の容量調整動作

まず、図6〜図9を参照して可変容量素子の容量調整動作を説明する。図6は図4に示す領域Bの部分拡大図である。図7(A)は可変容量素子の容量調整動作を説明する図であり、図7(B)はチューナブル・キャパシタの電圧依存性を示すグラフである。図8はチューナブル・キャパシタの動作の様子を示す断面図であり、図9はチューナブル・キャパシタの動作の様子を示す立体図である。

【0055】

図6に示すように、可変容量素子10は、機能面から見ると、振動防止部としてのブレーキ・キャパシタ20、可変容量としてのチューナブル・キャパシタ44、及び電極駆動部としての駆動キャパシタ46の3種類のキャパシタから構成されている。ブレーキ・キャパシタ20は、上部ブレーキ電極22と下部ブレーキ電極24とで構成されている。チューナブル・キャパシタ44は、固定電極16と可動電極18とで構成されている。駆動キャパシタ46は、駆動電極14と可動電極18及び下部ブレーキ電極24とで構成されている。ここで、チューナブル・キャパシタ44の容量を「C」とする。

【0056】

図7(A)に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46にV1の正電圧を印加する。駆動電極14及び可動電極18の間には、電源40から駆動電圧V1が印加される。これにより、駆動キャパシタ46の垂直方向の電極間距離が減少し、可動電極18が駆動電極14側に移動する。また、実線で囲んだチューナブル・キャパシタ44の対向電極面積が減少し、固定電極16と可動電極18との対向距離が増加する。これにより、チューナブル・キャパシタ44の容量Cが小さくなる。

【0057】

図7(B)に示すように、チューナブル・キャパシタ44の電極間距離dは、駆動電圧V1に依存して変化する。ここで、横軸が駆動電圧V1[V]であり、縦軸が固定電極16と可動電極18との電極間距離d[μm]である。図から分かるように、駆動電圧V1が0V〜3Vまで増加するに従い、垂直方向の電極間距離dは0μm〜1.2μmまで増加する。

【0058】

なお、駆動電圧V1と電極間距離dとの関係は、下記式(1)〜(4)から導出される下記式(5)に従って求めたものである。

【0059】

「U」は可動電極18と駆動電極14との間のエネルギーであり、下記式(1)で表される。

【0060】

【数1】

【0061】

「F」は可動電極18と駆動電極14との間の静電力であり、下記式(2)で表される。

【0062】

【数2】

【0063】

「k」は梁部34及びばね部材36のばね定数であり、下記式(3)で表される。ばね定数kの値は、梁部34及びばね部材36の形状や長さによって適宜設計できる。ここではk=0.6N/mとする。

【0064】

【数3】

【0065】

上記式(2)及び式(3)から、下記式(4)が導出される。

【0066】

【数4】

【0067】

上記式(1)〜(4)に基づいて、駆動電圧V1と電極間距離dとの関係は、下記式(5)で表される。

【0068】

【数5】

【0069】

なお、上記式(1)〜(5)において、「d」は可動電極18の変位、即ち、固定電極16と可動電極18との電極間距離である。「d0」はV1=0V時の可動電極18と駆動電極14との間の電極間距離であり、ここではd0=3.3μmとする。「S」は可動電極18の面積であり、ここでは300μm×300μmとする。「ε」は真空誘電率であり、ε=8.85E−12F/mとする。「K」は真空の比誘電率であり、ここでは1とする。本実施の形態におけるその他の各部材の「長さ、厚さ、距離」は、上述した通りである。

【0070】

上記式(5)からも分かるように、駆動電圧V1が0Vでは、図8(A)及び図9(A)に示すように、電極間距離dは約0μmである。このとき、容量Cは20.7pFとなる。一方、駆動電圧V1が2.83Vでは、図8(B)及び図9(B)に示すように、電極間距離dは約1.1μmである。このとき、容量Cは5.9pFとなる。このような動作により、チューナブル・キャパシタ44の容量Cの大きさが調整される。なお、容量Cの値はシミュレーションにより得られた値である。

【0071】

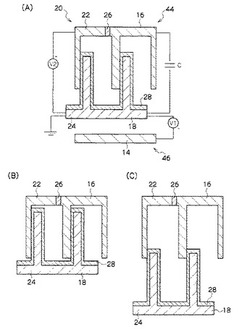

(2)可変容量素子の振動防止動作

次に、図10及び図11を参照して可変容量素子の振動防止動作を説明する。図10(A)〜(C)はブレーキ・キャパシタが可動電極の振動を防止する様子を示す図である。図11(A)〜(C)はブレーキ・キャパシタの動作下でのチューナブル・キャパシタの特性を示すグラフである。

【0072】

上述した通り、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46にV1の正電圧を印加すると、可動電極18が駆動電極14側に移動して、チューナブル・キャパシタ44の容量Cが小さくなる(図6、図7参照)。図7に示すように、可動電極18は静電力により所定位置に保持されているが、この状態のままでは、外部振動を受けて可動電極18が振れるおそれがある。この振動を防止するために、上部ブレーキ電極22及び下部ブレーキ電極24の間に、電源42からブレーキ電圧V2が印加される。

【0073】

図10(A)に示すように、ブレーキ電圧V2が印加されると、ブレーキ・キャパシタ20の下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との水平方向の電極間距離が0μmになる。下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との水平方向の電極間距離も0μmになる。即ち、各対向電極は誘電体層28を介して接触することになる。

【0074】

これによって、可動電極18と固定電極16とを大面積で接触させることが可能になると共に、電極間での摩擦力によって可動電極18を所定位置に安定に維持することができる。また、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0075】

例えば、図8(A)に示すように、駆動電圧V1が0Vで電極間距離dが約0μmの状態で3Vのブレーキ電圧V2が印加されると、図10(B)に示すように、下部ブレーキ電極24及び可動電極18は垂直方向の位置を維持したまま水平方向に移動し、対向電極は誘電体層28を介して接触することになり、摩擦力によりこの位置に固定される。

【0076】

同様に、図8(B)に示すように、駆動電圧V1が2.83Vで電極間距離dが約1.1μmの状態で3Vのブレーキ電圧V2が印加されると、図10(C)に示すように、下部ブレーキ電極24及び可動電極18は垂直方向の位置を維持したまま水平方向に移動し、対向電極は誘電体層28を介して接触することになり、摩擦力によりこの位置に固定される。

【0077】

図11(A)に示すように、チューナブル・キャパシタ44の電極間距離dは、駆動電圧V1に依存して変化する。ここで、横軸が駆動電圧V1[V]であり、縦軸が固定電極16と可動電極18との電極間距離d[μm]である。図から分かるように、駆動電圧V1が0V〜3Vまで増加するに従い、電極間距離dは0μm〜1.2μmまで増加する。

【0078】

また、図11(B)に示すように、駆動電圧V1に応じて電極間距離dが変化している場合にブレーキ電圧V2が印加されると、チューナブル・キャパシタ44の容量Cは、電極間距離dに依存して変化する。ここで、横軸が電極間距離d[μm]であり、縦軸が容量C[pF]である。図から分かるように、3Vのブレーキ電圧V2を印加する場合には、電極間距離dが0μm〜1.2μmまで増加するに従い、容量Cは約60pF〜約10pFまで減少する。

【0079】

実際に動作させて、チューナブル・キャパシタ44の容量Cと駆動電圧V1との関係を測定すると、図11(C)に示すように、3Vのブレーキ電圧V2を印加した場合には、駆動電圧V1が0Vから3Vまで増加するに従い、チューナブル・キャパシタ44の容量Cは、約60pFから約10pFまで減少する。ブレーキ電圧V2が0Vでは、駆動電圧V1が0Vで容量Cは20.7pFであり、駆動電圧V1が2.83Vで容量Cは5.9pFとなる。これと比較すると、3Vのブレーキ電圧V2を印加した場合には、チューナブル・キャパシタ44の容量Cは2〜3倍に増加する。即ち、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0080】

<可変容量素子の製造工程>

次に、図12及び図13を参照して、第1の実施の形態に係る可変容量素子の製造方法を説明する。ここでは、図4に領域Bで示す部分について製造工程の一例を示す。

【0081】

まず、図12(A)に示すように、支持基板12であるシリコン基板上に、例えばLP−CVD(Low Pressure CVD:減圧化学気相成長)法等の既知の方法を用いて、厚さ500nmの窒化シリコン(Si3N4)絶縁層13を成膜する。このSi3N4絶縁層13上に、例えばスパッタリング等の既知の方法を用いて、厚さ200nmのタングステンシリサイド(WSi2)を成膜して、WSi2駆動電極14を形成する。次に、図12(B)に示すように、WSi2駆動電極14上に、例えばLP−CVD法等の既知の方法を用いて、酸化シリコン(SiO2)層を3.3μmの厚さに堆積して、SiO2犠牲膜15を成膜する。

【0082】

次に、図12(C)に示すように、SiO2犠牲膜15上に、例えばLP−CVD法等の既知の方法を用いて、可動電極18等を形成するために、厚さ1.4μmの多結晶シリコン(Poly-Si)層17を成膜する。Poly-Si層17には燐(P)をドープする。燐をドープするために、原料ガスはSiH4以外に、不純物ガスとしてPH3を同時に導入する。燐をドープすることでPoly-Siの抵抗を低くすることができる。燐をドープしたPoly-Siは導体と見なすことができる。例えば、燐を5E20/cm3でドープした場合、620℃で成膜したPoly-Si膜の抵抗率は70mΩ・cmである。

【0083】

次に、図12(D)に示すように、Poly-Si層17を、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等、既知の方法で櫛歯状にパターニングして、可動電極18(櫛歯部18A)及び下部ブレーキ電極24(櫛歯部24A)を形成する。エッチング工程では、約1.2μmの深さまでエッチングする。

【0084】

次に、図12(E)に示すように、Poly-Si層17をパターニングして形成された可動電極18及び下部ブレーキ電極24の表面に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4層を成膜し、Si3N4誘電体層28を形成する。

【0085】

次に、図12(F)に示すように、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等の既知の方法で、Poly-Si層(可動電極18及び下部ブレーキ電極24)及びSi3N4誘電体層28を所定パターンで除去して、SiO2犠牲膜15を露出させ、リリースホール19を形成する。

【0086】

次に、図12(G)に示すように、例えばLP−CVD法等の既知の方法を用いて、Si3N4誘電体層28で被覆された可動電極18及び下部ブレーキ電極24の表面上に、SiO2犠牲膜15を更に0.1μmの厚さで成膜する。リリースホール19も、SiO2犠牲膜15で埋められる。次に、図12(H)に示すように、固定電極16等を形成するために、例えばLP−CVD法等の既知の方法を用いて、厚さ1.4μmのPoly-Si層21を堆積する。

【0087】

次に、図13(I)に示すように、例えばCMP(Chemical Mechanical Polishing:化学機械研磨)等の既知の方法を用いて、Poly-Si層21の表面を平坦化する。次に、図13(J)に示すように、誘電体26(絶縁部)を埋め込むために、ドライエッチングにより、Poly-Si層21を所定パターンで除去して、溝部23を形成する。

【0088】

次に、図13(K)に示すように、溝部23が形成されたPoly-Si層21の表面上に、厚さが200nmのSi3N4層25を成膜する。次に、図13(L)に示すように、Poly-Si層21の表面が露出するまでエッチングを行い、余分のSi3N4層25を除去して、Si3N4誘電体26を埋め込み形成する。次に、図13(M)に示すように、Poly-Si層21の表面を所定パターンで除去して、SiO2犠牲膜15をリリースするためのリリースホール27を形成する。

【0089】

最後に、図13(N)に示すように、固定電極16(櫛歯部16A)及び上部ブレーキ電極22(櫛歯部22A)を形成するために、SiO2犠牲膜15を既知の方法でリリースする。例えば、フッ酸に浸漬してSiO2犠牲膜15をウェットエッチングにより除去する。Si3N4はフッ酸にはほとんど溶解しないため、SiO2犠牲膜15だけを選択的に除去できる。

【0090】

この工程により、可動電極18(櫛歯部18A)及び下部ブレーキ電極24(櫛歯部24A)は、固定電極16(櫛歯部16A)及び上部ブレーキ電極22(櫛歯部22A)から切り離されると共に、駆動電極14からも切り離されて、自由に移動できるようになる。

【0091】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、可動電極側の櫛歯部と駆動電極側の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により可動電極の位置が固定され、外部振動による可動電極の振動が防止される。これにより、チューナブル・キャパシタを、所望の容量Cで安定に動作させることができる。

【0092】

また、本実施の形態では、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。

【0093】

また、本実施の形態では、上部ブレーキ電極及び固定電極は一体に形成されているので、上部ブレーキ電極及び固定電極を別々に形成する場合と比較すると、可変容量素子の作製工程がより簡単になる。

【0094】

(第2の実施の形態)

図14(A)〜(C)は本発明の第2の実施の形態に係る可変容量素子の部分拡大図である。図14(A)は第1の実施の形態の図6に対応する図である。第2の実施の形態に係る可変容量素子10Aは、下部ブレーキ電極24が付設された可動電極18の裏面側に、絶縁層50を介して可動駆動電極52が形成されている以外は、第1の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を一部省略する。

【0095】

図14(A)に示すように、可動電極18及び下部ブレーキ電極24は、平面視が矩形状の部材として導電性材料で一体に形成されている。この部材の内、固定電極16に対向する部分が可動電極18であり、上部ブレーキ電極22に対向する部分が下部ブレーキ電極24である。この部材は平面視が矩形状の基板を備えている。

【0096】

この基板の表面側には、固定電極16側に突出した複数の櫛歯部18Aと、上部ブレーキ電極22側に突出した単数又は複数の櫛歯部24Aとが設けられている。櫛歯部が形成された可動電極18及び下部ブレーキ電極24の表面は、誘電体層28で被覆されている。一方、基板の裏面側には、絶縁層50を介して可動駆動電極52が形成されている。即ち、可動電極18、下部ブレーキ電極24、絶縁層50、及び可動駆動電極52は、一体に形成されている。

【0097】

下部ブレーキ電極24が付設された可動電極18の面積は、対向する駆動電極14の面積とほぼ同じ大きさとされている。また、絶縁層50を介して形成された可動駆動電極52の面積も、対向する駆動電極14の面積とほぼ同じ大きさとされている。

【0098】

本実施の形態では、下部ブレーキ電極24が付設された可動電極18の面積、絶縁層50を介して形成された可動駆動電極52の面積は、各々300μm×300μmとされている。可動電極18及び下部ブレーキ電極24の厚さは約1.25μmである。基板の厚さが約0.05μmで、櫛歯部の高さが約1.2μmであり、合計の厚さが約1.25μmとなる。誘電体層28の厚さは約0.1μmである。絶縁層50の厚さは約0.1μmである。可動駆動電極52の厚さは約0.05μmである。

【0099】

また、本実施の形態では、可動電極18、下部ブレーキ電極24、及び可動駆動電極52用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。誘電体層28及び絶縁層50には、窒化シリコン(Si3N4)が用いられている。

【0100】

第1の実施の形態と同様に、可変容量素子10Aは、機能面から見ると、ブレーキ・キャパシタ20、チューナブル・キャパシタ44、及び駆動キャパシタ46Aの3種類のキャパシタから構成されている。本実施の形態では、駆動キャパシタ46Aは、駆動電極14と可動駆動電極52とで構成されている。

【0101】

図14(B)に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46AにV1の正電圧を印加する。駆動電極14及び可動駆動電極52の間には、電源40から駆動電圧V1が印加される。これにより、駆動キャパシタ46Aの垂直方向の電極間距離が減少し、可動電極18が可動駆動電極52と共に駆動電極14側に移動する。

【0102】

また、チューナブル・キャパシタ44の対向電極面積が減少し、固定電極16と可動電極18との対向距離も増加する。これにより、チューナブル・キャパシタ44の容量Cが小さくなる。本実施の形態では、駆動キャパシタ46Aの可動駆動電極52は、チューナブル・キャパシタ44の可動電極18と、絶縁層50により絶縁され、電気的に完全に分離されている。このため、チューナブル・キャパシタ44の動作時に、駆動電圧V1による影響(ノイズの発生等)が低減される。

【0103】

図14(C)に示すように、振動防止動作を実施する場合には、ブレーキ・キャパシタ20にブレーキ電圧V2を印加する。上部ブレーキ電極22及び下部ブレーキ電極24の間には、電源42からブレーキ電圧V2が印加される。ブレーキ電圧V2が印加されると、下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との水平方向の電極間距離が0μmになる。下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との電極間距離も0μmになる。即ち、各対向電極は誘電体層28を介して接触することになる。

【0104】

これによって、第1の実施の形態と同様に、可動電極18と固定電極16とを大面積で接触させることが可能になると共に、電極間での摩擦力によって可動電極18を所定位置に安定に維持することができる。また、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0105】

次に、図15及び図16を参照して、第2の実施の形態に係る可変容量素子の製造方法を説明する。第1の実施の形態と同様の工程は、簡単に説明する。

【0106】

まず、図15(A)に示すように、支持基板12であるシリコン基板上に、厚さ500nmのSi3N4絶縁層13を成膜する。このSi3N4絶縁層13上に、厚さ200nmのWSi2を成膜して、WSi2駆動電極14を形成する。次に、図15(B)に示すように、WSi2駆動電極14上に、SiO2を3.3μmの厚さに堆積して、SiO2犠牲膜15を成膜する。

【0107】

次に、図15(C)に示すように、SiO2犠牲膜15上に、例えばLP−CVD法等の既知の方法を用いて、厚さ50nmのPoly-Si膜を成膜して、Poly-Si可動駆動電極52を形成する。このPoly-Si可動駆動電極52上に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4を成膜して、Si3N4絶縁層50を形成する。

【0108】

次に、図15(D)に示すように、Si3N4絶縁層50上に、可動電極18等を形成するために、1.4μmのPoly-Si層17を成膜する。Poly-Si層17には燐(P)をドープする。次に、図15(E)に示すように、Poly-Si層17を、櫛歯状にパターニングして、可動電極18(櫛歯部18A)及び下部ブレーキ電極24(櫛歯部24A)を形成する。エッチング工程では、約1.2μmの深さまでエッチングする。

【0109】

次に、図15(F)に示すように、Poly-Si層17をパターニングして形成された可動電極18及び下部ブレーキ電極24の表面に、厚さが0.1μmのSi3N4を成膜し、Si3N4誘電体層28を形成する。次に、図15(G)に示すように、Poly-Si可動駆動電極52、Si3N4絶縁層50、Poly-Si層(可動電極18及び下部ブレーキ電極24)及びSi3N4誘電体層28を所定パターンで除去して、SiO2犠牲膜15を露出させ、リリースホール19を形成する。次に、図15(H)に示すように、SiO2犠牲膜15を更に0.1μmの厚さで成膜する。リリースホール19もSiO2犠牲膜15で埋められる。

【0110】

次に、図16(I)に示すように、固定電極16等を形成するために、厚さ1.4μmのPoly-Si層21を堆積する。次に、図16(J)に示すように、Poly-Si層21の表面を平坦化する。次に、図16(K)に示すように、Poly-Si層21を所定パターンで除去して、溝部23を形成する。次に、図16(L)に示すように、溝部23を埋めるように、厚さが200nmのSi3N4層25を成膜する。次に、図16(M)に示すように、Poly-Si層21の表面が露出するまでエッチングを行い、余分のSi3N4層25を除去して、Si3N4誘電体26を埋め込み形成する。次に、図16(N)に示すように、Poly-Si層21の表面を所定パターンで除去して、SiO2犠牲膜15をリリースするためのリリースホール27を形成する。

【0111】

最後に、図16(O)に示すように、固定電極16及び上部ブレーキ電極22を形成するために、SiO2犠牲膜15をリリースする。この工程により、可動電極18、下部ブレーキ電極24、絶縁層50、及び可動駆動電極52は、固定電極16及び上部ブレーキ電極22から切り離されると共に、駆動電極14からも切り離されて、自由に移動できるようになる。

【0112】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、可動電極側の櫛歯部と駆動電極側の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により可動電極の位置が固定され、外部振動による可動電極の振動が防止される。これにより、チューナブル・キャパシタを、所望の容量Cで安定に動作させることができる。

【0113】

また、本実施の形態では、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。

【0114】

また、本実施の形態では、上部ブレーキ電極及び固定電極は一体に形成されているので、上部ブレーキ電極及び固定電極を別々に形成する場合と比較すると、可変容量素子の作製工程がより簡単になる。

【0115】

更に、本実施の形態では、駆動キャパシタの可動駆動電極は、チューナブル・キャパシタの可動電極と絶縁層により絶縁されているので、チューナブル・キャパシタの動作時に、駆動電圧V1による影響が低減される。

【0116】

(第3の実施の形態)

図17は本発明の第3の実施の形態に係る可変容量素子の側面図である。図18(A)〜(C)は本発明の第3の実施の形態に係る可変容量素子の部分拡大図である。図17は第1の実施の形態の図3に対応する図である。図18(A)は第1の実施の形態の図6に対応する図である。第3の実施の形態に係る可変容量素子10Bは、支持基板12上に、駆動電極14を覆うように誘電層60を設けた以外は、第1の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0117】

第1の実施の形態と同様に、駆動電極14は平面視が支持基板12よりひと回り小さい矩形状とされ、支持基板上12の中央部分に形成されている。支持基板12上には、この駆動電極14を覆うように、駆動電極14より厚膜の誘電層60が設けられている。本実施の形態では、駆動電極14の厚さは約0.2μmであり、誘電層60の厚さは約2.2μmである。また、駆動電極14用の導電性材料には、WSi2が用いられ、誘電層60には、Si3N4が用いられている。

【0118】

図18(A)に示すように、可変容量素子10Bは、機能面から見ると、第1の実施の形態と同様に、ブレーキ・キャパシタ20、チューナブル・キャパシタ44、及び駆動キャパシタ46Bの3種類のキャパシタから構成されている。本実施の形態では、駆動キャパシタ46Bは、駆動電極14と誘電層60と可動電極18とで構成されている。

【0119】

図18(B)に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46BにV1の正電圧を印加する。駆動電極14及び可動電極18の間には、電源40から駆動電圧V1が印加される。これにより、駆動キャパシタ46Bの電極間距離が減少し、可動電極18が駆動電極14側に移動する。また、チューナブル・キャパシタ44の対向電極面積が減少し、固定電極16と可動電極18との対向距離も増加する。これにより、チューナブル・キャパシタ44の容量Cが小さくなる。

【0120】

本実施の形態では、駆動電極14と可動電極18との間に誘電層60を挿入することで、駆動キャパシタ46Bの容量は第1の実施の形態に比べてかなり大きくなる。下記式(6)に示すように、駆動キャパシタ46Bのばね常数kは、梁部(梁部34及びばね部材36)の機械的ばね常数kmと、電気的ばね常数keとの和になる。

【0121】

【化6】

【0122】

下記式(7)から分かるように、駆動キャパシタ46Bの容量が増加すると、電気的ばね常数keも大きくなる。ここで、各パラメータは駆動キャパシタ46Bに関するものであり、Cは平行平板の容量、Vは平行平板への印加電圧、dは電極間距離である。

【0123】

【化7】

【0124】

これを利用すると、例えば、上記梁部の機械的ばね定数kmを低く設計することが困難な場合等には、誘電層60の厚さを変更することにより電気ばね常数keを制御して、駆動キャパシタ46Bのばね常数kを調整することができる。

【0125】

図18(C)に示すように、振動防止動作を実施する場合には、ブレーキ・キャパシタ20にブレーキ電圧V2を印加する。上部ブレーキ電極22及び下部ブレーキ電極24の間には、電源42からブレーキ電圧V2が印加される。ブレーキ電圧V2が印加されると、ブレーキ・キャパシタ20の下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との電極間距離が0μmになる。

【0126】

下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との電極間距離も0μmになる。即ち、両電極は誘電体層28を介して接触することになる。これによって、可動電極18と固定電極16とを大面積で接触させることが可能になると共に、電極間での摩擦力によって可動電極18の位置に安定に維持することができる。また、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0127】

第3の実施の形態に係る可変容量素子10Bは、以下に説明する工程以外は、第1の実施の形態と同様の製造工程により製造することができる。即ち、第1の実施の形態で例示した図12(A)に示す工程において、支持基板12であるシリコン基板上に厚さ500nmのSi3N4絶縁層13を成膜し、このSi3N4絶縁層13上に厚さ200nmのWSi2を成膜してWSi2駆動電極14を形成する。

【0128】

この後に、WSi2駆動電極14上に、例えばLP−CVD法等の既知の方法を用いて、厚さ2.2μmのSi3N4誘電層60を形成する。次に、図12(B)に示す工程において、Si3N4誘電層60上に、例えばLP−CVD法等の既知の方法を用いて、SiO2を1.1μmの厚さに堆積して、SiO2犠牲膜15を成膜する。

【0129】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、可動電極側の櫛歯部と駆動電極側の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により可動電極の位置が固定され、外部振動による可動電極の振動が防止される。これにより、チューナブル・キャパシタを、所望の容量Cで安定に動作させることができる。

【0130】

また、本実施の形態では、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。

【0131】

また、本実施の形態では、上部ブレーキ電極及び固定電極は一体に形成されているので、上部ブレーキ電極及び固定電極を別々に形成する場合と比較すると、可変容量素子の作製工程がより簡単になる。

【0132】

更に、本実施の形態では、駆動キャパシタの電極間に誘電層を挿入することで、駆動キャパシタの容量がかなり大きくなる。駆動キャパシタのばね常数は、梁部の機械的ばね常数と電気的ばね常数との和になる。駆動キャパシタの容量が増加すると電気的ばね常数も大きくなるので、これを利用すると、誘電層の厚さを変更することにより電気ばね常数を制御して、駆動キャパシタのばね常数を調整することができる。

【0133】

(第4の実施の形態)

図19(A)〜(C)は本発明の第4の実施の形態に係る可変容量素子の部分拡大図である。図19(A)は第1の実施の形態の図6に対応する図である。第4の実施の形態に係る可変容量素子10Cは、第2の実施の形態と同様に、下部ブレーキ電極24が付設された可動電極18の裏面側に、絶縁層50を介して可動駆動電極52が形成されると共に、第3の実施の形態と同様に、支持基板12上に、駆動電極14を覆うように誘電層60を設けた以外は、第1の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0134】

本実施の形態の可変容量素子は、第1〜第3の実施の形態に係る可変容量素子と同様に、外部振動による可動電極の振動が防止されることにより、チューナブル・キャパシタを、所望の容量で安定に動作させることができる。また、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。また、上部ブレーキ電極及び固定電極は一体に形成されているので、可変容量素子の作製工程がより簡単になる。

【0135】

また、第2の実施の形態と同様に、駆動キャパシタの可動駆動電極は、チューナブル・キャパシタの可動電極と絶縁層により絶縁されているので、チューナブル・キャパシタの動作時に、駆動電圧V1による影響が低減される。

【0136】

更に、第3の実施の形態と同様に、駆動キャパシタの容量が増加すると電気的ばね常数も大きくなることを利用して、誘電層の厚さを変更することにより電気ばね常数を制御して、駆動キャパシタのばね常数を調整することができる。

【0137】

(第5の実施の形態)

<可変容量素子の概略構成>

図20〜図22を参照して、第5の実施の形態に係る可変容量素子の構成を簡単に説明する。図20は本発明の第5の実施の形態に係る可変容量素子を固定電極側から見た平面図である。図21は図20に示す可変容量素子の側面図である。図22は図20に示す可変容量素子のY−Y線断面図である。

【0138】

可変容量素子70は、シリコン等の半導体で構成された支持基板72、支持基板72上に配置された駆動電極74、駆動電極74に対向するように離間配置された固定電極76、駆動電極74と固定電極76との間に移動可能に保持された可動電極78、及び可動電極78の移動後の振動を防止する振動防止部としての複数のブレーキ・キャパシタ80を備えている。

【0139】

本実施の形態では、一対のブレーキ・キャパシタ80が2組、合計4個のブレーキ・キャパシタ80が設けられている。一対のブレーキ・キャパシタ80は、図面上、固定電極76を挟んで左右対称に配置されている。ブレーキ・キャパシタ80の各々は、上部ブレーキ電極82と、電圧印加により上部ブレーキ電極82と接触する下部ブレーキ電極84と、で構成されている。

【0140】

支持基板72は平面視が矩形状の平板である。駆動電極74は導電性材料により形成された薄膜電極である。駆動電極74は絶縁層(図示せず)を介して支持基板上72上に成膜されている。駆動電極74は平面視が支持基板72よりひと回り小さい矩形状とされ、支持基板上72の中央部分に形成されている。

【0141】

本実施の形態では、支持基板72の面積を400μm×400μmとし、駆動電極74の面積を300μm×300μmとしている。また、駆動電極74用の導電性材料には、WSi2が用いられている。絶縁層(図示せず)には、Si3N4が用いられている。駆動電極74の厚さは約0.2μmである。

【0142】

固定電極76は平面視が矩形状の基板を備えている。この基板には、支持基板72側に突出した複数の櫛歯部76Aが設けられている。固定電極76の櫛歯部76Aは、図示するY方向に延びた長尺状の板体であり、固定電極76の基板に対し直角を成すように設けられている。

【0143】

上部ブレーキ電極82は平面視が短冊状の基板を備えている。上部ブレーキ電極82の基板は、長手方向がY方向を向くと共に、長手方向の基板側面が固定電極76のY方向に延びた基板側面と対向するように配置されている。即ち、上部ブレーキ電極82は、固定電極76とは別個の部材として構成されている。

【0144】

上部ブレーキ電極82の基板には、支持基板72側に突出した単数又は複数の櫛歯部82Aが設けられている。上部ブレーキ電極82の櫛歯部82Aは、図示するY方向に延びた長尺状の板体であり、上部ブレーキ電極82の基板に対し直角を成すように設けられている。

【0145】

固定電極76の面積は、対向する駆動電極74の面積とほぼ同じ大きさとされている。固定電極76及び上部ブレーキ電極82は、導電性材料で形成されている。本実施の形態では、固定電極76の面積を300μm×300μmとしている。また、固定電極76及び上部ブレーキ電極82用の導電性材料には、Poly-Siが用いられている。

【0146】

可動電極78は平面視が矩形状の基板を備えている。この基板には、固定電極76側に突出した複数の櫛歯部78Aが設けられている。可動電極78の櫛歯部78Aは、図示するY方向に延びた長尺状の板体であり、可動電極78の基板に対し直角を成すように設けられている。

【0147】

下部ブレーキ電極84は平面視が短冊状の基板を備えている。下部ブレーキ電極84の基板は、上部ブレーキ電極82の基板と丁度対向するように設けられている。この基板には、上部ブレーキ電極82側に突出した複数の櫛歯部84Aが設けられている。下部ブレーキ電極84の櫛歯部84Aは、Y方向に延びた長尺状の板体であり、下部ブレーキ電極84の基板に対し直角を成すように設けられている。

【0148】

可動電極78の面積は、対向する固定電極76の面積とほぼ同じ大きさとされている。可動電極78及び下部ブレーキ電極84は、導電性材料で形成されている。本実施の形態では、可動電極78の面積を300μm×300μmとしている。また、可動電極78及び下部ブレーキ電極84用の導電性材料には、Poly-Siが用いられている。

【0149】

また、一対のブレーキ・キャパシタ80に対応して、一対の下部ブレーキ電極84が設けられている。一対の下部ブレーキ電極84の各々は、フレキシブルな連結部材86を介して、可動電極78の両側に対称に連結されている。フレキシブルな連結部材86は、短冊状の基部86Bとこの基部86Bの両端に各々立設された棒状の側部86Sとで構成されている。可動電極78側を内側、下部ブレーキ電極84を外側とする。外側に配置された側部86Sの一端が、下部ブレーキ電極84の基板に連結されている。一方、内側に配置された側部86Sの一端が、可動電極78の基板に連結されている。

【0150】

即ち、下部ブレーキ電極84、連結部材86、及び可動電極78は一体に形成されている。しかしながら、一対の下部ブレーキ電極84の各々は、可動電極78の両側に対称に連結されており、水平方向を反対側に移動するので、可動電極78は双方から引っ張られる。その結果、連結部材86の外側の側部86Sが弾性変形して湾曲するだけで、連結部材86自体は移動せず、可動電極78も移動しない。従って、可動電極78を移動させずに、下部ブレーキ電極84だけを移動させることができる。

【0151】

櫛歯部が形成された可動電極78及び下部ブレーキ電極84の表面は、誘電体層88で被覆されている。本実施の形態では、誘電体層88には、Si3N4が用いられている。

【0152】

固定電極76は、支持基板72上に立設された複数の支柱90により支持されて、支持基板72から所定の高さに固定配置されている。また、上部ブレーキ電極82も、支持基板72上に立設された複数の支柱90により支持されて、固定電極76とほぼ同じ高さに固定配置されている。1個の部材を支える支柱90の本数は3本以上が好ましい。複数の支柱90は、固定電極76及び上部ブレーキ電極82と同様に導電性材料で形成されている。本実施の形態では、支柱90用の導電性材料には、Poly-Siが用いられている。

【0153】

支持基板72の四隅の各々には、柱状のアンカー部92が立設されている。即ち、支持基板72上には、4本のアンカー部92が立設されている。4本のアンカー部92間には、長尺状の梁部94が架け渡されている。長尺状の梁部94は、可動電極78等を取り囲むように架け渡されている。本実施の形態では、幅1.4μmの長尺状の梁部94が、支持基板72から約3.5μmの高さに架け渡されている。

【0154】

可動電極78は、複数のばね部材96により梁部94に連結されている。可動電極78は、ばね部材96により梁部94に連結されることで、駆動電極74と固定電極76との間において、垂直方向及び水平方向に移動可能に保持されている。本実施の形態では、下部ブレーキ電極84及び可動電極78は、4個のばね部材96によって、長尺状の梁部94と同じ高さ(即ち、支持基板72から約3.5μmの高さ)に保持されている。

【0155】

アンカー部92、梁部94、及びばね部材96は、保持される可動電極78と同様に導電性材料で形成されている。本実施の形態では、アンカー部92、梁部94、及びばね部材96用の導電性材料には、Poly-Siが用いられている。

【0156】

また、図22及び図23に示すように、電極間に電圧を印加する前の初期状態では、可動電極78側の櫛歯部78A及び櫛歯部84Aの各々が、固定電極76側の櫛歯部76A及び櫛歯部82Aの間隙(櫛歯部が設けられていない領域)に対向するように、下部ブレーキ電極84が連結された可動電極78が所定位置に保持されている。

【0157】

これにより、可動電極78が固定電極76側に向って垂直方向に移動しても、可動電極78の櫛歯部78Aは、固定電極76側の隣接する2個の櫛歯部76Aの間隙(又は、櫛歯部76Aと支柱90との間隙)に侵入することができる。また、下部ブレーキ電極84の櫛歯部84Aは、固定電極76側の隣接する2個の櫛歯部82Aの間隙(又は、櫛歯部82Aと支柱90との間隙)に侵入することができる。本実施の形態では、例えば、櫛歯部76Aと櫛歯部78Aのように、対向電極の櫛歯部が嵌合された状態では、隣接する櫛歯部間の距離は約0.1μmである。

【0158】

上述した通り、櫛歯部が形成された可動電極78及び下部ブレーキ電極84の表面は、誘電体層88で被覆されている。従って、可動電極78と固定電極76との間には誘電体層88が必ず介在し、可動電極78の移動により両電極間が短絡されることはない。同様に、上部ブレーキ電極82と下部ブレーキ電極84との間には誘電体層88が必ず介在し、下部ブレーキ電極84の移動により両電極間が短絡されることはない。

【0159】

駆動電極74と可動電極78とは、両電極間に駆動電圧V1を印加する電源100に接続されている。また、上部ブレーキ電極82と下部ブレーキ電極84とは、両電極間にブレーキ電圧V2を印加する電源102に接続されている。なお、下部ブレーキ電極84及び可動電極78は、電源102に接続されると共に接地されている。従って、下部ブレーキ電極84と可動電極78とは、共に接地されてグランド電位となる。

【0160】

また、可変容量素子70は、機能面から見ると、振動防止部としてのブレーキ・キャパシタ80、可変容量としてのチューナブル・キャパシタ104、及び電極駆動部としての駆動キャパシタ106の3種類のキャパシタから構成されている。ブレーキ・キャパシタ80は、上部ブレーキ電極82と下部ブレーキ電極84とで構成されている。チューナブル・キャパシタ104は、固定電極76と可動電極78とで構成されている。駆動キャパシタ106は、駆動電極74と可動電極78及び下部ブレーキ電極84とで構成されている。ここで、チューナブル・キャパシタ104の容量を「C」とする。

【0161】

<可変容量素子の動作>

(1)可変容量素子の容量調整動作

まず、図23を参照して可変容量素子の容量調整動作を説明する。

図23に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ106にV1の正電圧を印加する。駆動電極74及び可動電極78の間には、電源100から駆動電圧V1が印加される。これにより、駆動キャパシタ106の垂直方向の電極間距離が減少し、可動電極78が駆動電極74側に移動する。また、チューナブル・キャパシタ104の対向電極面積が減少し、固定電極76と可動電極78との対向距離も増加する。これにより、チューナブル・キャパシタ104の容量Cが小さくなる。

【0162】

(2)可変容量素子の振動防止動作

次に、図24を参照して可変容量素子の振動防止動作を説明する。

図24に示すように、振動防止動作を実施する場合には、ブレーキ・キャパシタ80にブレーキ電圧V2を印加する。上部ブレーキ電極82及び下部ブレーキ電極84の間には、電源102からブレーキ電圧V2が印加される。ブレーキ電圧V2が印加されると、下部ブレーキ電極84が水平方向を外側に移動して、上部ブレーキ電極82と下部ブレーキ電極84との水平方向の電極間距離が0μmになる。即ち、両電極は誘電体層88を介して接触することになる。

【0163】

一方、可動電極78の両側には、一対の下部ブレーキ電極84が2組連結されている。一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動しても、連結部材86の外側の側部86Sが弾性変形して湾曲するだけで、連結部材86自体は水平方向には移動せず、可動電極78は水平方向に移動しない。

【0164】

即ち、下部ブレーキ電極84が水平方向に移動して、上部ブレーキ電極82と下部ブレーキ電極84とが大面積で接触することで、電極間での摩擦力によって下部ブレーキ電極84を垂直方向の所定位置に安定に維持することができる。同時に、一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動することで、可動電極78に対する引張り力が相殺されて可動電極78は移動せず、可動電極78を水平方向の所定位置に安定に維持することができる。

【0165】

この通り、振動防止動作時に、下部ブレーキ電極84が水平方向に各々移動しても、チューナブル・キャパシタ104では、固定電極76と可動電極78との対向距離は変化しないので、チューナブル・キャパシタ104の容量Cを一定に維持することができる。

【0166】

<可変容量素子の製造工程>

次に、図25及び図26を参照して、第5の実施の形態に係る可変容量素子の製造方法を説明する。ここでは、図22に示す構成の左半分の部分について製造工程の一例を示す。

【0167】

まず、図25(A)に示すように、支持基板72であるシリコン基板上に、例えばLP−CVD法等の既知の方法を用いて、厚さ500nmのSi3N4絶縁層73を成膜する。このSi3N4絶縁層73上に、例えばスパッタリング等の既知の方法を用いて、厚さ200nmのWSi2を成膜して、WSi2駆動電極74を形成する。次に、図25(B)に示すように、WSi2駆動電極74上に、例えばLP−CVD法等の既知の方法を用いて、SiO2層を1.1μmの厚さに堆積して、SiO2犠牲膜75を成膜する。

【0168】

次に、図25(C)に示すように、連結部材86の基部86Bを形成するために、SiO2犠牲膜75上に、例えばLP−CVD法等の既知の方法を用いて、厚さ1.1μmのPoly-Si層77Aを成膜する。Poly-Si層77Aには燐をドープする。燐をドープするために、原料ガスはSiH4以外に、不純物ガスとしてPH3を同時に導入する。

【0169】

次に、図25(D)に示すように、Poly-Si層77Aを、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等、既知の方法で短冊状にパターニングして、連結部材86の基部86Bを形成する。その後、連結部材86の側部86Sを形成するために、連結部材86の基部86B及び露出したSiO2犠牲膜75上に、更に厚さ2.2μmのSiO2犠牲膜75を成膜する。

【0170】

次に、図25(E)に示すように、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等の既知の方法で、SiO2犠牲膜75を所定パターンで除去して、連結部材86の基部86Bに到達する2個のスルーホール86Hを形成する。

【0171】

次に、図25(F)に示すように、可動電極78等を形成するために、SiO2犠牲膜75上に、例えばLP−CVD法等の既知の方法を用いて、厚さ2.2μmのPoly-Si層77Bを成膜する。Poly-Si層77Bには燐をドープする。2個のスルーホール86Hも、Poly-Si層77Bで埋められて、連結部材86の側部86Sが形成される。また、例えばCMP等の既知の方法を用いて、Poly-Si層77Bの表面を1.4μmの厚さまで平坦化する。

【0172】

次に、図25(G)に示すように、Poly-Si層77Bを、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等、既知の方法でパターニングして、可動電極78(櫛歯部78A)及び下部ブレーキ電極84(櫛歯部84A)を形成する。エッチング工程では、約1.2μmの深さまでエッチングする。

【0173】

次に、図25(H)に示すように、Poly-Si層77Bをパターニングして形成された可動電極78及び下部ブレーキ電極84の表面に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4層を成膜し、Si3N4誘電体層88を形成する。

【0174】

次に、図26(I)に示すように、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等の既知の方法で、Poly-Si層(可動電極78及び下部ブレーキ電極84)及びSi3N4誘電体層88を所定パターンで除去して、SiO2犠牲膜75を露出させ、リリースホール79を形成する。

【0175】

次に、図26(J)に示すように、例えばLP−CVD法等の既知の方法を用いて、Si3N4誘電体層88で被覆された可動電極78及び下部ブレーキ電極84の表面上に、SiO2犠牲膜75を更に0.1μmの厚さで成膜する。リリースホール79もSiO2犠牲膜75で埋められる。

【0176】

次に、図26(K)に示すように、固定電極76等を形成するために、例えばLP−CVD法等の既知の方法を用いて、厚さ1.4μmのPoly-Si層81を堆積する。次に、図26(L)に示すように、SiO2犠牲膜75の表面が露出するまでエッチングを行い、余分のPoly-Si層81を所定パターンで除去して、SiO2犠牲膜75をリリースするためのリリースホール87を形成する。

【0177】

最後に、図26(M)に示すように、固定電極76(櫛歯部76A)及び上部ブレーキ電極82(櫛歯部82A)を形成するために、SiO2犠牲膜75を既知の方法でリリースする。例えば、フッ酸に浸漬してSiO2犠牲膜75をウェットエッチングにより除去する。この工程により、可動電極78及び下部ブレーキ電極84は、固定電極76及び上部ブレーキ電極82から切り離されると共に、駆動電極74からも切り離されて、自由に移動できるようになる。また、可動電極78と下部ブレーキ電極84とを連結する連結部材86が形成される。

【0178】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、下部ブレーキ電極が水平方向に移動して、上部ブレーキ電極の櫛歯部と下部ブレーキ電極の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により下部ブレーキ電極の垂直方向の位置が固定される。

【0179】

一対の下部ブレーキ電極の各々は、可動電極の両側に対称に連結されており、下部ブレーキ電極の各々は水平方向を反対側に移動するので、可動電極は双方から引っ張られる。その結果、連結部材の外側の側部が弾性変形して湾曲するだけで、可動電極は水平方向にも垂直方向にも移動しない。従って、外部振動による可動電極の振動が防止される。

【0180】

また、固定電極と可動電極との対向距離はブレーキ電圧V2の印加により変化しないので、チューナブル・キャパシタを、所望の容量Cで更に安定に動作させることができる。

【0181】

(第6の実施の形態)

図27は本発明の第6の実施の形態に係る可変容量素子の部分拡大図である。図27は第2の実施の形態の図14(A)に対応する図である。第6の実施の形態に係る可変容量素子70Aは、下部ブレーキ電極84及び可動電極78の裏面側に、絶縁層110を介して可動駆動電極112が形成されている以外は、第5の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0182】

この場合は、可動駆動電極112が、可動電極78に対向する固定部112A、下部ブレーキ電極84に対向する可動部112B、及び固定部112Aと可動部112Bとを連結するフレキシブルな連結部112Cから一体に構成されている。一対のブレーキ・キャパシタ80に対応した一対の可動部112Bの各々は、連結部112Cを介して可動部112Bの両側に対称に連結されている。

【0183】

フレキシブルな連結部112Cは、短冊状の基部112Cbと、この基部112Cbの両端に各々立設された棒状の側部112Csとで構成されている。外側に配置された側部112Csの一端が可動部112Bに連結されると共に、内側に配置された側部112Csの一端が固定部112Aに連結されている。一対の可動部112Bの各々は、固定部112Aの両側に対称に連結されており、水平方向を反対側に移動するので、固定部112Aは双方から引っ張られる。

【0184】

その結果、連結部112Cの外側の側部112Csが弾性変形して湾曲するだけで、連結部112C自体は移動せず、固定部112Aも移動しない。従って、第5の実施の形態と同様に、可動電極78を移動させずに、下部ブレーキ電極84だけを移動させることができる。

【0185】

図27に示す第6の実施の形態に係る可変容量素子70Aは、以下に説明する工程以外は、第5の実施の形態と同様の製造工程により製造することができる。即ち、第5の実施の形態で例示した図25(F)に示す工程に代えて、図28(A)に示すように、SiO2犠牲膜75上に、例えばLP−CVD法等の既知の方法を用いて、厚さ50nmのPoly-Si層膜を成膜して、Poly-Si可動駆動電極112(112A,112B、112C)を形成する。

【0186】

次に、図28(B)に示すように、可動駆動電極112上に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4膜を成膜して、Si3N4絶縁層110を形成する。このSi3N4絶縁層110上に、例えばLP−CVD法等の既知の方法を用いて、可動電極78等を形成するために、1.05μmのPoly-Si層77Bを成膜する。Poly-Si層77Bには燐(P)をドープする。

【0187】

図29は可変容量素子70Aの振動防止動作を説明する図である。

図29に示すように、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ106にV1の正電圧を印加すると、可動電極78が駆動電極74側に移動する。しかしながら、静電力により可動電極78が駆動電極74側に移動した状態のままでは、外部振動を受けて可動電極78が振れる恐れがある。この振動を防止するために、ブレーキ・キャパシタ80にブレーキ電圧V2を印加する。上部ブレーキ電極82及び下部ブレーキ電極84の間には、電源102からブレーキ電圧V2が印加される。

【0188】

ブレーキ電圧V2が印加されると、下部ブレーキ電極84が水平方向に移動して、上部ブレーキ電極82と下部ブレーキ電極84との水平方向の電極間距離が0μmになる。即ち、両電極は誘電体層88を介して接触することになる。これにより、下部ブレーキ電極84及び可動電極78の垂直方向の位置が固定される。

【0189】

一方、可動電極78の両側には、絶縁層110及び可動駆動電極112を介して、一対の下部ブレーキ電極84が2組連結されている。一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動しても、可動駆動電極112の連結部112Cの外側の側部112Csが弾性変形して湾曲するだけで、連結部112C自体は水平方向には移動せず、可動電極78は水平方向に移動しない。

【0190】

即ち、下部ブレーキ電極84が水平方向に移動して、上部ブレーキ電極82と下部ブレーキ電極84とが大面積で接触することで、電極間での摩擦力によって下部ブレーキ電極84を垂直方向の所定位置に安定に維持することができる。同時に、一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動することで、可動電極78に対する引張り力が相殺されて可動電極78は移動せず、可動電極78を水平方向の所定位置に安定に維持することができる。

【0191】

この通り、振動防止動作時に、下部ブレーキ電極84が水平方向に各々移動しても、チューナブル・キャパシタ104では、固定電極76と可動電極78との対向距離は変化しないので、チューナブル・キャパシタ104の容量Cを一定に維持することができる。

【0192】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、下部ブレーキ電極が水平方向に移動して、上部ブレーキ電極の櫛歯部と下部ブレーキ電極の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により下部ブレーキ電極の垂直方向の位置が固定される。

【0193】

一対の下部ブレーキ電極の各々は、可動電極の両側に対称に連結されており、下部ブレーキ電極の各々は水平方向を反対側に移動するので、可動電極は双方から引っ張られる。その結果、連結部材の外側の側部が弾性変形して湾曲するだけで、可動電極は水平方向にも垂直方向にも移動しない。従って、外部振動による可動電極の振動が防止される。

【0194】

また、固定電極と可動電極との対向距離はブレーキ電圧V2の印加により変化しないので、チューナブル・キャパシタを、所望の容量Cで更に安定に動作させることができる。

【0195】

また、第2の実施の形態と同様に、可変容量素子は、下部ブレーキ電極及び可動電極の裏面側に、絶縁層を介して可動駆動電極が形成された構成としたことで、駆動キャパシタの可動駆動電極を、チューナブル・キャパシタの可動電極と絶縁層により絶縁することができる。これにより、チューナブル・キャパシタの動作時に、駆動電圧V1による影響が低減される。

【0196】

なお、第5、第6の実施の形態において、第3の実施の形態と同様に、支持基板上に、駆動電極を覆うように誘電層を設けてもよい。例えば、図30は第5の実施の形態に係る可変容量素子70の支持基板72上に、駆動電極74を覆うように誘電層130を設けた図であり、図31は第6の実施の形態に係る可変容量素子70Aの支持基板72上に、駆動電極74を覆うように誘電層130を設けた図である。誘電層130を設けた以外は、第5、第6の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0197】

この構成によれば、駆動キャパシタの電極間に誘電層を挿入することで、駆動キャパシタの容量がかなり大きくなる。駆動キャパシタのばね常数は、梁部の機械的ばね常数と電気的ばね常数との和になる。駆動キャパシタの容量が増加すると電気的ばね常数も大きくなるので、これを利用すると、誘電層の厚さを変更することにより電気ばね常数を制御して、駆動キャパシタのばね常数を調整することができる。

【図面の簡単な説明】

【0198】

【図1】本発明の第1の実施の形態に係る可変容量素子の外観を示す斜視図である。

【図2】可変容量素子を固定電極側から見た平面図である。

【図3】可変容量素子の側面図である。

【図4】図2に示す可変容量素子のX−X線断面図である。

【図5】(A)は図2に示す領域Aでの櫛歯部の嵌合状態を示す図であり、(B)は図2に示す領域Aでの対向電極の分解斜視図である。

【図6】図4に示す領域Bの部分拡大図である。

【図7】(A)は可変容量素子の容量調整動作を説明する図であり、(B)はチューナブル・キャパシタの電圧依存性を示すグラフである。

【図8】チューナブル・キャパシタの動作の様子を示す断面図である。

【図9】チューナブル・キャパシタの動作の様子を示す立体図である。

【図10】(A)及び(B)はブレーキ・キャパシタが可動電極の振動を防止する動作する様子を示す図である。

【図11】(A)〜(C)はブレーキ・キャパシタの動作下でのチューナブル・キャパシタの特性を示す図である。

【図12】(A)〜(H)は第1の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図13】(I)〜(N)は第1の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図14】(A)〜(C)は本発明の第2の実施の形態に係る可変容量素子の部分拡大図である。

【図15】(A)〜(H)は第2の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図16】(I)〜(O)は第2の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図17】本発明の第3の実施の形態に係る可変容量素子の側面図である。

【図18】(A)〜(C)は本発明の第3の実施の形態に係る可変容量素子の部分拡大図である。

【図19】(A)〜(C)は本発明の第4の実施の形態に係る可変容量素子の部分拡大図である。

【図20】本発明の第5の実施の形態に係る可変容量素子を固定電極側から見た平面図である。

【図21】図20に示す可変容量素子の側面図である。

【図22】図20に示す可変容量素子のY−Y線断面図である。

【図23】可変容量素子の容量調整動作を説明する図である。

【図24】可変容量素子の振動防止動作を説明する図である。

【図25】(A)〜(H)は第5の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図26】(I)〜(M)は第5の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図27】本発明の第6の実施の形態に係る可変容量素子の部分拡大図である。

【図28】(A)及び(B)は第6の実施の形態に係る可変容量素子の製造方法を説明するため図である。

【図29】可変容量素子の振動防止動作を説明する図である。

【図30】第5の実施の形態の変形例の構成を示す図である。

【図31】第6の実施の形態の変形例の構成を示す図である。

【符号の説明】

【0199】

10 可変容量素子

10A 可変容量素子

10B 可変容量素子

10C 可変容量素子

12 支持基板

13 Si3N4絶縁層

14 駆動電極

15 SiO2犠牲膜

16 固定電極

16A 櫛歯部

17 Poly-Si層

18 可動電極

18A 櫛歯部

19 リリースホール

20 ブレーキ・キャパシタ

21 Poly-Si層

22 上部ブレーキ電極

22A 櫛歯部

23 溝部

24 下部ブレーキ電極

24A 櫛歯部

25 窒化シリコン(Si3N4)層

26 誘電体

27 リリースホール

28 誘電体層

30 支柱

32 アンカー部

34 梁部

36 ばね部材

40 電源

42 電源

44 チューナブル・キャパシタ

46 駆動キャパシタ

46A 駆動キャパシタ

46B 駆動キャパシタ

50 絶縁層

52 可動駆動電極

60 誘電層

70 可変容量素子

70A 可変容量素子

72 支持基板

73 Si3N4絶縁層

74 駆動電極

75 SiO2犠牲膜

76 固定電極

76A 櫛歯部

77A Poly-Si層

77B Poly-Si層

78 可動電極

78A 櫛歯部

79 リリースホール

80 ブレーキ・キャパシタ

81 Poly-Si層

82 上部ブレーキ電極

82A 櫛歯部

84 下部ブレーキ電極

84A 櫛歯部

86 連結部材

86H スルーホール

86B 基部

86S 側部

87 リリースホール

88 誘電体層

90 支柱

92 アンカー部

94 梁部

96 ばね部材

100 電源

102 電源

104 チューナブル・キャパシタ

106 駆動キャパシタ

110 絶縁層

112 可動駆動電極

112B 可動部

112A 固定部

112C 連結部

130 誘電層

【技術分野】

【0001】

本発明は、可変容量素子に係り、特に、MEMS(Micro Electro Mechanical System)技術を適用した可変容量素子に関する。

【背景技術】

【0002】

近年、携帯電話に代表される無線通信機器は著しい進化を遂げている。次世代の携帯電話では、多数の周波数帯を利用する。このため、複数の周波数を受信可能なRF(Radio Frequency)フロントエンドの開発が進められている。この場合に問題となるのが、部品点数の増加である。特に、キャパシタやインダクター等の受動部品は共通化が難しく、周波数の数が増える分だけ部品点数が増加する。部品点数が増加すると、RFフロントエンドの体積が大きくなり、コストも高くなるという問題が生じる。

【0003】

これらの問題を解決する技術として、部品の大幅な小型化を可能にするMEMS技術が注目されている。MEMS技術とは、機械的な微小構造を作成し、超小型のデバイスを作製するものである。例えば、1つのデバイスで複数のインピーダンスを持つことが可能なMEMS・チューナブル・キャパシタを作製することができる。

【0004】

MEMS・チューナブル・キャパシタを用いて、チューナブル整合回路を構成することができる。このチューナブル整合回路をRFフロントエンドに適用することで、各周波数やシステムごとに動的に回路そのものを再構成することが可能となり、アンテナの本数や個別増幅器の個数を大幅に減らすことが期待できる。このため、種々のMEMS・チューナブル・キャパシタが提案されている。

【0005】

例えば、特許文献1には、基板上に第1電極と第2電極とを固定配置し、電圧印加によりアクチュエータで可動電極を駆動して、可動電極との接触により第1電極と第2電極との間の容量を変化させるMEMS型の可変容量素子が記載されている。

【0006】

特許文献2には、櫛型の第1電極と第2電極とが上下方向に対向配置された微小可動構造体(MEMS)が記載されている。この微小可動構造体では、第1電極と第2電極との間に電圧が印加されると静電力により駆動力が発生する。可動電極である第2電極が上下方向に移動することで、静電力が作用する面積が変化して、静電容量が変化する。

【0007】

一方、携帯電話等の小型の無線通信機器には、約3Vのバッテリーが使用されている。従って、携帯電話等に適用するためには、動作電圧が3V以下の低電圧動作が可能なMEMS・チューナブル・キャパシタが必要になる。即ち、0V〜3Vの範囲で、静電容量を大幅に変化させなければならない。特許文献2に記載された微小可動構造体のように、櫛型電極を用いた場合には、静電力が作用する面積が大きくなり、静電容量の変動幅を増大できるという利点がある。

【0008】

特許文献3には、特許文献2と同様に、固定電極と可動電極とに櫛型電極を用いた電機機械式マイクロ可変容量ダイオード(MEMS)が記載されている。このMEMS可変容量ダイオードでは、固定電極と可動電極との間に電圧が印加されると、静電力により可動電極が移動して静電容量を変化させる。また、櫛型電極は、ミラー素子等の他のMEMSデバイスにも用いられている。例えば、特許文献4には、電圧印加により基台の第1櫛型電極と可動部の第2櫛型電極との間に静電力が働き、可動部が基台の方向に移動するマイクロアクチュエータが記載されている。

【0009】

【特許文献1】特開2006−261480号公報

【特許文献2】特開2005−224934号公報

【特許文献3】特表2006−518926号公報

【特許文献4】特開2005−341788号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

上述した通り、携帯電話等に適用するために、動作電圧が3V以下の低電圧動作が可能なMEMSデバイスとして、櫛型電極を用いたMEMS・チューナブル・キャパシタ(可変容量素子)が検討されている。しかしながら、これらの可変容量素子には、移動後の可動電極の位置を安定して維持できないという問題があった。可動電極は、静電力で所定位置に維持されているためである。外部振動により可動電極の位置が変動すると、静電容量が変化して動作が不安定になるという不具合を生じる。

【0011】

また、固定電極と可動電極とは、互いの櫛歯部が噛み合うように動作する。従って、動作時に外部振動を受けて固定電極と可動電極とが接触し、短絡する恐れがある。

【0012】

本発明は、上記問題を解決すべく成されたものであり、移動後の可動電極の位置を維持して、所望の静電容量で安定に動作させることができる、外部振動に強い構造の可変容量素子を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するために請求項1に記載の可変容量素子は、支持基板と、前記支持基板の表面に形成された薄膜状の第1電極と、前記第1電極の上方に固定配置されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第2電極と、前記第1電極と前記第2電極との間に配置され、前記第2電極に対して垂直方向及び水平方向に移動可能に保持されると共に、前記第2電極の複数の櫛歯部の間隙に対向し且つ第2電極側に突出する複数の櫛歯部を備え、表面が誘電体層で被覆された平板状の第3電極であって、前記第2電極と共に可変容量を構成し、前記第1電極と該第2電極の間に印加された第1電圧に応じて垂直方向に駆動される第3電極と、前記第1電極の上方に固定配置され、前記第2電極と水平方向に接続されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第4電極であって、前記第2電極とは電気的に絶縁された第4電極と、前記第1電極と前記第4電極との間に配置され、前記第3電極と水平方向に接続されると共に、前記第4電極の複数の櫛歯部の間隙に対向し且つ第4電極側に突出する少なくとも1つの櫛歯部を備え、表面が誘電体層で被覆された平板状の第5電極であって、前記第4電極と共に前記第3電極の振動を防止する振動防止部を構成し、前記第4電極と該第5電極との間に印加された第2電圧に応じて水平方向に駆動されて、前記第4電極の櫛歯部と該第5電極の櫛歯部とが接触して静電力により前記第4電極に固定される第5電極と、を備えたことを特徴としている。

【0014】

請求項2に記載の可変容量素子は、請求項1に記載の発明において、前記第3電極及び前記第5電極の前記第1電極と対向する面に絶縁膜を介して第6電極を更に形成し、該第6電極と前記第1電極との間に印加された第1電圧に応じて前記第3電極が垂直方向に駆動されることを特徴としている。

【0015】

請求項3に記載の可変容量素子は、請求項1又は2に記載の発明において、前記第1電極と前記第3電極及び第5電極との間に、前記電極間での静電容量を調整する誘電体層が設けられたことを特徴としている。

【0016】

請求項4に記載の可変容量素子は、請求項1〜3の何れか1項に記載の発明において、前記第2電極と前記4電極とが1枚の平板として形成されたことを特徴としている。

【0017】

請求項5に記載の可変容量素子は、支持基板と、前記支持基板の表面に形成された薄膜状の第1電極と、前記第1電極の上方に固定配置されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第2電極と、前記第1電極と前記第2電極との間に配置され、前記第2電極に対して垂直方向及び水平方向に移動可能に保持されると共に、前記第2電極の複数の櫛歯部の間隙に対向し且つ第2電極側に突出する複数の櫛歯部を備え、表面が誘電体層で被覆された平板状の第3電極であって、前記第2電極と共に可変容量を構成し、前記第1電極と該第2電極の間に印加された第1電圧に応じて垂直方向に駆動される第3電極と、前記第1電極の上方に固定配置され、前記第2電極に対し左右対称となるように前記第2電極と水平方向に接続されると共に、前記第1電極側に突出する複数の櫛歯部を備えた平板状の第4電極であって、前記第2電極とは電気的に絶縁された複数対の第4電極と、前記第1電極と前記第4電極との間に配置され、前記第3電極と水平方向に接続されると共に、前記第4電極の複数の櫛歯部の間隙に対向し且つ第4電極側に突出する少なくとも1つの櫛歯部を備え、表面が誘電体層で被覆された平板状の第5電極であって、前記複数対の第4電極の各々に対応して設けられ、前記複数対の第4電極の各々と共に前記第3電極の振動を防止する振動防止部を構成し、前記第4電極と該第5電極との間に印加された第2電圧に応じて一対の第5電極が水平方向を反対向きに駆動されて、前記第4電極の櫛歯部と該第5電極の櫛歯部とが接触して静電力により前記複数対の第4電極の各々に固定される複数対の第5電極と、を備えたことを特徴としている。

【0018】

請求項6に記載の可変容量素子は、請求項5に記載の発明において、前記第3電極及び前記第5電極の前記第1電極と対向する面に絶縁膜を介して第6電極を更に形成し、該第6電極と前記第1電極との間に印加された第1電圧に応じて前記第3電極が垂直方向に駆動されることを特徴としている。

【0019】

請求項7に記載の可変容量素子は、請求項5又は6に記載の発明において、前記第1電極と前記第3電極及び第5電極との間に、前記電極間での静電容量を調整する誘電体層が設けられたことを特徴としている。

【0020】

請求項8に記載の可変容量素子は、請求項5〜7の何れか1項に記載の発明において、前記第2電極と前記複数対の第4電極の各々とが別々の平板として形成されたことを特徴としている。

【0021】

請求項9に記載の可変容量素子は、請求項5〜8の何れか1項に記載の発明において、前記第3電極と前記複数対の第5電極の各々とは、可とう性を有する材料で形成されたU字状の接続部材で接続されたことを特徴としている。

【0022】

請求項10に記載の可変容量素子は、請求項1〜9の何れか1項に記載の発明において、前記支持基板が、半導体基板又は結晶基板であることを特徴としている。

【0023】

請求項11に記載の可変容量素子は、請求項1〜10の何れか1項に記載の発明において、前記支持基板が、シリコン基板又は酸化アルミニウム基板であることを特徴としている。

【発明の効果】

【0024】

各請求項に係る発明によれば、以下の効果がある。

【0025】

請求項1に係る発明によれば、第4電極及び第5電極から構成される振動防止部にブレーキ電圧(第2電圧)を印加することで、駆動電圧(第1電圧)を印加して移動させた後の可動電極(第3電極)の垂直方向の位置を固定し、外部振動による可動電極(第3電極)の振動を防止して、可変容量素子を所望の静電容量で安定に動作させることができる、という効果がある。

【0026】

請求項2、請求項6に係る発明によれば、可動電極(第3電極)と絶縁された可動駆動電極(第6電極)を設けることで、容量調整動作時における駆動電圧(第1電圧)による影響を低減して、可変容量素子を所望の静電容量で更に安定に動作させることができる、という効果がある。

【0027】

請求項3、請求項7に係る発明によれば、更に、可動電極(第3電極)と駆動電極(第1電極)との間に誘電体層を設けることで、誘電体層の厚さで可動電極(第3電極)を支持する梁部のばね定数を制御して、可変容量素子を所望の静電容量で動作させることができる、という効果がある。

【0028】

請求項4に係る発明によれば、上部ブレーキ電極(第4電極)及び固定電極(第2電極)を一体に形成することで、作製工程が簡単になる、という効果がある。

【0029】

請求項5に係る発明によれば、下部ブレーキ電極(第5電極)及び可動電極(第3電極)をフレキシブルな接続部材で接続した状態で振動防止部にブレーキ電圧(第2電圧)を印加することで、駆動電圧(第1電圧)を印加して移動させた後の可動電極(第3電極)の垂直方向及び水平方向の位置を固定し、外部振動による可動電極(第3電極)の振動を防止して、可変容量素子を所望の静電容量で更に安定に動作させることができる、という効果がある。

【0030】

請求項8に係る発明によれば、上部ブレーキ電極(第4電極)及び固定電極(第2電極)を別体に形成することで、下部ブレーキ電極(第5電極)及び可動電極(第3電極)を別体に形成することができる、という効果がある。

【0031】

請求項9に係る発明によれば、下部ブレーキ電極(第5電極)と可動電極(第3電極)とを、別々に動かすことが可能になる、という効果がある。

【0032】

請求項10、11に係る発明によれば、RFフロントエンドに適用するチューナブル整合回路を構成するのにより好適な可変容量素子を提供できる、という効果がある。

【発明を実施するための最良の形態】

【0033】

以下、図面を参照して本発明の実施の形態の一例を詳細に説明する。

【0034】

(第1の実施の形態)

<可変容量素子の概略構成>

まず、図1〜図3を参照して、可変容量素子の構成を簡単に説明する。図1は本発明の第1の実施の形態に係る可変容量素子の外観を示す斜視図である。図2は可変容量素子を固定電極側から見た平面図である。図3は可変容量素子の側面図である。

【0035】

可変容量素子10は、シリコン等の半導体で構成された支持基板12、支持基板12上に配置された駆動電極14、駆動電極14に対向するように離間配置された固定電極16、駆動電極14と固定電極16との間に移動可能に保持された可動電極18、及び可動電極18の移動後の振動を防止する振動防止部としてのブレーキ・キャパシタ20を備えている。ブレーキ・キャパシタ20は、上部ブレーキ電極22と、電圧印加により上部ブレーキ電極22と接触する下部ブレーキ電極24とで構成されている。

【0036】

支持基板12は平面視が矩形状の平板である。支持基板12としては、半導体プロセスで使用可能な基板であればよく、シリコン基板等の半導体基板の外、酸化アルミニウム(Al2O3)等の結晶基板を用いることができる。駆動電極14は導電性材料により形成された薄膜電極である。導電性材料としては、半導体プロセスで一般的に使用されている材料を使用することができる。駆動電極14は絶縁層(図示せず)を介して支持基板上12上に成膜されている。駆動電極14は平面視が支持基板12よりひと回り小さい矩形状とされ、支持基板上12の中央部分に形成されている。

【0037】

本実施の形態では、支持基板12の面積を400μm×400μmとし、駆動電極14の面積を300μm×300μmとしている。支持基板12としては、シリコン(Si)等の半導体基板が用いられている。また、駆動電極14用の導電性材料には、タングステンシリサイド(WSi2)が用いられている。絶縁層(図示せず)には、窒化シリコン(Si3N4)が用いられている。駆動電極14の厚さは約0.2μmである。

【0038】

固定電極16は平面視が矩形状の基板を備えている。この基板には、後述する通り、支持基板12側に突出した複数の櫛歯部16Aが設けられている(図4参照)。上部ブレーキ電極22は平面視が短冊状の基板を備えている。この基板には、後述する通り、支持基板12側に突出した単数又は複数の櫛歯部22Aが設けられている(図4参照)。上部ブレーキ電極22の長手方向の基板側面が、誘電体26を介して固定電極16の長手方向の基板側面に接合されている。即ち、固定電極16、誘電体26、及び上部ブレーキ電極22は、平面視が矩形状の部材として一体に形成されている。上部ブレーキ電極22が付設された固定電極16の面積は、対向する駆動電極14の面積とほぼ同じ大きさとされている。固定電極16及び上部ブレーキ電極22は、同じ導電性材料で形成することができる。導電性材料としては、半導体プロセスで一般的に使用されている材料を使用することができる。

【0039】

本実施の形態では、上部ブレーキ電極22が付設された固定電極16の面積を300μm×300μmとしている。固定電極16及び上部ブレーキ電極22の厚さは約1.4μmである。基板の厚さが約0.2μmで、櫛歯部の高さが約1.2μmであり、合計の厚さが約1.4μmとなる。また、固定電極16及び上部ブレーキ電極22用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。誘電体26には、窒化シリコン(Si3N4)が用いられている。

【0040】

可動電極18及び下部ブレーキ電極24は、平面視が矩形状の部材として導電性材料で一体に形成されている。導電性材料としては、半導体プロセスで一般的に使用されている材料を使用することができる。固定電極16と可動電極18とは同じ材料で形成されていることが好ましい。この部材の内、固定電極16に対向する部分が可動電極18であり、上部ブレーキ電極22に対向する部分が下部ブレーキ電極24である。この部材は平面視が矩形状の基板を備えている。この基板には、後述する通り、固定電極16側に突出した複数の櫛歯部18Aと、上部ブレーキ電極22側に突出した単数又は複数の櫛歯部24Aとが設けられている(図4参照)。櫛歯部が形成された可動電極18及び下部ブレーキ電極24の表面は、誘電体層28で被覆されている。下部ブレーキ電極24が付設された可動電極18の面積は、対向する駆動電極14の面積とほぼ同じ大きさとされている。

【0041】

本実施の形態では、下部ブレーキ電極24が付設された可動電極18の面積を300μm×300μmとしている。可動電極18及び下部ブレーキ電極24の厚さは約1.4μmである。基板の厚さが約0.2μmで、櫛歯部の高さが約1.2μmであり、合計の厚さが約1.4μmとなる。誘電体層28の厚さは約0.1μmである。また、可動電極18及び下部ブレーキ電極24用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。誘電体層28には、窒化シリコン(Si3N4)が用いられている。

【0042】

上部ブレーキ電極22が付設された固定電極16は、支持基板12上に立設された複数の支柱30により支持されて、支持基板12から所定の高さに固定配置されている。支柱30の本数は3本以上が好ましい。複数の支柱30は、固定電極16と同じ導電性材料で形成することができる。本実施の形態では、支柱30用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。固定電極16は、支持基板12から約5μmの高さに配置されている。

【0043】

支持基板12の四隅の各々には、柱状のアンカー部32が立設されている。即ち、支持基板12上には、4本のアンカー部32が立設されている。4本のアンカー部32間には、長尺状の梁部34が架け渡されている。長尺状の梁部34は、可動電極18等を取り囲むように架け渡されている。本実施の形態では、幅1.4μmの長尺状の梁部34が、支持基板12から約3.5μmの高さに架け渡されている。

【0044】

下部ブレーキ電極24が付設された可動電極18は、複数のばね部材36により梁部34に連結されている。下部ブレーキ電極24が付設された可動電極18は、ばね部材36により梁部34に連結されることで、駆動電極14と固定電極16との間において、垂直方向及び水平方向に移動可能に保持されている。

【0045】

本実施の形態では、下部ブレーキ電極24及び可動電極18は、4個のばね部材36によって、長尺状の梁部34と同じ高さ(即ち、支持基板12から約3.5μmの高さ)に保持されている。アンカー部32、梁部34、及びばね部材36は、保持される可動電極18と同じ導電性材料で形成することができる。本実施の形態では、アンカー部32、梁部34、及びばね部材36用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。

【0046】

なお、支持基板12に平行な面内方向を水平方向とし、支持基板12に垂直な方向を垂直方向とする。面内方向において、矩形状の支持基板12の一辺が延びる方向をX方向とし、これに直交する方向をY方向とする。X方向及びY方向の各々に直交する方向がZ方向である。図1に示す斜視図では、Z方向の寸法を30倍に拡大して図示している。また、図3に示す側面図では、可動電極18は梁部34の背後にあり、固定電極16と可動電極18との間に介在する誘電体層28が模式的に表されている。

【0047】

<櫛型電極の構造>

次に、図4、図5を参照して、櫛型電極の構造を説明する。図4は図2に示す可変容量素子のX−X線断面図である。図5(A)は図2に示す領域Aでの櫛歯部の嵌合状態を示す図である。図2に示す領域Aは、誘電体26の近傍の約3μm×約10μmの小領域であり、図4では領域Bに相当する。図5(B)は図2に示す領域Aでの対向電極の分解斜視図である。

【0048】

図4に示すように、固定電極16には、複数の櫛歯部16Aが設けられている。上部ブレーキ電極22には、単数又は複数の櫛歯部22Aが設けられている。図4では、3個の櫛歯部16Aと1個の櫛歯部22Aとが図示されている。また、可動電極18には、複数の櫛歯部18Aが設けられている。下部ブレーキ電極24には、単数又は複数の櫛歯部24Aが設けられている。図4では、3個の櫛歯部18Aと2個の櫛歯部24Aとが図示されている。

【0049】

図5(B)に示すように、三次元構造で表すと、櫛歯部の各々は、誘電体26の長さ方向(図2ではY方向)に対し平行に延びた長尺状の板体である。例えば、可動電極18の櫛歯部18Aであれば、長尺状の板体である櫛歯部18Aは、Y方向に対し平行に延び且つ可動電極18の基板に対し直角を成すように、基板に設けられている。本実施の形態では、櫛歯部16A、櫛歯部18A、櫛歯部22A、及び櫛歯部24Aの各々は、高さ1.2μm、幅0.5μmで基板から突出している。また、同じ基板の隣接する2個の櫛歯部の離間距離は約0.9μmである。

【0050】

また、図4及び図5(A)に示すように、電極間に電圧を印加する前の初期状態では、可動電極18側の櫛歯部18A及び櫛歯部24Aの各々が、固定電極16側の櫛歯部16A及び櫛歯部22Aの間隙(櫛歯部が設けられていない領域)に対向するように、下部ブレーキ電極24が付設された可動電極18が所定位置に保持されている。

【0051】

これにより、可動電極18が固定電極16側に向って垂直方向に移動しても、可動電極18の櫛歯部18Aは、固定電極16側の隣接する2個の櫛歯部16Aの間隙に侵入することができる。また、下部ブレーキ電極24の櫛歯部24Aは、固定電極16側の櫛歯部16A及び櫛歯部22Aの間隙に侵入することができる。本実施の形態では、例えば、櫛歯部16Aと櫛歯部18Aのように、対向電極の櫛歯部が嵌合された状態では、対向する櫛歯部間の距離は約0.1μmである。

【0052】

上述した通り、櫛歯部が形成された可動電極18及び下部ブレーキ電極24の表面は、誘電体層28で被覆されている。従って、可動電極18と固定電極16との間には誘電体層28が必ず介在し、可動電極18の移動により両電極間が短絡されることはない。同様に、上部ブレーキ電極22と下部ブレーキ電極24との間には誘電体層28が必ず介在し、下部ブレーキ電極24の移動により両電極間が短絡されることはない。

【0053】

駆動電極14と可動電極18とは、両電極間に駆動電圧V1を印加する電源40に接続されている。また、上部ブレーキ電極22と下部ブレーキ24電極とは、両電極間にブレーキ電圧V2を印加する電源42に接続されている。なお、下部ブレーキ電極24及び可動電極18は、ばね部材36、梁部34、及びアンカー部32を介して、電源42に接続されると共に接地されている。従って、下部ブレーキ電極24と可動電極18とは、共に接地されてグランド電位となる。

【0054】

<可変容量素子の動作>

(1)可変容量素子の容量調整動作

まず、図6〜図9を参照して可変容量素子の容量調整動作を説明する。図6は図4に示す領域Bの部分拡大図である。図7(A)は可変容量素子の容量調整動作を説明する図であり、図7(B)はチューナブル・キャパシタの電圧依存性を示すグラフである。図8はチューナブル・キャパシタの動作の様子を示す断面図であり、図9はチューナブル・キャパシタの動作の様子を示す立体図である。

【0055】

図6に示すように、可変容量素子10は、機能面から見ると、振動防止部としてのブレーキ・キャパシタ20、可変容量としてのチューナブル・キャパシタ44、及び電極駆動部としての駆動キャパシタ46の3種類のキャパシタから構成されている。ブレーキ・キャパシタ20は、上部ブレーキ電極22と下部ブレーキ電極24とで構成されている。チューナブル・キャパシタ44は、固定電極16と可動電極18とで構成されている。駆動キャパシタ46は、駆動電極14と可動電極18及び下部ブレーキ電極24とで構成されている。ここで、チューナブル・キャパシタ44の容量を「C」とする。

【0056】

図7(A)に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46にV1の正電圧を印加する。駆動電極14及び可動電極18の間には、電源40から駆動電圧V1が印加される。これにより、駆動キャパシタ46の垂直方向の電極間距離が減少し、可動電極18が駆動電極14側に移動する。また、実線で囲んだチューナブル・キャパシタ44の対向電極面積が減少し、固定電極16と可動電極18との対向距離が増加する。これにより、チューナブル・キャパシタ44の容量Cが小さくなる。

【0057】

図7(B)に示すように、チューナブル・キャパシタ44の電極間距離dは、駆動電圧V1に依存して変化する。ここで、横軸が駆動電圧V1[V]であり、縦軸が固定電極16と可動電極18との電極間距離d[μm]である。図から分かるように、駆動電圧V1が0V〜3Vまで増加するに従い、垂直方向の電極間距離dは0μm〜1.2μmまで増加する。

【0058】

なお、駆動電圧V1と電極間距離dとの関係は、下記式(1)〜(4)から導出される下記式(5)に従って求めたものである。

【0059】

「U」は可動電極18と駆動電極14との間のエネルギーであり、下記式(1)で表される。

【0060】

【数1】

【0061】

「F」は可動電極18と駆動電極14との間の静電力であり、下記式(2)で表される。

【0062】

【数2】

【0063】

「k」は梁部34及びばね部材36のばね定数であり、下記式(3)で表される。ばね定数kの値は、梁部34及びばね部材36の形状や長さによって適宜設計できる。ここではk=0.6N/mとする。

【0064】

【数3】

【0065】

上記式(2)及び式(3)から、下記式(4)が導出される。

【0066】

【数4】

【0067】

上記式(1)〜(4)に基づいて、駆動電圧V1と電極間距離dとの関係は、下記式(5)で表される。

【0068】

【数5】

【0069】

なお、上記式(1)〜(5)において、「d」は可動電極18の変位、即ち、固定電極16と可動電極18との電極間距離である。「d0」はV1=0V時の可動電極18と駆動電極14との間の電極間距離であり、ここではd0=3.3μmとする。「S」は可動電極18の面積であり、ここでは300μm×300μmとする。「ε」は真空誘電率であり、ε=8.85E−12F/mとする。「K」は真空の比誘電率であり、ここでは1とする。本実施の形態におけるその他の各部材の「長さ、厚さ、距離」は、上述した通りである。

【0070】

上記式(5)からも分かるように、駆動電圧V1が0Vでは、図8(A)及び図9(A)に示すように、電極間距離dは約0μmである。このとき、容量Cは20.7pFとなる。一方、駆動電圧V1が2.83Vでは、図8(B)及び図9(B)に示すように、電極間距離dは約1.1μmである。このとき、容量Cは5.9pFとなる。このような動作により、チューナブル・キャパシタ44の容量Cの大きさが調整される。なお、容量Cの値はシミュレーションにより得られた値である。

【0071】

(2)可変容量素子の振動防止動作

次に、図10及び図11を参照して可変容量素子の振動防止動作を説明する。図10(A)〜(C)はブレーキ・キャパシタが可動電極の振動を防止する様子を示す図である。図11(A)〜(C)はブレーキ・キャパシタの動作下でのチューナブル・キャパシタの特性を示すグラフである。

【0072】

上述した通り、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46にV1の正電圧を印加すると、可動電極18が駆動電極14側に移動して、チューナブル・キャパシタ44の容量Cが小さくなる(図6、図7参照)。図7に示すように、可動電極18は静電力により所定位置に保持されているが、この状態のままでは、外部振動を受けて可動電極18が振れるおそれがある。この振動を防止するために、上部ブレーキ電極22及び下部ブレーキ電極24の間に、電源42からブレーキ電圧V2が印加される。

【0073】

図10(A)に示すように、ブレーキ電圧V2が印加されると、ブレーキ・キャパシタ20の下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との水平方向の電極間距離が0μmになる。下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との水平方向の電極間距離も0μmになる。即ち、各対向電極は誘電体層28を介して接触することになる。

【0074】

これによって、可動電極18と固定電極16とを大面積で接触させることが可能になると共に、電極間での摩擦力によって可動電極18を所定位置に安定に維持することができる。また、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0075】

例えば、図8(A)に示すように、駆動電圧V1が0Vで電極間距離dが約0μmの状態で3Vのブレーキ電圧V2が印加されると、図10(B)に示すように、下部ブレーキ電極24及び可動電極18は垂直方向の位置を維持したまま水平方向に移動し、対向電極は誘電体層28を介して接触することになり、摩擦力によりこの位置に固定される。

【0076】

同様に、図8(B)に示すように、駆動電圧V1が2.83Vで電極間距離dが約1.1μmの状態で3Vのブレーキ電圧V2が印加されると、図10(C)に示すように、下部ブレーキ電極24及び可動電極18は垂直方向の位置を維持したまま水平方向に移動し、対向電極は誘電体層28を介して接触することになり、摩擦力によりこの位置に固定される。

【0077】

図11(A)に示すように、チューナブル・キャパシタ44の電極間距離dは、駆動電圧V1に依存して変化する。ここで、横軸が駆動電圧V1[V]であり、縦軸が固定電極16と可動電極18との電極間距離d[μm]である。図から分かるように、駆動電圧V1が0V〜3Vまで増加するに従い、電極間距離dは0μm〜1.2μmまで増加する。

【0078】

また、図11(B)に示すように、駆動電圧V1に応じて電極間距離dが変化している場合にブレーキ電圧V2が印加されると、チューナブル・キャパシタ44の容量Cは、電極間距離dに依存して変化する。ここで、横軸が電極間距離d[μm]であり、縦軸が容量C[pF]である。図から分かるように、3Vのブレーキ電圧V2を印加する場合には、電極間距離dが0μm〜1.2μmまで増加するに従い、容量Cは約60pF〜約10pFまで減少する。

【0079】

実際に動作させて、チューナブル・キャパシタ44の容量Cと駆動電圧V1との関係を測定すると、図11(C)に示すように、3Vのブレーキ電圧V2を印加した場合には、駆動電圧V1が0Vから3Vまで増加するに従い、チューナブル・キャパシタ44の容量Cは、約60pFから約10pFまで減少する。ブレーキ電圧V2が0Vでは、駆動電圧V1が0Vで容量Cは20.7pFであり、駆動電圧V1が2.83Vで容量Cは5.9pFとなる。これと比較すると、3Vのブレーキ電圧V2を印加した場合には、チューナブル・キャパシタ44の容量Cは2〜3倍に増加する。即ち、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0080】

<可変容量素子の製造工程>

次に、図12及び図13を参照して、第1の実施の形態に係る可変容量素子の製造方法を説明する。ここでは、図4に領域Bで示す部分について製造工程の一例を示す。

【0081】

まず、図12(A)に示すように、支持基板12であるシリコン基板上に、例えばLP−CVD(Low Pressure CVD:減圧化学気相成長)法等の既知の方法を用いて、厚さ500nmの窒化シリコン(Si3N4)絶縁層13を成膜する。このSi3N4絶縁層13上に、例えばスパッタリング等の既知の方法を用いて、厚さ200nmのタングステンシリサイド(WSi2)を成膜して、WSi2駆動電極14を形成する。次に、図12(B)に示すように、WSi2駆動電極14上に、例えばLP−CVD法等の既知の方法を用いて、酸化シリコン(SiO2)層を3.3μmの厚さに堆積して、SiO2犠牲膜15を成膜する。

【0082】

次に、図12(C)に示すように、SiO2犠牲膜15上に、例えばLP−CVD法等の既知の方法を用いて、可動電極18等を形成するために、厚さ1.4μmの多結晶シリコン(Poly-Si)層17を成膜する。Poly-Si層17には燐(P)をドープする。燐をドープするために、原料ガスはSiH4以外に、不純物ガスとしてPH3を同時に導入する。燐をドープすることでPoly-Siの抵抗を低くすることができる。燐をドープしたPoly-Siは導体と見なすことができる。例えば、燐を5E20/cm3でドープした場合、620℃で成膜したPoly-Si膜の抵抗率は70mΩ・cmである。

【0083】

次に、図12(D)に示すように、Poly-Si層17を、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等、既知の方法で櫛歯状にパターニングして、可動電極18(櫛歯部18A)及び下部ブレーキ電極24(櫛歯部24A)を形成する。エッチング工程では、約1.2μmの深さまでエッチングする。

【0084】

次に、図12(E)に示すように、Poly-Si層17をパターニングして形成された可動電極18及び下部ブレーキ電極24の表面に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4層を成膜し、Si3N4誘電体層28を形成する。

【0085】

次に、図12(F)に示すように、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等の既知の方法で、Poly-Si層(可動電極18及び下部ブレーキ電極24)及びSi3N4誘電体層28を所定パターンで除去して、SiO2犠牲膜15を露出させ、リリースホール19を形成する。

【0086】

次に、図12(G)に示すように、例えばLP−CVD法等の既知の方法を用いて、Si3N4誘電体層28で被覆された可動電極18及び下部ブレーキ電極24の表面上に、SiO2犠牲膜15を更に0.1μmの厚さで成膜する。リリースホール19も、SiO2犠牲膜15で埋められる。次に、図12(H)に示すように、固定電極16等を形成するために、例えばLP−CVD法等の既知の方法を用いて、厚さ1.4μmのPoly-Si層21を堆積する。

【0087】

次に、図13(I)に示すように、例えばCMP(Chemical Mechanical Polishing:化学機械研磨)等の既知の方法を用いて、Poly-Si層21の表面を平坦化する。次に、図13(J)に示すように、誘電体26(絶縁部)を埋め込むために、ドライエッチングにより、Poly-Si層21を所定パターンで除去して、溝部23を形成する。

【0088】

次に、図13(K)に示すように、溝部23が形成されたPoly-Si層21の表面上に、厚さが200nmのSi3N4層25を成膜する。次に、図13(L)に示すように、Poly-Si層21の表面が露出するまでエッチングを行い、余分のSi3N4層25を除去して、Si3N4誘電体26を埋め込み形成する。次に、図13(M)に示すように、Poly-Si層21の表面を所定パターンで除去して、SiO2犠牲膜15をリリースするためのリリースホール27を形成する。

【0089】

最後に、図13(N)に示すように、固定電極16(櫛歯部16A)及び上部ブレーキ電極22(櫛歯部22A)を形成するために、SiO2犠牲膜15を既知の方法でリリースする。例えば、フッ酸に浸漬してSiO2犠牲膜15をウェットエッチングにより除去する。Si3N4はフッ酸にはほとんど溶解しないため、SiO2犠牲膜15だけを選択的に除去できる。

【0090】

この工程により、可動電極18(櫛歯部18A)及び下部ブレーキ電極24(櫛歯部24A)は、固定電極16(櫛歯部16A)及び上部ブレーキ電極22(櫛歯部22A)から切り離されると共に、駆動電極14からも切り離されて、自由に移動できるようになる。

【0091】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、可動電極側の櫛歯部と駆動電極側の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により可動電極の位置が固定され、外部振動による可動電極の振動が防止される。これにより、チューナブル・キャパシタを、所望の容量Cで安定に動作させることができる。

【0092】

また、本実施の形態では、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。

【0093】

また、本実施の形態では、上部ブレーキ電極及び固定電極は一体に形成されているので、上部ブレーキ電極及び固定電極を別々に形成する場合と比較すると、可変容量素子の作製工程がより簡単になる。

【0094】

(第2の実施の形態)

図14(A)〜(C)は本発明の第2の実施の形態に係る可変容量素子の部分拡大図である。図14(A)は第1の実施の形態の図6に対応する図である。第2の実施の形態に係る可変容量素子10Aは、下部ブレーキ電極24が付設された可動電極18の裏面側に、絶縁層50を介して可動駆動電極52が形成されている以外は、第1の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を一部省略する。

【0095】

図14(A)に示すように、可動電極18及び下部ブレーキ電極24は、平面視が矩形状の部材として導電性材料で一体に形成されている。この部材の内、固定電極16に対向する部分が可動電極18であり、上部ブレーキ電極22に対向する部分が下部ブレーキ電極24である。この部材は平面視が矩形状の基板を備えている。

【0096】

この基板の表面側には、固定電極16側に突出した複数の櫛歯部18Aと、上部ブレーキ電極22側に突出した単数又は複数の櫛歯部24Aとが設けられている。櫛歯部が形成された可動電極18及び下部ブレーキ電極24の表面は、誘電体層28で被覆されている。一方、基板の裏面側には、絶縁層50を介して可動駆動電極52が形成されている。即ち、可動電極18、下部ブレーキ電極24、絶縁層50、及び可動駆動電極52は、一体に形成されている。

【0097】

下部ブレーキ電極24が付設された可動電極18の面積は、対向する駆動電極14の面積とほぼ同じ大きさとされている。また、絶縁層50を介して形成された可動駆動電極52の面積も、対向する駆動電極14の面積とほぼ同じ大きさとされている。

【0098】

本実施の形態では、下部ブレーキ電極24が付設された可動電極18の面積、絶縁層50を介して形成された可動駆動電極52の面積は、各々300μm×300μmとされている。可動電極18及び下部ブレーキ電極24の厚さは約1.25μmである。基板の厚さが約0.05μmで、櫛歯部の高さが約1.2μmであり、合計の厚さが約1.25μmとなる。誘電体層28の厚さは約0.1μmである。絶縁層50の厚さは約0.1μmである。可動駆動電極52の厚さは約0.05μmである。

【0099】

また、本実施の形態では、可動電極18、下部ブレーキ電極24、及び可動駆動電極52用の導電性材料には、多結晶シリコン(Poly-Si)が用いられている。誘電体層28及び絶縁層50には、窒化シリコン(Si3N4)が用いられている。

【0100】

第1の実施の形態と同様に、可変容量素子10Aは、機能面から見ると、ブレーキ・キャパシタ20、チューナブル・キャパシタ44、及び駆動キャパシタ46Aの3種類のキャパシタから構成されている。本実施の形態では、駆動キャパシタ46Aは、駆動電極14と可動駆動電極52とで構成されている。

【0101】

図14(B)に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46AにV1の正電圧を印加する。駆動電極14及び可動駆動電極52の間には、電源40から駆動電圧V1が印加される。これにより、駆動キャパシタ46Aの垂直方向の電極間距離が減少し、可動電極18が可動駆動電極52と共に駆動電極14側に移動する。

【0102】

また、チューナブル・キャパシタ44の対向電極面積が減少し、固定電極16と可動電極18との対向距離も増加する。これにより、チューナブル・キャパシタ44の容量Cが小さくなる。本実施の形態では、駆動キャパシタ46Aの可動駆動電極52は、チューナブル・キャパシタ44の可動電極18と、絶縁層50により絶縁され、電気的に完全に分離されている。このため、チューナブル・キャパシタ44の動作時に、駆動電圧V1による影響(ノイズの発生等)が低減される。

【0103】

図14(C)に示すように、振動防止動作を実施する場合には、ブレーキ・キャパシタ20にブレーキ電圧V2を印加する。上部ブレーキ電極22及び下部ブレーキ電極24の間には、電源42からブレーキ電圧V2が印加される。ブレーキ電圧V2が印加されると、下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との水平方向の電極間距離が0μmになる。下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との電極間距離も0μmになる。即ち、各対向電極は誘電体層28を介して接触することになる。

【0104】

これによって、第1の実施の形態と同様に、可動電極18と固定電極16とを大面積で接触させることが可能になると共に、電極間での摩擦力によって可動電極18を所定位置に安定に維持することができる。また、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0105】

次に、図15及び図16を参照して、第2の実施の形態に係る可変容量素子の製造方法を説明する。第1の実施の形態と同様の工程は、簡単に説明する。

【0106】

まず、図15(A)に示すように、支持基板12であるシリコン基板上に、厚さ500nmのSi3N4絶縁層13を成膜する。このSi3N4絶縁層13上に、厚さ200nmのWSi2を成膜して、WSi2駆動電極14を形成する。次に、図15(B)に示すように、WSi2駆動電極14上に、SiO2を3.3μmの厚さに堆積して、SiO2犠牲膜15を成膜する。

【0107】

次に、図15(C)に示すように、SiO2犠牲膜15上に、例えばLP−CVD法等の既知の方法を用いて、厚さ50nmのPoly-Si膜を成膜して、Poly-Si可動駆動電極52を形成する。このPoly-Si可動駆動電極52上に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4を成膜して、Si3N4絶縁層50を形成する。

【0108】

次に、図15(D)に示すように、Si3N4絶縁層50上に、可動電極18等を形成するために、1.4μmのPoly-Si層17を成膜する。Poly-Si層17には燐(P)をドープする。次に、図15(E)に示すように、Poly-Si層17を、櫛歯状にパターニングして、可動電極18(櫛歯部18A)及び下部ブレーキ電極24(櫛歯部24A)を形成する。エッチング工程では、約1.2μmの深さまでエッチングする。

【0109】

次に、図15(F)に示すように、Poly-Si層17をパターニングして形成された可動電極18及び下部ブレーキ電極24の表面に、厚さが0.1μmのSi3N4を成膜し、Si3N4誘電体層28を形成する。次に、図15(G)に示すように、Poly-Si可動駆動電極52、Si3N4絶縁層50、Poly-Si層(可動電極18及び下部ブレーキ電極24)及びSi3N4誘電体層28を所定パターンで除去して、SiO2犠牲膜15を露出させ、リリースホール19を形成する。次に、図15(H)に示すように、SiO2犠牲膜15を更に0.1μmの厚さで成膜する。リリースホール19もSiO2犠牲膜15で埋められる。

【0110】

次に、図16(I)に示すように、固定電極16等を形成するために、厚さ1.4μmのPoly-Si層21を堆積する。次に、図16(J)に示すように、Poly-Si層21の表面を平坦化する。次に、図16(K)に示すように、Poly-Si層21を所定パターンで除去して、溝部23を形成する。次に、図16(L)に示すように、溝部23を埋めるように、厚さが200nmのSi3N4層25を成膜する。次に、図16(M)に示すように、Poly-Si層21の表面が露出するまでエッチングを行い、余分のSi3N4層25を除去して、Si3N4誘電体26を埋め込み形成する。次に、図16(N)に示すように、Poly-Si層21の表面を所定パターンで除去して、SiO2犠牲膜15をリリースするためのリリースホール27を形成する。

【0111】

最後に、図16(O)に示すように、固定電極16及び上部ブレーキ電極22を形成するために、SiO2犠牲膜15をリリースする。この工程により、可動電極18、下部ブレーキ電極24、絶縁層50、及び可動駆動電極52は、固定電極16及び上部ブレーキ電極22から切り離されると共に、駆動電極14からも切り離されて、自由に移動できるようになる。

【0112】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、可動電極側の櫛歯部と駆動電極側の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により可動電極の位置が固定され、外部振動による可動電極の振動が防止される。これにより、チューナブル・キャパシタを、所望の容量Cで安定に動作させることができる。

【0113】

また、本実施の形態では、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。

【0114】

また、本実施の形態では、上部ブレーキ電極及び固定電極は一体に形成されているので、上部ブレーキ電極及び固定電極を別々に形成する場合と比較すると、可変容量素子の作製工程がより簡単になる。

【0115】

更に、本実施の形態では、駆動キャパシタの可動駆動電極は、チューナブル・キャパシタの可動電極と絶縁層により絶縁されているので、チューナブル・キャパシタの動作時に、駆動電圧V1による影響が低減される。

【0116】

(第3の実施の形態)

図17は本発明の第3の実施の形態に係る可変容量素子の側面図である。図18(A)〜(C)は本発明の第3の実施の形態に係る可変容量素子の部分拡大図である。図17は第1の実施の形態の図3に対応する図である。図18(A)は第1の実施の形態の図6に対応する図である。第3の実施の形態に係る可変容量素子10Bは、支持基板12上に、駆動電極14を覆うように誘電層60を設けた以外は、第1の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0117】

第1の実施の形態と同様に、駆動電極14は平面視が支持基板12よりひと回り小さい矩形状とされ、支持基板上12の中央部分に形成されている。支持基板12上には、この駆動電極14を覆うように、駆動電極14より厚膜の誘電層60が設けられている。本実施の形態では、駆動電極14の厚さは約0.2μmであり、誘電層60の厚さは約2.2μmである。また、駆動電極14用の導電性材料には、WSi2が用いられ、誘電層60には、Si3N4が用いられている。

【0118】

図18(A)に示すように、可変容量素子10Bは、機能面から見ると、第1の実施の形態と同様に、ブレーキ・キャパシタ20、チューナブル・キャパシタ44、及び駆動キャパシタ46Bの3種類のキャパシタから構成されている。本実施の形態では、駆動キャパシタ46Bは、駆動電極14と誘電層60と可動電極18とで構成されている。

【0119】

図18(B)に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ46BにV1の正電圧を印加する。駆動電極14及び可動電極18の間には、電源40から駆動電圧V1が印加される。これにより、駆動キャパシタ46Bの電極間距離が減少し、可動電極18が駆動電極14側に移動する。また、チューナブル・キャパシタ44の対向電極面積が減少し、固定電極16と可動電極18との対向距離も増加する。これにより、チューナブル・キャパシタ44の容量Cが小さくなる。

【0120】

本実施の形態では、駆動電極14と可動電極18との間に誘電層60を挿入することで、駆動キャパシタ46Bの容量は第1の実施の形態に比べてかなり大きくなる。下記式(6)に示すように、駆動キャパシタ46Bのばね常数kは、梁部(梁部34及びばね部材36)の機械的ばね常数kmと、電気的ばね常数keとの和になる。

【0121】

【化6】

【0122】

下記式(7)から分かるように、駆動キャパシタ46Bの容量が増加すると、電気的ばね常数keも大きくなる。ここで、各パラメータは駆動キャパシタ46Bに関するものであり、Cは平行平板の容量、Vは平行平板への印加電圧、dは電極間距離である。

【0123】

【化7】

【0124】

これを利用すると、例えば、上記梁部の機械的ばね定数kmを低く設計することが困難な場合等には、誘電層60の厚さを変更することにより電気ばね常数keを制御して、駆動キャパシタ46Bのばね常数kを調整することができる。

【0125】

図18(C)に示すように、振動防止動作を実施する場合には、ブレーキ・キャパシタ20にブレーキ電圧V2を印加する。上部ブレーキ電極22及び下部ブレーキ電極24の間には、電源42からブレーキ電圧V2が印加される。ブレーキ電圧V2が印加されると、ブレーキ・キャパシタ20の下部ブレーキ電極24が水平方向に移動して、上部ブレーキ電極22と下部ブレーキ電極24との電極間距離が0μmになる。

【0126】

下部ブレーキ電極24と一体に形成された可動電極18も共に水平方向に移動して、可動電極18と固定電極16との電極間距離も0μmになる。即ち、両電極は誘電体層28を介して接触することになる。これによって、可動電極18と固定電極16とを大面積で接触させることが可能になると共に、電極間での摩擦力によって可動電極18の位置に安定に維持することができる。また、チューナブル・キャパシタ44の容量Cの変動量がより大きくなる。

【0127】

第3の実施の形態に係る可変容量素子10Bは、以下に説明する工程以外は、第1の実施の形態と同様の製造工程により製造することができる。即ち、第1の実施の形態で例示した図12(A)に示す工程において、支持基板12であるシリコン基板上に厚さ500nmのSi3N4絶縁層13を成膜し、このSi3N4絶縁層13上に厚さ200nmのWSi2を成膜してWSi2駆動電極14を形成する。

【0128】

この後に、WSi2駆動電極14上に、例えばLP−CVD法等の既知の方法を用いて、厚さ2.2μmのSi3N4誘電層60を形成する。次に、図12(B)に示す工程において、Si3N4誘電層60上に、例えばLP−CVD法等の既知の方法を用いて、SiO2を1.1μmの厚さに堆積して、SiO2犠牲膜15を成膜する。

【0129】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、可動電極側の櫛歯部と駆動電極側の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により可動電極の位置が固定され、外部振動による可動電極の振動が防止される。これにより、チューナブル・キャパシタを、所望の容量Cで安定に動作させることができる。

【0130】

また、本実施の形態では、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。

【0131】

また、本実施の形態では、上部ブレーキ電極及び固定電極は一体に形成されているので、上部ブレーキ電極及び固定電極を別々に形成する場合と比較すると、可変容量素子の作製工程がより簡単になる。

【0132】

更に、本実施の形態では、駆動キャパシタの電極間に誘電層を挿入することで、駆動キャパシタの容量がかなり大きくなる。駆動キャパシタのばね常数は、梁部の機械的ばね常数と電気的ばね常数との和になる。駆動キャパシタの容量が増加すると電気的ばね常数も大きくなるので、これを利用すると、誘電層の厚さを変更することにより電気ばね常数を制御して、駆動キャパシタのばね常数を調整することができる。

【0133】

(第4の実施の形態)

図19(A)〜(C)は本発明の第4の実施の形態に係る可変容量素子の部分拡大図である。図19(A)は第1の実施の形態の図6に対応する図である。第4の実施の形態に係る可変容量素子10Cは、第2の実施の形態と同様に、下部ブレーキ電極24が付設された可動電極18の裏面側に、絶縁層50を介して可動駆動電極52が形成されると共に、第3の実施の形態と同様に、支持基板12上に、駆動電極14を覆うように誘電層60を設けた以外は、第1の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0134】

本実施の形態の可変容量素子は、第1〜第3の実施の形態に係る可変容量素子と同様に、外部振動による可動電極の振動が防止されることにより、チューナブル・キャパシタを、所望の容量で安定に動作させることができる。また、ブレーキ電圧V2の印加により、チューナブル・キャパシタの容量の変動量がより大きくなる。また、上部ブレーキ電極及び固定電極は一体に形成されているので、可変容量素子の作製工程がより簡単になる。

【0135】

また、第2の実施の形態と同様に、駆動キャパシタの可動駆動電極は、チューナブル・キャパシタの可動電極と絶縁層により絶縁されているので、チューナブル・キャパシタの動作時に、駆動電圧V1による影響が低減される。

【0136】

更に、第3の実施の形態と同様に、駆動キャパシタの容量が増加すると電気的ばね常数も大きくなることを利用して、誘電層の厚さを変更することにより電気ばね常数を制御して、駆動キャパシタのばね常数を調整することができる。

【0137】

(第5の実施の形態)

<可変容量素子の概略構成>

図20〜図22を参照して、第5の実施の形態に係る可変容量素子の構成を簡単に説明する。図20は本発明の第5の実施の形態に係る可変容量素子を固定電極側から見た平面図である。図21は図20に示す可変容量素子の側面図である。図22は図20に示す可変容量素子のY−Y線断面図である。

【0138】

可変容量素子70は、シリコン等の半導体で構成された支持基板72、支持基板72上に配置された駆動電極74、駆動電極74に対向するように離間配置された固定電極76、駆動電極74と固定電極76との間に移動可能に保持された可動電極78、及び可動電極78の移動後の振動を防止する振動防止部としての複数のブレーキ・キャパシタ80を備えている。

【0139】

本実施の形態では、一対のブレーキ・キャパシタ80が2組、合計4個のブレーキ・キャパシタ80が設けられている。一対のブレーキ・キャパシタ80は、図面上、固定電極76を挟んで左右対称に配置されている。ブレーキ・キャパシタ80の各々は、上部ブレーキ電極82と、電圧印加により上部ブレーキ電極82と接触する下部ブレーキ電極84と、で構成されている。

【0140】

支持基板72は平面視が矩形状の平板である。駆動電極74は導電性材料により形成された薄膜電極である。駆動電極74は絶縁層(図示せず)を介して支持基板上72上に成膜されている。駆動電極74は平面視が支持基板72よりひと回り小さい矩形状とされ、支持基板上72の中央部分に形成されている。

【0141】

本実施の形態では、支持基板72の面積を400μm×400μmとし、駆動電極74の面積を300μm×300μmとしている。また、駆動電極74用の導電性材料には、WSi2が用いられている。絶縁層(図示せず)には、Si3N4が用いられている。駆動電極74の厚さは約0.2μmである。

【0142】

固定電極76は平面視が矩形状の基板を備えている。この基板には、支持基板72側に突出した複数の櫛歯部76Aが設けられている。固定電極76の櫛歯部76Aは、図示するY方向に延びた長尺状の板体であり、固定電極76の基板に対し直角を成すように設けられている。

【0143】

上部ブレーキ電極82は平面視が短冊状の基板を備えている。上部ブレーキ電極82の基板は、長手方向がY方向を向くと共に、長手方向の基板側面が固定電極76のY方向に延びた基板側面と対向するように配置されている。即ち、上部ブレーキ電極82は、固定電極76とは別個の部材として構成されている。

【0144】

上部ブレーキ電極82の基板には、支持基板72側に突出した単数又は複数の櫛歯部82Aが設けられている。上部ブレーキ電極82の櫛歯部82Aは、図示するY方向に延びた長尺状の板体であり、上部ブレーキ電極82の基板に対し直角を成すように設けられている。

【0145】

固定電極76の面積は、対向する駆動電極74の面積とほぼ同じ大きさとされている。固定電極76及び上部ブレーキ電極82は、導電性材料で形成されている。本実施の形態では、固定電極76の面積を300μm×300μmとしている。また、固定電極76及び上部ブレーキ電極82用の導電性材料には、Poly-Siが用いられている。

【0146】

可動電極78は平面視が矩形状の基板を備えている。この基板には、固定電極76側に突出した複数の櫛歯部78Aが設けられている。可動電極78の櫛歯部78Aは、図示するY方向に延びた長尺状の板体であり、可動電極78の基板に対し直角を成すように設けられている。

【0147】

下部ブレーキ電極84は平面視が短冊状の基板を備えている。下部ブレーキ電極84の基板は、上部ブレーキ電極82の基板と丁度対向するように設けられている。この基板には、上部ブレーキ電極82側に突出した複数の櫛歯部84Aが設けられている。下部ブレーキ電極84の櫛歯部84Aは、Y方向に延びた長尺状の板体であり、下部ブレーキ電極84の基板に対し直角を成すように設けられている。

【0148】

可動電極78の面積は、対向する固定電極76の面積とほぼ同じ大きさとされている。可動電極78及び下部ブレーキ電極84は、導電性材料で形成されている。本実施の形態では、可動電極78の面積を300μm×300μmとしている。また、可動電極78及び下部ブレーキ電極84用の導電性材料には、Poly-Siが用いられている。

【0149】

また、一対のブレーキ・キャパシタ80に対応して、一対の下部ブレーキ電極84が設けられている。一対の下部ブレーキ電極84の各々は、フレキシブルな連結部材86を介して、可動電極78の両側に対称に連結されている。フレキシブルな連結部材86は、短冊状の基部86Bとこの基部86Bの両端に各々立設された棒状の側部86Sとで構成されている。可動電極78側を内側、下部ブレーキ電極84を外側とする。外側に配置された側部86Sの一端が、下部ブレーキ電極84の基板に連結されている。一方、内側に配置された側部86Sの一端が、可動電極78の基板に連結されている。

【0150】

即ち、下部ブレーキ電極84、連結部材86、及び可動電極78は一体に形成されている。しかしながら、一対の下部ブレーキ電極84の各々は、可動電極78の両側に対称に連結されており、水平方向を反対側に移動するので、可動電極78は双方から引っ張られる。その結果、連結部材86の外側の側部86Sが弾性変形して湾曲するだけで、連結部材86自体は移動せず、可動電極78も移動しない。従って、可動電極78を移動させずに、下部ブレーキ電極84だけを移動させることができる。

【0151】

櫛歯部が形成された可動電極78及び下部ブレーキ電極84の表面は、誘電体層88で被覆されている。本実施の形態では、誘電体層88には、Si3N4が用いられている。

【0152】

固定電極76は、支持基板72上に立設された複数の支柱90により支持されて、支持基板72から所定の高さに固定配置されている。また、上部ブレーキ電極82も、支持基板72上に立設された複数の支柱90により支持されて、固定電極76とほぼ同じ高さに固定配置されている。1個の部材を支える支柱90の本数は3本以上が好ましい。複数の支柱90は、固定電極76及び上部ブレーキ電極82と同様に導電性材料で形成されている。本実施の形態では、支柱90用の導電性材料には、Poly-Siが用いられている。

【0153】

支持基板72の四隅の各々には、柱状のアンカー部92が立設されている。即ち、支持基板72上には、4本のアンカー部92が立設されている。4本のアンカー部92間には、長尺状の梁部94が架け渡されている。長尺状の梁部94は、可動電極78等を取り囲むように架け渡されている。本実施の形態では、幅1.4μmの長尺状の梁部94が、支持基板72から約3.5μmの高さに架け渡されている。

【0154】

可動電極78は、複数のばね部材96により梁部94に連結されている。可動電極78は、ばね部材96により梁部94に連結されることで、駆動電極74と固定電極76との間において、垂直方向及び水平方向に移動可能に保持されている。本実施の形態では、下部ブレーキ電極84及び可動電極78は、4個のばね部材96によって、長尺状の梁部94と同じ高さ(即ち、支持基板72から約3.5μmの高さ)に保持されている。

【0155】

アンカー部92、梁部94、及びばね部材96は、保持される可動電極78と同様に導電性材料で形成されている。本実施の形態では、アンカー部92、梁部94、及びばね部材96用の導電性材料には、Poly-Siが用いられている。

【0156】

また、図22及び図23に示すように、電極間に電圧を印加する前の初期状態では、可動電極78側の櫛歯部78A及び櫛歯部84Aの各々が、固定電極76側の櫛歯部76A及び櫛歯部82Aの間隙(櫛歯部が設けられていない領域)に対向するように、下部ブレーキ電極84が連結された可動電極78が所定位置に保持されている。

【0157】

これにより、可動電極78が固定電極76側に向って垂直方向に移動しても、可動電極78の櫛歯部78Aは、固定電極76側の隣接する2個の櫛歯部76Aの間隙(又は、櫛歯部76Aと支柱90との間隙)に侵入することができる。また、下部ブレーキ電極84の櫛歯部84Aは、固定電極76側の隣接する2個の櫛歯部82Aの間隙(又は、櫛歯部82Aと支柱90との間隙)に侵入することができる。本実施の形態では、例えば、櫛歯部76Aと櫛歯部78Aのように、対向電極の櫛歯部が嵌合された状態では、隣接する櫛歯部間の距離は約0.1μmである。

【0158】

上述した通り、櫛歯部が形成された可動電極78及び下部ブレーキ電極84の表面は、誘電体層88で被覆されている。従って、可動電極78と固定電極76との間には誘電体層88が必ず介在し、可動電極78の移動により両電極間が短絡されることはない。同様に、上部ブレーキ電極82と下部ブレーキ電極84との間には誘電体層88が必ず介在し、下部ブレーキ電極84の移動により両電極間が短絡されることはない。

【0159】

駆動電極74と可動電極78とは、両電極間に駆動電圧V1を印加する電源100に接続されている。また、上部ブレーキ電極82と下部ブレーキ電極84とは、両電極間にブレーキ電圧V2を印加する電源102に接続されている。なお、下部ブレーキ電極84及び可動電極78は、電源102に接続されると共に接地されている。従って、下部ブレーキ電極84と可動電極78とは、共に接地されてグランド電位となる。

【0160】

また、可変容量素子70は、機能面から見ると、振動防止部としてのブレーキ・キャパシタ80、可変容量としてのチューナブル・キャパシタ104、及び電極駆動部としての駆動キャパシタ106の3種類のキャパシタから構成されている。ブレーキ・キャパシタ80は、上部ブレーキ電極82と下部ブレーキ電極84とで構成されている。チューナブル・キャパシタ104は、固定電極76と可動電極78とで構成されている。駆動キャパシタ106は、駆動電極74と可動電極78及び下部ブレーキ電極84とで構成されている。ここで、チューナブル・キャパシタ104の容量を「C」とする。

【0161】

<可変容量素子の動作>

(1)可変容量素子の容量調整動作

まず、図23を参照して可変容量素子の容量調整動作を説明する。

図23に示すように、容量調整動作を実施する場合には、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ106にV1の正電圧を印加する。駆動電極74及び可動電極78の間には、電源100から駆動電圧V1が印加される。これにより、駆動キャパシタ106の垂直方向の電極間距離が減少し、可動電極78が駆動電極74側に移動する。また、チューナブル・キャパシタ104の対向電極面積が減少し、固定電極76と可動電極78との対向距離も増加する。これにより、チューナブル・キャパシタ104の容量Cが小さくなる。

【0162】

(2)可変容量素子の振動防止動作

次に、図24を参照して可変容量素子の振動防止動作を説明する。

図24に示すように、振動防止動作を実施する場合には、ブレーキ・キャパシタ80にブレーキ電圧V2を印加する。上部ブレーキ電極82及び下部ブレーキ電極84の間には、電源102からブレーキ電圧V2が印加される。ブレーキ電圧V2が印加されると、下部ブレーキ電極84が水平方向を外側に移動して、上部ブレーキ電極82と下部ブレーキ電極84との水平方向の電極間距離が0μmになる。即ち、両電極は誘電体層88を介して接触することになる。

【0163】

一方、可動電極78の両側には、一対の下部ブレーキ電極84が2組連結されている。一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動しても、連結部材86の外側の側部86Sが弾性変形して湾曲するだけで、連結部材86自体は水平方向には移動せず、可動電極78は水平方向に移動しない。

【0164】

即ち、下部ブレーキ電極84が水平方向に移動して、上部ブレーキ電極82と下部ブレーキ電極84とが大面積で接触することで、電極間での摩擦力によって下部ブレーキ電極84を垂直方向の所定位置に安定に維持することができる。同時に、一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動することで、可動電極78に対する引張り力が相殺されて可動電極78は移動せず、可動電極78を水平方向の所定位置に安定に維持することができる。

【0165】

この通り、振動防止動作時に、下部ブレーキ電極84が水平方向に各々移動しても、チューナブル・キャパシタ104では、固定電極76と可動電極78との対向距離は変化しないので、チューナブル・キャパシタ104の容量Cを一定に維持することができる。

【0166】

<可変容量素子の製造工程>

次に、図25及び図26を参照して、第5の実施の形態に係る可変容量素子の製造方法を説明する。ここでは、図22に示す構成の左半分の部分について製造工程の一例を示す。

【0167】

まず、図25(A)に示すように、支持基板72であるシリコン基板上に、例えばLP−CVD法等の既知の方法を用いて、厚さ500nmのSi3N4絶縁層73を成膜する。このSi3N4絶縁層73上に、例えばスパッタリング等の既知の方法を用いて、厚さ200nmのWSi2を成膜して、WSi2駆動電極74を形成する。次に、図25(B)に示すように、WSi2駆動電極74上に、例えばLP−CVD法等の既知の方法を用いて、SiO2層を1.1μmの厚さに堆積して、SiO2犠牲膜75を成膜する。

【0168】

次に、図25(C)に示すように、連結部材86の基部86Bを形成するために、SiO2犠牲膜75上に、例えばLP−CVD法等の既知の方法を用いて、厚さ1.1μmのPoly-Si層77Aを成膜する。Poly-Si層77Aには燐をドープする。燐をドープするために、原料ガスはSiH4以外に、不純物ガスとしてPH3を同時に導入する。

【0169】

次に、図25(D)に示すように、Poly-Si層77Aを、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等、既知の方法で短冊状にパターニングして、連結部材86の基部86Bを形成する。その後、連結部材86の側部86Sを形成するために、連結部材86の基部86B及び露出したSiO2犠牲膜75上に、更に厚さ2.2μmのSiO2犠牲膜75を成膜する。

【0170】

次に、図25(E)に示すように、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等の既知の方法で、SiO2犠牲膜75を所定パターンで除去して、連結部材86の基部86Bに到達する2個のスルーホール86Hを形成する。

【0171】

次に、図25(F)に示すように、可動電極78等を形成するために、SiO2犠牲膜75上に、例えばLP−CVD法等の既知の方法を用いて、厚さ2.2μmのPoly-Si層77Bを成膜する。Poly-Si層77Bには燐をドープする。2個のスルーホール86Hも、Poly-Si層77Bで埋められて、連結部材86の側部86Sが形成される。また、例えばCMP等の既知の方法を用いて、Poly-Si層77Bの表面を1.4μmの厚さまで平坦化する。

【0172】

次に、図25(G)に示すように、Poly-Si層77Bを、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等、既知の方法でパターニングして、可動電極78(櫛歯部78A)及び下部ブレーキ電極84(櫛歯部84A)を形成する。エッチング工程では、約1.2μmの深さまでエッチングする。

【0173】

次に、図25(H)に示すように、Poly-Si層77Bをパターニングして形成された可動電極78及び下部ブレーキ電極84の表面に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4層を成膜し、Si3N4誘電体層88を形成する。

【0174】

次に、図26(I)に示すように、例えばレジストを用いたフォトリソグラフィとドライエッチングとの組合せ等の既知の方法で、Poly-Si層(可動電極78及び下部ブレーキ電極84)及びSi3N4誘電体層88を所定パターンで除去して、SiO2犠牲膜75を露出させ、リリースホール79を形成する。

【0175】

次に、図26(J)に示すように、例えばLP−CVD法等の既知の方法を用いて、Si3N4誘電体層88で被覆された可動電極78及び下部ブレーキ電極84の表面上に、SiO2犠牲膜75を更に0.1μmの厚さで成膜する。リリースホール79もSiO2犠牲膜75で埋められる。

【0176】

次に、図26(K)に示すように、固定電極76等を形成するために、例えばLP−CVD法等の既知の方法を用いて、厚さ1.4μmのPoly-Si層81を堆積する。次に、図26(L)に示すように、SiO2犠牲膜75の表面が露出するまでエッチングを行い、余分のPoly-Si層81を所定パターンで除去して、SiO2犠牲膜75をリリースするためのリリースホール87を形成する。

【0177】

最後に、図26(M)に示すように、固定電極76(櫛歯部76A)及び上部ブレーキ電極82(櫛歯部82A)を形成するために、SiO2犠牲膜75を既知の方法でリリースする。例えば、フッ酸に浸漬してSiO2犠牲膜75をウェットエッチングにより除去する。この工程により、可動電極78及び下部ブレーキ電極84は、固定電極76及び上部ブレーキ電極82から切り離されると共に、駆動電極74からも切り離されて、自由に移動できるようになる。また、可動電極78と下部ブレーキ電極84とを連結する連結部材86が形成される。

【0178】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、下部ブレーキ電極が水平方向に移動して、上部ブレーキ電極の櫛歯部と下部ブレーキ電極の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により下部ブレーキ電極の垂直方向の位置が固定される。

【0179】

一対の下部ブレーキ電極の各々は、可動電極の両側に対称に連結されており、下部ブレーキ電極の各々は水平方向を反対側に移動するので、可動電極は双方から引っ張られる。その結果、連結部材の外側の側部が弾性変形して湾曲するだけで、可動電極は水平方向にも垂直方向にも移動しない。従って、外部振動による可動電極の振動が防止される。

【0180】

また、固定電極と可動電極との対向距離はブレーキ電圧V2の印加により変化しないので、チューナブル・キャパシタを、所望の容量Cで更に安定に動作させることができる。

【0181】

(第6の実施の形態)

図27は本発明の第6の実施の形態に係る可変容量素子の部分拡大図である。図27は第2の実施の形態の図14(A)に対応する図である。第6の実施の形態に係る可変容量素子70Aは、下部ブレーキ電極84及び可動電極78の裏面側に、絶縁層110を介して可動駆動電極112が形成されている以外は、第5の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0182】

この場合は、可動駆動電極112が、可動電極78に対向する固定部112A、下部ブレーキ電極84に対向する可動部112B、及び固定部112Aと可動部112Bとを連結するフレキシブルな連結部112Cから一体に構成されている。一対のブレーキ・キャパシタ80に対応した一対の可動部112Bの各々は、連結部112Cを介して可動部112Bの両側に対称に連結されている。

【0183】

フレキシブルな連結部112Cは、短冊状の基部112Cbと、この基部112Cbの両端に各々立設された棒状の側部112Csとで構成されている。外側に配置された側部112Csの一端が可動部112Bに連結されると共に、内側に配置された側部112Csの一端が固定部112Aに連結されている。一対の可動部112Bの各々は、固定部112Aの両側に対称に連結されており、水平方向を反対側に移動するので、固定部112Aは双方から引っ張られる。

【0184】

その結果、連結部112Cの外側の側部112Csが弾性変形して湾曲するだけで、連結部112C自体は移動せず、固定部112Aも移動しない。従って、第5の実施の形態と同様に、可動電極78を移動させずに、下部ブレーキ電極84だけを移動させることができる。

【0185】

図27に示す第6の実施の形態に係る可変容量素子70Aは、以下に説明する工程以外は、第5の実施の形態と同様の製造工程により製造することができる。即ち、第5の実施の形態で例示した図25(F)に示す工程に代えて、図28(A)に示すように、SiO2犠牲膜75上に、例えばLP−CVD法等の既知の方法を用いて、厚さ50nmのPoly-Si層膜を成膜して、Poly-Si可動駆動電極112(112A,112B、112C)を形成する。

【0186】

次に、図28(B)に示すように、可動駆動電極112上に、例えばLP−CVD法等の既知の方法を用いて、厚さ0.1μmのSi3N4膜を成膜して、Si3N4絶縁層110を形成する。このSi3N4絶縁層110上に、例えばLP−CVD法等の既知の方法を用いて、可動電極78等を形成するために、1.05μmのPoly-Si層77Bを成膜する。Poly-Si層77Bには燐(P)をドープする。

【0187】

図29は可変容量素子70Aの振動防止動作を説明する図である。

図29に示すように、ブレーキ電圧V2が0Vの状態で、駆動キャパシタ106にV1の正電圧を印加すると、可動電極78が駆動電極74側に移動する。しかしながら、静電力により可動電極78が駆動電極74側に移動した状態のままでは、外部振動を受けて可動電極78が振れる恐れがある。この振動を防止するために、ブレーキ・キャパシタ80にブレーキ電圧V2を印加する。上部ブレーキ電極82及び下部ブレーキ電極84の間には、電源102からブレーキ電圧V2が印加される。

【0188】

ブレーキ電圧V2が印加されると、下部ブレーキ電極84が水平方向に移動して、上部ブレーキ電極82と下部ブレーキ電極84との水平方向の電極間距離が0μmになる。即ち、両電極は誘電体層88を介して接触することになる。これにより、下部ブレーキ電極84及び可動電極78の垂直方向の位置が固定される。

【0189】

一方、可動電極78の両側には、絶縁層110及び可動駆動電極112を介して、一対の下部ブレーキ電極84が2組連結されている。一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動しても、可動駆動電極112の連結部112Cの外側の側部112Csが弾性変形して湾曲するだけで、連結部112C自体は水平方向には移動せず、可動電極78は水平方向に移動しない。

【0190】

即ち、下部ブレーキ電極84が水平方向に移動して、上部ブレーキ電極82と下部ブレーキ電極84とが大面積で接触することで、電極間での摩擦力によって下部ブレーキ電極84を垂直方向の所定位置に安定に維持することができる。同時に、一対の下部ブレーキ電極84の各々が、水平方向を反対方向に移動することで、可動電極78に対する引張り力が相殺されて可動電極78は移動せず、可動電極78を水平方向の所定位置に安定に維持することができる。

【0191】

この通り、振動防止動作時に、下部ブレーキ電極84が水平方向に各々移動しても、チューナブル・キャパシタ104では、固定電極76と可動電極78との対向距離は変化しないので、チューナブル・キャパシタ104の容量Cを一定に維持することができる。

【0192】

以上説明したように、本実施の形態の可変容量素子は、ブレーキ電圧V2が0Vの状態で、駆動キャパシタに駆動電圧V1を印加すると、可動電極が駆動電極側に移動して、チューナブル・キャパシタの容量Cを変化させる。この状態で、更にブレーキ・キャパシタにブレーキ電圧V2が印加されると、下部ブレーキ電極が水平方向に移動して、上部ブレーキ電極の櫛歯部と下部ブレーキ電極の櫛歯部とが誘電体層を介して接触するようになり、摩擦力により下部ブレーキ電極の垂直方向の位置が固定される。

【0193】

一対の下部ブレーキ電極の各々は、可動電極の両側に対称に連結されており、下部ブレーキ電極の各々は水平方向を反対側に移動するので、可動電極は双方から引っ張られる。その結果、連結部材の外側の側部が弾性変形して湾曲するだけで、可動電極は水平方向にも垂直方向にも移動しない。従って、外部振動による可動電極の振動が防止される。

【0194】

また、固定電極と可動電極との対向距離はブレーキ電圧V2の印加により変化しないので、チューナブル・キャパシタを、所望の容量Cで更に安定に動作させることができる。

【0195】

また、第2の実施の形態と同様に、可変容量素子は、下部ブレーキ電極及び可動電極の裏面側に、絶縁層を介して可動駆動電極が形成された構成としたことで、駆動キャパシタの可動駆動電極を、チューナブル・キャパシタの可動電極と絶縁層により絶縁することができる。これにより、チューナブル・キャパシタの動作時に、駆動電圧V1による影響が低減される。

【0196】

なお、第5、第6の実施の形態において、第3の実施の形態と同様に、支持基板上に、駆動電極を覆うように誘電層を設けてもよい。例えば、図30は第5の実施の形態に係る可変容量素子70の支持基板72上に、駆動電極74を覆うように誘電層130を設けた図であり、図31は第6の実施の形態に係る可変容量素子70Aの支持基板72上に、駆動電極74を覆うように誘電層130を設けた図である。誘電層130を設けた以外は、第5、第6の実施の形態と同様の構成であるため、同じ構成部分には同じ符号を付して説明を省略する。

【0197】

この構成によれば、駆動キャパシタの電極間に誘電層を挿入することで、駆動キャパシタの容量がかなり大きくなる。駆動キャパシタのばね常数は、梁部の機械的ばね常数と電気的ばね常数との和になる。駆動キャパシタの容量が増加すると電気的ばね常数も大きくなるので、これを利用すると、誘電層の厚さを変更することにより電気ばね常数を制御して、駆動キャパシタのばね常数を調整することができる。

【図面の簡単な説明】

【0198】

【図1】本発明の第1の実施の形態に係る可変容量素子の外観を示す斜視図である。

【図2】可変容量素子を固定電極側から見た平面図である。

【図3】可変容量素子の側面図である。

【図4】図2に示す可変容量素子のX−X線断面図である。

【図5】(A)は図2に示す領域Aでの櫛歯部の嵌合状態を示す図であり、(B)は図2に示す領域Aでの対向電極の分解斜視図である。

【図6】図4に示す領域Bの部分拡大図である。

【図7】(A)は可変容量素子の容量調整動作を説明する図であり、(B)はチューナブル・キャパシタの電圧依存性を示すグラフである。

【図8】チューナブル・キャパシタの動作の様子を示す断面図である。

【図9】チューナブル・キャパシタの動作の様子を示す立体図である。

【図10】(A)及び(B)はブレーキ・キャパシタが可動電極の振動を防止する動作する様子を示す図である。

【図11】(A)〜(C)はブレーキ・キャパシタの動作下でのチューナブル・キャパシタの特性を示す図である。

【図12】(A)〜(H)は第1の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図13】(I)〜(N)は第1の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図14】(A)〜(C)は本発明の第2の実施の形態に係る可変容量素子の部分拡大図である。

【図15】(A)〜(H)は第2の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図16】(I)〜(O)は第2の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図17】本発明の第3の実施の形態に係る可変容量素子の側面図である。

【図18】(A)〜(C)は本発明の第3の実施の形態に係る可変容量素子の部分拡大図である。

【図19】(A)〜(C)は本発明の第4の実施の形態に係る可変容量素子の部分拡大図である。

【図20】本発明の第5の実施の形態に係る可変容量素子を固定電極側から見た平面図である。

【図21】図20に示す可変容量素子の側面図である。

【図22】図20に示す可変容量素子のY−Y線断面図である。

【図23】可変容量素子の容量調整動作を説明する図である。

【図24】可変容量素子の振動防止動作を説明する図である。

【図25】(A)〜(H)は第5の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図26】(I)〜(M)は第5の実施の形態に係る可変容量素子の製造方法を説明するための工程図である。

【図27】本発明の第6の実施の形態に係る可変容量素子の部分拡大図である。

【図28】(A)及び(B)は第6の実施の形態に係る可変容量素子の製造方法を説明するため図である。

【図29】可変容量素子の振動防止動作を説明する図である。

【図30】第5の実施の形態の変形例の構成を示す図である。

【図31】第6の実施の形態の変形例の構成を示す図である。

【符号の説明】

【0199】

10 可変容量素子

10A 可変容量素子

10B 可変容量素子

10C 可変容量素子

12 支持基板

13 Si3N4絶縁層

14 駆動電極

15 SiO2犠牲膜

16 固定電極

16A 櫛歯部

17 Poly-Si層

18 可動電極

18A 櫛歯部

19 リリースホール

20 ブレーキ・キャパシタ

21 Poly-Si層

22 上部ブレーキ電極

22A 櫛歯部

23 溝部

24 下部ブレーキ電極

24A 櫛歯部

25 窒化シリコン(Si3N4)層

26 誘電体

27 リリースホール

28 誘電体層

30 支柱

32 アンカー部

34 梁部

36 ばね部材

40 電源

42 電源

44 チューナブル・キャパシタ

46 駆動キャパシタ

46A 駆動キャパシタ

46B 駆動キャパシタ

50 絶縁層

52 可動駆動電極

60 誘電層

70 可変容量素子