可変容量装置

【課題】 3つ以上のキャパシタンス値が得られると共に、装置の小型化と信号損失の低減が可能な可変容量装置を提供する。

【解決手段】 可変容量素子2の駆動容量C1は、駆動電圧制御回路31から出力される駆動電圧Vdに応じて変化する。駆動電圧制御回路31は、駆動容量C1の検出値と目標値とを比較する比較器32と、比較器32の比較結果に応じた駆動電圧Vdを発生させる駆動電圧発生回路34とを備える。駆動電圧発生回路34の電流出力型レベル変換回路35は、比較器32の比較結果に応じて平滑化容量45にソース電流i10またはシンク電流i20を流し、駆動電圧Vdを昇圧または降圧する。また、電流出力型レベル変換回路35は、過渡状態から定常状態に移行するときに、ソース電流i10またはシンク電流i20の電流値を徐々に小さくする。

【解決手段】 可変容量素子2の駆動容量C1は、駆動電圧制御回路31から出力される駆動電圧Vdに応じて変化する。駆動電圧制御回路31は、駆動容量C1の検出値と目標値とを比較する比較器32と、比較器32の比較結果に応じた駆動電圧Vdを発生させる駆動電圧発生回路34とを備える。駆動電圧発生回路34の電流出力型レベル変換回路35は、比較器32の比較結果に応じて平滑化容量45にソース電流i10またはシンク電流i20を流し、駆動電圧Vdを昇圧または降圧する。また、電流出力型レベル変換回路35は、過渡状態から定常状態に移行するときに、ソース電流i10またはシンク電流i20の電流値を徐々に小さくする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、駆動電圧に応じて静電容量が変化する可変容量素子を備えた可変容量装置に関する。

【背景技術】

【0002】

一般に、高周波通信用のマッチング回路に可変容量素子を用いる場合、マッチング可能な範囲を広くしたり、マッチングのための容量設定分解能を向上させるために、できる限り多くのキャパシタンス値を得られた方がよい。ここで、3つ以上のキャパシタンス値を得るには、2値の可変容量素子を複数個並列に接続するか、1個の可変容量素子で3つ以上のキャパシタンス値を得る構造にする必要がある。例えば特許文献1には、2値のキャパシタンス値を切り換える可変容量素子を開示されている。このような可変容量素子は、駆動電圧の印加により、対向電極同士を、誘電体層を介して接触または離間させる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−70940号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、特許文献1による可変容量素子を用いて多数のキャパシタンス値を得るためには、多数個の可変容量素子を形成すると共に、これらを接続する接続パターンを形成しなければならず、装置全体が大型化する傾向がある。また、接続パターンによる信号損失も無視できない値になるという問題がある。

【0005】

本発明は上述の問題に鑑みなされたものであり、本発明の目的は、3つ以上のキャパシタンス値が得られると共に、装置の小型化と信号損失の低減が可能な可変容量装置を提供することにある。

【課題を解決するための手段】

【0006】

上記課題を解決するために、請求項1の発明は、駆動電圧に応じて静電容量が変化する可変容量素子と、該可変容量素子の静電容量を検出する容量検出回路と、該容量検出回路による静電容量の検出値が所望の目標値に近付くように前記駆動電圧を制御する駆動電圧制御回路とを備えた可変容量装置において、前記駆動電圧制御回路は、前記静電容量の検出値と目標値とを比較する比較器と、該比較器の比較結果に応じてソース電流またはシンク電流を流す電流出力型レベル変換回路と、該電流出力型レベル変換回路がソース電流を流したときに前記駆動電圧を昇圧しシンク電流を流したときに前記駆動電圧を降圧する平滑化容量からなる電流電圧変換回路とを備え、前記電流出力型レベル変換回路は、過渡状態から定常状態に移行するときに、ソース電流およびシンク電流の電流値を徐々に小さくする構成としたことを特徴としている。

【0007】

請求項2の発明では、前記駆動電圧制御回路は、前記比較器の比較結果の切り換わりをカウントするカウンタ回路を備え、該カウンタ回路は、リセット信号によってカウント数がリセットされると、前記駆動電圧制御回路の電流値を過渡状態の大きさに設定し、比較結果の切り換わりをカウントする度に前記駆動電圧制御回路の電流値を小さくして、最終的に前記駆動電圧制御回路の電流値を過渡状態の大きさよりも小さい定常状態の大きさに収束させる構成としている。

【0008】

請求項3の発明では、前記電流出力型レベル変換回路は、前記カウンタ回路によって電流値が設定される可変電流源と、該可変電流源に流れる電流をコピーするカレントミラー回路と、前記比較器の比較結果に応じてソース電流回路とシンク電流回路とのうちいずれか一方を動作させ該カレントミラー回路を流れる電流に応じたソース電流またはシンク電流を流す電流出力回路とを備える構成としている。

【発明の効果】

【0009】

請求項1の発明では、駆動電圧に応じて可変容量素子の静電容量を連続的に変化させることができ、3つ以上のキャパシタンス値を得ることができる。また、複数の可変容量素子を接続する必要がなく、信号損失を低減することができる。さらに、電流出力型レベル変換回路によってソース電流またはシンク電流を流し、ソース電流とシンク電流によって駆動電圧を変化させる構成としたから、一般的な駆動電圧の発生手段として、例えば電圧レベル変換回路と、抵抗および容量からなる低域通過フィルタ回路とによって駆動電圧を発生させた場合に比べて、低域通過フィルタ回路の抵抗が不要になり、装置全体を小型化することができる。

【0010】

また、電流出力型レベル変換回路は、過渡状態から定常状態に移行するときに、ソース電流およびシンク電流の電流値を徐々に小さくする構成とした。このため、過渡状態ではソース電流およびシンク電流の電流値を大きくして、平滑化容量の充電量と放電量を増加させることができる。これにより、可変容量素子の静電容量を速やかに目標値に近付けることができ、静電容量が目標値に収束するまでの安定時間を短縮することができる。一方、過渡状態から定常状態に移行するときには、ソース電流およびシンク電流の電流値を徐々に小さくして、平滑化容量の充電量と放電量を減少させることができる。これにより、定常状態ではソース電流およびシンク電流の電流値を小さくして、目標値に対する静電容量の変動を小さくすることができ、容量精度を高めることができる。

【0011】

請求項2の発明では、カウンタ回路は、リセット信号によってカウント数がリセットされると、電流出力型レベル変換回路の電流値を過渡状態の大きさに設定する。このため、カウント数がリセットされた直後は、ソース電流およびシンク電流の電流値を大きくして、静電容量の検出値を目標値に向けて速やかに変化させることができる。

【0012】

また、カウンタ回路は、比較結果の切り換わりをカウントする度にソース電流およびシンク電流の電流値を徐々に小さくして、目標値に対する静電容量の変動幅を徐々に小さくすることができる。そして、最終的にソース電流およびシンク電流の電流値を過渡状態の大きさよりも小さい定常状態の大きさに収束させるから、定常状態ではソース電流およびシンク電流の電流値を小さくして、目標値に対する静電容量の変動を小さくすることができ、容量精度を高めることができる。

【0013】

請求項3の発明では、電流出力型レベル変換回路は、可変電流源と、カレントミラー回路と、電流出力回路とを備える構成とした。このため、カウンタ回路によって可変電流源の電流値を設定すると共に、可変電流源に流れる電流をカレントミラー回路によってコピーすることができる。そして、電流出力回路は、比較器の比較結果に応じてソース電流回路とシンク電流回路とのうちいずれか一方を動作させるから、ソース電流回路の動作時にはカレントミラー回路を流れる電流に応じたソース電流を流すことができ、シンク電流回路が動作時にはカレントミラー回路を流れる電流に応じたシンク電流を流すことができる。

【図面の簡単な説明】

【0014】

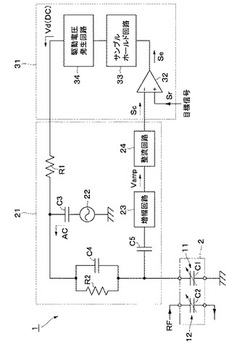

【図1】本発明の実施の形態による可変容量装置を示す全体構成図である。

【図2】図1中の可変容量素子を示す平面図である。

【図3】可変容量素子を図2中の矢示III−III方向からみた断面図である。

【図4】図1中の駆動電圧発生回路を示す回路図である。

【図5】設定開始時の駆動容量のキャパシタンス値が目標値に比べて小さい場合について、駆動容量、駆動電圧、比較結果信号、電流制御信号の時間変化を示す特性線図である。

【図6】設定開始時の駆動容量のキャパシタンス値が目標値に比べて大きい場合について、駆動容量、駆動電圧、比較結果信号、電流制御信号の時間変化を示す特性線図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態による可変容量装置について添付図面を参照しつつ詳細に説明する。

【0016】

図1は実施の形態による可変容量装置1を示している。この可変容量装置1は、可変容量素子2、容量検出回路21および駆動電圧制御回路31を備える。

【0017】

まず、図2および図3を用いて、可変容量素子2について説明する。

【0018】

可変容量素子2は、静電力による駆動するMEMS(Micro Electro Mechanical Systems)によって構成される。この可変容量素子2は、基板3、下駆動電極4A,4B,5、誘電体膜6、梁部7、パッド電極8,9A,9B,10A,10B、および抵抗パターン10C,10Dを備える。

【0019】

基板3は例えば矩形ガラス基板からなる。梁部7は、平面視して矩形平板状で、側面視してL字状に形成される。この梁部7は、図2中の右側の端部が基板3に接合される支持部となって、要部を基板3から離間した状態で支持する片持梁構造(バネ構造)の可動構造部である。また、梁部7は、導電性基板として例えば抵抗率0.01Ωcm以下の低抵抗Si基板(シリコン基板)からなり、ドーパントとして例えばP(リン)、As(ヒ素)、B(ホウ素)等を用いている。

【0020】

下駆動電極4A,4Bは、それぞれL字状で基板3の上面に形成され、梁部7の軸方向(図2中の左,右方向)に沿って長尺な線路状の端部を有する。下駆動電極5は、コ字状で基板3の上面に形成し、梁部7の軸方向に沿って長尺な線路状の両端部で下駆動電極4A,4Bの両脇を挟み込むように配置する。誘電体膜6は、例えば矩形状で厚み200nm程度の五酸化タンタルによって形成され、下駆動電極4A,4Bの端部と下駆動電極5の両端部とを覆うように基板3に積層される。下駆動電極4Aは、RF信号(高周波信号)の入力端子(または出力端子)にパッド電極9Aを介して接続され、下駆動電極4Bは、RF信号の出力端子(または入力端子)にパッド電極9Bを介して接続される。下駆動電極5は、パッド電極10Aおよび抵抗パターン10Cを介して駆動電圧VdとなるDC電圧(直流電圧)の入力端に接続される。梁部7は、パッド電極8,10B、および抵抗パターン10Dを介してグランドに接続される。抵抗パターン10C,10Dは、例えば厚み5nm程度の酸化チタン薄膜を用いて形成され、200kΩ程度の抵抗を有する。

【0021】

下駆動電極5の両端部は、梁部7に誘電体膜6を介して対向して配置され、これらの下駆動電極5および梁部7は駆動容量部11を構成する。駆動容量部11は、駆動電圧制御回路31から駆動電圧Vdが印加されると、下駆動電極5の両端部と梁部7との間に駆動容量C1(静電容量)を生じる。駆動容量C1は、静電引力によって梁部7を変形させ、梁部7を先端から誘電体膜6に接触させる。駆動電圧Vdが高電圧であるほど、梁部7と誘電体膜6との接触面積は大きくなる。

【0022】

下駆動電極4A,4Bは、梁部7に誘電体膜6を介して対向して配置され、これらの下駆動電極4A,4Bおよび梁部7は可変容量部12を構成する。可変容量部12は、例えば数百MHz〜数GHzの無線周波数を扱う回路の中で使用され、梁部7と誘電体膜6との接触面積に応じて変化する可変容量C2(静電容量)を生じる。可変容量部12からは、梁部7を介して駆動電圧制御回路31やグランドに高周波信号が漏洩する虞れがあるため、ここでは漏洩高周波信号を遮断する目的で抵抗パターン10C,10Dを形成している。

【0023】

図2に示す駆動容量部11の構造は、下駆動電極5と梁部7からなる電極対の間に信号(電圧)が直接印加される構造である(以下、この構造をMIM構造という)。また、可変容量部12の構造は、下駆動電極4Aと梁部7、下駆動電極4Bと梁部7からなる2組の電極対を直列に接続して、信号(電圧)が直接印加される構造である(以下、この構造をMIMIM構造という)。MIMIM構造は、MIM構造に比べて面積当りの静電引力が約1/4と小さく、セルフアクチュエーションによる梁部7の変形を抑制するのに有利である。一方、MIM構造は、MIMIM構造に比べて面積当りの静電引力が大きく、電極面積の低減に有利である。従って、大きな静電引力が必要となる駆動容量部11にはMIM構造を採用し、静電引力を抑制する必要がある可変容量部12にはMIMIM構造を採用するのが好ましい。

【0024】

なお、駆動容量部11および可変容量部12は、それぞれMIM構造、MIMIM構造のいずれの構造を採用してもよい。また、駆動容量部11の駆動容量C1と可変容量部12の可変容量C2は一緒に変化する。このため、駆動容量C1のキャパシタンス値は可変容量C2のキャパシタンス値と対応した値になる。

【0025】

次に、図1を用いて、容量検出回路21について説明する。

【0026】

容量検出回路21は、容量検出用交流信号源22、増幅回路23、および整流回路24を備える。容量検出用交流信号源22は、交流源となり、例えば約10MHzの容量検出用のAC信号(交流信号)を直流遮断用の容量C3(約100pF)に出力する。容量C3の出力端は、交流遮断用の抵抗R1を介して直流源となる駆動電圧発生回路34に接続される。このため、抵抗R1と容量C3との接続点で、駆動電圧発生回路34からのDC信号(駆動電圧Vd)に容量検出用のAC信号が重畳される。この重畳信号は、直流バイパス用の抵抗R2、および参照容量C4からなる並列回路に入力される。この並列回路の出力端には可変容量素子2の駆動容量C1が接続され、抵抗R2、参照容量C4、および駆動容量C1からなる容量回路を構成している。

【0027】

重畳信号のうちのDC成分となる駆動電圧Vdは、直流バイパス用の抵抗R2を介して駆動容量C1に印加され、静電引力により可変容量素子2における梁部7を変形させる。重畳信号のうちのAC成分は、参照容量C4と駆動容量C1で電圧分配され、両者の容量比に応じた振幅として参照容量C4と駆動容量C1との接続点から直流遮断用の容量C5に出力される。

【0028】

直流遮断用の容量C5の出力端には増幅回路23が接続され、増幅回路23は容量回路における電圧分配点からのAC出力の電圧レベルを増幅して増幅電圧Vampを出力する。増幅回路23の入力部には入力インピーダンスが非常に高いボルテージホロワ(図示せず)を設けていて、容量回路のAC出力を参照容量C4と駆動容量C1とで単純に電圧分配した電圧レベルにしている。増幅回路23で増幅された増幅電圧Vampは、整流回路24で整流される。増幅回路23の増幅率や、参照容量C4、容量検出用交流信号源22の電圧レベルを既知とすれば、整流回路24の出力する直流電圧は、駆動容量C1の容量を一意に反映した電圧レベルとなり、駆動容量C1が大きいほど電圧レベルが低くなる。このため、整流回路24の出力する直流電圧は、駆動容量C1を検出した検出信号Scとなり、検出信号Scの電圧レベルは、駆動容量C1の検出値に対応する。

【0029】

次に、図1を用いて、駆動電圧制御回路31について説明する。

【0030】

駆動電圧制御回路31は、比較器32、サンプルホールド回路33、および駆動電圧発生回路34を備える。

【0031】

比較器32には、駆動容量C1の目標値を指示するための目標信号Srが外部入力電圧として入力されると共に、整流回路24からの検出信号Scが入力される。この比較器32は、目標信号Srの電圧レベルと検出信号Scの電圧レベルとを比較して、これらの比較結果に応じた比較結果信号Seを出力する。このため、比較結果信号Seは、駆動容量C1の検出値と目標値との比較結果に応じて、LowレベルまたはHighレベルに切り換わる。例えば検出信号Scが目標信号Srよりも小さな電圧レベルである場合、即ち、駆動容量C1が目標値よりも大きな場合には、比較結果信号SeはHighレベルとなる。逆に、検出信号Scが目標信号Srよりも大きな電圧レベルである場合、即ち、駆動容量C1が目標値よりも小さな場合、比較結果信号SeはLowレベルとなる。比較器32の出力端は、比較結果信号Seを一定時間保持するサンプルホールド回路33を介して駆動電圧発生回路34に入力される。

【0032】

駆動電圧発生回路34は、比較器32の比較結果信号Seに応じて駆動電圧Vdを増加または減少させる。比較器32の比較結果信号SeがHighレベルであれば、駆動電圧Vdを低下させて駆動容量C1を減少させる方向に調整する。逆に、比較器32の比較結果信号SeがLowレベルであれば、駆動電圧Vdを上昇させて駆動容量C1を増加させる方向に調整する。

【0033】

次に、図4を用いて、駆動電圧発生回路34について説明する。

【0034】

駆動電圧制御回路34は、電流出力型レベル変換回路35、および電流電圧変換回路44を備える。

【0035】

電流出力型レベル変換回路35は、カウンタ回路36、可変電流源37、カレントミラー回路38、および電流出力回路39を備える。カウンタ回路36は、比較器32の比較結果の切り換わりをカウントし、カウント数に応じた電流制御信号X0〜X5を出力する。ここで、駆動容量C1が目標値に向けて変化している過渡状態では、電流制御信号X0〜X4はいずれかがHighレベルとなり、電流制御信号X5はLowレベルとなる。一方、駆動容量C1が目標値付近で安定した定常状態では、電流制御信号X0〜X4はLowレベルとなり、電流制御信号X5はHighレベルとなる。また、カウンタ回路36は、リセット信号RSの入力端を備え、リセット信号RSが入力されたときにカウント数をリセットする。

【0036】

可変電流源37は、カウンタ回路36からの電流制御信号X0〜X5に応じて電流値Ia〜Ifのいずれかが設定され、電流値Ia〜Ifに応じた電流iを流す。ここで、電流値Ia〜Ifは、以下の数1に示すように、電流値Iaから電流値Ifに向かうに従って順次小さい値に設定されている。

【0037】

【数1】

【0038】

電流値Ia〜Ieは過渡状態で流す電流iの大きさであり、電流値Ifは定常状態で流す電流iの大きさである。このため、過渡状態に応じて電流制御信号X0〜X4のいずれかがHighレベルとなるときに、電流値Ia〜Ieが設定される。一方、定常状態に応じて電流制御信号X5がHighレベルとなるときに、電流値Ifが設定される。定常状態の電流値Ifは、過渡状態のいずれの電流値Ia〜Ieよりも小さい(If<Ia〜Ie)。

【0039】

カレントミラー回路38は、3個のMOSスイッチMP1〜MP3を用いて構成され、可変電流源37に流れる電流iをコピーする。MOSスイッチMP1〜MP3は、pチャネルMOSFETからなり、ソース同士が互いに接続されると共に、ゲート同士が互いに接続される。また、MOSスイッチMP1のドレインは、可変電流源37に接続されると共に、MOSスイッチMP1〜MP3のゲートに接続される。これにより、MOSスイッチMP1に可変電流源37の電流iが流れたときには、MOSスイッチMP2,MP3のドレイン−ソース間にも、可変電流源37の電流iと同じ大きさの電流i1,i2が流れる。

【0040】

電流出力回路39は、選択回路40、ソース電流回路42、およびシンク電流回路43を備える。選択回路40は、比較結果信号Seに応じてソース電流回路42とシンク電流回路43のうちいずれか一方を選択的に動作させる。具体的には、選択回路40は、いずれか一方が選択的に動作する2個のMOSスイッチMN1,MN2と、NOT回路41とによって構成される。

【0041】

MOSスイッチMN1,MN2は、nチャネルMOSFETからなり、MOSスイッチMP2,MP3にそれぞれ直列接続される。具体的には、MOSスイッチMN1のドレインは、MOSスイッチMP2のドレインに接続される。このため、MOSスイッチMN1のドレイン−ソース間には、MOSスイッチMP2と同じ電流i1が流れる。また、MOSスイッチMN2のドレインはMOSスイッチMP3のドレインに接続される。このため、MOSスイッチMN2のドレイン−ソース間には、MOSスイッチMP3と同じ電流i2が流れる。

【0042】

MOSスイッチMN1のゲートには、NOT回路41を介して比較結果信号Seが入力される。このため、MOSスイッチMN1は、比較結果信号SeがHighレベルのときにOFFとなり、比較結果信号SeがLowレベルのときにONとなる。一方、MOSスイッチMN2のゲートには、比較結果信号Seが直接入力される。このため、MOSスイッチMN1は、比較結果信号SeがHighレベルのときにONとなり、比較結果信号SeがLowレベルのときにOFFとなる。この結果、2個のMOSスイッチMN1,MN2は、互いに逆の動作状態となり、インバータ動作する。

【0043】

ソース電流回路42は、第1のカレントミラー回路42Aと、第2のカレントミラー回路42Bとを備える。第1のカレントミラー回路42Aは、2個のMOSスイッチMN3,MN4によって構成される。MOSスイッチMN3,MN4は、それぞれnチャネルMOSFETからなり、ソースがいずれもグランドに接続されると共に、ゲート同士が互いに接続される。また、MOSスイッチMN3のドレインは、MOSスイッチMN1のソースに接続されると共に、MOSスイッチMN3,MN4のゲートに接続される。これにより、MOSスイッチMN1がONとなり、MOSスイッチMP2の電流i1が流れたときには、MOSスイッチMN3,MN4のドレイン−ソース間にも、MOSスイッチMP2の電流i1と同じ大きさの電流が流れる。

【0044】

第2のカレントミラー回路42Bは、2個のMOSスイッチMP4,MP5によって構成される。MOSスイッチMP4,MP5は、pチャネルMOSFETからなり、ソースがいずれも高電圧源(図示せず)に接続されると共に、ゲート同士が互いに接続される。このとき、MOSスイッチMP4,MP5のソースには、駆動電圧Vdの最大値よりも高い電圧Vhが印加される。また、MOSスイッチMP4のドレインは、MOSスイッチMN4のドレインに接続されると共に、MOSスイッチMP4,MP5のゲートに接続される。これにより、MOSスイッチMN4に流れた電流は、MOSスイッチMP4を通じてMOSスイッチMP5にコピーされる。

【0045】

さらに、MOSスイッチMP5のドレインは、電流電圧変換回路44の平滑化容量45に接続される。これにより、ソース電流回路42は、MOSスイッチMN1がONになったときに、MOSスイッチMP2の電流i1を第1,第2のカレントミラー回路42A,42Bによってコピーし、電流i1と同じ大きさのソース電流i10を平滑化容量45に向けて流入させる。

【0046】

シンク電流回路43は、2個のMOSスイッチMN5,MN6からなり、ソース電流回路42の第1のカレントミラー回路42Aとほぼ同様に構成される。このため、MOSスイッチMN5,MN6は、それぞれnチャネルMOSFETからなり、ソースがいずれもグランドに接続されると共に、ゲート同士が互いに接続される。また、MOSスイッチMN5のドレインは、MOSスイッチMN2のソースに接続されると共に、MOSスイッチMN5,MN6のゲートに接続される。これにより、MOSスイッチMN2がONとなり、MOSスイッチMP3の電流i2が流れたときには、MOSスイッチMN5,MN6のドレイン−ソース間にも、MOSスイッチMP3の電流i2と同じ大きさの電流が流れる。

【0047】

さらに、MOSスイッチMN6のドレインは、電流電圧変換回路44の平滑化容量45に接続される。これにより、ソース電流回路42は、MOSスイッチMN2がONになったときに、MOSスイッチMP3の電流i2をMOSスイッチMN5,MN6によってコピーし、電流i2と同じ大きさのシンク電流i20を平滑化容量45から流出させる。

【0048】

電流電圧変換回路44は、平滑化容量45を備える。平滑化容量45は、一端が電流出力回路39の出力端に接続され、他端がグランドに接続される。平滑化容量45の一端は、抵抗R1,R2を介して駆動容量C1に接続される。これにより、平滑化容量45は、駆動容量C1に向けて駆動電圧Vdを出力する。また、平滑化容量45は、ソース電流i10によって充電され、シンク電流i20によって放電される。このため、電流出力型レベル変換回路35がソース電流i10を流したときには駆動電圧Vdは昇圧し、シンク電流i20を流したときには駆動電圧Vdは降圧する。

【0049】

本発明の実施の形態による可変容量装置1は以上のような構成を有するものであり、次に駆動容量C1の設定動作について説明する。

【0050】

図5は、設定開始時の駆動容量C1のキャパシタンス値が目標値に比べて小さい場合を示している。カウンタ回路36にリセット信号RSが入力された時点t0から最初の比較結果の切り換わりが生じる時点t1までの動作は次のようになる。

【0051】

駆動容量C1の設定が開始されると、カウンタ回路36にリセット信号RSが入力され、カウンタ回路36は、電流制御信号X0をHighレベルとし、電流制御信号X1〜X5をLowレベルにする。これにより、可変電流源37は、過渡状態で最大の電流値Iaとなった電流iを流す。

【0052】

また、設定開始時では駆動容量C1のキャパシタンス値が目標値に比べて小さいから、比較器32はLowレベルの比較結果信号Seを出力する。このため、選択回路40によってソース電流回路42が選択され、電流値Iaに応じたソース電流i10が流れる。これにより、平滑化容量45は充電される。過渡状態の電流値Iaは定常状態の電流値Ifに比べて大きいから、定常状態よりも大きなソース電流i10が流れて、駆動容量C1は目標値に向けて速やかに変化する。

【0053】

ここで、駆動電圧Vdが駆動容量C1の目標値に対応した目標電圧値に達しても、可変容量素子2の動作遅延や容量検出回路21の信号応答遅延によって駆動容量C1は目標値に到達しない。このため、駆動電圧Vdは、目標電圧値を超えて増加し、オーバーシュート電圧が生じる。そして、駆動容量C1が目標値を超えて、容量検出回路21による検出信号Scの検出値が目標信号Srの目標値よりも大きくなると、比較器32による比較結果信号SeがLowレベルからHighレベルに切り換わり、次フェーズに移行する。

【0054】

最初の比較結果の切り換わりが生じた時点t1から2回目の比較結果の切り換わりが生じる時点t2までの動作は次のようになる。

【0055】

比較結果信号SeがLowレベルからHighレベルに切り換わると、カウンタ回路36のカウント数が1つ増加する。このとき、カウンタ回路36は、Highレベルとなった電流制御信号X1を出力し、電流制御信号X0,X2〜X5をLowレベルにする。このため、カウンタ回路36によって、電流値Iaよりも小さい電流値Ibに切り換わり、可変電流源37は、電流値Ibとなった電流iを流す。

【0056】

また、比較器32はHighレベルの比較結果信号Seを出力する。このため、選択回路40によってシンク電流回路43が選択され、電流値Ibに応じたシンク電流i20が流れる。これにより、平滑化容量45は放電されて、駆動電圧Vdが目標電圧値を超えて減少し、アンダーシュート電圧が生じる。このとき、電流値Ibは電流値Iaよりも小さいから、時点t2でのアンダーシュート電圧は、時点t1でのオーバーシュート電圧よりも小さくなる。そして、駆動容量C1が目標値を超え、容量検出回路21による検出信号Scの検出値が目標信号Srの目標値よりも小さくなると、比較器32による比較結果信号SeがHighレベルからLowレベルに切り換わり、次フェーズに移行する。

【0057】

2回目の比較結果の切り換わりが生じる時点t2から5回目の比較結果の切り換わりが生じる時点t5までの動作は次のようになる。

【0058】

2回目の比較結果の切り換わりが生じる時点t2では、カウンタ回路36は、電流制御信号X2をHighレベルにし、電流制御信号X0,X1,X3〜X5をLowレベルにする。このため、カウンタ回路36によって、電流値Ibよりも小さい電流値Icに切り換わり、可変電流源37は、電流値Icとなった電流iを流す。このとき、比較器32はLowレベルの比較結果信号Seを出力するから、選択回路40によってソース電流回路42が選択され、電流値Icに応じたソース電流i10が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて増加する。

【0059】

3回目の比較結果の切り換わりが生じる時点t3では、カウンタ回路36は、電流制御信号X3をHighレベルにし、電流制御信号X0〜X2,X4,X5をLowレベルにする。このため、カウンタ回路36によって、電流値Icよりも小さい電流値Idに切り換わり、可変電流源37は、電流値Idとなった電流iを流す。このとき、比較器32はHighレベルの比較結果信号Seを出力するから、選択回路40によってシンク電流回路43が選択され、電流値Idに応じたシンク電流i20が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて減少する。

【0060】

4回目の比較結果の切り換わりが生じる時点t4では、カウンタ回路36は、電流制御信号X4をHighレベルにし、電流制御信号X0〜X3,X5をLowレベルにする。このため、カウンタ回路36によって、電流値Idよりも小さい電流値Ieに切り換わり、可変電流源37は、電流値Ieとなった電流iを流す。このとき、比較器32はLowレベルの比較結果信号Seを出力するから、選択回路40によってソース電流回路42が選択され、電流値Ieに応じたソース電流i10が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて増加する。

【0061】

5回目の比較結果の切り換わりが生じる時点t5では、カウンタ回路36は、電流制御信号X5をHighレベルにし、電流制御信号X0〜X4をLowレベルにする。このため、カウンタ回路36によって、電流値Ieよりも小さい電流値Ifに切り換わり、可変電流源37は、電流値Ifとなった電流iを流す。このとき、比較器32はHighレベルの比較結果信号Seを出力するから、選択回路40によってシンク電流回路43が選択され、電流値Ifに応じたシンク電流i20が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて減少する。そして、時点t2〜t5に移行するに従って、オーバーシュート電圧やアンダーシュート電圧は徐々に小さくなる。

【0062】

5回目の比較結果の切り換わりが生じる時点t5以降の動作は次のようになる。

【0063】

カウンタ回路36は、Highレベルとなった電流制御信号X5を出力し、電流制御信号X0〜X4をLowレベルにする。このため、カウンタ回路36によって、過渡状態の電流値Ia〜Ieよりも小さい定常状態の電流値Ifが設定されるから、可変電流源37は、電流値Ifとなった電流iを流す。このとき、電流出力型レベル変換回路35は、比較結果信号Seに応じてソース電流回路42とシンク電流回路43のうちいずれか一方を選択的に動作させ、比較結果信号SeがLowレベルのときに電流値Ifとなったソース電流i10を流し、比較結果信号SeがHighレベルのときに電流値Ifとなったシンク電流i20を流す。定常状態の電流値Ifは過渡状態の電流値Ia〜Ieよりも小さいから、目標値に対する駆動電圧Vdの変動幅は小さくなり、高い容量精度を得ることができる。このように、電流出力型レベル変換回路35は、駆動電圧Vdが目標電圧値に近付くように、フィードバック動作を行う。

【0064】

図6は、設定開始時の駆動容量C1のキャパシタンス値が目標値に比べて大きい場合を示している。この場合でも、前述した設定開始時の駆動容量C1のキャパシタンス値が目標値に比べて小さい場合とほぼ同様に動作する。

【0065】

以上説明した通り、本実施の形態による可変容量装置1によれば、駆動電圧Vdに応じて駆動容量C1や可変容量C2のキャパシタンス値を連続的に変化させることができ、3つ以上のキャパシタンス値を得ることができる。また、ソース電流i10とシンク電流i20によって駆動電圧Vdを変化させる構成としたから、例えば抵抗と容量からなる低域通過フィルタ回路を用いて駆動電圧を発生させた場合に比べて、装置全体を小型化することができる。

【0066】

具体的に説明すると、一般的に、集積回路において、受動素子である抵抗やコンデンサは大型化する傾向がある。本実施の形態による可変容量装置1では、このような受動素子である抵抗を省くことができ、装置全体を小型化することができる。

【0067】

また、一般的に、過渡状態から定常状態に移行するまでの安定時間と、駆動容量C1の容量精度はトレードオフの関係にある。このため、低域通過フィルタ回路の抵抗値を小さく、またはキャパシタンス値を大きくして、安定時間を短縮すると、容量精度は低下する。逆に、低域通過フィルタ回路の抵抗値を大きく、またはキャパシタンス値を小さくして、容量精度を高めると、安定時間が長くなる。

【0068】

これに対し、本実施の形態では、電流出力型レベル変換回路35は、過渡状態から定常状態に移行するときに、ソース電流i10およびシンク電流i20の電流値を徐々に小さくする構成とした。このため、例えば設定開始時のように過渡状態の初期段階ではソース電流i10およびシンク電流i20の電流値Iaを大きくして、平滑化容量の充電量と放電量を増加させることができる。これにより、可変容量素子2の駆動容量C1を速やかに目標値に近付けることができ、駆動容量C1が目標値に収束するまでの安定時間を短縮することができる。一方、過渡状態から定常状態に移行するときには、電流値Ia〜Ifを順次切り換えるから、ソース電流i10およびシンク電流i20の電流値を徐々に小さくして、平滑化容量の充電量と放電量を減少させることができる。そして、定常状態ではソース電流i10およびシンク電流i20の電流値を最も小さい電流値Ifに設定するから、目標値に対する駆動容量C1の変動を小さくすることができ、容量精度を高めることができる。この結果、高い容量精度を実現しながら、目標値に収束するまでの安定時間を短縮することができる。

【0069】

なお、前記実施の形態では、電流出力型レベル変換回路35はMOSFETを用いて構成したが、例えばバイポーラトランジスタジス等の他のスイッチ素子を用いて構成してもよい。

【0070】

また、前記実施の形態では、可変容量素子2の駆動容量C1を検出して駆動容量C1を変化させる構成としたが、可変容量C2を検出して駆動容量C1を変化させる構成としてもよい。また、駆動容量C1と可変容量C2を共通化した単一の可変容量を設け、この可変容量を検出し、変化させる構成としてもよい。

【0071】

また、前記実施の形態では、5回目の比較結果の切り換わりが生じる時点t5で定常状態の電流値Ifに収束させる構成とした。しかし、本発明はこれに限らず、例えば2回目〜4回目の比較結果の切り換わりが生じる時点t2〜t4で定常状態の電流値に収束させる構成としてもよく、6回目以降の任意のn回目の比較結果の切り換わりが生じる時点tnで定常状態の電流値に収束させる構成としてもよい。

【0072】

また、前記実施の形態では、可変電流源37の電流iを変化させることによってソース電流i10およびシンク電流i20を変化させる構成としたが、電流源の電流値を固定したまま、ソース電流i10およびシンク電流i20を変化させる構成としてもよい。この場合、例えばソース電流回路42のカレントミラー回路42Bを複数個並列に接続し、これら複数個のカレントミラー回路42Bのうち動作する個数を増加または減少させることによって、ソース電流i10を変化させる構成としてもよい。同様に、シンク電流回路43をなすカレントミラー回路を複数個並列に接続し、これら複数個のカレントミラー回路のうち動作する個数を増加または減少させることによって、シンク電流i20を変化させる構成としてもよい。

【符号の説明】

【0073】

1 可変容量装置

2 可変容量素子

21 容量検出回路

31 駆動電圧制御回路

32 比較器

35 電流出力型レベル変換回路

36 カウンタ回路

37 可変電流源

38 カレントミラー回路

39 電流出力回路

40 選択回路

42 ソース電流回路

43 シンク電流回路

44 電流電圧変換回路

45 平滑化容量

【技術分野】

【0001】

本発明は、駆動電圧に応じて静電容量が変化する可変容量素子を備えた可変容量装置に関する。

【背景技術】

【0002】

一般に、高周波通信用のマッチング回路に可変容量素子を用いる場合、マッチング可能な範囲を広くしたり、マッチングのための容量設定分解能を向上させるために、できる限り多くのキャパシタンス値を得られた方がよい。ここで、3つ以上のキャパシタンス値を得るには、2値の可変容量素子を複数個並列に接続するか、1個の可変容量素子で3つ以上のキャパシタンス値を得る構造にする必要がある。例えば特許文献1には、2値のキャパシタンス値を切り換える可変容量素子を開示されている。このような可変容量素子は、駆動電圧の印加により、対向電極同士を、誘電体層を介して接触または離間させる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−70940号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、特許文献1による可変容量素子を用いて多数のキャパシタンス値を得るためには、多数個の可変容量素子を形成すると共に、これらを接続する接続パターンを形成しなければならず、装置全体が大型化する傾向がある。また、接続パターンによる信号損失も無視できない値になるという問題がある。

【0005】

本発明は上述の問題に鑑みなされたものであり、本発明の目的は、3つ以上のキャパシタンス値が得られると共に、装置の小型化と信号損失の低減が可能な可変容量装置を提供することにある。

【課題を解決するための手段】

【0006】

上記課題を解決するために、請求項1の発明は、駆動電圧に応じて静電容量が変化する可変容量素子と、該可変容量素子の静電容量を検出する容量検出回路と、該容量検出回路による静電容量の検出値が所望の目標値に近付くように前記駆動電圧を制御する駆動電圧制御回路とを備えた可変容量装置において、前記駆動電圧制御回路は、前記静電容量の検出値と目標値とを比較する比較器と、該比較器の比較結果に応じてソース電流またはシンク電流を流す電流出力型レベル変換回路と、該電流出力型レベル変換回路がソース電流を流したときに前記駆動電圧を昇圧しシンク電流を流したときに前記駆動電圧を降圧する平滑化容量からなる電流電圧変換回路とを備え、前記電流出力型レベル変換回路は、過渡状態から定常状態に移行するときに、ソース電流およびシンク電流の電流値を徐々に小さくする構成としたことを特徴としている。

【0007】

請求項2の発明では、前記駆動電圧制御回路は、前記比較器の比較結果の切り換わりをカウントするカウンタ回路を備え、該カウンタ回路は、リセット信号によってカウント数がリセットされると、前記駆動電圧制御回路の電流値を過渡状態の大きさに設定し、比較結果の切り換わりをカウントする度に前記駆動電圧制御回路の電流値を小さくして、最終的に前記駆動電圧制御回路の電流値を過渡状態の大きさよりも小さい定常状態の大きさに収束させる構成としている。

【0008】

請求項3の発明では、前記電流出力型レベル変換回路は、前記カウンタ回路によって電流値が設定される可変電流源と、該可変電流源に流れる電流をコピーするカレントミラー回路と、前記比較器の比較結果に応じてソース電流回路とシンク電流回路とのうちいずれか一方を動作させ該カレントミラー回路を流れる電流に応じたソース電流またはシンク電流を流す電流出力回路とを備える構成としている。

【発明の効果】

【0009】

請求項1の発明では、駆動電圧に応じて可変容量素子の静電容量を連続的に変化させることができ、3つ以上のキャパシタンス値を得ることができる。また、複数の可変容量素子を接続する必要がなく、信号損失を低減することができる。さらに、電流出力型レベル変換回路によってソース電流またはシンク電流を流し、ソース電流とシンク電流によって駆動電圧を変化させる構成としたから、一般的な駆動電圧の発生手段として、例えば電圧レベル変換回路と、抵抗および容量からなる低域通過フィルタ回路とによって駆動電圧を発生させた場合に比べて、低域通過フィルタ回路の抵抗が不要になり、装置全体を小型化することができる。

【0010】

また、電流出力型レベル変換回路は、過渡状態から定常状態に移行するときに、ソース電流およびシンク電流の電流値を徐々に小さくする構成とした。このため、過渡状態ではソース電流およびシンク電流の電流値を大きくして、平滑化容量の充電量と放電量を増加させることができる。これにより、可変容量素子の静電容量を速やかに目標値に近付けることができ、静電容量が目標値に収束するまでの安定時間を短縮することができる。一方、過渡状態から定常状態に移行するときには、ソース電流およびシンク電流の電流値を徐々に小さくして、平滑化容量の充電量と放電量を減少させることができる。これにより、定常状態ではソース電流およびシンク電流の電流値を小さくして、目標値に対する静電容量の変動を小さくすることができ、容量精度を高めることができる。

【0011】

請求項2の発明では、カウンタ回路は、リセット信号によってカウント数がリセットされると、電流出力型レベル変換回路の電流値を過渡状態の大きさに設定する。このため、カウント数がリセットされた直後は、ソース電流およびシンク電流の電流値を大きくして、静電容量の検出値を目標値に向けて速やかに変化させることができる。

【0012】

また、カウンタ回路は、比較結果の切り換わりをカウントする度にソース電流およびシンク電流の電流値を徐々に小さくして、目標値に対する静電容量の変動幅を徐々に小さくすることができる。そして、最終的にソース電流およびシンク電流の電流値を過渡状態の大きさよりも小さい定常状態の大きさに収束させるから、定常状態ではソース電流およびシンク電流の電流値を小さくして、目標値に対する静電容量の変動を小さくすることができ、容量精度を高めることができる。

【0013】

請求項3の発明では、電流出力型レベル変換回路は、可変電流源と、カレントミラー回路と、電流出力回路とを備える構成とした。このため、カウンタ回路によって可変電流源の電流値を設定すると共に、可変電流源に流れる電流をカレントミラー回路によってコピーすることができる。そして、電流出力回路は、比較器の比較結果に応じてソース電流回路とシンク電流回路とのうちいずれか一方を動作させるから、ソース電流回路の動作時にはカレントミラー回路を流れる電流に応じたソース電流を流すことができ、シンク電流回路が動作時にはカレントミラー回路を流れる電流に応じたシンク電流を流すことができる。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態による可変容量装置を示す全体構成図である。

【図2】図1中の可変容量素子を示す平面図である。

【図3】可変容量素子を図2中の矢示III−III方向からみた断面図である。

【図4】図1中の駆動電圧発生回路を示す回路図である。

【図5】設定開始時の駆動容量のキャパシタンス値が目標値に比べて小さい場合について、駆動容量、駆動電圧、比較結果信号、電流制御信号の時間変化を示す特性線図である。

【図6】設定開始時の駆動容量のキャパシタンス値が目標値に比べて大きい場合について、駆動容量、駆動電圧、比較結果信号、電流制御信号の時間変化を示す特性線図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態による可変容量装置について添付図面を参照しつつ詳細に説明する。

【0016】

図1は実施の形態による可変容量装置1を示している。この可変容量装置1は、可変容量素子2、容量検出回路21および駆動電圧制御回路31を備える。

【0017】

まず、図2および図3を用いて、可変容量素子2について説明する。

【0018】

可変容量素子2は、静電力による駆動するMEMS(Micro Electro Mechanical Systems)によって構成される。この可変容量素子2は、基板3、下駆動電極4A,4B,5、誘電体膜6、梁部7、パッド電極8,9A,9B,10A,10B、および抵抗パターン10C,10Dを備える。

【0019】

基板3は例えば矩形ガラス基板からなる。梁部7は、平面視して矩形平板状で、側面視してL字状に形成される。この梁部7は、図2中の右側の端部が基板3に接合される支持部となって、要部を基板3から離間した状態で支持する片持梁構造(バネ構造)の可動構造部である。また、梁部7は、導電性基板として例えば抵抗率0.01Ωcm以下の低抵抗Si基板(シリコン基板)からなり、ドーパントとして例えばP(リン)、As(ヒ素)、B(ホウ素)等を用いている。

【0020】

下駆動電極4A,4Bは、それぞれL字状で基板3の上面に形成され、梁部7の軸方向(図2中の左,右方向)に沿って長尺な線路状の端部を有する。下駆動電極5は、コ字状で基板3の上面に形成し、梁部7の軸方向に沿って長尺な線路状の両端部で下駆動電極4A,4Bの両脇を挟み込むように配置する。誘電体膜6は、例えば矩形状で厚み200nm程度の五酸化タンタルによって形成され、下駆動電極4A,4Bの端部と下駆動電極5の両端部とを覆うように基板3に積層される。下駆動電極4Aは、RF信号(高周波信号)の入力端子(または出力端子)にパッド電極9Aを介して接続され、下駆動電極4Bは、RF信号の出力端子(または入力端子)にパッド電極9Bを介して接続される。下駆動電極5は、パッド電極10Aおよび抵抗パターン10Cを介して駆動電圧VdとなるDC電圧(直流電圧)の入力端に接続される。梁部7は、パッド電極8,10B、および抵抗パターン10Dを介してグランドに接続される。抵抗パターン10C,10Dは、例えば厚み5nm程度の酸化チタン薄膜を用いて形成され、200kΩ程度の抵抗を有する。

【0021】

下駆動電極5の両端部は、梁部7に誘電体膜6を介して対向して配置され、これらの下駆動電極5および梁部7は駆動容量部11を構成する。駆動容量部11は、駆動電圧制御回路31から駆動電圧Vdが印加されると、下駆動電極5の両端部と梁部7との間に駆動容量C1(静電容量)を生じる。駆動容量C1は、静電引力によって梁部7を変形させ、梁部7を先端から誘電体膜6に接触させる。駆動電圧Vdが高電圧であるほど、梁部7と誘電体膜6との接触面積は大きくなる。

【0022】

下駆動電極4A,4Bは、梁部7に誘電体膜6を介して対向して配置され、これらの下駆動電極4A,4Bおよび梁部7は可変容量部12を構成する。可変容量部12は、例えば数百MHz〜数GHzの無線周波数を扱う回路の中で使用され、梁部7と誘電体膜6との接触面積に応じて変化する可変容量C2(静電容量)を生じる。可変容量部12からは、梁部7を介して駆動電圧制御回路31やグランドに高周波信号が漏洩する虞れがあるため、ここでは漏洩高周波信号を遮断する目的で抵抗パターン10C,10Dを形成している。

【0023】

図2に示す駆動容量部11の構造は、下駆動電極5と梁部7からなる電極対の間に信号(電圧)が直接印加される構造である(以下、この構造をMIM構造という)。また、可変容量部12の構造は、下駆動電極4Aと梁部7、下駆動電極4Bと梁部7からなる2組の電極対を直列に接続して、信号(電圧)が直接印加される構造である(以下、この構造をMIMIM構造という)。MIMIM構造は、MIM構造に比べて面積当りの静電引力が約1/4と小さく、セルフアクチュエーションによる梁部7の変形を抑制するのに有利である。一方、MIM構造は、MIMIM構造に比べて面積当りの静電引力が大きく、電極面積の低減に有利である。従って、大きな静電引力が必要となる駆動容量部11にはMIM構造を採用し、静電引力を抑制する必要がある可変容量部12にはMIMIM構造を採用するのが好ましい。

【0024】

なお、駆動容量部11および可変容量部12は、それぞれMIM構造、MIMIM構造のいずれの構造を採用してもよい。また、駆動容量部11の駆動容量C1と可変容量部12の可変容量C2は一緒に変化する。このため、駆動容量C1のキャパシタンス値は可変容量C2のキャパシタンス値と対応した値になる。

【0025】

次に、図1を用いて、容量検出回路21について説明する。

【0026】

容量検出回路21は、容量検出用交流信号源22、増幅回路23、および整流回路24を備える。容量検出用交流信号源22は、交流源となり、例えば約10MHzの容量検出用のAC信号(交流信号)を直流遮断用の容量C3(約100pF)に出力する。容量C3の出力端は、交流遮断用の抵抗R1を介して直流源となる駆動電圧発生回路34に接続される。このため、抵抗R1と容量C3との接続点で、駆動電圧発生回路34からのDC信号(駆動電圧Vd)に容量検出用のAC信号が重畳される。この重畳信号は、直流バイパス用の抵抗R2、および参照容量C4からなる並列回路に入力される。この並列回路の出力端には可変容量素子2の駆動容量C1が接続され、抵抗R2、参照容量C4、および駆動容量C1からなる容量回路を構成している。

【0027】

重畳信号のうちのDC成分となる駆動電圧Vdは、直流バイパス用の抵抗R2を介して駆動容量C1に印加され、静電引力により可変容量素子2における梁部7を変形させる。重畳信号のうちのAC成分は、参照容量C4と駆動容量C1で電圧分配され、両者の容量比に応じた振幅として参照容量C4と駆動容量C1との接続点から直流遮断用の容量C5に出力される。

【0028】

直流遮断用の容量C5の出力端には増幅回路23が接続され、増幅回路23は容量回路における電圧分配点からのAC出力の電圧レベルを増幅して増幅電圧Vampを出力する。増幅回路23の入力部には入力インピーダンスが非常に高いボルテージホロワ(図示せず)を設けていて、容量回路のAC出力を参照容量C4と駆動容量C1とで単純に電圧分配した電圧レベルにしている。増幅回路23で増幅された増幅電圧Vampは、整流回路24で整流される。増幅回路23の増幅率や、参照容量C4、容量検出用交流信号源22の電圧レベルを既知とすれば、整流回路24の出力する直流電圧は、駆動容量C1の容量を一意に反映した電圧レベルとなり、駆動容量C1が大きいほど電圧レベルが低くなる。このため、整流回路24の出力する直流電圧は、駆動容量C1を検出した検出信号Scとなり、検出信号Scの電圧レベルは、駆動容量C1の検出値に対応する。

【0029】

次に、図1を用いて、駆動電圧制御回路31について説明する。

【0030】

駆動電圧制御回路31は、比較器32、サンプルホールド回路33、および駆動電圧発生回路34を備える。

【0031】

比較器32には、駆動容量C1の目標値を指示するための目標信号Srが外部入力電圧として入力されると共に、整流回路24からの検出信号Scが入力される。この比較器32は、目標信号Srの電圧レベルと検出信号Scの電圧レベルとを比較して、これらの比較結果に応じた比較結果信号Seを出力する。このため、比較結果信号Seは、駆動容量C1の検出値と目標値との比較結果に応じて、LowレベルまたはHighレベルに切り換わる。例えば検出信号Scが目標信号Srよりも小さな電圧レベルである場合、即ち、駆動容量C1が目標値よりも大きな場合には、比較結果信号SeはHighレベルとなる。逆に、検出信号Scが目標信号Srよりも大きな電圧レベルである場合、即ち、駆動容量C1が目標値よりも小さな場合、比較結果信号SeはLowレベルとなる。比較器32の出力端は、比較結果信号Seを一定時間保持するサンプルホールド回路33を介して駆動電圧発生回路34に入力される。

【0032】

駆動電圧発生回路34は、比較器32の比較結果信号Seに応じて駆動電圧Vdを増加または減少させる。比較器32の比較結果信号SeがHighレベルであれば、駆動電圧Vdを低下させて駆動容量C1を減少させる方向に調整する。逆に、比較器32の比較結果信号SeがLowレベルであれば、駆動電圧Vdを上昇させて駆動容量C1を増加させる方向に調整する。

【0033】

次に、図4を用いて、駆動電圧発生回路34について説明する。

【0034】

駆動電圧制御回路34は、電流出力型レベル変換回路35、および電流電圧変換回路44を備える。

【0035】

電流出力型レベル変換回路35は、カウンタ回路36、可変電流源37、カレントミラー回路38、および電流出力回路39を備える。カウンタ回路36は、比較器32の比較結果の切り換わりをカウントし、カウント数に応じた電流制御信号X0〜X5を出力する。ここで、駆動容量C1が目標値に向けて変化している過渡状態では、電流制御信号X0〜X4はいずれかがHighレベルとなり、電流制御信号X5はLowレベルとなる。一方、駆動容量C1が目標値付近で安定した定常状態では、電流制御信号X0〜X4はLowレベルとなり、電流制御信号X5はHighレベルとなる。また、カウンタ回路36は、リセット信号RSの入力端を備え、リセット信号RSが入力されたときにカウント数をリセットする。

【0036】

可変電流源37は、カウンタ回路36からの電流制御信号X0〜X5に応じて電流値Ia〜Ifのいずれかが設定され、電流値Ia〜Ifに応じた電流iを流す。ここで、電流値Ia〜Ifは、以下の数1に示すように、電流値Iaから電流値Ifに向かうに従って順次小さい値に設定されている。

【0037】

【数1】

【0038】

電流値Ia〜Ieは過渡状態で流す電流iの大きさであり、電流値Ifは定常状態で流す電流iの大きさである。このため、過渡状態に応じて電流制御信号X0〜X4のいずれかがHighレベルとなるときに、電流値Ia〜Ieが設定される。一方、定常状態に応じて電流制御信号X5がHighレベルとなるときに、電流値Ifが設定される。定常状態の電流値Ifは、過渡状態のいずれの電流値Ia〜Ieよりも小さい(If<Ia〜Ie)。

【0039】

カレントミラー回路38は、3個のMOSスイッチMP1〜MP3を用いて構成され、可変電流源37に流れる電流iをコピーする。MOSスイッチMP1〜MP3は、pチャネルMOSFETからなり、ソース同士が互いに接続されると共に、ゲート同士が互いに接続される。また、MOSスイッチMP1のドレインは、可変電流源37に接続されると共に、MOSスイッチMP1〜MP3のゲートに接続される。これにより、MOSスイッチMP1に可変電流源37の電流iが流れたときには、MOSスイッチMP2,MP3のドレイン−ソース間にも、可変電流源37の電流iと同じ大きさの電流i1,i2が流れる。

【0040】

電流出力回路39は、選択回路40、ソース電流回路42、およびシンク電流回路43を備える。選択回路40は、比較結果信号Seに応じてソース電流回路42とシンク電流回路43のうちいずれか一方を選択的に動作させる。具体的には、選択回路40は、いずれか一方が選択的に動作する2個のMOSスイッチMN1,MN2と、NOT回路41とによって構成される。

【0041】

MOSスイッチMN1,MN2は、nチャネルMOSFETからなり、MOSスイッチMP2,MP3にそれぞれ直列接続される。具体的には、MOSスイッチMN1のドレインは、MOSスイッチMP2のドレインに接続される。このため、MOSスイッチMN1のドレイン−ソース間には、MOSスイッチMP2と同じ電流i1が流れる。また、MOSスイッチMN2のドレインはMOSスイッチMP3のドレインに接続される。このため、MOSスイッチMN2のドレイン−ソース間には、MOSスイッチMP3と同じ電流i2が流れる。

【0042】

MOSスイッチMN1のゲートには、NOT回路41を介して比較結果信号Seが入力される。このため、MOSスイッチMN1は、比較結果信号SeがHighレベルのときにOFFとなり、比較結果信号SeがLowレベルのときにONとなる。一方、MOSスイッチMN2のゲートには、比較結果信号Seが直接入力される。このため、MOSスイッチMN1は、比較結果信号SeがHighレベルのときにONとなり、比較結果信号SeがLowレベルのときにOFFとなる。この結果、2個のMOSスイッチMN1,MN2は、互いに逆の動作状態となり、インバータ動作する。

【0043】

ソース電流回路42は、第1のカレントミラー回路42Aと、第2のカレントミラー回路42Bとを備える。第1のカレントミラー回路42Aは、2個のMOSスイッチMN3,MN4によって構成される。MOSスイッチMN3,MN4は、それぞれnチャネルMOSFETからなり、ソースがいずれもグランドに接続されると共に、ゲート同士が互いに接続される。また、MOSスイッチMN3のドレインは、MOSスイッチMN1のソースに接続されると共に、MOSスイッチMN3,MN4のゲートに接続される。これにより、MOSスイッチMN1がONとなり、MOSスイッチMP2の電流i1が流れたときには、MOSスイッチMN3,MN4のドレイン−ソース間にも、MOSスイッチMP2の電流i1と同じ大きさの電流が流れる。

【0044】

第2のカレントミラー回路42Bは、2個のMOSスイッチMP4,MP5によって構成される。MOSスイッチMP4,MP5は、pチャネルMOSFETからなり、ソースがいずれも高電圧源(図示せず)に接続されると共に、ゲート同士が互いに接続される。このとき、MOSスイッチMP4,MP5のソースには、駆動電圧Vdの最大値よりも高い電圧Vhが印加される。また、MOSスイッチMP4のドレインは、MOSスイッチMN4のドレインに接続されると共に、MOSスイッチMP4,MP5のゲートに接続される。これにより、MOSスイッチMN4に流れた電流は、MOSスイッチMP4を通じてMOSスイッチMP5にコピーされる。

【0045】

さらに、MOSスイッチMP5のドレインは、電流電圧変換回路44の平滑化容量45に接続される。これにより、ソース電流回路42は、MOSスイッチMN1がONになったときに、MOSスイッチMP2の電流i1を第1,第2のカレントミラー回路42A,42Bによってコピーし、電流i1と同じ大きさのソース電流i10を平滑化容量45に向けて流入させる。

【0046】

シンク電流回路43は、2個のMOSスイッチMN5,MN6からなり、ソース電流回路42の第1のカレントミラー回路42Aとほぼ同様に構成される。このため、MOSスイッチMN5,MN6は、それぞれnチャネルMOSFETからなり、ソースがいずれもグランドに接続されると共に、ゲート同士が互いに接続される。また、MOSスイッチMN5のドレインは、MOSスイッチMN2のソースに接続されると共に、MOSスイッチMN5,MN6のゲートに接続される。これにより、MOSスイッチMN2がONとなり、MOSスイッチMP3の電流i2が流れたときには、MOSスイッチMN5,MN6のドレイン−ソース間にも、MOSスイッチMP3の電流i2と同じ大きさの電流が流れる。

【0047】

さらに、MOSスイッチMN6のドレインは、電流電圧変換回路44の平滑化容量45に接続される。これにより、ソース電流回路42は、MOSスイッチMN2がONになったときに、MOSスイッチMP3の電流i2をMOSスイッチMN5,MN6によってコピーし、電流i2と同じ大きさのシンク電流i20を平滑化容量45から流出させる。

【0048】

電流電圧変換回路44は、平滑化容量45を備える。平滑化容量45は、一端が電流出力回路39の出力端に接続され、他端がグランドに接続される。平滑化容量45の一端は、抵抗R1,R2を介して駆動容量C1に接続される。これにより、平滑化容量45は、駆動容量C1に向けて駆動電圧Vdを出力する。また、平滑化容量45は、ソース電流i10によって充電され、シンク電流i20によって放電される。このため、電流出力型レベル変換回路35がソース電流i10を流したときには駆動電圧Vdは昇圧し、シンク電流i20を流したときには駆動電圧Vdは降圧する。

【0049】

本発明の実施の形態による可変容量装置1は以上のような構成を有するものであり、次に駆動容量C1の設定動作について説明する。

【0050】

図5は、設定開始時の駆動容量C1のキャパシタンス値が目標値に比べて小さい場合を示している。カウンタ回路36にリセット信号RSが入力された時点t0から最初の比較結果の切り換わりが生じる時点t1までの動作は次のようになる。

【0051】

駆動容量C1の設定が開始されると、カウンタ回路36にリセット信号RSが入力され、カウンタ回路36は、電流制御信号X0をHighレベルとし、電流制御信号X1〜X5をLowレベルにする。これにより、可変電流源37は、過渡状態で最大の電流値Iaとなった電流iを流す。

【0052】

また、設定開始時では駆動容量C1のキャパシタンス値が目標値に比べて小さいから、比較器32はLowレベルの比較結果信号Seを出力する。このため、選択回路40によってソース電流回路42が選択され、電流値Iaに応じたソース電流i10が流れる。これにより、平滑化容量45は充電される。過渡状態の電流値Iaは定常状態の電流値Ifに比べて大きいから、定常状態よりも大きなソース電流i10が流れて、駆動容量C1は目標値に向けて速やかに変化する。

【0053】

ここで、駆動電圧Vdが駆動容量C1の目標値に対応した目標電圧値に達しても、可変容量素子2の動作遅延や容量検出回路21の信号応答遅延によって駆動容量C1は目標値に到達しない。このため、駆動電圧Vdは、目標電圧値を超えて増加し、オーバーシュート電圧が生じる。そして、駆動容量C1が目標値を超えて、容量検出回路21による検出信号Scの検出値が目標信号Srの目標値よりも大きくなると、比較器32による比較結果信号SeがLowレベルからHighレベルに切り換わり、次フェーズに移行する。

【0054】

最初の比較結果の切り換わりが生じた時点t1から2回目の比較結果の切り換わりが生じる時点t2までの動作は次のようになる。

【0055】

比較結果信号SeがLowレベルからHighレベルに切り換わると、カウンタ回路36のカウント数が1つ増加する。このとき、カウンタ回路36は、Highレベルとなった電流制御信号X1を出力し、電流制御信号X0,X2〜X5をLowレベルにする。このため、カウンタ回路36によって、電流値Iaよりも小さい電流値Ibに切り換わり、可変電流源37は、電流値Ibとなった電流iを流す。

【0056】

また、比較器32はHighレベルの比較結果信号Seを出力する。このため、選択回路40によってシンク電流回路43が選択され、電流値Ibに応じたシンク電流i20が流れる。これにより、平滑化容量45は放電されて、駆動電圧Vdが目標電圧値を超えて減少し、アンダーシュート電圧が生じる。このとき、電流値Ibは電流値Iaよりも小さいから、時点t2でのアンダーシュート電圧は、時点t1でのオーバーシュート電圧よりも小さくなる。そして、駆動容量C1が目標値を超え、容量検出回路21による検出信号Scの検出値が目標信号Srの目標値よりも小さくなると、比較器32による比較結果信号SeがHighレベルからLowレベルに切り換わり、次フェーズに移行する。

【0057】

2回目の比較結果の切り換わりが生じる時点t2から5回目の比較結果の切り換わりが生じる時点t5までの動作は次のようになる。

【0058】

2回目の比較結果の切り換わりが生じる時点t2では、カウンタ回路36は、電流制御信号X2をHighレベルにし、電流制御信号X0,X1,X3〜X5をLowレベルにする。このため、カウンタ回路36によって、電流値Ibよりも小さい電流値Icに切り換わり、可変電流源37は、電流値Icとなった電流iを流す。このとき、比較器32はLowレベルの比較結果信号Seを出力するから、選択回路40によってソース電流回路42が選択され、電流値Icに応じたソース電流i10が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて増加する。

【0059】

3回目の比較結果の切り換わりが生じる時点t3では、カウンタ回路36は、電流制御信号X3をHighレベルにし、電流制御信号X0〜X2,X4,X5をLowレベルにする。このため、カウンタ回路36によって、電流値Icよりも小さい電流値Idに切り換わり、可変電流源37は、電流値Idとなった電流iを流す。このとき、比較器32はHighレベルの比較結果信号Seを出力するから、選択回路40によってシンク電流回路43が選択され、電流値Idに応じたシンク電流i20が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて減少する。

【0060】

4回目の比較結果の切り換わりが生じる時点t4では、カウンタ回路36は、電流制御信号X4をHighレベルにし、電流制御信号X0〜X3,X5をLowレベルにする。このため、カウンタ回路36によって、電流値Idよりも小さい電流値Ieに切り換わり、可変電流源37は、電流値Ieとなった電流iを流す。このとき、比較器32はLowレベルの比較結果信号Seを出力するから、選択回路40によってソース電流回路42が選択され、電流値Ieに応じたソース電流i10が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて増加する。

【0061】

5回目の比較結果の切り換わりが生じる時点t5では、カウンタ回路36は、電流制御信号X5をHighレベルにし、電流制御信号X0〜X4をLowレベルにする。このため、カウンタ回路36によって、電流値Ieよりも小さい電流値Ifに切り換わり、可変電流源37は、電流値Ifとなった電流iを流す。このとき、比較器32はHighレベルの比較結果信号Seを出力するから、選択回路40によってシンク電流回路43が選択され、電流値Ifに応じたシンク電流i20が流れる。これにより、駆動電圧Vdは、目標電圧値を超えて減少する。そして、時点t2〜t5に移行するに従って、オーバーシュート電圧やアンダーシュート電圧は徐々に小さくなる。

【0062】

5回目の比較結果の切り換わりが生じる時点t5以降の動作は次のようになる。

【0063】

カウンタ回路36は、Highレベルとなった電流制御信号X5を出力し、電流制御信号X0〜X4をLowレベルにする。このため、カウンタ回路36によって、過渡状態の電流値Ia〜Ieよりも小さい定常状態の電流値Ifが設定されるから、可変電流源37は、電流値Ifとなった電流iを流す。このとき、電流出力型レベル変換回路35は、比較結果信号Seに応じてソース電流回路42とシンク電流回路43のうちいずれか一方を選択的に動作させ、比較結果信号SeがLowレベルのときに電流値Ifとなったソース電流i10を流し、比較結果信号SeがHighレベルのときに電流値Ifとなったシンク電流i20を流す。定常状態の電流値Ifは過渡状態の電流値Ia〜Ieよりも小さいから、目標値に対する駆動電圧Vdの変動幅は小さくなり、高い容量精度を得ることができる。このように、電流出力型レベル変換回路35は、駆動電圧Vdが目標電圧値に近付くように、フィードバック動作を行う。

【0064】

図6は、設定開始時の駆動容量C1のキャパシタンス値が目標値に比べて大きい場合を示している。この場合でも、前述した設定開始時の駆動容量C1のキャパシタンス値が目標値に比べて小さい場合とほぼ同様に動作する。

【0065】

以上説明した通り、本実施の形態による可変容量装置1によれば、駆動電圧Vdに応じて駆動容量C1や可変容量C2のキャパシタンス値を連続的に変化させることができ、3つ以上のキャパシタンス値を得ることができる。また、ソース電流i10とシンク電流i20によって駆動電圧Vdを変化させる構成としたから、例えば抵抗と容量からなる低域通過フィルタ回路を用いて駆動電圧を発生させた場合に比べて、装置全体を小型化することができる。

【0066】

具体的に説明すると、一般的に、集積回路において、受動素子である抵抗やコンデンサは大型化する傾向がある。本実施の形態による可変容量装置1では、このような受動素子である抵抗を省くことができ、装置全体を小型化することができる。

【0067】

また、一般的に、過渡状態から定常状態に移行するまでの安定時間と、駆動容量C1の容量精度はトレードオフの関係にある。このため、低域通過フィルタ回路の抵抗値を小さく、またはキャパシタンス値を大きくして、安定時間を短縮すると、容量精度は低下する。逆に、低域通過フィルタ回路の抵抗値を大きく、またはキャパシタンス値を小さくして、容量精度を高めると、安定時間が長くなる。

【0068】

これに対し、本実施の形態では、電流出力型レベル変換回路35は、過渡状態から定常状態に移行するときに、ソース電流i10およびシンク電流i20の電流値を徐々に小さくする構成とした。このため、例えば設定開始時のように過渡状態の初期段階ではソース電流i10およびシンク電流i20の電流値Iaを大きくして、平滑化容量の充電量と放電量を増加させることができる。これにより、可変容量素子2の駆動容量C1を速やかに目標値に近付けることができ、駆動容量C1が目標値に収束するまでの安定時間を短縮することができる。一方、過渡状態から定常状態に移行するときには、電流値Ia〜Ifを順次切り換えるから、ソース電流i10およびシンク電流i20の電流値を徐々に小さくして、平滑化容量の充電量と放電量を減少させることができる。そして、定常状態ではソース電流i10およびシンク電流i20の電流値を最も小さい電流値Ifに設定するから、目標値に対する駆動容量C1の変動を小さくすることができ、容量精度を高めることができる。この結果、高い容量精度を実現しながら、目標値に収束するまでの安定時間を短縮することができる。

【0069】

なお、前記実施の形態では、電流出力型レベル変換回路35はMOSFETを用いて構成したが、例えばバイポーラトランジスタジス等の他のスイッチ素子を用いて構成してもよい。

【0070】

また、前記実施の形態では、可変容量素子2の駆動容量C1を検出して駆動容量C1を変化させる構成としたが、可変容量C2を検出して駆動容量C1を変化させる構成としてもよい。また、駆動容量C1と可変容量C2を共通化した単一の可変容量を設け、この可変容量を検出し、変化させる構成としてもよい。

【0071】

また、前記実施の形態では、5回目の比較結果の切り換わりが生じる時点t5で定常状態の電流値Ifに収束させる構成とした。しかし、本発明はこれに限らず、例えば2回目〜4回目の比較結果の切り換わりが生じる時点t2〜t4で定常状態の電流値に収束させる構成としてもよく、6回目以降の任意のn回目の比較結果の切り換わりが生じる時点tnで定常状態の電流値に収束させる構成としてもよい。

【0072】

また、前記実施の形態では、可変電流源37の電流iを変化させることによってソース電流i10およびシンク電流i20を変化させる構成としたが、電流源の電流値を固定したまま、ソース電流i10およびシンク電流i20を変化させる構成としてもよい。この場合、例えばソース電流回路42のカレントミラー回路42Bを複数個並列に接続し、これら複数個のカレントミラー回路42Bのうち動作する個数を増加または減少させることによって、ソース電流i10を変化させる構成としてもよい。同様に、シンク電流回路43をなすカレントミラー回路を複数個並列に接続し、これら複数個のカレントミラー回路のうち動作する個数を増加または減少させることによって、シンク電流i20を変化させる構成としてもよい。

【符号の説明】

【0073】

1 可変容量装置

2 可変容量素子

21 容量検出回路

31 駆動電圧制御回路

32 比較器

35 電流出力型レベル変換回路

36 カウンタ回路

37 可変電流源

38 カレントミラー回路

39 電流出力回路

40 選択回路

42 ソース電流回路

43 シンク電流回路

44 電流電圧変換回路

45 平滑化容量

【特許請求の範囲】

【請求項1】

駆動電圧に応じて静電容量が変化する可変容量素子と、該可変容量素子の静電容量を検出する容量検出回路と、該容量検出回路による静電容量の検出値が所望の目標値に近付くように前記駆動電圧を制御する駆動電圧制御回路とを備えた可変容量装置において、

前記駆動電圧制御回路は、前記静電容量の検出値と目標値とを比較する比較器と、該比較器の比較結果に応じてソース電流またはシンク電流を流す電流出力型レベル変換回路と、該電流出力型レベル変換回路がソース電流を流したときに前記駆動電圧を昇圧しシンク電流を流したときに前記駆動電圧を降圧する平滑化容量からなる電流電圧変換回路とを備え、

前記電流出力型レベル変換回路は、過渡状態から定常状態に移行するときに、ソース電流およびシンク電流の電流値を徐々に小さくする構成としたことを特徴とする可変容量装置。

【請求項2】

前記駆動電圧制御回路は、前記比較器の比較結果の切り換わりをカウントするカウンタ回路を備え、

該カウンタ回路は、リセット信号によってカウント数がリセットされると、前記駆動電圧制御回路の電流値を過渡状態の大きさに設定し、比較結果の切り換わりをカウントする度に前記駆動電圧制御回路の電流値を小さくして、最終的に前記駆動電圧制御回路の電流値を過渡状態の大きさよりも小さい定常状態の大きさに収束させる構成としてなる請求項1に記載の可変容量装置。

【請求項3】

前記電流出力型レベル変換回路は、前記カウンタ回路によって電流値が設定される可変電流源と、該可変電流源に流れる電流をコピーするカレントミラー回路と、前記比較器の比較結果に応じてソース電流回路とシンク電流回路とのうちいずれか一方を動作させ該カレントミラー回路を流れる電流に応じたソース電流またはシンク電流を流す電流出力回路とを備える構成としてなる請求項2に記載の可変容量装置。

【請求項1】

駆動電圧に応じて静電容量が変化する可変容量素子と、該可変容量素子の静電容量を検出する容量検出回路と、該容量検出回路による静電容量の検出値が所望の目標値に近付くように前記駆動電圧を制御する駆動電圧制御回路とを備えた可変容量装置において、

前記駆動電圧制御回路は、前記静電容量の検出値と目標値とを比較する比較器と、該比較器の比較結果に応じてソース電流またはシンク電流を流す電流出力型レベル変換回路と、該電流出力型レベル変換回路がソース電流を流したときに前記駆動電圧を昇圧しシンク電流を流したときに前記駆動電圧を降圧する平滑化容量からなる電流電圧変換回路とを備え、

前記電流出力型レベル変換回路は、過渡状態から定常状態に移行するときに、ソース電流およびシンク電流の電流値を徐々に小さくする構成としたことを特徴とする可変容量装置。

【請求項2】

前記駆動電圧制御回路は、前記比較器の比較結果の切り換わりをカウントするカウンタ回路を備え、

該カウンタ回路は、リセット信号によってカウント数がリセットされると、前記駆動電圧制御回路の電流値を過渡状態の大きさに設定し、比較結果の切り換わりをカウントする度に前記駆動電圧制御回路の電流値を小さくして、最終的に前記駆動電圧制御回路の電流値を過渡状態の大きさよりも小さい定常状態の大きさに収束させる構成としてなる請求項1に記載の可変容量装置。

【請求項3】

前記電流出力型レベル変換回路は、前記カウンタ回路によって電流値が設定される可変電流源と、該可変電流源に流れる電流をコピーするカレントミラー回路と、前記比較器の比較結果に応じてソース電流回路とシンク電流回路とのうちいずれか一方を動作させ該カレントミラー回路を流れる電流に応じたソース電流またはシンク電流を流す電流出力回路とを備える構成としてなる請求項2に記載の可変容量装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−4842(P2013−4842A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−136137(P2011−136137)

【出願日】平成23年6月20日(2011.6.20)

【出願人】(000006231)株式会社村田製作所 (3,635)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月20日(2011.6.20)

【出願人】(000006231)株式会社村田製作所 (3,635)

[ Back to top ]