可変抵抗器及びこれを用いたフィルタ、可変利得増幅器及び集積回路

【課題】チューニング回路を必要とせずに位相遅れのばらつきを抑制可能な可変抵抗器を提供する。

【解決手段】シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗Rと;前記第1の抵抗よりも小さな抵抗値を持ち、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗rと;前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

【解決手段】シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗Rと;前記第1の抵抗よりも小さな抵抗値を持ち、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗rと;前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シリコン基板上に形成される可変抵抗器及びこれを用いたフィルタ、可変利得増幅器及び集積回路に関する。

【背景技術】

【0002】

従来、共通の抵抗、複数の調整用の抵抗及びスイッチで構成され、上記スイッチを用いて共通の抵抗に接続される調整用の抵抗を切り替えることにより、所望の抵抗値を得る可変抵抗器が知られている。

【0003】

可変抵抗器をシリコン基板上に形成すると、基板との間に寄生容量が生じる。可変抵抗器と基板間の寄生容量は、信号の位相遅れを引き起こす。また、調整用の抵抗を切り替えると共通の抵抗と調整用の抵抗の分圧比も変化するため、共通の抵抗及び調整用の抵抗の間の節点における電圧振幅は一定でない。従って、上記節点と基板との間の寄生容量の影響は一定でなく、信号の位相遅れにばらつきが生じる。例えば、上記可変抵抗器を用いてフィルタを構成した場合に、上記位相遅れのばらつきによってフィルタ特性が劣化する。

【0004】

非特許文献1には、上記位相遅れのばらつきを調整するためのQチューニング(Quality-factor tuning)回路が記載されている。

【非特許文献1】S. Kousai et al, "A 19.7MHz, 5th Order Active-RC Chebyshev LPF for IEEE802.11n with Automatic Quality Factor Tuning Scheme," A-SSCC 2006.

【発明の開示】

【発明が解決しようとする課題】

【0005】

従来の可変抵抗器をシリコン基板上に形成すると寄生容量による信号の位相遅れ及び当該位相遅れのばらつきが生じるという問題がある。位相遅れが一定量であれば回路技術により、位相遅れをキャンセルすることができるが、位相遅れのばらつきを調整するにはQチューニング回路などの複雑なチューニング回路が必要となり、全体の回路規模が増大してしまう。

【0006】

従って、本発明はチューニング回路を必要とせずに位相遅れのばらつきを抑制可能な可変抵抗器を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一態様に係る可変抵抗器は、シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗と;前記第1の抵抗よりも抵抗値が小さく、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と;前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

【0008】

本発明の他の態様に係る可変抵抗器は、シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、入力端子に一端が接続される第1の抵抗と;前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と;前記第2の抵抗よりも抵抗値が小さく、前記複数の第2の抵抗の他端にそれぞれの一端が共通に接続される複数の第3の抵抗と;前記第1の抵抗の他端と前記出力端子との間に挿入され、前記第2の抵抗から1つの抵抗を選択し、選択した第2の抵抗の他端に接続されている第3の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

【発明の効果】

【0009】

本発明によれば、チューニング回路を必要とせずに位相遅れのばらつきを抑制可能な可変抵抗器を提供できる。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照して、本発明の実施形態について説明する。

(第1の実施形態)

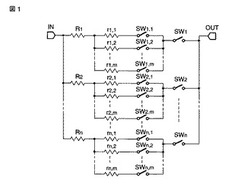

図1に示すように、本発明の第1の実施形態に係る可変抵抗器は、電圧入力端子IN、粗調用抵抗R、粗調用スイッチSW、微調用抵抗r、微調用スイッチSW及び電流出力端子OUTを有する。図1の可変抵抗器では粗調用スイッチSWによってn(nは2以上の任意の整数)個の粗調用抵抗Rから1つが選択され、微調用スイッチSWによって当該粗調用抵抗Rに接続されるm(mは2以上の任意の整数)個の微調用抵抗rから1つが選択される。尚、粗調用抵抗Rの各々に接続される微調用抵抗rの数は一致させなくてもよいが、以下の説明では粗調用抵抗Rの各々に接続される微調用抵抗の数はmとしている。図1に示す可変抵抗器では、粗調用スイッチSW及び微調用スイッチSWによって選択される粗調用抵抗R及び微調用抵抗rを切り替えることによってm×n種類の抵抗値が実現できる。

【0011】

n個の粗調用抵抗R1、R2、・・・、Rnの一端は、電圧入力端子INから並列に接続される。尚、説明を簡単にするため、粗調用抵抗R1、R2、・・・、Rnは抵抗値の小さいものから昇順に並んでいるものとする。即ち、R1<R2<・・・<Rnである。

【0012】

微調用抵抗rは、上記粗調用抵抗R1、R2、・・・、Rnの他端から並列にm個ずつ接続される。尚、説明を簡単にするため、同一の粗調用抵抗Ri(iは1以上n以下の任意の整数)に接続される微調用抵抗ri,1、ri,2、・・・、ri,mは昇順に並んでいるものとする。即ち、ri,1<ri,2<・・・<ri,mである。また、全ての微調用抵抗rは上記粗調用抵抗Rの最小値R1よりも小さな抵抗値を持つ。

【0013】

微調用スイッチSWi,j(jは1以上m以下の任意の整数)の一端は、上記微調用抵抗ri,jの各々の他端に直列に接続される。微調用スイッチSWは、制御信号によってオンオフを制御される。具体的には、微調整スイッチrは例えば図2に示すように、制御信号Vcと当該制御信号Vcの反転信号をゲート端子で受けるMOSトランジスタ対で構成され、入力端子in及び出力端子outを接続または開放する。また、上記微調用抵抗SWi,1、SWi,2、・・・、SWi,mの他端は互いに接続されている。

【0014】

粗調用スイッチSWiは、上記微調用スイッチSWi,1、SWi,2、・・・、SWi,mの他端と電流出力端子OUTとの間に夫々挿入され、上記制御信号によってオンオフ制御される。

【0015】

粗調整スイッチSW及び微調用スイッチSWは電流出力端子OUT側でなく、電圧入力端子IN側に設けられてもよいが、電圧出力端子OUT側に設けたほうがスイッチの非線形性による信号歪を抑えられる。

【0016】

図1の可変抵抗器では、制御信号によって粗調用スイッチSW及び微調用スイッチSWを夫々1つオンにすることにより、粗調用抵抗Ri及び当該粗調用抵抗Riに接続される微調用抵抗ri,jを選択し、抵抗値Ri+ri,jを実現する。即ち、図1の可変抵抗器では、制御信号によって離散的に抵抗値を変化させている。

【0017】

ここで、粗調用抵抗R及び微調用抵抗rは以下の関係式を満たすことが望ましい。

【数1】

【0018】

即ち、粗調用抵抗Rのより大きなものを選択すれば、微調用信号rのいずれを選択するかに係わらず可変抵抗器の抵抗値R+rは必ず大きくなるようにする。以下、関係式(1)を満たすことの技術的な意義について具体例を用いて説明する。

【0019】

例えば、4つの抵抗値22、24、26、28kΩを2つの粗調用抵抗R1及びR2、4つの微調整用抵抗r1,1、r1,2、r2,1、r2,2で実現する場合について説明する。まず、第1の例では、抵抗値R1=21kΩ、R2=25kΩ、r1,1=r2,1=1kΩ、r1,2=r2,2=3kΩを与える。第1の例は関係式(1)を満たす。一方、第2の例では、抵抗値R1=21kΩ、R2=23kΩ、r1,1=r2,1=1kΩ、r1,2=r2,2=5kΩを与える。第2の例はR2+r2,1>R1+r1,2となり、関係式(1)を満たさない。

【0020】

ここで、粗調用抵抗Rと微調用抵抗rの間の節点における寄生容量の影響を考慮すると、当該節点における電圧振幅は小さいほうがよい。この電圧振幅は、粗調用抵抗Rと微調用抵抗rの分圧比(r/(R+r)、ただしRは粗調用抵抗の抵抗値、rは微調用抵抗の抵抗値)に依存し、分圧比が小さいほど電圧振幅が小さくなる。

【0021】

上記第1の例において、分圧比が最も大きくなるのは、抵抗値が24kΩを実現(R1=21kΩ、r1,2=3kΩを選択)する場合である。この場合、接点における分圧比は3/(21+3)=1/8である。一方、第2の例で分圧比が最も大きくなるのは、抵抗値が26kΩを実現(R1=21kΩ、r1,2=5kΩを選択)する場合である。この場合、分圧比は5/(21+5)≒1/5となる。

【0022】

また、上記第1の例において、分圧比が最も小さくなるのは、抵抗値が26kΩを実現(R2=25kΩ、r2,1=1kΩを選択)する場合である。この場合、接点における分圧比は1/(25+1)=1/26である。一方、第2の例で分圧比が最も小さくなるのは、抵抗値が24kΩを実現(R2=23kΩ、r2,1=1kΩを選択)する場合である。この場合、分圧比は1/(23+1)=1/24となる。

【0023】

このように、最大、最小の分圧比を比較すると、いずれも第1の例の方が小さくなることがわかる。また分圧比の最大値と最小値の差を比較すると、第1の例は、(1/8)÷(1/26)=3.25、第2の例は、(1/5)÷(1/24)=4.8となる。これより、第1の例は、抵抗の選択による分圧比の変化が第2の例に比べて小さいことがわかる。

【0024】

従って、関係式(1)を満たす第1の例は、第2の例に比べて分圧比が小さく、接点における電圧振幅も小さくなる。また、第1の例では、第2の例に比べて、分圧比の変化、すなわち電圧振幅の変化も小さいため、信号の位相遅れのばらつきを抑制することができる。

【0025】

以下、本実施形態に係る可変抵抗器の一例として、16の抵抗値を切り替え可能な可変抵抗器について図3を用いて説明する。図3に示す可変抵抗器では、4個の粗調用抵抗R1、R2、R3及びR4及び16個の微調用抵抗r1,1、r1,2、r1,3、r1,4、r2,1、・・・、r4,4を用いて16の抵抗値を切り替え可能としている。尚、図3では粗調用抵抗R及び当該粗調用抵抗Rに接続する微調用抵抗rの割り振りを4×4としているが、これに限らず2×8、8×2あるいは粗調用抵抗R毎に異なる数の微調用抵抗rを割り振ってもよい。粗調用抵抗Rを多く設けたほうが、微調用抵抗rによる微調幅が小さくなり粗調用抵抗Rと微調用抵抗rの間のノードの電圧振幅を小さく抑えやすく、寄生容量による位相遅れの影響を受けにくい。しかしながら、粗調用抵抗Rを多く設けると、回路規模が増大するため、粗調用抵抗Rの数は単純に増やすのではなく可変抵抗器に要求される仕様に従って適宜定める必要がある。

【0026】

図3に示す可変抵抗器の粗調用スイッチSW及び微調用スイッチSWの各々は、例えば4ビットの制御コードで表される制御信号によってオンオフが制御される。各制御コードと粗調用スイッチ及び微調用スイッチのオンオフの関係は特に限定しないが、以下の説明では図4に示すテーブルに従ってオンオフが制御されるものとする。図4に示すように、制御コードの上位2ビットは粗調用スイッチSWのオンオフを制御しており、「00」であれば粗調用スイッチSW1、「01」であれば粗調用スイッチSW2、「10」であれば粗調用スイッチSW3、「11」であれば粗調用スイッチSW4が夫々オンとなる。一方、制御コードの下位2ビットは微調用スイッチSWのオンオフを制御しており、「00」であれば微調用スイッチSWi,1、「01」であれば微調用スイッチSWi,2、「10」であれば微調用スイッチSWi,3、「11」であれば微調用スイッチSWi,4が夫々オンとなる。

【0027】

より具体的には、制御コードのビット値が「0000」から「1111」まで増大するに従って、図3に示す可変抵抗器の抵抗値も単調に増加する。即ち、図3に示す可変抵抗は、制御コード「0000」のときに最小の抵抗値R1+r1,1を持ち、「1111」のときに最大の抵抗値R4+r4,4を持つ。

【0028】

図3の可変抵抗器と基板との間の寄生容量を図5に示す。図5において、粗調用抵抗R及び微調用抵抗rは抵抗値に応じて長さを変えて示してある。以下、図6及び図7を用いて、図3の可変抵抗器が最小の抵抗値R1+r1,1を持つ場合と最大の抵抗値R4+r4,4を持つ場合の寄生容量の影響について定性的に説明する。

【0029】

図6には、図3の可変抵抗器が最小の抵抗値R1+r1,1を持つ場合の等価回路について、図5と同様に抵抗値に応じて抵抗の長さを変えて示してある。図6において、オフの粗調用スイッチSW2、SW3及びSW4に接続される粗調用抵抗R2、R3及びR4、微調用抵抗r2,1、r2,2、r2,3、r2,4、r3,1、・・・、r4,4及びこれらの寄生容量は、電流出力端子OUTから切り離され、電圧入力端子INとグラウンドとの間の寄生抵抗Rp11及び当該寄生抵抗Rp11に直列接続される容量Cp11として等価的に接続される。

【0030】

寄生抵抗Rp11は使用されていない粗調用抵抗R2、R3及びR4を含むため抵抗値が比較的大きく、寄生容量Cp11による位相遅れの影響は見えにくい。また、電圧入力端子INは電圧源で駆動されるため、寄生容量Cp11から出力される位相の遅れた電流のほとんどは電圧源に流れ込み、出力電流に影響を与えない。

【0031】

また、オフの微調用スイッチSW1,2、SW1,3及びSW1,4に接続される微調用抵抗r1,2、r1,3及びr1,4及びこれらの寄生容量は、粗調用抵抗と微調用抵抗との間の節点Aとグラウンドとの間の寄生抵抗Rp12及び当該寄生抵抗Rp12に直列接続される寄生容量Cp12として等価的に接続される。本実施形態に係る可変抵抗器では、節点Aにおける電圧振幅は抵抗分圧によって十分小さく抑えられ、また、寄生容量Cp12の容量値も小さいため、当該寄生容量Cp12から出力される位相の遅れた電流の振幅も小さく、出力電流にほとんど影響を与えない。また、電流出力端子OUTに接続される寄生容量Cp13についても、電流出力端子OUTにおける電圧振幅が非常に小さいため影響をほとんど与えない。

【0032】

図7には、図3の可変抵抗器が最大の抵抗値R4+r4,4を持つ場合の等価回路について、図6と同様に示してある。図7において、オフの粗調用スイッチSW1、SW2及びSW3に接続される粗調用抵抗R1、R2及びR3、微調用抵抗r1,1、r1,2、r1,3、r1,4、r2,1、・・・、r3,4及びこれらの寄生容量は、電流出力端子OUTから切り離され、電圧入力端子INとグラウンドとの間の寄生抵抗Rp21及び当該寄生抵抗Rp21に直列接続される容量Cp21として等価的に接続される。

【0033】

寄生抵抗Rp21は使用されていない粗調用抵抗R1、R2及びR3を含むため抵抗値が比較的大きく、寄生容量Cp21による位相遅れの影響は見えにくい。また、電圧入力端子INは電圧源で駆動されるため、寄生容量Cp21から出力される位相の遅れた電流のほとんどは電圧源に流れ込み、出力電流に影響を与えない。

【0034】

また、オフの微調用スイッチSW4,1、SW4,2及びSW4,3に接続される微調用抵抗r4,1、r4,2及びr4,3及びこれらの寄生容量は、粗調用抵抗と微調用抵抗との間の節点Aとグラウンドとの間の寄生抵抗Rp22及び当該寄生抵抗Rp22に直列接続される寄生容量Cp22として等価的に接続される。本実施形態に係る可変抵抗器では、節点Aにおける電圧振幅は抵抗分圧によって十分小さく抑えられ、また、寄生容量Cp22の容量値も小さいため、当該寄生容量Cp22から出力される位相の遅れた電流の振幅も小さく、出力電流にほとんど影響を与えない。また、電流出力端子OUTに接続される寄生容量Cp23についても、電流出力端子OUTにおける電圧振幅が非常に小さいため影響をほとんど与えない。

【0035】

以下、図8を用いて、図3の可変抵抗器における寄生容量の影響について従来例と比較し、定量的に説明する。まず、図9に示すように、比較対象となる従来例の可変抵抗器は、共通の抵抗RI−8RU、16個の調整用の抵抗RU、2RU、・・・、16RU及びスイッチSWU1、SWU2、・・・・、SWU16で構成される。図9の可変抵抗器では、上記スイッチSWU1、SWU2、・・・・、SWU16を用いて共通の抵抗RI−8RUに接続される調整用の抵抗RU、2RU、・・・、16RUを切り替え、RI−7RUからRI−8RUまで16値の切り替えが可能である。図3及び図9の可変抵抗器は可変幅として数十%程度を想定しているため、可変幅を25%とし、25kΩをセンター値とした場合の群遅延特性の比較結果を図8に示す。尚、群遅延量は、位相の周波数微分値に−1を乗じて得られる値で、各信号周波数における遅延時間を表す。

【0036】

図8において、横軸が信号周波数[Hz]、縦軸が群遅延量[s]を夫々表し、各信号周波数における図3の可変抵抗器の群遅延量を実線、図9の可変抵抗器の群遅延量を破線で夫々示している。抵抗値を最小値から最大値まで変化させた場合の群遅延量のばらつきは、図3の可変抵抗器では0.4n[s]程度で安定しており、図9の可変抵抗器に比べて、1/5以下に抑えられることがわかる。また、図3の可変抵抗器は群遅延量そのものも1n[s]を下回っており、図9の可変抵抗器に比べて小さいことがわかる。

【0037】

以上説明したように、本実施形態に係る可変抵抗器では粗調用抵抗とこれに比べて抵抗値の小さい微調用抵抗を用いており、抵抗値を変化させても両抵抗の間の節点に接続される寄生容量及び当該節点における電圧振幅を安定して小さく抑えられる。従って、本実施形態に係る可変抵抗器によれば、チューニング回路を必要とせずに寄生容量による位相遅れのばらつきを小さくし、かつ、位相遅れそのものも低減させることができる。

【0038】

(第2の実施形態)

図10に示すように、本発明の第2の実施形態に係る可変抵抗器の一例は、図3の可変抵抗器から粗調用スイッチSW1、SW2、SW3及びSW4を取り除き、微調用スイッチSW1,1、SW1,2、SW1,3、SW1,4、SW2,1、・・・、SW4,4の他端に電流出力端子OUTを直接接続している。

【0039】

図3の可変抵抗器と同様、図10の可変抵抗器では4ビットの制御コードで表現される制御信号によって微調用スイッチSW1,1、SW1,2、SW1,3、SW1,4、SW2,1、・・・、SW4,4のオンオフを制御する。即ち、図10の可変抵抗器は、例えば図11に示すように制御コードと当該制御コードによってオンとなる微調用スイッチを一対一で対応付けることにより、16の抵抗値を切り替えることができる。

【0040】

以上説明したように、本実施形態に係る可変抵抗器では粗調用スイッチを取り除き、微調用スイッチの他端と電流出力端子OUTを直接接続している。従って、本実施形態に係る可変抵抗器によれば、スイッチの数を減らし、粗調用スイッチによる寄生抵抗の影響を緩和することができる。

【0041】

(第3の実施形態)

前述した第2の実施形態では、微調用スイッチは排他的に動作し、同時に複数の微調用スイッチがオンとなることはない。しかしながら、本発明の第3の実施形態に係る可変抵抗器では同時に複数の微調用スイッチがオンとなってもよい。

【0042】

以下、図12を用いて本実施形態に係る可変抵抗器の一例について説明する。図12の可変抵抗器は、電圧入力端子IN、4個の粗調用抵抗R、8個の微調用抵抗r、12個の微調用スイッチSW及び電流出力端子OUTを有し、16の抵抗値を切り替え可能である。

【0043】

4個の粗調用抵抗R11、R12、R13及びR14の一端は、電圧入力端子INから並列に接続される。上記粗調用抵抗Rk(kは11以上14以下の任意の整数)の他端には微調用スイッチSWk,0の一端が接続されると共に、微調用抵抗rk,1及びrk,2の一端が並列に接続される。尚、説明を簡単にするため、粗調用抵抗の抵抗値は、R11<R12<R13<R14とし、粗調用抵抗Rkに接続される微調用抵抗の抵抗値は、rk,1<rk,2とする。また、全ての微調用抵抗rは上記粗調用抵抗Rの最小値R11よりも小さな抵抗値を持つ。上記微調用抵抗rk,1及びrk,2の他端には、微調用スイッチSWk,1及びSWk,2の一端が接続される。各微調用スイッチSWの他端は共に電流出力端子OUTに接続される。

【0044】

図3及び図10の可変抵抗器と同様、図12の可変抵抗器では4ビットの制御コードで表現される制御信号によって微調用スイッチSW11,1、SW11,2、SW12,1、・・・、SW14,2のオンオフを制御する。即ち、図12の可変抵抗器は、例えば図13に示すように制御コードと当該制御コードによってオンとなる微調用スイッチを制御することにより、16の抵抗値を切り替えることができる。

【0045】

まず、前述した第2の実施形態と同様に同時に1つの微調用スイッチのみがオンとなる場合の抵抗値について説明する。制御コードの下位2ビットが「00」のときに微調用スイッチSWk,0がオンとなり、図12の可変抵抗器の抵抗値はRkとなる。また、制御コードの下位2ビットが「10」のときに微調用スイッチSWk,1がオンとなり、図12の可変抵抗器の抵抗値はRk+rk,1となる。また、制御コードの下位2ビットが「11」のときに微調用スイッチSWk,2オンとなり、図12の可変抵抗器の抵抗値はRk+rk,2なる。

【0046】

次に、同時に複数の微調用スイッチがオンとなる場合の抵抗値について説明する。制御コードの下位2ビットが「01」のときに微調用スイッチSWk,1及びSWk,2がオンとなる。このとき、粗調用抵抗Rkの他端には微調用抵抗rk,1及びrk,2の一端が並列に接続され、図12の可変抵抗器の抵抗値はRk+rk,1//rk,2となる。ここで、「//」は抵抗の並列接続を表す。従って、微調用スイッチSWk,1及びSWk,2がオンのとき、抵抗値rk,1//rk,2の微調用抵抗を粗調用抵抗Rkに接続するのと同様の効果が得られる。尚、抵抗値rk,1//rk,2は、rk,1よりも小さいので、粗調用抵抗Rkに接続される微調用抵抗の抵抗値は、0<rk,1//rk,2<rk,1<rk,2となる。

【0047】

以上説明したように、本実施形態に係る可変抵抗器では同時に複数の微調用抵抗が選択されることを許容し、切り替え可能な抵抗値を増大させている。従って、本実施形態に係る可変抵抗器によれば、微調用抵抗及び微調用スイッチの数を減らすことができる。尚、図12では、微調用抵抗として0Ω(ショート)を設けたが、0Ωを設けなくてもよい。また、同時に3本以上の微調用抵抗が選択されてもよい。

【0048】

(第4の実施形態)

本発明の第4の実施形態に係る可変抵抗器では、前述した第1乃至第3の実施形態における粗調用抵抗Rと電圧入力端子INとの間に共通の抵抗Rcを設ける。

例えば図14に示すように、図12の可変抵抗器において共通の抵抗Rcを設けることにより、各粗調用抵抗RkをRk−Rcに置き換えることができる。抵抗をシリコン基板上で形成する場合、面積は抵抗値に対して単調に増加するため、粗調用抵抗に共通部分を設けることにより回路面積を削減できる。

【0049】

以上説明したように、本実施形態に係る可変抵抗器では粗調用抵抗と電圧入力端子との間に共通の抵抗を設けている。従って、本実施形態に係る可変抵抗器によれば各粗調用抵抗の抵抗値を低減させて回路面積を削減することができる。

【0050】

(第5の実施形態)

前述した第1乃至第4の実施形態に係る可変抵抗器はアクティブ・フィルタに応用可能である。本発明の第5の実施形態では第1乃至第4のいずれかの実施形態に係る可変抵抗器と、演算増幅器と、容量とを用いてアクティブ・フィルタを構成する。

【0051】

第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて、例えば図15Aに示す5次抵抗両終端型LCフィルタから図15Bに示すアクティブ・フィルタを構成することができる。図15Bのアクティブ・フィルタでは、演算増幅器の入力端子に第1乃至第4のいずれかの実施形態に係る可変抵抗器の電流出力端子OUTを接続し、信号歪を低く保つと共に位相回転量を抑えている。また、可変抵抗器の抵抗値を切り替えることにより、カットオフ周波数をスケーリングして帯域幅を切り替えることができる。また、可変抵抗器の抵抗値を変えることにより、容量及び抵抗の製造ばらつきを補償することもできる。

【0052】

以上説明したように、本実施形態に係るアクティブ・フィルタでは、第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて構成している。従って、本実施形態に係るフィルタによれば可変抵抗器の抵抗値を切り替えて帯域幅を可変にしたり、他の構成素子の製造ばらつきを補償したりすることができる。

【0053】

(第6の実施形態)

前述した第1乃至第4の実施形態に係る可変抵抗器は可変利得増幅器に応用可能である。本発明の第6の実施形態では第1乃至第4のいずれかの実施形態に係る可変抵抗器と、演算増幅器とを用いて可変利得増幅器を構成する。

【0054】

図16に示すように、本実施形態に係る可変利得増幅器は演算増幅器の入力端子に第1乃至第4のいずれかの実施形態に係る可変抵抗器VR11及びVR12の電流出力端子OUTを接続し、信号歪を低く保つと共に位相回転量を抑えている。また、演算増幅器の出力は第1乃至第4のいずれかの実施形態に係る可変抵抗器VR21及びVR22によって帰還をかけられている。本実施形態に係る可変利得増幅器の利得は、可変抵抗器VR11、VR12、VR21及びVR22の抵抗値を変化させることによって切り替えることができる。

【0055】

以上説明したように、本実施形態に係る可変利得増幅器では、第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて構成している。従って、本実施形態に係るフィルタによれば可変抵抗器による信号の位相遅れが減少するため可変利得増幅器を広帯域で動作させることができる。

【0056】

(第7の実施形態)

前述した第5の実施形態に係るフィルタ及び第6の実施形態に係る可変利得増幅器は、無線通信機の送受信システムに応用可能である。本発明の第7の実施形態では第5の実施形態に係るフィルタ及び第6の実施形態に係る可変利得増幅器を用いて受信機を構成する。

【0057】

図17に示すように、本実施形態に係る受信機はアンテナ101、低雑音増幅器102、周波数変換器103、フィルタ104、可変利得増幅器105及びアナログ−デジタル変換器106を有する。

【0058】

アンテナ101は電波を受信し、受信信号を低雑音増幅器102に渡す。低雑音増幅器102は、上記受信信号を増幅する。周波数変換器103は、上記低雑音増幅器102によって増幅された受信信号をダウンコンバートして、受信ベースバンド信号をフィルタ104に渡す。

【0059】

フィルタ104は、前述した第5の実施形態に係るフィルタであって、受信ベースバンド信号から妨害波を除去する。可変利得増幅器105は、前述した第6の実施形態に係る可変利得増幅器であって、フィルタ104で妨害波除去された受信ベースバンド信号を所望の信号レベルまで増幅し、アナログ−デジタル変換器106に渡す。

【0060】

アナログ−デジタル変換器106は、可変利得増幅器105で増幅された受信ベースバンド信号をデジタル受信信号に変換する。上記デジタル受信信号は、図示しないデジタル処理部によって復調される。

【0061】

以上説明したように、本実施形態に係る受信機では、第5の実施形態に係るフィルタ及び第6の実施形態に係る可変利得増幅器を用いて構成している。従って、本実施形態に係る受信機によれば、フィルタ及び可変利得増幅器の位相遅れが低減し、高い復調精度を得られる。

【0062】

なお、本発明は上記各実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また上記各実施形態に開示されている複数の構成要素を適宜組み合わせることによって種々の発明を形成できる。また例えば、各実施形態に示される全構成要素からいくつかの構成要素を削除した構成も考えられる。さらに、異なる実施形態に記載した構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0063】

【図1】第1の実施形態に係る可変抵抗器を示す回路図。

【図2】図1に示すスイッチの一例を示す回路図。

【図3】図1の可変抵抗器の一例を示す回路図。

【図4】図3の可変抵抗器における制御コードとスイッチのオンオフの対応を示すテーブル。

【図5】図3の可変抵抗器における寄生容量を概念的に示す図。

【図6】図3の可変抵抗器が最小値を持つ場合の寄生素子を概念的に示す図。

【図7】図3の可変抵抗器が最大値を持つ場合の寄生素子を概念的に示す図。

【図8】図3の可変抵抗器及び従来例の群遅延特性を示すグラフ図。

【図9】図8における従来例の可変抵抗器を示す回路図。

【図10】第2の実施形態に係る可変抵抗器の一例を示す回路図。

【図11】図10の可変抵抗器における制御コードとスイッチのオンオフの対応を示すテーブル。

【図12】第3の実施形態に係る可変抵抗器の一例を示す回路図。

【図13】図12の可変抵抗器における制御コードとスイッチのオンオフの対応を示すテーブル。

【図14】第4の実施形態に係る可変抵抗器の一例を示す回路図。

【図15A】5次抵抗両終端型LCフィルタの一例を示す回路図。

【図15B】第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて構成した、図15AのLCフィルタに相当するアクティブ・フィルタを示す回路図。

【図16】第1乃至第3のいずれかの実施形態に係る可変抵抗器を用いて構成した可変利得増幅器を示す回路図。

【図17】図15Bのアクティブ・フィルタ及び図16に示す可変利得増幅器を用いて構成した受信機を示すブロック図。

【符号の説明】

【0064】

101・・・アンテナ

102・・・周波数変換器

103・・・低雑音増幅器

104・・・フィルタ

105・・・可変利得増幅器

106・・・アナログ−デジタル変換器

【技術分野】

【0001】

本発明は、シリコン基板上に形成される可変抵抗器及びこれを用いたフィルタ、可変利得増幅器及び集積回路に関する。

【背景技術】

【0002】

従来、共通の抵抗、複数の調整用の抵抗及びスイッチで構成され、上記スイッチを用いて共通の抵抗に接続される調整用の抵抗を切り替えることにより、所望の抵抗値を得る可変抵抗器が知られている。

【0003】

可変抵抗器をシリコン基板上に形成すると、基板との間に寄生容量が生じる。可変抵抗器と基板間の寄生容量は、信号の位相遅れを引き起こす。また、調整用の抵抗を切り替えると共通の抵抗と調整用の抵抗の分圧比も変化するため、共通の抵抗及び調整用の抵抗の間の節点における電圧振幅は一定でない。従って、上記節点と基板との間の寄生容量の影響は一定でなく、信号の位相遅れにばらつきが生じる。例えば、上記可変抵抗器を用いてフィルタを構成した場合に、上記位相遅れのばらつきによってフィルタ特性が劣化する。

【0004】

非特許文献1には、上記位相遅れのばらつきを調整するためのQチューニング(Quality-factor tuning)回路が記載されている。

【非特許文献1】S. Kousai et al, "A 19.7MHz, 5th Order Active-RC Chebyshev LPF for IEEE802.11n with Automatic Quality Factor Tuning Scheme," A-SSCC 2006.

【発明の開示】

【発明が解決しようとする課題】

【0005】

従来の可変抵抗器をシリコン基板上に形成すると寄生容量による信号の位相遅れ及び当該位相遅れのばらつきが生じるという問題がある。位相遅れが一定量であれば回路技術により、位相遅れをキャンセルすることができるが、位相遅れのばらつきを調整するにはQチューニング回路などの複雑なチューニング回路が必要となり、全体の回路規模が増大してしまう。

【0006】

従って、本発明はチューニング回路を必要とせずに位相遅れのばらつきを抑制可能な可変抵抗器を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一態様に係る可変抵抗器は、シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗と;前記第1の抵抗よりも抵抗値が小さく、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と;前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

【0008】

本発明の他の態様に係る可変抵抗器は、シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、入力端子に一端が接続される第1の抵抗と;前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と;前記第2の抵抗よりも抵抗値が小さく、前記複数の第2の抵抗の他端にそれぞれの一端が共通に接続される複数の第3の抵抗と;前記第1の抵抗の他端と前記出力端子との間に挿入され、前記第2の抵抗から1つの抵抗を選択し、選択した第2の抵抗の他端に接続されている第3の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

【発明の効果】

【0009】

本発明によれば、チューニング回路を必要とせずに位相遅れのばらつきを抑制可能な可変抵抗器を提供できる。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照して、本発明の実施形態について説明する。

(第1の実施形態)

図1に示すように、本発明の第1の実施形態に係る可変抵抗器は、電圧入力端子IN、粗調用抵抗R、粗調用スイッチSW、微調用抵抗r、微調用スイッチSW及び電流出力端子OUTを有する。図1の可変抵抗器では粗調用スイッチSWによってn(nは2以上の任意の整数)個の粗調用抵抗Rから1つが選択され、微調用スイッチSWによって当該粗調用抵抗Rに接続されるm(mは2以上の任意の整数)個の微調用抵抗rから1つが選択される。尚、粗調用抵抗Rの各々に接続される微調用抵抗rの数は一致させなくてもよいが、以下の説明では粗調用抵抗Rの各々に接続される微調用抵抗の数はmとしている。図1に示す可変抵抗器では、粗調用スイッチSW及び微調用スイッチSWによって選択される粗調用抵抗R及び微調用抵抗rを切り替えることによってm×n種類の抵抗値が実現できる。

【0011】

n個の粗調用抵抗R1、R2、・・・、Rnの一端は、電圧入力端子INから並列に接続される。尚、説明を簡単にするため、粗調用抵抗R1、R2、・・・、Rnは抵抗値の小さいものから昇順に並んでいるものとする。即ち、R1<R2<・・・<Rnである。

【0012】

微調用抵抗rは、上記粗調用抵抗R1、R2、・・・、Rnの他端から並列にm個ずつ接続される。尚、説明を簡単にするため、同一の粗調用抵抗Ri(iは1以上n以下の任意の整数)に接続される微調用抵抗ri,1、ri,2、・・・、ri,mは昇順に並んでいるものとする。即ち、ri,1<ri,2<・・・<ri,mである。また、全ての微調用抵抗rは上記粗調用抵抗Rの最小値R1よりも小さな抵抗値を持つ。

【0013】

微調用スイッチSWi,j(jは1以上m以下の任意の整数)の一端は、上記微調用抵抗ri,jの各々の他端に直列に接続される。微調用スイッチSWは、制御信号によってオンオフを制御される。具体的には、微調整スイッチrは例えば図2に示すように、制御信号Vcと当該制御信号Vcの反転信号をゲート端子で受けるMOSトランジスタ対で構成され、入力端子in及び出力端子outを接続または開放する。また、上記微調用抵抗SWi,1、SWi,2、・・・、SWi,mの他端は互いに接続されている。

【0014】

粗調用スイッチSWiは、上記微調用スイッチSWi,1、SWi,2、・・・、SWi,mの他端と電流出力端子OUTとの間に夫々挿入され、上記制御信号によってオンオフ制御される。

【0015】

粗調整スイッチSW及び微調用スイッチSWは電流出力端子OUT側でなく、電圧入力端子IN側に設けられてもよいが、電圧出力端子OUT側に設けたほうがスイッチの非線形性による信号歪を抑えられる。

【0016】

図1の可変抵抗器では、制御信号によって粗調用スイッチSW及び微調用スイッチSWを夫々1つオンにすることにより、粗調用抵抗Ri及び当該粗調用抵抗Riに接続される微調用抵抗ri,jを選択し、抵抗値Ri+ri,jを実現する。即ち、図1の可変抵抗器では、制御信号によって離散的に抵抗値を変化させている。

【0017】

ここで、粗調用抵抗R及び微調用抵抗rは以下の関係式を満たすことが望ましい。

【数1】

【0018】

即ち、粗調用抵抗Rのより大きなものを選択すれば、微調用信号rのいずれを選択するかに係わらず可変抵抗器の抵抗値R+rは必ず大きくなるようにする。以下、関係式(1)を満たすことの技術的な意義について具体例を用いて説明する。

【0019】

例えば、4つの抵抗値22、24、26、28kΩを2つの粗調用抵抗R1及びR2、4つの微調整用抵抗r1,1、r1,2、r2,1、r2,2で実現する場合について説明する。まず、第1の例では、抵抗値R1=21kΩ、R2=25kΩ、r1,1=r2,1=1kΩ、r1,2=r2,2=3kΩを与える。第1の例は関係式(1)を満たす。一方、第2の例では、抵抗値R1=21kΩ、R2=23kΩ、r1,1=r2,1=1kΩ、r1,2=r2,2=5kΩを与える。第2の例はR2+r2,1>R1+r1,2となり、関係式(1)を満たさない。

【0020】

ここで、粗調用抵抗Rと微調用抵抗rの間の節点における寄生容量の影響を考慮すると、当該節点における電圧振幅は小さいほうがよい。この電圧振幅は、粗調用抵抗Rと微調用抵抗rの分圧比(r/(R+r)、ただしRは粗調用抵抗の抵抗値、rは微調用抵抗の抵抗値)に依存し、分圧比が小さいほど電圧振幅が小さくなる。

【0021】

上記第1の例において、分圧比が最も大きくなるのは、抵抗値が24kΩを実現(R1=21kΩ、r1,2=3kΩを選択)する場合である。この場合、接点における分圧比は3/(21+3)=1/8である。一方、第2の例で分圧比が最も大きくなるのは、抵抗値が26kΩを実現(R1=21kΩ、r1,2=5kΩを選択)する場合である。この場合、分圧比は5/(21+5)≒1/5となる。

【0022】

また、上記第1の例において、分圧比が最も小さくなるのは、抵抗値が26kΩを実現(R2=25kΩ、r2,1=1kΩを選択)する場合である。この場合、接点における分圧比は1/(25+1)=1/26である。一方、第2の例で分圧比が最も小さくなるのは、抵抗値が24kΩを実現(R2=23kΩ、r2,1=1kΩを選択)する場合である。この場合、分圧比は1/(23+1)=1/24となる。

【0023】

このように、最大、最小の分圧比を比較すると、いずれも第1の例の方が小さくなることがわかる。また分圧比の最大値と最小値の差を比較すると、第1の例は、(1/8)÷(1/26)=3.25、第2の例は、(1/5)÷(1/24)=4.8となる。これより、第1の例は、抵抗の選択による分圧比の変化が第2の例に比べて小さいことがわかる。

【0024】

従って、関係式(1)を満たす第1の例は、第2の例に比べて分圧比が小さく、接点における電圧振幅も小さくなる。また、第1の例では、第2の例に比べて、分圧比の変化、すなわち電圧振幅の変化も小さいため、信号の位相遅れのばらつきを抑制することができる。

【0025】

以下、本実施形態に係る可変抵抗器の一例として、16の抵抗値を切り替え可能な可変抵抗器について図3を用いて説明する。図3に示す可変抵抗器では、4個の粗調用抵抗R1、R2、R3及びR4及び16個の微調用抵抗r1,1、r1,2、r1,3、r1,4、r2,1、・・・、r4,4を用いて16の抵抗値を切り替え可能としている。尚、図3では粗調用抵抗R及び当該粗調用抵抗Rに接続する微調用抵抗rの割り振りを4×4としているが、これに限らず2×8、8×2あるいは粗調用抵抗R毎に異なる数の微調用抵抗rを割り振ってもよい。粗調用抵抗Rを多く設けたほうが、微調用抵抗rによる微調幅が小さくなり粗調用抵抗Rと微調用抵抗rの間のノードの電圧振幅を小さく抑えやすく、寄生容量による位相遅れの影響を受けにくい。しかしながら、粗調用抵抗Rを多く設けると、回路規模が増大するため、粗調用抵抗Rの数は単純に増やすのではなく可変抵抗器に要求される仕様に従って適宜定める必要がある。

【0026】

図3に示す可変抵抗器の粗調用スイッチSW及び微調用スイッチSWの各々は、例えば4ビットの制御コードで表される制御信号によってオンオフが制御される。各制御コードと粗調用スイッチ及び微調用スイッチのオンオフの関係は特に限定しないが、以下の説明では図4に示すテーブルに従ってオンオフが制御されるものとする。図4に示すように、制御コードの上位2ビットは粗調用スイッチSWのオンオフを制御しており、「00」であれば粗調用スイッチSW1、「01」であれば粗調用スイッチSW2、「10」であれば粗調用スイッチSW3、「11」であれば粗調用スイッチSW4が夫々オンとなる。一方、制御コードの下位2ビットは微調用スイッチSWのオンオフを制御しており、「00」であれば微調用スイッチSWi,1、「01」であれば微調用スイッチSWi,2、「10」であれば微調用スイッチSWi,3、「11」であれば微調用スイッチSWi,4が夫々オンとなる。

【0027】

より具体的には、制御コードのビット値が「0000」から「1111」まで増大するに従って、図3に示す可変抵抗器の抵抗値も単調に増加する。即ち、図3に示す可変抵抗は、制御コード「0000」のときに最小の抵抗値R1+r1,1を持ち、「1111」のときに最大の抵抗値R4+r4,4を持つ。

【0028】

図3の可変抵抗器と基板との間の寄生容量を図5に示す。図5において、粗調用抵抗R及び微調用抵抗rは抵抗値に応じて長さを変えて示してある。以下、図6及び図7を用いて、図3の可変抵抗器が最小の抵抗値R1+r1,1を持つ場合と最大の抵抗値R4+r4,4を持つ場合の寄生容量の影響について定性的に説明する。

【0029】

図6には、図3の可変抵抗器が最小の抵抗値R1+r1,1を持つ場合の等価回路について、図5と同様に抵抗値に応じて抵抗の長さを変えて示してある。図6において、オフの粗調用スイッチSW2、SW3及びSW4に接続される粗調用抵抗R2、R3及びR4、微調用抵抗r2,1、r2,2、r2,3、r2,4、r3,1、・・・、r4,4及びこれらの寄生容量は、電流出力端子OUTから切り離され、電圧入力端子INとグラウンドとの間の寄生抵抗Rp11及び当該寄生抵抗Rp11に直列接続される容量Cp11として等価的に接続される。

【0030】

寄生抵抗Rp11は使用されていない粗調用抵抗R2、R3及びR4を含むため抵抗値が比較的大きく、寄生容量Cp11による位相遅れの影響は見えにくい。また、電圧入力端子INは電圧源で駆動されるため、寄生容量Cp11から出力される位相の遅れた電流のほとんどは電圧源に流れ込み、出力電流に影響を与えない。

【0031】

また、オフの微調用スイッチSW1,2、SW1,3及びSW1,4に接続される微調用抵抗r1,2、r1,3及びr1,4及びこれらの寄生容量は、粗調用抵抗と微調用抵抗との間の節点Aとグラウンドとの間の寄生抵抗Rp12及び当該寄生抵抗Rp12に直列接続される寄生容量Cp12として等価的に接続される。本実施形態に係る可変抵抗器では、節点Aにおける電圧振幅は抵抗分圧によって十分小さく抑えられ、また、寄生容量Cp12の容量値も小さいため、当該寄生容量Cp12から出力される位相の遅れた電流の振幅も小さく、出力電流にほとんど影響を与えない。また、電流出力端子OUTに接続される寄生容量Cp13についても、電流出力端子OUTにおける電圧振幅が非常に小さいため影響をほとんど与えない。

【0032】

図7には、図3の可変抵抗器が最大の抵抗値R4+r4,4を持つ場合の等価回路について、図6と同様に示してある。図7において、オフの粗調用スイッチSW1、SW2及びSW3に接続される粗調用抵抗R1、R2及びR3、微調用抵抗r1,1、r1,2、r1,3、r1,4、r2,1、・・・、r3,4及びこれらの寄生容量は、電流出力端子OUTから切り離され、電圧入力端子INとグラウンドとの間の寄生抵抗Rp21及び当該寄生抵抗Rp21に直列接続される容量Cp21として等価的に接続される。

【0033】

寄生抵抗Rp21は使用されていない粗調用抵抗R1、R2及びR3を含むため抵抗値が比較的大きく、寄生容量Cp21による位相遅れの影響は見えにくい。また、電圧入力端子INは電圧源で駆動されるため、寄生容量Cp21から出力される位相の遅れた電流のほとんどは電圧源に流れ込み、出力電流に影響を与えない。

【0034】

また、オフの微調用スイッチSW4,1、SW4,2及びSW4,3に接続される微調用抵抗r4,1、r4,2及びr4,3及びこれらの寄生容量は、粗調用抵抗と微調用抵抗との間の節点Aとグラウンドとの間の寄生抵抗Rp22及び当該寄生抵抗Rp22に直列接続される寄生容量Cp22として等価的に接続される。本実施形態に係る可変抵抗器では、節点Aにおける電圧振幅は抵抗分圧によって十分小さく抑えられ、また、寄生容量Cp22の容量値も小さいため、当該寄生容量Cp22から出力される位相の遅れた電流の振幅も小さく、出力電流にほとんど影響を与えない。また、電流出力端子OUTに接続される寄生容量Cp23についても、電流出力端子OUTにおける電圧振幅が非常に小さいため影響をほとんど与えない。

【0035】

以下、図8を用いて、図3の可変抵抗器における寄生容量の影響について従来例と比較し、定量的に説明する。まず、図9に示すように、比較対象となる従来例の可変抵抗器は、共通の抵抗RI−8RU、16個の調整用の抵抗RU、2RU、・・・、16RU及びスイッチSWU1、SWU2、・・・・、SWU16で構成される。図9の可変抵抗器では、上記スイッチSWU1、SWU2、・・・・、SWU16を用いて共通の抵抗RI−8RUに接続される調整用の抵抗RU、2RU、・・・、16RUを切り替え、RI−7RUからRI−8RUまで16値の切り替えが可能である。図3及び図9の可変抵抗器は可変幅として数十%程度を想定しているため、可変幅を25%とし、25kΩをセンター値とした場合の群遅延特性の比較結果を図8に示す。尚、群遅延量は、位相の周波数微分値に−1を乗じて得られる値で、各信号周波数における遅延時間を表す。

【0036】

図8において、横軸が信号周波数[Hz]、縦軸が群遅延量[s]を夫々表し、各信号周波数における図3の可変抵抗器の群遅延量を実線、図9の可変抵抗器の群遅延量を破線で夫々示している。抵抗値を最小値から最大値まで変化させた場合の群遅延量のばらつきは、図3の可変抵抗器では0.4n[s]程度で安定しており、図9の可変抵抗器に比べて、1/5以下に抑えられることがわかる。また、図3の可変抵抗器は群遅延量そのものも1n[s]を下回っており、図9の可変抵抗器に比べて小さいことがわかる。

【0037】

以上説明したように、本実施形態に係る可変抵抗器では粗調用抵抗とこれに比べて抵抗値の小さい微調用抵抗を用いており、抵抗値を変化させても両抵抗の間の節点に接続される寄生容量及び当該節点における電圧振幅を安定して小さく抑えられる。従って、本実施形態に係る可変抵抗器によれば、チューニング回路を必要とせずに寄生容量による位相遅れのばらつきを小さくし、かつ、位相遅れそのものも低減させることができる。

【0038】

(第2の実施形態)

図10に示すように、本発明の第2の実施形態に係る可変抵抗器の一例は、図3の可変抵抗器から粗調用スイッチSW1、SW2、SW3及びSW4を取り除き、微調用スイッチSW1,1、SW1,2、SW1,3、SW1,4、SW2,1、・・・、SW4,4の他端に電流出力端子OUTを直接接続している。

【0039】

図3の可変抵抗器と同様、図10の可変抵抗器では4ビットの制御コードで表現される制御信号によって微調用スイッチSW1,1、SW1,2、SW1,3、SW1,4、SW2,1、・・・、SW4,4のオンオフを制御する。即ち、図10の可変抵抗器は、例えば図11に示すように制御コードと当該制御コードによってオンとなる微調用スイッチを一対一で対応付けることにより、16の抵抗値を切り替えることができる。

【0040】

以上説明したように、本実施形態に係る可変抵抗器では粗調用スイッチを取り除き、微調用スイッチの他端と電流出力端子OUTを直接接続している。従って、本実施形態に係る可変抵抗器によれば、スイッチの数を減らし、粗調用スイッチによる寄生抵抗の影響を緩和することができる。

【0041】

(第3の実施形態)

前述した第2の実施形態では、微調用スイッチは排他的に動作し、同時に複数の微調用スイッチがオンとなることはない。しかしながら、本発明の第3の実施形態に係る可変抵抗器では同時に複数の微調用スイッチがオンとなってもよい。

【0042】

以下、図12を用いて本実施形態に係る可変抵抗器の一例について説明する。図12の可変抵抗器は、電圧入力端子IN、4個の粗調用抵抗R、8個の微調用抵抗r、12個の微調用スイッチSW及び電流出力端子OUTを有し、16の抵抗値を切り替え可能である。

【0043】

4個の粗調用抵抗R11、R12、R13及びR14の一端は、電圧入力端子INから並列に接続される。上記粗調用抵抗Rk(kは11以上14以下の任意の整数)の他端には微調用スイッチSWk,0の一端が接続されると共に、微調用抵抗rk,1及びrk,2の一端が並列に接続される。尚、説明を簡単にするため、粗調用抵抗の抵抗値は、R11<R12<R13<R14とし、粗調用抵抗Rkに接続される微調用抵抗の抵抗値は、rk,1<rk,2とする。また、全ての微調用抵抗rは上記粗調用抵抗Rの最小値R11よりも小さな抵抗値を持つ。上記微調用抵抗rk,1及びrk,2の他端には、微調用スイッチSWk,1及びSWk,2の一端が接続される。各微調用スイッチSWの他端は共に電流出力端子OUTに接続される。

【0044】

図3及び図10の可変抵抗器と同様、図12の可変抵抗器では4ビットの制御コードで表現される制御信号によって微調用スイッチSW11,1、SW11,2、SW12,1、・・・、SW14,2のオンオフを制御する。即ち、図12の可変抵抗器は、例えば図13に示すように制御コードと当該制御コードによってオンとなる微調用スイッチを制御することにより、16の抵抗値を切り替えることができる。

【0045】

まず、前述した第2の実施形態と同様に同時に1つの微調用スイッチのみがオンとなる場合の抵抗値について説明する。制御コードの下位2ビットが「00」のときに微調用スイッチSWk,0がオンとなり、図12の可変抵抗器の抵抗値はRkとなる。また、制御コードの下位2ビットが「10」のときに微調用スイッチSWk,1がオンとなり、図12の可変抵抗器の抵抗値はRk+rk,1となる。また、制御コードの下位2ビットが「11」のときに微調用スイッチSWk,2オンとなり、図12の可変抵抗器の抵抗値はRk+rk,2なる。

【0046】

次に、同時に複数の微調用スイッチがオンとなる場合の抵抗値について説明する。制御コードの下位2ビットが「01」のときに微調用スイッチSWk,1及びSWk,2がオンとなる。このとき、粗調用抵抗Rkの他端には微調用抵抗rk,1及びrk,2の一端が並列に接続され、図12の可変抵抗器の抵抗値はRk+rk,1//rk,2となる。ここで、「//」は抵抗の並列接続を表す。従って、微調用スイッチSWk,1及びSWk,2がオンのとき、抵抗値rk,1//rk,2の微調用抵抗を粗調用抵抗Rkに接続するのと同様の効果が得られる。尚、抵抗値rk,1//rk,2は、rk,1よりも小さいので、粗調用抵抗Rkに接続される微調用抵抗の抵抗値は、0<rk,1//rk,2<rk,1<rk,2となる。

【0047】

以上説明したように、本実施形態に係る可変抵抗器では同時に複数の微調用抵抗が選択されることを許容し、切り替え可能な抵抗値を増大させている。従って、本実施形態に係る可変抵抗器によれば、微調用抵抗及び微調用スイッチの数を減らすことができる。尚、図12では、微調用抵抗として0Ω(ショート)を設けたが、0Ωを設けなくてもよい。また、同時に3本以上の微調用抵抗が選択されてもよい。

【0048】

(第4の実施形態)

本発明の第4の実施形態に係る可変抵抗器では、前述した第1乃至第3の実施形態における粗調用抵抗Rと電圧入力端子INとの間に共通の抵抗Rcを設ける。

例えば図14に示すように、図12の可変抵抗器において共通の抵抗Rcを設けることにより、各粗調用抵抗RkをRk−Rcに置き換えることができる。抵抗をシリコン基板上で形成する場合、面積は抵抗値に対して単調に増加するため、粗調用抵抗に共通部分を設けることにより回路面積を削減できる。

【0049】

以上説明したように、本実施形態に係る可変抵抗器では粗調用抵抗と電圧入力端子との間に共通の抵抗を設けている。従って、本実施形態に係る可変抵抗器によれば各粗調用抵抗の抵抗値を低減させて回路面積を削減することができる。

【0050】

(第5の実施形態)

前述した第1乃至第4の実施形態に係る可変抵抗器はアクティブ・フィルタに応用可能である。本発明の第5の実施形態では第1乃至第4のいずれかの実施形態に係る可変抵抗器と、演算増幅器と、容量とを用いてアクティブ・フィルタを構成する。

【0051】

第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて、例えば図15Aに示す5次抵抗両終端型LCフィルタから図15Bに示すアクティブ・フィルタを構成することができる。図15Bのアクティブ・フィルタでは、演算増幅器の入力端子に第1乃至第4のいずれかの実施形態に係る可変抵抗器の電流出力端子OUTを接続し、信号歪を低く保つと共に位相回転量を抑えている。また、可変抵抗器の抵抗値を切り替えることにより、カットオフ周波数をスケーリングして帯域幅を切り替えることができる。また、可変抵抗器の抵抗値を変えることにより、容量及び抵抗の製造ばらつきを補償することもできる。

【0052】

以上説明したように、本実施形態に係るアクティブ・フィルタでは、第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて構成している。従って、本実施形態に係るフィルタによれば可変抵抗器の抵抗値を切り替えて帯域幅を可変にしたり、他の構成素子の製造ばらつきを補償したりすることができる。

【0053】

(第6の実施形態)

前述した第1乃至第4の実施形態に係る可変抵抗器は可変利得増幅器に応用可能である。本発明の第6の実施形態では第1乃至第4のいずれかの実施形態に係る可変抵抗器と、演算増幅器とを用いて可変利得増幅器を構成する。

【0054】

図16に示すように、本実施形態に係る可変利得増幅器は演算増幅器の入力端子に第1乃至第4のいずれかの実施形態に係る可変抵抗器VR11及びVR12の電流出力端子OUTを接続し、信号歪を低く保つと共に位相回転量を抑えている。また、演算増幅器の出力は第1乃至第4のいずれかの実施形態に係る可変抵抗器VR21及びVR22によって帰還をかけられている。本実施形態に係る可変利得増幅器の利得は、可変抵抗器VR11、VR12、VR21及びVR22の抵抗値を変化させることによって切り替えることができる。

【0055】

以上説明したように、本実施形態に係る可変利得増幅器では、第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて構成している。従って、本実施形態に係るフィルタによれば可変抵抗器による信号の位相遅れが減少するため可変利得増幅器を広帯域で動作させることができる。

【0056】

(第7の実施形態)

前述した第5の実施形態に係るフィルタ及び第6の実施形態に係る可変利得増幅器は、無線通信機の送受信システムに応用可能である。本発明の第7の実施形態では第5の実施形態に係るフィルタ及び第6の実施形態に係る可変利得増幅器を用いて受信機を構成する。

【0057】

図17に示すように、本実施形態に係る受信機はアンテナ101、低雑音増幅器102、周波数変換器103、フィルタ104、可変利得増幅器105及びアナログ−デジタル変換器106を有する。

【0058】

アンテナ101は電波を受信し、受信信号を低雑音増幅器102に渡す。低雑音増幅器102は、上記受信信号を増幅する。周波数変換器103は、上記低雑音増幅器102によって増幅された受信信号をダウンコンバートして、受信ベースバンド信号をフィルタ104に渡す。

【0059】

フィルタ104は、前述した第5の実施形態に係るフィルタであって、受信ベースバンド信号から妨害波を除去する。可変利得増幅器105は、前述した第6の実施形態に係る可変利得増幅器であって、フィルタ104で妨害波除去された受信ベースバンド信号を所望の信号レベルまで増幅し、アナログ−デジタル変換器106に渡す。

【0060】

アナログ−デジタル変換器106は、可変利得増幅器105で増幅された受信ベースバンド信号をデジタル受信信号に変換する。上記デジタル受信信号は、図示しないデジタル処理部によって復調される。

【0061】

以上説明したように、本実施形態に係る受信機では、第5の実施形態に係るフィルタ及び第6の実施形態に係る可変利得増幅器を用いて構成している。従って、本実施形態に係る受信機によれば、フィルタ及び可変利得増幅器の位相遅れが低減し、高い復調精度を得られる。

【0062】

なお、本発明は上記各実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また上記各実施形態に開示されている複数の構成要素を適宜組み合わせることによって種々の発明を形成できる。また例えば、各実施形態に示される全構成要素からいくつかの構成要素を削除した構成も考えられる。さらに、異なる実施形態に記載した構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0063】

【図1】第1の実施形態に係る可変抵抗器を示す回路図。

【図2】図1に示すスイッチの一例を示す回路図。

【図3】図1の可変抵抗器の一例を示す回路図。

【図4】図3の可変抵抗器における制御コードとスイッチのオンオフの対応を示すテーブル。

【図5】図3の可変抵抗器における寄生容量を概念的に示す図。

【図6】図3の可変抵抗器が最小値を持つ場合の寄生素子を概念的に示す図。

【図7】図3の可変抵抗器が最大値を持つ場合の寄生素子を概念的に示す図。

【図8】図3の可変抵抗器及び従来例の群遅延特性を示すグラフ図。

【図9】図8における従来例の可変抵抗器を示す回路図。

【図10】第2の実施形態に係る可変抵抗器の一例を示す回路図。

【図11】図10の可変抵抗器における制御コードとスイッチのオンオフの対応を示すテーブル。

【図12】第3の実施形態に係る可変抵抗器の一例を示す回路図。

【図13】図12の可変抵抗器における制御コードとスイッチのオンオフの対応を示すテーブル。

【図14】第4の実施形態に係る可変抵抗器の一例を示す回路図。

【図15A】5次抵抗両終端型LCフィルタの一例を示す回路図。

【図15B】第1乃至第4のいずれかの実施形態に係る可変抵抗器を用いて構成した、図15AのLCフィルタに相当するアクティブ・フィルタを示す回路図。

【図16】第1乃至第3のいずれかの実施形態に係る可変抵抗器を用いて構成した可変利得増幅器を示す回路図。

【図17】図15Bのアクティブ・フィルタ及び図16に示す可変利得増幅器を用いて構成した受信機を示すブロック図。

【符号の説明】

【0064】

101・・・アンテナ

102・・・周波数変換器

103・・・低雑音増幅器

104・・・フィルタ

105・・・可変利得増幅器

106・・・アナログ−デジタル変換器

【特許請求の範囲】

【請求項1】

シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、

前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗と、

前記第1の抵抗よりも抵抗値が小さく、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と、

前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と

を具備することを特徴とする可変抵抗器。

【請求項2】

前記スイッチ部は、前記第2の抵抗の各々と直列に接続され、制御信号によってオンオフ制御される複数の第1のスイッチを含むことを特徴とする請求項1記載の可変抵抗器。

【請求項3】

前記スイッチ部は、前記第2の抵抗の各々と直列に接続され、制御信号によってオンオフ制御される複数の第1のスイッチと、

前記第1の抵抗の各々と直列に接続され、前記制御信号によってオンオフ制御される複数の第2のスイッチとを含むことを特徴とする請求項1記載の可変抵抗器。

【請求項4】

前記複数の第1の抵抗はそれぞれ抵抗値が異なり、抵抗値が増加するように前記第1の抵抗の選択を前記スイッチ部が切り替えた場合、前記スイッチ部による前記第2の抵抗の選択状態によらず前記スイッチ部が前記第1の抵抗から選択した抵抗及び前記第2の抵抗から選択した抵抗の抵抗値の和は増大するように前記第1の抵抗及び第2の抵抗の抵抗値が設定されていることを特徴とする請求項1記載の可変抵抗器。

【請求項5】

シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、

入力端子に一端が接続される第1の抵抗と、

前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と、

前記第2の抵抗よりも抵抗値が小さく、前記複数の第2の抵抗の他端にそれぞれの一端が共通に接続される複数の第3の抵抗と、

前記第1の抵抗の他端と前記出力端子との間に挿入され、前記第2の抵抗から1つの抵抗を選択し、選択した第2の抵抗の他端に接続されている第3の抵抗から少なくとも1つの抵抗を選択するスイッチ部と

を具備することを特徴とする可変抵抗器。

【請求項6】

演算増幅器と、

前記演算増幅器に接続された請求項1乃至5のいずれか1項記載の可変抵抗器と、

前記演算増幅器に接続されたキャパシタと、を含むアクティブ・フィルタ。

【請求項7】

演算増幅器と、

前記演算増幅器に接続された請求項1乃至5のいずれか1項記載の可変抵抗器と、を含む可変利得増幅器。

【請求項8】

請求項1乃至5のいずれか1項記載の可変抵抗器を含む集積回路。

【請求項1】

シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、

前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗と、

前記第1の抵抗よりも抵抗値が小さく、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と、

前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と

を具備することを特徴とする可変抵抗器。

【請求項2】

前記スイッチ部は、前記第2の抵抗の各々と直列に接続され、制御信号によってオンオフ制御される複数の第1のスイッチを含むことを特徴とする請求項1記載の可変抵抗器。

【請求項3】

前記スイッチ部は、前記第2の抵抗の各々と直列に接続され、制御信号によってオンオフ制御される複数の第1のスイッチと、

前記第1の抵抗の各々と直列に接続され、前記制御信号によってオンオフ制御される複数の第2のスイッチとを含むことを特徴とする請求項1記載の可変抵抗器。

【請求項4】

前記複数の第1の抵抗はそれぞれ抵抗値が異なり、抵抗値が増加するように前記第1の抵抗の選択を前記スイッチ部が切り替えた場合、前記スイッチ部による前記第2の抵抗の選択状態によらず前記スイッチ部が前記第1の抵抗から選択した抵抗及び前記第2の抵抗から選択した抵抗の抵抗値の和は増大するように前記第1の抵抗及び第2の抵抗の抵抗値が設定されていることを特徴とする請求項1記載の可変抵抗器。

【請求項5】

シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、

入力端子に一端が接続される第1の抵抗と、

前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗と、

前記第2の抵抗よりも抵抗値が小さく、前記複数の第2の抵抗の他端にそれぞれの一端が共通に接続される複数の第3の抵抗と、

前記第1の抵抗の他端と前記出力端子との間に挿入され、前記第2の抵抗から1つの抵抗を選択し、選択した第2の抵抗の他端に接続されている第3の抵抗から少なくとも1つの抵抗を選択するスイッチ部と

を具備することを特徴とする可変抵抗器。

【請求項6】

演算増幅器と、

前記演算増幅器に接続された請求項1乃至5のいずれか1項記載の可変抵抗器と、

前記演算増幅器に接続されたキャパシタと、を含むアクティブ・フィルタ。

【請求項7】

演算増幅器と、

前記演算増幅器に接続された請求項1乃至5のいずれか1項記載の可変抵抗器と、を含む可変利得増幅器。

【請求項8】

請求項1乃至5のいずれか1項記載の可変抵抗器を含む集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15A】

【図15B】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15A】

【図15B】

【図16】

【図17】

【公開番号】特開2009−44527(P2009−44527A)

【公開日】平成21年2月26日(2009.2.26)

【国際特許分類】

【出願番号】特願2007−208095(P2007−208095)

【出願日】平成19年8月9日(2007.8.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成21年2月26日(2009.2.26)

【国際特許分類】

【出願日】平成19年8月9日(2007.8.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]