同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、同期回路、同期方法、および受信システムに関し、特に、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする同期回路、同期方法、および受信システムに関する。

【背景技術】

【0002】

近年、携帯電話やデジタル放送(衛星/地上波)、無線LANなどの無線デジタル伝送技術の発展がめざましい。

【0003】

例えば、無線デジタル伝送に用いられる受信機において、高い受信性能を実現するためには、各同期回路の性能が重要となる。とりわけ搬送波周波数位相同期回路に関しては、ビット誤りに直接的な影響を与えるため、その同期性能が受信性能に対して極めて重要になる。

【0004】

周波数・位相同期回路の代表例としてデジタルPLL(Phase-Locked Loop)が挙げられる。

【0005】

デジタルPLLを用いた周波数・位相同期回路は、位相誤差検出器、ループフィルタ、数値制御発振器(NCO)により構成される。

【0006】

図1は、デジタルPLLを用いた周波数・位相同期回路を含む、従来の受信機の構成の一部を示す図である。

【0007】

図1に示すように、受信機には、RF(Radio Frequency)回路2と復調回路3が設けられる。アンテナ1において電波が受信されることによって得られた受信信号はRF回路2の乗算器2−1に入力される。

【0008】

乗算器2−1は、局部発振器2−2から供給された局部発振信号と、アンテナ1から供給された受信信号を乗算し、得られた信号をLPF(Low Pass Filter)2−3に供給する。

【0009】

局部発振器2−2は、局部発振信号を生成し、乗算器2−1に出力する。

【0010】

LPF2−3は、乗算器2−1から出力される乗算信号を入力し、低域周波数成分のみを通過させるフィルタリング処理を行い、A/D(Analog/Digital)変換器2−4に出力する。

【0011】

PSK(Phase Shift Keying)変調などで変調が施されている受信信号の周波数をfc、位相をθc、局部発振器2−2により生成された局部発振信号の周波数をf0、位相をθ0とすると、LPFから出力される信号には、fc−f0に相当する周波数差Δfが含まれ、θc−θ0に相当する位相差θが含まれる。

【0012】

A/D変換器2−4は、LPF2−3から出力された信号に対してA/D変換を施す。A/D変換が施されることによって得られたデジタルの受信信号である受信信号riは復調回路3に供給される。iは、その受信信号が何番目のシンボルの信号であるのかを表す。

【0013】

受信信号riには、2πΔft+θとして表される位相誤差が含まれる。

【0014】

図2は、図1の復調回路3に設けられる、デジタルPLLを用いた周波数・位相同期回路の構成を示す図である。

【0015】

図2に示すように、周波数・位相同期回路は、PLL回路11と乗算器12から構成される。PLL回路11は、乗算器21、位相誤差検出器22、ループフィルタ23、および数値制御発振器(NCO)24から構成される。

【0016】

PSK変調が施されている受信信号riは、PLL回路11の乗算器21と、乗算器12にそれぞれ入力される。

【0017】

PLL回路11の乗算器21は、数値制御発振器24から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、乗算して得られた信号を位相誤差検出器22に出力する。

【0018】

位相誤差検出器22は、乗算器21が出力する信号に残留する位相誤差を検出し、ループフィルタ23に出力する。

【0019】

例えば、受信信号riが既知シンボルの信号である場合、位相誤差検出器22は、乗算器21の出力信号によって表されるシンボルの位相と、既知シンボルの位相との差を位相誤差として検出する。また、受信信号riが既知シンボルの信号ではない場合、位相誤差検出器22は、乗算器21の出力信号によって表される実際のシンボルの位相と、その硬判定結果のシンボルの位相との差を位相誤差として検出する。

【0020】

ループフィルタ23は比例積分型のループフィルタであり、位相誤差検出器22が出力する位相誤差の検出値にフィルタリングを施し、数値制御発振器24に出力する。

【0021】

詳細には、ループフィルタ23の乗算器23−1は、位相誤差検出器22から供給された位相誤差の検出値を、設定されているループゲインG1に従ってG1倍し、乗算器23−2と加算器23−4に出力する。

【0022】

乗算器23−2は、乗算器23−1から供給された、G1倍された位相誤差の検出値を、設定されているループゲインG2に従ってG2倍し、積分器23−3に出力する。乗算器23−1、乗算器23−2は、入力信号に対してループゲインG1またはG2の重みを付加する重み付け乗算器である。

【0023】

積分器23−3は、乗算器23−2の出力を積分し、加算器23−4に出力する。

【0024】

加算器23−4は、乗算器23−1の出力と積分器23−3の出力を加算し、フィルタリング結果として数値制御発振器24に出力する。

【0025】

数値制御発振器24は、ループフィルタ23のフィルタリング結果に基づいて位相制御量e-j(2πΔft+θ)を生成し、乗算器21と乗算器12に出力する。

【0026】

乗算器12は、数値制御発振器24から出力された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号を同期検波信号diとして出力する。

【0027】

ところで、ループフィルタ23のループゲインG1、G2は、ループフィルタ23の特性であるフィルタ帯域を決定する。ループフィルタ23の帯域とPLL回路11の性能については、以下のような関係を有することが知られている。

【0028】

すなわち、ループフィルタの帯域が広い(大きい)場合、位相誤差変動への追従性が上がる一方で、PLLから出力される同期検波信号のジッタ量が大きくなる。逆に、ループフィルタの帯域が狭い(小さい)場合は位相誤差変動への追従性は落ちるが、出力同期検波信号のジッタ量は小さくなる。

【0029】

【特許文献1】特開2009−26426号公報

【発明の開示】

【発明が解決しようとする課題】

【0030】

しかしながら、実際の無線デジタル伝送の受信機においては、局部発振器の温度依存特性やRF回路内での意図せぬ発振等により、受信信号の位相、周波数に雑音が生じることがある。従って、デジタルPLLを用いた周波数・同期回路において、最適な同期性能を実現するためには、受信機特性の固体差や時間変動によって適したループゲインを設定する必要がある。

【0031】

従来のデジタルPLLでは、ループゲインを固定的に設定することしかできず、最適な受信性能を得るためには、受信環境に合わせて調整されたループゲインを個体毎に設定しなくてはならない。また、温度等により伝送チャネルが動的に変化し、それに応じて最適なループゲインが動的に変化するような場合、使用しているループゲインが最適なものではなくなってしまう。

【0032】

さらに、PLLのループフィルタにとって最適となるループゲインは、受信信号における変調方式によっても異なる場合がある。例えば、日本の衛星デジタル放送方式では1フレーム内で複数の変調方式が混在する。このような場合、単一のループゲインしか設定できないとすると、ある変調方式には最適なループゲインであっても、他の変調方式には最適ではなくなるため、受信性能の劣化をもたらす。

【0033】

本発明はこのような状況に鑑みてなされたものであり、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにするものである。

【課題を解決するための手段】

【0034】

本発明の第1の側面は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する同期回路である。

【0035】

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差と前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差の大きさを比較する比較手段と、指定された伝送モードの前記スロットに対応する受信信号が入力されている間、前記比較手段による比較が行われる都度、前記第2のPLL回路に含まれる第2のループフィルタのループゲインの値を所定の量だけ変更することで前記伝送モードにおける最適なループゲイン設定値を探索するループゲイン探索手段とをさらに備え、前記保持手段は、前記ループゲイン探索手段により前記第2のループフィルタのループゲインの値が所定の回数変更された場合、前記第1のループフィルタのループゲインとして設定されている値を、前記伝送モードにおける最適なループゲイン設定値として保持するようにすることができる。

【0036】

前記受信信号のスロットのそれぞれの伝送モードを特定する情報である伝送モード番号を、前記受信信号を復号して得られる制御情報に基づいて特定する伝送モード番号特定手段とをさらに備え、前記ループゲイン探索手段は、前記特定された伝送モード番号が前記指定された伝送モードに対応するものである場合、前記最適なループゲイン設定値を探索し、前記保持手段は、前記伝送モード番号特定手段により特定された伝送モード番号に対応づけて前記最適なループゲイン設定値を保持するようにすることができる。

【0037】

前記第1のPLL回路は、位相制御後の信号に残留する位相誤差を検出する第1の検出回路と、前記第1の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第1のループフィルタと、前記第1のループフィルタによるフィルタ処理の結果に応じて前記第1の位相制御信号を出力する第1の発振回路と、前記第1の発振回路から出力された前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第1の検出回路に出力する前記第1の出力回路とを備え、前記第2のPLL回路は、位相制御後の信号に残留する位相誤差を検出する第2の検出回路と、前記第2の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第2のループフィルタと、前記第2のループフィルタによるフィルタ処理の結果に応じて前記第2の位相制御信号を出力する第2の発振回路と、前記第2の発振回路から出力された前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第2の検出回路に出力する前記第2の出力回路とを備えるようにすることができる。

【0038】

前記第1のループフィルタは、前記第1の検出回路により検出された位相誤差に第1のループゲインを乗算する第1の乗算回路と、前記第1の乗算回路による乗算後の位相誤差に第2のループゲインを乗算する第2の乗算回路と、前記第1の乗算回路による乗算後の位相誤差と、前記第2の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第1の発振回路に出力する第1の加算回路とを備え、前記第2のループフィルタは、前記第2の検出回路により検出された位相誤差に第3のループゲインを乗算する第3の乗算回路と、前記第3の乗算回路による乗算後の位相誤差に第4のループゲインを乗算する第4の乗算回路と、前記第3の乗算回路による乗算後の位相誤差と、前記第4の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第2の発振回路に出力する第2の加算回路とを備えるようにすることができる。

【0039】

前記制御回路は、前記第1のループゲインと前記第3のループゲインの値としてそれぞれ異なる値を設定するようにすることができる。

【0040】

本発明の第1の側面は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を第1のPLL回路から出力し、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を第2のPLL回路から出力し、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第1の出力回路から出力し、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第2の出力回路から出力し、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を第1の検出回路において検出し、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を第2の検出回路において検出し、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定し、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持するステップを含み、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記伝送モード毎に前記ループゲイン設定値が保持される同期方法である。

【0041】

本発明の第2の側面は、伝送路を介して送信されてきた信号を取得する取得手段と、

前記取得手段により取得された信号に対して同期検波処理を含む処理を行う伝送路復号処理手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0042】

本発明の第3の側面は、伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、前記伝送路復号処理手段による処理後の信号に対して、送信対象のデータを復号する処理を施す情報源復号処理手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0043】

本発明の第4の側面は、伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、前記伝送路復号処理手段による処理後の信号に基づいて、画像または音声を出力する出力手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0044】

本発明の第5の側面は、伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、前記伝送路復号処理手段による処理後の信号を記録する記録手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0045】

本発明においては、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号が第1のPLL回路から出力され、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号が第2のPLL回路から出力され、前記第1の位相制御信号に基づいて前記受信信号の位相が制御され、位相制御後の信号が第1の出力回路から出力され、前記第2の位相制御信号に基づいて前記受信信号の位相が制御され、位相制御後の信号が第2の出力回路から出力され、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差が第1の検出回路において検出され、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差が第2の検出回路において検出され、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値が設定され、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値が保持され、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記伝送モード毎に前記ループゲイン設定値が保持される。

【発明の効果】

【0046】

本発明によれば、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができる。

【図面の簡単な説明】

【0047】

【図1】デジタルPLLを用いた周波数・位相同期回路を含む、従来の受信機の構成の一部を示す図である。

【図2】図1に設けられる、デジタルPLLを用いた周波数・位相同期回路の構成を示す図である。

【図3】高度BSのフレームの構成を説明する図である。

【図4】高度BSの1フレーム内での伝送モードの例を示す図である。

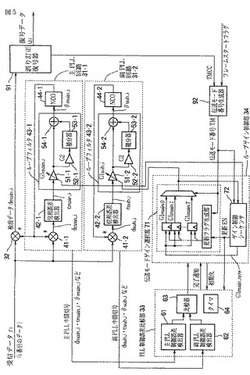

【図5】本発明の一実施形態に係る周波数・位相同期回路の構成例を示すブロック図である。

【図6】ループゲイン制御処理の例を説明するフローチャートである。

【図7】本発明の周波数・位相同期回路を適用した受信システムの第1実施の形態の構成例を示すブロック図である。

【図8】本発明の周波数・位相同期回路を適用した受信システムの第2実施の形態の構成例を示すブロック図である。

【図9】本発明の周波数・位相同期回路を適用した受信システムの第3実施の形態の構成例を示すブロック図である。

【図10】パーソナルコンピュータの構成例を示すブロック図である。

【発明を実施するための形態】

【0048】

以下、図面を参照して、本発明の実施の形態について説明する。

【0049】

最初に、日本の次世代衛星デジタル放送である高度広帯域衛星デジタル放送(高度BS)のフレーム構成について説明する。

【0050】

図3は、高度BSのフレームの構成を説明する図である。同図に示されるように、1フレームは、120の変調スロットで構成されており、この例では、各変調スロットが、変調スロット#1乃至変調スロット#120として示されている。

【0051】

各変調スロットには、同期のための24シンボル(同図には、Fsync、!Fsync、Ssyncと示されている)および信号点の位置の判定などに用いられる32シンボル(同図には、Pilotと示されている)からなる既知シンボルが含まれている。

【0052】

また、各変調スロットには、136シンボルで構成される66の伝送データが含まれている。例えば、変調スロット#1における伝送データは、Data#1乃至Data#66として示されており、変調スロット#2における伝送データは、Data#67乃至Data#132として示されている。

【0053】

さらに、各変調スロットにおいては、伝送・多重に関する制御情報であって4シンボルで構成されるTMCCが、各伝送データの間に挿入されている。図中では、Tとして示されているものがTMCCである。

【0054】

このように構成される高度BSの1フレームは、合計1,115,520シンボルで構成されることになる。

【0055】

また、高度BSでは1フレーム内で複数の変調方式を混在させることが可能となる。例えば、1フレーム内に最大8の伝送モードを定義することが可能であり、個々の伝送モードにおいて異なる変調方式が採用されるようにすることができる。高度BSでは、BPSK、QPSK、8PSK、16APSK、および32APSKの5種類の変調方式を用いることが可能とされている。

【0056】

図4は、高度BSの1フレーム内での伝送モードの例を示す図である。簡単のため、伝送モード数は2としている。同図に示されるように、例えば、変調スロット#1乃至変調スロット#40に対しては、変調方式が32APSKである伝送モード1が割り当てられ、変調スロット#41乃至変調スロット#120に対しては、変調方式が16APSKである伝送モード2が割り当てられる。

【0057】

各変調スロットの伝送モードは、当該フレームより2フレーム前のTMCCを解析することにより特定することができるようになされている。従って、受信機は、2フレーム前に受信したフレームの各変調スロットに挿入されたTMCCを全て取得して記憶しておくことにより、受信したフレームの各変調スロットの変調方式を特定するようになされている。なお、各変調スロットの伝送モードに関わらず、TMCCは、常にπ/2シフトBPSK変調されるようになされている。

【0058】

本発明においては、例えば、図4に示されるように、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【0059】

図5は、本発明の一実施形態に係る周波数・位相同期回路の構成例を示すブロック図である。

【0060】

図5に示す周波数・位相同期回路が、例えば、図1に示す構成と同じ構成を有する受信機の復調回路3に設けられる。

【0061】

図5に示す周波数・位相同期回路の構成は、主に、同じ構成を有するPLLが一つ追加されることによって主副2系統のPLL回路が設けられる点、2系統のPLL回路内のループフィルタのループゲインが可変になっている点、および、ループゲインを制御する構成が追加して設けられている点が、従来の回路構成と異なる。

【0062】

2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、それぞれ、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。それぞれに設けられるループフィルタのループゲインとして同じ値が設定され、同じ信号が入力された場合、主PLL回路31−1から出力される信号と副PLL回路31−2から出力される信号は一致する。

【0063】

後述するように、主PLL回路31−1は、同期検波を実際に行うための回路であり、副PLL回路31−2は、主PLL回路31−1のループフィルタの特性を規定するループゲインを決定するためのいわばトライアルを行うための回路である。

【0064】

i番目(iシンボル目)の信号である受信信号riは、主PLL回路31−1の乗算器41−1、副PLL回路31−2の乗算器41−2、および、乗算器32に入力される。受信信号riには、上述したように2πΔft+θとして表される位相誤差が含まれる。

【0065】

主PLL回路31−1の乗算器41−1は、数値制御発振器44−1から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号dmain,iを位相誤差検出器42−1に出力する。乗算器41−1から出力される信号は、乗算器32から出力される、位相制御の信号である同期検波信号dmain,iと同じ信号になる。

【0066】

位相誤差検出器42−1は、乗算器41−1が出力する信号に残留する位相誤差を検出し、主位相誤差検出値emain,iを出力する。位相誤差検出器42−1においては、図2の位相誤差検出器22と同様にして位相誤差の検出が行われる。後述する副PLL回路31−2の位相誤差検出器42−2においても同様である。

【0067】

位相誤差検出器42−1から出力された主位相誤差検出値emain,iは、ループフィルタ43−1の乗算器51−1に供給される。

【0068】

ループフィルタ43−1は比例積分型のループフィルタであり、位相誤差検出器42−1が出力する主位相誤差検出値emain,iにフィルタリングを施し、数値制御発振器44−1に出力する。

【0069】

詳細には、ループフィルタ43−1の乗算器51−1は、主位相誤差検出値emain,iを、ループゲイン制御部34により設定されたループゲインG1mainに従ってG1main倍し、乗算器52−1と加算器54−1に出力する。

【0070】

乗算器52−1は、乗算器51−1から供給された、G1main倍された主位相誤差検出値emain,iをさらにG2倍し、積分器53−1に出力する。

【0071】

積分器53−1は、乗算器52−1の出力を積分し、加算器54−1に出力する。

【0072】

加算器54−1は、乗算器51−1の出力と積分器53−1の出力を加算し、フィルタリング結果θmain,iとして数値制御発振器44−1に出力する。

【0073】

数値制御発振器44−1は、ループフィルタ43−1のフィルタリング結果に基づいて位相制御量e-j(2πΔft+θ)を生成し、乗算器41−1と乗算器32に出力する。

【0074】

乗算器32は、主PLL回路31−1の数値制御発振器44−1から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号を同期検波信号dmain,iとして出力する。

【0075】

なお、信号dmain,iと、主位相誤差検出値emain,iと、フィルタリング結果θmain,iとを含む信号が、主PLL回路31−1から、PLL制御誤差比較部33の主PLL制御誤差検出部61に、主PLL中間信号として供給されるようになされている。

【0076】

副PLL回路31−2においても、主PLL回路31−1に入力される信号と同じ受信信号riを対象として同様の処理が行われる。

【0077】

すなわち、副PLL回路31−2の乗算器41−2は、数値制御発振器44−2から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号dsub,iを位相誤差検出器42−2に出力する。

【0078】

位相誤差検出器42−2は、乗算器41−2が出力する信号に残留する位相誤差を検出し、副位相誤差検出値esub,iを出力する。位相誤差検出器42−2から出力された副位相誤差検出値esub,iは、ループフィルタ43−2の乗算器51−2に供給される。

【0079】

ループフィルタ43−2の乗算器51−2は、副位相誤差検出値esub,iを、ループゲイン制御部34により設定されたループゲインG1subに従ってG1sub倍し、乗算器52−2と加算器54−2に出力する。

【0080】

例えば、乗算器51−2には、ループゲインG1subとして、主PLL回路31−1の乗算器51−1に設定されたループゲインG1mainとは異なる値が設定される。

【0081】

乗算器52−2は、乗算器51−2から供給された、G1sub倍された副位相誤差検出値esub,iをさらにG2倍し、積分器53−2に出力する。主PLL回路31−1の乗算器52−1と、副PLL回路31−2の乗算器52−2においては、同じループゲインを用いて重み付けが行われることになる。ループゲインG2は、予め設定された固定の値である。

【0082】

積分器53−2は、乗算器52−2の出力を積分し、加算器54−2に出力する。

【0083】

加算器54−2は、乗算器51−2の出力と積分器53−2の出力を加算し、フィルタリング結果θsub,iとして数値制御発振器44−2に出力する。

【0084】

数値制御発振器44−2は、ループフィルタ43−2のフィルタリング結果に基づいて位相制御量e-j(2πΔft+θ)を生成し、乗算器41−2に出力する。

【0085】

なお、信号dmain,iと、副位相誤差検出値esub,iと、フィルタリング結果θsub,iとを含む信号が、副PLL回路31−2から、PLL制御誤差比較部33の副PLL制御誤差検出部62に、副PLL中間信号として供給されるようになされている。

【0086】

PLL制御誤差比較部33の主PLL制御誤差検出器61は、受信信号riが入力される毎に主PLL回路31−1から供給される主PLL中間信号を受信する。例えば、主PLL制御誤差検出器61は、所定の数のシンボルの受信信号riを対象として得られた主位相誤差検出値emain,iに基づいて、主位相誤差検出値emain,iの分散値を算出し、制御誤差値vmainとして比較器63に出力する。

【0087】

乗算器41−1による乗算結果、すなわち主PLL回路31−1における位相制御後の信号に残留する位相誤差の検出値である主位相誤差検出値emain,iに基づいて算出される値であるから、制御誤差値vmainは、主PLL回路31−1による位相制御の誤差を表す。

【0088】

副PLL制御誤差検出器62は、受信信号riが入力される毎に副PLL回路31−2から供給される副PLL中間信号を受信する。例えば、副PLL制御誤差検出器62は、所定の数のシンボルの受信信号riを対象として得られた副位相誤差検出値esub,iに基づいて、副位相誤差検出値esub,iの分散値を算出し、制御誤差値vsubとして比較器63に出力する。

【0089】

乗算器41−2による乗算結果、すなわち副PLL回路31−2における位相制御後の信号に残留する位相誤差の検出値である副位相誤差検出値esub,iに基づいて算出される値であるから、制御誤差値vsubは、副PLL回路31−2による位相制御の誤差を表す。

【0090】

比較器63は、主PLL制御誤差検出器61から供給された制御誤差値vmainと、副PLL制御誤差検出器62から供給された制御誤差値vsubの大小の比較結果を、比較結果出力通知がタイマ64から供給されることに応じてループゲイン制御部34に出力する。

【0091】

上述したように、主PLL回路31−1のループフィルタ43−1と副PLL回路31−2のループフィルタ43−2においては、それぞれ異なるループゲインであるループゲインG1main,G1subが用いられる。従って、主PLL制御誤差検出器61により算出される制御誤差値vmainと、副PLL制御誤差検出器62により算出される制御誤差値vsubには、ループゲインG1main,G1subの差に応じた差が現れる。

【0092】

ここでは、制御誤差値vmainと、制御誤差値vsubは、主位相誤差検出値emain,iと、副位相誤差検出値esub,iに基づいて算出される例について説明したが、例えば、信号dmain,i、またはフィルタリング結果θmain,iと、信号dsub,i、またはフィルタリング結果θsub,iが用いられて算出されるようにしてもよい。

【0093】

タイマ64は、初期化フラグがループゲイン制御部34から供給されることに応じて時間の計測を開始し、所定の時間が経過したタイミングで、比較完了通知をループゲイン制御部34に出力する。タイマ64には制御誤差値の算出にかかる時間が予め設定されており、その時間の計測がタイマ64により行われる。また、タイマ64は、比較完了通知をループゲイン制御部34に出力するのと同時に、比較結果出力通知を比較器63に出力する。

【0094】

ループゲイン制御部34は、内部にゲイン制御シーケンサ72を持ち、主PLL回路31−1と副PLL回路31−2の動作状況を監視しながら、最適なループゲインを探索し、それぞれのループフィルタに設定するようになされている。

【0095】

例えば、ループゲイン制御部34は、主PLL制御誤差検出器61により算出された制御誤差値vmainの方が、副PLL制御誤差検出器62により算出された制御誤差値vsubより大きい場合、それまで設定していたループゲインG1mainに替えて、ループゲインG1subと同じ値を主PLL回路31−1のループフィルタ43−1に設定する。

【0096】

制御誤差値vmainの方が制御誤差値vsubより大きいということは、副PLL回路31−2のループフィルタ43−2に設定したループゲインG1subを設定した方が、より誤差の少ない同期捕捉を行うことができることを意味する。従って、この場合、主PLL回路31−1のループフィルタ43−1のループゲインG1mainが、ループゲインG1subによって置き換えられる。

【0097】

また、ループゲイン制御部34のゲイン制御シーケンサ72は、副PLL制御誤差検出器62により算出された制御誤差値vsubの方が、主PLL制御誤差検出器61により算出された制御誤差値vmainより大きい場合、主PLL回路31−1のループフィルタ43−1のループゲインG1mainをそのままにする。

【0098】

上述した制御誤差値vsubの方が制御誤差値vmainより大きいということは、ループゲインG1mainをそのまま用いても、ループゲインG1subを用いる場合より、より誤差の少ない同期捕捉を行うことができることを意味する。従って、この場合、主PLL回路31−1のループフィルタ43−1のループゲインG1mainを、ループゲインG1subによって置き換えることは行われない。

【0099】

このようにループゲインG1mainを置き換えるか否かの処理がなされた後、ループフィルタ43−2のループゲインG1subの方が変更される。そして、再び制御誤差値vsubと制御誤差値vmainとの大きさの比較が行われ、ループゲインG1mainを置き換えるか否かが判定されることになる。このようにして、最適なループゲインが探索されるのである。

【0100】

ループゲインG1subを変更する際、ゲイン制御シーケンサ72は、ループゲインG1subを、例えば、量子化された設定G1の最小ステップをαとしてG1sub = G1sub+αに設定する。このとき、設定後のG1subが、設定範囲内の最大値G1maxを超える場合は、ループゲイン制御部34は、探索完了信号を出力するようになされている。

【0101】

また、ループゲイン制御部34は、内部の伝送モード別ゲイン選択部71によりループゲインG1mainを伝送モード毎に保持、選択して出力するようになされている。そのため、伝送モード別ゲイン選択部は伝送モード毎の最適ループゲインを保持するためのレジスタを、伝送モードの最大数N(Nは、例えば、8)と同じ数だけ有する。これらのレジスタの出力値をそれぞれ、G1main0、G1main1、・・・G1mainN-1とする。

【0102】

受信信号riの伝送モード、各伝送モードにおいて採用される変調方式、その伝送モードに割り当てられた変調スロットは、誤り訂正復号器91から供給されるTMCCにより特定される。

【0103】

伝送モード番号生成器92は、入力されるフレームスタートフラグを基点に受信シンボルをカウントし、受信シンボルのカウント値に基づいて、現在受信されたシンボルがどの変調スロットに属するかを特定する。そして、伝送モード番号生成器92は、TMCCから取得された各伝送モードに割り当てられた変調スロットを表す情報に基づいて、現在受信されたシンボルの伝送モードを識別する番号(伝送モード番号と称する)TMを特定して、これをループゲイン制御部34に出力する。

【0104】

例えば、n個の伝送モードが多重された伝送方式を受信している場合、伝送モード番号TMは0、1、・・・n−1となる。

【0105】

ゲイン制御シーケンサ72は、最適なループゲインを探索すべき伝送モード番号TMtargetを保持し、TM=TMtargetとなるシンボル受信時のみPLL制御誤差比較部33と伝送モード別ゲイン選択部71を動作させる。ゲイン制御シーケンサ72は、TM=TMtargetとなるシンボルの受信期間においてHighとなる更新EN(イネーブル)をPLL制御誤差比較部33と伝送モード別ゲイン選択部71に出力するようになされている。

【0106】

更新ENがHighとなっている場合、PLL制御誤差比較部33は、上述した処理を行うようになされている。また、更新ENがHighとなっている場合、ループゲインG1mainを、ループゲインG1subによって置き換えるとき、伝送モード別ゲイン選択部71内の更新フラグ生成部により、当該伝送モード番号TMに対応するループゲインレジスタへの書き込みフラグが出力されるようになされている。

【0107】

図5に示す周波数・位相同期回路が起動された場合、まず、TMtarget=0として最適なループゲインを探索すべき伝送モード番号は初期値に設定される。次いで、主PLL回路31−1と副PLL回路31−2のループゲインの初期値が設定されるようになされている。

【0108】

主PLL回路31−1と副PLL回路31−2のループゲインの初期化が済んだ後、ループゲイン制御部34からPLL制御誤差比較部33に初期化フラグが出力されるようになされている。

【0109】

ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、それまでの制御誤差値比較結果及びタイマ64をリセットした後に、上述したように制御誤差値vmain,i,vsub,iを算出し、比較器63において、この制御誤差値の大小比較を開始する。

【0110】

PLL制御誤差比較部33のタイマ64はリセット後にタイムカウントを開始し、制御誤差値算出に必要な時間に達したところで、ループゲイン制御部34に対し比較完了通知を出力すると同時に、比較器63に対して比較結果出力命令を出力するようになされている。これにより、比較器63からループゲイン制御部34に対して制御誤差比較結果が出力されることになる。

【0111】

ループゲイン制御部34は、制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。この際、上述したように、ループゲインG1mainを、ループゲインG1subによって置き換えられる場合、ゲイン制御シーケンサ72からループゲインG1subが伝送モード別ゲイン選択部71に供給されるようになされている。

【0112】

伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

【0113】

また、伝送モード別ゲイン選択部71は、伝送モード番号生成器92から供給される伝送モード番号TMに対応するループゲインをG1main0、G1main1、・・・G1mainN-1から選択して出力し、ループフィルタ43−1のループゲインとして供給するようになされている。

【0114】

PLL制御誤差比較部33からの比較完了通知を受け取るまでの間に、ゲイン制御シーケンサ72から探索完了信号が出力された場合、全伝送モードの最適ゲインの探索が一巡したかどうか確認するためTMtargetの値がn−1と等しいか否かが判定される。TMtargetの値がn−1と等しくない場合、次の伝送モードの最適ゲインを探索するよう、TMtargetの値が1だけインクリメントされるとともに、主PLL回路31−1と副PLL回路31−2のループゲインは再び初期化される。

【0115】

このように、TMtargetの値0乃至n−1のそれぞれについて最適なループゲインが探索されていくことになる。このようにすることで、変調方式の異なる各伝送モードのそれぞれについて最適なループゲインを設定することが可能となる。

【0116】

また、PLL制御誤差比較部33からの比較完了通知を受け取るまでの間に、ゲイン制御シーケンサ72から探索完了信号が出力された場合、TMtargetの値がn−1と等しいとき、TMtargetの値が再度0に設定されるようにしてもよい。すなわち、TMtargetの値0乃至n−1のそれぞれについて一度最適なループゲインが探索された後、再びTMtargetの値0乃至n−1のそれぞれについて最適なループゲインが探索されるようにしてもよい。

【0117】

こうすることで、例えば、伝送チャネルの伝送特性に時間変動が存在する場合においても常に最適なループゲインを探索して利用し続けることが可能となる。

【0118】

次に、図6のフローチャートを参照して、図5の周波数・位相同期回路によるループゲイン制御処理について説明する。

【0119】

ステップS11において、ゲイン制御シーケンサ72は、変数TMtargetを初期値である0に設定する。

【0120】

ステップS12において、ゲイン制御シーケンサ72は、伝送モード別ゲイン選択部71内のループゲインレジスタであって、変数TMtargetに対応するループゲインレジスタの初期値を設定する。ここでは、当該ループゲインレジスタの設定値がG1main_newとして表わされており、初期値はG1initとされている。なお、設定値G1main_newは、ループフィルタ43−1のループゲインG1mainとして用いられることになる。

【0121】

また、ステップS12において、ゲイン制御シーケンサ72は、ループフィルタ43−2のループゲインG1subの初期値を設定する。ループゲインG1subの初期値は、ループゲインの最小値とされ、ここではG1minとされている。なお、設定値G1subは、ループフィルタ43−2のループゲインG1subとして用いられることになる。

【0122】

ループゲインの初期設定を行った後、ステップS13において、ループゲイン制御部34は、PLL制御誤差比較部33に対して初期化フラグを出力する。

【0123】

これにより、初期化フラグを受信したPLL制御誤差比較部33においては、それまでの制御誤差値の比較結果と内部タイマの計測値がリセットされることになる。

【0124】

また、PLL制御誤差比較部33の主PLL制御誤差検出器61においては、主PLL回路31−1により出力された主PLL中間信号に基づいて制御誤差値vmainが算出される。副PLL制御誤差検出器62においては、副PLL回路31−2により出力された副PLL中間信号に基づいて制御誤差値vsubが算出される。

【0125】

タイマ64においては、リセット後にタイムカウントが開始され、制御誤差値vmain、vsubの算出に必要な時間が経過したとき、ループゲイン制御部34に対して比較完了通知が出力され、それと同時に、比較器63に対して比較結果出力命令が出力される。比較結果出力命令が供給されることに応じて、比較器63からループゲイン制御部34に対して、制御誤差値vmainと、制御誤差値vsubとの大小の比較結果が出力される。

【0126】

ステップS14において、ゲイン制御シーケンサ72は、タイマ64から出力される比較完了通知を検出したか否かを判定し、まだ、比較完了通知を検出していないと判定された場合、処理は、ステップS20に進む。

【0127】

ステップS20では、探索完了信号が出力されたか否かが判定され、まだ、出力されていないと判定された場合、処理は、ステップS21に進み、例えば、タイマ64からの比較完了通知を検出するポーリングを一定の時間間隔で行い、待機する。その後、処理は、ステップS14に戻る。

【0128】

ステップS14において、比較完了通知を検出したと判定された場合、処理は、ステップS15に進む。

【0129】

ステップS15において、ゲイン制御シーケンサ72は、比較器63から供給された比較結果に基づいて、vmain>vsubであるか否かを判定する。

【0130】

vmain>vsubであるとステップS15において判定した場合、ステップS16において、ゲイン制御シーケンサ72は、ループゲインG1main_newを、ループフィルタ43−2のループゲインとしていま設定しているG1subに置き換える。このとき、ゲイン制御シーケンサ72から伝送モード別ゲイン選択部71内の更新フラグ生成部に所定の信号が出力され、更新フラグ生成部により、現在の伝送モード番号TMに対応するループゲインレジスタへの書き込みフラグが出力される。

【0131】

一方、vmain>vsubではなく、vmain≦vsubであるとステップS15において判定された場合、ステップS16の処理はスキップされる。

【0132】

ステップS17において、ゲイン制御シーケンサ72は、ループゲインG1subとしてG1sub+αを設定して更新する。ここでαは、ループゲインG1(G1main、またはG1sub)を量子化した最小ステップに相当するゲイン量である。

【0133】

ステップS18において、ゲイン制御シーケンサ72は、ステップS17の処理により更新された後のループゲインG1subが、設定範囲内の最大値G1maxを超えるか否かを判定する。

【0134】

ステップS18において、ループゲインG1subが、最大値G1maxを超えたと判定された場合、処理は、ステップS19に進み、ゲイン制御シーケンサ72は、探索完了信号を出力する。

【0135】

ステップS18において、ループゲインG1subが、最大値G1maxを超えていないと判定された場合、ステップS19の処理はスキップされる。

【0136】

ステップS18において、ループゲインG1subが、最大値G1maxを超えていないと判定された場合、または、ステップS19の処理の後、処理は、ステップS13に戻る。

【0137】

ステップS19で探索完了信号が出力された場合、その後のステップS20の処理では、探索完了信号が出力されたと判定されるので、処理は、ステップS22に進む。

【0138】

ステップS22において、ゲイン制御シーケンサ72は、変数TMtargetの値がn−1と等しいか否かを判定し、変数TMtargetの値がn−1と等しくないと判定された場合、処理は、ステップS23に進む。ステップS23において、ゲイン制御シーケンサ72は、変数TMtargetの値を1だけインクリメントする。その後、処理は、ステップS12に戻る。すなわち、次の伝送モード番号において最適となるループゲインの探索が行われることになる。

【0139】

一方、ステップS22において、変数TMtargetの値がn−1と等しいと判定された場合、処理は、ステップS11に戻る。すなわち、全ての伝送モード番号について最適なループゲインが探索された後、あらためてTMtargetの値0乃至n−1のそれぞれについて最適なループゲインが探索される。なお、2回目以降の探索においては、ステップS12の処理において、G1main_newを初期化する必要はない。

【0140】

なお、ステップS22において、変数TMtargetの値がn−1と等しいと判定された場合、処理が終了されるようにしてもよい。

【0141】

このようにして、ループゲイン制御処理が実行される。このように、本発明によれば、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができる。

【0142】

以上においては、周波数・位相同期回路において、検出された位相誤差に対する直接の乗算に用いられるループゲインG1として最適なループゲインを探索する例について説明したが、ループゲインG1を用いた乗算後の位相誤差に対する乗算に用いられるループゲインG2が探索されるようにしてもよい。

【0143】

また、ループゲインG1とループゲインG2の両方が探索されるようにしてもよい。

【0144】

図7は、本発明の周波数・位相同期回路を適用した受信システムの第1実施の形態の構成例を示すブロック図である。

【0145】

図7の受信システムは、取得部101、伝送路復号処理部102、および情報源復号処理部103から構成される。

【0146】

取得部101は、地上デジタル放送、衛星デジタル放送、CATV網、インターネットその他のネットワーク等の図示せぬ伝送路を介して信号を取得し、伝送路復号処理部102に供給する。

【0147】

伝送路復号処理部102は、取得部101が伝送路を介して取得した信号に対して、同期検波と誤り訂正を含む伝送路復号処理を施し、その結果得られる信号を情報源復号処理部103に供給する。すなわち、伝送路復号処理部102には、図5に示される周波数・位相同期回路の構成が含まれており、その周波数・位相同期回路において、上述した同期検波が行われる。

【0148】

情報源復号処理部103は、伝送路復号処理が施された信号に対して、圧縮された情報を元の情報に伸張し、送信対象のデータを取得する処理を含む情報源復号処理を施す。

【0149】

すなわち、取得部101が伝送路を介して取得した信号には、画像や音声等のデータ量を少なくするために、情報を圧縮する圧縮符号化が施されていることがある。その場合、情報源復号処理部103は、伝送路復号処理が施された信号に対して、圧縮された情報を元の情報に伸張する処理等の情報源復号処理を施す。

【0150】

なお、取得部101が伝送路を介して取得した信号に圧縮符号化が施されていない場合、情報源復号処理部103では、圧縮された情報を元の情報に伸張する処理は行われない。ここで、伸張処理としては、例えば、MPEGデコード等がある。また、情報源復号処理には、伸張処理の他、デスクランブル等が含まれることがある。

【0151】

図7の受信システムは、例えば、デジタルテレビジョン放送を受信するテレビチューナ等に適用することができる。なお、取得部101、伝送路復号処理部102、および情報源復号処理部103は、それぞれ、1つの独立した装置(ハードウェア(IC(Integrated Circuit)等))、又はソフトウェアモジュール)として構成することが可能である。

【0152】

また、取得部101、伝送路復号処理部102、および、情報源復号処理部103については、それらの3つのセットを1つの独立した装置として構成することが可能である。取得部101と伝送路復号処理部102とのセットを1つの独立した装置として構成することも可能であるし、伝送路復号処理部102と情報源復号処理部103とのセットを1つの独立した装置として構成することも可能である。

【0153】

図8は、本発明の周波数・位相同期回路を適用した受信システムの第2実施の形態の構成例を示すブロック図である。

【0154】

図8に示す構成のうち、図7に示す構成と対応する構成については、同一の符号を付してあり、その説明は適宜省略する。

【0155】

図8の受信システムの構成は、取得部101、伝送路復号処理部102、および情報源復号処理部103を有する点で図7の構成と共通し、出力部111が新たに設けられている点で図7の構成と相違する。

【0156】

出力部111は、例えば、画像を表示する表示装置や音声を出力するスピーカであり、情報源復号処理部103から出力される信号としての画像や音声等を出力する。すなわち、出力部111は、画像を表示し、あるいは、音声を出力する。

【0157】

図8の受信システムは、例えば、デジタル放送としてのテレビジョン放送を受信するTVや、ラジオ放送を受信するラジオ受信機等に適用することができる。

【0158】

なお、取得部101において取得された信号に圧縮符号化が施されていない場合、伝送路復号処理部102が出力する信号が、直接、出力部111に供給される。

【0159】

図9は、本発明の周波数・位相同期回路を適用した受信システムの第3実施の形態の構成例を示すブロック図である。

【0160】

図9に示す構成のうち、図7に示す構成と対応する構成については同一の符号を付してあり、その説明は適宜省略する。

【0161】

図9の受信システムの構成は、取得部101、および伝送路復号処理部102を有する点で図7の構成と共通し、情報源復号処理部103が設けられておらず、記録部121が新たに設けられている点で図7の構成と相違する。

【0162】

記録部121は、伝送路復号処理部102が出力する信号(例えば、MPEGのTSのTSパケット)を、光ディスクや、ハードディスク(磁気ディスク)、フラッシュメモリ等の記録

(記憶)媒体に記録する(記憶させる)。

【0163】

以上のような図9の受信システムは、テレビジョン放送を録画するレコーダ機器等に適用することができる。

【0164】

なお、情報源復号処理部103を設け、情報源復号処理部103で情報源復号処理が施された後の信号、すなわち、デコードによって得られる画像や音声を記録部121で記録するようにしてもよい。

【0165】

なお、上述した一連の処理は、ハードウェアにより実行させることもできるし、ソフトウェアにより実行させることもできる。上述した一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータにネットワークや記録媒体からインストールされる。また、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば図10に示されるような汎用のパーソナルコンピュータ700などに、ネットワークや記録媒体からインストールされる。

【0166】

図10において、CPU(Central Processing Unit)701は、ROM(Read Only Memory)702に記憶されているプログラム、または記憶部708からRAM(Random Access Memory)703にロードされたプログラムに従って各種の処理を実行する。RAM703にはまた、CPU701が各種の処理を実行する上において必要なデータなども適宜記憶される。

【0167】

CPU701、ROM702、およびRAM703は、バス704を介して相互に接続されている。このバス704にはまた、入出力インタフェース705も接続されている。

【0168】

入出力インタフェース705には、キーボード、マウスなどよりなる入力部706、LCD(Liquid Crystal display)などよりなるディスプレイ、並びにスピーカなどよりなる出力部707が接続されている。また、入出力インタフェース705には、ハードディスクなどより構成される記憶部708、モデム、LANカードなどのネットワークインタフェースカードなどより構成される通信部709が接続されている。通信部709は、インターネットを含むネットワークを介しての通信処理を行う。

【0169】

入出力インタフェース705にはまた、必要に応じてドライブ710が接続され、磁気ディスク、光ディスク、光磁気ディスク、或いは半導体メモリなどのリムーバブルメディア711が適宜装着されている。そして、それらのリムーバブルメディアから読み出されたコンピュータプログラムが、必要に応じて記憶部708にインストールされる。

【0170】

上述した一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが、インターネットなどのネットワークや、リムーバブルメディア711などからなる記録媒体からインストールされる。

【0171】

なお、この記録媒体は、図10に示される、装置本体とは別に、ユーザにプログラムを配信するために配布される、プログラムが記録されている磁気ディスク(フロッピディスク(登録商標)を含む)、光ディスク(CD-ROM(Compact Disk-Read Only Memory),DVD(Digital Versatile Disk)を含む)、光磁気ディスク(MD(Mini-Disk)(登録商標)を含む)、もしくは半導体メモリなどよりなるリムーバブルメディア711により構成されるものだけでなく、装置本体に予め組み込まれた状態でユーザに配信される、プログラムが記録されているROM702や、記憶部708に含まれるハードディスクなどで構成されるものも含む。

【0172】

なお、本明細書において上述した一連の処理は、記載された順序に沿って時系列的に行われる処理はもちろん、必ずしも時系列的に処理されなくとも、並列的あるいは個別に実行される処理をも含むものである。

【0173】

また、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【符号の説明】

【0174】

31−1 主PLL回路, 31−2 副PLL回路, 32 乗算器, 33 PLL制御誤差比較部, 34 ループゲイン制御部, 41−1,41−2 乗算器, 42−1,42−2 位相誤差検出器, 43−1,43−2 ループフィルタ, 44−1,44−2 数値制御発振器, 51−1,51−2 乗算器, 52−1,52−2 乗算器, 53−1,53−2 積分器, 54−1,54−2 加算器, 61 主PLL制御誤差検出器, 62 副PLL制御誤差検出器, 63 比較器, 64 タイマ, 71 伝送モード別ゲイン選択部, 72 ゲイン制御シーケンサ, 91 誤り訂正復号部, 92 伝送モード番号生成器

【技術分野】

【0001】

本発明は、同期回路、同期方法、および受信システムに関し、特に、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする同期回路、同期方法、および受信システムに関する。

【背景技術】

【0002】

近年、携帯電話やデジタル放送(衛星/地上波)、無線LANなどの無線デジタル伝送技術の発展がめざましい。

【0003】

例えば、無線デジタル伝送に用いられる受信機において、高い受信性能を実現するためには、各同期回路の性能が重要となる。とりわけ搬送波周波数位相同期回路に関しては、ビット誤りに直接的な影響を与えるため、その同期性能が受信性能に対して極めて重要になる。

【0004】

周波数・位相同期回路の代表例としてデジタルPLL(Phase-Locked Loop)が挙げられる。

【0005】

デジタルPLLを用いた周波数・位相同期回路は、位相誤差検出器、ループフィルタ、数値制御発振器(NCO)により構成される。

【0006】

図1は、デジタルPLLを用いた周波数・位相同期回路を含む、従来の受信機の構成の一部を示す図である。

【0007】

図1に示すように、受信機には、RF(Radio Frequency)回路2と復調回路3が設けられる。アンテナ1において電波が受信されることによって得られた受信信号はRF回路2の乗算器2−1に入力される。

【0008】

乗算器2−1は、局部発振器2−2から供給された局部発振信号と、アンテナ1から供給された受信信号を乗算し、得られた信号をLPF(Low Pass Filter)2−3に供給する。

【0009】

局部発振器2−2は、局部発振信号を生成し、乗算器2−1に出力する。

【0010】

LPF2−3は、乗算器2−1から出力される乗算信号を入力し、低域周波数成分のみを通過させるフィルタリング処理を行い、A/D(Analog/Digital)変換器2−4に出力する。

【0011】

PSK(Phase Shift Keying)変調などで変調が施されている受信信号の周波数をfc、位相をθc、局部発振器2−2により生成された局部発振信号の周波数をf0、位相をθ0とすると、LPFから出力される信号には、fc−f0に相当する周波数差Δfが含まれ、θc−θ0に相当する位相差θが含まれる。

【0012】

A/D変換器2−4は、LPF2−3から出力された信号に対してA/D変換を施す。A/D変換が施されることによって得られたデジタルの受信信号である受信信号riは復調回路3に供給される。iは、その受信信号が何番目のシンボルの信号であるのかを表す。

【0013】

受信信号riには、2πΔft+θとして表される位相誤差が含まれる。

【0014】

図2は、図1の復調回路3に設けられる、デジタルPLLを用いた周波数・位相同期回路の構成を示す図である。

【0015】

図2に示すように、周波数・位相同期回路は、PLL回路11と乗算器12から構成される。PLL回路11は、乗算器21、位相誤差検出器22、ループフィルタ23、および数値制御発振器(NCO)24から構成される。

【0016】

PSK変調が施されている受信信号riは、PLL回路11の乗算器21と、乗算器12にそれぞれ入力される。

【0017】

PLL回路11の乗算器21は、数値制御発振器24から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、乗算して得られた信号を位相誤差検出器22に出力する。

【0018】

位相誤差検出器22は、乗算器21が出力する信号に残留する位相誤差を検出し、ループフィルタ23に出力する。

【0019】

例えば、受信信号riが既知シンボルの信号である場合、位相誤差検出器22は、乗算器21の出力信号によって表されるシンボルの位相と、既知シンボルの位相との差を位相誤差として検出する。また、受信信号riが既知シンボルの信号ではない場合、位相誤差検出器22は、乗算器21の出力信号によって表される実際のシンボルの位相と、その硬判定結果のシンボルの位相との差を位相誤差として検出する。

【0020】

ループフィルタ23は比例積分型のループフィルタであり、位相誤差検出器22が出力する位相誤差の検出値にフィルタリングを施し、数値制御発振器24に出力する。

【0021】

詳細には、ループフィルタ23の乗算器23−1は、位相誤差検出器22から供給された位相誤差の検出値を、設定されているループゲインG1に従ってG1倍し、乗算器23−2と加算器23−4に出力する。

【0022】

乗算器23−2は、乗算器23−1から供給された、G1倍された位相誤差の検出値を、設定されているループゲインG2に従ってG2倍し、積分器23−3に出力する。乗算器23−1、乗算器23−2は、入力信号に対してループゲインG1またはG2の重みを付加する重み付け乗算器である。

【0023】

積分器23−3は、乗算器23−2の出力を積分し、加算器23−4に出力する。

【0024】

加算器23−4は、乗算器23−1の出力と積分器23−3の出力を加算し、フィルタリング結果として数値制御発振器24に出力する。

【0025】

数値制御発振器24は、ループフィルタ23のフィルタリング結果に基づいて位相制御量e-j(2πΔft+θ)を生成し、乗算器21と乗算器12に出力する。

【0026】

乗算器12は、数値制御発振器24から出力された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号を同期検波信号diとして出力する。

【0027】

ところで、ループフィルタ23のループゲインG1、G2は、ループフィルタ23の特性であるフィルタ帯域を決定する。ループフィルタ23の帯域とPLL回路11の性能については、以下のような関係を有することが知られている。

【0028】

すなわち、ループフィルタの帯域が広い(大きい)場合、位相誤差変動への追従性が上がる一方で、PLLから出力される同期検波信号のジッタ量が大きくなる。逆に、ループフィルタの帯域が狭い(小さい)場合は位相誤差変動への追従性は落ちるが、出力同期検波信号のジッタ量は小さくなる。

【0029】

【特許文献1】特開2009−26426号公報

【発明の開示】

【発明が解決しようとする課題】

【0030】

しかしながら、実際の無線デジタル伝送の受信機においては、局部発振器の温度依存特性やRF回路内での意図せぬ発振等により、受信信号の位相、周波数に雑音が生じることがある。従って、デジタルPLLを用いた周波数・同期回路において、最適な同期性能を実現するためには、受信機特性の固体差や時間変動によって適したループゲインを設定する必要がある。

【0031】

従来のデジタルPLLでは、ループゲインを固定的に設定することしかできず、最適な受信性能を得るためには、受信環境に合わせて調整されたループゲインを個体毎に設定しなくてはならない。また、温度等により伝送チャネルが動的に変化し、それに応じて最適なループゲインが動的に変化するような場合、使用しているループゲインが最適なものではなくなってしまう。

【0032】

さらに、PLLのループフィルタにとって最適となるループゲインは、受信信号における変調方式によっても異なる場合がある。例えば、日本の衛星デジタル放送方式では1フレーム内で複数の変調方式が混在する。このような場合、単一のループゲインしか設定できないとすると、ある変調方式には最適なループゲインであっても、他の変調方式には最適ではなくなるため、受信性能の劣化をもたらす。

【0033】

本発明はこのような状況に鑑みてなされたものであり、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにするものである。

【課題を解決するための手段】

【0034】

本発明の第1の側面は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する同期回路である。

【0035】

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差と前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差の大きさを比較する比較手段と、指定された伝送モードの前記スロットに対応する受信信号が入力されている間、前記比較手段による比較が行われる都度、前記第2のPLL回路に含まれる第2のループフィルタのループゲインの値を所定の量だけ変更することで前記伝送モードにおける最適なループゲイン設定値を探索するループゲイン探索手段とをさらに備え、前記保持手段は、前記ループゲイン探索手段により前記第2のループフィルタのループゲインの値が所定の回数変更された場合、前記第1のループフィルタのループゲインとして設定されている値を、前記伝送モードにおける最適なループゲイン設定値として保持するようにすることができる。

【0036】

前記受信信号のスロットのそれぞれの伝送モードを特定する情報である伝送モード番号を、前記受信信号を復号して得られる制御情報に基づいて特定する伝送モード番号特定手段とをさらに備え、前記ループゲイン探索手段は、前記特定された伝送モード番号が前記指定された伝送モードに対応するものである場合、前記最適なループゲイン設定値を探索し、前記保持手段は、前記伝送モード番号特定手段により特定された伝送モード番号に対応づけて前記最適なループゲイン設定値を保持するようにすることができる。

【0037】

前記第1のPLL回路は、位相制御後の信号に残留する位相誤差を検出する第1の検出回路と、前記第1の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第1のループフィルタと、前記第1のループフィルタによるフィルタ処理の結果に応じて前記第1の位相制御信号を出力する第1の発振回路と、前記第1の発振回路から出力された前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第1の検出回路に出力する前記第1の出力回路とを備え、前記第2のPLL回路は、位相制御後の信号に残留する位相誤差を検出する第2の検出回路と、前記第2の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第2のループフィルタと、前記第2のループフィルタによるフィルタ処理の結果に応じて前記第2の位相制御信号を出力する第2の発振回路と、前記第2の発振回路から出力された前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第2の検出回路に出力する前記第2の出力回路とを備えるようにすることができる。

【0038】

前記第1のループフィルタは、前記第1の検出回路により検出された位相誤差に第1のループゲインを乗算する第1の乗算回路と、前記第1の乗算回路による乗算後の位相誤差に第2のループゲインを乗算する第2の乗算回路と、前記第1の乗算回路による乗算後の位相誤差と、前記第2の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第1の発振回路に出力する第1の加算回路とを備え、前記第2のループフィルタは、前記第2の検出回路により検出された位相誤差に第3のループゲインを乗算する第3の乗算回路と、前記第3の乗算回路による乗算後の位相誤差に第4のループゲインを乗算する第4の乗算回路と、前記第3の乗算回路による乗算後の位相誤差と、前記第4の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第2の発振回路に出力する第2の加算回路とを備えるようにすることができる。

【0039】

前記制御回路は、前記第1のループゲインと前記第3のループゲインの値としてそれぞれ異なる値を設定するようにすることができる。

【0040】

本発明の第1の側面は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を第1のPLL回路から出力し、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を第2のPLL回路から出力し、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第1の出力回路から出力し、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第2の出力回路から出力し、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を第1の検出回路において検出し、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を第2の検出回路において検出し、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定し、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持するステップを含み、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記伝送モード毎に前記ループゲイン設定値が保持される同期方法である。

【0041】

本発明の第2の側面は、伝送路を介して送信されてきた信号を取得する取得手段と、

前記取得手段により取得された信号に対して同期検波処理を含む処理を行う伝送路復号処理手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0042】

本発明の第3の側面は、伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、前記伝送路復号処理手段による処理後の信号に対して、送信対象のデータを復号する処理を施す情報源復号処理手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0043】

本発明の第4の側面は、伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、前記伝送路復号処理手段による処理後の信号に基づいて、画像または音声を出力する出力手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0044】

本発明の第5の側面は、伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、前記伝送路復号処理手段による処理後の信号を記録する記録手段とを備え、前記伝送路復号処理手段は、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する受信システムである。

【0045】

本発明においては、入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号が第1のPLL回路から出力され、前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号が第2のPLL回路から出力され、前記第1の位相制御信号に基づいて前記受信信号の位相が制御され、位相制御後の信号が第1の出力回路から出力され、前記第2の位相制御信号に基づいて前記受信信号の位相が制御され、位相制御後の信号が第2の出力回路から出力され、前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差が第1の検出回路において検出され、前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差が第2の検出回路において検出され、前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値が設定され、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値が保持され、前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、前記伝送モード毎に前記ループゲイン設定値が保持される。

【発明の効果】

【0046】

本発明によれば、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができる。

【図面の簡単な説明】

【0047】

【図1】デジタルPLLを用いた周波数・位相同期回路を含む、従来の受信機の構成の一部を示す図である。

【図2】図1に設けられる、デジタルPLLを用いた周波数・位相同期回路の構成を示す図である。

【図3】高度BSのフレームの構成を説明する図である。

【図4】高度BSの1フレーム内での伝送モードの例を示す図である。

【図5】本発明の一実施形態に係る周波数・位相同期回路の構成例を示すブロック図である。

【図6】ループゲイン制御処理の例を説明するフローチャートである。

【図7】本発明の周波数・位相同期回路を適用した受信システムの第1実施の形態の構成例を示すブロック図である。

【図8】本発明の周波数・位相同期回路を適用した受信システムの第2実施の形態の構成例を示すブロック図である。

【図9】本発明の周波数・位相同期回路を適用した受信システムの第3実施の形態の構成例を示すブロック図である。

【図10】パーソナルコンピュータの構成例を示すブロック図である。

【発明を実施するための形態】

【0048】

以下、図面を参照して、本発明の実施の形態について説明する。

【0049】

最初に、日本の次世代衛星デジタル放送である高度広帯域衛星デジタル放送(高度BS)のフレーム構成について説明する。

【0050】

図3は、高度BSのフレームの構成を説明する図である。同図に示されるように、1フレームは、120の変調スロットで構成されており、この例では、各変調スロットが、変調スロット#1乃至変調スロット#120として示されている。

【0051】

各変調スロットには、同期のための24シンボル(同図には、Fsync、!Fsync、Ssyncと示されている)および信号点の位置の判定などに用いられる32シンボル(同図には、Pilotと示されている)からなる既知シンボルが含まれている。

【0052】

また、各変調スロットには、136シンボルで構成される66の伝送データが含まれている。例えば、変調スロット#1における伝送データは、Data#1乃至Data#66として示されており、変調スロット#2における伝送データは、Data#67乃至Data#132として示されている。

【0053】

さらに、各変調スロットにおいては、伝送・多重に関する制御情報であって4シンボルで構成されるTMCCが、各伝送データの間に挿入されている。図中では、Tとして示されているものがTMCCである。

【0054】

このように構成される高度BSの1フレームは、合計1,115,520シンボルで構成されることになる。

【0055】

また、高度BSでは1フレーム内で複数の変調方式を混在させることが可能となる。例えば、1フレーム内に最大8の伝送モードを定義することが可能であり、個々の伝送モードにおいて異なる変調方式が採用されるようにすることができる。高度BSでは、BPSK、QPSK、8PSK、16APSK、および32APSKの5種類の変調方式を用いることが可能とされている。

【0056】

図4は、高度BSの1フレーム内での伝送モードの例を示す図である。簡単のため、伝送モード数は2としている。同図に示されるように、例えば、変調スロット#1乃至変調スロット#40に対しては、変調方式が32APSKである伝送モード1が割り当てられ、変調スロット#41乃至変調スロット#120に対しては、変調方式が16APSKである伝送モード2が割り当てられる。

【0057】

各変調スロットの伝送モードは、当該フレームより2フレーム前のTMCCを解析することにより特定することができるようになされている。従って、受信機は、2フレーム前に受信したフレームの各変調スロットに挿入されたTMCCを全て取得して記憶しておくことにより、受信したフレームの各変調スロットの変調方式を特定するようになされている。なお、各変調スロットの伝送モードに関わらず、TMCCは、常にπ/2シフトBPSK変調されるようになされている。

【0058】

本発明においては、例えば、図4に示されるように、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【0059】

図5は、本発明の一実施形態に係る周波数・位相同期回路の構成例を示すブロック図である。

【0060】

図5に示す周波数・位相同期回路が、例えば、図1に示す構成と同じ構成を有する受信機の復調回路3に設けられる。

【0061】

図5に示す周波数・位相同期回路の構成は、主に、同じ構成を有するPLLが一つ追加されることによって主副2系統のPLL回路が設けられる点、2系統のPLL回路内のループフィルタのループゲインが可変になっている点、および、ループゲインを制御する構成が追加して設けられている点が、従来の回路構成と異なる。

【0062】

2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、それぞれ、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。それぞれに設けられるループフィルタのループゲインとして同じ値が設定され、同じ信号が入力された場合、主PLL回路31−1から出力される信号と副PLL回路31−2から出力される信号は一致する。

【0063】

後述するように、主PLL回路31−1は、同期検波を実際に行うための回路であり、副PLL回路31−2は、主PLL回路31−1のループフィルタの特性を規定するループゲインを決定するためのいわばトライアルを行うための回路である。

【0064】

i番目(iシンボル目)の信号である受信信号riは、主PLL回路31−1の乗算器41−1、副PLL回路31−2の乗算器41−2、および、乗算器32に入力される。受信信号riには、上述したように2πΔft+θとして表される位相誤差が含まれる。

【0065】

主PLL回路31−1の乗算器41−1は、数値制御発振器44−1から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号dmain,iを位相誤差検出器42−1に出力する。乗算器41−1から出力される信号は、乗算器32から出力される、位相制御の信号である同期検波信号dmain,iと同じ信号になる。

【0066】

位相誤差検出器42−1は、乗算器41−1が出力する信号に残留する位相誤差を検出し、主位相誤差検出値emain,iを出力する。位相誤差検出器42−1においては、図2の位相誤差検出器22と同様にして位相誤差の検出が行われる。後述する副PLL回路31−2の位相誤差検出器42−2においても同様である。

【0067】

位相誤差検出器42−1から出力された主位相誤差検出値emain,iは、ループフィルタ43−1の乗算器51−1に供給される。

【0068】

ループフィルタ43−1は比例積分型のループフィルタであり、位相誤差検出器42−1が出力する主位相誤差検出値emain,iにフィルタリングを施し、数値制御発振器44−1に出力する。

【0069】

詳細には、ループフィルタ43−1の乗算器51−1は、主位相誤差検出値emain,iを、ループゲイン制御部34により設定されたループゲインG1mainに従ってG1main倍し、乗算器52−1と加算器54−1に出力する。

【0070】

乗算器52−1は、乗算器51−1から供給された、G1main倍された主位相誤差検出値emain,iをさらにG2倍し、積分器53−1に出力する。

【0071】

積分器53−1は、乗算器52−1の出力を積分し、加算器54−1に出力する。

【0072】

加算器54−1は、乗算器51−1の出力と積分器53−1の出力を加算し、フィルタリング結果θmain,iとして数値制御発振器44−1に出力する。

【0073】

数値制御発振器44−1は、ループフィルタ43−1のフィルタリング結果に基づいて位相制御量e-j(2πΔft+θ)を生成し、乗算器41−1と乗算器32に出力する。

【0074】

乗算器32は、主PLL回路31−1の数値制御発振器44−1から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号を同期検波信号dmain,iとして出力する。

【0075】

なお、信号dmain,iと、主位相誤差検出値emain,iと、フィルタリング結果θmain,iとを含む信号が、主PLL回路31−1から、PLL制御誤差比較部33の主PLL制御誤差検出部61に、主PLL中間信号として供給されるようになされている。

【0076】

副PLL回路31−2においても、主PLL回路31−1に入力される信号と同じ受信信号riを対象として同様の処理が行われる。

【0077】

すなわち、副PLL回路31−2の乗算器41−2は、数値制御発振器44−2から供給された位相制御量e-j(2πΔft+θ)を受信信号riに乗算し、得られた信号dsub,iを位相誤差検出器42−2に出力する。

【0078】

位相誤差検出器42−2は、乗算器41−2が出力する信号に残留する位相誤差を検出し、副位相誤差検出値esub,iを出力する。位相誤差検出器42−2から出力された副位相誤差検出値esub,iは、ループフィルタ43−2の乗算器51−2に供給される。

【0079】

ループフィルタ43−2の乗算器51−2は、副位相誤差検出値esub,iを、ループゲイン制御部34により設定されたループゲインG1subに従ってG1sub倍し、乗算器52−2と加算器54−2に出力する。

【0080】

例えば、乗算器51−2には、ループゲインG1subとして、主PLL回路31−1の乗算器51−1に設定されたループゲインG1mainとは異なる値が設定される。

【0081】

乗算器52−2は、乗算器51−2から供給された、G1sub倍された副位相誤差検出値esub,iをさらにG2倍し、積分器53−2に出力する。主PLL回路31−1の乗算器52−1と、副PLL回路31−2の乗算器52−2においては、同じループゲインを用いて重み付けが行われることになる。ループゲインG2は、予め設定された固定の値である。

【0082】

積分器53−2は、乗算器52−2の出力を積分し、加算器54−2に出力する。

【0083】

加算器54−2は、乗算器51−2の出力と積分器53−2の出力を加算し、フィルタリング結果θsub,iとして数値制御発振器44−2に出力する。

【0084】

数値制御発振器44−2は、ループフィルタ43−2のフィルタリング結果に基づいて位相制御量e-j(2πΔft+θ)を生成し、乗算器41−2に出力する。

【0085】

なお、信号dmain,iと、副位相誤差検出値esub,iと、フィルタリング結果θsub,iとを含む信号が、副PLL回路31−2から、PLL制御誤差比較部33の副PLL制御誤差検出部62に、副PLL中間信号として供給されるようになされている。

【0086】

PLL制御誤差比較部33の主PLL制御誤差検出器61は、受信信号riが入力される毎に主PLL回路31−1から供給される主PLL中間信号を受信する。例えば、主PLL制御誤差検出器61は、所定の数のシンボルの受信信号riを対象として得られた主位相誤差検出値emain,iに基づいて、主位相誤差検出値emain,iの分散値を算出し、制御誤差値vmainとして比較器63に出力する。

【0087】

乗算器41−1による乗算結果、すなわち主PLL回路31−1における位相制御後の信号に残留する位相誤差の検出値である主位相誤差検出値emain,iに基づいて算出される値であるから、制御誤差値vmainは、主PLL回路31−1による位相制御の誤差を表す。

【0088】

副PLL制御誤差検出器62は、受信信号riが入力される毎に副PLL回路31−2から供給される副PLL中間信号を受信する。例えば、副PLL制御誤差検出器62は、所定の数のシンボルの受信信号riを対象として得られた副位相誤差検出値esub,iに基づいて、副位相誤差検出値esub,iの分散値を算出し、制御誤差値vsubとして比較器63に出力する。

【0089】

乗算器41−2による乗算結果、すなわち副PLL回路31−2における位相制御後の信号に残留する位相誤差の検出値である副位相誤差検出値esub,iに基づいて算出される値であるから、制御誤差値vsubは、副PLL回路31−2による位相制御の誤差を表す。

【0090】

比較器63は、主PLL制御誤差検出器61から供給された制御誤差値vmainと、副PLL制御誤差検出器62から供給された制御誤差値vsubの大小の比較結果を、比較結果出力通知がタイマ64から供給されることに応じてループゲイン制御部34に出力する。

【0091】

上述したように、主PLL回路31−1のループフィルタ43−1と副PLL回路31−2のループフィルタ43−2においては、それぞれ異なるループゲインであるループゲインG1main,G1subが用いられる。従って、主PLL制御誤差検出器61により算出される制御誤差値vmainと、副PLL制御誤差検出器62により算出される制御誤差値vsubには、ループゲインG1main,G1subの差に応じた差が現れる。

【0092】

ここでは、制御誤差値vmainと、制御誤差値vsubは、主位相誤差検出値emain,iと、副位相誤差検出値esub,iに基づいて算出される例について説明したが、例えば、信号dmain,i、またはフィルタリング結果θmain,iと、信号dsub,i、またはフィルタリング結果θsub,iが用いられて算出されるようにしてもよい。

【0093】

タイマ64は、初期化フラグがループゲイン制御部34から供給されることに応じて時間の計測を開始し、所定の時間が経過したタイミングで、比較完了通知をループゲイン制御部34に出力する。タイマ64には制御誤差値の算出にかかる時間が予め設定されており、その時間の計測がタイマ64により行われる。また、タイマ64は、比較完了通知をループゲイン制御部34に出力するのと同時に、比較結果出力通知を比較器63に出力する。

【0094】

ループゲイン制御部34は、内部にゲイン制御シーケンサ72を持ち、主PLL回路31−1と副PLL回路31−2の動作状況を監視しながら、最適なループゲインを探索し、それぞれのループフィルタに設定するようになされている。

【0095】

例えば、ループゲイン制御部34は、主PLL制御誤差検出器61により算出された制御誤差値vmainの方が、副PLL制御誤差検出器62により算出された制御誤差値vsubより大きい場合、それまで設定していたループゲインG1mainに替えて、ループゲインG1subと同じ値を主PLL回路31−1のループフィルタ43−1に設定する。

【0096】

制御誤差値vmainの方が制御誤差値vsubより大きいということは、副PLL回路31−2のループフィルタ43−2に設定したループゲインG1subを設定した方が、より誤差の少ない同期捕捉を行うことができることを意味する。従って、この場合、主PLL回路31−1のループフィルタ43−1のループゲインG1mainが、ループゲインG1subによって置き換えられる。

【0097】

また、ループゲイン制御部34のゲイン制御シーケンサ72は、副PLL制御誤差検出器62により算出された制御誤差値vsubの方が、主PLL制御誤差検出器61により算出された制御誤差値vmainより大きい場合、主PLL回路31−1のループフィルタ43−1のループゲインG1mainをそのままにする。

【0098】

上述した制御誤差値vsubの方が制御誤差値vmainより大きいということは、ループゲインG1mainをそのまま用いても、ループゲインG1subを用いる場合より、より誤差の少ない同期捕捉を行うことができることを意味する。従って、この場合、主PLL回路31−1のループフィルタ43−1のループゲインG1mainを、ループゲインG1subによって置き換えることは行われない。

【0099】

このようにループゲインG1mainを置き換えるか否かの処理がなされた後、ループフィルタ43−2のループゲインG1subの方が変更される。そして、再び制御誤差値vsubと制御誤差値vmainとの大きさの比較が行われ、ループゲインG1mainを置き換えるか否かが判定されることになる。このようにして、最適なループゲインが探索されるのである。

【0100】

ループゲインG1subを変更する際、ゲイン制御シーケンサ72は、ループゲインG1subを、例えば、量子化された設定G1の最小ステップをαとしてG1sub = G1sub+αに設定する。このとき、設定後のG1subが、設定範囲内の最大値G1maxを超える場合は、ループゲイン制御部34は、探索完了信号を出力するようになされている。

【0101】

また、ループゲイン制御部34は、内部の伝送モード別ゲイン選択部71によりループゲインG1mainを伝送モード毎に保持、選択して出力するようになされている。そのため、伝送モード別ゲイン選択部は伝送モード毎の最適ループゲインを保持するためのレジスタを、伝送モードの最大数N(Nは、例えば、8)と同じ数だけ有する。これらのレジスタの出力値をそれぞれ、G1main0、G1main1、・・・G1mainN-1とする。

【0102】

受信信号riの伝送モード、各伝送モードにおいて採用される変調方式、その伝送モードに割り当てられた変調スロットは、誤り訂正復号器91から供給されるTMCCにより特定される。

【0103】

伝送モード番号生成器92は、入力されるフレームスタートフラグを基点に受信シンボルをカウントし、受信シンボルのカウント値に基づいて、現在受信されたシンボルがどの変調スロットに属するかを特定する。そして、伝送モード番号生成器92は、TMCCから取得された各伝送モードに割り当てられた変調スロットを表す情報に基づいて、現在受信されたシンボルの伝送モードを識別する番号(伝送モード番号と称する)TMを特定して、これをループゲイン制御部34に出力する。

【0104】

例えば、n個の伝送モードが多重された伝送方式を受信している場合、伝送モード番号TMは0、1、・・・n−1となる。

【0105】

ゲイン制御シーケンサ72は、最適なループゲインを探索すべき伝送モード番号TMtargetを保持し、TM=TMtargetとなるシンボル受信時のみPLL制御誤差比較部33と伝送モード別ゲイン選択部71を動作させる。ゲイン制御シーケンサ72は、TM=TMtargetとなるシンボルの受信期間においてHighとなる更新EN(イネーブル)をPLL制御誤差比較部33と伝送モード別ゲイン選択部71に出力するようになされている。

【0106】

更新ENがHighとなっている場合、PLL制御誤差比較部33は、上述した処理を行うようになされている。また、更新ENがHighとなっている場合、ループゲインG1mainを、ループゲインG1subによって置き換えるとき、伝送モード別ゲイン選択部71内の更新フラグ生成部により、当該伝送モード番号TMに対応するループゲインレジスタへの書き込みフラグが出力されるようになされている。

【0107】

図5に示す周波数・位相同期回路が起動された場合、まず、TMtarget=0として最適なループゲインを探索すべき伝送モード番号は初期値に設定される。次いで、主PLL回路31−1と副PLL回路31−2のループゲインの初期値が設定されるようになされている。

【0108】

主PLL回路31−1と副PLL回路31−2のループゲインの初期化が済んだ後、ループゲイン制御部34からPLL制御誤差比較部33に初期化フラグが出力されるようになされている。

【0109】

ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、それまでの制御誤差値比較結果及びタイマ64をリセットした後に、上述したように制御誤差値vmain,i,vsub,iを算出し、比較器63において、この制御誤差値の大小比較を開始する。

【0110】

PLL制御誤差比較部33のタイマ64はリセット後にタイムカウントを開始し、制御誤差値算出に必要な時間に達したところで、ループゲイン制御部34に対し比較完了通知を出力すると同時に、比較器63に対して比較結果出力命令を出力するようになされている。これにより、比較器63からループゲイン制御部34に対して制御誤差比較結果が出力されることになる。

【0111】

ループゲイン制御部34は、制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。この際、上述したように、ループゲインG1mainを、ループゲインG1subによって置き換えられる場合、ゲイン制御シーケンサ72からループゲインG1subが伝送モード別ゲイン選択部71に供給されるようになされている。

【0112】

伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

【0113】

また、伝送モード別ゲイン選択部71は、伝送モード番号生成器92から供給される伝送モード番号TMに対応するループゲインをG1main0、G1main1、・・・G1mainN-1から選択して出力し、ループフィルタ43−1のループゲインとして供給するようになされている。

【0114】

PLL制御誤差比較部33からの比較完了通知を受け取るまでの間に、ゲイン制御シーケンサ72から探索完了信号が出力された場合、全伝送モードの最適ゲインの探索が一巡したかどうか確認するためTMtargetの値がn−1と等しいか否かが判定される。TMtargetの値がn−1と等しくない場合、次の伝送モードの最適ゲインを探索するよう、TMtargetの値が1だけインクリメントされるとともに、主PLL回路31−1と副PLL回路31−2のループゲインは再び初期化される。

【0115】

このように、TMtargetの値0乃至n−1のそれぞれについて最適なループゲインが探索されていくことになる。このようにすることで、変調方式の異なる各伝送モードのそれぞれについて最適なループゲインを設定することが可能となる。

【0116】

また、PLL制御誤差比較部33からの比較完了通知を受け取るまでの間に、ゲイン制御シーケンサ72から探索完了信号が出力された場合、TMtargetの値がn−1と等しいとき、TMtargetの値が再度0に設定されるようにしてもよい。すなわち、TMtargetの値0乃至n−1のそれぞれについて一度最適なループゲインが探索された後、再びTMtargetの値0乃至n−1のそれぞれについて最適なループゲインが探索されるようにしてもよい。

【0117】

こうすることで、例えば、伝送チャネルの伝送特性に時間変動が存在する場合においても常に最適なループゲインを探索して利用し続けることが可能となる。

【0118】

次に、図6のフローチャートを参照して、図5の周波数・位相同期回路によるループゲイン制御処理について説明する。

【0119】

ステップS11において、ゲイン制御シーケンサ72は、変数TMtargetを初期値である0に設定する。

【0120】

ステップS12において、ゲイン制御シーケンサ72は、伝送モード別ゲイン選択部71内のループゲインレジスタであって、変数TMtargetに対応するループゲインレジスタの初期値を設定する。ここでは、当該ループゲインレジスタの設定値がG1main_newとして表わされており、初期値はG1initとされている。なお、設定値G1main_newは、ループフィルタ43−1のループゲインG1mainとして用いられることになる。

【0121】

また、ステップS12において、ゲイン制御シーケンサ72は、ループフィルタ43−2のループゲインG1subの初期値を設定する。ループゲインG1subの初期値は、ループゲインの最小値とされ、ここではG1minとされている。なお、設定値G1subは、ループフィルタ43−2のループゲインG1subとして用いられることになる。

【0122】

ループゲインの初期設定を行った後、ステップS13において、ループゲイン制御部34は、PLL制御誤差比較部33に対して初期化フラグを出力する。

【0123】

これにより、初期化フラグを受信したPLL制御誤差比較部33においては、それまでの制御誤差値の比較結果と内部タイマの計測値がリセットされることになる。

【0124】

また、PLL制御誤差比較部33の主PLL制御誤差検出器61においては、主PLL回路31−1により出力された主PLL中間信号に基づいて制御誤差値vmainが算出される。副PLL制御誤差検出器62においては、副PLL回路31−2により出力された副PLL中間信号に基づいて制御誤差値vsubが算出される。

【0125】

タイマ64においては、リセット後にタイムカウントが開始され、制御誤差値vmain、vsubの算出に必要な時間が経過したとき、ループゲイン制御部34に対して比較完了通知が出力され、それと同時に、比較器63に対して比較結果出力命令が出力される。比較結果出力命令が供給されることに応じて、比較器63からループゲイン制御部34に対して、制御誤差値vmainと、制御誤差値vsubとの大小の比較結果が出力される。

【0126】

ステップS14において、ゲイン制御シーケンサ72は、タイマ64から出力される比較完了通知を検出したか否かを判定し、まだ、比較完了通知を検出していないと判定された場合、処理は、ステップS20に進む。

【0127】

ステップS20では、探索完了信号が出力されたか否かが判定され、まだ、出力されていないと判定された場合、処理は、ステップS21に進み、例えば、タイマ64からの比較完了通知を検出するポーリングを一定の時間間隔で行い、待機する。その後、処理は、ステップS14に戻る。

【0128】

ステップS14において、比較完了通知を検出したと判定された場合、処理は、ステップS15に進む。

【0129】

ステップS15において、ゲイン制御シーケンサ72は、比較器63から供給された比較結果に基づいて、vmain>vsubであるか否かを判定する。

【0130】

vmain>vsubであるとステップS15において判定した場合、ステップS16において、ゲイン制御シーケンサ72は、ループゲインG1main_newを、ループフィルタ43−2のループゲインとしていま設定しているG1subに置き換える。このとき、ゲイン制御シーケンサ72から伝送モード別ゲイン選択部71内の更新フラグ生成部に所定の信号が出力され、更新フラグ生成部により、現在の伝送モード番号TMに対応するループゲインレジスタへの書き込みフラグが出力される。

【0131】

一方、vmain>vsubではなく、vmain≦vsubであるとステップS15において判定された場合、ステップS16の処理はスキップされる。

【0132】

ステップS17において、ゲイン制御シーケンサ72は、ループゲインG1subとしてG1sub+αを設定して更新する。ここでαは、ループゲインG1(G1main、またはG1sub)を量子化した最小ステップに相当するゲイン量である。

【0133】

ステップS18において、ゲイン制御シーケンサ72は、ステップS17の処理により更新された後のループゲインG1subが、設定範囲内の最大値G1maxを超えるか否かを判定する。

【0134】

ステップS18において、ループゲインG1subが、最大値G1maxを超えたと判定された場合、処理は、ステップS19に進み、ゲイン制御シーケンサ72は、探索完了信号を出力する。

【0135】

ステップS18において、ループゲインG1subが、最大値G1maxを超えていないと判定された場合、ステップS19の処理はスキップされる。

【0136】

ステップS18において、ループゲインG1subが、最大値G1maxを超えていないと判定された場合、または、ステップS19の処理の後、処理は、ステップS13に戻る。

【0137】

ステップS19で探索完了信号が出力された場合、その後のステップS20の処理では、探索完了信号が出力されたと判定されるので、処理は、ステップS22に進む。

【0138】

ステップS22において、ゲイン制御シーケンサ72は、変数TMtargetの値がn−1と等しいか否かを判定し、変数TMtargetの値がn−1と等しくないと判定された場合、処理は、ステップS23に進む。ステップS23において、ゲイン制御シーケンサ72は、変数TMtargetの値を1だけインクリメントする。その後、処理は、ステップS12に戻る。すなわち、次の伝送モード番号において最適となるループゲインの探索が行われることになる。

【0139】

一方、ステップS22において、変数TMtargetの値がn−1と等しいと判定された場合、処理は、ステップS11に戻る。すなわち、全ての伝送モード番号について最適なループゲインが探索された後、あらためてTMtargetの値0乃至n−1のそれぞれについて最適なループゲインが探索される。なお、2回目以降の探索においては、ステップS12の処理において、G1main_newを初期化する必要はない。

【0140】

なお、ステップS22において、変数TMtargetの値がn−1と等しいと判定された場合、処理が終了されるようにしてもよい。

【0141】

このようにして、ループゲイン制御処理が実行される。このように、本発明によれば、受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができる。

【0142】

以上においては、周波数・位相同期回路において、検出された位相誤差に対する直接の乗算に用いられるループゲインG1として最適なループゲインを探索する例について説明したが、ループゲインG1を用いた乗算後の位相誤差に対する乗算に用いられるループゲインG2が探索されるようにしてもよい。

【0143】

また、ループゲインG1とループゲインG2の両方が探索されるようにしてもよい。

【0144】

図7は、本発明の周波数・位相同期回路を適用した受信システムの第1実施の形態の構成例を示すブロック図である。

【0145】

図7の受信システムは、取得部101、伝送路復号処理部102、および情報源復号処理部103から構成される。

【0146】

取得部101は、地上デジタル放送、衛星デジタル放送、CATV網、インターネットその他のネットワーク等の図示せぬ伝送路を介して信号を取得し、伝送路復号処理部102に供給する。

【0147】

伝送路復号処理部102は、取得部101が伝送路を介して取得した信号に対して、同期検波と誤り訂正を含む伝送路復号処理を施し、その結果得られる信号を情報源復号処理部103に供給する。すなわち、伝送路復号処理部102には、図5に示される周波数・位相同期回路の構成が含まれており、その周波数・位相同期回路において、上述した同期検波が行われる。

【0148】

情報源復号処理部103は、伝送路復号処理が施された信号に対して、圧縮された情報を元の情報に伸張し、送信対象のデータを取得する処理を含む情報源復号処理を施す。

【0149】

すなわち、取得部101が伝送路を介して取得した信号には、画像や音声等のデータ量を少なくするために、情報を圧縮する圧縮符号化が施されていることがある。その場合、情報源復号処理部103は、伝送路復号処理が施された信号に対して、圧縮された情報を元の情報に伸張する処理等の情報源復号処理を施す。

【0150】

なお、取得部101が伝送路を介して取得した信号に圧縮符号化が施されていない場合、情報源復号処理部103では、圧縮された情報を元の情報に伸張する処理は行われない。ここで、伸張処理としては、例えば、MPEGデコード等がある。また、情報源復号処理には、伸張処理の他、デスクランブル等が含まれることがある。

【0151】

図7の受信システムは、例えば、デジタルテレビジョン放送を受信するテレビチューナ等に適用することができる。なお、取得部101、伝送路復号処理部102、および情報源復号処理部103は、それぞれ、1つの独立した装置(ハードウェア(IC(Integrated Circuit)等))、又はソフトウェアモジュール)として構成することが可能である。

【0152】

また、取得部101、伝送路復号処理部102、および、情報源復号処理部103については、それらの3つのセットを1つの独立した装置として構成することが可能である。取得部101と伝送路復号処理部102とのセットを1つの独立した装置として構成することも可能であるし、伝送路復号処理部102と情報源復号処理部103とのセットを1つの独立した装置として構成することも可能である。

【0153】

図8は、本発明の周波数・位相同期回路を適用した受信システムの第2実施の形態の構成例を示すブロック図である。

【0154】

図8に示す構成のうち、図7に示す構成と対応する構成については、同一の符号を付してあり、その説明は適宜省略する。

【0155】

図8の受信システムの構成は、取得部101、伝送路復号処理部102、および情報源復号処理部103を有する点で図7の構成と共通し、出力部111が新たに設けられている点で図7の構成と相違する。

【0156】

出力部111は、例えば、画像を表示する表示装置や音声を出力するスピーカであり、情報源復号処理部103から出力される信号としての画像や音声等を出力する。すなわち、出力部111は、画像を表示し、あるいは、音声を出力する。

【0157】

図8の受信システムは、例えば、デジタル放送としてのテレビジョン放送を受信するTVや、ラジオ放送を受信するラジオ受信機等に適用することができる。

【0158】

なお、取得部101において取得された信号に圧縮符号化が施されていない場合、伝送路復号処理部102が出力する信号が、直接、出力部111に供給される。

【0159】

図9は、本発明の周波数・位相同期回路を適用した受信システムの第3実施の形態の構成例を示すブロック図である。

【0160】

図9に示す構成のうち、図7に示す構成と対応する構成については同一の符号を付してあり、その説明は適宜省略する。

【0161】

図9の受信システムの構成は、取得部101、および伝送路復号処理部102を有する点で図7の構成と共通し、情報源復号処理部103が設けられておらず、記録部121が新たに設けられている点で図7の構成と相違する。

【0162】

記録部121は、伝送路復号処理部102が出力する信号(例えば、MPEGのTSのTSパケット)を、光ディスクや、ハードディスク(磁気ディスク)、フラッシュメモリ等の記録

(記憶)媒体に記録する(記憶させる)。

【0163】

以上のような図9の受信システムは、テレビジョン放送を録画するレコーダ機器等に適用することができる。

【0164】

なお、情報源復号処理部103を設け、情報源復号処理部103で情報源復号処理が施された後の信号、すなわち、デコードによって得られる画像や音声を記録部121で記録するようにしてもよい。

【0165】

なお、上述した一連の処理は、ハードウェアにより実行させることもできるし、ソフトウェアにより実行させることもできる。上述した一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータにネットワークや記録媒体からインストールされる。また、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば図10に示されるような汎用のパーソナルコンピュータ700などに、ネットワークや記録媒体からインストールされる。

【0166】

図10において、CPU(Central Processing Unit)701は、ROM(Read Only Memory)702に記憶されているプログラム、または記憶部708からRAM(Random Access Memory)703にロードされたプログラムに従って各種の処理を実行する。RAM703にはまた、CPU701が各種の処理を実行する上において必要なデータなども適宜記憶される。

【0167】

CPU701、ROM702、およびRAM703は、バス704を介して相互に接続されている。このバス704にはまた、入出力インタフェース705も接続されている。

【0168】

入出力インタフェース705には、キーボード、マウスなどよりなる入力部706、LCD(Liquid Crystal display)などよりなるディスプレイ、並びにスピーカなどよりなる出力部707が接続されている。また、入出力インタフェース705には、ハードディスクなどより構成される記憶部708、モデム、LANカードなどのネットワークインタフェースカードなどより構成される通信部709が接続されている。通信部709は、インターネットを含むネットワークを介しての通信処理を行う。

【0169】

入出力インタフェース705にはまた、必要に応じてドライブ710が接続され、磁気ディスク、光ディスク、光磁気ディスク、或いは半導体メモリなどのリムーバブルメディア711が適宜装着されている。そして、それらのリムーバブルメディアから読み出されたコンピュータプログラムが、必要に応じて記憶部708にインストールされる。

【0170】

上述した一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが、インターネットなどのネットワークや、リムーバブルメディア711などからなる記録媒体からインストールされる。

【0171】

なお、この記録媒体は、図10に示される、装置本体とは別に、ユーザにプログラムを配信するために配布される、プログラムが記録されている磁気ディスク(フロッピディスク(登録商標)を含む)、光ディスク(CD-ROM(Compact Disk-Read Only Memory),DVD(Digital Versatile Disk)を含む)、光磁気ディスク(MD(Mini-Disk)(登録商標)を含む)、もしくは半導体メモリなどよりなるリムーバブルメディア711により構成されるものだけでなく、装置本体に予め組み込まれた状態でユーザに配信される、プログラムが記録されているROM702や、記憶部708に含まれるハードディスクなどで構成されるものも含む。

【0172】

なお、本明細書において上述した一連の処理は、記載された順序に沿って時系列的に行われる処理はもちろん、必ずしも時系列的に処理されなくとも、並列的あるいは個別に実行される処理をも含むものである。

【0173】

また、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【符号の説明】

【0174】

31−1 主PLL回路, 31−2 副PLL回路, 32 乗算器, 33 PLL制御誤差比較部, 34 ループゲイン制御部, 41−1,41−2 乗算器, 42−1,42−2 位相誤差検出器, 43−1,43−2 ループフィルタ, 44−1,44−2 数値制御発振器, 51−1,51−2 乗算器, 52−1,52−2 乗算器, 53−1,53−2 積分器, 54−1,54−2 加算器, 61 主PLL制御誤差検出器, 62 副PLL制御誤差検出器, 63 比較器, 64 タイマ, 71 伝送モード別ゲイン選択部, 72 ゲイン制御シーケンサ, 91 誤り訂正復号部, 92 伝送モード番号生成器

【特許請求の範囲】

【請求項1】

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

同期回路。

【請求項2】

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差と前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差の大きさを比較する比較手段と、

指定された伝送モードの前記スロットに対応する受信信号が入力されている間、前記比較手段による比較が行われる都度、前記第2のPLL回路に含まれる第2のループフィルタのループゲインの値を所定の量だけ変更することで前記伝送モードにおける最適なループゲイン設定値を探索するループゲイン探索手段とをさらに備え、

前記保持手段は、

前記ループゲイン探索手段により前記第2のループフィルタのループゲインの値が所定の回数変更された場合、前記第1のループフィルタのループゲインとして設定されている値を、前記伝送モードにおける最適なループゲイン設定値として保持する

請求項1に記載の同期回路。

【請求項3】

前記受信信号のスロットのそれぞれの伝送モードを特定する情報である伝送モード番号を、前記受信信号を復号して得られる制御情報に基づいて特定する伝送モード番号特定手段をさらに備え、

前記ループゲイン探索手段は、

前記特定された伝送モード番号が前記指定された伝送モードに対応するものである場合、前記最適なループゲイン設定値を探索し、

前記保持手段は、

前記伝送モード番号特定手段により特定された伝送モード番号に対応づけて前記最適なループゲイン設定値を保持する

請求項2に記載の同期回路。

【請求項4】

前記第1のPLL回路は、

位相制御後の信号に残留する位相誤差を検出する第1の検出回路と、

前記第1の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第1のループフィルタと、

前記第1のループフィルタによるフィルタ処理の結果に応じて前記第1の位相制御信号を出力する第1の発振回路と、

前記第1の発振回路から出力された前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第1の検出回路に出力する前記第1の出力回路と

を備え、

前記第2のPLL回路は、

位相制御後の信号に残留する位相誤差を検出する第2の検出回路と、

前記第2の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第2のループフィルタと、

前記第2のループフィルタによるフィルタ処理の結果に応じて前記第2の位相制御信号を出力する第2の発振回路と、

前記第2の発振回路から出力された前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第2の検出回路に出力する前記第2の出力回路と

を備える

請求項1に記載の同期回路。

【請求項5】

前記第1のループフィルタは、

前記第1の検出回路により検出された位相誤差に第1のループゲインを乗算する第1の乗算回路と、

前記第1の乗算回路による乗算後の位相誤差に第2のループゲインを乗算する第2の乗算回路と、

前記第1の乗算回路による乗算後の位相誤差と、前記第2の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第1の発振回路に出力する第1の加算回路と

を備え、

前記第2のループフィルタは、

前記第2の検出回路により検出された位相誤差に第3のループゲインを乗算する第3の乗算回路と、

前記第3の乗算回路による乗算後の位相誤差に第4のループゲインを乗算する第4の乗算回路と、

前記第3の乗算回路による乗算後の位相誤差と、前記第4の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第2の発振回路に出力する第2の加算回路と

を備える

請求項4に記載の同期回路。

【請求項6】

前記制御回路は、前記第1のループゲインと前記第3のループゲインの値としてそれぞれ異なる値を設定する

請求項5に記載の同期回路。

【請求項7】

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を第1のPLL回路から出力し、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を第2のPLL回路から出力し、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第1の出力回路から出力し、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第2の出力回路から出力し、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を第1の検出回路において検出し、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を第2の検出回路において検出し、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定し、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持するステップを含み、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記伝送モード毎に前記ループゲイン設定値が保持される

同期方法。

【請求項8】

伝送路を介して送信されてきた信号を取得する取得手段と、

前記取得手段により取得された信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【請求項9】

伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、

前記伝送路復号処理手段による処理後の信号に対して、送信対象のデータを復号する処理を施す情報源復号処理手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【請求項10】

伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、

前記伝送路復号処理手段による処理後の信号に基づいて、画像または音声を出力する出力手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【請求項11】

伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、

前記伝送路復号処理手段による処理後の信号を記録する記録手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【請求項1】

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

同期回路。

【請求項2】

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差と前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差の大きさを比較する比較手段と、

指定された伝送モードの前記スロットに対応する受信信号が入力されている間、前記比較手段による比較が行われる都度、前記第2のPLL回路に含まれる第2のループフィルタのループゲインの値を所定の量だけ変更することで前記伝送モードにおける最適なループゲイン設定値を探索するループゲイン探索手段とをさらに備え、

前記保持手段は、

前記ループゲイン探索手段により前記第2のループフィルタのループゲインの値が所定の回数変更された場合、前記第1のループフィルタのループゲインとして設定されている値を、前記伝送モードにおける最適なループゲイン設定値として保持する

請求項1に記載の同期回路。

【請求項3】

前記受信信号のスロットのそれぞれの伝送モードを特定する情報である伝送モード番号を、前記受信信号を復号して得られる制御情報に基づいて特定する伝送モード番号特定手段をさらに備え、

前記ループゲイン探索手段は、

前記特定された伝送モード番号が前記指定された伝送モードに対応するものである場合、前記最適なループゲイン設定値を探索し、

前記保持手段は、

前記伝送モード番号特定手段により特定された伝送モード番号に対応づけて前記最適なループゲイン設定値を保持する

請求項2に記載の同期回路。

【請求項4】

前記第1のPLL回路は、

位相制御後の信号に残留する位相誤差を検出する第1の検出回路と、

前記第1の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第1のループフィルタと、

前記第1のループフィルタによるフィルタ処理の結果に応じて前記第1の位相制御信号を出力する第1の発振回路と、

前記第1の発振回路から出力された前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第1の検出回路に出力する前記第1の出力回路と

を備え、

前記第2のPLL回路は、

位相制御後の信号に残留する位相誤差を検出する第2の検出回路と、

前記第2の検出回路により検出された位相誤差に対してフィルタ処理を施す前記第2のループフィルタと、

前記第2のループフィルタによるフィルタ処理の結果に応じて前記第2の位相制御信号を出力する第2の発振回路と、

前記第2の発振回路から出力された前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を、位相誤差の検出対象の信号として前記第2の検出回路に出力する前記第2の出力回路と

を備える

請求項1に記載の同期回路。

【請求項5】

前記第1のループフィルタは、

前記第1の検出回路により検出された位相誤差に第1のループゲインを乗算する第1の乗算回路と、

前記第1の乗算回路による乗算後の位相誤差に第2のループゲインを乗算する第2の乗算回路と、

前記第1の乗算回路による乗算後の位相誤差と、前記第2の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第1の発振回路に出力する第1の加算回路と

を備え、

前記第2のループフィルタは、

前記第2の検出回路により検出された位相誤差に第3のループゲインを乗算する第3の乗算回路と、

前記第3の乗算回路による乗算後の位相誤差に第4のループゲインを乗算する第4の乗算回路と、

前記第3の乗算回路による乗算後の位相誤差と、前記第4の乗算回路による乗算後の位相誤差の積分結果とを加算し、前記第2の発振回路に出力する第2の加算回路と

を備える

請求項4に記載の同期回路。

【請求項6】

前記制御回路は、前記第1のループゲインと前記第3のループゲインの値としてそれぞれ異なる値を設定する

請求項5に記載の同期回路。

【請求項7】

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を第1のPLL回路から出力し、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を第2のPLL回路から出力し、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第1の出力回路から出力し、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を第2の出力回路から出力し、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を第1の検出回路において検出し、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を第2の検出回路において検出し、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定し、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持するステップを含み、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記伝送モード毎に前記ループゲイン設定値が保持される

同期方法。

【請求項8】

伝送路を介して送信されてきた信号を取得する取得手段と、

前記取得手段により取得された信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【請求項9】

伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、

前記伝送路復号処理手段による処理後の信号に対して、送信対象のデータを復号する処理を施す情報源復号処理手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【請求項10】

伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、

前記伝送路復号処理手段による処理後の信号に基づいて、画像または音声を出力する出力手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【請求項11】

伝送路を介して取得した信号に対して同期検波処理を含む処理を行う伝送路復号処理手段と、

前記伝送路復号処理手段による処理後の信号を記録する記録手段と

を備え、

前記伝送路復号処理手段は、

入力された受信信号に基づいて、前記受信信号の位相の制御量を表す第1の位相制御信号を出力する第1のPLL回路と、

前記第1のPLL回路に入力される前記受信信号と同じ信号が入力され、前記受信信号の位相の制御量を表す第2の位相制御信号を出力する第2のPLL回路と、

前記第1の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第1の出力回路と、

前記第2の位相制御信号に基づいて前記受信信号の位相を制御し、位相制御後の信号を出力する第2の出力回路と、

前記第1の出力回路から出力された位相制御後の信号に基づいて、前記第1のPLL回路における位相制御誤差を検出する第1の検出回路と、

前記第2の出力回路から出力された位相制御後の信号に基づいて、前記第2のPLL回路における位相制御誤差を検出する第2の検出回路と、

前記第1の検出回路により検出された前記第1のPLL回路における位相制御誤差の方が、前記第2の検出回路により検出された前記第2のPLL回路における位相制御誤差より大きい場合、前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして、前記第2のPLL回路に含まれる第2のループフィルタのループゲインと同じ値を設定する制御回路と、

前記第1のPLL回路に含まれる第1のループフィルタのループゲインとして設定されたループゲイン設定値を保持する保持手段とを備え、

前記受信信号は、異なる変調方式に対応する複数の伝送モードで伝送される複数のスロットからなるフレーム単位に構成され、

前記保持手段は、前記伝送モード毎に前記ループゲイン設定値を保持する

受信システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−75028(P2012−75028A)

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願番号】特願2010−219644(P2010−219644)

【出願日】平成22年9月29日(2010.9.29)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願日】平成22年9月29日(2010.9.29)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]