向上した熱散逸能力を有する3D集積電子デバイス構造

【課題】向上した熱散逸能力を有するマイクロ電子デバイス構造を提供する。

【解決手段】構造は、基板110にフリップチップ接合される三次元(3D)集積チップアセンブリ105を含む。チップアセンブリは、その上に配置される能動素子144を含むデバイス基板132を含む。キャップ層114は、デバイス基板132に物理的に接合され、能動素子144の周囲の気密シール148を少なくとも部分的に画定する。マイクロ電子デバイス構造は、それを通る複数の熱散逸経路を提供し、その中で生成される熱を散逸させる。

【解決手段】構造は、基板110にフリップチップ接合される三次元(3D)集積チップアセンブリ105を含む。チップアセンブリは、その上に配置される能動素子144を含むデバイス基板132を含む。キャップ層114は、デバイス基板132に物理的に接合され、能動素子144の周囲の気密シール148を少なくとも部分的に画定する。マイクロ電子デバイス構造は、それを通る複数の熱散逸経路を提供し、その中で生成される熱を散逸させる。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書において提示する実施形態は、マイクロ電子デバイス構造に関し、より詳細には、向上した熱散逸能力を有する三次元(3D)マイクロ電子集積回路(IC)チップ構造に関する。

【背景技術】

【0002】

微小電気機械システム(MEMS)は、サイズが1マイクロメートル(1ミクロン)未満から約1mm以上に及び得る、マイクロスイッチのような小型デバイスである。3D集積回路は一般的に、垂直および水平の両方において集積される積層構成にある2層以上の電子的構成要素を含む。これらのデバイスは一般的に、長期間にわたって動作するために制御環境を必要とする。熱の散逸は任意の高出力電子機器または電気的用途において主要な課題であり、高出力の微小電気機械システムすなわちMEMSデバイスにおいて非常に重要である。TSVと称される基板貫通ビアが、メモリチップのようなチップのスタックにおいて、他の機能の中でもチップ間の熱経路を提供する伝導体として利用される。熱を散逸させる追加の手段が集積される場合がある。

【0003】

ほとんどのMEMSデバイスはワイヤボンディングを使用して相互接続される。しかしながら、高性能MEMS用途では、ワイヤボンディングによってデバイスの性能が著しく制限されることになる可能性がある。ワイヤボンディングに付随する制限は、以下の、ワイヤの電流処理能力、および、短い電流サージの処理に特に影響を与え得る不十分な熱経路を含むが、これらには限定されない要因に関連する。他の場合では、MEMSデバイスはリボンボンディングを使用して相互接続される場合があるが、これにはデバイスの性能に同様の制限がある。

【0004】

熱散逸が不十分であることに起因する性能劣化に加えて、湿気、粒子またはガスのような汚染物質がデバイスを取り巻く環境内に導入されることによって、金属接点の固着、汚染、または干渉が引き起こされる可能性があり、これによってデバイスの故障がもたらされる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第7897503号明細書

【発明の概要】

【0006】

従って、通電能力が向上したより信頼性の高い高性能デバイスをもたらす、熱散逸経路の改善のような、改善された熱的管理を含む改善されたマイクロ電子チップ構造が望ましい場合がある。加えて、これは、能動素子に対する汚染からの保護を提供することができる。

【0007】

原出願の発明の範囲に一致する特定の態様を下記に記載する。これらの態様は、本発明がとり得る特定の形態の簡単な概要を読者に提供するためにのみ提示されること、および、これらの態様は本発明の範囲を限定するようには意図されていないことが理解されるべきである。事実、本発明は、下記に記載されていない場合があるさまざまな態様を包含することができる。

【0008】

特定の態様によれば、三次元(3D)集積チップアセンブリおよび基板を含む装置が開示され、三次元(3D)集積チップアセンブリは基板にフリップチップ接合され、複数の熱散逸経路が三次元(3D)集積チップアセンブリを通じて延在し、その中で生成される熱を散逸させる。チップアセンブリは、デバイス基板と、デバイス基板上に配置される1つまたは複数の熱生成要素を備える能動素子と、デバイス基板に物理的に接合されるキャップ層と、能動素子の周囲に形成される気密シールとを含み、気密シールは少なくとも部分的に、デバイス基板およびキャップ層によって画定される。

【0009】

他の実施形態によれば、三次元(3D)集積チップアセンブリと、基板と、熱伝導材料(TIM)を介して三次元(3D)集積チップアセンブリに近接して配置されるヒートスプレッダとを含む装置が開示される。三次元(3D)集積チップアセンブリは、基板にフリップチップ接合される。装置は、装置内で生成される熱を散逸させるための、三次元(3D)集積チップアセンブリを通る複数の熱散逸経路を提供する。チップアセンブリは、デバイス基板と、デバイス基板上に配置される1つまたは複数の集積回路を備える能動素子と、デバイス基板に物理的に接合され、半導体材料を含むキャップ層と、能動素子の周囲に形成される気密シールとを含み、気密シールは少なくとも部分的に、デバイス基板およびキャップ層によって画定される。

【0010】

さらなる実施形態によれば、キャップ層と、少なくとも部分的にキャップ層によって画定される気密シールと、基板とを含むMEMSデバイスを含む装置が開示される。MEMSデバイスは、基板にフリップチップ接合されるように構成される。

【0011】

さらなる実施形態によれば、装置内の熱を散逸させる方法であって、三次元(3D)集積チップアセンブリを提供することを含む、方法が開示される。チップアセンブリを提供する方法は、第1の主面および第2の主面を有するデバイス基板を提供することと、デバイス基板上に、1つまたは複数の集積回路を備える能動素子を配置することと、デバイス基板にキャップ層を接合することと、能動素子の周囲に気密シールを形成することと、複数の入出力接続部を含む基板を提供することとを含む。デバイス基板は、第1の主面および第2の主面のうちの少なくとも一方の上に複数の入出力接続部を含む。キャップ層は、第1の主面および第2の主面を有し、第1の主面および第2の主面のうちの少なくとも一方の上に複数の入出力接点を含む。気密シールは少なくとも部分的に、デバイス基板およびキャップ層によって画定される。方法は、装置を形成するために三次元(3D)集積チップアセンブリの基板へのフリップチップ接合をさらに提供し、装置は三次元(3D)集積チップアセンブリを通る複数の熱散逸経路を提供し、装置内で生成される熱を散逸させる。

【0012】

本発明のさまざまな態様に関連して上記の特徴のさまざまな改良が存在する。さらなる特徴も同様にこれらのさまざまな態様に組み込まれてもよい。これらの改良および追加の特徴は個別にまたは何らかの組み合わせにおいて存在してもよい。例えば、例示される実施形態のうちの1つまたは複数に関連して下記に論じられるさまざまな特徴が、単独でまたは何らかの組み合わせにおいて本発明の上記の態様のいずれかに組み込まれてもよい。ここでも、上記で提示されている簡単な概要は、特許請求される主題を限定することなく、読者に本発明の特定の態様およびコンテキストを周知させることのみを意図したものである。

【0013】

アセンブリの部品は部分的には一方の方向において、かつ部分的にはもう一方の方向において処理されるため、「上面」および「底面」という用語はここでは使用されない。代わりに、「第1の表面」および「第2の表面」という用語が使用され、それによって、完成したデバイス構造において第1の表面のすべてが最終的に同じ方向に面し、完成したデバイス構造においてすべての第2の表面が同じ方向に面する。

【図面の簡単な説明】

【0014】

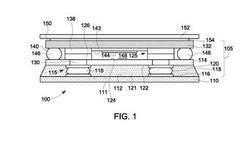

【図1】一実施形態による、熱散逸能力が向上した三次元集積電子アセンブリを含むデバイス構造の断面図である。

【図2】一実施形態による、熱散逸経路を示す、図1のデバイス構造の断面図である。

【図3】別の実施形態による、熱散逸能力が向上した三次元集積電子アセンブリを含むデバイス構造の断面図である。

【図4】さらに別の実施形態による、熱散逸能力が向上した三次元集積電子アセンブリを含むデバイス構造の断面図である。

【図5】一実施形態によるデバイス構造における、過渡電流立ち上がり状態における熱散逸を比較したグラフである。

【発明を実施するための形態】

【0015】

1つまたは複数の具体的な実施形態を下記に説明する。これらの実施形態の簡潔な記載を提供するために、実際の実施態様のすべての特徴が本明細書に記載されているとは限らない場合がある。工学的または設計プロジェクトにおけるものとしての、任意のこのような実際の実施態様の開発において、開発者の特定の目標を達成するために、システム関連およびビジネス関連の制約の順守のような、多数の実施態様特有の決定が為されなければならず、これは実施形態ごとに変わり得ることが認識されるべきである。その上、このような開発努力は複雑かつ時間のかかるものであり得るが、それにもかかわらず、本開示の利益を得る当業者にとっては日常的な設計、製造および生産の作業であろうことが認識されるべきである。

【0016】

革新的な3D集積マイクロ電子チップアセンブリ、特に、熱的管理を改善する手段を含む微小電気機械システム(MEMS)デバイスが開示される。3D集積デバイスアセンブリは、これはデバイス構造内で生成された熱を効率的に熱散逸させ、相互接続構造における電気抵抗を低減しながら、向上した通電能力を提供するのに役立つ、集積された層と、並列接続された相互接続部とを含む。

【0017】

図面は、熱散逸を向上させることが可能な3D集積チップアセンブリを含む、マイクロ電子デバイス、特にMEMSデバイスの例示的な構造を示す。ここで図面を、特に図1を参照すると、同様の参照符号はいくつかの図全体を通じて同様の要素を指すが、熱散逸能力が向上した3D集積チップアセンブリを採用するデバイス構造の一例の実施形態が断面図で示されている。全体的に100で示されるこのデバイス構造は、第1の主面111および第2の主面112を有する基板110に載置される3D集積チップアセンブリ105を含む。3D集積チップアセンブリ105は概して、第1の主面122および第2の主面124を有するキャップ層114と、第1の主面140および第2の主面150を有するデバイス基板132とを備える。デバイス構造100の製造中、3D集積チップアセンブリ105は基板110の第2の主面112に載置される。デバイス構造100のこの特定の実施形態において、キャップ層114は、本明細書においてはフリップチップバンプ接合とも称される、高い通電能力を可能にする複数のマイクロバンプ接続部115を利用して第1の主面122を介して基板110に載置される。デバイス基板132は、標準的な金属相互接続(まもなく説明する)によってデバイス基板132の第1の主面140を介して、キャップ層114の第2の主面124上に載置される。ヒートスプレッダ152が、熱伝導材料(TIM)154を介してデバイス基板132の第2の主面150上に配置されることができる。基板110、キャップ層114、デバイス基板132、複数の層の間の相互接続部、熱伝導材料134およびヒートスプレッダ136を含む積層される要素が、組み合わさってデバイス構造100を形成する。

【0018】

この特定の実施形態では、電気相互接続のための基板110は当該技術分野において既知のプリント回路基板(PCB)であってもよい。しかしながら、代替的な実施形態における基板材料は、シリコン、炭化ケイ素、ガリウムヒ素などのような金属酸化膜半導体(MOS)ベースの層のような能動素子層を含んでもよく、または能動層を考慮しない場合には、研磨された金属、柔軟なプラスチック、ポリイミド、半導体材料、またはガラスもしくは水晶材などの絶縁体のような任意の平坦な支持材料から成ってもよいことを当業者は認識しよう。

【0019】

この特定の実施形態では、デバイス基板132は当該技術分野において既知のシリコンから成ってもよい。しかしながら、代替的な実施形態におけるデバイス基板材料は、シリコン、炭化ケイ素、ガリウムヒ素、窒化ガリウム、アルミナ、サファイア、チタン、鋼鉄、プラスチック、ポリイミド、ガラス、石英などのような、半導体およびMEMSベースの製造工程およびパッケージング工程に適合する任意の平坦な支持材料を含んでもよいことを当業者は認識しよう。

【0020】

基板110の第2の主面112は、複数の並列に構成されるはんだバンプ118を介して、キャップ層114の第1の主面122上に配置されるとともに基板110の入出力接点116に整合するように構成される複数の第1の入出力接点120にはんだ付けされて示されている複数の入出力接点116を含む。3D集積チップアセンブリ105、より詳細にはキャップ層114が取り付けられることになる、キャップ層114の入出力接点(まもなく説明する)に整合するようにパターニングされ配置される基板110層の複数の入出力接点116を製造するのに、標準的なウェハプロセスが使用される。複数の入出力接点116は、1つまたは複数の金属層、例えば、銅、ニッケルおよび/または金の層として構築され得る。入出力接点スタックにおける金属層の実際の組成は基板110の材料によって決まることになる。一実施形態では、デバイス構造132およびキャップ層114は、最初にともに接合されて、本明細書において「MEMS」または「デバイスチップ」とも称される3D集積チップアセンブリ105を形成し、これはその後はんだバンプ118を介して基板110に取り付けられる。好ましい実施形態では、多くの並列バンプが使用されて、高電流キャリアならびに熱シャントとして役割を果たす。並列マイクロバンプ相互接続は、パッケージサイズ、IOカウントなどに応じて、IO当たり2〜50またはそれ以上の数に及ぶことができる。

【0021】

当該技術分野において既知であるアンダーフィル材料121が、基板110とキャップ層114との間に配置されるものとして示されている。アンダーフィル材料121は、基板110とキャップ層114との間の空間を埋めるために使用することができ、それによって、マイクロバンプ接続部115、より詳細には複数の入出力接続部116、複数の第1の入出力接続部120およびはんだバンプ118が固定されたままになる。基板110とキャップ層114との間で膨張率が異なる場合、それらは、デバイス構造100が動作中に生成される熱に起因して加熱または冷却されるときに膨張または収縮する量が異なる場合がある。デバイス構造100のこの加熱または冷却は、デバイス構造100のさまざまな層の間に相対運動をもたらす場合がある。アンダーフィル材料121を含むことが、基板110とキャップ層114との間で相互接続して安全でなくなることを防止するのに役立つ場合がある。

【0022】

キャップ層114は、第2の主面124上で、デバイス基板132上に形成される複数の入出力接点(まもなく説明する)と整合し、または他の様態で結合もしくは適合するように構成される、複数の第2の入出力接点126を支持するようにさらに構成される。キャップ層114の下側主面122から第2の主面124への相互接続は、例えば、ビア形成のためのレーザ、高速反応性イオンエッチングなどを使用して構築される複数の基板貫通ビア130、より詳細には複数のシリコン貫通ビア(TSV)130を構築すること、およびビアメタライゼーションのための標準的なウェハプロセスを含むさまざまな手段によって達成することができる。

【0023】

図示されるように、複数の第1の入出力接点120は、複数のウェハ貫通ビア128を介して、キャップ層114の第2の主面124上に配置される複数の第2の入出力接点126に電気的に接続する。複数のウェハ貫通ビア128はキャップ層114から電気的に絶縁される。

【0024】

本明細書に記載されるデバイス100の1つの実施形態は、基板110がプリント回路基板(PCB)でない場合には、半導体材料からキャップ層114を製造すること、および、例えば、キャップ層114の材料を、このキャップ層が接続されることになる基板110に一致させることを含む。より具体的には、デバイス構造100を製造する1つの方法は、基板110によって採用される材料に一致する半導体材料、例えば、シリコンから成るキャップ層114を選択することである。これによって機械適応力、負担が最小限に抑えられ、その他の点では高信頼性パッケージおよび相互接続が提供され、均等な電気的相互接続性能ももたらされる。例として、デバイス構造100がシリコン基板110を含む場合、キャップ層114もシリコンから製造されてもよい。シリコンベースの集積回路デバイスが今日優勢を占めているため、本明細書において提供される説明はシリコンキャップ層114を論じているものであり得る。しかしながら、デバイス基板材料およびキャップ層材料は、シリコン、炭化ケイ素、ガリウムヒ素などを含む任意の半導体材料、または代替的には石英のような材料などを含み得ることを当業者は認識しよう。キャップ層114の製造に、ウェハ処理を使用してキャップ層114上に複数の第1の入出力接点120を作成することを含む、標準的なウェハプロセスを採用することができる。

【0025】

キャップ層114の材料が選択された後、複数のウェハ貫通ビア128が(例えば、キャップ層114を貫通するプラズマエッチング、穿孔、レーザ穿孔、化学エッチング、高速反応性イオンエッチング、レーザ切断などによって)作成され、任意選択的に、キャップ層114と後続の電気的相互接続とを電気的に絶縁するために絶縁され、金属化されてキャップ層114の第1の主面122からキャップ層114の第2の主面124までの電気的接続が形成される。

【0026】

上記のようなビア作成に続いて、金属化されたウェハ貫通ビア128を作成するために標準的なウェハプロセス(フォトリソグラフィ、湿式化学、物理気相成長(PVD)、電気めっきなど)を採用することができる。貫通ビア構築工程の1つの実施形態は、(応力を軽減するために)湿式化学を使用して、続いて、キャップ層114の表面および(ビアを充填することなく)ビアの壁面を部分的に被覆する絶縁層を確立するために酸化させ、キャップ層114からの必要な電気的絶縁を提供することである。次いで、シードメタルが堆積されてビア内に金属層が確立され、その後、ビアが金属、例えば、銅、ニッケル、金などによってめっきされる。フォトマスクが被着され、もしあれば、貫通ビアに対する回路(例えば、入出力)接点および相互接続部がパターニングされる。完成すると、図1に示されるようなキャップ層114が実現し、金属化された貫通ビアはキャップ層114の第1の主面122から第2の主面124まで延在する。

【0027】

貫通ビアの形成に続いて、複数の第1の入出力接点120の製造に加えて、キャップ層114が取り付けられることになる、デバイス基板132の入出力接点に整合するようにパターニングされ配置される、キャップ層114の複数の入出力接点126を製造するのに、標準的なウェハプロセスが使用される。反対側の、キャップ層114の第1の主面122上には例えば、複数の入出力接点120が形成される。複数の入出力接点120および126は、金属層、例えば、銅、ニッケルおよび/または金の層のスタックとして構築され得る。入出力接点スタックにおける金属層の実際の組成はキャップ層114の材料および使用される取り付け方法によって決まることになる。

【0028】

図1の実施形態では、キャップ層114内に形成される複数のウェハ貫通ビア128が、キャップ層114の第1の主面122上に配置されることになる複数の第1の入出力接点120およびキャップ層114の第2の主面124上に配置されることになる複数の第2の入出力接点126の下にまたは近接して位置合わせされる。複数の第2の入出力接点126は、1つの実施形態では、複数の入出力接点138またはキャップ層114が取り付けられることになるデバイス基板132のパッド構成に整合するようにパターニングされ、一方で複数の第1の入出力接点120は、同じくキャップ層114が接続されることになる基板110への接続を容易にするように構成される。1つの実施形態では、ウェハ貫通ビア128の直径は、ウェハ貫通ビア128の量およびデバイス基板132、複数の入出力接点138および複数の入出力接点116の位置によって決まる。高密度入出力構成のために、各ビア128の直径は、今日の技術を使用すれば10マイクロメートル(10ミクロン)以下にまで小さくすることができる。

【0029】

図示されるように、キャップ層114の第1の主面122上に配置される複数の第1の入出力接点120は、金属化されたビア128を介して、キャップ層114の第2の主面124上に配置される複数の第2の入出力接点126に電気的に接続する。

【0030】

デバイス基板132は、既に説明されたように、第1の主面140上に形成される複数の入出力接点138を含む。複数の入出力接点138は、熱圧着などを通じて、キャップ層114の第2の主面124上に配置されるとともにキャップ層114の入出力接点126に整合するように構成される複数の第2の入出力接点126にはんだ付けされて示されている。相互接続部125を形成するために図面全体を通じて2つの別個の層が描かれているが、任意の数の材料層を利用することができることが理解されるべきである。熱伝導性配線143が、能動素子の、デバイス基板132の第1の主面140への相互接続および熱の散逸(まもなく説明する)を提供する。「能動素子」という用語は、本明細書使用される場合、半導体集積回路(IC)、単純な抵抗器、音響(超音波)センサのようなセンサ、光(LCD、フォトダイオード、空間光変調器)デバイス、または任意の類似のタイプの熱生成デバイスのような、任意の熱生成要素を含んでもよい。示されている例示的な実施形態では、能動素子144は、微小電気機械システム(MEMS)回路、特にマイクロスケール継電器を含む。

【0031】

図1に示されているように、シールリング146は能動素子144の気密シーリングを提供する。シーリング146は、ガラスフリット、共晶金属組成物、高分子接着剤、熱圧着メタルボンドなどのような、任意の既知のシーリング材料から成ってもよい。ガラスフリットシールリング146を含む実施形態では、組み立て中、チクソペーストのようなガラスフリットリングがデバイス基板132またはキャップ層114のうちの一方の上にスクリーン印刷され、乾燥されることができる。例示的な実施形態では、フリットの厚さは5〜20マイクロメートル(5〜20ミクロン)の範囲内にある。印刷されたガラスフリットリングは、最終的には、個別の能動素子(複数の場合もあり)144に対する気密シール148を形成することになる。気密シール148を形成するために、ガラス粒子を溶融させるウェハボンディング工程が実行され、それによって、シールリング146および気密シール148が作成される。通常のガラスフリットリングのウェハ処理は、ガラスリフロー、および、真空下でかつウェハからウェハへの力が印加された状態で約400℃の接着温度を採用することができる。リフローされたガラスフリットのシーリング工程は、シールリング146が、キャップ層114の第2の主面124とデバイス基板132の第1の主面140との間で能動素子144を気密封止することを可能にする。動作中の機械的構成要素によって生成される運動に起因して、能動素子144は、外気、および、湿気、塵埃粒子などのような望ましくない粒子の影響を受けやすい。シールリング146および能動素子144の周囲の気密シール148は、これらの望ましくない汚染からの保護を提供することができる。

【0032】

デバイス基板132の第2の主面150は、任意選択のヒートスプレッダ152に、それらの間に配置される熱伝導材料(TIM)154を介して取り付けられてもよい。示されている実施形態では、能動素子144によって生成される熱は、ヒートスプレッダ152を通じて外部環境内に散逸させることができる。ヒートスプレッダ152およびTIM154を含むか否かは、構造100内に追加の熱散逸能力が必要か否かによって决まり得る。

【0033】

上記で論じられたように構築されるキャップ層114、能動素子144の気密シール、複数の並列相互接続およびデバイス構造100全体は、高出力マイクロ電子チップ構造、より詳細には高出力微小電気機械システム(MEMS)内の熱散逸に付随する問題のいくらかまたはすべてを軽減することができる。加えて、本明細書に記載されるように構築される3D集積チップアセンブリ105は、高精度の高容量装着機を用いて容易に選定および配置され、パッケージングのために基板110上に組み付けられることができる。

【0034】

ここで図2を参照すると、上記の記載に従って構築されるデバイス構造100が示されており、これは、一実施形態による複数の熱散逸経路156を描いたものである。既に述べたように、同様の参照符号はいくつかの図面全体を通じて同様の要素を指す。過渡電流状態の間、複数の熱散逸経路156は示されているように利用可能である。本明細書において開示されるような熱散逸経路156は、熱が最初にバルク基板を通じて流れ、次いでTIMを通じて、次いでヒートスプレッダへと流れることを必要とするヒートスプレッダと比較して、熱生成を電力線を介した散逸へと直接結び付ける。示されるように、動作中、デバイス基板100、より詳細には能動素子144によって生成される熱は、複数の熱散逸経路156を介して、特に、デバイス144からの熱を相互接続構造125へ、下ってはんだバンプフリップチップアセンブリ115へと導く、ウェハまたはキャップ表面上の熱伝導配線143に沿って散逸される。熱散逸経路156は、能動素子144からその金属相互接続部までの連続的な熱伝導金属経路を提供し、従って、熱散逸のための主要な経路としての役割を果たす。フリップチップ相互接続部115は、熱生成源、より詳細には能動素子144に、バルクシリコンなどを通じての熱散逸にもっぱら依拠するよりも良好に熱的に結合される各電気的接合部を通じて多くの熱散逸経路156を提供する。多くの並列のより短い電気路156を提供することに加えて、フリップチップ相互接続部115は、より短い散逸経路156を提供する。描かれているように、熱は、基110とキャップ層114との間に位置するフリップチップ接合部によって形成されるマイクロバンプ相互接続部115、および、キャップ層114とデバイス基板132との間に形成される金属相互接続部125によって散逸され得る。任意の追加の熱が、デバイス基板100内に含まれる場合にはヒートスプレッダ152を通じて散逸されてもよい。記載されている新規のフリップチップ手法は、より短い相互接続経路長を提供し、それによって、熱を散逸させるためにより好ましいものにする。このような短くかつ高度に並列化された熱経路は、ワイヤボンドおよびリボンボンディングのような他の相互接続方法にまさる重要な利点を供する。

【0035】

より高出力の熱散逸能力を採用するデバイス構造構成のさらなる例が図3および図4に描かれており、ここでも、同様の参照符号は図面全体を通じて同様の要素を指す。図3をより具体的に参照すると、基板110と、概してキャップ層114およびデバイス基板132を備える3D集積チップアセンブリ105とを含むデバイス基板の別の実施形態200が示されている。この特定の実施形態では、図1および図2に描かれている実施形態とは対照的に、デバイス基板132が3D集積チップアセンブリ105の下側部分内に配置されており、より詳細には、キャップ層114がデバイス基板132の第2の主面150上に配置されている。加えて、能動素子144が、熱伝導性配線143を介してデバイス基板132の第2の主面150上に位置付けられている。デバイス基板132は、その中に形成される複数のウェハ貫通ビア130と、その第1の主面140の上に配置される複数の第1の入出力接点120とをさらに含み、複数の第1の入出力接点120は、複数のウェハ貫通ビア130を通じて能動素子144に電気的に接続されている。図1および図2に示されている第1の実施形態のものと同様に構成されるフリップチップバンプ相互接続部が、基板110の第2の主面112と、デバイス基板132の第1の主面140との間に形成される。アンダーフィル材料121も提供されることができる。シールリング146は、デバイス基板132とキャップ層114との間に能動素子144に対する気密シール148を形成する。加えて、シールリング146は、デバイス基板132の第2の主面150とキャップ層114の第1の主面122との間に物理的接合を提供する。この特定の実施形態では、図1および図2に描かれている実施形態とは対照的に、ヒートスプレッダ152および熱伝導材料154は省かれている。最初に開示された実施形態と同様に、デバイス構造200、より詳細には能動素子144によって生成される熱は、同様に図2に示されている熱散逸経路に従って散逸される。3D集積チップアセンブリ105内のキャップ層114およびデバイス基板132の構成に関わりなく、熱伝導材料154およびヒートスプレッダ152を含むか否かは、依然として追加の熱散逸能力が必要であるか否かによって決まることが付加的に理解されるべきである。

【0036】

ここで図4を参照すると、概して図1および図2に描かれている実施形態と同様にスタック内に構成されている、基板110と、概してキャップ層114およびデバイス基板132を備える3D集積チップアセンブリ105とを含むデバイス構造のさらに別の実施形態300が示されている。この特定の実施形態では、図1および図2に描かれている実施形態とは対照的に、ヒートスプレッダ152および熱伝導材料154は省かれている。任意選択のヒートスプレッダ152が、熱伝導材料(TIM)154を介してキャップ層114の第1の主面124上に位置付けられている。この特定の実施形態ではシールリングが省かれており、能動素子144に対する気密シール148は、デバイス基板132と、キャップ層114と、キャップ層114およびデバイス基板132の間に形成される金属相互接続部125とによって形成される。より具体的には、キャップ層114の第2の主面124上に形成される複数の第2の入出力接点126、および、デバイス基板132の第1の主面140上に形成される複数の入出力接点138が、能動素子144の周囲の気密シール148を提供する。さらに別の代替の実施形態では、追加のシールを形成するために、キャップ層114およびデバイス基板132の間に形成される金属相互接続部125のセットと、ビア130と、キャップ層114および基板110の間に形成される相互接続部116、120およびバンプ118とを備える、追加の相互接続ビア構造が能動素子144の周囲に含まれることができる。

【0037】

既に開示された実施形態と同様に、デバイス構造300、より詳細には能動素子144によって生成される熱は、同様に図2に示されている熱散逸経路に従って散逸される。図4はキャップ層114が基板110に取り付けられることを可能にするように位置決められて構成されている3D集積チップアセンブリ105を含んでいるが、代替的な実施形態では、キャップ層114およびデバイス基板132は、デバイス基板132が基板110に取り付けられることを可能にするために、図3に記載および図示されているように、3D集積チップアセンブリ105内の構成に関して逆になってもよいことが理解されるべきである。3D集積チップアセンブリ105内のキャップ層114およびデバイス基板132の構成に関わりなく、熱伝導材料154およびヒートスプレッダ152を含むか否かは、依然として追加の熱散逸能力が必要であるか否かによって決まることが付加的に理解されるべきである。

【0038】

図5には、既知の相互接続/スタック構成および本明細書に記載される新規の相互接続/スタック構成を含む高出力マイクロ電子デバイス構造の実施形態の熱散逸を示すシミュレーション結果400が示されている。より具体的には、熱散逸は、フリップチップボード構成の熱散逸品質の向上を示す図5においてグラフで表されている。電流(A)がx軸402上に表されており、パッケージ内の(通常はMEMSビームにおける)最大温度および温度(K)がy軸403上に表されている。標準的なワイヤボンド/配線相互接続およびヒートスプレッダを含む、既知のマイクロ電子デバイス構造における一般的な熱散逸が線404に描かれている。示されているように、約30アンペアの電流において、ワイヤボンド/配線相互接続はパッケージされたデバイスの熱伝導性を限定しており、700Kを超えて示されているように温度を過剰に熱くしてしまっている。

【0039】

銅ストラップ相互接続およびヒートスプレッダを含む、既知のマイクロ電子デバイス構造の一般的な熱散逸が線406に描かれている。示されているように、約30アンペアの電流において、銅ストラップ相互接続を含む既知のデバイスにおける熱は、ワイヤボンド/配線相互接続を含む上記のデバイスよりも効率的に熱を散逸させることが可能であるが、デバイスが460Kを超える温度に留まるような熱散逸が可能であるに過ぎない。

【0040】

図1〜図4の上記の実施形態におけるもののような、キャップ層と、気密シールと、相互接続とを含むように構成されるマイクロ電子デバイス構造の一般的な熱散逸が線408および410において描かれている。線408において示されているように、約30アンペアの電流において、図1〜図4に描かれているもののような、キャップ層と、気密シールと、新規のフリップチップ相互接続と、ヒートスプレッダとを含む新規のデバイスは、ワイヤボンド/配線相互接続またはリボンベースの相互接続を含む上記の既知のデバイスよりも効率的に熱を散逸させることが可能である。線408において描かれているように、温度は効率的に散逸され、約30アンペアにおけるデバイスの温度は400K未満である。

【0041】

図4の上記の実施形態におけるもののような、キャップ層と、気密シールと、相互接続とを含むように構成されるマイクロ電子デバイス構造であって、ヒートスプレッダがデバイス構造内に組み込まれていない、マイクロ電子デバイス構造の一般的な熱散逸が線410において描かれている。線410において示されているように、約30アンペアの電流において、図1〜図4に描かれているもののような、キャップ層と、新規のフリップチップ相互接続とを含むが、ヒートスプレッダを含まない新規のデバイスは、線408におけるヒートスプレッダを組み込んだフリップチップの実施形態よりも熱を散逸させないが、依然として、ヒートスプレッダが利用されたワイヤボンド/配線相互接続または銅ストラップ相互接続を含む上記の既知のデバイスよりも効率的に熱を散逸させることが可能である。線410において描かれているように、この実施形態における温度は効率的に散逸され、約30アンペアにおけるデバイスの温度は450K未満である。

【0042】

上記の例から、本明細書において、微小電気機械システム(MEMS)デバイスのような高出力マイクロ電子デバイスにおける熱散逸を向上させるために採用されることができる新規の相互接続構造およびデバイス構造スタックまたはパッケージが提供されることを当業者は理解しよう。標標準的な化学、機械的処理などを使用して、このデバイスを、キャップ層、デバイス基板、複数の金属相互接続部および能動素子を備える3D集積チップアセンブリと、3D集積チップアセンブリおよび下層基板の間の複数のバンプ相互接続部と、能動素子の周囲でかつキャップ層およびデバイス基板の間にある気密シールとを含むように製造することによって、コストが低く、高性能で、収率の高いデバイス構造を得ることができる。さらに、本明細書において開示されるデバイス構造および技法は結果として、熱散逸能力の向上による熱的管理の改善、パッケージ統合の簡易化、および電気抵抗相互接続の低減を含むが、これらに限定されない利点をもたらすことができる。より薄い、壊れやすい集積回路チップおよびデバイスのための機械的および熱的管理システムも提供される。

【0043】

本発明はさまざまな変更および代替の形態の影響を受け得るが、具体的な実施形態が例として図面内に示されており、本明細書において詳細に記載されている。しかしながら、本発明は開示されている特定の形態に限定されるようには意図されていないことが理解されるべきである。そうではなく、本発明は、添付の特許請求の範囲によって定義される発明の趣旨および範囲内に入るすべての変更、均等物、および代替物を包含するものである。

【符号の説明】

【0044】

100 デバイスアセンブリ

105 3D集積チップアセンブリ

110 基板

111 110の第1の主面

112 110の第2の主面

114 キャップ層

115 マイクロバンプ接続部

116 複数の入出力接点

118 はんだバンプ

120 複数の第1の入出力接点

121 アンダーフィル材料

122 114の第1の主面

124 114の第2の主面

125 金属相互接続部

126 複数の第2の入出力接点

128 複数のウェハ貫通ビア

130 複数のシリコン貫通電極(TSV)

132 デバイス基板

134 熱伝導材料

136 ヒートスプレッダ

138 複数の入出力接点

140 132の第1の主面

141 熱伝導層

142 はんだバンプ

143 熱伝導性配線

144 能動素子

146 ガラスフリット

148 気密シール

150 132の第2の主面

152 ヒートスプレッダ

154 熱伝導材料

156 熱散逸経路

200 第2の実施形態

300 第3の実施形態

【技術分野】

【0001】

本明細書において提示する実施形態は、マイクロ電子デバイス構造に関し、より詳細には、向上した熱散逸能力を有する三次元(3D)マイクロ電子集積回路(IC)チップ構造に関する。

【背景技術】

【0002】

微小電気機械システム(MEMS)は、サイズが1マイクロメートル(1ミクロン)未満から約1mm以上に及び得る、マイクロスイッチのような小型デバイスである。3D集積回路は一般的に、垂直および水平の両方において集積される積層構成にある2層以上の電子的構成要素を含む。これらのデバイスは一般的に、長期間にわたって動作するために制御環境を必要とする。熱の散逸は任意の高出力電子機器または電気的用途において主要な課題であり、高出力の微小電気機械システムすなわちMEMSデバイスにおいて非常に重要である。TSVと称される基板貫通ビアが、メモリチップのようなチップのスタックにおいて、他の機能の中でもチップ間の熱経路を提供する伝導体として利用される。熱を散逸させる追加の手段が集積される場合がある。

【0003】

ほとんどのMEMSデバイスはワイヤボンディングを使用して相互接続される。しかしながら、高性能MEMS用途では、ワイヤボンディングによってデバイスの性能が著しく制限されることになる可能性がある。ワイヤボンディングに付随する制限は、以下の、ワイヤの電流処理能力、および、短い電流サージの処理に特に影響を与え得る不十分な熱経路を含むが、これらには限定されない要因に関連する。他の場合では、MEMSデバイスはリボンボンディングを使用して相互接続される場合があるが、これにはデバイスの性能に同様の制限がある。

【0004】

熱散逸が不十分であることに起因する性能劣化に加えて、湿気、粒子またはガスのような汚染物質がデバイスを取り巻く環境内に導入されることによって、金属接点の固着、汚染、または干渉が引き起こされる可能性があり、これによってデバイスの故障がもたらされる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第7897503号明細書

【発明の概要】

【0006】

従って、通電能力が向上したより信頼性の高い高性能デバイスをもたらす、熱散逸経路の改善のような、改善された熱的管理を含む改善されたマイクロ電子チップ構造が望ましい場合がある。加えて、これは、能動素子に対する汚染からの保護を提供することができる。

【0007】

原出願の発明の範囲に一致する特定の態様を下記に記載する。これらの態様は、本発明がとり得る特定の形態の簡単な概要を読者に提供するためにのみ提示されること、および、これらの態様は本発明の範囲を限定するようには意図されていないことが理解されるべきである。事実、本発明は、下記に記載されていない場合があるさまざまな態様を包含することができる。

【0008】

特定の態様によれば、三次元(3D)集積チップアセンブリおよび基板を含む装置が開示され、三次元(3D)集積チップアセンブリは基板にフリップチップ接合され、複数の熱散逸経路が三次元(3D)集積チップアセンブリを通じて延在し、その中で生成される熱を散逸させる。チップアセンブリは、デバイス基板と、デバイス基板上に配置される1つまたは複数の熱生成要素を備える能動素子と、デバイス基板に物理的に接合されるキャップ層と、能動素子の周囲に形成される気密シールとを含み、気密シールは少なくとも部分的に、デバイス基板およびキャップ層によって画定される。

【0009】

他の実施形態によれば、三次元(3D)集積チップアセンブリと、基板と、熱伝導材料(TIM)を介して三次元(3D)集積チップアセンブリに近接して配置されるヒートスプレッダとを含む装置が開示される。三次元(3D)集積チップアセンブリは、基板にフリップチップ接合される。装置は、装置内で生成される熱を散逸させるための、三次元(3D)集積チップアセンブリを通る複数の熱散逸経路を提供する。チップアセンブリは、デバイス基板と、デバイス基板上に配置される1つまたは複数の集積回路を備える能動素子と、デバイス基板に物理的に接合され、半導体材料を含むキャップ層と、能動素子の周囲に形成される気密シールとを含み、気密シールは少なくとも部分的に、デバイス基板およびキャップ層によって画定される。

【0010】

さらなる実施形態によれば、キャップ層と、少なくとも部分的にキャップ層によって画定される気密シールと、基板とを含むMEMSデバイスを含む装置が開示される。MEMSデバイスは、基板にフリップチップ接合されるように構成される。

【0011】

さらなる実施形態によれば、装置内の熱を散逸させる方法であって、三次元(3D)集積チップアセンブリを提供することを含む、方法が開示される。チップアセンブリを提供する方法は、第1の主面および第2の主面を有するデバイス基板を提供することと、デバイス基板上に、1つまたは複数の集積回路を備える能動素子を配置することと、デバイス基板にキャップ層を接合することと、能動素子の周囲に気密シールを形成することと、複数の入出力接続部を含む基板を提供することとを含む。デバイス基板は、第1の主面および第2の主面のうちの少なくとも一方の上に複数の入出力接続部を含む。キャップ層は、第1の主面および第2の主面を有し、第1の主面および第2の主面のうちの少なくとも一方の上に複数の入出力接点を含む。気密シールは少なくとも部分的に、デバイス基板およびキャップ層によって画定される。方法は、装置を形成するために三次元(3D)集積チップアセンブリの基板へのフリップチップ接合をさらに提供し、装置は三次元(3D)集積チップアセンブリを通る複数の熱散逸経路を提供し、装置内で生成される熱を散逸させる。

【0012】

本発明のさまざまな態様に関連して上記の特徴のさまざまな改良が存在する。さらなる特徴も同様にこれらのさまざまな態様に組み込まれてもよい。これらの改良および追加の特徴は個別にまたは何らかの組み合わせにおいて存在してもよい。例えば、例示される実施形態のうちの1つまたは複数に関連して下記に論じられるさまざまな特徴が、単独でまたは何らかの組み合わせにおいて本発明の上記の態様のいずれかに組み込まれてもよい。ここでも、上記で提示されている簡単な概要は、特許請求される主題を限定することなく、読者に本発明の特定の態様およびコンテキストを周知させることのみを意図したものである。

【0013】

アセンブリの部品は部分的には一方の方向において、かつ部分的にはもう一方の方向において処理されるため、「上面」および「底面」という用語はここでは使用されない。代わりに、「第1の表面」および「第2の表面」という用語が使用され、それによって、完成したデバイス構造において第1の表面のすべてが最終的に同じ方向に面し、完成したデバイス構造においてすべての第2の表面が同じ方向に面する。

【図面の簡単な説明】

【0014】

【図1】一実施形態による、熱散逸能力が向上した三次元集積電子アセンブリを含むデバイス構造の断面図である。

【図2】一実施形態による、熱散逸経路を示す、図1のデバイス構造の断面図である。

【図3】別の実施形態による、熱散逸能力が向上した三次元集積電子アセンブリを含むデバイス構造の断面図である。

【図4】さらに別の実施形態による、熱散逸能力が向上した三次元集積電子アセンブリを含むデバイス構造の断面図である。

【図5】一実施形態によるデバイス構造における、過渡電流立ち上がり状態における熱散逸を比較したグラフである。

【発明を実施するための形態】

【0015】

1つまたは複数の具体的な実施形態を下記に説明する。これらの実施形態の簡潔な記載を提供するために、実際の実施態様のすべての特徴が本明細書に記載されているとは限らない場合がある。工学的または設計プロジェクトにおけるものとしての、任意のこのような実際の実施態様の開発において、開発者の特定の目標を達成するために、システム関連およびビジネス関連の制約の順守のような、多数の実施態様特有の決定が為されなければならず、これは実施形態ごとに変わり得ることが認識されるべきである。その上、このような開発努力は複雑かつ時間のかかるものであり得るが、それにもかかわらず、本開示の利益を得る当業者にとっては日常的な設計、製造および生産の作業であろうことが認識されるべきである。

【0016】

革新的な3D集積マイクロ電子チップアセンブリ、特に、熱的管理を改善する手段を含む微小電気機械システム(MEMS)デバイスが開示される。3D集積デバイスアセンブリは、これはデバイス構造内で生成された熱を効率的に熱散逸させ、相互接続構造における電気抵抗を低減しながら、向上した通電能力を提供するのに役立つ、集積された層と、並列接続された相互接続部とを含む。

【0017】

図面は、熱散逸を向上させることが可能な3D集積チップアセンブリを含む、マイクロ電子デバイス、特にMEMSデバイスの例示的な構造を示す。ここで図面を、特に図1を参照すると、同様の参照符号はいくつかの図全体を通じて同様の要素を指すが、熱散逸能力が向上した3D集積チップアセンブリを採用するデバイス構造の一例の実施形態が断面図で示されている。全体的に100で示されるこのデバイス構造は、第1の主面111および第2の主面112を有する基板110に載置される3D集積チップアセンブリ105を含む。3D集積チップアセンブリ105は概して、第1の主面122および第2の主面124を有するキャップ層114と、第1の主面140および第2の主面150を有するデバイス基板132とを備える。デバイス構造100の製造中、3D集積チップアセンブリ105は基板110の第2の主面112に載置される。デバイス構造100のこの特定の実施形態において、キャップ層114は、本明細書においてはフリップチップバンプ接合とも称される、高い通電能力を可能にする複数のマイクロバンプ接続部115を利用して第1の主面122を介して基板110に載置される。デバイス基板132は、標準的な金属相互接続(まもなく説明する)によってデバイス基板132の第1の主面140を介して、キャップ層114の第2の主面124上に載置される。ヒートスプレッダ152が、熱伝導材料(TIM)154を介してデバイス基板132の第2の主面150上に配置されることができる。基板110、キャップ層114、デバイス基板132、複数の層の間の相互接続部、熱伝導材料134およびヒートスプレッダ136を含む積層される要素が、組み合わさってデバイス構造100を形成する。

【0018】

この特定の実施形態では、電気相互接続のための基板110は当該技術分野において既知のプリント回路基板(PCB)であってもよい。しかしながら、代替的な実施形態における基板材料は、シリコン、炭化ケイ素、ガリウムヒ素などのような金属酸化膜半導体(MOS)ベースの層のような能動素子層を含んでもよく、または能動層を考慮しない場合には、研磨された金属、柔軟なプラスチック、ポリイミド、半導体材料、またはガラスもしくは水晶材などの絶縁体のような任意の平坦な支持材料から成ってもよいことを当業者は認識しよう。

【0019】

この特定の実施形態では、デバイス基板132は当該技術分野において既知のシリコンから成ってもよい。しかしながら、代替的な実施形態におけるデバイス基板材料は、シリコン、炭化ケイ素、ガリウムヒ素、窒化ガリウム、アルミナ、サファイア、チタン、鋼鉄、プラスチック、ポリイミド、ガラス、石英などのような、半導体およびMEMSベースの製造工程およびパッケージング工程に適合する任意の平坦な支持材料を含んでもよいことを当業者は認識しよう。

【0020】

基板110の第2の主面112は、複数の並列に構成されるはんだバンプ118を介して、キャップ層114の第1の主面122上に配置されるとともに基板110の入出力接点116に整合するように構成される複数の第1の入出力接点120にはんだ付けされて示されている複数の入出力接点116を含む。3D集積チップアセンブリ105、より詳細にはキャップ層114が取り付けられることになる、キャップ層114の入出力接点(まもなく説明する)に整合するようにパターニングされ配置される基板110層の複数の入出力接点116を製造するのに、標準的なウェハプロセスが使用される。複数の入出力接点116は、1つまたは複数の金属層、例えば、銅、ニッケルおよび/または金の層として構築され得る。入出力接点スタックにおける金属層の実際の組成は基板110の材料によって決まることになる。一実施形態では、デバイス構造132およびキャップ層114は、最初にともに接合されて、本明細書において「MEMS」または「デバイスチップ」とも称される3D集積チップアセンブリ105を形成し、これはその後はんだバンプ118を介して基板110に取り付けられる。好ましい実施形態では、多くの並列バンプが使用されて、高電流キャリアならびに熱シャントとして役割を果たす。並列マイクロバンプ相互接続は、パッケージサイズ、IOカウントなどに応じて、IO当たり2〜50またはそれ以上の数に及ぶことができる。

【0021】

当該技術分野において既知であるアンダーフィル材料121が、基板110とキャップ層114との間に配置されるものとして示されている。アンダーフィル材料121は、基板110とキャップ層114との間の空間を埋めるために使用することができ、それによって、マイクロバンプ接続部115、より詳細には複数の入出力接続部116、複数の第1の入出力接続部120およびはんだバンプ118が固定されたままになる。基板110とキャップ層114との間で膨張率が異なる場合、それらは、デバイス構造100が動作中に生成される熱に起因して加熱または冷却されるときに膨張または収縮する量が異なる場合がある。デバイス構造100のこの加熱または冷却は、デバイス構造100のさまざまな層の間に相対運動をもたらす場合がある。アンダーフィル材料121を含むことが、基板110とキャップ層114との間で相互接続して安全でなくなることを防止するのに役立つ場合がある。

【0022】

キャップ層114は、第2の主面124上で、デバイス基板132上に形成される複数の入出力接点(まもなく説明する)と整合し、または他の様態で結合もしくは適合するように構成される、複数の第2の入出力接点126を支持するようにさらに構成される。キャップ層114の下側主面122から第2の主面124への相互接続は、例えば、ビア形成のためのレーザ、高速反応性イオンエッチングなどを使用して構築される複数の基板貫通ビア130、より詳細には複数のシリコン貫通ビア(TSV)130を構築すること、およびビアメタライゼーションのための標準的なウェハプロセスを含むさまざまな手段によって達成することができる。

【0023】

図示されるように、複数の第1の入出力接点120は、複数のウェハ貫通ビア128を介して、キャップ層114の第2の主面124上に配置される複数の第2の入出力接点126に電気的に接続する。複数のウェハ貫通ビア128はキャップ層114から電気的に絶縁される。

【0024】

本明細書に記載されるデバイス100の1つの実施形態は、基板110がプリント回路基板(PCB)でない場合には、半導体材料からキャップ層114を製造すること、および、例えば、キャップ層114の材料を、このキャップ層が接続されることになる基板110に一致させることを含む。より具体的には、デバイス構造100を製造する1つの方法は、基板110によって採用される材料に一致する半導体材料、例えば、シリコンから成るキャップ層114を選択することである。これによって機械適応力、負担が最小限に抑えられ、その他の点では高信頼性パッケージおよび相互接続が提供され、均等な電気的相互接続性能ももたらされる。例として、デバイス構造100がシリコン基板110を含む場合、キャップ層114もシリコンから製造されてもよい。シリコンベースの集積回路デバイスが今日優勢を占めているため、本明細書において提供される説明はシリコンキャップ層114を論じているものであり得る。しかしながら、デバイス基板材料およびキャップ層材料は、シリコン、炭化ケイ素、ガリウムヒ素などを含む任意の半導体材料、または代替的には石英のような材料などを含み得ることを当業者は認識しよう。キャップ層114の製造に、ウェハ処理を使用してキャップ層114上に複数の第1の入出力接点120を作成することを含む、標準的なウェハプロセスを採用することができる。

【0025】

キャップ層114の材料が選択された後、複数のウェハ貫通ビア128が(例えば、キャップ層114を貫通するプラズマエッチング、穿孔、レーザ穿孔、化学エッチング、高速反応性イオンエッチング、レーザ切断などによって)作成され、任意選択的に、キャップ層114と後続の電気的相互接続とを電気的に絶縁するために絶縁され、金属化されてキャップ層114の第1の主面122からキャップ層114の第2の主面124までの電気的接続が形成される。

【0026】

上記のようなビア作成に続いて、金属化されたウェハ貫通ビア128を作成するために標準的なウェハプロセス(フォトリソグラフィ、湿式化学、物理気相成長(PVD)、電気めっきなど)を採用することができる。貫通ビア構築工程の1つの実施形態は、(応力を軽減するために)湿式化学を使用して、続いて、キャップ層114の表面および(ビアを充填することなく)ビアの壁面を部分的に被覆する絶縁層を確立するために酸化させ、キャップ層114からの必要な電気的絶縁を提供することである。次いで、シードメタルが堆積されてビア内に金属層が確立され、その後、ビアが金属、例えば、銅、ニッケル、金などによってめっきされる。フォトマスクが被着され、もしあれば、貫通ビアに対する回路(例えば、入出力)接点および相互接続部がパターニングされる。完成すると、図1に示されるようなキャップ層114が実現し、金属化された貫通ビアはキャップ層114の第1の主面122から第2の主面124まで延在する。

【0027】

貫通ビアの形成に続いて、複数の第1の入出力接点120の製造に加えて、キャップ層114が取り付けられることになる、デバイス基板132の入出力接点に整合するようにパターニングされ配置される、キャップ層114の複数の入出力接点126を製造するのに、標準的なウェハプロセスが使用される。反対側の、キャップ層114の第1の主面122上には例えば、複数の入出力接点120が形成される。複数の入出力接点120および126は、金属層、例えば、銅、ニッケルおよび/または金の層のスタックとして構築され得る。入出力接点スタックにおける金属層の実際の組成はキャップ層114の材料および使用される取り付け方法によって決まることになる。

【0028】

図1の実施形態では、キャップ層114内に形成される複数のウェハ貫通ビア128が、キャップ層114の第1の主面122上に配置されることになる複数の第1の入出力接点120およびキャップ層114の第2の主面124上に配置されることになる複数の第2の入出力接点126の下にまたは近接して位置合わせされる。複数の第2の入出力接点126は、1つの実施形態では、複数の入出力接点138またはキャップ層114が取り付けられることになるデバイス基板132のパッド構成に整合するようにパターニングされ、一方で複数の第1の入出力接点120は、同じくキャップ層114が接続されることになる基板110への接続を容易にするように構成される。1つの実施形態では、ウェハ貫通ビア128の直径は、ウェハ貫通ビア128の量およびデバイス基板132、複数の入出力接点138および複数の入出力接点116の位置によって決まる。高密度入出力構成のために、各ビア128の直径は、今日の技術を使用すれば10マイクロメートル(10ミクロン)以下にまで小さくすることができる。

【0029】

図示されるように、キャップ層114の第1の主面122上に配置される複数の第1の入出力接点120は、金属化されたビア128を介して、キャップ層114の第2の主面124上に配置される複数の第2の入出力接点126に電気的に接続する。

【0030】

デバイス基板132は、既に説明されたように、第1の主面140上に形成される複数の入出力接点138を含む。複数の入出力接点138は、熱圧着などを通じて、キャップ層114の第2の主面124上に配置されるとともにキャップ層114の入出力接点126に整合するように構成される複数の第2の入出力接点126にはんだ付けされて示されている。相互接続部125を形成するために図面全体を通じて2つの別個の層が描かれているが、任意の数の材料層を利用することができることが理解されるべきである。熱伝導性配線143が、能動素子の、デバイス基板132の第1の主面140への相互接続および熱の散逸(まもなく説明する)を提供する。「能動素子」という用語は、本明細書使用される場合、半導体集積回路(IC)、単純な抵抗器、音響(超音波)センサのようなセンサ、光(LCD、フォトダイオード、空間光変調器)デバイス、または任意の類似のタイプの熱生成デバイスのような、任意の熱生成要素を含んでもよい。示されている例示的な実施形態では、能動素子144は、微小電気機械システム(MEMS)回路、特にマイクロスケール継電器を含む。

【0031】

図1に示されているように、シールリング146は能動素子144の気密シーリングを提供する。シーリング146は、ガラスフリット、共晶金属組成物、高分子接着剤、熱圧着メタルボンドなどのような、任意の既知のシーリング材料から成ってもよい。ガラスフリットシールリング146を含む実施形態では、組み立て中、チクソペーストのようなガラスフリットリングがデバイス基板132またはキャップ層114のうちの一方の上にスクリーン印刷され、乾燥されることができる。例示的な実施形態では、フリットの厚さは5〜20マイクロメートル(5〜20ミクロン)の範囲内にある。印刷されたガラスフリットリングは、最終的には、個別の能動素子(複数の場合もあり)144に対する気密シール148を形成することになる。気密シール148を形成するために、ガラス粒子を溶融させるウェハボンディング工程が実行され、それによって、シールリング146および気密シール148が作成される。通常のガラスフリットリングのウェハ処理は、ガラスリフロー、および、真空下でかつウェハからウェハへの力が印加された状態で約400℃の接着温度を採用することができる。リフローされたガラスフリットのシーリング工程は、シールリング146が、キャップ層114の第2の主面124とデバイス基板132の第1の主面140との間で能動素子144を気密封止することを可能にする。動作中の機械的構成要素によって生成される運動に起因して、能動素子144は、外気、および、湿気、塵埃粒子などのような望ましくない粒子の影響を受けやすい。シールリング146および能動素子144の周囲の気密シール148は、これらの望ましくない汚染からの保護を提供することができる。

【0032】

デバイス基板132の第2の主面150は、任意選択のヒートスプレッダ152に、それらの間に配置される熱伝導材料(TIM)154を介して取り付けられてもよい。示されている実施形態では、能動素子144によって生成される熱は、ヒートスプレッダ152を通じて外部環境内に散逸させることができる。ヒートスプレッダ152およびTIM154を含むか否かは、構造100内に追加の熱散逸能力が必要か否かによって决まり得る。

【0033】

上記で論じられたように構築されるキャップ層114、能動素子144の気密シール、複数の並列相互接続およびデバイス構造100全体は、高出力マイクロ電子チップ構造、より詳細には高出力微小電気機械システム(MEMS)内の熱散逸に付随する問題のいくらかまたはすべてを軽減することができる。加えて、本明細書に記載されるように構築される3D集積チップアセンブリ105は、高精度の高容量装着機を用いて容易に選定および配置され、パッケージングのために基板110上に組み付けられることができる。

【0034】

ここで図2を参照すると、上記の記載に従って構築されるデバイス構造100が示されており、これは、一実施形態による複数の熱散逸経路156を描いたものである。既に述べたように、同様の参照符号はいくつかの図面全体を通じて同様の要素を指す。過渡電流状態の間、複数の熱散逸経路156は示されているように利用可能である。本明細書において開示されるような熱散逸経路156は、熱が最初にバルク基板を通じて流れ、次いでTIMを通じて、次いでヒートスプレッダへと流れることを必要とするヒートスプレッダと比較して、熱生成を電力線を介した散逸へと直接結び付ける。示されるように、動作中、デバイス基板100、より詳細には能動素子144によって生成される熱は、複数の熱散逸経路156を介して、特に、デバイス144からの熱を相互接続構造125へ、下ってはんだバンプフリップチップアセンブリ115へと導く、ウェハまたはキャップ表面上の熱伝導配線143に沿って散逸される。熱散逸経路156は、能動素子144からその金属相互接続部までの連続的な熱伝導金属経路を提供し、従って、熱散逸のための主要な経路としての役割を果たす。フリップチップ相互接続部115は、熱生成源、より詳細には能動素子144に、バルクシリコンなどを通じての熱散逸にもっぱら依拠するよりも良好に熱的に結合される各電気的接合部を通じて多くの熱散逸経路156を提供する。多くの並列のより短い電気路156を提供することに加えて、フリップチップ相互接続部115は、より短い散逸経路156を提供する。描かれているように、熱は、基110とキャップ層114との間に位置するフリップチップ接合部によって形成されるマイクロバンプ相互接続部115、および、キャップ層114とデバイス基板132との間に形成される金属相互接続部125によって散逸され得る。任意の追加の熱が、デバイス基板100内に含まれる場合にはヒートスプレッダ152を通じて散逸されてもよい。記載されている新規のフリップチップ手法は、より短い相互接続経路長を提供し、それによって、熱を散逸させるためにより好ましいものにする。このような短くかつ高度に並列化された熱経路は、ワイヤボンドおよびリボンボンディングのような他の相互接続方法にまさる重要な利点を供する。

【0035】

より高出力の熱散逸能力を採用するデバイス構造構成のさらなる例が図3および図4に描かれており、ここでも、同様の参照符号は図面全体を通じて同様の要素を指す。図3をより具体的に参照すると、基板110と、概してキャップ層114およびデバイス基板132を備える3D集積チップアセンブリ105とを含むデバイス基板の別の実施形態200が示されている。この特定の実施形態では、図1および図2に描かれている実施形態とは対照的に、デバイス基板132が3D集積チップアセンブリ105の下側部分内に配置されており、より詳細には、キャップ層114がデバイス基板132の第2の主面150上に配置されている。加えて、能動素子144が、熱伝導性配線143を介してデバイス基板132の第2の主面150上に位置付けられている。デバイス基板132は、その中に形成される複数のウェハ貫通ビア130と、その第1の主面140の上に配置される複数の第1の入出力接点120とをさらに含み、複数の第1の入出力接点120は、複数のウェハ貫通ビア130を通じて能動素子144に電気的に接続されている。図1および図2に示されている第1の実施形態のものと同様に構成されるフリップチップバンプ相互接続部が、基板110の第2の主面112と、デバイス基板132の第1の主面140との間に形成される。アンダーフィル材料121も提供されることができる。シールリング146は、デバイス基板132とキャップ層114との間に能動素子144に対する気密シール148を形成する。加えて、シールリング146は、デバイス基板132の第2の主面150とキャップ層114の第1の主面122との間に物理的接合を提供する。この特定の実施形態では、図1および図2に描かれている実施形態とは対照的に、ヒートスプレッダ152および熱伝導材料154は省かれている。最初に開示された実施形態と同様に、デバイス構造200、より詳細には能動素子144によって生成される熱は、同様に図2に示されている熱散逸経路に従って散逸される。3D集積チップアセンブリ105内のキャップ層114およびデバイス基板132の構成に関わりなく、熱伝導材料154およびヒートスプレッダ152を含むか否かは、依然として追加の熱散逸能力が必要であるか否かによって決まることが付加的に理解されるべきである。

【0036】

ここで図4を参照すると、概して図1および図2に描かれている実施形態と同様にスタック内に構成されている、基板110と、概してキャップ層114およびデバイス基板132を備える3D集積チップアセンブリ105とを含むデバイス構造のさらに別の実施形態300が示されている。この特定の実施形態では、図1および図2に描かれている実施形態とは対照的に、ヒートスプレッダ152および熱伝導材料154は省かれている。任意選択のヒートスプレッダ152が、熱伝導材料(TIM)154を介してキャップ層114の第1の主面124上に位置付けられている。この特定の実施形態ではシールリングが省かれており、能動素子144に対する気密シール148は、デバイス基板132と、キャップ層114と、キャップ層114およびデバイス基板132の間に形成される金属相互接続部125とによって形成される。より具体的には、キャップ層114の第2の主面124上に形成される複数の第2の入出力接点126、および、デバイス基板132の第1の主面140上に形成される複数の入出力接点138が、能動素子144の周囲の気密シール148を提供する。さらに別の代替の実施形態では、追加のシールを形成するために、キャップ層114およびデバイス基板132の間に形成される金属相互接続部125のセットと、ビア130と、キャップ層114および基板110の間に形成される相互接続部116、120およびバンプ118とを備える、追加の相互接続ビア構造が能動素子144の周囲に含まれることができる。

【0037】

既に開示された実施形態と同様に、デバイス構造300、より詳細には能動素子144によって生成される熱は、同様に図2に示されている熱散逸経路に従って散逸される。図4はキャップ層114が基板110に取り付けられることを可能にするように位置決められて構成されている3D集積チップアセンブリ105を含んでいるが、代替的な実施形態では、キャップ層114およびデバイス基板132は、デバイス基板132が基板110に取り付けられることを可能にするために、図3に記載および図示されているように、3D集積チップアセンブリ105内の構成に関して逆になってもよいことが理解されるべきである。3D集積チップアセンブリ105内のキャップ層114およびデバイス基板132の構成に関わりなく、熱伝導材料154およびヒートスプレッダ152を含むか否かは、依然として追加の熱散逸能力が必要であるか否かによって決まることが付加的に理解されるべきである。

【0038】

図5には、既知の相互接続/スタック構成および本明細書に記載される新規の相互接続/スタック構成を含む高出力マイクロ電子デバイス構造の実施形態の熱散逸を示すシミュレーション結果400が示されている。より具体的には、熱散逸は、フリップチップボード構成の熱散逸品質の向上を示す図5においてグラフで表されている。電流(A)がx軸402上に表されており、パッケージ内の(通常はMEMSビームにおける)最大温度および温度(K)がy軸403上に表されている。標準的なワイヤボンド/配線相互接続およびヒートスプレッダを含む、既知のマイクロ電子デバイス構造における一般的な熱散逸が線404に描かれている。示されているように、約30アンペアの電流において、ワイヤボンド/配線相互接続はパッケージされたデバイスの熱伝導性を限定しており、700Kを超えて示されているように温度を過剰に熱くしてしまっている。

【0039】

銅ストラップ相互接続およびヒートスプレッダを含む、既知のマイクロ電子デバイス構造の一般的な熱散逸が線406に描かれている。示されているように、約30アンペアの電流において、銅ストラップ相互接続を含む既知のデバイスにおける熱は、ワイヤボンド/配線相互接続を含む上記のデバイスよりも効率的に熱を散逸させることが可能であるが、デバイスが460Kを超える温度に留まるような熱散逸が可能であるに過ぎない。

【0040】

図1〜図4の上記の実施形態におけるもののような、キャップ層と、気密シールと、相互接続とを含むように構成されるマイクロ電子デバイス構造の一般的な熱散逸が線408および410において描かれている。線408において示されているように、約30アンペアの電流において、図1〜図4に描かれているもののような、キャップ層と、気密シールと、新規のフリップチップ相互接続と、ヒートスプレッダとを含む新規のデバイスは、ワイヤボンド/配線相互接続またはリボンベースの相互接続を含む上記の既知のデバイスよりも効率的に熱を散逸させることが可能である。線408において描かれているように、温度は効率的に散逸され、約30アンペアにおけるデバイスの温度は400K未満である。

【0041】

図4の上記の実施形態におけるもののような、キャップ層と、気密シールと、相互接続とを含むように構成されるマイクロ電子デバイス構造であって、ヒートスプレッダがデバイス構造内に組み込まれていない、マイクロ電子デバイス構造の一般的な熱散逸が線410において描かれている。線410において示されているように、約30アンペアの電流において、図1〜図4に描かれているもののような、キャップ層と、新規のフリップチップ相互接続とを含むが、ヒートスプレッダを含まない新規のデバイスは、線408におけるヒートスプレッダを組み込んだフリップチップの実施形態よりも熱を散逸させないが、依然として、ヒートスプレッダが利用されたワイヤボンド/配線相互接続または銅ストラップ相互接続を含む上記の既知のデバイスよりも効率的に熱を散逸させることが可能である。線410において描かれているように、この実施形態における温度は効率的に散逸され、約30アンペアにおけるデバイスの温度は450K未満である。

【0042】

上記の例から、本明細書において、微小電気機械システム(MEMS)デバイスのような高出力マイクロ電子デバイスにおける熱散逸を向上させるために採用されることができる新規の相互接続構造およびデバイス構造スタックまたはパッケージが提供されることを当業者は理解しよう。標標準的な化学、機械的処理などを使用して、このデバイスを、キャップ層、デバイス基板、複数の金属相互接続部および能動素子を備える3D集積チップアセンブリと、3D集積チップアセンブリおよび下層基板の間の複数のバンプ相互接続部と、能動素子の周囲でかつキャップ層およびデバイス基板の間にある気密シールとを含むように製造することによって、コストが低く、高性能で、収率の高いデバイス構造を得ることができる。さらに、本明細書において開示されるデバイス構造および技法は結果として、熱散逸能力の向上による熱的管理の改善、パッケージ統合の簡易化、および電気抵抗相互接続の低減を含むが、これらに限定されない利点をもたらすことができる。より薄い、壊れやすい集積回路チップおよびデバイスのための機械的および熱的管理システムも提供される。

【0043】

本発明はさまざまな変更および代替の形態の影響を受け得るが、具体的な実施形態が例として図面内に示されており、本明細書において詳細に記載されている。しかしながら、本発明は開示されている特定の形態に限定されるようには意図されていないことが理解されるべきである。そうではなく、本発明は、添付の特許請求の範囲によって定義される発明の趣旨および範囲内に入るすべての変更、均等物、および代替物を包含するものである。

【符号の説明】

【0044】

100 デバイスアセンブリ

105 3D集積チップアセンブリ

110 基板

111 110の第1の主面

112 110の第2の主面

114 キャップ層

115 マイクロバンプ接続部

116 複数の入出力接点

118 はんだバンプ

120 複数の第1の入出力接点

121 アンダーフィル材料

122 114の第1の主面

124 114の第2の主面

125 金属相互接続部

126 複数の第2の入出力接点

128 複数のウェハ貫通ビア

130 複数のシリコン貫通電極(TSV)

132 デバイス基板

134 熱伝導材料

136 ヒートスプレッダ

138 複数の入出力接点

140 132の第1の主面

141 熱伝導層

142 はんだバンプ

143 熱伝導性配線

144 能動素子

146 ガラスフリット

148 気密シール

150 132の第2の主面

152 ヒートスプレッダ

154 熱伝導材料

156 熱散逸経路

200 第2の実施形態

300 第3の実施形態

【特許請求の範囲】

【請求項1】

三次元(3D)集積チップアセンブリ(105)であって、

デバイス基板(132)、

前記デバイス基板(132)上に配置される1つまたは複数の熱生成要素を備える能動素子(144)、

前記デバイス基板(132)に物理的に接合されるキャップ層(114)、および

前記能動素子(144)の周囲に形成される気密シール(148)であって、少なくとも部分的に、前記デバイス基板(132)および前記キャップ層(114)によって画定される、気密シール

を備える、チップアセンブリと、

基板(110)とを備え、前記三次元(3D)集積チップアセンブリ(105)は、前記基板(110)にフリップチップ接合され、

複数の熱散逸経路(156)が、その中で生成される熱を散逸させるために前記三次元(3D)集積チップアセンブリ(105)を通じて延在する、装置(100、200、300)。

【請求項2】

前記装置(100、300)からの熱の散逸を容易にするために、熱伝導材料(TIM)(154)を介して前記三次元(3D)集積チップアセンブリ(105)に近接して位置付けられるヒートスプレッダ(152)をさらに備える、請求項1記載の装置(100、300)。

【請求項3】

前記キャップ層(114)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(122)の上に配置される複数の第1の入出力接点(120)と、その第2の主面(124)の上に配置される複数の第2の入出力接点(126)とをさらに備え、前記複数の第2の入出力接点(126)は、前記複数のウェハ貫通ビア(130)を通じて前記複数の第1の入出力接点(120)に電気的に接続されている、請求項1記載の装置(100、300)。

【請求項4】

前記デバイス基板(132)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(140)の上に配置される複数の第1の入出力接点(120)とをさらに備え、前記複数の第1の入出力接点(120)は、前記複数のウェハ貫通ビア(130)を通じて前記能動素子(144)に電気的に接続されている、請求項1記載の装置(200)。

【請求項5】

前記能動素子(144)の周囲に形成される前記気密シール(148)は、前記デバイス基板(132)と、前記キャップ層(114)と、前記キャップ層(114)および前記デバイス基板(132)を相互接続する前記複数の電気的相互接続(126、138、143)とによって画定される、請求項1記載の装置。

【請求項6】

前記能動素子(144)の周囲に配置されるシールリング(146)をさらに備え、前記能動素子(144)の周囲に形成される前記気密シール(148)は、前記デバイス基板(132)と、前記キャップ層(114)と、前記シールリング(146)とによって画定される、請求項1記載の装置。

【請求項7】

キャップ層(114)、および、少なくとも部分的に前記キャップ層(114)によって画定される気密シール(148)を含むMEMSデバイス(105)と、

基板(110)とを備え、

前記MEMSデバイス(105)は、前記基板(110)にフリップチップ接合されるように構成される、装置。

【請求項8】

前記キャップ層(114)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(122)の上に配置される複数の第1の入出力接点(120)と、その第2の主面(124)の上に配置される複数の第2の入出力接点(126)とをさらに備え、前記複数の第2の入出力接点(124)は、前記複数のウェハ貫通ビア(130)を通じて前記複数の第1の入出力接点(120)に電気的に接続されており、

前記キャップ層(114)の前記第1の主面(122)の上に配置される前記複数の第1の入出力接点(120)は、前記キャップ層(114)が取り付けられることになる前記基板(110)の複数の入出力パッド(116)への結合を容易にし、

前記キャップ層(114)の前記第2の主面(124)の上に配置される前記複数の第2の入出力接点(126)は、同じく前記キャップ層(114)が取り付けられることになる前記デバイス基板(132)の複数の入出力接点(138)への結合を容易にする、請求項7記載の装置。

【請求項9】

前記デバイス基板(132)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(140)の上に配置される複数の第1の入出力接点(120)とをさらに備え、前記複数の第1の入出力接点(120)は前記複数のウェハ貫通ビア(130)および複数の熱伝導性配線(143)を通じて前記能動素子(144)に電気的に接続され、前記デバイス基板(132)の前記第1の主面(140)の上に配置される前記複数の第1の入出力接点(120)は、前記デバイス基板(132)が取り付けられることになる前記基板(110)の複数の入出力パッド(116)への結合を容易にする、請求項7記載の装置(200)。

【請求項10】

方法であって、

三次元(3D)集積チップアセンブリ(105)を提供することであって、前記チップアセンブリを提供する方法は、

第1の主面(140)および第2の主面(150)を有するデバイス基板(132)を提供することであって、前記デバイス基板(132)は、前記第1の主面(140)および前記第2の主面(150)のうちの少なくとも一方の上に複数の入出力接続部(138、143)を含む、提供すること、

前記デバイス基板(132)上に1つまたは複数の集積回路を備える能動素子(144)を配置すること、

キャップ層(114)を前記デバイス基板(132)に接合することであって、前記キャップ層(114)は、第1の主面(122)および第2の主面(124)を有する、接合すること、

前記能動素子(144)の周囲に気密シール(158)を形成することであって、前記気密シール(158)は少なくとも部分的に、前記デバイス基板(132)および前記キャップ層(114)によって画定される、形成すること、ならびに

複数の入出力接続部(116)を含む基板(110)を提供すること

を含む、三次元(3D)集積チップアセンブリを提供することと、

装置(100、200、300)を形成するために前記三次元(3D)集積チップアセンブリ(105)を前記基板(110)にフリップチップ接合することとを含み、

前記装置(100、200、300)は、前記装置(100、200、300)内で生成される熱を散逸させるための、前記三次元(3D)集積チップアセンブリ(105)を通る複数の熱散逸経路(156)を提供する、方法。

【請求項1】

三次元(3D)集積チップアセンブリ(105)であって、

デバイス基板(132)、

前記デバイス基板(132)上に配置される1つまたは複数の熱生成要素を備える能動素子(144)、

前記デバイス基板(132)に物理的に接合されるキャップ層(114)、および

前記能動素子(144)の周囲に形成される気密シール(148)であって、少なくとも部分的に、前記デバイス基板(132)および前記キャップ層(114)によって画定される、気密シール

を備える、チップアセンブリと、

基板(110)とを備え、前記三次元(3D)集積チップアセンブリ(105)は、前記基板(110)にフリップチップ接合され、

複数の熱散逸経路(156)が、その中で生成される熱を散逸させるために前記三次元(3D)集積チップアセンブリ(105)を通じて延在する、装置(100、200、300)。

【請求項2】

前記装置(100、300)からの熱の散逸を容易にするために、熱伝導材料(TIM)(154)を介して前記三次元(3D)集積チップアセンブリ(105)に近接して位置付けられるヒートスプレッダ(152)をさらに備える、請求項1記載の装置(100、300)。

【請求項3】

前記キャップ層(114)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(122)の上に配置される複数の第1の入出力接点(120)と、その第2の主面(124)の上に配置される複数の第2の入出力接点(126)とをさらに備え、前記複数の第2の入出力接点(126)は、前記複数のウェハ貫通ビア(130)を通じて前記複数の第1の入出力接点(120)に電気的に接続されている、請求項1記載の装置(100、300)。

【請求項4】

前記デバイス基板(132)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(140)の上に配置される複数の第1の入出力接点(120)とをさらに備え、前記複数の第1の入出力接点(120)は、前記複数のウェハ貫通ビア(130)を通じて前記能動素子(144)に電気的に接続されている、請求項1記載の装置(200)。

【請求項5】

前記能動素子(144)の周囲に形成される前記気密シール(148)は、前記デバイス基板(132)と、前記キャップ層(114)と、前記キャップ層(114)および前記デバイス基板(132)を相互接続する前記複数の電気的相互接続(126、138、143)とによって画定される、請求項1記載の装置。

【請求項6】

前記能動素子(144)の周囲に配置されるシールリング(146)をさらに備え、前記能動素子(144)の周囲に形成される前記気密シール(148)は、前記デバイス基板(132)と、前記キャップ層(114)と、前記シールリング(146)とによって画定される、請求項1記載の装置。

【請求項7】

キャップ層(114)、および、少なくとも部分的に前記キャップ層(114)によって画定される気密シール(148)を含むMEMSデバイス(105)と、

基板(110)とを備え、

前記MEMSデバイス(105)は、前記基板(110)にフリップチップ接合されるように構成される、装置。

【請求項8】

前記キャップ層(114)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(122)の上に配置される複数の第1の入出力接点(120)と、その第2の主面(124)の上に配置される複数の第2の入出力接点(126)とをさらに備え、前記複数の第2の入出力接点(124)は、前記複数のウェハ貫通ビア(130)を通じて前記複数の第1の入出力接点(120)に電気的に接続されており、

前記キャップ層(114)の前記第1の主面(122)の上に配置される前記複数の第1の入出力接点(120)は、前記キャップ層(114)が取り付けられることになる前記基板(110)の複数の入出力パッド(116)への結合を容易にし、

前記キャップ層(114)の前記第2の主面(124)の上に配置される前記複数の第2の入出力接点(126)は、同じく前記キャップ層(114)が取り付けられることになる前記デバイス基板(132)の複数の入出力接点(138)への結合を容易にする、請求項7記載の装置。

【請求項9】

前記デバイス基板(132)は、その中に形成される複数のウェハ貫通ビア(130)と、その第1の主面(140)の上に配置される複数の第1の入出力接点(120)とをさらに備え、前記複数の第1の入出力接点(120)は前記複数のウェハ貫通ビア(130)および複数の熱伝導性配線(143)を通じて前記能動素子(144)に電気的に接続され、前記デバイス基板(132)の前記第1の主面(140)の上に配置される前記複数の第1の入出力接点(120)は、前記デバイス基板(132)が取り付けられることになる前記基板(110)の複数の入出力パッド(116)への結合を容易にする、請求項7記載の装置(200)。

【請求項10】

方法であって、

三次元(3D)集積チップアセンブリ(105)を提供することであって、前記チップアセンブリを提供する方法は、

第1の主面(140)および第2の主面(150)を有するデバイス基板(132)を提供することであって、前記デバイス基板(132)は、前記第1の主面(140)および前記第2の主面(150)のうちの少なくとも一方の上に複数の入出力接続部(138、143)を含む、提供すること、

前記デバイス基板(132)上に1つまたは複数の集積回路を備える能動素子(144)を配置すること、

キャップ層(114)を前記デバイス基板(132)に接合することであって、前記キャップ層(114)は、第1の主面(122)および第2の主面(124)を有する、接合すること、

前記能動素子(144)の周囲に気密シール(158)を形成することであって、前記気密シール(158)は少なくとも部分的に、前記デバイス基板(132)および前記キャップ層(114)によって画定される、形成すること、ならびに

複数の入出力接続部(116)を含む基板(110)を提供すること

を含む、三次元(3D)集積チップアセンブリを提供することと、

装置(100、200、300)を形成するために前記三次元(3D)集積チップアセンブリ(105)を前記基板(110)にフリップチップ接合することとを含み、

前記装置(100、200、300)は、前記装置(100、200、300)内で生成される熱を散逸させるための、前記三次元(3D)集積チップアセンブリ(105)を通る複数の熱散逸経路(156)を提供する、方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−80923(P2013−80923A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−210260(P2012−210260)

【出願日】平成24年9月25日(2012.9.25)

【出願人】(390041542)ゼネラル・エレクトリック・カンパニイ (6,332)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2012−210260(P2012−210260)

【出願日】平成24年9月25日(2012.9.25)

【出願人】(390041542)ゼネラル・エレクトリック・カンパニイ (6,332)

【Fターム(参考)】

[ Back to top ]