周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、周波数シンセサイザに関する。

【背景技術】

【0002】

周波数シンセサイザとして、電圧制御発振器の出力信号をA/D変換(アナログ/ディジタル変換)し、得られたディジタル信号を処理して処理結果を電圧制御発振器に入力し、これによりPLL(Phase Locked Loop)を形成するものが知られている。例えば特許文献1には、電圧制御発振器の出力信号をA/D変換(アナログ/ディジタル変換)し、そのディジタル信号により作成される正弦波信号を直交検波して当該正弦波信号と検波に用いた正弦波信号との差分周波数で回転する回転ベクトルを取り出し、この回転ベクトルと、当該回転ベクトルとは逆に回転しかつ設定周波数に対応する周波数で回転する回転ベクトルと、の差分速度を積分して電圧制御発振器の入力電圧とする周波数シンセサイザが記載されている。

しかしながらPLL中に位相雑音が存在し、このため周波数シンセサイザの出力に位相雑音が発生するという課題がある。

【0003】

そこで本件出願人は、こうした位相雑音の問題を解決すべく、電圧制御発振部(Voltage Controlled Oscillator;以下、VCOという)からのアナログ周波数信号と、ダイレクト・ディジタルシンセサイザ(Direct Digital Synthesizer:以下、DDSという)などのディジタル周波数発振部から出力されるディジタル周波数信号をディジタル/アナログ変換(D/A変換)して得られた信号との差分を取って増幅し、この増幅された差分信号をA/D変換してから検波信号により直交検波して、両周波数信号の位相差を取り出して積分し、この積分値に応じた電圧を前記電圧制御発振部に供給することによりアナログ周波数信号の周波数を調整する新型のPLLを開発している。

【0004】

差動増幅器にて差分を取ってから出力信号を増幅することにより、信号をアナログ/ディジタル変換する際に発生する量子化誤差を、差分信号の振幅に対して相対的に低く抑えることができるので、こうした量子化誤差などに起因する位相雑音を改善することができる。

ここで差分信号と直交検波される検波信号には、DDSから出力されたディジタル周波数信号の位相を90°だけずらした信号を用いており、この検波信号と差分信号中のDDSから出力された周波数信号成分とが直交していることにより、アナログ周波数信号側の位相のずれを正確に取り出すことができる。

【0005】

ところがディジタル化された差分信号を得るために用いられるD/A変換器などの回路のなかには、回路を立ち上げる度に当該回路に信号を入力してから演算結果が出力されるまでの時間(以下レイテンシという)が変動してしまうものがあることが分かった。このようにレイテンシが変動してしまうと、正確な直交検波を実行できなくなり、VCOの周波数調整の精度が低下してしまうという問題がある。

【0006】

ここで特許文献2には、周波数信号などの標本再生信号を、VCOから出力されるサンプルクロックに同期してサンプリングし、サンプリング値を目標値と比較することによりサンプルクロックと目標クロックの位相差を誤差補正回路にて検出し、この位相差をVCOにフィードバックしてサンプリングクロックの周波数を調節する従来型のPLLにおいて、VCOと誤差補正回路との間に可変式の遅延回路を設ける技術が記載されている。この遅延回路には、後段の誤差補正回路にて検出された位相差がフィードバックされ、位相差の大きさに応じて遅延量を増減することにより、PLLの立ち上げ初期の位相差をキャンセルし、短時間でサンプルクロックを目標クロックに同期させることができるようになっているが、PLL内の回路が持つレイテンシの変動の影響を解消する手法については何ら開示されていない。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−74291号公報:請求項1、段落0017〜段落0021、図1

【特許文献2】特開平11−214990:請求項1、段落0023〜段落0025、図6

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明はこのような事情の下になされたものであり、その目的は、精度の高い周波数調整が可能であると共に、安定して作動する周波数シンセサイザ及び周波数シンセサイザの調整方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明に係る周波数シンセサイザは、電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給する周波数シンセサイザであって、

前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、

前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号中に含まれる周波数設定部由来の周波数信号が前記位相検出部に入力されるまでのタイミングと、前記出力された時点から検波信号が前記位相検出部に入力されるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、

前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、

前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力し、前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する制御部と、を備えたことを特徴とする。

【0010】

前記周波数シンセサイザは、以下の特徴を備えていてもよい。

(a)前記制御部は、前記差動増幅器に前記テスト用の周波数信号を入力するときには、当該差動増幅器の差動利得、または前記周波数設定部から出力されるディジタルの周波数信号の信号レベルを通常使用時に比べて小さくすること。

(b)前記第2の位相補正部は、シフトレジスタにより構成されていること。

(c)前記周波数設定部は、ダイレクト・ディジタル・シンセサイザであること。

【0011】

また、他の発明に係る周波数シンセサイザの調整方法は、電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給し、前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、前記出力された時点から検波信号が得られるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、を備えた周波数シンセサイザの調整方法であって、

この周波数シンセサイザの立ち上げ時に、前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力する工程と、

前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する工程と、を含むことを特徴とする。

【発明の効果】

【0012】

本発明の周波数シンセサイザは、電圧制御発振部から出力された周波数信号との位相差を検出するために、周波数設定部から出力される周波数信号と、この周波数信号の位相を90°ずらした検波信号とが異なる経路を通って位相検出部に入力されて直交検波に利用される際に、これら2つの信号が位相検出部に入力されるタイミングをそろえるための第1の位相補正部と第2の位相補正部とを備えている。そして第1の位相補正部は予め定めた量だけ前記検波信号の位相を補正する一方、第2の位相補正部は検波信号を出力するタイミングをクロック単位で遅らせることができる。この結果、周波数設定部から出力された周波数信号が通る経路に設けられているディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる場合であっても、この変換時間の変化に応じて検波信号の出力タイミングを遅らせ、周波数設定部から同時に出力された周波数信号−検波信号間の位相差を小さくすることができるので、電圧制御発振部及び周波数設定部の各々の周波数信号の位相差を正確に把握して精度の高い周波数調整を行うことができる。

【図面の簡単な説明】

【0013】

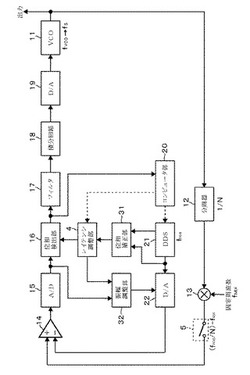

【図1】実施の形態に係る周波数シンセサイザのブロック図である。

【図2】前記周波数シンセサイザに設けられている積分回路の構成図である。

【図3】前記周波数シンセサイザに設けられているレイテンシ調整部の構成図である。

【図4】前記立ち上げ時における周波数シンセサイザの動作を示すタイミングチャートである。

【図5】前記立ち上げ時において位相検出部から出力される信号の強度を模式的に示す説明図である。

【図6】前記周波数シンセサイザの立ち上げ時の動作の流れを示すフロー図である。

【発明を実施するための形態】

【0014】

以下、図1に示したブロック図を参照しながら、本実施の形態に係る周波数シンセサイザの構成について説明する。本例に係る周波数シンセサイザは、電圧制御発振部であるVCO11から出力された周波数信号を帰還信号として、DDS21(Direct Digital Synthesizer)から出力された周波数信号との位相比較を行い、これらの周波数の位相差に対応する電圧を積分して、VCO11の入力側に供給するPLL(Phased Lock Loop)回路を形成している。これらの信号の周波数差がゼロになったときにPLLがロックされ、VCO11の出力周波数が設定周波数にロックされることになる。このDDS21は特許請求の範囲の周波数設定部に相当する。

【0015】

図1中VCO11は、供給電圧に応じた周波数fVCOの正弦波であるアナログの周波数信号を出力する役割を果たす。VCO11の後段に設けられた分周器12は、VCO11から出力された周波数信号を1/N(Nは整数)に分周して、その周波数を(fVCO/N)とする機能を有する。

【0016】

ミキサ13は、分周器12から出力された周波数信号に、周波数fMIXの固定周波数信号を乗算し、ヘテロダインの原理により得られる「(fVCO/N)±fMIX」の2つの周波数を持つ信号のうち、低周波数「(fVCO/N)―fMIX」の信号を取り出すことができる。ミキサ13から出力された周波数信号は、後段の差動増幅器14に入力される。

【0017】

差動増幅器14には、VCO11側からの周波数信号に加えて、この信号と位相比較を行うための周波数信号がDDS21側より入力されるので、先にDDS21についての説明を行う。DDS21は、不図示の波形テーブルに例えば正弦波の振幅データを位相データに対応付けて記憶しており、後述のシステムクロック201からのクロック信号の入力タイミング毎に予め設定された位相幅データを累積加算して得た位相データに基づいて振幅データを読み出すことにより、設定された周波数のディジタルの周波数信号を出力する機能を備えている。システムクロック201の基準となるクロックの発生源は、例えば水晶発振器などから構成される。

【0018】

DDS21では、位相幅データの値を大きくすることにより、波形テーブルに記憶されている波形データが位相幅データの大きさに応じて読み飛ばされ、これによって周波数を調整している。即ち、位相幅データの値を大きくするほど周波数の高い信号を出力することができる。本例におけるDDS21は例えばcos(ωt)(ωは角速度[rad/秒])の周波数信号と、当該周波数信号の位相を90°ずらした検波信号sin(ωt)とを同時に出力することができる。またDDS21は、これら周波数信号及び検波信号の信号レベル(信号強度)を各々独立して増減することができる。但し後述するように、DDS21からの周波数信号のレベルの調整は、D/A変換器22により行ってもよい。

【0019】

本例では、例えば周波数シンセサイザの制御部をなすコンピュータ部20からDDS21に対して、設定周波数を決定する位相幅データの設定が行われる。例えば周波数シンセサイザの設定周波数をfsとしたとき、DDS21から出力される信号の周波数fDDSは、VCO11から出力される周波数信号が設定周波数にロックされたときに、ミキサ13から出力される信号の周波数「(fS/N)―fMIX」と一致するように設定され、この値に基づいて前記位相幅データが設定される。DDS21から出力された周波数信号は、D/A変換器22を介してアナログの周波数信号に変換され、既述の差動増幅器14に入力されることになる。このD/A変換器22は特許請求の範囲のディジタル/アナログ変換部に相当する。

【0020】

差動増幅器14はVCO11側のミキサ13から入力された周波数信号とDDS21側から入力された周波数信号との差分値を算出し、この結果を増幅してから後段のA/D変換器15へと出力する役割を果たす。このように差動増幅器14を設け、VCO11、DDS21の双方から出力される周波数信号の差分をとって増幅した差分信号を出力することにより、後段のA/D変換器15でのアナログ信号からのディジタル信号のサンプリング時に当該信号を所定のビット数に丸める際に発生する位相雑音の発生を低減している。

【0021】

本発明者は、A/D変換器における位相雑音劣化のない理想的な周波数シンセサイザのシミュレーション結果と実際の周波数シンセサイザの出力とを比較することにより、A/D変換器における位相雑音の劣化量は最大で10dB程度の大きさであることを把握している。そこで差動増幅器14は、2つの周波数信号の差分値を10dB以上の例えば26dB増幅する(20倍に増幅する)ことにより、A/D変換器15にて発生する位相雑音の劣化をキャンセル(相殺)できることが実証的に確認されており、本実施の形態に係る周波数シンセサイザはこのような考え方に基づいて差動増幅器14を備えた構成となっている。

【0022】

既述のようにDDS21から出力される周波数信号をcos(ωt)とし、VCO11側からのミキサ13出口の周波数信号はcos(ω’t)(ω’は角速度[rad/秒])としたとき、VCO11の出力周波数fVCOが設定周波数fsに十分に近づきPLLがロックされる直前の状態においては、ω≒ω’=ω+Δω(Δω≪1)となるのでミキサ13出口の周波数信号はcos(ωt+Δωt)と表現できる。Δω≪1の条件下では、Δωtの値は時間的に殆ど変化しないので、位相のずれΔθと表すことができる。

【0023】

即ち、PLLがロックされる直前の状態においては、DDS21側から差動増幅器14に入力される周波数信号をcos(ωt)、ミキサ13から差動増幅器14に入力される周波数信号をcos(ωt+Δθ)と表すことができ、差動増幅器14からは、以下の(1)式で表される周波数信号が出力されることになる。

20{cos(ωt+Δθ)−cos(ωt)} …(1)

【0024】

差動増幅器14の後段に設けられたA/D変換器15は、当該(1)式で表される信号をディジタル信号に変換する役割を果たすが、DDS21から出力された周波数信号は、D/A変換器22にてアナログ変換される際に時間遅れを生じ、また差動増幅器14にて差分信号を取得し、この差分信号をA/D変換器15でディジタル信号に変換する際にも処理に伴う時間遅れを生ずる。この時間遅れをΔtで表し、t’=t+Δtとすると、A/D変換器15からの出力信号は下記の(1)’式で表すことができる。ここで、ミキサ13出力に対するD/A変換器22の処理に起因する時間遅れは、両周波数信号の位相差Δθに含めることができる。

20{cos(ωt’+Δθ)−cos(ωt’)} …(1)’

【0025】

そしてA/D変換器15の後段には、2つの周波数信号の位相差Δθを検出するための直交検波部である位相検出部16が設けられている。位相検出部16は、(1)’式で表される前段のA/D変換器15からの出力信号に、当該(1)’式に含まれるcos(ωt’)と直交する検波信号sin(ωt’)を乗じて、位相差成分を取り出すための前処理を行う機能を備えている。

【0026】

既述のようにDDS21からは、差動増幅器14に入力される周波数信号(cos(ωt))とこれに直交する検波信号(sin(ωt))とを並行して出力することができる。この検波信号に対して、D/A変換器22、差動増幅器14及びA/D変換器15において発生する時間遅れΔtを相殺する位相補正が位相補正部31及びレイテンシ調整部4にて行われ、こうして位相補正された検波信号sin(ωt’)が位相検出部16へと入力される。位相検出部16にて実行される演算を整理すると、下記(2)式で表される出力が得られる。

sin(ωt’)

×[20{cos(ωt’+Δθ)−cos(ωt’)}]

=(20/2)sin(2ωt’+Δθ)+(20/2)sin(−Δθ)

+(20/2)sin(2ωt’)…(2)

【0027】

位相検出部16の後段には、フィルタ17が設けられており(2)式で表される位相検出部16の出力から交流成分を除去して、直流成分である(20/2)sin(−Δθ)=−(20/2)sin(Δθ)を取り出すことにより、VCO11側及びDDS21側の2つの周波数信号の位相差を知ることができる。

【0028】

積分回路18は、本例の周波数シンセサイザを構成するPLL回路のループフィルタに相当し、フィルタ17にて検出した位相差に対応する信号「−(20/2)sin(Δθ)」にPLL回路のループゲインを調整するための係数を乗算し、その信号を積分系と直接系とに分けた後に加算する構成となっている。

【0029】

図2は、積分回路18の構成例を示しており、図中181は入力信号に調整係数を乗ずる乗算部、182は乗算後の信号を累積加算する累積加算部、183は乗算後の信号(直接系)と累積加算部182からの出力信号(積分系)とを加算する加算部である。積分回路18は、入力された「−(20/2)sin(Δθ)」の値がゼロとなるように、PLL回路のループ制御を実行する役割を果たす。

【0030】

積分回路18の後段にはD/A変換器19が設けられており、積分回路18からの出力がアナログ信号に変換されて、D/A変換器19の出力がVCO11に制御電圧として入力され、PLL回路による周波数調整を実行することができる。

【0031】

ここで図1に示した32は、差動増幅器14に入力されるDDS側の周波数信号と、ミキサ13側からの周波数信号との振幅をそろえるために、差動増幅器14からの周波数信号と、DDS21からの周波数信号(cos(ωt’):位相補正部31及びレイテンシ調整部4にて時間遅れΔtの調整済み)とに基づいてD/A変換器22より出力されるアナログ信号の振幅を調整するための振幅調整部である。

【0032】

ここで先に説明したように、位相補正部31及びレイテンシ調整部4は、D/A変換器22、差動増幅器14及びその後段のA/D変換器15の処理にて発生するの時間遅れを補正する役割を果たしている。ところが背景技術で説明したようにこれらの機器のなかには回路を立ち上げる度に処理時間(レイテンシ)が変動し、その結果、DDS21から出力された周波数信号がD/A変換器22→作動増幅器14→A/D変換器15を経て位相検出部16に到達するまでの時間遅れが変動してしまう場合がある。このように時間遅れが変動すると、(2)式を用いて説明したVCO11側(ミキサ13)からの周波数信号とDDS21側からの周波数信号との位相差を性格に把握することが困難になり、PLL回路の制御精度を低下させてしまう。

【0033】

そこで本実施の形態に係る周波数シンセサイザには、位相補正部31及びレイテンシ調整部4の2種類の回路が設けられており、これによりD/A変換器22、作動増幅器14、A/D変換器15の各機器にて発生する時間遅れが精度よく相殺されように、検波信号の位相補正を行う構成となっている。

【0034】

本例では時間遅れが発生する既述の3つの回路(D/A変換器22、作動増幅器14、A/D変換器15)のうち、例えばD/A変換器22のレイテンシが立ち上がりの度に変動する場合について説明する。このとき位相補正部31は、作動増幅器14、A/D変換器15における一定時間の時間遅れ、及びD/A変換器22にて発生する時間遅れのうち、レイテンシ調整部4では調整しきれない短時間の時間遅れを調整するために、予め定められた補正量だけ検波信号の位相を補正する役割を果たしている。位相補正部31には、インバータやコンデンサを備えた周知のパルス遅延回路などが利用される。位相補正部31は本実施の形態の第1の位相補正部に相当する。

【0035】

一方、レイテンシ調整部4は、D/A変換器22におけるD/A変換に要する処理時間(変換時間)が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、検波信号が出力されるタイミングを遅らせると共に、この遅らせるタイミング(遅延量)を変化させることができる。レイテンシ調整部4は本実施の形態の第2の位相補正部に相当する。

【0036】

図3は、本実施の形態に係るレイテンシ調整部4の構成例を示している。レイテンシ調整部4は、例えば周知のシフトレジスタを備えており、システムクロック201からのクロック信号の入力タイミングに同期して、位相補正部31から入力された信号をクロック単位で遅らせて位相補正部16へと出力することができる。

【0037】

例えば図3に示したレイテンシ調整部4は、DDS21や位相補正部31から出力される検波信号のビット数に応じたデータを記憶可能な複数個、例えば3個のレジスタ部41a〜41cを直列に接続してなるシフトレジスタを備えている。各レジスタ部41a〜41cはシステムクロック201からのクロック信号を受け取ったタイミングで保持しているデータを後段へ出力することにより、検波信号の出力タイミングをクロック単位で遅らせて(位相を補正して)出力することができる。

【0038】

そして各レジスタ部41a〜41bからの出力は、切り替えスイッチ42との接続点S1〜S3側にも出力され、この切り替えスイッチ42の接続先を選択することによって位相検出部16に入力される検波信号の遅延量(位相の補正量)を変更することができる。また本例に係る切り替えスイッチ42には、位相補正部31からの出力タイミングを遅らせずにそのまま出力するための接点S0が設けられている。

【0039】

上述の構成を備えたレイテンシ調製部4にて最適な遅延量を求める手法について説明する。例えばDDS21から出力された周波数信号cos(ωt)がD/A変換器22→差動増幅器14→A/D変換器15を経て位相検出部16に入力されるまでに生じる時間遅れをΔt1とし、同じくDDS21から出力された検波信号sin(ωt)が位相補正部31→レイテンシ調整部4を経て位相検出部16に入力されるまでに行われる位相の補正量をΔt2とする。

【0040】

このとき差動増幅器14へのVCO11側(ミキサ13)からの周波数信号の入力を遮断し、当該差動増幅器14のゲインを1とすると、位相検出部16では以下の(3)式の演算が実行される。

sin(ω(t+Δt2))×cos(ω(t+Δt1))

=(1/2)sin(ω(2t+Δt2+Δt1))

+(1/2)sin(ω(Δt2−Δt1))…(3)

(3)式の演算結果においても交流成分を除去すれば、(1/2)sin(ω(Δt2−Δt1))に対応する信号が取り出され、Δt2の値がΔt1に近づくほど、(1/2)sin(ω(Δt2−Δt1))の値が0に近づくことになる。

【0041】

そこで図3に示したレイテンシ調整部4における切り替えスイッチ42の接続先を接点S0〜S3へと変更してΔt2を順次変化させ、(1/2)sin(ω(Δt2−Δt1))の値が0に最も近くなる接点を選択することにより、当該立ち上げ時におけるD/A変換器22の遅れ時間を相殺する、検波信号の位相の補正量を決定することができる。

【0042】

以上に説明した手法によるレイテンシ調整部4での遅延量の決定(以下、レイテンシ調整という)を実行可能とするため、本実施の形態の形態に係る周波数シンセサイザではレイテンシ調整実行時にVCO11側(ミキサ13)からの周波数信号の入力を遮断するためのスイッチ部5が設けられている。このスイッチ部5を開とすることにより、DDS21から出力された周波数信号がテスト用の信号として位相検出部16に入力されることになる。

【0043】

またVCO11側からの入力がなくなることにより、差動増幅器14からはアナログ変換されたDDS21の周波数信号がそのまま増幅されて出力されることになるが、差分を取っていない周波数信号を増幅して検波信号との直交検波を行うと、検波される信号同士の振幅の差が大きすぎて検波精度を低下させる要因となる。そこで例えばDDS21は、レイテンシ調整時にはその信号レベルを下げて周波数信号の出力を行うようになっている。

【0044】

また、位相検出部16の出力は例えばコンピュータ部20へと出力され、当該コンピュータ部20内にて交流成分を除去する処理が行われ、時間遅れΔt2と補正量Δt1との差を表すデータを記憶しておくことができる。またコンピュータ部20は、切り替えスイッチ42の各接点S0〜S3への切り替え状態と対応付けて前記Δt2とΔt1との差を表すデータを記憶し、当該データの絶対値が最小となる接点をそのときのレイテンシ調整動作における最適な補正量に対応する接点として選択することができる。

【0045】

以上の構成を備えたレイテンシ調整部4にて、最適な遅延量を決定する手法について図4、図5を参照しながら説明する。図4はレイテンシを調整する動作において、システムクロック201からのクロック信号に基づいて各回路に入出力される信号を示すタイミングチャートを簡略化して示したものである。各チャートは、上段から順に、クロック信号、差動増幅器14を経由して位相検出部16に入力される周波数信号、切り替えスイッチ42の各接点S0〜S3より位相検出部16に入力される検波信号、位相検出部16より出力される信号を示している。

【0046】

DDS21からは、例えばωt0〜ωt7の8クロックの間に、1周期分の周波数信号(cos(ωt1)〜cos(ωt7))及び検波信号(sin(ωt1)〜sin(ωt7))が繰り返し出力される。図示の便宜上、図5のDDS21の出力チャート中にはこれらの周波数信号、検波信号をまとめて「e^(jωt0)〜e^(jωt7)」と示してある。

【0047】

図4に示したチャートの例では、DDS21から出力された周波数信号は、差動増幅器14等を経由することにより、4クロック後に位相検出部16へと入力されている。一方、レイテンシ調整部での遅延量がゼロである接点S0からの出力は、DDS21出力の2クロック後に位相検出部16へと入力されている。このことから、本例では、位相補正部31では、クロック信号の2クロック分だけDDS21から出力された検波信号の位相を遅らせる補正が行われていることが分かる。そして、接点S1〜S3からは、位相補正部31にて位相補正された後の検波信号に対して、検波信号を出力するタイミングを1クロック単位ずつ遅らせた信号が出力されている。

【0048】

ここで今、図4中に示すタイミングにて、切り替えスイッチ42を接点S0に接続すると、位相検出部16では例えば周波数信号と検波信号とが入力されてから1クロック経過した後のタイミングで(3)式の演算を実行した結果がコンピュータ部20へ向けて出力される。また、図4中に、S1、S2、…と示すタイミングで切り替えスイッチ42の接点を切り替えた場合にも同様に周波数信号及び検波信号の入力タイミングの1クロック後に上述の演算結果が出力される。

【0049】

そこでコンピュータ部20では、切り替えスイッチ42の接点の切り替えタイミング及びその接続先と、位相検出部16より取得したデータとを対応付けて記憶しておくことにより、レイテンシ調整部4にて検波信号が送れて出力されるクロック数と周波数信号‐検波信号間の位相の一致度合い(既述の(1/2)sin(ω(Δt2−Δt1))との関係を把握することができる。

【0050】

図4によれば、例えば切り替えスイッチ42を接点S0(遅延量0クロック)に接続した直後の位相検出部16からの出力A3は「cos(ωt6)×(sin(ωt0))」となり、レイテンシ調整部4からの出力が2クロック分進んでいるので、周波数信号‐検波信号間の位相が一致した結果は得られない。一方、切り替えスイッチ42を接点S2(遅延量2クロック)に接続した直後の位相検出部16からの出力A3は「cos(ωt2)×(sin(ωt2))」となり、両信号の位相が一致していることを把握できる。

【0051】

図4では説明の便宜上、切り替えスイッチ42を2クロック毎に変更した場合を示しているが、実際には、例えば数百ミリ秒〜数秒程度ずつ、予め設定した時間ごとに切り替えスイッチ42の接続先の接点を例えばS0→S1→S2→S3と切り替えていく。この結果、コンピュータ部20では、図5に示すように「(1/2)sin(ω(Δt2−Δt1))」の値が時間軸に沿って各接点に対応付けて記憶される(図5中には絶対値で示してある)。そしてこの値が最も小さくなる接点が、今回の立ち上げ動作におけるD/A変換器22のレイテンシを相殺する遅延量に対応する接点として選択されることになる。

【0052】

以上に説明した構成を備えた周波数シンセサイザの作用について図6のフロー図を参照しながら説明する。周波数シンセサイザの立ち上げを開始し(スタート)その電源が投入されると(ステップS1)、レイテンシ調整部4の切り替えスイッチ42を接点S0に接続して検波信号の遅延量を「0クロック」に設定する(ステップS2)。また、スイッチ部5を開として、VCO11を差動増幅器14から切り離すと共に(ステップS3)、DDS21の周波数信号(及び検波信号)の周波数及び当該DDS21から作動増幅器14へ出力されるディジタル信号の信号レベルを各々予め定められた値に設定する(ステップS4)。ここで例えばDDS21から作動増幅器14へ出力されるディジタル信号の信号レベルは、通常運転時の20分の1のレベルに設定される一方、検波信号として位相補正部31へ出力されるディジタル信号は通常運転時のレベルに設定される。

【0053】

そしてDDS21より周波数信号及び検波信号の出力が開始されると(ステップS5)、位相検出部16より出力された演算結果がコンピュータ部20で処理され、周波数信号と検波信号との位相差を示すデータとして記憶される(ステップS6)。こうして予め設定した時間が経過したら、切り替えスイッチ42の接続先を切り替えて、レイテンシ調整部4の遅延量を1クロックだけインクリメントする(ステップS7)。

【0054】

その結果、遅延量が3クロックを超えていなければ(ステップS8;NO)、切り替えスイッチ42の切り替え先があることになるので、その状態で所定時間両信号の位相差を検出し、その結果を記憶してから(ステップS7)レイテンシ調整部4の遅延量を1クロック分だけインクリメントする動作を繰り返す(ステップS8)。そして、遅延量が3クロックを超えて4クロックとなり、これ以上、クロック数を増加させる接点がなくなったら(ステップS8;YES)、図4、図5を用いて説明した考え方に基づいて最適な遅延量を選択し、切り替えスイッチ42の接続先をこの遅延量に対応する接点に切り替える(ステップS9)。

【0055】

この結果、今回の立ち上げ動作におけるD/A変換器22のレイテンシを相殺する遅延量がレイテンシ調整部4にて選択されたことになるので、スイッチ部5を閉じて差動増幅器14をVCO11側に接続し、DDS21から作動増幅器14へ向けて出力されるディジタル信号の信号レベルを通常動作時のレベルに戻し(ステップS10)こうしてレイテンシの調整動作を終え(エンド)、PLL回路全体を作動させて周波数シンセサイザを立ち上げていく。

【0056】

この後の周波数シンセサイザの立ち上げ動作についても簡単に説明しておく。この例では周波数シンセサイザの各設定値設定周波数をfs=8755.5MHz、分周器12をN=104、ミキサ13の固定周波数信号fMIX=80MHzとする。また周波数シンセサイザは、不図示の周波数引き込み機構を備えており、その立ち上げ時においてVCO11の出力周波数を設定周波数の近傍まで引き込むことが可能となっている。

【0057】

周波数引き込み機構の作用によりVCO11の出力周波数が設定周波数の近傍まで引き込まれたら、PLL回路が作用し、VCO11からの出力は、分周器12にて1/104の周波数に分周され、ミキサ13にて固定周波数80MHzが乗算されてから、差動増幅器14へ向けて出力される。ここで、fVCO=fsとなった場合には、ミキサ13からは8755.5×106/104−80×106=4187500Hzの周波数信号が出力されることになる。

【0058】

一方、DDS21においては、出力周波数fDDSが上述の4187500Hzとなるようにコンピュータ部20からの設定がなされており、この出力周波数を持つ周波数信号が、D/A変換器22にて振幅調整された後、差動増幅器14に入力される。この結果、差動増幅器14からは、ミキサ13から出力されたVCO11側の周波数信号とDDS21側の周波数信号との差分を20倍に増幅した差分信号が出力され、この差分信号が位相検出部16にて直交検波されて両周波数信号の位相差Δθを検出するための演算がなされる。ここで既述のように周波数シンセサイザの立ち上げ時においてDDS21から位相検出部16へ入力される周波数信号と検波信号との位相が良好に一致していることにより、VCO11側の周波数信号との位相差Δθを精度よく検出することができる。

【0059】

そして位相検出部16からは既述の(2)式に示した信号が出力されてフィルタ17にて当該位相差に対応する信号「−(20/2)sin(Δθ)」が取り出さる。フィルタ17で取り出された信号は、積分回路18にて積分、加算されD/A変換器19にてアナログデータに変換された後、制御電圧としてVCO11に印加される。このPLL回路により「−(20/2)sin(Δθ)=0」、即ちΔθ=0となるようにループ制御が実行され、Δθ=0となったときVCO11の出力周波数fVCOが設定周波数fsにロックされると共に、ミキサ13から出力される周波数信号がDDS21からの出力に同期した状態となる。

【0060】

以上に説明した周波数シンセサイザによれば、以下の効果がある。周波数シンセサイザは、VCO11から出力された周波数信号との位相差を検出するために、DDS21から出力される周波数信号と、この周波数信号の位相を90°ずらした検波信号とが異なる経路を通って位相検出部16に入力されて直交検波に利用される際に、これら2つの信号が位相検出部に入力されるタイミングをそろえるための位相補正部31とレイテンシ調整部4とを備えている。そして位相補正部31は予め定めた量だけ前記検波信号の位相を補正する一方、レイテンシ調整部4は検波信号を出力するタイミングをクロック単位で遅らせることができる。この結果、DDS21から出力された周波数信号が通る経路に設けられているD/A変換器22の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる場合であっても、この立ち上げ時間の変化に応じて検波信号の出力タイミングを遅らせ、DDS21から同時に出力された周波数信号−検波信号間の位相差を小さくすることができるので、VCO11及びDDS21の各々の周波数信号の位相差を正確に把握して精度の高い周波数調整を行うことができる。

【0061】

ここで検波信号を補正する順序は図1に示したように位相補正部31→レイテンシ調整部4の順に行う場合に限られず、この順番を入れ替えてもよい。また本例では周波数シンセサイザを立ち上げるたびに処理の時間が変換する回路の例としてD/A変換部22を挙げたが、このほか差動増幅器14やその後段のA/D変換器15にて同様の現象が発生する場合にも、検波信号に対して予め設定した補正量だけ位相の補正を行う位相補正部31と、検波信号をクロック単位で遅らせて出力することにより位相の補正を行うレイテンシ調整部4とを組み合わせることにより、前記現象の発生に伴う不都合を解消することができる。

【0062】

また、レイテンシ調整部4を構成するシフトレジスタ内に設けるレジスタ部の数は、図3に示した3個の例に限定されず、調整量の異なる接続点が2つ以上設けられていれば3個より少なくてもよいし、多くてもよい。さらにはレジスタ部を通らない接点S0は設けなくてもよい。このほか、最適な調整量はコンピュータ部20を利用して決定する場合に限定されず、位相検出部から出力された信号に基づいて、例えば手動で切り替えスイッチ42の接続点を切り替えてもよい。さらに、レイテンシ調整部4は図3に示すようにシフトレジスタを用いる場合に限定されず、例えば遅延素子などを利用してもよい。

【0063】

そしてレイテンシ調整時にVOC11側からの周波数信号の入力を遮断するスイッチ部は、図1に示すように回路中に当該スイッチ部5を物理的に設ける場合に限定されない。例えばコンピュータ部20からの指示に基づいて分周器12の出力を停止することができるように構成し、レイテンシ調整時にはこの分周器12からの出力を停止することにより、VOC11側から作動増幅器14への周波数信号の入力を遮断してもよい。この場合には、分周器12がスイッチ部としての役割も果たしていることになる。

【0064】

またレイテンシ調整の際に、DDS21から作動増幅器14へ出力される周波数信号の出力レベルを通常使用時に比べて小さくする手法に代えて、差動増幅器14側のゲインを小さくしてもよい。例えば差動増幅器14はコンピュータ部20からの制御によるゲインの変更を可能とし、周波数シンセサイザの通常運転時にはそのゲインを20倍とする一方、レイテンシ調整時には位相検出部16に入力される周波数信号と検波信号との振幅をほぼ一致させるため、差動増幅器14のゲインを1倍とするように、ゲインを切り替える構成とする場合などが考えられる。

【符号の説明】

【0065】

11 電圧制御発振器(VCO)

14 差動増幅器

15 A/D変換器

16 位相検出部

20 コンピュータ部

21 DDS

22 D/A変換器

31 位相補正部

4 レイテンシ調整部

41a〜41c

レジスタ部

42 切り替えスイッチ

5 スイッチ部

【技術分野】

【0001】

本発明は、周波数シンセサイザに関する。

【背景技術】

【0002】

周波数シンセサイザとして、電圧制御発振器の出力信号をA/D変換(アナログ/ディジタル変換)し、得られたディジタル信号を処理して処理結果を電圧制御発振器に入力し、これによりPLL(Phase Locked Loop)を形成するものが知られている。例えば特許文献1には、電圧制御発振器の出力信号をA/D変換(アナログ/ディジタル変換)し、そのディジタル信号により作成される正弦波信号を直交検波して当該正弦波信号と検波に用いた正弦波信号との差分周波数で回転する回転ベクトルを取り出し、この回転ベクトルと、当該回転ベクトルとは逆に回転しかつ設定周波数に対応する周波数で回転する回転ベクトルと、の差分速度を積分して電圧制御発振器の入力電圧とする周波数シンセサイザが記載されている。

しかしながらPLL中に位相雑音が存在し、このため周波数シンセサイザの出力に位相雑音が発生するという課題がある。

【0003】

そこで本件出願人は、こうした位相雑音の問題を解決すべく、電圧制御発振部(Voltage Controlled Oscillator;以下、VCOという)からのアナログ周波数信号と、ダイレクト・ディジタルシンセサイザ(Direct Digital Synthesizer:以下、DDSという)などのディジタル周波数発振部から出力されるディジタル周波数信号をディジタル/アナログ変換(D/A変換)して得られた信号との差分を取って増幅し、この増幅された差分信号をA/D変換してから検波信号により直交検波して、両周波数信号の位相差を取り出して積分し、この積分値に応じた電圧を前記電圧制御発振部に供給することによりアナログ周波数信号の周波数を調整する新型のPLLを開発している。

【0004】

差動増幅器にて差分を取ってから出力信号を増幅することにより、信号をアナログ/ディジタル変換する際に発生する量子化誤差を、差分信号の振幅に対して相対的に低く抑えることができるので、こうした量子化誤差などに起因する位相雑音を改善することができる。

ここで差分信号と直交検波される検波信号には、DDSから出力されたディジタル周波数信号の位相を90°だけずらした信号を用いており、この検波信号と差分信号中のDDSから出力された周波数信号成分とが直交していることにより、アナログ周波数信号側の位相のずれを正確に取り出すことができる。

【0005】

ところがディジタル化された差分信号を得るために用いられるD/A変換器などの回路のなかには、回路を立ち上げる度に当該回路に信号を入力してから演算結果が出力されるまでの時間(以下レイテンシという)が変動してしまうものがあることが分かった。このようにレイテンシが変動してしまうと、正確な直交検波を実行できなくなり、VCOの周波数調整の精度が低下してしまうという問題がある。

【0006】

ここで特許文献2には、周波数信号などの標本再生信号を、VCOから出力されるサンプルクロックに同期してサンプリングし、サンプリング値を目標値と比較することによりサンプルクロックと目標クロックの位相差を誤差補正回路にて検出し、この位相差をVCOにフィードバックしてサンプリングクロックの周波数を調節する従来型のPLLにおいて、VCOと誤差補正回路との間に可変式の遅延回路を設ける技術が記載されている。この遅延回路には、後段の誤差補正回路にて検出された位相差がフィードバックされ、位相差の大きさに応じて遅延量を増減することにより、PLLの立ち上げ初期の位相差をキャンセルし、短時間でサンプルクロックを目標クロックに同期させることができるようになっているが、PLL内の回路が持つレイテンシの変動の影響を解消する手法については何ら開示されていない。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−74291号公報:請求項1、段落0017〜段落0021、図1

【特許文献2】特開平11−214990:請求項1、段落0023〜段落0025、図6

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明はこのような事情の下になされたものであり、その目的は、精度の高い周波数調整が可能であると共に、安定して作動する周波数シンセサイザ及び周波数シンセサイザの調整方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明に係る周波数シンセサイザは、電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給する周波数シンセサイザであって、

前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、

前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号中に含まれる周波数設定部由来の周波数信号が前記位相検出部に入力されるまでのタイミングと、前記出力された時点から検波信号が前記位相検出部に入力されるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、

前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、

前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力し、前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する制御部と、を備えたことを特徴とする。

【0010】

前記周波数シンセサイザは、以下の特徴を備えていてもよい。

(a)前記制御部は、前記差動増幅器に前記テスト用の周波数信号を入力するときには、当該差動増幅器の差動利得、または前記周波数設定部から出力されるディジタルの周波数信号の信号レベルを通常使用時に比べて小さくすること。

(b)前記第2の位相補正部は、シフトレジスタにより構成されていること。

(c)前記周波数設定部は、ダイレクト・ディジタル・シンセサイザであること。

【0011】

また、他の発明に係る周波数シンセサイザの調整方法は、電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給し、前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、前記出力された時点から検波信号が得られるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、を備えた周波数シンセサイザの調整方法であって、

この周波数シンセサイザの立ち上げ時に、前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力する工程と、

前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する工程と、を含むことを特徴とする。

【発明の効果】

【0012】

本発明の周波数シンセサイザは、電圧制御発振部から出力された周波数信号との位相差を検出するために、周波数設定部から出力される周波数信号と、この周波数信号の位相を90°ずらした検波信号とが異なる経路を通って位相検出部に入力されて直交検波に利用される際に、これら2つの信号が位相検出部に入力されるタイミングをそろえるための第1の位相補正部と第2の位相補正部とを備えている。そして第1の位相補正部は予め定めた量だけ前記検波信号の位相を補正する一方、第2の位相補正部は検波信号を出力するタイミングをクロック単位で遅らせることができる。この結果、周波数設定部から出力された周波数信号が通る経路に設けられているディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる場合であっても、この変換時間の変化に応じて検波信号の出力タイミングを遅らせ、周波数設定部から同時に出力された周波数信号−検波信号間の位相差を小さくすることができるので、電圧制御発振部及び周波数設定部の各々の周波数信号の位相差を正確に把握して精度の高い周波数調整を行うことができる。

【図面の簡単な説明】

【0013】

【図1】実施の形態に係る周波数シンセサイザのブロック図である。

【図2】前記周波数シンセサイザに設けられている積分回路の構成図である。

【図3】前記周波数シンセサイザに設けられているレイテンシ調整部の構成図である。

【図4】前記立ち上げ時における周波数シンセサイザの動作を示すタイミングチャートである。

【図5】前記立ち上げ時において位相検出部から出力される信号の強度を模式的に示す説明図である。

【図6】前記周波数シンセサイザの立ち上げ時の動作の流れを示すフロー図である。

【発明を実施するための形態】

【0014】

以下、図1に示したブロック図を参照しながら、本実施の形態に係る周波数シンセサイザの構成について説明する。本例に係る周波数シンセサイザは、電圧制御発振部であるVCO11から出力された周波数信号を帰還信号として、DDS21(Direct Digital Synthesizer)から出力された周波数信号との位相比較を行い、これらの周波数の位相差に対応する電圧を積分して、VCO11の入力側に供給するPLL(Phased Lock Loop)回路を形成している。これらの信号の周波数差がゼロになったときにPLLがロックされ、VCO11の出力周波数が設定周波数にロックされることになる。このDDS21は特許請求の範囲の周波数設定部に相当する。

【0015】

図1中VCO11は、供給電圧に応じた周波数fVCOの正弦波であるアナログの周波数信号を出力する役割を果たす。VCO11の後段に設けられた分周器12は、VCO11から出力された周波数信号を1/N(Nは整数)に分周して、その周波数を(fVCO/N)とする機能を有する。

【0016】

ミキサ13は、分周器12から出力された周波数信号に、周波数fMIXの固定周波数信号を乗算し、ヘテロダインの原理により得られる「(fVCO/N)±fMIX」の2つの周波数を持つ信号のうち、低周波数「(fVCO/N)―fMIX」の信号を取り出すことができる。ミキサ13から出力された周波数信号は、後段の差動増幅器14に入力される。

【0017】

差動増幅器14には、VCO11側からの周波数信号に加えて、この信号と位相比較を行うための周波数信号がDDS21側より入力されるので、先にDDS21についての説明を行う。DDS21は、不図示の波形テーブルに例えば正弦波の振幅データを位相データに対応付けて記憶しており、後述のシステムクロック201からのクロック信号の入力タイミング毎に予め設定された位相幅データを累積加算して得た位相データに基づいて振幅データを読み出すことにより、設定された周波数のディジタルの周波数信号を出力する機能を備えている。システムクロック201の基準となるクロックの発生源は、例えば水晶発振器などから構成される。

【0018】

DDS21では、位相幅データの値を大きくすることにより、波形テーブルに記憶されている波形データが位相幅データの大きさに応じて読み飛ばされ、これによって周波数を調整している。即ち、位相幅データの値を大きくするほど周波数の高い信号を出力することができる。本例におけるDDS21は例えばcos(ωt)(ωは角速度[rad/秒])の周波数信号と、当該周波数信号の位相を90°ずらした検波信号sin(ωt)とを同時に出力することができる。またDDS21は、これら周波数信号及び検波信号の信号レベル(信号強度)を各々独立して増減することができる。但し後述するように、DDS21からの周波数信号のレベルの調整は、D/A変換器22により行ってもよい。

【0019】

本例では、例えば周波数シンセサイザの制御部をなすコンピュータ部20からDDS21に対して、設定周波数を決定する位相幅データの設定が行われる。例えば周波数シンセサイザの設定周波数をfsとしたとき、DDS21から出力される信号の周波数fDDSは、VCO11から出力される周波数信号が設定周波数にロックされたときに、ミキサ13から出力される信号の周波数「(fS/N)―fMIX」と一致するように設定され、この値に基づいて前記位相幅データが設定される。DDS21から出力された周波数信号は、D/A変換器22を介してアナログの周波数信号に変換され、既述の差動増幅器14に入力されることになる。このD/A変換器22は特許請求の範囲のディジタル/アナログ変換部に相当する。

【0020】

差動増幅器14はVCO11側のミキサ13から入力された周波数信号とDDS21側から入力された周波数信号との差分値を算出し、この結果を増幅してから後段のA/D変換器15へと出力する役割を果たす。このように差動増幅器14を設け、VCO11、DDS21の双方から出力される周波数信号の差分をとって増幅した差分信号を出力することにより、後段のA/D変換器15でのアナログ信号からのディジタル信号のサンプリング時に当該信号を所定のビット数に丸める際に発生する位相雑音の発生を低減している。

【0021】

本発明者は、A/D変換器における位相雑音劣化のない理想的な周波数シンセサイザのシミュレーション結果と実際の周波数シンセサイザの出力とを比較することにより、A/D変換器における位相雑音の劣化量は最大で10dB程度の大きさであることを把握している。そこで差動増幅器14は、2つの周波数信号の差分値を10dB以上の例えば26dB増幅する(20倍に増幅する)ことにより、A/D変換器15にて発生する位相雑音の劣化をキャンセル(相殺)できることが実証的に確認されており、本実施の形態に係る周波数シンセサイザはこのような考え方に基づいて差動増幅器14を備えた構成となっている。

【0022】

既述のようにDDS21から出力される周波数信号をcos(ωt)とし、VCO11側からのミキサ13出口の周波数信号はcos(ω’t)(ω’は角速度[rad/秒])としたとき、VCO11の出力周波数fVCOが設定周波数fsに十分に近づきPLLがロックされる直前の状態においては、ω≒ω’=ω+Δω(Δω≪1)となるのでミキサ13出口の周波数信号はcos(ωt+Δωt)と表現できる。Δω≪1の条件下では、Δωtの値は時間的に殆ど変化しないので、位相のずれΔθと表すことができる。

【0023】

即ち、PLLがロックされる直前の状態においては、DDS21側から差動増幅器14に入力される周波数信号をcos(ωt)、ミキサ13から差動増幅器14に入力される周波数信号をcos(ωt+Δθ)と表すことができ、差動増幅器14からは、以下の(1)式で表される周波数信号が出力されることになる。

20{cos(ωt+Δθ)−cos(ωt)} …(1)

【0024】

差動増幅器14の後段に設けられたA/D変換器15は、当該(1)式で表される信号をディジタル信号に変換する役割を果たすが、DDS21から出力された周波数信号は、D/A変換器22にてアナログ変換される際に時間遅れを生じ、また差動増幅器14にて差分信号を取得し、この差分信号をA/D変換器15でディジタル信号に変換する際にも処理に伴う時間遅れを生ずる。この時間遅れをΔtで表し、t’=t+Δtとすると、A/D変換器15からの出力信号は下記の(1)’式で表すことができる。ここで、ミキサ13出力に対するD/A変換器22の処理に起因する時間遅れは、両周波数信号の位相差Δθに含めることができる。

20{cos(ωt’+Δθ)−cos(ωt’)} …(1)’

【0025】

そしてA/D変換器15の後段には、2つの周波数信号の位相差Δθを検出するための直交検波部である位相検出部16が設けられている。位相検出部16は、(1)’式で表される前段のA/D変換器15からの出力信号に、当該(1)’式に含まれるcos(ωt’)と直交する検波信号sin(ωt’)を乗じて、位相差成分を取り出すための前処理を行う機能を備えている。

【0026】

既述のようにDDS21からは、差動増幅器14に入力される周波数信号(cos(ωt))とこれに直交する検波信号(sin(ωt))とを並行して出力することができる。この検波信号に対して、D/A変換器22、差動増幅器14及びA/D変換器15において発生する時間遅れΔtを相殺する位相補正が位相補正部31及びレイテンシ調整部4にて行われ、こうして位相補正された検波信号sin(ωt’)が位相検出部16へと入力される。位相検出部16にて実行される演算を整理すると、下記(2)式で表される出力が得られる。

sin(ωt’)

×[20{cos(ωt’+Δθ)−cos(ωt’)}]

=(20/2)sin(2ωt’+Δθ)+(20/2)sin(−Δθ)

+(20/2)sin(2ωt’)…(2)

【0027】

位相検出部16の後段には、フィルタ17が設けられており(2)式で表される位相検出部16の出力から交流成分を除去して、直流成分である(20/2)sin(−Δθ)=−(20/2)sin(Δθ)を取り出すことにより、VCO11側及びDDS21側の2つの周波数信号の位相差を知ることができる。

【0028】

積分回路18は、本例の周波数シンセサイザを構成するPLL回路のループフィルタに相当し、フィルタ17にて検出した位相差に対応する信号「−(20/2)sin(Δθ)」にPLL回路のループゲインを調整するための係数を乗算し、その信号を積分系と直接系とに分けた後に加算する構成となっている。

【0029】

図2は、積分回路18の構成例を示しており、図中181は入力信号に調整係数を乗ずる乗算部、182は乗算後の信号を累積加算する累積加算部、183は乗算後の信号(直接系)と累積加算部182からの出力信号(積分系)とを加算する加算部である。積分回路18は、入力された「−(20/2)sin(Δθ)」の値がゼロとなるように、PLL回路のループ制御を実行する役割を果たす。

【0030】

積分回路18の後段にはD/A変換器19が設けられており、積分回路18からの出力がアナログ信号に変換されて、D/A変換器19の出力がVCO11に制御電圧として入力され、PLL回路による周波数調整を実行することができる。

【0031】

ここで図1に示した32は、差動増幅器14に入力されるDDS側の周波数信号と、ミキサ13側からの周波数信号との振幅をそろえるために、差動増幅器14からの周波数信号と、DDS21からの周波数信号(cos(ωt’):位相補正部31及びレイテンシ調整部4にて時間遅れΔtの調整済み)とに基づいてD/A変換器22より出力されるアナログ信号の振幅を調整するための振幅調整部である。

【0032】

ここで先に説明したように、位相補正部31及びレイテンシ調整部4は、D/A変換器22、差動増幅器14及びその後段のA/D変換器15の処理にて発生するの時間遅れを補正する役割を果たしている。ところが背景技術で説明したようにこれらの機器のなかには回路を立ち上げる度に処理時間(レイテンシ)が変動し、その結果、DDS21から出力された周波数信号がD/A変換器22→作動増幅器14→A/D変換器15を経て位相検出部16に到達するまでの時間遅れが変動してしまう場合がある。このように時間遅れが変動すると、(2)式を用いて説明したVCO11側(ミキサ13)からの周波数信号とDDS21側からの周波数信号との位相差を性格に把握することが困難になり、PLL回路の制御精度を低下させてしまう。

【0033】

そこで本実施の形態に係る周波数シンセサイザには、位相補正部31及びレイテンシ調整部4の2種類の回路が設けられており、これによりD/A変換器22、作動増幅器14、A/D変換器15の各機器にて発生する時間遅れが精度よく相殺されように、検波信号の位相補正を行う構成となっている。

【0034】

本例では時間遅れが発生する既述の3つの回路(D/A変換器22、作動増幅器14、A/D変換器15)のうち、例えばD/A変換器22のレイテンシが立ち上がりの度に変動する場合について説明する。このとき位相補正部31は、作動増幅器14、A/D変換器15における一定時間の時間遅れ、及びD/A変換器22にて発生する時間遅れのうち、レイテンシ調整部4では調整しきれない短時間の時間遅れを調整するために、予め定められた補正量だけ検波信号の位相を補正する役割を果たしている。位相補正部31には、インバータやコンデンサを備えた周知のパルス遅延回路などが利用される。位相補正部31は本実施の形態の第1の位相補正部に相当する。

【0035】

一方、レイテンシ調整部4は、D/A変換器22におけるD/A変換に要する処理時間(変換時間)が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、検波信号が出力されるタイミングを遅らせると共に、この遅らせるタイミング(遅延量)を変化させることができる。レイテンシ調整部4は本実施の形態の第2の位相補正部に相当する。

【0036】

図3は、本実施の形態に係るレイテンシ調整部4の構成例を示している。レイテンシ調整部4は、例えば周知のシフトレジスタを備えており、システムクロック201からのクロック信号の入力タイミングに同期して、位相補正部31から入力された信号をクロック単位で遅らせて位相補正部16へと出力することができる。

【0037】

例えば図3に示したレイテンシ調整部4は、DDS21や位相補正部31から出力される検波信号のビット数に応じたデータを記憶可能な複数個、例えば3個のレジスタ部41a〜41cを直列に接続してなるシフトレジスタを備えている。各レジスタ部41a〜41cはシステムクロック201からのクロック信号を受け取ったタイミングで保持しているデータを後段へ出力することにより、検波信号の出力タイミングをクロック単位で遅らせて(位相を補正して)出力することができる。

【0038】

そして各レジスタ部41a〜41bからの出力は、切り替えスイッチ42との接続点S1〜S3側にも出力され、この切り替えスイッチ42の接続先を選択することによって位相検出部16に入力される検波信号の遅延量(位相の補正量)を変更することができる。また本例に係る切り替えスイッチ42には、位相補正部31からの出力タイミングを遅らせずにそのまま出力するための接点S0が設けられている。

【0039】

上述の構成を備えたレイテンシ調製部4にて最適な遅延量を求める手法について説明する。例えばDDS21から出力された周波数信号cos(ωt)がD/A変換器22→差動増幅器14→A/D変換器15を経て位相検出部16に入力されるまでに生じる時間遅れをΔt1とし、同じくDDS21から出力された検波信号sin(ωt)が位相補正部31→レイテンシ調整部4を経て位相検出部16に入力されるまでに行われる位相の補正量をΔt2とする。

【0040】

このとき差動増幅器14へのVCO11側(ミキサ13)からの周波数信号の入力を遮断し、当該差動増幅器14のゲインを1とすると、位相検出部16では以下の(3)式の演算が実行される。

sin(ω(t+Δt2))×cos(ω(t+Δt1))

=(1/2)sin(ω(2t+Δt2+Δt1))

+(1/2)sin(ω(Δt2−Δt1))…(3)

(3)式の演算結果においても交流成分を除去すれば、(1/2)sin(ω(Δt2−Δt1))に対応する信号が取り出され、Δt2の値がΔt1に近づくほど、(1/2)sin(ω(Δt2−Δt1))の値が0に近づくことになる。

【0041】

そこで図3に示したレイテンシ調整部4における切り替えスイッチ42の接続先を接点S0〜S3へと変更してΔt2を順次変化させ、(1/2)sin(ω(Δt2−Δt1))の値が0に最も近くなる接点を選択することにより、当該立ち上げ時におけるD/A変換器22の遅れ時間を相殺する、検波信号の位相の補正量を決定することができる。

【0042】

以上に説明した手法によるレイテンシ調整部4での遅延量の決定(以下、レイテンシ調整という)を実行可能とするため、本実施の形態の形態に係る周波数シンセサイザではレイテンシ調整実行時にVCO11側(ミキサ13)からの周波数信号の入力を遮断するためのスイッチ部5が設けられている。このスイッチ部5を開とすることにより、DDS21から出力された周波数信号がテスト用の信号として位相検出部16に入力されることになる。

【0043】

またVCO11側からの入力がなくなることにより、差動増幅器14からはアナログ変換されたDDS21の周波数信号がそのまま増幅されて出力されることになるが、差分を取っていない周波数信号を増幅して検波信号との直交検波を行うと、検波される信号同士の振幅の差が大きすぎて検波精度を低下させる要因となる。そこで例えばDDS21は、レイテンシ調整時にはその信号レベルを下げて周波数信号の出力を行うようになっている。

【0044】

また、位相検出部16の出力は例えばコンピュータ部20へと出力され、当該コンピュータ部20内にて交流成分を除去する処理が行われ、時間遅れΔt2と補正量Δt1との差を表すデータを記憶しておくことができる。またコンピュータ部20は、切り替えスイッチ42の各接点S0〜S3への切り替え状態と対応付けて前記Δt2とΔt1との差を表すデータを記憶し、当該データの絶対値が最小となる接点をそのときのレイテンシ調整動作における最適な補正量に対応する接点として選択することができる。

【0045】

以上の構成を備えたレイテンシ調整部4にて、最適な遅延量を決定する手法について図4、図5を参照しながら説明する。図4はレイテンシを調整する動作において、システムクロック201からのクロック信号に基づいて各回路に入出力される信号を示すタイミングチャートを簡略化して示したものである。各チャートは、上段から順に、クロック信号、差動増幅器14を経由して位相検出部16に入力される周波数信号、切り替えスイッチ42の各接点S0〜S3より位相検出部16に入力される検波信号、位相検出部16より出力される信号を示している。

【0046】

DDS21からは、例えばωt0〜ωt7の8クロックの間に、1周期分の周波数信号(cos(ωt1)〜cos(ωt7))及び検波信号(sin(ωt1)〜sin(ωt7))が繰り返し出力される。図示の便宜上、図5のDDS21の出力チャート中にはこれらの周波数信号、検波信号をまとめて「e^(jωt0)〜e^(jωt7)」と示してある。

【0047】

図4に示したチャートの例では、DDS21から出力された周波数信号は、差動増幅器14等を経由することにより、4クロック後に位相検出部16へと入力されている。一方、レイテンシ調整部での遅延量がゼロである接点S0からの出力は、DDS21出力の2クロック後に位相検出部16へと入力されている。このことから、本例では、位相補正部31では、クロック信号の2クロック分だけDDS21から出力された検波信号の位相を遅らせる補正が行われていることが分かる。そして、接点S1〜S3からは、位相補正部31にて位相補正された後の検波信号に対して、検波信号を出力するタイミングを1クロック単位ずつ遅らせた信号が出力されている。

【0048】

ここで今、図4中に示すタイミングにて、切り替えスイッチ42を接点S0に接続すると、位相検出部16では例えば周波数信号と検波信号とが入力されてから1クロック経過した後のタイミングで(3)式の演算を実行した結果がコンピュータ部20へ向けて出力される。また、図4中に、S1、S2、…と示すタイミングで切り替えスイッチ42の接点を切り替えた場合にも同様に周波数信号及び検波信号の入力タイミングの1クロック後に上述の演算結果が出力される。

【0049】

そこでコンピュータ部20では、切り替えスイッチ42の接点の切り替えタイミング及びその接続先と、位相検出部16より取得したデータとを対応付けて記憶しておくことにより、レイテンシ調整部4にて検波信号が送れて出力されるクロック数と周波数信号‐検波信号間の位相の一致度合い(既述の(1/2)sin(ω(Δt2−Δt1))との関係を把握することができる。

【0050】

図4によれば、例えば切り替えスイッチ42を接点S0(遅延量0クロック)に接続した直後の位相検出部16からの出力A3は「cos(ωt6)×(sin(ωt0))」となり、レイテンシ調整部4からの出力が2クロック分進んでいるので、周波数信号‐検波信号間の位相が一致した結果は得られない。一方、切り替えスイッチ42を接点S2(遅延量2クロック)に接続した直後の位相検出部16からの出力A3は「cos(ωt2)×(sin(ωt2))」となり、両信号の位相が一致していることを把握できる。

【0051】

図4では説明の便宜上、切り替えスイッチ42を2クロック毎に変更した場合を示しているが、実際には、例えば数百ミリ秒〜数秒程度ずつ、予め設定した時間ごとに切り替えスイッチ42の接続先の接点を例えばS0→S1→S2→S3と切り替えていく。この結果、コンピュータ部20では、図5に示すように「(1/2)sin(ω(Δt2−Δt1))」の値が時間軸に沿って各接点に対応付けて記憶される(図5中には絶対値で示してある)。そしてこの値が最も小さくなる接点が、今回の立ち上げ動作におけるD/A変換器22のレイテンシを相殺する遅延量に対応する接点として選択されることになる。

【0052】

以上に説明した構成を備えた周波数シンセサイザの作用について図6のフロー図を参照しながら説明する。周波数シンセサイザの立ち上げを開始し(スタート)その電源が投入されると(ステップS1)、レイテンシ調整部4の切り替えスイッチ42を接点S0に接続して検波信号の遅延量を「0クロック」に設定する(ステップS2)。また、スイッチ部5を開として、VCO11を差動増幅器14から切り離すと共に(ステップS3)、DDS21の周波数信号(及び検波信号)の周波数及び当該DDS21から作動増幅器14へ出力されるディジタル信号の信号レベルを各々予め定められた値に設定する(ステップS4)。ここで例えばDDS21から作動増幅器14へ出力されるディジタル信号の信号レベルは、通常運転時の20分の1のレベルに設定される一方、検波信号として位相補正部31へ出力されるディジタル信号は通常運転時のレベルに設定される。

【0053】

そしてDDS21より周波数信号及び検波信号の出力が開始されると(ステップS5)、位相検出部16より出力された演算結果がコンピュータ部20で処理され、周波数信号と検波信号との位相差を示すデータとして記憶される(ステップS6)。こうして予め設定した時間が経過したら、切り替えスイッチ42の接続先を切り替えて、レイテンシ調整部4の遅延量を1クロックだけインクリメントする(ステップS7)。

【0054】

その結果、遅延量が3クロックを超えていなければ(ステップS8;NO)、切り替えスイッチ42の切り替え先があることになるので、その状態で所定時間両信号の位相差を検出し、その結果を記憶してから(ステップS7)レイテンシ調整部4の遅延量を1クロック分だけインクリメントする動作を繰り返す(ステップS8)。そして、遅延量が3クロックを超えて4クロックとなり、これ以上、クロック数を増加させる接点がなくなったら(ステップS8;YES)、図4、図5を用いて説明した考え方に基づいて最適な遅延量を選択し、切り替えスイッチ42の接続先をこの遅延量に対応する接点に切り替える(ステップS9)。

【0055】

この結果、今回の立ち上げ動作におけるD/A変換器22のレイテンシを相殺する遅延量がレイテンシ調整部4にて選択されたことになるので、スイッチ部5を閉じて差動増幅器14をVCO11側に接続し、DDS21から作動増幅器14へ向けて出力されるディジタル信号の信号レベルを通常動作時のレベルに戻し(ステップS10)こうしてレイテンシの調整動作を終え(エンド)、PLL回路全体を作動させて周波数シンセサイザを立ち上げていく。

【0056】

この後の周波数シンセサイザの立ち上げ動作についても簡単に説明しておく。この例では周波数シンセサイザの各設定値設定周波数をfs=8755.5MHz、分周器12をN=104、ミキサ13の固定周波数信号fMIX=80MHzとする。また周波数シンセサイザは、不図示の周波数引き込み機構を備えており、その立ち上げ時においてVCO11の出力周波数を設定周波数の近傍まで引き込むことが可能となっている。

【0057】

周波数引き込み機構の作用によりVCO11の出力周波数が設定周波数の近傍まで引き込まれたら、PLL回路が作用し、VCO11からの出力は、分周器12にて1/104の周波数に分周され、ミキサ13にて固定周波数80MHzが乗算されてから、差動増幅器14へ向けて出力される。ここで、fVCO=fsとなった場合には、ミキサ13からは8755.5×106/104−80×106=4187500Hzの周波数信号が出力されることになる。

【0058】

一方、DDS21においては、出力周波数fDDSが上述の4187500Hzとなるようにコンピュータ部20からの設定がなされており、この出力周波数を持つ周波数信号が、D/A変換器22にて振幅調整された後、差動増幅器14に入力される。この結果、差動増幅器14からは、ミキサ13から出力されたVCO11側の周波数信号とDDS21側の周波数信号との差分を20倍に増幅した差分信号が出力され、この差分信号が位相検出部16にて直交検波されて両周波数信号の位相差Δθを検出するための演算がなされる。ここで既述のように周波数シンセサイザの立ち上げ時においてDDS21から位相検出部16へ入力される周波数信号と検波信号との位相が良好に一致していることにより、VCO11側の周波数信号との位相差Δθを精度よく検出することができる。

【0059】

そして位相検出部16からは既述の(2)式に示した信号が出力されてフィルタ17にて当該位相差に対応する信号「−(20/2)sin(Δθ)」が取り出さる。フィルタ17で取り出された信号は、積分回路18にて積分、加算されD/A変換器19にてアナログデータに変換された後、制御電圧としてVCO11に印加される。このPLL回路により「−(20/2)sin(Δθ)=0」、即ちΔθ=0となるようにループ制御が実行され、Δθ=0となったときVCO11の出力周波数fVCOが設定周波数fsにロックされると共に、ミキサ13から出力される周波数信号がDDS21からの出力に同期した状態となる。

【0060】

以上に説明した周波数シンセサイザによれば、以下の効果がある。周波数シンセサイザは、VCO11から出力された周波数信号との位相差を検出するために、DDS21から出力される周波数信号と、この周波数信号の位相を90°ずらした検波信号とが異なる経路を通って位相検出部16に入力されて直交検波に利用される際に、これら2つの信号が位相検出部に入力されるタイミングをそろえるための位相補正部31とレイテンシ調整部4とを備えている。そして位相補正部31は予め定めた量だけ前記検波信号の位相を補正する一方、レイテンシ調整部4は検波信号を出力するタイミングをクロック単位で遅らせることができる。この結果、DDS21から出力された周波数信号が通る経路に設けられているD/A変換器22の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる場合であっても、この立ち上げ時間の変化に応じて検波信号の出力タイミングを遅らせ、DDS21から同時に出力された周波数信号−検波信号間の位相差を小さくすることができるので、VCO11及びDDS21の各々の周波数信号の位相差を正確に把握して精度の高い周波数調整を行うことができる。

【0061】

ここで検波信号を補正する順序は図1に示したように位相補正部31→レイテンシ調整部4の順に行う場合に限られず、この順番を入れ替えてもよい。また本例では周波数シンセサイザを立ち上げるたびに処理の時間が変換する回路の例としてD/A変換部22を挙げたが、このほか差動増幅器14やその後段のA/D変換器15にて同様の現象が発生する場合にも、検波信号に対して予め設定した補正量だけ位相の補正を行う位相補正部31と、検波信号をクロック単位で遅らせて出力することにより位相の補正を行うレイテンシ調整部4とを組み合わせることにより、前記現象の発生に伴う不都合を解消することができる。

【0062】

また、レイテンシ調整部4を構成するシフトレジスタ内に設けるレジスタ部の数は、図3に示した3個の例に限定されず、調整量の異なる接続点が2つ以上設けられていれば3個より少なくてもよいし、多くてもよい。さらにはレジスタ部を通らない接点S0は設けなくてもよい。このほか、最適な調整量はコンピュータ部20を利用して決定する場合に限定されず、位相検出部から出力された信号に基づいて、例えば手動で切り替えスイッチ42の接続点を切り替えてもよい。さらに、レイテンシ調整部4は図3に示すようにシフトレジスタを用いる場合に限定されず、例えば遅延素子などを利用してもよい。

【0063】

そしてレイテンシ調整時にVOC11側からの周波数信号の入力を遮断するスイッチ部は、図1に示すように回路中に当該スイッチ部5を物理的に設ける場合に限定されない。例えばコンピュータ部20からの指示に基づいて分周器12の出力を停止することができるように構成し、レイテンシ調整時にはこの分周器12からの出力を停止することにより、VOC11側から作動増幅器14への周波数信号の入力を遮断してもよい。この場合には、分周器12がスイッチ部としての役割も果たしていることになる。

【0064】

またレイテンシ調整の際に、DDS21から作動増幅器14へ出力される周波数信号の出力レベルを通常使用時に比べて小さくする手法に代えて、差動増幅器14側のゲインを小さくしてもよい。例えば差動増幅器14はコンピュータ部20からの制御によるゲインの変更を可能とし、周波数シンセサイザの通常運転時にはそのゲインを20倍とする一方、レイテンシ調整時には位相検出部16に入力される周波数信号と検波信号との振幅をほぼ一致させるため、差動増幅器14のゲインを1倍とするように、ゲインを切り替える構成とする場合などが考えられる。

【符号の説明】

【0065】

11 電圧制御発振器(VCO)

14 差動増幅器

15 A/D変換器

16 位相検出部

20 コンピュータ部

21 DDS

22 D/A変換器

31 位相補正部

4 レイテンシ調整部

41a〜41c

レジスタ部

42 切り替えスイッチ

5 スイッチ部

【特許請求の範囲】

【請求項1】

電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給する周波数シンセサイザであって、

前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、

前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号中に含まれる周波数設定部由来の周波数信号が前記位相検出部に入力されるまでのタイミングと、前記出力された時点から検波信号が前記位相検出部に入力されるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、

前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、

前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力し、前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する制御部と、を備えたことを特徴とする周波数シンセサイザ。

【請求項2】

前記制御部は、前記差動増幅器に前記テスト用の周波数信号を入力するときには、当該差動増幅器の差動利得、または前記周波数設定部から出力されるディジタルの周波数信号の信号レベルを通常使用時に比べて小さくすることを特徴とする請求項1に記載の周波数シンセサイザ。

【請求項3】

前記第2の位相補正部は、シフトレジスタにより構成されていることを特徴とする請求項1または2に記載の周波数シンセサイザ。

【請求項4】

前記周波数設定部は、ダイレクト・ディジタル・シンセサイザであることを特徴とする請求項1ないし3のいずれか一つに記載の周波数シンセサイザ。

【請求項5】

電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給し、前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号中に含まれる周波数設定部由来の周波数信号が前記位相検出部に入力されるまでのタイミングと、前記出力された時点から検波信号が前記位相検出部に入力されるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、を備えた周波数シンセサイザの調整方法であって、

この周波数シンセサイザの立ち上げ時に、前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力する工程と、

前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する工程と、を含むことを特徴とする周波数シンセサイザの調整方法。

【請求項1】

電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給する周波数シンセサイザであって、

前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、

前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号中に含まれる周波数設定部由来の周波数信号が前記位相検出部に入力されるまでのタイミングと、前記出力された時点から検波信号が前記位相検出部に入力されるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、

前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、

前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力し、前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する制御部と、を備えたことを特徴とする周波数シンセサイザ。

【請求項2】

前記制御部は、前記差動増幅器に前記テスト用の周波数信号を入力するときには、当該差動増幅器の差動利得、または前記周波数設定部から出力されるディジタルの周波数信号の信号レベルを通常使用時に比べて小さくすることを特徴とする請求項1に記載の周波数シンセサイザ。

【請求項3】

前記第2の位相補正部は、シフトレジスタにより構成されていることを特徴とする請求項1または2に記載の周波数シンセサイザ。

【請求項4】

前記周波数設定部は、ダイレクト・ディジタル・シンセサイザであることを特徴とする請求項1ないし3のいずれか一つに記載の周波数シンセサイザ。

【請求項5】

電圧制御発振部から出力された周波数信号と、周波数設定部から出力された設定周波数のディジタルの周波数信号をディジタル/アナログ変換部を介して得たアナログの周波数信号と、を差動増幅器に入力し、この差動増幅器にて得られたアナログの差分信号をアナログ/ディジタル変換部を介して得たディジタルの周波数信号と、前記周波数設定部から出力されるディジタルの周波数信号の位相を90°ずらした検波信号と、を位相差検出部により直交検波して両周波数信号の位相差を取り出し、この位相差を積分してその積分値に応じた電圧を前記電圧制御発振部に制御電圧として供給し、前記電圧制御発振部と差動増幅器との間に設けられたスイッチ部と、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号中に含まれる周波数設定部由来の周波数信号が前記位相検出部に入力されるまでのタイミングと、前記出力された時点から検波信号が前記位相検出部に入力されるまでのタイミングとをそろえるために予め定めた補正量だけ前記検波信号の位相を補正する第1の位相補正部と、前記ディジタル/アナログ変換部の信号の変換時間が周波数シンセサイザの立ち上げの度に異なる不都合を解消するために、前記検波信号をクロック単位で遅らせて出力する第2の位相補正部と、を備えた周波数シンセサイザの調整方法であって、

この周波数シンセサイザの立ち上げ時に、前記スイッチ部により電圧制御発振部を差動増幅器から切り離した状態で前記ディジタル信号発振部からテスト用の周波数信号を出力する工程と、

前記第2の位相補正部における遅延のクロック数を順次変えて、前記位相検出部で得た位相差が最小になるクロック数を遅延量とするように第2の位相補正部を設定する工程と、を含むことを特徴とする周波数シンセサイザの調整方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2011−188309(P2011−188309A)

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願番号】特願2010−52278(P2010−52278)

【出願日】平成22年3月9日(2010.3.9)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願日】平成22年3月9日(2010.3.9)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

[ Back to top ]