周波数シンセサイザ

【課題】 外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号が「断」となった場合には、SW3に可変電圧供給回路12からの出力電圧にループフィルタ4に出力させる切替信号を出力し、更にループフィルタ4からの出力電圧を1/N分圧器13で分圧した電圧を微調制御電圧とし、オフセット電圧供給回路15からの電圧を粗調電圧として加算器14で加算してOCXO5の制御電圧として出力する周波数シンセサイザである。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号が「断」となった場合には、SW3に可変電圧供給回路12からの出力電圧にループフィルタ4に出力させる切替信号を出力し、更にループフィルタ4からの出力電圧を1/N分圧器13で分圧した電圧を微調制御電圧とし、オフセット電圧供給回路15からの電圧を粗調電圧として加算器14で加算してOCXO5の制御電圧として出力する周波数シンセサイザである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、周波数シンセサイザに係り、特に、外部基準信号の入力が切断した時にPLLループから固定電圧へ切り替わる際の周波数変動を抑えることができる周波数シンセサイザに関する。

【背景技術】

【0002】

[従来の技術]

[従来の周波数シンセサイザ:図5]

従来の周波数シンセサイザについて図5を参照しながら説明する。図5は、従来の周波数シンセサイザの構成ブロック図である。

従来の周波数シンセサイザは、図5に示すように、PLL(Phase Locked Loop)−IC(Integrated Circuit)(1)1と、可変抵抗2と、スイッチ(SW)3と、ループフィルタ(1)4と、OCXO(Oven Controlled Crystal Oscillator)5と、PLL−IC(2)6と、ループフィルタ(2)7と、VCO(Voltage Controlled Oscillator)8と、AMP(Amplifier)9と、検波回路10と、制御回路11とを備えている。

【0003】

[従来の周波数シンセサイザの動作]

従来の周波数シンセサイザは、図5に示すように、OCXOが例えば10MHz又は40MHzで発振するものであり、PLL−IC(1)1で外部基準(REF)入力信号(例えばルビジウム信号等の10MHz)と同期される。

そして、その同期した信号を基準としてPLL−IC(2)6とVCO8を用いて高周波のシンセサイザ(例えば1GHz)を構成している。

【0004】

制御回路11は、PLL−IC1,6に対して、所望の周波数となるような設定データを出力し、出力周波数を決定する。

また、制御回路は、外部REF入力信号の有無を、検波回路10を介して判定し、入力がある場合は、SW3をPLL−IC(1)1側として、PLLループを構成するが、入力がない場合は、SW3を可変抵抗2側として、可変抵抗2で決まる一定の電圧値をOCXO5の制御端子に供給する。

【0005】

[関連技術]

尚、関連する先行技術として、特開平08−330954号公報「PLL回路」(埼玉日本電気株式会社)[特許文献1]、特開2004−234182号公報「クロック制御システム」(埼玉日本電気株式会社)[特許文献2]、特開2006−067350号公報「信号発生装置」(日本無線株式会社)[特許文献3]がある。

【0006】

特許文献1には、PLL回路において、スイッチ制御部が、位相比較器が出力する位相差電圧とバイアス電圧発生部が出力するバイアス電圧を比較し、電圧差があるときはスイッチをオンしてバイアス電圧をループフィルタのコンデンサに供給し、電圧差がなくなってきたときはスイッチをオフにしてバイアス電圧の供給を断することが記載されている。

【0007】

特許文献2には、クロック制御システムにおいて、クロック切り替え回路がクロック信号と固定値レベルを入力し、クロック信号の停止又は断を検出した場合に、固定値レベルに切り替えてPLLに出力することが記載されている。

【0008】

特許文献3には、信号発生装置において、外部/自走切り換えスイッチが、基準クロック信号が断した場合、基準クロック信号と電圧制御発振器が出力する信号との位相関係に基づく信号から、自走クロック発生器が出力する信号と電圧制御発振器が出力する信号との位相関係に基づく信号に切り換えてループフィルタに出力することが記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平08−330954号公報

【特許文献2】特開2004−234182号公報

【特許文献3】特開2006−067350号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、従来の周波数シンセサイザでは、何らかの要因で外部REF入力信号が有り(入り)の状態から無し(断)の状態になった場合に、SW3はPLLループ側から可変抵抗2で決まる一定電圧側に切り替わるようになっているが、外部REF入力信号が無くなった瞬間に、PLL−IC(1)1は位相比較できなくなり、SW3で可変抵抗2に切り替わるまでの時間が長いと、PLL−IC(1)1のチャージポンプ出力が不安定になってしまい、出力周波数が所望の周波数からずれてしまうという問題点があった。

【0011】

[外部REF入力信号が断となった場合の状況:図6]

外部REF入力信号が断となった場合の状況について図6を参照しながら説明する。図6は、外部REF入力信号が断となった場合の従来の状況を示す図である。

横軸を時間として、図6の一段目には外部REF入力信号、二段目にはSW切替信号、三段目にはチャージポンプ出力となるOCXO制御電圧、四段目にはAMP9からの出力周波数が示されている。

【0012】

図6に示すように、Aの時点まで外部REF入力信号が有り(存在)の場合、次の瞬間から外部REF入力信号が無し(不存在)となるが、制御回路11で外部REF入力信号の断を判定してSW3にSW切替信号を出力することになる。

但し、SW切替信号が出力されるのは、Aの時点より遅れてBの時点となる。このA時点からB時点までの時間経過で、チャージポンプ出力に電位変化が発生し、その電位変化によってOCXO制御電圧が不安定となり、結果的には出力周波数が変動するものであった。

【0013】

A時点からB時点までの時間は、検波回路10で外部REF入力信号が断となってから、制御回路11を介してSW切替信号の制御を行うまでの時間であり、この時間を小さくするか又は外部REF入力信号が断となっても、OCXO制御電圧の電圧変化ΔV1 を極めて小さくすることが必要である。

さらに、PLLループ時と可変抵抗で決まる一定電圧値との差ΔV2 を極めて小さくすることが必要である。

【0014】

[外部REF入力信号が断となった場合の詳細状況:図7]

外部REF入力信号が断となった場合の詳細状況について図7を参照しながら説明する。図7は、外部REF入力信号が断となった場合の従来の詳細状況を示す図である。

出力周波数の変動の詳細は、図7に示すように、例えば、OCXO周波数が40MHzで、OCXO制御電圧範囲が制御電圧0〜5V、VF感度2ppm/V(80Hz/V)、VCO出力周波数が804,292,857Hzで、ΔV1 が0.1V、Δ2 が0.05Vである場合に、ΔV1 下がった場合の出力周波数は、804,292,696Hzであり、ΔV2 上がった場合の出力周波数は804,292,937Hzとなっている。

【0015】

尚、特許文献1〜3では、基準信号の断(無し)を検出して固定電圧を電圧制御発振器に制御電圧として出力し、基準信号の入力(有り)を検出すると、PLLループを形成するものであるが、外部基準信号の断になってスイッチが切り替わるまでの間に発生する周波数の変動量を最小限にするものとはなっていないものである。

【0016】

本発明は上記実情に鑑みて為されたもので、外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供することを目的とする。

【課題を解決するための手段】

【0017】

上記従来例の問題点を解決するための本発明は、周波数シンセサイザであって、恒温槽付水晶発振器と、電圧制御発振器と、外部基準入力信号と恒温槽付水晶発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第1のPLL−ICと、可変電圧を供給する可変電圧供給回路と、第1のPLL−ICの出力と電圧供給回路の出力電圧を外部からの切替信号により選択して出力するスイッチと、スイッチで選択された出力を平滑化して出力する第1のループフィルタと、第1のループフィルタからの出力電圧を分圧して微調制御電圧として出力する分圧器と、オフセット電圧を供給するオフセット電圧供給回路と、オフセット電圧供給回路からのオフセット電圧を粗調電圧とし、当該粗調電圧に微調制御電圧を加算して恒温槽付水晶発振器の制御電圧として出力する加算器と、恒温槽付水晶発振器からの出力信号と電圧制御発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第2のPLL−ICと、第2のPLL−ICからの出力を平滑化して電圧制御発振器の制御電圧として出力する第2のループフィルタと、電圧制御発振器の出力を増幅する増幅器と、外部基準入力信号を入力して検波する検波回路と、検波回路からの検波出力を入力し、外部基準入力信号が入力されている「入」の場合には、スイッチに第1のPLL−ICの出力を第1のループフィルタに出力させる切替信号を出力し、外部基準入力信号が入力されていない「断」の場合には、スイッチに可変電圧供給回路の出力を第1のループフィルタに出力させる切替信号を出力し、第1のPLL−ICと第2のPLL−ICに所望の周波数を出力させるためのデータを設定する制御回路とを有することを特徴とする。

【0018】

本発明は、上記周波数シンセサイザにおいて、制御回路が、第1のループフィルタからの出力電圧をモニタし、可変電圧供給回路からスイッチに供給される電圧を、外部基準入力信号が入力されている「入」の場合に第1のPLL−ICからの出力電圧になるよう制御することを特徴とする。

【0019】

本発明は、上記周波数シンセサイザにおいて、制御回路が、加算器からの制御電圧をモニタし、オフセット電圧供給回路から前記加算器に供給される粗調電圧を、外部基準入力信号が入力されている「入」の場合と外部基準入力信号が入力されていない「断」の場合で同じ電圧になるよう制御することを特徴とする。

【0020】

本発明は、上記周波数シンセサイザにおいて、可変電圧供給回路が、抵抗とコンデンサを用いたフィルタで構成され、第1のループフィルタからの出力電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする。

【0021】

本発明は、上記周波数シンセサイザにおいて、オフセット電圧供給回路が、抵抗とコンデンサを用いたフィルタで構成され、加算器からの制御電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする。

【発明の効果】

【0022】

本発明によれば、分圧器が、第1のループフィルタからの出力電圧を分圧して微調制御電圧として出力し、加算器が、オフセット電圧供給回路からのオフセット電圧を粗調電圧とし、当該粗調電圧に微調制御電圧を加算して恒温槽付水晶発振器の制御電圧として出力し、制御回路が、検波回路からの検波出力を入力し、外部基準入力信号が入力されている「入」の場合には、スイッチに第1のPLL−ICの出力を第1のループフィルタに出力させる切替信号を出力し、外部基準入力信号が入力されていない「断」の場合には、スイッチに可変電圧供給回路の出力を第1のループフィルタに出力させる切替信号を出力し、第1のPLL−ICと第2のPLL−ICに所望の周波数を出力させるためのデータを設定する周波数シンセサイザとしているので、外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる効果がある。

【図面の簡単な説明】

【0023】

【図1】本発明の実施の形態に係る周波数シンセサイザの構成ブロック図である。

【図2】外部REF入力信号が断となった場合の実施の形態の状況を示す図である。

【図3】1/N分圧器の回路図である。

【図4】加算器の回路図である。

【図5】従来の周波数シンセサイザの構成ブロック図である。

【図6】外部REF入力信号が断となった場合の従来の状況を示す図である。

【図7】外部REF入力信号が断となった場合の従来の詳細状況を示す図である。

【発明を実施するための形態】

【0024】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係る周波数シンセサイザは、外部基準入力信号が「断」となった場合に、スイッチの切り替えにより可変電圧供給回路からPLL−ICの出力電圧に近い電圧が供給され、ループフィルタからの出力電圧を分圧した電圧を微調制御電圧とし、オフセット電圧供給回路からの電圧を粗調電圧として加算器で加算してOCXOに供給しているので、外部基準入力信号の「断」から自走までの制御電圧の変動を小さくでき、出力周波数の変動を抑えることができるものである。

【0025】

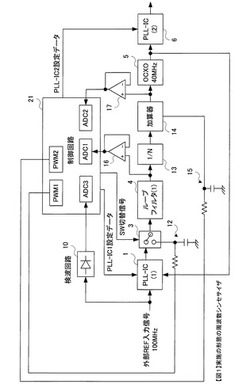

[本PLL回路:図1]

本発明の実施の形態に係る周波数シンセサイザについて図1を参照しながら説明する。図1は、本発明の実施の形態に係る周波数シンセサイザの構成ブロック図である。

本発明の実施の形態に係る周波数シンセサイザ(本シンセサイザ)は、図1に示すように、PLL−IC(1)1と、可変電圧供給回路12と、スイッチ(SW)3と、ループフィルタ(1)4と、1/N分圧器13と、加算器14と、OCXO5と、PLL−IC(2)6と、ループフィルタ(2)と、VCOと、AMPと、検波回路10と、オフセット電圧供給回路15と、バッファ16と、バッファ17と、制御回路(マイコン)21とを基本的に有している。

【0026】

図5の従来の周波数シンセサイザと比較して、可変電圧供給回路12、1/N分圧器13、加算器14、オフセット電圧供給回路15、バッファ16、バッファ17が設けられ、制御回路21の制御内容が相違している。

尚、図1では、紙面の制約で、PLL−IC(2)6の後段の、ループフィルタ(2)、VCO、AMPを記載していないが、図5と同様に、図1でもそれら構成を備えている。

【0027】

[本シンセサイザの各部]

本シンセサイザの各部について具体的に説明する。

PLL−IC(1)1は、外部基準(REF)入力信号、例えばルビジウム信号等の10MHzの信号を入力すると共に、OCXO5からの出力信号を入力し、OCXO5からの信号を分周し、外部REF入力信号との位相比較を行い、位相差をパルス幅の電圧でSW3の一方の入力端子に出力する。

従って、PLL−ICには、分周器、位相比較器、チャージポンプ等の回路構成をワンチップに収納したものである。

尚、PLL−IC(1)1には、所望の周波数を得るための、制御回路11からPLL−IC(1)用の設定データが入力され、設定される。

【0028】

可変電圧供給回路12は、抵抗R1とコンデンサC1とから構成されるR1C1フィルタであり、コンデンサC1の一端がSW3の他方の端子に接続し、コンデンサC1の他方の端子が接地され、コンデンサC1の一端に抵抗R1の一端が接続し、抵抗R1の他端には制御回路21から特定の電圧が供給される。

そして、抵抗R1を介してコンデンサC1に蓄積された電荷によりSW3の他端に、外部REF入力信号の断となる前の電圧に近い直流電圧(可変電圧)を供給している。

【0029】

スイッチ(SW)3は、制御回路21からのSW切替信号に基づいて、2つの入力端子のいずれかを選択し、ループフィルタ(1)4にPLL−IC(1)1からの出力信号又は可変電圧供給回路12からの可変電圧を出力する。

ループフィルタ(1)4は、SW3からの出力を平滑化し、制御電圧として1/N分圧器13とバッファ16に出力する。

【0030】

1/N分圧器13は、ループフィルタ(1)4からの制御電圧を1/Nに分圧し、加算器14に出力する。

1/N分圧器13で分圧することで、信号の変化量を小さい信号に変換する。従って、加算器14に入力される電圧は、「微調制御電圧」といえる。

バッファ16は、ループフィルタ(1)4からの制御電圧をモニタしており、制御回路21にモニタ電圧を出力する。

【0031】

加算器14は、1/N分圧器13からの微調制御電圧を一方の入力端子に入力すると共に、オフセット電圧供給回路15からのオフセット電圧(粗調電圧)を他方の入力端子に入力し、粗調電圧に微調制御電圧を加算してOCXO5とバッファ17に出力する。

バッファ17は、加算器14からの制御電圧をモニタしており、制御回路21にモニタ電圧を出力する。

【0032】

オフセット電圧供給回路15は、抵抗R2とコンデンサC2とから構成されるR2C2フィルタであり、コンデンサC2の一端が加算器14の他方の入力端子に接続し、コンデンサC2の他方の端子が接地され、コンデンサC2の一端に抵抗R2の一端が接続し、抵抗R2の他端には制御回路21から特定の電圧が供給される。

そして、抵抗R2を介してコンデンサC2に蓄積された電荷により加算器14の他方の入力端子に、直流のオフセット電圧を供給している。オフセット電圧は、外部REF入力信号の有無に関係なく供給されるもので、OCXO5に対する「粗調電圧」といえる。

【0033】

OCXO(恒温槽付水晶発振器)5は、加算器14からの出力を制御電圧として入力し、例えば、40MHzの発振周波数をPLL−IC(2)6及びPLL−IC(1)1に出力する。

【0034】

PLL−IC(2)6は、OCXO5からの出力信号とVCOからの出力信号を入力し、VCOからの信号を分周し、OCXO5からの信号との位相比較を行い、位相差をパルス幅の電圧でループフィルタ(2)に出力する。

尚、PLL−IC(2)6には、所望の周波数を得るための、制御回路21からPLL−IC(2)用の設定データが入力され、設定される。

【0035】

ループフィルタ(2)は、ループフィルタ(1)4と同様に、PLL−IC(2)6からの出力を平滑化し、制御電圧としてVCOに出力する。

VCO(電圧制御発振器)は、ループフィルタ(2)からの出力を制御電圧として発振動作を行い、AMP及びPLL−IC(2)6に発振信号を出力する。

AMP(増幅器)は、VCOからの発振信号を増幅して出力する。

【0036】

検波回路10は、外部REF入力信号を分岐して入力し、入力信号の検波を行い、検波出力(検波結果)を制御回路21に出力する。

そして、検波回路10は、外部REF入力信号が断となったことを検出し、また、外部REF入力信号が「断」から「入」となったことも検出して、制御回路21に出力する。

【0037】

検波回路10からの出力は、制御回路21で、ADC(アナログ/デジタル変換器)3でデジタル信号に変換して取り込まれる。

【0038】

また、制御回路21は、検波回路10から外部REF入力信号の「断」検出が入力されると、SW3に可変電圧供給回路12を選択するようSW切替信号を出力する。

更に、制御回路21は、検波回路10から外部REF入力信号の「入」検出が入力されると、SW3にPLL−IC(1)1を選択するようSW切替信号を出力する。

【0039】

また、制御回路21は、ループフィルタ(1)4からの出力を、バッファ16を介して入力し、ADC1でデジタル信号に変換して取り込み、内部の記憶部に電圧値を記憶し、当該電圧値に応じて可変電圧供給回路12に供給される電圧が決定され、PWM(Pulse Width Modulation)1でパルスにより可変電圧供給回路12に出力される。

【0040】

また、制御回路21は、加算器14からの出力を、バッファ17を介して入力し、ADC2でデジタル信号に変換して取り込み、内部の記憶部に電圧値を記憶し、当該電圧値に応じてオフセット電圧供給回路15に供給される電圧が決定され、PWM2でパルスによりオフセット電圧供給回路15に出力される。

【0041】

[本シンセサイザの動作]

次に、本シンセサイザの動作について説明する。

制御回路21は、検波回路10からの外部REF入力信号の「入」検出の入力により、SW3をPLL−IC(1)1を選択させるSW切替信号を出力する。

【0042】

PLL−IC(1)1では、外部REF入力信号とOCXO5からの信号との位相比較を行い、位相差の電圧を、SW3を介してループフィルタ(1)4に出力する。

位相差の電圧は、ループフィルタ(1)4で平滑化され、1/N分圧器13とバッファ16に出力される。

1/N分圧器13で分圧された信号(微調電圧)は、加算器14に出力される。

【0043】

加算器14では、オフセット電圧供給回路15からの粗調電圧に1/N分圧器13からの微調電圧を加算し、OCXO5とバッファ17に出力する。

OCXO5で発振動作がなされ、発振信号がPLL−IC(2)6とPLL−IC(1)1に出力される。

PLL−IC(2)6では、OCXO5からの信号とVCOからの信号の位相比較が為され、位相差の電圧がループフィルタ(2)で平滑化され、VCOの制御電圧として入力されて、VCOから発振信号がPLL−IC(2)とAMPに出力される。

【0044】

そして、バッファ16でモニタされた電圧に応じて可変電圧供給回路12に出力する電圧値を制御回路21が決定し、パルスの電圧として可変電圧供給回路12に供給される。

また、バッファ17でモニタされた電圧に応じてオフセット電圧供給回路15に出力する電圧値を制御回路21が決定し、パルスの電圧としてオフセット電圧供給回路15に供給される。

【0045】

そして、制御回路21は、検波回路10からの外部REF入力信号の「断」検出の入力により、SW3に可変電圧供給回路12を選択させるSW切替信号を出力する。

ここで、外部REF入力信号の「断」により、SW3が切り替わって可変電圧供給回路12からの可変電圧がループフィルタ(1)4に出力されるが、バッファ16でモニタされた電圧に基づいて外部REF入力信号の「入」状態の時から制御回路21が可変電圧供給回路12に電圧を供給しているので、切り替えに伴う変動量(ΔV1 )を抑えることができる。

【0046】

更に、外部REF入力信号の「入」又は「断」に拘わらず、オフセット電圧供給回路15から加算器14に粗調電圧が供給されているので、SW3の切り替えに伴う変動量(ΔV2 )をほとんど発生させることがない。

【0047】

[本シンセサイザの特徴的事項]

本シンセサイザにおける特徴的事項について具体的に説明する。

OCXO5に対する制御電圧とループフィルタ(1)4の出力電圧は、常時、制御回路21でモニタし、記憶部に電圧値を記憶しておく。

OCXO5の制御電圧の変動量ΔV1 を小さくするために、ループフィルタ(1)4の出力電圧は、1/Nに分圧した後、微調制御電圧として加算器14に入力される。

【0048】

外部REF入力信号が「断」した瞬間の周波数変化が1Hz以下になるよう、分圧比N=200とする。

つまり、1Hz/804,292,857Hz=0.001243ppmであり、0.001243ppm/2ppm=0.6215mV、制御電圧変動量ΔV1 =0.1Vであれば、0.1V/0.6215mV=162≪200として計算される。

【0049】

粗調電圧は、制御回路21がPWM2で出力し、オフセット電圧供給回路15のR2C2フィルタを介して、直流電圧として加算器14に入力される。

R2C2フィルタの時定数は、ループフィルタ(1)4の時定数より十分大きな時定数としておく。

また、粗調電圧は、ループフィルタ(1)4の出力電圧がOCXO5の中点電圧(約2.5V)程度になるように、制御回路21で制御する。

【0050】

外部REF入力信号が「入」の場合、SW3がPLLループ側になっており、OCXO5の制御電圧=粗調電圧+微調制御電圧でPLLロックしている。

制御回路21は、PWM1と可変電圧供給回路12のR1C1フィルタにて、R1C1フィルタが供給する電圧がPLL−IC(1)1の出力電圧と同じになるよう、制御する。

R1C1フィルタの時定数は、ループフィルタ(1)4の時定数より十分大きな時定数としておく。

外部REF入力信号が「断」の場合は、SW3がR1C1フィルタ側になっており、OCXO5の制御電圧は、外部REF入力信号が「入」の場合の電圧と同じになる。

【0051】

[外部REF入力信号が断となった場合の実施の形態の状況:図2]

次に、外部REF入力信号が断となった場合の実施の形態における状況について図2を参照しながら説明する。図2は、外部REF入力信号が断となった場合の実施の形態の状況を示す図である。

図6の従来の状況と比較して、図2では大幅な改善が見られる。

【0052】

分圧比N=200とした場合、制御電圧変動量ΔV1 =0.1V/200=0.5mVであるため、OCXO5の出力としては、2ppm*0.5mV=0.001ppmの周波数変化となり、周波数シンセサイザ出力804,292,857Hzに対して、周波数変動量Δf1=0.8Hzの周波数変化となる。

【0053】

SW切替信号による切り替え後の可変電圧(一定電圧)値は、PLLループ時の電圧値となるよう調整しているため、ΔV2 =0(ゼロ)であり、周波数はPLLロック時の周波数と一致する。

【0054】

[1/N分圧器:図3]

次に、1/N分圧器13の構成について図3を参照しながら説明する。図3は、1/N分圧器13の回路図である。

1/N分圧器13は、図3に示すように、反転アップを用い、ループフィルタ(1)4からの信号(In)が(−)入力端子に抵抗Raを介して入力され、(+)入力端子は接地され、出力端子からは分圧信号(Out)が出力されると共に、その出力信号が抵抗Rbを介して帰還して入力されるようになっている。

【0055】

[加算器:図4]

次に、加算器14の構成について図4を参照しながら説明する。図4は、加算器の回路図である。

加算器14は、図4に示すように、オペアップを用い、(−)入力端子に抵抗Rcを介して微調制御電圧が入力され、(+)入力端子には粗調電圧が入力され、出力端子からはOCXO制御電圧が出力されると共に、その出力が抵抗Rdを介して(−)入力端子に帰還して入力されるようになっている。

【0056】

[実施の形態の効果]

本シンセサイザによれば、外部REF入力信号「断」の場合に、SW高速切替回路12が内部基準信号のクロックを用いて制御回路11より高速にSW3をPLL−IC(1)1から可変抵抗2に切り替えるSW切替信号を出力するようにしているので、外部REF入力信号「断」から自走までの期間が短くなり、出力周波数の変動を抑えることができる効果がある。

【0057】

また、本シンセサイザによれば、外部REF入力信号「断」から「入」となった場合にも、SW高速切替回路12が内部基準信号のクロックを用いて制御回路11より高速にSW3を可変抵抗2からPLL−IC(1)1に切り替えるSW切替信号を出力するようにしているので、再度の外部REF入力信号「入」から自走終了までの期間が短くなり、出力周波数の変動を抑えることができる効果がある。

【産業上の利用可能性】

【0058】

本発明は、外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザに好適である。

【符号の説明】

【0059】

1...PLL−IC(1)、 2...可変抵抗、 3...スイッチ(SW)、 4...ループフィルタ(1)、 5...OCXO、 6...PLL−IC(2)、 7...ループフィルタ(2)、 8...VCO、 9...AMP、 10...検波回路、 11...制御回路(マイコン)、 12...可変電圧供給回路、 13...1/N分圧器、 14...加算器、 15...オフセット電圧供給回路、 16...バッファ、 17...バッファ、 21...制御回路

【技術分野】

【0001】

本発明は、周波数シンセサイザに係り、特に、外部基準信号の入力が切断した時にPLLループから固定電圧へ切り替わる際の周波数変動を抑えることができる周波数シンセサイザに関する。

【背景技術】

【0002】

[従来の技術]

[従来の周波数シンセサイザ:図5]

従来の周波数シンセサイザについて図5を参照しながら説明する。図5は、従来の周波数シンセサイザの構成ブロック図である。

従来の周波数シンセサイザは、図5に示すように、PLL(Phase Locked Loop)−IC(Integrated Circuit)(1)1と、可変抵抗2と、スイッチ(SW)3と、ループフィルタ(1)4と、OCXO(Oven Controlled Crystal Oscillator)5と、PLL−IC(2)6と、ループフィルタ(2)7と、VCO(Voltage Controlled Oscillator)8と、AMP(Amplifier)9と、検波回路10と、制御回路11とを備えている。

【0003】

[従来の周波数シンセサイザの動作]

従来の周波数シンセサイザは、図5に示すように、OCXOが例えば10MHz又は40MHzで発振するものであり、PLL−IC(1)1で外部基準(REF)入力信号(例えばルビジウム信号等の10MHz)と同期される。

そして、その同期した信号を基準としてPLL−IC(2)6とVCO8を用いて高周波のシンセサイザ(例えば1GHz)を構成している。

【0004】

制御回路11は、PLL−IC1,6に対して、所望の周波数となるような設定データを出力し、出力周波数を決定する。

また、制御回路は、外部REF入力信号の有無を、検波回路10を介して判定し、入力がある場合は、SW3をPLL−IC(1)1側として、PLLループを構成するが、入力がない場合は、SW3を可変抵抗2側として、可変抵抗2で決まる一定の電圧値をOCXO5の制御端子に供給する。

【0005】

[関連技術]

尚、関連する先行技術として、特開平08−330954号公報「PLL回路」(埼玉日本電気株式会社)[特許文献1]、特開2004−234182号公報「クロック制御システム」(埼玉日本電気株式会社)[特許文献2]、特開2006−067350号公報「信号発生装置」(日本無線株式会社)[特許文献3]がある。

【0006】

特許文献1には、PLL回路において、スイッチ制御部が、位相比較器が出力する位相差電圧とバイアス電圧発生部が出力するバイアス電圧を比較し、電圧差があるときはスイッチをオンしてバイアス電圧をループフィルタのコンデンサに供給し、電圧差がなくなってきたときはスイッチをオフにしてバイアス電圧の供給を断することが記載されている。

【0007】

特許文献2には、クロック制御システムにおいて、クロック切り替え回路がクロック信号と固定値レベルを入力し、クロック信号の停止又は断を検出した場合に、固定値レベルに切り替えてPLLに出力することが記載されている。

【0008】

特許文献3には、信号発生装置において、外部/自走切り換えスイッチが、基準クロック信号が断した場合、基準クロック信号と電圧制御発振器が出力する信号との位相関係に基づく信号から、自走クロック発生器が出力する信号と電圧制御発振器が出力する信号との位相関係に基づく信号に切り換えてループフィルタに出力することが記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平08−330954号公報

【特許文献2】特開2004−234182号公報

【特許文献3】特開2006−067350号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、従来の周波数シンセサイザでは、何らかの要因で外部REF入力信号が有り(入り)の状態から無し(断)の状態になった場合に、SW3はPLLループ側から可変抵抗2で決まる一定電圧側に切り替わるようになっているが、外部REF入力信号が無くなった瞬間に、PLL−IC(1)1は位相比較できなくなり、SW3で可変抵抗2に切り替わるまでの時間が長いと、PLL−IC(1)1のチャージポンプ出力が不安定になってしまい、出力周波数が所望の周波数からずれてしまうという問題点があった。

【0011】

[外部REF入力信号が断となった場合の状況:図6]

外部REF入力信号が断となった場合の状況について図6を参照しながら説明する。図6は、外部REF入力信号が断となった場合の従来の状況を示す図である。

横軸を時間として、図6の一段目には外部REF入力信号、二段目にはSW切替信号、三段目にはチャージポンプ出力となるOCXO制御電圧、四段目にはAMP9からの出力周波数が示されている。

【0012】

図6に示すように、Aの時点まで外部REF入力信号が有り(存在)の場合、次の瞬間から外部REF入力信号が無し(不存在)となるが、制御回路11で外部REF入力信号の断を判定してSW3にSW切替信号を出力することになる。

但し、SW切替信号が出力されるのは、Aの時点より遅れてBの時点となる。このA時点からB時点までの時間経過で、チャージポンプ出力に電位変化が発生し、その電位変化によってOCXO制御電圧が不安定となり、結果的には出力周波数が変動するものであった。

【0013】

A時点からB時点までの時間は、検波回路10で外部REF入力信号が断となってから、制御回路11を介してSW切替信号の制御を行うまでの時間であり、この時間を小さくするか又は外部REF入力信号が断となっても、OCXO制御電圧の電圧変化ΔV1 を極めて小さくすることが必要である。

さらに、PLLループ時と可変抵抗で決まる一定電圧値との差ΔV2 を極めて小さくすることが必要である。

【0014】

[外部REF入力信号が断となった場合の詳細状況:図7]

外部REF入力信号が断となった場合の詳細状況について図7を参照しながら説明する。図7は、外部REF入力信号が断となった場合の従来の詳細状況を示す図である。

出力周波数の変動の詳細は、図7に示すように、例えば、OCXO周波数が40MHzで、OCXO制御電圧範囲が制御電圧0〜5V、VF感度2ppm/V(80Hz/V)、VCO出力周波数が804,292,857Hzで、ΔV1 が0.1V、Δ2 が0.05Vである場合に、ΔV1 下がった場合の出力周波数は、804,292,696Hzであり、ΔV2 上がった場合の出力周波数は804,292,937Hzとなっている。

【0015】

尚、特許文献1〜3では、基準信号の断(無し)を検出して固定電圧を電圧制御発振器に制御電圧として出力し、基準信号の入力(有り)を検出すると、PLLループを形成するものであるが、外部基準信号の断になってスイッチが切り替わるまでの間に発生する周波数の変動量を最小限にするものとはなっていないものである。

【0016】

本発明は上記実情に鑑みて為されたもので、外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供することを目的とする。

【課題を解決するための手段】

【0017】

上記従来例の問題点を解決するための本発明は、周波数シンセサイザであって、恒温槽付水晶発振器と、電圧制御発振器と、外部基準入力信号と恒温槽付水晶発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第1のPLL−ICと、可変電圧を供給する可変電圧供給回路と、第1のPLL−ICの出力と電圧供給回路の出力電圧を外部からの切替信号により選択して出力するスイッチと、スイッチで選択された出力を平滑化して出力する第1のループフィルタと、第1のループフィルタからの出力電圧を分圧して微調制御電圧として出力する分圧器と、オフセット電圧を供給するオフセット電圧供給回路と、オフセット電圧供給回路からのオフセット電圧を粗調電圧とし、当該粗調電圧に微調制御電圧を加算して恒温槽付水晶発振器の制御電圧として出力する加算器と、恒温槽付水晶発振器からの出力信号と電圧制御発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第2のPLL−ICと、第2のPLL−ICからの出力を平滑化して電圧制御発振器の制御電圧として出力する第2のループフィルタと、電圧制御発振器の出力を増幅する増幅器と、外部基準入力信号を入力して検波する検波回路と、検波回路からの検波出力を入力し、外部基準入力信号が入力されている「入」の場合には、スイッチに第1のPLL−ICの出力を第1のループフィルタに出力させる切替信号を出力し、外部基準入力信号が入力されていない「断」の場合には、スイッチに可変電圧供給回路の出力を第1のループフィルタに出力させる切替信号を出力し、第1のPLL−ICと第2のPLL−ICに所望の周波数を出力させるためのデータを設定する制御回路とを有することを特徴とする。

【0018】

本発明は、上記周波数シンセサイザにおいて、制御回路が、第1のループフィルタからの出力電圧をモニタし、可変電圧供給回路からスイッチに供給される電圧を、外部基準入力信号が入力されている「入」の場合に第1のPLL−ICからの出力電圧になるよう制御することを特徴とする。

【0019】

本発明は、上記周波数シンセサイザにおいて、制御回路が、加算器からの制御電圧をモニタし、オフセット電圧供給回路から前記加算器に供給される粗調電圧を、外部基準入力信号が入力されている「入」の場合と外部基準入力信号が入力されていない「断」の場合で同じ電圧になるよう制御することを特徴とする。

【0020】

本発明は、上記周波数シンセサイザにおいて、可変電圧供給回路が、抵抗とコンデンサを用いたフィルタで構成され、第1のループフィルタからの出力電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする。

【0021】

本発明は、上記周波数シンセサイザにおいて、オフセット電圧供給回路が、抵抗とコンデンサを用いたフィルタで構成され、加算器からの制御電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする。

【発明の効果】

【0022】

本発明によれば、分圧器が、第1のループフィルタからの出力電圧を分圧して微調制御電圧として出力し、加算器が、オフセット電圧供給回路からのオフセット電圧を粗調電圧とし、当該粗調電圧に微調制御電圧を加算して恒温槽付水晶発振器の制御電圧として出力し、制御回路が、検波回路からの検波出力を入力し、外部基準入力信号が入力されている「入」の場合には、スイッチに第1のPLL−ICの出力を第1のループフィルタに出力させる切替信号を出力し、外部基準入力信号が入力されていない「断」の場合には、スイッチに可変電圧供給回路の出力を第1のループフィルタに出力させる切替信号を出力し、第1のPLL−ICと第2のPLL−ICに所望の周波数を出力させるためのデータを設定する周波数シンセサイザとしているので、外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる効果がある。

【図面の簡単な説明】

【0023】

【図1】本発明の実施の形態に係る周波数シンセサイザの構成ブロック図である。

【図2】外部REF入力信号が断となった場合の実施の形態の状況を示す図である。

【図3】1/N分圧器の回路図である。

【図4】加算器の回路図である。

【図5】従来の周波数シンセサイザの構成ブロック図である。

【図6】外部REF入力信号が断となった場合の従来の状況を示す図である。

【図7】外部REF入力信号が断となった場合の従来の詳細状況を示す図である。

【発明を実施するための形態】

【0024】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係る周波数シンセサイザは、外部基準入力信号が「断」となった場合に、スイッチの切り替えにより可変電圧供給回路からPLL−ICの出力電圧に近い電圧が供給され、ループフィルタからの出力電圧を分圧した電圧を微調制御電圧とし、オフセット電圧供給回路からの電圧を粗調電圧として加算器で加算してOCXOに供給しているので、外部基準入力信号の「断」から自走までの制御電圧の変動を小さくでき、出力周波数の変動を抑えることができるものである。

【0025】

[本PLL回路:図1]

本発明の実施の形態に係る周波数シンセサイザについて図1を参照しながら説明する。図1は、本発明の実施の形態に係る周波数シンセサイザの構成ブロック図である。

本発明の実施の形態に係る周波数シンセサイザ(本シンセサイザ)は、図1に示すように、PLL−IC(1)1と、可変電圧供給回路12と、スイッチ(SW)3と、ループフィルタ(1)4と、1/N分圧器13と、加算器14と、OCXO5と、PLL−IC(2)6と、ループフィルタ(2)と、VCOと、AMPと、検波回路10と、オフセット電圧供給回路15と、バッファ16と、バッファ17と、制御回路(マイコン)21とを基本的に有している。

【0026】

図5の従来の周波数シンセサイザと比較して、可変電圧供給回路12、1/N分圧器13、加算器14、オフセット電圧供給回路15、バッファ16、バッファ17が設けられ、制御回路21の制御内容が相違している。

尚、図1では、紙面の制約で、PLL−IC(2)6の後段の、ループフィルタ(2)、VCO、AMPを記載していないが、図5と同様に、図1でもそれら構成を備えている。

【0027】

[本シンセサイザの各部]

本シンセサイザの各部について具体的に説明する。

PLL−IC(1)1は、外部基準(REF)入力信号、例えばルビジウム信号等の10MHzの信号を入力すると共に、OCXO5からの出力信号を入力し、OCXO5からの信号を分周し、外部REF入力信号との位相比較を行い、位相差をパルス幅の電圧でSW3の一方の入力端子に出力する。

従って、PLL−ICには、分周器、位相比較器、チャージポンプ等の回路構成をワンチップに収納したものである。

尚、PLL−IC(1)1には、所望の周波数を得るための、制御回路11からPLL−IC(1)用の設定データが入力され、設定される。

【0028】

可変電圧供給回路12は、抵抗R1とコンデンサC1とから構成されるR1C1フィルタであり、コンデンサC1の一端がSW3の他方の端子に接続し、コンデンサC1の他方の端子が接地され、コンデンサC1の一端に抵抗R1の一端が接続し、抵抗R1の他端には制御回路21から特定の電圧が供給される。

そして、抵抗R1を介してコンデンサC1に蓄積された電荷によりSW3の他端に、外部REF入力信号の断となる前の電圧に近い直流電圧(可変電圧)を供給している。

【0029】

スイッチ(SW)3は、制御回路21からのSW切替信号に基づいて、2つの入力端子のいずれかを選択し、ループフィルタ(1)4にPLL−IC(1)1からの出力信号又は可変電圧供給回路12からの可変電圧を出力する。

ループフィルタ(1)4は、SW3からの出力を平滑化し、制御電圧として1/N分圧器13とバッファ16に出力する。

【0030】

1/N分圧器13は、ループフィルタ(1)4からの制御電圧を1/Nに分圧し、加算器14に出力する。

1/N分圧器13で分圧することで、信号の変化量を小さい信号に変換する。従って、加算器14に入力される電圧は、「微調制御電圧」といえる。

バッファ16は、ループフィルタ(1)4からの制御電圧をモニタしており、制御回路21にモニタ電圧を出力する。

【0031】

加算器14は、1/N分圧器13からの微調制御電圧を一方の入力端子に入力すると共に、オフセット電圧供給回路15からのオフセット電圧(粗調電圧)を他方の入力端子に入力し、粗調電圧に微調制御電圧を加算してOCXO5とバッファ17に出力する。

バッファ17は、加算器14からの制御電圧をモニタしており、制御回路21にモニタ電圧を出力する。

【0032】

オフセット電圧供給回路15は、抵抗R2とコンデンサC2とから構成されるR2C2フィルタであり、コンデンサC2の一端が加算器14の他方の入力端子に接続し、コンデンサC2の他方の端子が接地され、コンデンサC2の一端に抵抗R2の一端が接続し、抵抗R2の他端には制御回路21から特定の電圧が供給される。

そして、抵抗R2を介してコンデンサC2に蓄積された電荷により加算器14の他方の入力端子に、直流のオフセット電圧を供給している。オフセット電圧は、外部REF入力信号の有無に関係なく供給されるもので、OCXO5に対する「粗調電圧」といえる。

【0033】

OCXO(恒温槽付水晶発振器)5は、加算器14からの出力を制御電圧として入力し、例えば、40MHzの発振周波数をPLL−IC(2)6及びPLL−IC(1)1に出力する。

【0034】

PLL−IC(2)6は、OCXO5からの出力信号とVCOからの出力信号を入力し、VCOからの信号を分周し、OCXO5からの信号との位相比較を行い、位相差をパルス幅の電圧でループフィルタ(2)に出力する。

尚、PLL−IC(2)6には、所望の周波数を得るための、制御回路21からPLL−IC(2)用の設定データが入力され、設定される。

【0035】

ループフィルタ(2)は、ループフィルタ(1)4と同様に、PLL−IC(2)6からの出力を平滑化し、制御電圧としてVCOに出力する。

VCO(電圧制御発振器)は、ループフィルタ(2)からの出力を制御電圧として発振動作を行い、AMP及びPLL−IC(2)6に発振信号を出力する。

AMP(増幅器)は、VCOからの発振信号を増幅して出力する。

【0036】

検波回路10は、外部REF入力信号を分岐して入力し、入力信号の検波を行い、検波出力(検波結果)を制御回路21に出力する。

そして、検波回路10は、外部REF入力信号が断となったことを検出し、また、外部REF入力信号が「断」から「入」となったことも検出して、制御回路21に出力する。

【0037】

検波回路10からの出力は、制御回路21で、ADC(アナログ/デジタル変換器)3でデジタル信号に変換して取り込まれる。

【0038】

また、制御回路21は、検波回路10から外部REF入力信号の「断」検出が入力されると、SW3に可変電圧供給回路12を選択するようSW切替信号を出力する。

更に、制御回路21は、検波回路10から外部REF入力信号の「入」検出が入力されると、SW3にPLL−IC(1)1を選択するようSW切替信号を出力する。

【0039】

また、制御回路21は、ループフィルタ(1)4からの出力を、バッファ16を介して入力し、ADC1でデジタル信号に変換して取り込み、内部の記憶部に電圧値を記憶し、当該電圧値に応じて可変電圧供給回路12に供給される電圧が決定され、PWM(Pulse Width Modulation)1でパルスにより可変電圧供給回路12に出力される。

【0040】

また、制御回路21は、加算器14からの出力を、バッファ17を介して入力し、ADC2でデジタル信号に変換して取り込み、内部の記憶部に電圧値を記憶し、当該電圧値に応じてオフセット電圧供給回路15に供給される電圧が決定され、PWM2でパルスによりオフセット電圧供給回路15に出力される。

【0041】

[本シンセサイザの動作]

次に、本シンセサイザの動作について説明する。

制御回路21は、検波回路10からの外部REF入力信号の「入」検出の入力により、SW3をPLL−IC(1)1を選択させるSW切替信号を出力する。

【0042】

PLL−IC(1)1では、外部REF入力信号とOCXO5からの信号との位相比較を行い、位相差の電圧を、SW3を介してループフィルタ(1)4に出力する。

位相差の電圧は、ループフィルタ(1)4で平滑化され、1/N分圧器13とバッファ16に出力される。

1/N分圧器13で分圧された信号(微調電圧)は、加算器14に出力される。

【0043】

加算器14では、オフセット電圧供給回路15からの粗調電圧に1/N分圧器13からの微調電圧を加算し、OCXO5とバッファ17に出力する。

OCXO5で発振動作がなされ、発振信号がPLL−IC(2)6とPLL−IC(1)1に出力される。

PLL−IC(2)6では、OCXO5からの信号とVCOからの信号の位相比較が為され、位相差の電圧がループフィルタ(2)で平滑化され、VCOの制御電圧として入力されて、VCOから発振信号がPLL−IC(2)とAMPに出力される。

【0044】

そして、バッファ16でモニタされた電圧に応じて可変電圧供給回路12に出力する電圧値を制御回路21が決定し、パルスの電圧として可変電圧供給回路12に供給される。

また、バッファ17でモニタされた電圧に応じてオフセット電圧供給回路15に出力する電圧値を制御回路21が決定し、パルスの電圧としてオフセット電圧供給回路15に供給される。

【0045】

そして、制御回路21は、検波回路10からの外部REF入力信号の「断」検出の入力により、SW3に可変電圧供給回路12を選択させるSW切替信号を出力する。

ここで、外部REF入力信号の「断」により、SW3が切り替わって可変電圧供給回路12からの可変電圧がループフィルタ(1)4に出力されるが、バッファ16でモニタされた電圧に基づいて外部REF入力信号の「入」状態の時から制御回路21が可変電圧供給回路12に電圧を供給しているので、切り替えに伴う変動量(ΔV1 )を抑えることができる。

【0046】

更に、外部REF入力信号の「入」又は「断」に拘わらず、オフセット電圧供給回路15から加算器14に粗調電圧が供給されているので、SW3の切り替えに伴う変動量(ΔV2 )をほとんど発生させることがない。

【0047】

[本シンセサイザの特徴的事項]

本シンセサイザにおける特徴的事項について具体的に説明する。

OCXO5に対する制御電圧とループフィルタ(1)4の出力電圧は、常時、制御回路21でモニタし、記憶部に電圧値を記憶しておく。

OCXO5の制御電圧の変動量ΔV1 を小さくするために、ループフィルタ(1)4の出力電圧は、1/Nに分圧した後、微調制御電圧として加算器14に入力される。

【0048】

外部REF入力信号が「断」した瞬間の周波数変化が1Hz以下になるよう、分圧比N=200とする。

つまり、1Hz/804,292,857Hz=0.001243ppmであり、0.001243ppm/2ppm=0.6215mV、制御電圧変動量ΔV1 =0.1Vであれば、0.1V/0.6215mV=162≪200として計算される。

【0049】

粗調電圧は、制御回路21がPWM2で出力し、オフセット電圧供給回路15のR2C2フィルタを介して、直流電圧として加算器14に入力される。

R2C2フィルタの時定数は、ループフィルタ(1)4の時定数より十分大きな時定数としておく。

また、粗調電圧は、ループフィルタ(1)4の出力電圧がOCXO5の中点電圧(約2.5V)程度になるように、制御回路21で制御する。

【0050】

外部REF入力信号が「入」の場合、SW3がPLLループ側になっており、OCXO5の制御電圧=粗調電圧+微調制御電圧でPLLロックしている。

制御回路21は、PWM1と可変電圧供給回路12のR1C1フィルタにて、R1C1フィルタが供給する電圧がPLL−IC(1)1の出力電圧と同じになるよう、制御する。

R1C1フィルタの時定数は、ループフィルタ(1)4の時定数より十分大きな時定数としておく。

外部REF入力信号が「断」の場合は、SW3がR1C1フィルタ側になっており、OCXO5の制御電圧は、外部REF入力信号が「入」の場合の電圧と同じになる。

【0051】

[外部REF入力信号が断となった場合の実施の形態の状況:図2]

次に、外部REF入力信号が断となった場合の実施の形態における状況について図2を参照しながら説明する。図2は、外部REF入力信号が断となった場合の実施の形態の状況を示す図である。

図6の従来の状況と比較して、図2では大幅な改善が見られる。

【0052】

分圧比N=200とした場合、制御電圧変動量ΔV1 =0.1V/200=0.5mVであるため、OCXO5の出力としては、2ppm*0.5mV=0.001ppmの周波数変化となり、周波数シンセサイザ出力804,292,857Hzに対して、周波数変動量Δf1=0.8Hzの周波数変化となる。

【0053】

SW切替信号による切り替え後の可変電圧(一定電圧)値は、PLLループ時の電圧値となるよう調整しているため、ΔV2 =0(ゼロ)であり、周波数はPLLロック時の周波数と一致する。

【0054】

[1/N分圧器:図3]

次に、1/N分圧器13の構成について図3を参照しながら説明する。図3は、1/N分圧器13の回路図である。

1/N分圧器13は、図3に示すように、反転アップを用い、ループフィルタ(1)4からの信号(In)が(−)入力端子に抵抗Raを介して入力され、(+)入力端子は接地され、出力端子からは分圧信号(Out)が出力されると共に、その出力信号が抵抗Rbを介して帰還して入力されるようになっている。

【0055】

[加算器:図4]

次に、加算器14の構成について図4を参照しながら説明する。図4は、加算器の回路図である。

加算器14は、図4に示すように、オペアップを用い、(−)入力端子に抵抗Rcを介して微調制御電圧が入力され、(+)入力端子には粗調電圧が入力され、出力端子からはOCXO制御電圧が出力されると共に、その出力が抵抗Rdを介して(−)入力端子に帰還して入力されるようになっている。

【0056】

[実施の形態の効果]

本シンセサイザによれば、外部REF入力信号「断」の場合に、SW高速切替回路12が内部基準信号のクロックを用いて制御回路11より高速にSW3をPLL−IC(1)1から可変抵抗2に切り替えるSW切替信号を出力するようにしているので、外部REF入力信号「断」から自走までの期間が短くなり、出力周波数の変動を抑えることができる効果がある。

【0057】

また、本シンセサイザによれば、外部REF入力信号「断」から「入」となった場合にも、SW高速切替回路12が内部基準信号のクロックを用いて制御回路11より高速にSW3を可変抵抗2からPLL−IC(1)1に切り替えるSW切替信号を出力するようにしているので、再度の外部REF入力信号「入」から自走終了までの期間が短くなり、出力周波数の変動を抑えることができる効果がある。

【産業上の利用可能性】

【0058】

本発明は、外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザに好適である。

【符号の説明】

【0059】

1...PLL−IC(1)、 2...可変抵抗、 3...スイッチ(SW)、 4...ループフィルタ(1)、 5...OCXO、 6...PLL−IC(2)、 7...ループフィルタ(2)、 8...VCO、 9...AMP、 10...検波回路、 11...制御回路(マイコン)、 12...可変電圧供給回路、 13...1/N分圧器、 14...加算器、 15...オフセット電圧供給回路、 16...バッファ、 17...バッファ、 21...制御回路

【特許請求の範囲】

【請求項1】

周波数シンセサイザであって、

恒温槽付水晶発振器と、

電圧制御発振器と、

外部基準入力信号と前記恒温槽付水晶発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第1のPLL−ICと、

可変電圧を供給する可変電圧供給回路と、

前記第1のPLL−ICの出力と前記電圧供給回路の出力電圧を外部からの切替信号により選択して出力するスイッチと、

前記スイッチで選択された出力を平滑化して出力する第1のループフィルタと、

前記第1のループフィルタからの出力電圧を分圧して微調制御電圧として出力する分圧器と、

オフセット電圧を供給するオフセット電圧供給回路と、

前記オフセット電圧供給回路からのオフセット電圧を粗調電圧とし、当該粗調電圧に前記微調制御電圧を加算して前記恒温槽付水晶発振器の制御電圧として出力する加算器と、

前記恒温槽付水晶発振器からの出力信号と前記電圧制御発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第2のPLL−ICと、

前記第2のPLL−ICからの出力を平滑化して前記電圧制御発振器の制御電圧として出力する第2のループフィルタと、

前記電圧制御発振器の出力を増幅する増幅器と、

前記外部基準入力信号を入力して検波する検波回路と、

前記検波回路からの検波出力を入力し、前記外部基準入力信号が入力されている「入」の場合には、前記スイッチに前記第1のPLL−ICの出力を前記第1のループフィルタに出力させる切替信号を出力し、前記外部基準入力信号が入力されていない「断」の場合には、前記スイッチに前記可変電圧供給回路の出力を前記第1のループフィルタに出力させる切替信号を出力し、前記第1のPLL−ICと前記第2のPLL−ICに所望の周波数を出力させるためのデータを設定する制御回路とを有することを特徴とする周波数シンセサイザ。

【請求項2】

制御回路は、第1のループフィルタからの出力電圧をモニタし、可変電圧供給回路からスイッチに供給される電圧を、外部基準入力信号が入力されている「入」の場合に第1のPLL−ICからの出力電圧になるよう制御することを特徴とする請求項1記載の周波数シンセサイザ。

【請求項3】

制御回路は、加算器からの制御電圧をモニタし、オフセット電圧供給回路から前記加算器に供給される粗調電圧を、外部基準入力信号が入力されている「入」の場合と前記外部基準入力信号が入力されていない「断」の場合で同じ電圧になるよう制御することを特徴とする請求項1又は2記載の周波数シンセサイザ。

【請求項4】

可変電圧供給回路は、抵抗とコンデンサを用いたフィルタで構成され、第1のループフィルタからの出力電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする請求項1乃至3のいずれか記載の周波数シンセサイザ。

【請求項5】

オフセット電圧供給回路は、抵抗とコンデンサを用いたフィルタで構成され、加算器からの制御電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする請求項1乃至3のいずれか記載の周波数シンセサイザ。

【請求項1】

周波数シンセサイザであって、

恒温槽付水晶発振器と、

電圧制御発振器と、

外部基準入力信号と前記恒温槽付水晶発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第1のPLL−ICと、

可変電圧を供給する可変電圧供給回路と、

前記第1のPLL−ICの出力と前記電圧供給回路の出力電圧を外部からの切替信号により選択して出力するスイッチと、

前記スイッチで選択された出力を平滑化して出力する第1のループフィルタと、

前記第1のループフィルタからの出力電圧を分圧して微調制御電圧として出力する分圧器と、

オフセット電圧を供給するオフセット電圧供給回路と、

前記オフセット電圧供給回路からのオフセット電圧を粗調電圧とし、当該粗調電圧に前記微調制御電圧を加算して前記恒温槽付水晶発振器の制御電圧として出力する加算器と、

前記恒温槽付水晶発振器からの出力信号と前記電圧制御発振器からの出力信号を入力し、位相比較し、位相差に応じた信号を出力する第2のPLL−ICと、

前記第2のPLL−ICからの出力を平滑化して前記電圧制御発振器の制御電圧として出力する第2のループフィルタと、

前記電圧制御発振器の出力を増幅する増幅器と、

前記外部基準入力信号を入力して検波する検波回路と、

前記検波回路からの検波出力を入力し、前記外部基準入力信号が入力されている「入」の場合には、前記スイッチに前記第1のPLL−ICの出力を前記第1のループフィルタに出力させる切替信号を出力し、前記外部基準入力信号が入力されていない「断」の場合には、前記スイッチに前記可変電圧供給回路の出力を前記第1のループフィルタに出力させる切替信号を出力し、前記第1のPLL−ICと前記第2のPLL−ICに所望の周波数を出力させるためのデータを設定する制御回路とを有することを特徴とする周波数シンセサイザ。

【請求項2】

制御回路は、第1のループフィルタからの出力電圧をモニタし、可変電圧供給回路からスイッチに供給される電圧を、外部基準入力信号が入力されている「入」の場合に第1のPLL−ICからの出力電圧になるよう制御することを特徴とする請求項1記載の周波数シンセサイザ。

【請求項3】

制御回路は、加算器からの制御電圧をモニタし、オフセット電圧供給回路から前記加算器に供給される粗調電圧を、外部基準入力信号が入力されている「入」の場合と前記外部基準入力信号が入力されていない「断」の場合で同じ電圧になるよう制御することを特徴とする請求項1又は2記載の周波数シンセサイザ。

【請求項4】

可変電圧供給回路は、抵抗とコンデンサを用いたフィルタで構成され、第1のループフィルタからの出力電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする請求項1乃至3のいずれか記載の周波数シンセサイザ。

【請求項5】

オフセット電圧供給回路は、抵抗とコンデンサを用いたフィルタで構成され、加算器からの制御電圧のモニタ結果に基づいて制御回路から特定の電圧が印加されることを特徴とする請求項1乃至3のいずれか記載の周波数シンセサイザ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−74604(P2013−74604A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−214495(P2011−214495)

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

[ Back to top ]