周波数シンセサイザ

【課題】ディジタル処理を用いたPLLにより周波数シンセサイザを構成するにあたって、A/D変換部を不要とすること。

【解決手段】設定周波数に応じたディジタル値を積分することにより、位相信号となる鋸波を生成する。一方電圧制御発振器から出力される周波数信号を分周回路を介してエッジ検出部に入力し、前記周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた矩形波信号を生成する。そしてラッチ回路にて、前記矩形波信号により鋸波の値をラッチし、この値をループフィルタにて積分し、電圧制御発振器の制御電圧とする。

【解決手段】設定周波数に応じたディジタル値を積分することにより、位相信号となる鋸波を生成する。一方電圧制御発振器から出力される周波数信号を分周回路を介してエッジ検出部に入力し、前記周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた矩形波信号を生成する。そしてラッチ回路にて、前記矩形波信号により鋸波の値をラッチし、この値をループフィルタにて積分し、電圧制御発振器の制御電圧とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ディジタル信号処理を用いたPLLにより構成した周波数シンセサイザに関する。

【背景技術】

【0002】

標準信号発生器の一つとしてPLL(Phase Locked Loop)を用いた周波数シンセサイザが知られており、その応用としては例えば移動局における局発振部や無線通信機器の試験用信号源、放送機器などが挙げられる。通信分野において周波数シンセサイザを適用する場合には、他のチャンネルとの混信を避けるためにノイズが少ないことが要求され、電波が過密化している状況下では周波数をできるだけ細かく設定できることが望ましい。

【0003】

そこで本件出願人は、このような要請を充足しつつ、回路構成が簡素な周波数シンセサイザを開発し、その技術は既に特許文献1などに開示されている。例えば特許文献1の手法では、電圧制御発振器の出力信号をA/D(アナログ/ディジタル)変換して、出力信号に対応する回転ベクトルを生成すると共に、この回転ベクトルとの位相比較を行うための回転ベクトルを生成し、位相比較結果をループフィルタを通した後D/A変換し、得られたアナログ信号を電圧制御発振器に制御電圧として入力している。

【0004】

しかしながらこのような装置は、A/D(アナログ/ディジタル)変換し、そのディジタル信号を処理してD/A変換しているため、回路が複雑であるという課題がある。また位相比較を行うための回転ベクトルを生成するために、複素平面上のディジタルデータを記憶するテーブルが必要になる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−74291号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明はこのような事情の下になされたものであり、PLLを用いた簡素な構成である周波数シンセサイザを提供することにある。

【課題を解決するための手段】

【0007】

本発明の周波数シンセサイザは、電圧制御発振器と、

前記電圧制御発振器から出力される周波数信号を分周する分周回路と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を積分することにより、鋸歯状の積分波形である鋸波を生成する積分波形生成部と、

前記分周回路から出力される周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた周波数の矩形波信号を出力するエッジ検出部と、

前記積分波形生成部にて生成された鋸波の値を前記矩形波信号によりラッチするラッチ回路と、

このラッチ回路にてラッチした鋸波の値を積分するループフィルタと、

このループフィルタの出力をディジタル/アナログ変換して前記電圧制御発振器に出力するディジタル/アナログ変換部と、を備えたことを特徴とする。

【0008】

前記積分波形生成部にて積分するディジタル値は、例えば2の補数が用いられる。

前記ラッチ回路から出力される鋸波の値を移動平均処理してループフィルタに出力する移動平均処理回路を備えた構成を好ましい一態様として挙げることができる。

【発明の効果】

【0009】

本発明は、ディジタル信号処理を用いたPLLにより構成した周波数シンセサイザにおいて、ディジタル信号により生成した位相信号である鋸波の値を、電圧制御発振器から出力される周波数信号の周波数に応じた矩形波信号によりラッチし、ラッチした値に基づいて電圧制御発振器の制御電圧を生成している。このためA/D変換部を不要とし、また大きな容量のデータテーブルも不要であり、簡易な構成とすることができる。そして前記位相信号(鋸波)とラッチのタイミング信号である矩形波信号とは非同期であることから、設定周波数によってはスプリアスを発生する懸念があるが、ラッチされた鋸波の値を移動平均することによりスプリアスの発生を抑制することができる。

【図面の簡単な説明】

【0010】

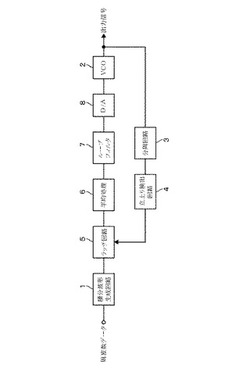

【図1】本発明に係る周波数シンセサイザの実施形態の全体構成を示すブロック図である。

【図2】積分波形生成部の回路を示すブロック図である。

【図3】積分波形生成部の動作を示す説明図である。

【図4】積分波形生成部の出力波形を示す波形図である。

【図5】前記実施形態に用いられる立ち上がり検出回路を示すブロック図である。

【図6】前記立ち上がり検出回路の動作を示すタイムチャートである。

【図7】前記実施形態の動作を示すタイムチャートである。

【発明を実施するための形態】

【0011】

図1は、本発明に係る周波数シンセサイザの実施形態の全体構成を示すブロック図であり、1は積分波形生成回路である。この積分波形生成回路1は、入力されたディジタル値(周波数データ)に応じた周波数の鋸波(鋸歯状の積分波形である波)をディジタルデータで出力する機能を有し、図2に示すように加算部11の後段にフリップフロップ回路12を設け、フリップフロップ回路12の出力を加算部11にて入力値と加算するように構成されている。フリップフロップ回路12には、図示しないクロック発生源からクロック信号が入力され、クロック信号の入力のタイミングにより加算部11からの入力データが出力される。クロック信号の周波数は、出力されるディジタル値群により特定される鋸波の周波数として例えば5MHzを得たい場合には、例えば20MHz程度とされる。この鋸波は、PLLループ上の位相波の役割を果たすものである。

【0012】

積分波形生成回路1の動作について、説明の便宜上4ビットのディジタル値により動作する場合を例に挙げて図3を参照しながら説明する。ディジタル値は「2」の補数として取り扱われており、例えば当該回路1に入力される周波数データである入力値が例えば「0001」であるとすると、入力値とフリップフロップ回路12の出力値とが加算されて加算値が増えていくが、加算値が「0111」となり、次に「0001」が入力されると、「1000」となって十進値は負の値に変わる。従ってフリップフロップ回路12に入力されるクロック信号のパルス番号(便宜上の番号である)と、周波数データ(入力値)と、出力値との関係は図3に示すようになり、図4に示すように出力波形は入力値の積分波形である鋸波となる。そしてこの鋸波の周波数は、設定される周波数データである入力値に応じて決まることから、この周波数データは後述のように信号発生器の設定周波数を決定するデータとなる。なお積分波形生成回路1のディジタル信号は、4ビットで説明しているが、実際には例えば32ビットの信号が用いられる。

【0013】

図1に戻って2は電圧制御発振器(VCO)であり、矩形波からなる周波数信号を出力する。この電圧制御発振器2の出力を帰還する経路には、前記周波数信号を分周する分周回路3が設けられ、この分周回路3の後段には、分周された周波数信号(矩形波信号)の立ち上がりを検出する立ち上がり検出回路4が設けられている。この立ち上がり検出回路4は、図5に示すように図示しないクロック源からのクロック信号と分周回路3からの矩形波信号とが入力される第1のフリップフロップ回路41と、このフリップフロップ回路41の出力信号とクロック信号とが入力される第2のフリップフロップ回路42と、両フリップフロップ回路41、42の出力が入力されるNAND回路43とからなる。図6は、図5に示す回路における各部の信号波形であり、図6のタイムチャートの符号は、図5の各部の符号に対応している。

【0014】

図6から分かるように、分周回路3からの矩形波信号の立ち上がりを検出して矩形波信号(図6の(5)参照)が得られている。この例では、分周回路3からの矩形波信号の立ち上がりを検出しているが、分周回路3からの矩形波信号の立ち下がり検出するようにしてもよく、要するに当該矩形波信号に同期する矩形波信号が得られればよい。従って立ち上がり検出回路4は、エッジ検出部の一例に相当する。

【0015】

図1に戻って5はラッチ回路であり、積分波形生成回路1にて得られたディジタルデータからなる鋸波の値(ディジタル値)を、前記立ち上がり検出回路4から出力される矩形波によりラッチする。6は移動平均処理回路であり、ラッチ回路5から出力される鋸波の値を予め設定された回数だけ積分し、その積分値をその回数分で割る処理を行う。7はループフィルタであり、移動平均処理回路6から出力される平均値を積分し、PLLのゲインを調整する機能を有する。8はD/A変換部であり、ループフィルタ7の出力をD/A変換して電圧制御発振器2に制御電圧として供給する。

【0016】

次に上述実施の形態の作用について説明する。先ず実施形態である周波数シンセサイザから出力すべき目的とする周波数に応じた周波数データを設定する。周波数設定データと鋸波の周波数との関係について模式的な一例を述べる。例えば図示しないクロック発生源から出力されるクロック信号の周波数が16MHzであるとすると、既述の鋸波の生成例においては、周波数設定データを「1」とすれば、鋸波の周波数は1MHzとなり(図3参照)、周波数設定データを「2」とすれば、2MHzとなる。

【0017】

ここで図1に示すPLLの動作を図7を参照しながら説明する。電圧制御発振器2の出力が分周回路3にて分周され、立ち上がり検出回路4は、図7(a)に示す分周出力(矩形波である周波数信号)の立ち上がりを検出して、図7(b)に示すように矩形波信号を出力する。ラッチ回路5は、この矩形波信号により前記鋸波のディジタル値をラッチし(図7(c)参照)、ラッチしたディジタル値を移動平均処理回路6に出力する(図7(d)参照)。この移動平均処理回路6にて、ラッチしたディジタル値を、予め設定したディジタル値の数だけ移動平均し、移動平均した値をループフィルタ7にて積分し、電圧制御発振器2に制御電圧として出力する。

【0018】

今、例えばPLLの動作状態がロック状態から外れて、電圧制御発振器2の出力周波数が位相信号である鋸波の周波数よりも低くなったとすると、図7(c)に示すようにラッチポイントが鋸波のゼロクロスポイントよりも進行するので、ラッチ回路5にてラッチした鋸波のディジタル値は正の値となる。このためループフィルタ7の出力が大きくなり、これにより電圧制御発振器2の出力周波数が高くなるので、ラッチポイントがゼロクロスポイントに向かい、やがてPLLの動作状態がロック状態となる。

【0019】

また逆に電圧制御発振器2の出力周波数が位相信号である鋸波の周波数よりも高くなったとすると、ラッチポイントが鋸波のゼロクロスポイントよりも遅延するので、ラッチした値は負の値となる。このためループフィルタ7の出力が小さくなり、これにより電圧制御発振器2の出力周波数が低くなるので、ラッチポイントがゼロクロスポイントに向かい、やがてPLLの動作状態がロック状態となる。

【0020】

上述の実施の形態によれば、ディジタル信号処理を用いたPLLにより構成した周波数シンセサイザにおいて、ディジタル信号により生成した位相信号である鋸波の値を、電圧制御発振器からの出力を分周した矩形波信号によりラッチし、ラッチした値に基づいて電圧制御発振器の制御電圧を生成している。このためA/D変換部を不要とし、また大きな容量のデータテーブルも不要であり、簡易な構成とすることができる。

【0021】

上述実施の形態では、積分波形生成回路1にて取り扱うディジタル値は「2」の補数とであるが、ディジタル値としては「2」の補数に限られるものではない。従って鋸波を構成するディジタル値は、正の値のみの組み合わせであっても良いし、負の値のみの組み合わせであっても良い。

本発明は、ラッチされた鋸波の値を移動平均することに限定されない。しかしながら位相信号である鋸波とラッチのタイミング信号である矩形波信号とは非同期であることから、設定周波数によってはスプリアスを発生する懸念がある。このため設定周波数によっては、ラッチされた鋸波の値を移動平均することによりスプリアスの発生を抑制することができるという利点がある。

【符号の説明】

【0022】

1 積分波形生成回路

2 電圧制御発振器

4 立ち上がり検出回路

5 ラッチ回路

6 移動平均処理回路

7 ループフィルタ

【技術分野】

【0001】

本発明は、ディジタル信号処理を用いたPLLにより構成した周波数シンセサイザに関する。

【背景技術】

【0002】

標準信号発生器の一つとしてPLL(Phase Locked Loop)を用いた周波数シンセサイザが知られており、その応用としては例えば移動局における局発振部や無線通信機器の試験用信号源、放送機器などが挙げられる。通信分野において周波数シンセサイザを適用する場合には、他のチャンネルとの混信を避けるためにノイズが少ないことが要求され、電波が過密化している状況下では周波数をできるだけ細かく設定できることが望ましい。

【0003】

そこで本件出願人は、このような要請を充足しつつ、回路構成が簡素な周波数シンセサイザを開発し、その技術は既に特許文献1などに開示されている。例えば特許文献1の手法では、電圧制御発振器の出力信号をA/D(アナログ/ディジタル)変換して、出力信号に対応する回転ベクトルを生成すると共に、この回転ベクトルとの位相比較を行うための回転ベクトルを生成し、位相比較結果をループフィルタを通した後D/A変換し、得られたアナログ信号を電圧制御発振器に制御電圧として入力している。

【0004】

しかしながらこのような装置は、A/D(アナログ/ディジタル)変換し、そのディジタル信号を処理してD/A変換しているため、回路が複雑であるという課題がある。また位相比較を行うための回転ベクトルを生成するために、複素平面上のディジタルデータを記憶するテーブルが必要になる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−74291号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明はこのような事情の下になされたものであり、PLLを用いた簡素な構成である周波数シンセサイザを提供することにある。

【課題を解決するための手段】

【0007】

本発明の周波数シンセサイザは、電圧制御発振器と、

前記電圧制御発振器から出力される周波数信号を分周する分周回路と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を積分することにより、鋸歯状の積分波形である鋸波を生成する積分波形生成部と、

前記分周回路から出力される周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた周波数の矩形波信号を出力するエッジ検出部と、

前記積分波形生成部にて生成された鋸波の値を前記矩形波信号によりラッチするラッチ回路と、

このラッチ回路にてラッチした鋸波の値を積分するループフィルタと、

このループフィルタの出力をディジタル/アナログ変換して前記電圧制御発振器に出力するディジタル/アナログ変換部と、を備えたことを特徴とする。

【0008】

前記積分波形生成部にて積分するディジタル値は、例えば2の補数が用いられる。

前記ラッチ回路から出力される鋸波の値を移動平均処理してループフィルタに出力する移動平均処理回路を備えた構成を好ましい一態様として挙げることができる。

【発明の効果】

【0009】

本発明は、ディジタル信号処理を用いたPLLにより構成した周波数シンセサイザにおいて、ディジタル信号により生成した位相信号である鋸波の値を、電圧制御発振器から出力される周波数信号の周波数に応じた矩形波信号によりラッチし、ラッチした値に基づいて電圧制御発振器の制御電圧を生成している。このためA/D変換部を不要とし、また大きな容量のデータテーブルも不要であり、簡易な構成とすることができる。そして前記位相信号(鋸波)とラッチのタイミング信号である矩形波信号とは非同期であることから、設定周波数によってはスプリアスを発生する懸念があるが、ラッチされた鋸波の値を移動平均することによりスプリアスの発生を抑制することができる。

【図面の簡単な説明】

【0010】

【図1】本発明に係る周波数シンセサイザの実施形態の全体構成を示すブロック図である。

【図2】積分波形生成部の回路を示すブロック図である。

【図3】積分波形生成部の動作を示す説明図である。

【図4】積分波形生成部の出力波形を示す波形図である。

【図5】前記実施形態に用いられる立ち上がり検出回路を示すブロック図である。

【図6】前記立ち上がり検出回路の動作を示すタイムチャートである。

【図7】前記実施形態の動作を示すタイムチャートである。

【発明を実施するための形態】

【0011】

図1は、本発明に係る周波数シンセサイザの実施形態の全体構成を示すブロック図であり、1は積分波形生成回路である。この積分波形生成回路1は、入力されたディジタル値(周波数データ)に応じた周波数の鋸波(鋸歯状の積分波形である波)をディジタルデータで出力する機能を有し、図2に示すように加算部11の後段にフリップフロップ回路12を設け、フリップフロップ回路12の出力を加算部11にて入力値と加算するように構成されている。フリップフロップ回路12には、図示しないクロック発生源からクロック信号が入力され、クロック信号の入力のタイミングにより加算部11からの入力データが出力される。クロック信号の周波数は、出力されるディジタル値群により特定される鋸波の周波数として例えば5MHzを得たい場合には、例えば20MHz程度とされる。この鋸波は、PLLループ上の位相波の役割を果たすものである。

【0012】

積分波形生成回路1の動作について、説明の便宜上4ビットのディジタル値により動作する場合を例に挙げて図3を参照しながら説明する。ディジタル値は「2」の補数として取り扱われており、例えば当該回路1に入力される周波数データである入力値が例えば「0001」であるとすると、入力値とフリップフロップ回路12の出力値とが加算されて加算値が増えていくが、加算値が「0111」となり、次に「0001」が入力されると、「1000」となって十進値は負の値に変わる。従ってフリップフロップ回路12に入力されるクロック信号のパルス番号(便宜上の番号である)と、周波数データ(入力値)と、出力値との関係は図3に示すようになり、図4に示すように出力波形は入力値の積分波形である鋸波となる。そしてこの鋸波の周波数は、設定される周波数データである入力値に応じて決まることから、この周波数データは後述のように信号発生器の設定周波数を決定するデータとなる。なお積分波形生成回路1のディジタル信号は、4ビットで説明しているが、実際には例えば32ビットの信号が用いられる。

【0013】

図1に戻って2は電圧制御発振器(VCO)であり、矩形波からなる周波数信号を出力する。この電圧制御発振器2の出力を帰還する経路には、前記周波数信号を分周する分周回路3が設けられ、この分周回路3の後段には、分周された周波数信号(矩形波信号)の立ち上がりを検出する立ち上がり検出回路4が設けられている。この立ち上がり検出回路4は、図5に示すように図示しないクロック源からのクロック信号と分周回路3からの矩形波信号とが入力される第1のフリップフロップ回路41と、このフリップフロップ回路41の出力信号とクロック信号とが入力される第2のフリップフロップ回路42と、両フリップフロップ回路41、42の出力が入力されるNAND回路43とからなる。図6は、図5に示す回路における各部の信号波形であり、図6のタイムチャートの符号は、図5の各部の符号に対応している。

【0014】

図6から分かるように、分周回路3からの矩形波信号の立ち上がりを検出して矩形波信号(図6の(5)参照)が得られている。この例では、分周回路3からの矩形波信号の立ち上がりを検出しているが、分周回路3からの矩形波信号の立ち下がり検出するようにしてもよく、要するに当該矩形波信号に同期する矩形波信号が得られればよい。従って立ち上がり検出回路4は、エッジ検出部の一例に相当する。

【0015】

図1に戻って5はラッチ回路であり、積分波形生成回路1にて得られたディジタルデータからなる鋸波の値(ディジタル値)を、前記立ち上がり検出回路4から出力される矩形波によりラッチする。6は移動平均処理回路であり、ラッチ回路5から出力される鋸波の値を予め設定された回数だけ積分し、その積分値をその回数分で割る処理を行う。7はループフィルタであり、移動平均処理回路6から出力される平均値を積分し、PLLのゲインを調整する機能を有する。8はD/A変換部であり、ループフィルタ7の出力をD/A変換して電圧制御発振器2に制御電圧として供給する。

【0016】

次に上述実施の形態の作用について説明する。先ず実施形態である周波数シンセサイザから出力すべき目的とする周波数に応じた周波数データを設定する。周波数設定データと鋸波の周波数との関係について模式的な一例を述べる。例えば図示しないクロック発生源から出力されるクロック信号の周波数が16MHzであるとすると、既述の鋸波の生成例においては、周波数設定データを「1」とすれば、鋸波の周波数は1MHzとなり(図3参照)、周波数設定データを「2」とすれば、2MHzとなる。

【0017】

ここで図1に示すPLLの動作を図7を参照しながら説明する。電圧制御発振器2の出力が分周回路3にて分周され、立ち上がり検出回路4は、図7(a)に示す分周出力(矩形波である周波数信号)の立ち上がりを検出して、図7(b)に示すように矩形波信号を出力する。ラッチ回路5は、この矩形波信号により前記鋸波のディジタル値をラッチし(図7(c)参照)、ラッチしたディジタル値を移動平均処理回路6に出力する(図7(d)参照)。この移動平均処理回路6にて、ラッチしたディジタル値を、予め設定したディジタル値の数だけ移動平均し、移動平均した値をループフィルタ7にて積分し、電圧制御発振器2に制御電圧として出力する。

【0018】

今、例えばPLLの動作状態がロック状態から外れて、電圧制御発振器2の出力周波数が位相信号である鋸波の周波数よりも低くなったとすると、図7(c)に示すようにラッチポイントが鋸波のゼロクロスポイントよりも進行するので、ラッチ回路5にてラッチした鋸波のディジタル値は正の値となる。このためループフィルタ7の出力が大きくなり、これにより電圧制御発振器2の出力周波数が高くなるので、ラッチポイントがゼロクロスポイントに向かい、やがてPLLの動作状態がロック状態となる。

【0019】

また逆に電圧制御発振器2の出力周波数が位相信号である鋸波の周波数よりも高くなったとすると、ラッチポイントが鋸波のゼロクロスポイントよりも遅延するので、ラッチした値は負の値となる。このためループフィルタ7の出力が小さくなり、これにより電圧制御発振器2の出力周波数が低くなるので、ラッチポイントがゼロクロスポイントに向かい、やがてPLLの動作状態がロック状態となる。

【0020】

上述の実施の形態によれば、ディジタル信号処理を用いたPLLにより構成した周波数シンセサイザにおいて、ディジタル信号により生成した位相信号である鋸波の値を、電圧制御発振器からの出力を分周した矩形波信号によりラッチし、ラッチした値に基づいて電圧制御発振器の制御電圧を生成している。このためA/D変換部を不要とし、また大きな容量のデータテーブルも不要であり、簡易な構成とすることができる。

【0021】

上述実施の形態では、積分波形生成回路1にて取り扱うディジタル値は「2」の補数とであるが、ディジタル値としては「2」の補数に限られるものではない。従って鋸波を構成するディジタル値は、正の値のみの組み合わせであっても良いし、負の値のみの組み合わせであっても良い。

本発明は、ラッチされた鋸波の値を移動平均することに限定されない。しかしながら位相信号である鋸波とラッチのタイミング信号である矩形波信号とは非同期であることから、設定周波数によってはスプリアスを発生する懸念がある。このため設定周波数によっては、ラッチされた鋸波の値を移動平均することによりスプリアスの発生を抑制することができるという利点がある。

【符号の説明】

【0022】

1 積分波形生成回路

2 電圧制御発振器

4 立ち上がり検出回路

5 ラッチ回路

6 移動平均処理回路

7 ループフィルタ

【特許請求の範囲】

【請求項1】

電圧制御発振器と、

前記電圧制御発振器から出力される周波数信号を分周する分周回路と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を積分することにより、鋸歯状の積分波形である鋸波を生成する積分波形生成部と、

前記分周回路から出力される周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた周波数の矩形波信号を出力するエッジ検出部と、

前記積分波形生成部にて生成された鋸波の値を前記矩形波信号によりラッチするラッチ回路と、

このラッチ回路にてラッチした鋸波の値を積分するループフィルタと、

このループフィルタの出力をディジタル/アナログ変換して前記電圧制御発振器に出力するディジタル/アナログ変換部と、を備えたことを特徴とする周波数シンセサイザ。

【請求項2】

前記積分波形生成部にて積分するディジタル値は、2の補数であることを特徴とする請求項1記載の周波数シンセサイザ。

【請求項3】

前記ラッチ回路から出力される鋸波の値を移動平均処理してループフィルタに出力する移動平均処理回路を備えたことを特徴とする請求項1記載の周波数シンセサイザ。

【請求項1】

電圧制御発振器と、

前記電圧制御発振器から出力される周波数信号を分周する分周回路と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を積分することにより、鋸歯状の積分波形である鋸波を生成する積分波形生成部と、

前記分周回路から出力される周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた周波数の矩形波信号を出力するエッジ検出部と、

前記積分波形生成部にて生成された鋸波の値を前記矩形波信号によりラッチするラッチ回路と、

このラッチ回路にてラッチした鋸波の値を積分するループフィルタと、

このループフィルタの出力をディジタル/アナログ変換して前記電圧制御発振器に出力するディジタル/アナログ変換部と、を備えたことを特徴とする周波数シンセサイザ。

【請求項2】

前記積分波形生成部にて積分するディジタル値は、2の補数であることを特徴とする請求項1記載の周波数シンセサイザ。

【請求項3】

前記ラッチ回路から出力される鋸波の値を移動平均処理してループフィルタに出力する移動平均処理回路を備えたことを特徴とする請求項1記載の周波数シンセサイザ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−9365(P2013−9365A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2012−114869(P2012−114869)

【出願日】平成24年5月18日(2012.5.18)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成24年5月18日(2012.5.18)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

[ Back to top ]