周波数判定回路および半導体装置

【課題】長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供する。

【解決手段】複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路201において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有する。例えば、所定のパルス幅よりも短いパルス幅の信号を検出し、その検出した信号のパルス数をカウントする。予めパルスのカウント数と周波数の対応付けをしておくことで、カウント数に基づいて周波数を判定することができる。

【解決手段】複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路201において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有する。例えば、所定のパルス幅よりも短いパルス幅の信号を検出し、その検出した信号のパルス数をカウントする。予めパルスのカウント数と周波数の対応付けをしておくことで、カウント数に基づいて周波数を判定することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、周波数判定回路の技術に関し、特に、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路、およびこの周波数判定回路を備えた半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

例えば、近年のIT装置の高速化に伴い、送受信LSI間を転送するデータレートが増大し、伝送路によって送信信号の劣化が起こるため、長距離高速伝送が困難になっている。このような問題に対して、波形整形の機能を有している、例えばバックプレーンシグナルコンディショナのようなLSIを送受信LSI間に挿入することで長距離高速伝送が実現できる。送受信LSI間に挿入するLSIは、複数の転送レートで動作するため周波数を判定する技術が要求される。

【0003】

例えば、特許文献1には、入力信号のサンプリング周波数を判別することができない問題に対して、予め定められた複数の周波数のうち、いずれか1つの周波数を有する入力クロック信号の周波数を判別する技術が示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−76965号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述したような特許文献1などを含む従来の周波数を判定する技術においては、複数の周波数の異なるデータ信号から周波数を特定する場合、データ信号のパルス数をカウントしても周波数を判定することは困難である。これは、データ信号のパターンは一定ではなく、長短のパルス幅が混在しているため、カウントしているパルス幅が必ずしも所定のパルス幅よりも短いパルス幅とは限らないからである。従って、長短のパルス幅が混在しているデータ信号の中から所定のパルス幅よりも短いパルス幅のみをカウントする必要がある。

【0006】

そこで、本発明は以上の課題に鑑みてなされたものであり、長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供することを主な目的とするものである。

【0007】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0009】

すなわち、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定することを特徴とする。

【0010】

具体的には、周波数判定回路は、所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路と、このデータレート検出回路で検出した信号をカウントするカウンタ回路と、周波数を判定する区間を制御するためのタイマー回路と、このタイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、カウンタ回路でカウントされたカウント数から周波数を判定する制御回路とを有することを特徴とする。

【0011】

また、上記のような特徴を有する周波数判定回路を備えた半導体装置にも適用することができる。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0013】

すなわち、長短のパルス幅が混在するデータ信号の周波数を判定することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態1における、データ転送を行う複数の集積回路を備えたデータ転送システムの構成の一例を示す図である。

【図2】本発明の実施の形態1において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

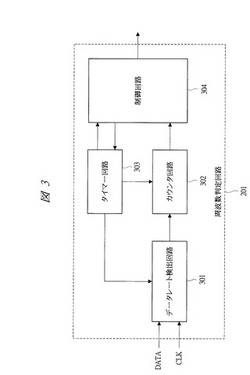

【図3】本発明の実施の形態1において、周波数判定回路の構成の一例を示すブロック図である。

【図4】本発明の実施の形態1において、データレート検出回路の構成の一例を示す回路図である。

【図5】本発明の実施の形態1において、データレート検出回路の動作の一例を説明するための信号波形図である。

【図6】本発明の実施の形態1において、データレート検出回路の動作の一例(4.0GHzのクロック信号、2.5GHzのデータ信号の場合)を説明するための信号波形図である。

【図7】本発明の実施の形態1において、データレート検出回路の動作の一例(4.0GHzのクロック信号、8.0GHzのデータ信号の場合)を説明するための信号波形図である。

【図8】本発明の実施の形態2において、データレート検出回路の部分の構成の一例を示す回路図である。

【図9】本発明の実施の形態2において、比較のためのデータレート検出回路の部分の動作の一例(遅延回路がない場合)を説明するための信号波形図である。

【図10】本発明の実施の形態2において、データレート検出回路の部分の動作の一例(遅延回路がある場合)を説明するための信号波形図である。

【図11】本発明の実施の形態2において、データレート検出回路の部分の構成の変形例を示す回路図である。

【図12】本発明の実施の形態3において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【図13】本発明の実施の形態4において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【図14】本発明の実施の形態5において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【発明を実施するための形態】

【0015】

以下の実施の形態においては、便宜上その必要があるときは、複数の実施の形態またはセクションに分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0016】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0017】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0018】

<本発明の実施の形態の概要>

本発明の実施の形態の周波数判定回路は、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路であって、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路(201)を有することを特徴とする。

【0019】

この周波数を判定する回路としては、具体的には、所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路(301)と、データレート検出回路で検出した信号をカウントするカウンタ回路(302)と、周波数を判定する区間を制御するためのタイマー回路(303)と、タイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、カウンタ回路でカウントされたカウント数から周波数を判定する制御回路(304)とを有することを特徴とする。

【0020】

以上説明した本発明の実施の形態の概要に基づいた、各実施の形態を以下において具体的に説明する。以下に説明する実施の形態は本発明を用いた一例であり、本発明は以下の実施の形態により限定されるものではない。

【0021】

[実施の形態1]

本発明の実施の形態1を、図1〜図7に基づいて説明する。

【0022】

<データ転送システムの構成>

まず、図1に基づいて、本実施の形態1における、データ転送を行う複数の集積回路(半導体装置)を備えたデータ転送システムの構成の一例について説明する。図1は、このデータ転送を行う複数の集積回路を備えたデータ転送システムの構成の一例を示す図である。

【0023】

図1に示すデータ転送システムは、送信側の集積回路101と、この集積回路101を実装するボード104と、受信側の集積回路102と、この集積回路102を実装するボード105と、データ転送用の集積回路103と、この集積回路103を実装したマザーボード106から構成され、送信側の集積回路101を実装したボード104と、受信側の集積回路102を実装したボード105が、データ転送用の集積回路103を実装したマザーボード106上に、コネクタ接続により実装されている。

【0024】

このデータ転送システムは、送信側の集積回路101からボード104およびマザーボード106を介してデータ転送用の集積回路103に電気的に接続され、さらに、データ転送用の集積回路103からマザーボード106およびボード105を介して受信側の集積回路102に電気的に接続されている。図1では、データ転送用の集積回路103を介して送信側の集積回路101から受信側の集積回路102へデータ転送を行う例を示している。データ転送用の集積回路103は、高速伝送路のリピータとしての機能および波形等化回路を備え、送信側の集積回路101からデータを受け取り、波形整形後のデータを受信側の集積回路102に転送する。

【0025】

このようなデータ転送システムにおいて、送信側の集積回路101、受信側の集積回路102、データ転送用の集積回路103のそれぞれは、例えば半導体基板上に各集積回路を形成した半導体チップなどの半導体装置として製造される。本発明では、これらの半導体装置のうち、データ転送用の集積回路103を形成した半導体装置に特徴を有し、以下において詳細に説明する。

【0026】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

次に、図2に基づいて、前述したデータ転送用の集積回路103のデータ転送を行う伝送系の構成の一例について説明する。図2は、このデータ転送用の集積回路103のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0027】

図2に示すデータ転送用の集積回路103は、周波数判定回路201と、入力回路(Rcv)202と、出力回路(Drv)203と、CDR(Clock Data Recovery)回路204と、PLL(Phase Locked Loop)回路205と、セレクタ回路206から構成される。

【0028】

入力回路202は、送信側の集積回路101からのデータを受け取り、周波数判定回路201、CDR回路204、セレクタ回路206に出力する。

【0029】

周波数判定回路201は、入力回路202から受け取ったデータについて、PLL回路205で生成した参照クロックに基づいて、周波数を判定し、この判定結果をセレクタ回路206に出力する。この周波数判定回路201は、詳細は後述するが、複数の周波数の異なるデータ信号から、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定することを特徴とする。

【0030】

CDR回路204は、入力回路202から受け取ったデータからクロックを抽出し、データを復元し、このデータをセレクタ回路206に出力する。

【0031】

PLL回路205は、位相同期制御により参照クロックを生成し、この参照クロックを周波数判定回路201に出力する。

【0032】

セレクタ回路206は、入力回路202から受け取ったデータと、CDR回路204で復元されたデータを入力として、周波数判定回路201からの判定結果に基づいて一方のデータを選択し、出力回路203に出力する。

【0033】

出力回路203は、セレクタ回路206で選択されたデータを、波形等化部で波形整形後、受信側の集積回路102に転送する。この出力回路203は、データを波形整形して出力する波形等化部を含む。

【0034】

<周波数判定回路の構成>

次に、図3に基づいて、前述した周波数判定回路201の構成の一例について説明する。 図3は、この周波数判定回路201の構成の一例を示すブロック図である。

【0035】

図3に示す周波数判定回路201は、データレート検出回路301と、カウンタ回路302と、タイマー回路303と、制御回路304から構成される。

【0036】

データレート検出回路301は、図2に示した入力回路202からのデータ(DATA)とPLL回路205からのクロック(CLK)を入力として、所定のパルス幅よりも短いパルス幅の信号を検出し、この検出結果をカウンタ回路302に出力する。

【0037】

カウンタ回路302は、データレート検出回路301からの検出結果から、このデータレート検出回路301で検出した信号をカウントし、このカウント結果を制御回路304に出力する。

【0038】

タイマー回路303は、周波数を判定する区間を制御し、この制御結果をデータレート検出回路301、カウンタ回路302、制御回路304に出力する。このタイマー回路303で、データレート(周波数)を判定する区間を制御することで、データレート判定後に不要な回路を停止することができる。

【0039】

制御回路304は、カウンタ回路302からのカウント結果、タイマー回路303からの制御結果を受けて、タイマー回路303で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、カウンタ回路302でカウントされたカウント数から周波数を判定し、この判定結果を図2に示したセレクタ回路206に出力する。この制御回路304の判定結果は、タイマー回路303にもフィードバックされる。この制御回路304では、カウント数から周波数を判定するために、予めカウント数がどの周波数に対応しているのかを設定しておく。

【0040】

<データレート検出回路の構成および動作>

次に、図4〜図7に基づいて、前述したデータレート検出回路301の構成および動作の一例について説明する。図4は、このデータレート検出回路301の構成の一例を示す回路図である。図5は、このデータレート検出回路301の動作の一例を説明するための信号波形図である。また、図6は4.0GHzのクロック信号、2.5GHzのデータ信号の場合の動作、図7は4.0GHzのクロック信号、8.0GHzのデータ信号の場合の動作をそれぞれ説明するための信号波形図である。

【0041】

図4に示すデータレート検出回路301は、データ信号の中から所定のパルス幅よりも短いパルス幅を検出する回路であり、FF(フリップフロップ)回路410,411,412,413,414と、EXOR(排他的論理和)回路415,416と、AND(論理積)回路417と、FF回路418から構成される。

【0042】

図4および後述する図5において、420はクロック信号(CLK)、419はデータ信号(DATA)、401〜409は出力信号、501〜526は信号パターンを示している。なお、420,419,401〜409の各信号の符号は、信号名に対応する信号配線についても同じ符号を付して説明する場合もある。

【0043】

図5に示す、データレート検出回路301が所定のパルス幅よりも短いパルス幅を検出する場合の動作では、所定のパルス幅をクロック信号のパルス幅とする。クロック信号420を、FF回路410,412,413,414,418に供給するが、所定のパルス幅(クロック信号のパルス幅)よりも短いパルス幅を検出する必要があるため、クロック信号420を反転した信号をFF回路411に供給する。

【0044】

例えば、データ信号419の状態が信号パターン“010”(501)の場合、所定のパルス幅よりも短いパルス幅なので検出する必要がある。このとき、FF回路410の出力信号401が“010”(502)、FF回路411の出力信号402が“000”(503,504)となる。出力信号401を受けてFF回路412の出力信号403が“010”(505)、出力信号402を受けてFF回路413の出力信号404が“000”(506,507)となる。出力信号404を受けてFF回路414の出力信号405が“000”(508,509)となる。出力信号403,404を受けてEXOR回路415の出力信号406が“010”(510)、出力信号403,405を受けてEXOR回路416の出力信号407が“010”(511)となる。出力信号406,407を受けてAND回路417の出力信号408が“010”(512)となる。出力信号408を受けてFF回路418の出力信号409が“010”(513)となる。

【0045】

一方、データ信号419の状態が信号パターン“0110”(514)の場合、所定のパルス幅よりも長いパルス幅なので検出する必要が無い。このとき、FF回路410の出力信号401が“010”(515)、FF回路411の出力信号402が“010”(516,517)となる。出力信号401を受けてFF回路412の出力信号403が“010”(518)、出力信号402を受けてFF回路413の出力信号404が“010”(519,520)となる。出力信号404を受けてFF回路414の出力信号405が“010”(521,522)となる。出力信号403,404を受けてEXOR回路415の出力信号406が“000”(523)、出力信号403,405を受けてEXOR回路416の出力信号407が“011”(524)となる。出力信号406,407を受けてAND回路417の出力信号408が“000”(525)となる。出力信号408を受けてFF回路418の出力信号409が“000”(526)となる。

【0046】

以上の動作により、データ信号419の状態が信号パターン“010”(501)の場合にはFF回路418の出力信号409が“010”(513)となり、データ信号419の状態が信号パターン“0110”(514)の場合にはFF回路418の出力信号409が“000”となるので、長短のパルス幅が混在しているデータ信号419の中から所定のパルス幅よりも短いパルス幅のみを検出することができる。

【0047】

このデータレート検出回路301の出力側に接続されるカウンタ回路302は、データレート検出回路301から供給される出力信号409のパルスをカウントし、制御回路304にその結果を供給する。

【0048】

図6は、図4に示すデータレート検出回路301が4.0GHz(250ps)のクロック信号420、2.5GHzのデータ信号419でパターン“0101010”を受けた場合の動作を示している。このデータ信号419の中に含まれる最も短いパルス幅は400psであり、所定のパルス幅(クロック信号420の1周期:250ps)より長いためにパルスが検出できず(出力信号409)、カウント回路302でのパルスのカウント数は“0”となる。

【0049】

図7は、図4に示すデータレート検出回路301が4.0GHz(250ps)のクロック信号420、8.0GHzのデータ信号419でパターン“0101010”を受けた場合の動作を示している。図6に示すデータ信号419のパターンとは異なり、最も短いパルス幅が125psであり、所定のパルス幅(クロック信号420の1周期:250ps)よりも短いことからパルスを検出することが可能であり(出力信号409)、カウント回路302でのパルスのカウント数は“3”となる。

【0050】

例えば、本発明を用いずにデータ信号のパルスをカウントすると、どちらのデータ信号もパルスのカウント数は“3”となり、周波数の区別がつかない。すなわち、本発明を用いることで、データレートによってパルスのカウント数に差異が生じ、その結果から周波数を判定することが可能である。

【0051】

このデータレート検出回路301に接続されるタイマー回路303は、データレートを判定する区間を制御する。データレートを判定する区間を制御することで、データレート判定後に不要な回路を停止することができるので、余分な電力の消費を抑えることができる。

【0052】

また、カウント回路302、タイマー回路303に接続される制御回路304は、カウント回路302でカウントした結果を受け、カウント数から周波数を判定し、その結果を出力する。この判定のために、予めカウント数がどの周波数に対応しているのかを設定しておくことが必要である。

【0053】

<実施の形態1の効果>

以上説明した本実施の形態1のデータ転送システムに備えられるデータ転送用の集積回路103のデータ転送を行う伝送系を構成する周波数判定回路201によれば、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路、具体的にはデータレート検出回路301、カウンタ回路302、タイマー回路303、および制御回路304を有することにより、長短のパルス幅が混在するデータ信号の周波数を判定することができる。そして、この周波数判定回路201を出力バッファの部分に備えたデータ転送用の集積回路103を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じて出力特性を変更することが可能となる。

【0054】

[実施の形態2]

本発明の実施の形態2を、図8〜図11に基づいて説明する。

【0055】

本実施の形態2における、データ転送を行う複数の集積回路を備えたデータ転送システムの構成(図1)、このデータ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成(図2)、このデータ転送用の集積回路のデータ転送を行う伝送系を構成する周波数判定回路の構成(図3)は、前記実施の形態1と同様であるので、ここでの説明は省略する。

【0056】

本実施の形態2は、周波数判定回路を構成するデータレート検出回路の部分の構成および動作が前記実施の形態1(図4)と異なり、以下においては、主にデータレート検出回路の部分の異なる点について説明する。

【0057】

<データレート検出回路の部分の構成および動作>

図8〜図11に基づいて、データレート検出回路301の部分の構成および動作の一例について説明する。図8は、このデータレート検出回路301の部分の構成の一例を示す回路図である。図9は、比較のためのデータレート検出回路301の部分の動作の一例(遅延回路821がない場合)を説明するための信号波形図である。図10は、データレート検出回路301の部分の動作の一例(遅延回路821がある場合)を説明するための信号波形図である。

【0058】

図8に示すデータレート検出回路301の部分は、図4に示したデータレート検出回路301に加えて、このデータレート検出回路301のデータ信号入力の前段に接続される遅延回路821を備えている。

【0059】

図8および後述する図9,図10において、420はクロック信号(CLK)、419はデータ信号(DATA)、822は遅延後のデータ信号、401〜409は出力信号、901〜913は信号パターン、1001〜1014は信号パターンを示している。

【0060】

図9は、遅延回路821が必要な理由を述べるための動作を示す図である。図4に示したデータレート検出回路301が図9に示すデータ信号419のパターンを受けた場合(901)、データ信号の中には所定のパルス幅よりも短いパルス幅が存在しているが、出力信号401(902)〜408(912)を経て出力信号409(913)に示すように、所定のパルス幅よりも短いパルス幅を検出することができないため、周波数を正確に判定することができない。

【0061】

一方、図10は、図8に示すデータレート検出回路301と遅延回路821の構成で、図9に示すデータ信号419を受けた場合の動作を示す図である。図8に示すデータレート検出回路301が図10に示すデータ信号419のパターンを受けた場合(1001)、データ信号419に遅延回路821で遅延を持たせたことにより(出力信号822(1002))、出力信号401(1003)〜408(1013)を経て出力信号409(1014)に示すように、所定のパルス幅よりも短いパルス幅を検出することが可能となり、周波数を正確に判定することができる。

【0062】

<実施の形態2の効果>

以上説明した本実施の形態2においても、前記実施の形態1と同様の効果が得られると共に、データレート検出回路301と遅延回路821の構成により、より一層、所定のパルス幅よりも短いパルス幅を検出することができるので、長短のパルス幅が混在するデータ信号の周波数を正確に判定することができる。

【0063】

<実施の形態2(実施の形態1)の変形例>

図11は、実施の形態2(実施の形態1)の変形例として、データレート検出回路301の部分を、データレート検出回路301を2段と遅延回路821で構成した例を示す回路図である。

【0064】

図11に示すデータレート検出回路301の部分は、データ信号(DATA)を直接受けるデータレート検出回路301(図11において上側)と、遅延回路821を介して遅延を持たせてから受けるデータレート検出回路301(図11において下側)を並列接続して組み合わせ、それぞれのパルスを検出することで、所定のパルス幅よりも短いパルス幅をパターンによらず検出することができる。よって、この実施の形態2(実施の形態1)の変形例では、実施の形態2(図8)に比べて、より一層、長短のパルス幅が混在するデータ信号の周波数を正確に判定することができる。

【0065】

[実施の形態3]

本発明の実施の形態3を、図12に基づいて説明する。

【0066】

本実施の形態3における、データ転送を行う複数の集積回路を備えたデータ転送システムの構成(図1)は、前記実施の形態1と同様であるので、ここでの説明は省略する。

【0067】

本実施の形態3は、データ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成が前記実施の形態1(図2)および2と異なり、以下においては、主にデータ転送用の集積回路のデータ転送を行う伝送系の構成の異なる点について説明する。

【0068】

なお、このデータ転送用の集積回路のデータ転送を行う伝送系を構成する周波数判定回路(図3)、この周波数判定回路を構成するデータレート検出回路(図4,図8)などは、前記実施の形態1および2と同様の回路を用いることができる。

【0069】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

図12に基づいて、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例について説明する。図12は、このデータ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0070】

図12に示すデータ転送用の集積回路のデータ転送を行う伝送系の構成は、図2に示したデータ転送用の集積回路のデータ転送を行う伝送系の構成に対して、周波数判定回路201と出力回路203との間に接続される特性制御回路1201を備えている点で異なる。

【0071】

この特性制御回路1201は、TAP係数をTAP信号1202,1203,1204,1205のいずれかから選択するセレクタ回路1206を備え、このセレクタ回路1206で、周波数判定回路201から出力される周波数判定の結果に応じてTAP係数をTAP信号1202,1203,1204,1205のいずれかに切り替えることができる回路である。例えば、このTAP係数のTAP信号1202,1203,1204,1205には、低い方から高い方へ順に、LLレベル、LHレベル、HLレベル、HHレベルなどの設定信号が一例として考えられる。

【0072】

この特性制御回路1201からの切り替え結果は出力回路203に入力され、この出力回路203の波形等化部が切り替えられたTAP係数に基づいて制御される。TAP係数を切り替えることにより、伝送路の周波数特性を打ち消すような出力エンファシス量を設定することができる。すなわち、この特性制御回路1201で伝送系の特性を制御することができる。

【0073】

<実施の形態3の効果>

以上説明した本実施の形態3においても、前記実施の形態1および2と同様の効果が得られると共に、特性制御回路1201により、TAP係数を切り替えて伝送路の周波数特性を打ち消すことができるので、伝送系の特性を制御することができる。そして、この特性制御回路1201を出力バッファの部分に備えたデータ転送用の集積回路を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じて波形等化部のTAP設定を動的に変更することが可能となる。

【0074】

[実施の形態4]

本発明の実施の形態4を、図13に基づいて説明する。

【0075】

本実施の形態4も、前記実施の形態3と同様に、データ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成が前記実施の形態1(図2)、2および3(図12)と異なり、以下においては、主にデータ転送用の集積回路のデータ転送を行う伝送系の構成の異なる点について説明する。

【0076】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

図13に基づいて、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例について説明する。図13は、このデータ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0077】

図13に示すデータ転送用の集積回路のデータ転送を行う伝送系の構成は、図12に示したデータ転送用の集積回路のデータ転送を行う伝送系の構成に対して、特性制御回路1301が、TAP係数を選択するのではなく、TAP生成の方式を選択する点で異なる。

【0078】

この特性制御回路1301は、ディレイを用いたTAP生成回路1302と、FFを用いたTAP生成回路1303と、これらの一方を選択するセレクタ回路1304を備えている。ディレイを用いたTAP生成回路1302は入力回路202に直接に接続され、FFを用いたTAP生成回路1303はCDR回路204に接続されている。

【0079】

この特性制御回路1301は、周波数判定回路201から出力される周波数判定の結果に応じて、ディレイを用いたTAP生成回路1302またはFFを用いたTAP生成回路1303を選択するための信号をセレクタ回路1304に供給することで、ディレイを用いたTAP生成回路1302またはFFを用いたTAP生成回路1303の一方を選択して、エンファシスを発生させるための回路である。すなわち、この特性制御回路1301で伝送系の特性を制御することができる。

【0080】

例えば、通常動作時には、CDR回路を使い入力信号をリタイミングするため、FFを用いたTAP生成回路1303を用いてTAP用波形を生成する。このFFを用いたTAP生成回路1303としては、4個のFFを従属接続して、PRE信号(−1cyc)とMAIN信号とPOST1信号(+1cyc)とPOST2信号(+2cyc)の4TAPなどの方式が一例として考えられる。一方、低速動作時には、CDR回路などのクロックを使用する回路を停止し、ディレイを用いたTAP生成回路1302を用いて波形を生成する。このディレイを用いたTAP生成回路1302としては、1個のディレイを用いて、MAIN信号とPOST1信号(+1cyc)の2TAPなどの方式が一例として考えられる。

【0081】

<実施の形態4の効果>

以上説明した本実施の形態4においても、前記実施の形態1および2と同様の効果が得られると共に、特性制御回路1301により、TAP生成の方式を切り替えて伝送路の周波数特性を打ち消すことができるので、前記実施の形態3と同様に伝送系の特性を制御することができる。そして、この特性制御回路1301を出力バッファの部分に備えたデータ転送用の集積回路を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じてTAP生成の方式を動的に変更することが可能となる。

【0082】

[実施の形態5]

本発明の実施の形態5を、図14に基づいて説明する。

【0083】

本実施の形態5も、前記実施の形態3および4と同様に、データ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成が前記実施の形態1(図2)、2、3(図12)および4(図13)と異なり、以下においては、主にデータ転送用の集積回路のデータ転送を行う伝送系の構成の異なる点について説明する。

【0084】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

図14に基づいて、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例について説明する。図14は、このデータ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0085】

図14に示すデータ転送用の集積回路のデータ転送を行う伝送系の構成は、図12に示したデータ転送用の集積回路のデータ転送を行う伝送系の構成に対して、非動作時の出力レベルを切り替える点で異なる。

【0086】

このデータ転送用の集積回路のデータ転送を行う伝送系の構成では、周波数判定回路201に特性制御回路1401が接続され、出力回路203の出力に電源とグランド間に直列接続した可変抵抗1402,1403(差動信号のP極)、1404,1405(差動信号のN極)が接続され、これらの可変抵抗1402,1403,1404,1405は周波数判定回路201からの出力により制御される。

【0087】

図14に示す特性制御回路1401は、周波数判定回路201から出力される周波数判定の結果に応じて、出力回路203の出力レベルを可変抵抗1402,1403,1404,1405により可変するための信号を出力することで、複数の規格に自動的に対応することができる回路である。すなわち、本実施の形態5は、前記実施の形態3,4とは異なり、転送レートに応じた特性の向上ではなく、転送レートが異なるような複数規格への自動的対応を可能としている。

【0088】

例えば、PCI−Expressと10G−Ether/FCのように異なる規格に対応する場合に、PCI−Expressモード時には、非動作時の出力レベルが中間レベルになるように設定しておき、HおよびL固定への変更も可能にして、周波数判定回路で10G−Ether/FCの転送レートと認識した場合には、非動作時の出力レベルをHまたはLに変更するなどの一例が考えられる。

【0089】

<実施の形態5の効果>

以上説明した本実施の形態5においても、前記実施の形態1および2と同様の効果が得られると共に、特性制御回路1401と可変抵抗1402,1403,1404,1405の構成により、出力回路203の出力レベルを可変して非動作時の出力レベルを切り替えることなどができるので、複数の規格に自動的に対応することができる。そして、この特性制御回路1401と可変抵抗1402,1403,1404,1405の構成を出力バッファの部分に備えたデータ転送用の集積回路を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じて非動作時出力レベルを動的に変更することが可能となる。

【0090】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0091】

本発明は、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路、およびこの周波数判定回路を備えた半導体装置に利用可能である。

【符号の説明】

【0092】

101…集積回路(送信側)、102…集積回路(受信側)、103…集積回路(データ転送用)、104…ボード、105…ボード、106…マザーボード、

201…周波数判定回路、202…入力回路、203…出力回路、204…CDR回路、205…PLL回路、206…セレクタ回路、

301…データレート検出回路、302…カウンタ回路、303…タイマー回路、304…制御回路、

401〜409…出力信号、410〜414…FF回路、415〜416…EXOR回路、417…AND回路、418…FF回路、419…データ信号、420…クロック信号、

501〜526…信号パターン、

821…遅延回路、822…出力信号、

901〜913…信号パターン、

1001〜1014…信号パターン、

1201…特性制御回路、1202〜1205…TAP信号、1206…セレクタ回路、

1301…特性制御回路、1302…ディレイを用いたTAP生成回路、1303…FFを用いたTAP生成回路、1304…セレクタ回路、

1401…特性制御回路、1402〜1405…可変抵抗。

【技術分野】

【0001】

本発明は、周波数判定回路の技術に関し、特に、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路、およびこの周波数判定回路を備えた半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

例えば、近年のIT装置の高速化に伴い、送受信LSI間を転送するデータレートが増大し、伝送路によって送信信号の劣化が起こるため、長距離高速伝送が困難になっている。このような問題に対して、波形整形の機能を有している、例えばバックプレーンシグナルコンディショナのようなLSIを送受信LSI間に挿入することで長距離高速伝送が実現できる。送受信LSI間に挿入するLSIは、複数の転送レートで動作するため周波数を判定する技術が要求される。

【0003】

例えば、特許文献1には、入力信号のサンプリング周波数を判別することができない問題に対して、予め定められた複数の周波数のうち、いずれか1つの周波数を有する入力クロック信号の周波数を判別する技術が示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−76965号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述したような特許文献1などを含む従来の周波数を判定する技術においては、複数の周波数の異なるデータ信号から周波数を特定する場合、データ信号のパルス数をカウントしても周波数を判定することは困難である。これは、データ信号のパターンは一定ではなく、長短のパルス幅が混在しているため、カウントしているパルス幅が必ずしも所定のパルス幅よりも短いパルス幅とは限らないからである。従って、長短のパルス幅が混在しているデータ信号の中から所定のパルス幅よりも短いパルス幅のみをカウントする必要がある。

【0006】

そこで、本発明は以上の課題に鑑みてなされたものであり、長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供することを主な目的とするものである。

【0007】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0009】

すなわち、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定することを特徴とする。

【0010】

具体的には、周波数判定回路は、所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路と、このデータレート検出回路で検出した信号をカウントするカウンタ回路と、周波数を判定する区間を制御するためのタイマー回路と、このタイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、カウンタ回路でカウントされたカウント数から周波数を判定する制御回路とを有することを特徴とする。

【0011】

また、上記のような特徴を有する周波数判定回路を備えた半導体装置にも適用することができる。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0013】

すなわち、長短のパルス幅が混在するデータ信号の周波数を判定することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態1における、データ転送を行う複数の集積回路を備えたデータ転送システムの構成の一例を示す図である。

【図2】本発明の実施の形態1において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【図3】本発明の実施の形態1において、周波数判定回路の構成の一例を示すブロック図である。

【図4】本発明の実施の形態1において、データレート検出回路の構成の一例を示す回路図である。

【図5】本発明の実施の形態1において、データレート検出回路の動作の一例を説明するための信号波形図である。

【図6】本発明の実施の形態1において、データレート検出回路の動作の一例(4.0GHzのクロック信号、2.5GHzのデータ信号の場合)を説明するための信号波形図である。

【図7】本発明の実施の形態1において、データレート検出回路の動作の一例(4.0GHzのクロック信号、8.0GHzのデータ信号の場合)を説明するための信号波形図である。

【図8】本発明の実施の形態2において、データレート検出回路の部分の構成の一例を示す回路図である。

【図9】本発明の実施の形態2において、比較のためのデータレート検出回路の部分の動作の一例(遅延回路がない場合)を説明するための信号波形図である。

【図10】本発明の実施の形態2において、データレート検出回路の部分の動作の一例(遅延回路がある場合)を説明するための信号波形図である。

【図11】本発明の実施の形態2において、データレート検出回路の部分の構成の変形例を示す回路図である。

【図12】本発明の実施の形態3において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【図13】本発明の実施の形態4において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【図14】本発明の実施の形態5において、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【発明を実施するための形態】

【0015】

以下の実施の形態においては、便宜上その必要があるときは、複数の実施の形態またはセクションに分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0016】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0017】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0018】

<本発明の実施の形態の概要>

本発明の実施の形態の周波数判定回路は、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路であって、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路(201)を有することを特徴とする。

【0019】

この周波数を判定する回路としては、具体的には、所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路(301)と、データレート検出回路で検出した信号をカウントするカウンタ回路(302)と、周波数を判定する区間を制御するためのタイマー回路(303)と、タイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、カウンタ回路でカウントされたカウント数から周波数を判定する制御回路(304)とを有することを特徴とする。

【0020】

以上説明した本発明の実施の形態の概要に基づいた、各実施の形態を以下において具体的に説明する。以下に説明する実施の形態は本発明を用いた一例であり、本発明は以下の実施の形態により限定されるものではない。

【0021】

[実施の形態1]

本発明の実施の形態1を、図1〜図7に基づいて説明する。

【0022】

<データ転送システムの構成>

まず、図1に基づいて、本実施の形態1における、データ転送を行う複数の集積回路(半導体装置)を備えたデータ転送システムの構成の一例について説明する。図1は、このデータ転送を行う複数の集積回路を備えたデータ転送システムの構成の一例を示す図である。

【0023】

図1に示すデータ転送システムは、送信側の集積回路101と、この集積回路101を実装するボード104と、受信側の集積回路102と、この集積回路102を実装するボード105と、データ転送用の集積回路103と、この集積回路103を実装したマザーボード106から構成され、送信側の集積回路101を実装したボード104と、受信側の集積回路102を実装したボード105が、データ転送用の集積回路103を実装したマザーボード106上に、コネクタ接続により実装されている。

【0024】

このデータ転送システムは、送信側の集積回路101からボード104およびマザーボード106を介してデータ転送用の集積回路103に電気的に接続され、さらに、データ転送用の集積回路103からマザーボード106およびボード105を介して受信側の集積回路102に電気的に接続されている。図1では、データ転送用の集積回路103を介して送信側の集積回路101から受信側の集積回路102へデータ転送を行う例を示している。データ転送用の集積回路103は、高速伝送路のリピータとしての機能および波形等化回路を備え、送信側の集積回路101からデータを受け取り、波形整形後のデータを受信側の集積回路102に転送する。

【0025】

このようなデータ転送システムにおいて、送信側の集積回路101、受信側の集積回路102、データ転送用の集積回路103のそれぞれは、例えば半導体基板上に各集積回路を形成した半導体チップなどの半導体装置として製造される。本発明では、これらの半導体装置のうち、データ転送用の集積回路103を形成した半導体装置に特徴を有し、以下において詳細に説明する。

【0026】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

次に、図2に基づいて、前述したデータ転送用の集積回路103のデータ転送を行う伝送系の構成の一例について説明する。図2は、このデータ転送用の集積回路103のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0027】

図2に示すデータ転送用の集積回路103は、周波数判定回路201と、入力回路(Rcv)202と、出力回路(Drv)203と、CDR(Clock Data Recovery)回路204と、PLL(Phase Locked Loop)回路205と、セレクタ回路206から構成される。

【0028】

入力回路202は、送信側の集積回路101からのデータを受け取り、周波数判定回路201、CDR回路204、セレクタ回路206に出力する。

【0029】

周波数判定回路201は、入力回路202から受け取ったデータについて、PLL回路205で生成した参照クロックに基づいて、周波数を判定し、この判定結果をセレクタ回路206に出力する。この周波数判定回路201は、詳細は後述するが、複数の周波数の異なるデータ信号から、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定することを特徴とする。

【0030】

CDR回路204は、入力回路202から受け取ったデータからクロックを抽出し、データを復元し、このデータをセレクタ回路206に出力する。

【0031】

PLL回路205は、位相同期制御により参照クロックを生成し、この参照クロックを周波数判定回路201に出力する。

【0032】

セレクタ回路206は、入力回路202から受け取ったデータと、CDR回路204で復元されたデータを入力として、周波数判定回路201からの判定結果に基づいて一方のデータを選択し、出力回路203に出力する。

【0033】

出力回路203は、セレクタ回路206で選択されたデータを、波形等化部で波形整形後、受信側の集積回路102に転送する。この出力回路203は、データを波形整形して出力する波形等化部を含む。

【0034】

<周波数判定回路の構成>

次に、図3に基づいて、前述した周波数判定回路201の構成の一例について説明する。 図3は、この周波数判定回路201の構成の一例を示すブロック図である。

【0035】

図3に示す周波数判定回路201は、データレート検出回路301と、カウンタ回路302と、タイマー回路303と、制御回路304から構成される。

【0036】

データレート検出回路301は、図2に示した入力回路202からのデータ(DATA)とPLL回路205からのクロック(CLK)を入力として、所定のパルス幅よりも短いパルス幅の信号を検出し、この検出結果をカウンタ回路302に出力する。

【0037】

カウンタ回路302は、データレート検出回路301からの検出結果から、このデータレート検出回路301で検出した信号をカウントし、このカウント結果を制御回路304に出力する。

【0038】

タイマー回路303は、周波数を判定する区間を制御し、この制御結果をデータレート検出回路301、カウンタ回路302、制御回路304に出力する。このタイマー回路303で、データレート(周波数)を判定する区間を制御することで、データレート判定後に不要な回路を停止することができる。

【0039】

制御回路304は、カウンタ回路302からのカウント結果、タイマー回路303からの制御結果を受けて、タイマー回路303で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、カウンタ回路302でカウントされたカウント数から周波数を判定し、この判定結果を図2に示したセレクタ回路206に出力する。この制御回路304の判定結果は、タイマー回路303にもフィードバックされる。この制御回路304では、カウント数から周波数を判定するために、予めカウント数がどの周波数に対応しているのかを設定しておく。

【0040】

<データレート検出回路の構成および動作>

次に、図4〜図7に基づいて、前述したデータレート検出回路301の構成および動作の一例について説明する。図4は、このデータレート検出回路301の構成の一例を示す回路図である。図5は、このデータレート検出回路301の動作の一例を説明するための信号波形図である。また、図6は4.0GHzのクロック信号、2.5GHzのデータ信号の場合の動作、図7は4.0GHzのクロック信号、8.0GHzのデータ信号の場合の動作をそれぞれ説明するための信号波形図である。

【0041】

図4に示すデータレート検出回路301は、データ信号の中から所定のパルス幅よりも短いパルス幅を検出する回路であり、FF(フリップフロップ)回路410,411,412,413,414と、EXOR(排他的論理和)回路415,416と、AND(論理積)回路417と、FF回路418から構成される。

【0042】

図4および後述する図5において、420はクロック信号(CLK)、419はデータ信号(DATA)、401〜409は出力信号、501〜526は信号パターンを示している。なお、420,419,401〜409の各信号の符号は、信号名に対応する信号配線についても同じ符号を付して説明する場合もある。

【0043】

図5に示す、データレート検出回路301が所定のパルス幅よりも短いパルス幅を検出する場合の動作では、所定のパルス幅をクロック信号のパルス幅とする。クロック信号420を、FF回路410,412,413,414,418に供給するが、所定のパルス幅(クロック信号のパルス幅)よりも短いパルス幅を検出する必要があるため、クロック信号420を反転した信号をFF回路411に供給する。

【0044】

例えば、データ信号419の状態が信号パターン“010”(501)の場合、所定のパルス幅よりも短いパルス幅なので検出する必要がある。このとき、FF回路410の出力信号401が“010”(502)、FF回路411の出力信号402が“000”(503,504)となる。出力信号401を受けてFF回路412の出力信号403が“010”(505)、出力信号402を受けてFF回路413の出力信号404が“000”(506,507)となる。出力信号404を受けてFF回路414の出力信号405が“000”(508,509)となる。出力信号403,404を受けてEXOR回路415の出力信号406が“010”(510)、出力信号403,405を受けてEXOR回路416の出力信号407が“010”(511)となる。出力信号406,407を受けてAND回路417の出力信号408が“010”(512)となる。出力信号408を受けてFF回路418の出力信号409が“010”(513)となる。

【0045】

一方、データ信号419の状態が信号パターン“0110”(514)の場合、所定のパルス幅よりも長いパルス幅なので検出する必要が無い。このとき、FF回路410の出力信号401が“010”(515)、FF回路411の出力信号402が“010”(516,517)となる。出力信号401を受けてFF回路412の出力信号403が“010”(518)、出力信号402を受けてFF回路413の出力信号404が“010”(519,520)となる。出力信号404を受けてFF回路414の出力信号405が“010”(521,522)となる。出力信号403,404を受けてEXOR回路415の出力信号406が“000”(523)、出力信号403,405を受けてEXOR回路416の出力信号407が“011”(524)となる。出力信号406,407を受けてAND回路417の出力信号408が“000”(525)となる。出力信号408を受けてFF回路418の出力信号409が“000”(526)となる。

【0046】

以上の動作により、データ信号419の状態が信号パターン“010”(501)の場合にはFF回路418の出力信号409が“010”(513)となり、データ信号419の状態が信号パターン“0110”(514)の場合にはFF回路418の出力信号409が“000”となるので、長短のパルス幅が混在しているデータ信号419の中から所定のパルス幅よりも短いパルス幅のみを検出することができる。

【0047】

このデータレート検出回路301の出力側に接続されるカウンタ回路302は、データレート検出回路301から供給される出力信号409のパルスをカウントし、制御回路304にその結果を供給する。

【0048】

図6は、図4に示すデータレート検出回路301が4.0GHz(250ps)のクロック信号420、2.5GHzのデータ信号419でパターン“0101010”を受けた場合の動作を示している。このデータ信号419の中に含まれる最も短いパルス幅は400psであり、所定のパルス幅(クロック信号420の1周期:250ps)より長いためにパルスが検出できず(出力信号409)、カウント回路302でのパルスのカウント数は“0”となる。

【0049】

図7は、図4に示すデータレート検出回路301が4.0GHz(250ps)のクロック信号420、8.0GHzのデータ信号419でパターン“0101010”を受けた場合の動作を示している。図6に示すデータ信号419のパターンとは異なり、最も短いパルス幅が125psであり、所定のパルス幅(クロック信号420の1周期:250ps)よりも短いことからパルスを検出することが可能であり(出力信号409)、カウント回路302でのパルスのカウント数は“3”となる。

【0050】

例えば、本発明を用いずにデータ信号のパルスをカウントすると、どちらのデータ信号もパルスのカウント数は“3”となり、周波数の区別がつかない。すなわち、本発明を用いることで、データレートによってパルスのカウント数に差異が生じ、その結果から周波数を判定することが可能である。

【0051】

このデータレート検出回路301に接続されるタイマー回路303は、データレートを判定する区間を制御する。データレートを判定する区間を制御することで、データレート判定後に不要な回路を停止することができるので、余分な電力の消費を抑えることができる。

【0052】

また、カウント回路302、タイマー回路303に接続される制御回路304は、カウント回路302でカウントした結果を受け、カウント数から周波数を判定し、その結果を出力する。この判定のために、予めカウント数がどの周波数に対応しているのかを設定しておくことが必要である。

【0053】

<実施の形態1の効果>

以上説明した本実施の形態1のデータ転送システムに備えられるデータ転送用の集積回路103のデータ転送を行う伝送系を構成する周波数判定回路201によれば、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路、具体的にはデータレート検出回路301、カウンタ回路302、タイマー回路303、および制御回路304を有することにより、長短のパルス幅が混在するデータ信号の周波数を判定することができる。そして、この周波数判定回路201を出力バッファの部分に備えたデータ転送用の集積回路103を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じて出力特性を変更することが可能となる。

【0054】

[実施の形態2]

本発明の実施の形態2を、図8〜図11に基づいて説明する。

【0055】

本実施の形態2における、データ転送を行う複数の集積回路を備えたデータ転送システムの構成(図1)、このデータ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成(図2)、このデータ転送用の集積回路のデータ転送を行う伝送系を構成する周波数判定回路の構成(図3)は、前記実施の形態1と同様であるので、ここでの説明は省略する。

【0056】

本実施の形態2は、周波数判定回路を構成するデータレート検出回路の部分の構成および動作が前記実施の形態1(図4)と異なり、以下においては、主にデータレート検出回路の部分の異なる点について説明する。

【0057】

<データレート検出回路の部分の構成および動作>

図8〜図11に基づいて、データレート検出回路301の部分の構成および動作の一例について説明する。図8は、このデータレート検出回路301の部分の構成の一例を示す回路図である。図9は、比較のためのデータレート検出回路301の部分の動作の一例(遅延回路821がない場合)を説明するための信号波形図である。図10は、データレート検出回路301の部分の動作の一例(遅延回路821がある場合)を説明するための信号波形図である。

【0058】

図8に示すデータレート検出回路301の部分は、図4に示したデータレート検出回路301に加えて、このデータレート検出回路301のデータ信号入力の前段に接続される遅延回路821を備えている。

【0059】

図8および後述する図9,図10において、420はクロック信号(CLK)、419はデータ信号(DATA)、822は遅延後のデータ信号、401〜409は出力信号、901〜913は信号パターン、1001〜1014は信号パターンを示している。

【0060】

図9は、遅延回路821が必要な理由を述べるための動作を示す図である。図4に示したデータレート検出回路301が図9に示すデータ信号419のパターンを受けた場合(901)、データ信号の中には所定のパルス幅よりも短いパルス幅が存在しているが、出力信号401(902)〜408(912)を経て出力信号409(913)に示すように、所定のパルス幅よりも短いパルス幅を検出することができないため、周波数を正確に判定することができない。

【0061】

一方、図10は、図8に示すデータレート検出回路301と遅延回路821の構成で、図9に示すデータ信号419を受けた場合の動作を示す図である。図8に示すデータレート検出回路301が図10に示すデータ信号419のパターンを受けた場合(1001)、データ信号419に遅延回路821で遅延を持たせたことにより(出力信号822(1002))、出力信号401(1003)〜408(1013)を経て出力信号409(1014)に示すように、所定のパルス幅よりも短いパルス幅を検出することが可能となり、周波数を正確に判定することができる。

【0062】

<実施の形態2の効果>

以上説明した本実施の形態2においても、前記実施の形態1と同様の効果が得られると共に、データレート検出回路301と遅延回路821の構成により、より一層、所定のパルス幅よりも短いパルス幅を検出することができるので、長短のパルス幅が混在するデータ信号の周波数を正確に判定することができる。

【0063】

<実施の形態2(実施の形態1)の変形例>

図11は、実施の形態2(実施の形態1)の変形例として、データレート検出回路301の部分を、データレート検出回路301を2段と遅延回路821で構成した例を示す回路図である。

【0064】

図11に示すデータレート検出回路301の部分は、データ信号(DATA)を直接受けるデータレート検出回路301(図11において上側)と、遅延回路821を介して遅延を持たせてから受けるデータレート検出回路301(図11において下側)を並列接続して組み合わせ、それぞれのパルスを検出することで、所定のパルス幅よりも短いパルス幅をパターンによらず検出することができる。よって、この実施の形態2(実施の形態1)の変形例では、実施の形態2(図8)に比べて、より一層、長短のパルス幅が混在するデータ信号の周波数を正確に判定することができる。

【0065】

[実施の形態3]

本発明の実施の形態3を、図12に基づいて説明する。

【0066】

本実施の形態3における、データ転送を行う複数の集積回路を備えたデータ転送システムの構成(図1)は、前記実施の形態1と同様であるので、ここでの説明は省略する。

【0067】

本実施の形態3は、データ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成が前記実施の形態1(図2)および2と異なり、以下においては、主にデータ転送用の集積回路のデータ転送を行う伝送系の構成の異なる点について説明する。

【0068】

なお、このデータ転送用の集積回路のデータ転送を行う伝送系を構成する周波数判定回路(図3)、この周波数判定回路を構成するデータレート検出回路(図4,図8)などは、前記実施の形態1および2と同様の回路を用いることができる。

【0069】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

図12に基づいて、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例について説明する。図12は、このデータ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0070】

図12に示すデータ転送用の集積回路のデータ転送を行う伝送系の構成は、図2に示したデータ転送用の集積回路のデータ転送を行う伝送系の構成に対して、周波数判定回路201と出力回路203との間に接続される特性制御回路1201を備えている点で異なる。

【0071】

この特性制御回路1201は、TAP係数をTAP信号1202,1203,1204,1205のいずれかから選択するセレクタ回路1206を備え、このセレクタ回路1206で、周波数判定回路201から出力される周波数判定の結果に応じてTAP係数をTAP信号1202,1203,1204,1205のいずれかに切り替えることができる回路である。例えば、このTAP係数のTAP信号1202,1203,1204,1205には、低い方から高い方へ順に、LLレベル、LHレベル、HLレベル、HHレベルなどの設定信号が一例として考えられる。

【0072】

この特性制御回路1201からの切り替え結果は出力回路203に入力され、この出力回路203の波形等化部が切り替えられたTAP係数に基づいて制御される。TAP係数を切り替えることにより、伝送路の周波数特性を打ち消すような出力エンファシス量を設定することができる。すなわち、この特性制御回路1201で伝送系の特性を制御することができる。

【0073】

<実施の形態3の効果>

以上説明した本実施の形態3においても、前記実施の形態1および2と同様の効果が得られると共に、特性制御回路1201により、TAP係数を切り替えて伝送路の周波数特性を打ち消すことができるので、伝送系の特性を制御することができる。そして、この特性制御回路1201を出力バッファの部分に備えたデータ転送用の集積回路を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じて波形等化部のTAP設定を動的に変更することが可能となる。

【0074】

[実施の形態4]

本発明の実施の形態4を、図13に基づいて説明する。

【0075】

本実施の形態4も、前記実施の形態3と同様に、データ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成が前記実施の形態1(図2)、2および3(図12)と異なり、以下においては、主にデータ転送用の集積回路のデータ転送を行う伝送系の構成の異なる点について説明する。

【0076】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

図13に基づいて、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例について説明する。図13は、このデータ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0077】

図13に示すデータ転送用の集積回路のデータ転送を行う伝送系の構成は、図12に示したデータ転送用の集積回路のデータ転送を行う伝送系の構成に対して、特性制御回路1301が、TAP係数を選択するのではなく、TAP生成の方式を選択する点で異なる。

【0078】

この特性制御回路1301は、ディレイを用いたTAP生成回路1302と、FFを用いたTAP生成回路1303と、これらの一方を選択するセレクタ回路1304を備えている。ディレイを用いたTAP生成回路1302は入力回路202に直接に接続され、FFを用いたTAP生成回路1303はCDR回路204に接続されている。

【0079】

この特性制御回路1301は、周波数判定回路201から出力される周波数判定の結果に応じて、ディレイを用いたTAP生成回路1302またはFFを用いたTAP生成回路1303を選択するための信号をセレクタ回路1304に供給することで、ディレイを用いたTAP生成回路1302またはFFを用いたTAP生成回路1303の一方を選択して、エンファシスを発生させるための回路である。すなわち、この特性制御回路1301で伝送系の特性を制御することができる。

【0080】

例えば、通常動作時には、CDR回路を使い入力信号をリタイミングするため、FFを用いたTAP生成回路1303を用いてTAP用波形を生成する。このFFを用いたTAP生成回路1303としては、4個のFFを従属接続して、PRE信号(−1cyc)とMAIN信号とPOST1信号(+1cyc)とPOST2信号(+2cyc)の4TAPなどの方式が一例として考えられる。一方、低速動作時には、CDR回路などのクロックを使用する回路を停止し、ディレイを用いたTAP生成回路1302を用いて波形を生成する。このディレイを用いたTAP生成回路1302としては、1個のディレイを用いて、MAIN信号とPOST1信号(+1cyc)の2TAPなどの方式が一例として考えられる。

【0081】

<実施の形態4の効果>

以上説明した本実施の形態4においても、前記実施の形態1および2と同様の効果が得られると共に、特性制御回路1301により、TAP生成の方式を切り替えて伝送路の周波数特性を打ち消すことができるので、前記実施の形態3と同様に伝送系の特性を制御することができる。そして、この特性制御回路1301を出力バッファの部分に備えたデータ転送用の集積回路を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じてTAP生成の方式を動的に変更することが可能となる。

【0082】

[実施の形態5]

本発明の実施の形態5を、図14に基づいて説明する。

【0083】

本実施の形態5も、前記実施の形態3および4と同様に、データ転送システムに備えられるデータ転送用の集積回路のデータ転送を行う伝送系の構成が前記実施の形態1(図2)、2、3(図12)および4(図13)と異なり、以下においては、主にデータ転送用の集積回路のデータ転送を行う伝送系の構成の異なる点について説明する。

【0084】

<データ転送用の集積回路のデータ転送を行う伝送系の構成>

図14に基づいて、データ転送用の集積回路のデータ転送を行う伝送系の構成の一例について説明する。図14は、このデータ転送用の集積回路のデータ転送を行う伝送系の構成の一例を示すブロック図である。

【0085】

図14に示すデータ転送用の集積回路のデータ転送を行う伝送系の構成は、図12に示したデータ転送用の集積回路のデータ転送を行う伝送系の構成に対して、非動作時の出力レベルを切り替える点で異なる。

【0086】

このデータ転送用の集積回路のデータ転送を行う伝送系の構成では、周波数判定回路201に特性制御回路1401が接続され、出力回路203の出力に電源とグランド間に直列接続した可変抵抗1402,1403(差動信号のP極)、1404,1405(差動信号のN極)が接続され、これらの可変抵抗1402,1403,1404,1405は周波数判定回路201からの出力により制御される。

【0087】

図14に示す特性制御回路1401は、周波数判定回路201から出力される周波数判定の結果に応じて、出力回路203の出力レベルを可変抵抗1402,1403,1404,1405により可変するための信号を出力することで、複数の規格に自動的に対応することができる回路である。すなわち、本実施の形態5は、前記実施の形態3,4とは異なり、転送レートに応じた特性の向上ではなく、転送レートが異なるような複数規格への自動的対応を可能としている。

【0088】

例えば、PCI−Expressと10G−Ether/FCのように異なる規格に対応する場合に、PCI−Expressモード時には、非動作時の出力レベルが中間レベルになるように設定しておき、HおよびL固定への変更も可能にして、周波数判定回路で10G−Ether/FCの転送レートと認識した場合には、非動作時の出力レベルをHまたはLに変更するなどの一例が考えられる。

【0089】

<実施の形態5の効果>

以上説明した本実施の形態5においても、前記実施の形態1および2と同様の効果が得られると共に、特性制御回路1401と可変抵抗1402,1403,1404,1405の構成により、出力回路203の出力レベルを可変して非動作時の出力レベルを切り替えることなどができるので、複数の規格に自動的に対応することができる。そして、この特性制御回路1401と可変抵抗1402,1403,1404,1405の構成を出力バッファの部分に備えたデータ転送用の集積回路を形成した半導体装置によれば、入力信号から動作レートを判断し、その結果に応じて非動作時出力レベルを動的に変更することが可能となる。

【0090】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0091】

本発明は、複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路、およびこの周波数判定回路を備えた半導体装置に利用可能である。

【符号の説明】

【0092】

101…集積回路(送信側)、102…集積回路(受信側)、103…集積回路(データ転送用)、104…ボード、105…ボード、106…マザーボード、

201…周波数判定回路、202…入力回路、203…出力回路、204…CDR回路、205…PLL回路、206…セレクタ回路、

301…データレート検出回路、302…カウンタ回路、303…タイマー回路、304…制御回路、

401〜409…出力信号、410〜414…FF回路、415〜416…EXOR回路、417…AND回路、418…FF回路、419…データ信号、420…クロック信号、

501〜526…信号パターン、

821…遅延回路、822…出力信号、

901〜913…信号パターン、

1001〜1014…信号パターン、

1201…特性制御回路、1202〜1205…TAP信号、1206…セレクタ回路、

1301…特性制御回路、1302…ディレイを用いたTAP生成回路、1303…FFを用いたTAP生成回路、1304…セレクタ回路、

1401…特性制御回路、1402〜1405…可変抵抗。

【特許請求の範囲】

【請求項1】

複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路であって、

前記複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有することを特徴とする周波数判定回路。

【請求項2】

請求項1記載の周波数判定回路において、

前記所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路と、

前記データレート検出回路で検出した信号をカウントするカウンタ回路と、

周波数を判定する区間を制御するためのタイマー回路と、

前記タイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、前記カウンタ回路でカウントされたカウント数から周波数を判定する制御回路とを有することを特徴とする周波数判定回路。

【請求項3】

請求項2記載の周波数判定回路において、

前記データレート検出回路の前段に、取り込んだデータ信号を遅延する遅延回路を有することを特徴とする周波数判定回路。

【請求項4】

請求項3記載の周波数判定回路において、

前記データレート検出回路の前段に前記遅延回路を接続した構成と、

前記データレート検出回路を有する構成とを並列接続して構成されることを特徴とする周波数判定回路。

【請求項5】

複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路を有する半導体装置であって、

前記周波数判定回路は、前記複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有することを特徴とする半導体装置。

【請求項6】

請求項5記載の半導体装置において、

前記周波数判定回路は、

前記所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路と、

前記データレート検出回路で検出した信号をカウントするカウンタ回路と、

周波数を判定する区間を制御するためのタイマー回路と、

前記タイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、前記カウンタ回路でカウントされたカウント数から周波数を判定する制御回路とを有することを特徴とする半導体装置。

【請求項7】

請求項6記載の半導体装置において、

前記データレート検出回路の前段に、取り込んだデータ信号を遅延する遅延回路が接続されていることを特徴とする半導体装置。

【請求項8】

請求項7記載の半導体装置において、

前記周波数判定回路は、前記データレート検出回路の前段に前記遅延回路を接続した構成と、前記データレート検出回路を有する構成とを並列接続して構成されることを特徴とする半導体装置。

【請求項9】

請求項5記載の半導体装置において、

前記周波数判定回路の判定結果に基づいて伝送系の特性を制御する特性制御回路をさらに有することを特徴とする半導体装置。

【請求項10】

請求項9記載の半導体装置において、

前記特性制御回路は、前記データ信号を波形整形して出力する波形等化部を含む出力回路に接続され、前記波形等化部のTAP係数を選択する回路を有することを特徴とする半導体装置。

【請求項11】

請求項9記載の半導体装置において、

前記特性制御回路は、前記データ信号を波形整形して出力する波形等化部を含む出力回路に接続され、前記波形等化部のTAP生成の方式を選択する回路を有することを特徴とする半導体装置。

【請求項12】

請求項9記載の半導体装置において、

前記特性制御回路は、可変抵抗を介して、前記データ信号を波形整形して出力する波形等化部を含む出力回路に接続され、前記可変抵抗を制御して前記出力回路の出力レベルを可変することを特徴とする半導体装置。

【請求項1】

複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路であって、

前記複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有することを特徴とする周波数判定回路。

【請求項2】

請求項1記載の周波数判定回路において、

前記所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路と、

前記データレート検出回路で検出した信号をカウントするカウンタ回路と、

周波数を判定する区間を制御するためのタイマー回路と、

前記タイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、前記カウンタ回路でカウントされたカウント数から周波数を判定する制御回路とを有することを特徴とする周波数判定回路。

【請求項3】

請求項2記載の周波数判定回路において、

前記データレート検出回路の前段に、取り込んだデータ信号を遅延する遅延回路を有することを特徴とする周波数判定回路。

【請求項4】

請求項3記載の周波数判定回路において、

前記データレート検出回路の前段に前記遅延回路を接続した構成と、

前記データレート検出回路を有する構成とを並列接続して構成されることを特徴とする周波数判定回路。

【請求項5】

複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路を有する半導体装置であって、

前記周波数判定回路は、前記複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有することを特徴とする半導体装置。

【請求項6】

請求項5記載の半導体装置において、

前記周波数判定回路は、

前記所定のパルス幅よりも短いパルス幅の信号を検出するデータレート検出回路と、

前記データレート検出回路で検出した信号をカウントするカウンタ回路と、

周波数を判定する区間を制御するためのタイマー回路と、

前記タイマー回路で制御された周波数を判定する区間内で、予め対応付けられたカウント数と周波数との関係に基づいて、前記カウンタ回路でカウントされたカウント数から周波数を判定する制御回路とを有することを特徴とする半導体装置。

【請求項7】

請求項6記載の半導体装置において、

前記データレート検出回路の前段に、取り込んだデータ信号を遅延する遅延回路が接続されていることを特徴とする半導体装置。

【請求項8】

請求項7記載の半導体装置において、

前記周波数判定回路は、前記データレート検出回路の前段に前記遅延回路を接続した構成と、前記データレート検出回路を有する構成とを並列接続して構成されることを特徴とする半導体装置。

【請求項9】

請求項5記載の半導体装置において、

前記周波数判定回路の判定結果に基づいて伝送系の特性を制御する特性制御回路をさらに有することを特徴とする半導体装置。

【請求項10】

請求項9記載の半導体装置において、

前記特性制御回路は、前記データ信号を波形整形して出力する波形等化部を含む出力回路に接続され、前記波形等化部のTAP係数を選択する回路を有することを特徴とする半導体装置。

【請求項11】

請求項9記載の半導体装置において、

前記特性制御回路は、前記データ信号を波形整形して出力する波形等化部を含む出力回路に接続され、前記波形等化部のTAP生成の方式を選択する回路を有することを特徴とする半導体装置。

【請求項12】

請求項9記載の半導体装置において、

前記特性制御回路は、可変抵抗を介して、前記データ信号を波形整形して出力する波形等化部を含む出力回路に接続され、前記可変抵抗を制御して前記出力回路の出力レベルを可変することを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−156676(P2012−156676A)

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願番号】特願2011−12743(P2011−12743)

【出願日】平成23年1月25日(2011.1.25)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願日】平成23年1月25日(2011.1.25)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]