周波数測定装置

【課題】複雑な回路を用いることなく、周波数測定分解能を改善した周波数変化の測定装置を提供する。

【解決手段】本発明の周波数測定装置は、供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応した、2つの値間にパルス列状に存在する一連のカウント値を出力する短ゲートタイムカウンタ部(20)と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタ(30)と、を備え、上記短ゲートタイムカウンタ部(20)は、上記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(自然数)ビットカウンタで上記一連のカウント値を出力する、ことを特徴とする。

【解決手段】本発明の周波数測定装置は、供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応した、2つの値間にパルス列状に存在する一連のカウント値を出力する短ゲートタイムカウンタ部(20)と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタ(30)と、を備え、上記短ゲートタイムカウンタ部(20)は、上記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(自然数)ビットカウンタで上記一連のカウント値を出力する、ことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、周波数の測定に関し、特に、僅かな周波数の変化を検出し得る測定法及び測定装置に関する。

【背景技術】

【0002】

周波数測定の方式には、決められたゲートタイム内に通過するパルスをカウントする直接カウント方式(特許文献1)と、パルス周期を正確に計測しその時間の逆数から周波数を求めるレシプロカル方式が知られている(非特許文献1)。直接カウント方式は比較的小規模の回路で実現することができるが、周波数分解能を高めるためにはゲートタイムを長く取る必要がある(例えば、0.1Hzの分解能を得るために必要なゲートタイムは10秒である。)。レシプロカル方式はこの欠点を克服することができるが、パルス間隔を正確に測定するための回路が直接カウント形式と比較して大規模となる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特表平6−501554号公報

【非特許文献】

【0004】

【非特許文献1】片野 和也, 連載第14回 時間測定器の使い方,測定器の正しい使い方入門, 月刊「トランジスタ技術」, p.331 (Feb.1994)

【発明の概要】

【発明が解決しようとする課題】

【0005】

水晶振動子を用いたQCM(Quartz Crystal Microbalance)法を使用することで振動子基板表面の微量の質量変化を周波数変化に変換することが出来る。例えば、ニオイ成分が付着する材料を振動子基板表面に設けることによって各種のニオイセンサを形成することが出来る。ニオイ成分は単体もしくは複数の物質で構成される。このニオイセンサに試料ガスを付与してニオイ成分を付着させ、振動子表面の質量を変化させると周波数が変化する。単数もしくは複数の種類のセンサを用意しこの変化を観察することによって、特定のニオイ成分が存在することを推定する。人の鼻には350種類程度の嗅細胞が存在し、犬の鼻の場合は1000種類程度存在すると言われており、各々の嗅細胞に付着するニオイ成分の割合を脳がパターン認識することでニオイを識別している。生体の嗅覚に学ぶと、ニオイ成分を検出し特定するためには、多数のニオイセンサ(センサアレイ)を使用し、各センサの出力パターンをコンピュータで解析してニオイ成分のパターンを特定することが必要である。

【0006】

しかしながら、各ニオイセンサの周波数変化を検出するために各センサの出力に周波数変化を検出するカウンタや信号処理回路を設けなければならない。更に、水晶振動子の周波数(例えば、30MHz)が付着物質によって変化するといってもわずか数Hzから数100Hz程度のものでしかなく、1Hz以下の変化である場合もある。上述したように直接カウント方式では、周波数分解能を高めるためにはゲートタイムを相当に長く取る必要がある。測定の際の誤差として、プラスマイナス1カウント誤差、トリガレベルの揺らぎによる誤差に加え、ゲートタイムを長くした場合、水晶振動子の発振安定性に起因する誤差が重畳されることになる。レシプロカル方式のカウンタを用いることでこのような欠点を補うことができるが、1つのカウンタの回路が大規模となるため多数のセンサを備えるセンサアレイには不向きである。

【0007】

よって、本発明の目的は複雑な回路を用いることなく、周波数測定分解能を改善した周波数変化の測定装置を提供することである。また、周波数測定に用いるカウンタ回路を可及的に簡素に構成し得る周波数の測定装置を提供することである。

【課題を解決するための手段】

【0008】

上記目的を達成するため、本発明の周波数測定装置は、供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、を備え、上記短ゲートタイムカウンタ部は、上記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(nは2以上の自然数である。)ビットカウンタで上記一連のカウント値を出力する、ことを特徴とする。

【0009】

かかる構成においては、まず、ゲートタイムを短くして被測定パルス列信号をサンプリングすることで周波数に対応するカウント値がパルス列として振る舞う(時間軸上のある範囲において、2つの値のいずれかとなるパルス列状の一連のカウント値として出力される)。このとき、被測定周波数の変化に応じたパルス列の密度変化が測定される。このパルス列をローパスフィルタに通すことでパルス列から被測定周波数信号を得る。被測定周波数信号の周波数変化範囲がある範囲内である場合には、フルレンジのカウンタの上位ビットには変化がなく、下位nビット部分に周波数変化が現れる。したがって、nビットのカウンタを使用することで周波数変化を抽出することが出来、フルレンジのカウンタ回路を簡易な構成に置き換えることか可能となる。

【0010】

好ましくは、上記nが2〜4ビットである。2ビット以上のカウンタとすることによって、カウント値の一連の変化からオーバーフロー(桁上がり)やアンダフロー(桁下がり)の発生を判別することが出来る。例えば、3ビットのカウンタとすることによって、2ビットカウンタの場合よりもオーバーフロー(桁上がり)やアンダフロー(桁下がり)の発生をより減少することが可能となり、カウント値の補正やサンプリング周波数の調整の回数を減少することが出来る。

【0011】

上記周波数測定装置は、更に、上記供給されるパルス列信号をm(自然数)分周して上記短ゲートタイムカウンタ部に供給する分周器(プリスケーラ)と、上記ローパスフィルタから出力されるレベル信号をm倍する乗算器と、を含むことが望ましい。

それにより、供給されるパルス列信号が高周波数である場合、高速で動作する分周器を前段に設けることで、後続するカウンタ部以降を相対的に低速動作の回路で構成することが可能となる。これは消費電力の低減にもなる。また、分周率mを可変にすることでカウンタ部に供給されるパルス列信号の見かけの周波数を切り換えることが可能となって具合が良い。

【0012】

また、本発明の周波数測定装置は、供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を得るローパスフィルタと、を備え、上記短ゲートタイムカウンタ部は、上記パルス列信号が供給される1ビットカウンタと、上記パルス列信号の周波数を増加又は減少させると共にこれに対応して上記1ビットカウンタから出力されるカウント値の増減方向を判別し、該判別結果に基づいて該1ビットカウンタのカウント値の正逆を決定する極性判別回路とを含む。

【0013】

被測定パルス列信号の周波数変化が少ない場合には1ビットのカウンタで短ゲートカウンタ部をより簡易に回路構成することが可能である。ただ、この場合には、カウントしている“0”と“1”の値が大小(真値)を意味しているのか、補数を意味するのかが不明であるので、極性判別回路によってパルス列信号の周波数を一方向に変化させ、これに対応してカウント値が増加したか減少したかを判別することによってカウント値の意味(真値か、補数値か)を判別可能とする。

【0014】

カウント値が真値を表しているのか、補数値を表しているのかについては、被測定周波数およびサンプリング周波数(ゲートタイム)の関数として表されるため、これらの値が既知であるか、もしくは被測定周波数を1度だけ別途測定することで既知とすることで知ることができる。この場合は、上記極性判別回路は省略できる。

【0015】

好ましくは、上記nビットカウンタの上位pビットをカウンタ出力とし、その下位(m−p)ビットを分周器として使用する。それにより、分周器とカウンタの機能を1つのカウンタで実現できる。例えば、4ビットカウンタの上位2ビットを出力ビットとすることで、下位2ビットによって、1/4分周器が構成される。

【0016】

また、本発明の周波数測定装置は、供給されるパルス列信号をm(mは自然数)分周する分周器と、分周されたパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、上記ローパスフィルタから出力されるレベル信号をm倍する乗算器と、を備える。

【0017】

かかる構成とすることによって、分周器部分のみを高速化すれば良く、短ゲートタイムカウンタ部以降を相対的に低速で動作させることが可能となって具合がよい。上記ローパスフィルタから出力される値は被測定パルス信号の周波数の1/m倍であるため、m倍することで適切なスケーリングを行うことができる。また、分周率mを可変にすることでカウンタ部に供給されるパルス密度を切り換えることが可能となって具合が良い。

【0018】

ここで、スケーリングのための乗算回路を設けたが、スケーリングを気にしなくても良い場合はこれを省略することができる。

【0019】

上記ゲート時間は1秒よりも小さく装置の動作限界よりも大きい時間である。例えば、上記ゲート時間は1秒よりも小さく0.01μ秒よりも大きい時間である。

【0020】

望ましくは、上記ゲート時間は1秒よりも小さく装置の動作限界よりも大きい時間である。例えば、0.1m秒程度のゲートサンプリングを行う場合、従来の直接カウント方式に比べ、例えば、時間分解能で1〜2桁、SN比で2〜3桁程度の性能向上を期待することが出来る。周波数のカウントとデータ収録をハードウエアにより行う構成とすることで、1μ秒を下回るゲート時間で測定を行うこともできる。

【0021】

望ましくは、上記短ゲートタイムカウンタ部は、上記パルス列信号に対して不感期間を生じないカウンタを備える。ここで、不感期間とは、カウンタのリセットやカウント値の転送時に生ずる、カウンタに入力されるパルス列信号を測定することが出来ない期間である。後述するように、短ゲートタイムカウンタ部の出力パルス列にカウンタのリセット動作などによって不連続が生じると、前後のデータ列(値)が遮断されて一種の外乱となるので好ましくない。

【0022】

望ましくは、上記ローパスフィルタが、アナログフィルタ又はデジタルフィルタである。

【0023】

上記ローパスフィルタがアナログフィルタであることが望ましい。デジタルフィルタで必要となるメモリと演算装置を省くことが出来る。また、短ゲートタイムカウンタ部のカウント値が2値を取りパルス列として振舞う場合(図4)、アナログフィルタのローパスフィルタがD−A変換器として機能するので具合がよい。カウンタの出力がnビットデータの場合には、ローパスフィルタの前段にD−A変換器を用いる構成とすることが出来る。

【0024】

上記ローパスフィルタがデジタルフィルタであることが望ましい。移動平均フィルタであることはより望ましい。移動平均フィルタは、一般のFIRフィルタ(有限インパルス応答フィルタ)に比べて回路規模が相対的に小さく計算量が少なく構成することができ、IIRフィルタ(有限インパルス応答フィルタ)に比べても、直線位相特性を実現でき安定性も保証できるなど、FIRフィルタの持つ利点をそのまま享受することができる。

【0025】

上記ローパスフィルタが、移動平均フィルタを多段(2段以上)に直列接続した構成であることが望ましい。多段移動平均フィルタは1段の移動平均フィルタに比べ、計算量の増加を最小限に抑えつつローパスフィルタとしての性能を向上できる利点がある。

【0026】

上記不感期間を生じないカウンタが、上記パルス列信号を累積的に計数する直接カウント方式のカウンタと、計数された前回の累積カウント値と今回の累積カウント値との差から今回カウント値を得る減算器と、を含むことが望ましい。それにより、2つのカウンタを用いて交互に動作させずとも不感期間のないカウンタを構成することが可能となる。

【0027】

望ましくは、上記ローパスフィルタは、デジタルフィルタとアナログフィルタとを組み合わせたものである。それにより、SN比の良いデジタルフィルタと演算の必要のないアナログフィルタの利点を組み合わせることができる。デジタルフィルタのみの処理に比べてデジタルフィルタとアナログフィルタの組み合わせでは、デジタルフィルタのローパスフィルタとしての性能はそれほど要求されないのでタップ数を大幅に削減することができる。例えば、デジタルフィルタに1段の移動平均フィルタを用いる場合、フィルタ処理にアップダウンカウンタを用いることができるので、タップ数の削減に加えて回路も簡素化することができる。

【0028】

また、本発明の周波数の測定方法は、供給されるパルス列信号を短ゲートタイムカウンタで短いゲート時間で連続的に計数し、該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を得て、この一連のカウント値からローパスフィルタで高周波成分を除去し、上記供給されるパルス列信号の周波数に対応するレベル信号を得るものであり、上記短ゲートタイムカウンタとして、上記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(nは2以上の自然数)ビットカウンタを用いて上記一連のカウント値を出力する。好ましくは、上記nが2〜4ビットである。比較的に簡易な構成で周波数測定を行うことが可能となる。

【0029】

更に、上記供給されるパルス列信号を分周器で分周して前記短ゲートタイムカウンタ部に供給すると共に、上記ローパスフィルタから出力されるレベル信号を乗算器でスケーリングする。それにより、パルス列信号の見かけ上の周波数を下げることが可能となる。

【図面の簡単な説明】

【0030】

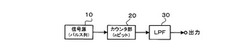

【図1】本願発明の概要を説明する図である。

【図2】短ゲートカウンタ部20の構成例を説明する図である。

【図3】短ゲートカウンタ部20の他の構成例を説明する図である。

【図4】短ゲートカウンタ部20によるカウント値の例を説明する図である。

【図5】ローパスフィルタ30の出力例を示す図である。

【図6】短ゲートタイム方式を説明する説明図である。

【図7】短ゲートタイム方式による出力例を説明する説明図である。

【図8】短ゲートタイム方式による効果例を説明する説明図である。

【図9】入力の不連続の影響を説明する図である。

【図10】ローパスフィルタ(アナログ)の例を説明する図である。

【図11】ローパスフィルタ(アナログ)の出力例を説明する図である。

【図12】ローパスフィルタ(移動平均)の例を説明する図である。

【図13】移動平均計算の例を説明する図であり、図中の2行目の数列が1段移動平均フィルタ出力値(1段目のタップ数10)に相当し、3行目の数列が2段移動平均フィルタ出力値(2段目のタップ数10)に相当する。

【図14】ローパスフィルタ(移動平均)のインパルス応答例を説明する図である。

【図15】ローパスフィルタ(移動平均)の出力例を説明する図である。

【図16】ローパスフィルタをデジタルフィルタとアナログフィルタとを組み合わせて構成する例を説明する図である。

【図17】参考例のデジタルフィルタ(移動平均フィルタ3段構成)の出力例を説明する図である。

【図18】参考例のアナログフィルタの出力例を説明する説明図である。

【図19】デジタルフィルタ(移動平均フィルタ1段構成)の出力をD/A変換した出力例を説明する図である。

【図20】D/A変換値をアナログフィルタによって処理した例を説明する図である。

【図21】短ゲートカウンタ部をnビットのカウンタで構成する例を説明する図である。

【図22】3ビットカウンタの出力例を説明する説明図である。

【図23】ローパスフィルタの出力例を説明する図である。

【図24】短ゲートカウンタ部20を2ビットカウンタで構成する例を説明する図である。

【図25】2ビットカウンタの出力例を説明する説明図である。

【図26】ローパスフィルタの出力例を示す図である。

【図27】2ビット出力の短ゲートカウンタ部の後段に2ビット出力を4ビット出力に変換する回路を設けた例を説明する図である。

【図28】2ビットカウンタの出力例を説明する説明図である。

【図29】ローパスフィルタへの4ビット入力値の例を説明する説明図である。

【図30】4ビット入力されローパスフィルタの出力例を示す図である。

【図31】1ビットカウンタで短ゲート部を構成した例を説明する図である。

【図32】1ビットカウンタで短ゲート部を構成した場合の出力例を示す図。

【図33】1ビットカウンタの出力が補数である場合の出力例を示す図である。

【図34】補数出力を補正した出力例を説明する図である。

【図35】短ゲートカウンタの前段に分周器を用いる例を説明する図である。

【図36】分周器を用いた場合の出力例を説明する図である。

【図37】4ビットカウンタの上位2ビットを出力に使用してプリスケーラとカウンタとして機能させる例を説明する説明図である。

【図38】4ビットカウンタの上位2ビットを使用した場合の出力例を示す図である。

【図39】センサアレイに本願を適用した例を説明する図である。

【図40】従来の方法によるセンサアレイの出力例を示す図である。

【図41】本願の方法によるセンサアレイの出力例を示す図である。

【発明を実施するための形態】

【0031】

以下、図面を参照して本発明の実施の形態について説明する。図1乃至図3は、本発明の周波数測定装置の概略を示している。各図において、対応する部分には、同一符号を付している。

【0032】

図1において、信号源10はパルス列信号を発生する。信号源10は、例えば、発振周波数f0が30MHzの水晶発振器であり、後述のニオイセンサ、ガスセンサ、バイオセンサなどの検出部に相当する。ニオイ物質などが水晶振動子に付着すると付着量に応じて発振周波数が低下する。このパルス列信号は短ゲートタイムカウンタ(以下、単に「短ゲートカウンタ」と称する。)部20に供給される。短ゲートカウンタ20は、供給されるパルス列信号のパルス計数を短いゲート時間で途切れることなく行う。カウント値はパルス列信号の周波数と対応関係にあり、ローパスフィルタ(LPF)30に逐次供給される。

【0033】

図4はカウント値の例を示している。この例では、サンプリング周波数100Hz(ゲート時間0.01秒)でパルス列信号を計数した場合を示している。サンプリング周波数100Hzの場合には、周波数分解能も100Hzまで低下するため、1つの計数値のみからは供給パルス列信号の100Hz以下の情報を検出できないが、1秒間に100個の計数値が得られることになる。計数値の100倍である周波数は、30,072,300Hzと30,072,400Hzの間に時間軸上にパルス状に分布している。

【0034】

ここで、サンプリングにおける量子化誤差(±1カウント誤差)について説明する。例えば、直接カウント方式のカウンタで123.34Hzで安定しているパルス列信号を測定する場合について検討する。

【0035】

ゲート時間10秒の場合: 10秒ごとに1233カウント又は1234カウント

【0036】

これを1/10倍した、123.3Hzもしくは123.4Hzの表示(10秒ごと)となる。(測定誤差は0.1Hz)

【0037】

ゲート時間1秒の場合: 1秒ごとに123カウント又は124カウント

【0038】

123Hzもしくは124Hzの表示(1秒ごと)となる。(測定誤差は1Hz)

【0039】

ゲート時間0.1秒の場合: 0.1秒ごとに12カウント又は13カウント

【0040】

これを10倍した、120Hzもしくは130Hzの表示(0.1秒ごと)となる。(測定誤差は10Hz)

【0041】

ゲート時間0.01秒の場合: 0.01秒ごとに1カウント又は0カウント

【0042】

これを100倍した、100Hzもしくは200Hzの表示(0.01秒ごと)となる。(測定誤差は100Hz)

【0043】

このように、ある一点の周波数で安定しているパルス列信号をカウントした場合は

ゲート時間に対応した量子化誤差が生じ、計数値はゲート時間によって定まる2つの値間を振幅とするパルス列状に分布する。一方、カウントするパルス列信号の周波数が変動する場合でも、変動が上記測定誤差に収まる範囲であれば、計数値は2つの値間を振幅とするパルス列状に分布するのに変わりない。例えばゲート時間0.01秒の場合、カウントするパルス列信号の周波数の変動が100〜200Hzの間で収まっている限り、100Hzもしくは200Hzの表示が得られる。

【0044】

図4に示すように、1秒未満の短いゲート時間でサンプリングを行う方式(以下、「短ゲートタイムカウント方式」という。)では、カウント値がパルス列として振る舞い、被測定周波数の変化に応じパルス列の頻度(粗密)が変化する。振動周波数の大小が当該パルス列の密度の大小に対応する。カウントするパルス列信号の周波数に関する情報は、パルス列として振る舞うカウント値の周波数スペクトルの低域成分に存在する。そこで、ローパスフィルタによってカウント値から低域成分を抽出する(量子化誤差に起因する高調波成分を除去する)ことによってカウントするパルス列信号の周波数の情報を復調することが出来る。

【0045】

図5は、上述した図4のカウント値の列をタップ数512の(デジタル)ローパスフィルタ30に与えて高周波成分を除去した例を示している。同図に示されるように供給されたパルス列信号の周波数の変化が連続的な(アナログ的)な曲線として出力される。100Hzのサンプリング周期の計数では測定不能な領域まで、特に、1Hz以下の周波数変化まで検出することが可能となっている。

【0046】

次に、短ゲートタイムカウント方式と直接カウント方式との比較について図6及び図7を参照して説明する。

【0047】

図6のグラフにおいて、縦軸は周波数、横軸は時間を表している。図中の曲線Aは、直接カウント方式でゲート時間を1秒に設定してサンプリングを行った場合を示している。曲線Bは、直接カウント方式でゲート時間を0.1秒に設定してサンプリングを行った場合を示している。曲線Cは、直接カウント方式でゲート時間を0.01秒に設定してサンプリングを行った場合を示している。なお、曲線Cは、時間軸の単位(桁)が異なり同一グラフ上に波形を表せないので下方に別途表示されている。曲線Dは、直接カウント方式でゲート時間を0.01秒+ローパスフィルタに設定してサンプリングを行った場合(短ゲートタイムカウント方式)を示している。図7は、図6の周波数軸のレンジを拡大して、曲線A及び曲線Dを比較している。本願の曲線Dは数10mHzオーダーまで読み取ることが出来る。

【0048】

図6より、ゲート時間が1秒未満であることによって、カウントするパルス列信号の周波数変化が測定誤差内に収まるためカウント値が2値のいずれかとなりパルス列状になることが判る。パルス頻度(パルス密度)は周波数の変化の大小に応じて変化することが判る。すなわち、パルス列状に振る舞うカウント値は時間軸方向にカウントするパルス列信号の周波数情報を含んでいることが判る。したがって、ゲート時間を短くしたことにより一つの計測値に含まれる測定誤差は拡大するが、ローパスフィルタによりこの影響は取り除かれ、SN比は改善される。ゲート時間が1秒の場合には、曲線がジグザクとなって1Hz以下の周波数が判らないが、これをローパスフィルタによって高周波成分を除去する処理を行えば本願の特性に類似する滑らかな特性を同様に得ることが出来る。したがって、ゲート時間が1Hzでも周波数変化の帯域が1Hzよるも低くゆっくりした変化の場合には本方式を適用することが可能である。

【0049】

このように、短ゲートタイムカウント方式では、ゲート時間を短くする(サンプリング周波数を高くする)と、各々の測定誤差は大きくなるがたくさんの測定値の列が得られ、ローパスフィルタによって高域成分を取り除くことが出来、図8に示すように、周波数測定分解能は向上する。回路規模を小さく抑えることができるため、マルチチャンネル化が容易である。アナログローパスフィルタを用いることによってアナログ出力にも対応することが可能である。

【0050】

図2は、上述した短ゲートカウンタ部20の第1の構成例を示している。短ゲートカウンタ部20は、信号源から供給されるパルス列信号を途切れることなく計数する(入力信号に対して不感期間を設けないように)ことが望まれる。

【0051】

図9は、計数が途切れた場合(ローパスフィルタへの計数値列が欠けた場合)のローパスフィルタの周波数出力例を示している。同図中に点線の円で示されるように外乱となることが判る。

【0052】

そこで、第1の実施例では、第1カウンタ21と第2カウンタ22の2つのカウンタを備える構成とする。パルス列信号は第1カウンタ21と第2カウンタ22の両方に供給される。制御部23は両カウンタにゲート信号、リセット信号を夫々送り、両カウンタの出力をスイッチを介してローパスフィルタ30に供給する。両カウンタから計数値を交互に出力し、一方が計数しているときに他方がリセットやデータ転送などをすることによって、カウンタのリセットやデータ転送時に生ずる不感期間を回避する。なお、制御部23はハードウエアとして構成しても良いし、パソコンなどによってソフトウェアで構成しても良い。

【0053】

図3は、短ゲートカウンタ部20の第2の構成例を示している。この実施例では1つのカウンタ24を用いている。カウンタ24は直接カウント方式のカウンタであり、サンプリングしたパルス信号を常時計数し累積値を出力する(リセットしない)。カウンタ24の出力は減算器25と前回累積値を保持するレジスタ26に送られる。減算器25はカウンタ24から出力される今回累積値から前回累積値を減じて今回計数値を得て、ローパスフィルタ30に供給する。装置全体の動作は図1の測定装置の場合と同様である。

【0054】

図10は、ローパスフィルタ30をアナログ回路で構成した例を示す。この例では、抵抗R1〜R3、キャパシタC1,C2、オペアンプOP1からなるローパスフィルタを二段接続としている。短ゲートカウンタ20から1ビットシリアルで出力される場合には、そのままローパスフィルタ30に入力することが出来る。短ゲートカウンタ20からnビットで出力される場合には、D−A変換器を介して入力することが出来る。

【0055】

図11は、サンプリング周波数を1000Hzとした場合のアナログローパスフィルタ30の出力例を示している。

【0056】

図12は、ローパスフィルタ30を移動平均フィルタによって構成した例を示す。同図において、31は加算器、32はシフトレジスタ、33は減算器、34はインバータ、35は各部に動作タイミングクロックを供給する制御部。36は割算器である。

【0057】

カウンタから出力された計数値は、加算器31とタップ数相当の記憶領域を備えるシフトレジスタ32の両方に与えられる。シフトレジスタ32内を平均値計算の対象となるN個のデータが他と同期して順次移動する。加算器31の他方には前回計算のトータル値が供給されており、加算器は新計数値と前回のトータル値とを加算する。この累積加算値からシフトレジスタ32で先頭の(旧い)データの計数値を減算器33で除き、これを新トータル値とする。新トータル値を前回トータル値として加算器に戻し、新トータル値を除算器36で対象データ数Nで割り算する。このような計算を全データについて行うことによって移動平均値が求められる。ここで、割算器は出力値を周波数(Hz)にスケーリングする機能を持つが、スケーリングを気にしなくても良い場合は省略することができる。また、移動平均フィルタを多段の構成とする場合、最終段にのみ割算器を配しても良い。

【0058】

図13は、移動平均フィルタの出力を概略的に説明する図である。この例では、計測の対象となるパルス列信号の周波数が123.34Hzを維持している状態から124.7Hzに徐々に変化するものとする。まず、ゲート時間0.1秒でサンプリングすると、カウンタ20から、12または13の計数値がある割合で送られる。10個のデータのトータルの3つの組は124、123、125…となって124.7Hz方向に値が移動する。ここで、12または13の計数値の10個(タップ数10)を移動平均計算の対象とする(一段目の移動平均)。一段目の移動平均値より、右方向に移動するにつれて数値が増えたデータの出現が増加することがわかる。更に、一段目の移動平均値を入力として2段目の移動平均(タップ数10)の計算を行うとこの傾向は強められ、精度も向上する。移動平均フィルタを多段用いることは、ローパスフィルタの特性である減衰傾度を急峻にすることに相当し、同時に12または13からなるパルス列の周波数スペクトルから高域成分を取り除くことに相当する。

【0059】

実施例では、移動平均フィルタ(ローパスフィルタ)を三段接続している(タップ数全体4096、タップ数818(一段)、1640(二段)、1640(三段)の三段移動平均フィルタ)。

【0060】

図14は、上記三段移動平均フィルタのインパルス応答を示している。図15は、上記三段移動平均フィルタの出力例を示している。このように、1Hz以下の周波数変化を測定することが出来る。なお、移動平均フィルタは所望の特性を得るために多段構成とすることができる。

【0061】

次に、デジタルフィルタとアナログフィルタとの組み合わせによってローパスフィルタ30を構成する場合について図16乃至図20を参照して説明する。

【0062】

図16は、ローパスフィルタ30をデジタルフィルタ(ローパスフィルタ)30a、D/A変換器30b及びアナログフィルタ(ローパスフィルタ)30cによって構成した例を示している。この構成には以下のような利点がある。

【0063】

まず、サンプリング周波数が高く、被測定周波数の信号変化がサンプリング周波数に対して小さいとき、デジタルフィルタ処理では問題なく復調することができる場合でも、アナログフィルタ処理ではSN比が低下する場合がある。これは、被測定周波数の信号変化に対応するフィルタ処理後の出力の変化が、パルスの振幅に比べて小さいために見掛けのダイナミックレンジが縮小することによる。デジタルフィルタ処理の場合には、量子化されたカウント値の情報は劣化しないので、このような問題は生じない。

【0064】

例えば、1000Hzのサンプリング周波数を用い、100Hzの周波数変化を観測しようとした場合であれば、1000mVのパルスをアナログフィルタ処理すると100mVの電圧変化を観察することになる。同様の条件で、0.1Hzの周波数変化を観察しようとした場合、電圧変化は0.1mVとなる。そのため、例えば、測定に1mVのノイズが存在する環境では0.1Hzの信号を検出することができない。

【0065】

一方、カウント値として量子化された周波数の情報は、デジタル処理により劣化することはないので、デジタルフィルタ処理の場合はこのような問題は生じない。したがって、デジタルフィルタと組み合わせることでSN比を改善することができる。具体的には、上述のようにデジタルフィルタ30aの出力をDA変換器30bによってD−A変換し、アナログフィルタ30cに入力する構成とする。

【0066】

デジタルフィルタのみの処理に比べ、デジタルフィルタ30aとアナログフィルタ30cの組み合わせでは、デジタルフィルタ30aのローパスフィルタとしての性能はそれほど要求されないのでタップ数を大幅に削減することができる。特に、デジタルフィルタ30aとして1段移動平均フィルタを用いる場合、フィルタ処理にアップダウンカウンタを用いることができるので、タップ数の削減に加えて回路も簡素化することができる。

【0067】

図17乃至図20を参照して、ローパスフィルタ30をデジタルフィルタとアナログフィルタの組み合わせで構成し、1000Hzのサンプリング周波数によるカウントを行った場合の特性例を説明する。

【0068】

まず、図17は、比較例としてのデジタルフィルタ処理(3段移動平均フィルタ、タップ数4096)のみによるローパスフィルタ30の出力例を示す。また、図18は、比較例としてのアナログフィルタ処理のみによるローパスフィルタ30の出力例を示す。アナログフィルタではノイズの影響が大きい(SN比が低下する)ことが判る。

【0069】

図19は、図16に示すように、ローパスフィルタ30をデジタルフィルタ30a(1段移動平均フィルタ、タップ数128)、D/A変換器30b及びアナログフィルタ30cの組み合わせで構成した場合の、デジタルフィルタ30aの出力のDA変換値の出力例を示している。デジタルフィルタ30aのタップ数(1段移動平均フィルタ、タップ数128)は、比較例(3段移動平均フィルタ、タップ数4096)に比べて大幅に減少している。

【0070】

図20は、図19のD/A変換器出力をローパスフィルタ30cによってアナログ処理した例を示している。なお、アナログローパスフィルタの構成例は図10に示されている。図20に示されるように、図18のアナログローパスフィルタ単独の場合に比べ、SN比が改善されており、図17に示されたデジタルフィルタのみを用いた場合と同様に信号を検出できることがわかる。既述のように、デジタルフィルタ30aのタップ数は大幅に削減されている。

【0071】

このように、ローパスフィルタをデジタルフィルタとアナログフィルタで構成することによってSN比の低下を防止しつつデジタルフィルタのタップ数の削減(演算量の減少)と回路の簡素化を図ることが可能となる。

【0072】

次に、短ゲートカウンタ部20のカウンタ回路構成の簡素化(桁数の減少)等に関して説明する。上述の実施例では、短ゲートカウンタ部20は、計数値を表示するに足りるビット数(桁数)の回路規模で構成し、ローパスフィルタを介してパルス列信号の周波数を検出することができる。

【0073】

しかしながら、周波数の絶対的な値を測定するのではなく、周波数の時間変動分(差分)を計測すればよい場合がある。上述した短ゲートタイムカウント方式を用いると、カウンタ回路出力の下位ビットの数ビット部分に変化分が現れるので、これに対応したnビット分のカウンタを使用することでカウンタ回路構成を簡単に構成することが可能となる。

【0074】

図21は、このような回路を簡易に構成する実施例を示しており、同図において、図1と対応する部分には、同一符号を付している。

【0075】

既述したように、信号源10はパルス列信号を発生する。このパルス列信号は短ゲートタイムカウンタ部20に供給される。短ゲートタイムカウンタ部20は、供給されるパルス列信号のパルス計数を短いゲート時間(サンプリング周波数)で途切れることなく行う。カウント値はローパスフィルタ30に逐次供給される。短ゲートカウンタ20は、パルス列信号の周波数(例えば、30MHz)を表示するに必要なビット数(桁数)よりも少ない、nビットのカウンタで構成されている。

【0076】

図22は、nビットのカウンタとして3ビットカウンタを使用した出力値例を示している。サンプリング周波数は、10Hzである。この例では、3ビットカウンタの出力値は6〜2の範囲内(10進数表示)で変化しており、桁上がり、桁下がりが生じていない。このような場合には、短ゲートカウンタ部20を3ビットカウンタで構成することができる。

【0077】

図23は、上記3ビットカウンタのカウント値列からローパスフィルタ30(タップ数64)で高調波成分を除いて周波数成分を復調した例を示している。このデータだけでは、絶対的な周波数を把握することは出来ないが、パルス列信号の周波数変化を十分に把握することが出来る。

【0078】

図24は、上述した短ゲートカウンタ部20のnビットカウンタとして2ビットカウンタを使用する例を示している。同図において、図21と対応する部分には同一符号を付し、かかる部分の説明は省略する。

供給されるパルス列信号を短いゲート時間でサンプリングし、カウント値に桁上がり、桁下がりが生じない場合には、2ビットのカウンタを使用することが出来る。

【0079】

図25は、100Hzでサンプリングされた2ビットカウンタの出力値の例を示している。同図において、縦軸はカウント値(10進数表示)、横軸は時間を表している。同図では、2ビット出力のカウンタ部20は、「1」と「2」のカウント値を交互にパルス列状に出力している。

【0080】

図26は、2ビットカウンタのカウント値列からローパスフィルタ30(タップ数512)で周波数成分を抽出した状態を示している。同図において、縦軸は周波数、横軸は時間を表している。1Hz以下の周波数分解能で検出することが出来る。

【0081】

次に、nビットカウンタを用いた場合に、カウント値がnビットカウンタのカウント出力範囲外となる場合(桁上がり(オバーフロー)、桁下がり(アンダーフロー))について説明する。

【0082】

図27乃至図30は、2ビットカウンタの桁上がり、桁下がりの処理を行う実施例を示している。この実施例では、桁上がり、桁下がりに対応するため、2ビットカウンタのカウント値出力を4ビット出力に置き換えてローパスフィルタに供給している。

【0083】

この例では、短ゲートカウンタ部20は、2ビットのカウンタ24を用いている。カウンタ24は直接方式のカウンタであり、サンプリングしたパルス信号を常時計数して累積値を出力する(リセットしない)。カウンタ24の出力は減算器25と前回累積値を保持するレジスタ26に送られる。減算器25はカウンタ24から出力される今回累積値から前回累積値を減じて今回計数値を得る(図3参照)。

【0084】

減算器25の出力のカウント値(今回計数値)は2−4ビット変換部28に供給される。2-4ビット変換部28は、マイクロプロセッサ(MPU)によるデータ処理プログラムあるいはプログラマブルロジックなどによって構成され、連続な2ビットのカウント値列から、桁上がり、桁下がりの発生を判別し、桁上がり、桁下がりした値を表示した4ビット値でローパスフィルタ30に出力する。

【0085】

桁上がり、桁下がりの発生を判別は、例えば、2ビットカウンタ24は、10進数表示で「0」、「1」、「2」、「3」を出力するが、増加方向においてカウント値は「3」の次の「4」では「0」に戻る。また、減少方向においてカウント値は「0」の次の「−1」では「3」に戻る。したがって、カウント値が「2」、「3」(2進数で10,11)を繰り返している状態から「0」(2進数で00)に変化した場合には桁上がりが生じたと判別することが出来る。また、カウント値が「0」、「1」(2進数で00,01)を繰り返している状態から「3」(2進数で11、補数)に変化した場合には桁下がりが生じたと判別することが出来る。

【0086】

なお、減算器25と2−4ビット変換部28の機能を持つ、2ビット入力4ビット出力の減算器を用いることとしても良い。

【0087】

図28及び図29は、それぞれ2-4ビット変換部28への入力値の例と2-4ビット変換部28の出力値の例とを示している(サンプリング周波数10Hz)。2-4ビット変換部28は、2ビットカウンタが1と0(10進数)を交互に出力しているとき、これに対応して1と0(10進数)を出力する。次に、図28中に示すように第1の桁下がりが生じると、2-4ビット変換部28は出力を−1、0の交互出力状態とする。更に、カウント値3、2の交互入力状態、2、1の交互入力状態、1、0の交互入力状態への各レベル低下に対応して2-4ビット変換部28の出力を−1、−2の交互出力状態、−2、−3の交互出力状態、−3、−4の交互出力状値とする。更に、2ビットカウンタ出力の第2の桁下がりに対応して2-4ビット変換部28の出力を−4、−5の交互出力状態とする。次に、2ビットカウント値の0、1の交互入力状態に対応して−3、−4の交互出力状態とする。以下同様に、カウント値1、2の交互入力状態、カウント値2、3の交互入力状態、カウント値3、0の交互入力(第1の桁上がり発生)、0、1の交互入力状態への各レベル低下に対応して2-4ビット変換部28の出力を−3、−2の交互出力状態、−2、−1の交互出力状態、−1、0の交互出力状態、0、1の交互出力状態とする。

【0088】

図30は、図29に示す4ビットのカウント値列からローパスフィルタ30(タップ数64)によって高周波成分を除いて周波数成分を抽出した例を示している。周波数の変化を十分に把握することが出来る。

【0089】

図31は、短ゲートカウンタ部20を1ビットカウンタで構成した他の実施例を示している。同図において、図1と対応する部分にはは同一符号を付し、かかる部分の説明は省略する。

【0090】

既述したように、信号源の周波数変化範囲が既知である場合、短ゲートカウンタ部20のサンプリング周波数を上げることによって1ビットのカウンタにおいて桁上がりの生じない条件に設定することが可能である。この場合には、1ビットのカウンタで上述した実施例と同様の測定結果を得ることが出来る。

【0091】

しかしながら、1ビットの情報では、カウント値の0と1の出力がカウント値の大小に対応しているのか、補数の関係なのかを判断することが出来ない。そこで、この実施例では、ビット判別部70を設けている。ビット判別部70は、信号源10の発振周波数を増減させ、これに対応してローパスフィルタの出力が増減する場合には、カウント値の0と1の出力がカウント値の大小に対応していると判別する。また、信号源10の発振周波数を増減させ、これに対応してローパスフィルタの出力が減増する場合には、カウント値の0と1の出力が補数の関係(出力が逆)になっていると判別する。補数の関係になっている場合には、ローパスフィルタ30の出力を正逆反転部60によって出力特性を反転させる。

【0092】

図32乃至図34は、上記1ビットカウンタを用いた実施例におけるローパスフィルタ(各例タップ数2048)の出力例を示している。図33は、カウント値が補数の場合の周波数の出力波形を示している。図34は、ローパスフィルタを通過後の周波数出力を反転させたものである。反転させることで元の波形に補正されることが判る。

【0093】

図35は、短ゲートカウンタ20の前段に分周器を設けてスケーリングを行うようにした例を示している。同図において、図1と対応する部分には同一符号を付し、かかる部分の説明は省略する。

同図に示す例では、信号源10からのパルス列信号を分周器40でm分周し、短ゲートカウンタ20に供給する。短ゲートカウンタ20が1秒よりも小さいゲート時間の短ゲート信号によって計数を行い、一連のカウント値列をローパスフィルタ30に供給する。ローパスフィルタ30で抽出された周波数信号を乗算器50でm倍にすることで元のパルス列信号の周波数情報が得られる。

【0094】

図36は、上記実施例の構成で分周器40の分周率m、乗算器50の乗率mを16とし、ローパスフィルタ30(タップ数2048)で処理した場合の周波数出力の例を示している。他の例と同様に1Hz以下の平滑な周波数出力を得ることが出来る。

かかる分周器(プリスケーラ)を短ゲートカウンタ部の前に設けることにより、被測定周波数が高い周波数である場合、分周器のみを高速化すればよく、カウンタ部以降の回路を相対的に低い周波数で駆動することが可能となって具合がよい。

【0095】

図37は、図35に示す実施例の応用例であり、図35と対応する部分には同一符号を付し、かかる部分の説明は省略する。

【0096】

この実施例では、分周器40と短ゲートカウンタ部20とを4ビットカウンタで構成している。例えば、4ビットカウンタの上位2ビットを使用することで、4分周する分周器と2ビットカウンタとを組み合わせた場合と同様の出力が得られる。すなわち、mビットカウンタの上位ビットp(例えば、上位2ビット)を出力ビットに使用し、下位(m−p)ビットをプリスケーラとして使用することが出来る。他の構成は図35の場合と同様である。

【0097】

図38は、4ビットカウンタの上位2ビットを使用した例の周波数の出力例であり、サンプリング周波数は1000Hz、ローパスフィルタのタップ数は2048である。1Hz以下の周波数を識別可能な滑らかな出力が得られる。

【0098】

図39は、本願の周波数測定装置を多数のニオイセンサ10a〜10nを備えた信号源10としてのニオイセンサアレイに設けた例を示している。短ゲートセンサ部20、ローパスフィルタ30については既に説明したので省略する。

【0099】

図40は、従来法の直接カウント方式でサンプリング周波数1Hzでセンサアレイの8チャンネル分の出力例を示している。途中時間軸上の矢印部分でニオイ成分を数秒間供給した。ニオイ成分がセンサに付着することで周波数が減少し、付着したニオイ物質は10秒程度で脱離した。

【0100】

図41は、同じ条件で本発明の短ゲートタイムカウント方式で測定した例を示している。時間分解能および周波数分解能ともに改善されていることが判る。また、短ゲートタイムカウント方式では回路が複雑にならないのでマルチセンサモジュール(あるいは基板)等に使用して好都合である。

【0101】

上述した本願の実施例によれば、短ゲートカウント部を2ビットカウンタで構成するので、カウンタ回路が簡素化され、消費電力を抑制することが可能となる。

【0102】

また、カウント値をインクリメントやディクリメントする機能を設けたことによって、使用しているカウンタのビットにおいて桁上がりや桁下がりの生じる周波数変動にも対応することが可能となって具合がよい。

【0103】

また、表示出力外に桁上げ、桁下げの生じないnビットのカウンタで短ゲートカウント部を構成することによって、桁上げ、桁下げの発生に対応してカウント値を増減する補正回路が不要となって具合がよい。

【0104】

また、1ビットカウンタで短ゲートカウンタ部を構成した場合には、カウンタ回路が簡素化される。

【0105】

また、mビットカウンタの上位2ビットを使用することで、プリスケーラとカウンタとしての機能を内蔵することが可能となって具合がよい。

【0106】

なお、上述した各実施は適宜に組み合わせることが出来る。

【0107】

以上説明したように、短ゲートタイムでカウントを行い、ローパスフィルタを通す方式とすることにより、レシプロカル方式に比べ回路が複雑にならない。時間・周波数分解能を同時に改善できる。サンプリング周波数が被測定信号に対してオーバーサンプリングとなるような条件下で測定する場合に好適である。また、従来の直接カウント方式では、デューティサイクル変調の影響を受けやすいので、この影響が無視できない場合は工夫が必要であるが、本方式では、サンプリング周波数を高めることで影響が低減されるため、特別な工夫を要しない。

【0108】

また、短ゲートタイムカウント方式は、ゲートタイムを短くして測定点を増やし、データ列の高域スペクトル成分を取り除くことでカウント値を得る方式であり、周波数分解能が著しく改善される。しかしながら、測定値1つ1つが持つ量子化誤差が大きいため、1つの測定点の欠如が分解能に与える影響が相対的に大きくなる。従って、パルス信号を途切れないようにカウントすることの出来るカウンタを使用することで、測定誤差を低減することができる。

【0109】

実施例で提案しているリセットの必要がないカウンタを使用することは有効である。リセット動作やデータ読み込み等により生じる不感時間を設けない構造にするために、2つのカウンタを切り替えて使用する方法があるが、回路規模が大きくなる。この方式は、2つのラッチ回路を用意し、それを切り替えて使用することで代用することができる。この場合、カウント値は測定値から前回の測定値を減じることで算出される。カウンタの動作周波数よりもサンプリング周波数が低い場合は、計算時間に余裕を持たせることができる。このようにすることで、カウンタは1つで済み、回路規模は大きくならない。

【0110】

本発明の方式を備えた装置を使用すれば、カウント方式の別によらず従来の周波数カウンタから得られる測定値に対し本信号処理を適用することで、測定系に変更を加えることなくセンサの分解能が改善される。本方式を念頭に設計されたカウンタは、同じ性能を持つ従来方式のカウンタに比べ回路規模が小さく、マルチチャネル化も容易である。本発明の短ゲートタイムカウント方式は、ニオイセンサ、ガスセンサ、バイオセンサ、周波数変化を利用したA−D変換素子などに使用して好都合である。

【符号の説明】

【0111】

10 信号源、20 短ゲートカウンタ部、30 ローパスフィルタ

【技術分野】

【0001】

本発明は、周波数の測定に関し、特に、僅かな周波数の変化を検出し得る測定法及び測定装置に関する。

【背景技術】

【0002】

周波数測定の方式には、決められたゲートタイム内に通過するパルスをカウントする直接カウント方式(特許文献1)と、パルス周期を正確に計測しその時間の逆数から周波数を求めるレシプロカル方式が知られている(非特許文献1)。直接カウント方式は比較的小規模の回路で実現することができるが、周波数分解能を高めるためにはゲートタイムを長く取る必要がある(例えば、0.1Hzの分解能を得るために必要なゲートタイムは10秒である。)。レシプロカル方式はこの欠点を克服することができるが、パルス間隔を正確に測定するための回路が直接カウント形式と比較して大規模となる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特表平6−501554号公報

【非特許文献】

【0004】

【非特許文献1】片野 和也, 連載第14回 時間測定器の使い方,測定器の正しい使い方入門, 月刊「トランジスタ技術」, p.331 (Feb.1994)

【発明の概要】

【発明が解決しようとする課題】

【0005】

水晶振動子を用いたQCM(Quartz Crystal Microbalance)法を使用することで振動子基板表面の微量の質量変化を周波数変化に変換することが出来る。例えば、ニオイ成分が付着する材料を振動子基板表面に設けることによって各種のニオイセンサを形成することが出来る。ニオイ成分は単体もしくは複数の物質で構成される。このニオイセンサに試料ガスを付与してニオイ成分を付着させ、振動子表面の質量を変化させると周波数が変化する。単数もしくは複数の種類のセンサを用意しこの変化を観察することによって、特定のニオイ成分が存在することを推定する。人の鼻には350種類程度の嗅細胞が存在し、犬の鼻の場合は1000種類程度存在すると言われており、各々の嗅細胞に付着するニオイ成分の割合を脳がパターン認識することでニオイを識別している。生体の嗅覚に学ぶと、ニオイ成分を検出し特定するためには、多数のニオイセンサ(センサアレイ)を使用し、各センサの出力パターンをコンピュータで解析してニオイ成分のパターンを特定することが必要である。

【0006】

しかしながら、各ニオイセンサの周波数変化を検出するために各センサの出力に周波数変化を検出するカウンタや信号処理回路を設けなければならない。更に、水晶振動子の周波数(例えば、30MHz)が付着物質によって変化するといってもわずか数Hzから数100Hz程度のものでしかなく、1Hz以下の変化である場合もある。上述したように直接カウント方式では、周波数分解能を高めるためにはゲートタイムを相当に長く取る必要がある。測定の際の誤差として、プラスマイナス1カウント誤差、トリガレベルの揺らぎによる誤差に加え、ゲートタイムを長くした場合、水晶振動子の発振安定性に起因する誤差が重畳されることになる。レシプロカル方式のカウンタを用いることでこのような欠点を補うことができるが、1つのカウンタの回路が大規模となるため多数のセンサを備えるセンサアレイには不向きである。

【0007】

よって、本発明の目的は複雑な回路を用いることなく、周波数測定分解能を改善した周波数変化の測定装置を提供することである。また、周波数測定に用いるカウンタ回路を可及的に簡素に構成し得る周波数の測定装置を提供することである。

【課題を解決するための手段】

【0008】

上記目的を達成するため、本発明の周波数測定装置は、供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、を備え、上記短ゲートタイムカウンタ部は、上記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(nは2以上の自然数である。)ビットカウンタで上記一連のカウント値を出力する、ことを特徴とする。

【0009】

かかる構成においては、まず、ゲートタイムを短くして被測定パルス列信号をサンプリングすることで周波数に対応するカウント値がパルス列として振る舞う(時間軸上のある範囲において、2つの値のいずれかとなるパルス列状の一連のカウント値として出力される)。このとき、被測定周波数の変化に応じたパルス列の密度変化が測定される。このパルス列をローパスフィルタに通すことでパルス列から被測定周波数信号を得る。被測定周波数信号の周波数変化範囲がある範囲内である場合には、フルレンジのカウンタの上位ビットには変化がなく、下位nビット部分に周波数変化が現れる。したがって、nビットのカウンタを使用することで周波数変化を抽出することが出来、フルレンジのカウンタ回路を簡易な構成に置き換えることか可能となる。

【0010】

好ましくは、上記nが2〜4ビットである。2ビット以上のカウンタとすることによって、カウント値の一連の変化からオーバーフロー(桁上がり)やアンダフロー(桁下がり)の発生を判別することが出来る。例えば、3ビットのカウンタとすることによって、2ビットカウンタの場合よりもオーバーフロー(桁上がり)やアンダフロー(桁下がり)の発生をより減少することが可能となり、カウント値の補正やサンプリング周波数の調整の回数を減少することが出来る。

【0011】

上記周波数測定装置は、更に、上記供給されるパルス列信号をm(自然数)分周して上記短ゲートタイムカウンタ部に供給する分周器(プリスケーラ)と、上記ローパスフィルタから出力されるレベル信号をm倍する乗算器と、を含むことが望ましい。

それにより、供給されるパルス列信号が高周波数である場合、高速で動作する分周器を前段に設けることで、後続するカウンタ部以降を相対的に低速動作の回路で構成することが可能となる。これは消費電力の低減にもなる。また、分周率mを可変にすることでカウンタ部に供給されるパルス列信号の見かけの周波数を切り換えることが可能となって具合が良い。

【0012】

また、本発明の周波数測定装置は、供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を得るローパスフィルタと、を備え、上記短ゲートタイムカウンタ部は、上記パルス列信号が供給される1ビットカウンタと、上記パルス列信号の周波数を増加又は減少させると共にこれに対応して上記1ビットカウンタから出力されるカウント値の増減方向を判別し、該判別結果に基づいて該1ビットカウンタのカウント値の正逆を決定する極性判別回路とを含む。

【0013】

被測定パルス列信号の周波数変化が少ない場合には1ビットのカウンタで短ゲートカウンタ部をより簡易に回路構成することが可能である。ただ、この場合には、カウントしている“0”と“1”の値が大小(真値)を意味しているのか、補数を意味するのかが不明であるので、極性判別回路によってパルス列信号の周波数を一方向に変化させ、これに対応してカウント値が増加したか減少したかを判別することによってカウント値の意味(真値か、補数値か)を判別可能とする。

【0014】

カウント値が真値を表しているのか、補数値を表しているのかについては、被測定周波数およびサンプリング周波数(ゲートタイム)の関数として表されるため、これらの値が既知であるか、もしくは被測定周波数を1度だけ別途測定することで既知とすることで知ることができる。この場合は、上記極性判別回路は省略できる。

【0015】

好ましくは、上記nビットカウンタの上位pビットをカウンタ出力とし、その下位(m−p)ビットを分周器として使用する。それにより、分周器とカウンタの機能を1つのカウンタで実現できる。例えば、4ビットカウンタの上位2ビットを出力ビットとすることで、下位2ビットによって、1/4分周器が構成される。

【0016】

また、本発明の周波数測定装置は、供給されるパルス列信号をm(mは自然数)分周する分周器と、分周されたパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、上記一連のカウント値から高周波成分を除去して上記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、上記ローパスフィルタから出力されるレベル信号をm倍する乗算器と、を備える。

【0017】

かかる構成とすることによって、分周器部分のみを高速化すれば良く、短ゲートタイムカウンタ部以降を相対的に低速で動作させることが可能となって具合がよい。上記ローパスフィルタから出力される値は被測定パルス信号の周波数の1/m倍であるため、m倍することで適切なスケーリングを行うことができる。また、分周率mを可変にすることでカウンタ部に供給されるパルス密度を切り換えることが可能となって具合が良い。

【0018】

ここで、スケーリングのための乗算回路を設けたが、スケーリングを気にしなくても良い場合はこれを省略することができる。

【0019】

上記ゲート時間は1秒よりも小さく装置の動作限界よりも大きい時間である。例えば、上記ゲート時間は1秒よりも小さく0.01μ秒よりも大きい時間である。

【0020】

望ましくは、上記ゲート時間は1秒よりも小さく装置の動作限界よりも大きい時間である。例えば、0.1m秒程度のゲートサンプリングを行う場合、従来の直接カウント方式に比べ、例えば、時間分解能で1〜2桁、SN比で2〜3桁程度の性能向上を期待することが出来る。周波数のカウントとデータ収録をハードウエアにより行う構成とすることで、1μ秒を下回るゲート時間で測定を行うこともできる。

【0021】

望ましくは、上記短ゲートタイムカウンタ部は、上記パルス列信号に対して不感期間を生じないカウンタを備える。ここで、不感期間とは、カウンタのリセットやカウント値の転送時に生ずる、カウンタに入力されるパルス列信号を測定することが出来ない期間である。後述するように、短ゲートタイムカウンタ部の出力パルス列にカウンタのリセット動作などによって不連続が生じると、前後のデータ列(値)が遮断されて一種の外乱となるので好ましくない。

【0022】

望ましくは、上記ローパスフィルタが、アナログフィルタ又はデジタルフィルタである。

【0023】

上記ローパスフィルタがアナログフィルタであることが望ましい。デジタルフィルタで必要となるメモリと演算装置を省くことが出来る。また、短ゲートタイムカウンタ部のカウント値が2値を取りパルス列として振舞う場合(図4)、アナログフィルタのローパスフィルタがD−A変換器として機能するので具合がよい。カウンタの出力がnビットデータの場合には、ローパスフィルタの前段にD−A変換器を用いる構成とすることが出来る。

【0024】

上記ローパスフィルタがデジタルフィルタであることが望ましい。移動平均フィルタであることはより望ましい。移動平均フィルタは、一般のFIRフィルタ(有限インパルス応答フィルタ)に比べて回路規模が相対的に小さく計算量が少なく構成することができ、IIRフィルタ(有限インパルス応答フィルタ)に比べても、直線位相特性を実現でき安定性も保証できるなど、FIRフィルタの持つ利点をそのまま享受することができる。

【0025】

上記ローパスフィルタが、移動平均フィルタを多段(2段以上)に直列接続した構成であることが望ましい。多段移動平均フィルタは1段の移動平均フィルタに比べ、計算量の増加を最小限に抑えつつローパスフィルタとしての性能を向上できる利点がある。

【0026】

上記不感期間を生じないカウンタが、上記パルス列信号を累積的に計数する直接カウント方式のカウンタと、計数された前回の累積カウント値と今回の累積カウント値との差から今回カウント値を得る減算器と、を含むことが望ましい。それにより、2つのカウンタを用いて交互に動作させずとも不感期間のないカウンタを構成することが可能となる。

【0027】

望ましくは、上記ローパスフィルタは、デジタルフィルタとアナログフィルタとを組み合わせたものである。それにより、SN比の良いデジタルフィルタと演算の必要のないアナログフィルタの利点を組み合わせることができる。デジタルフィルタのみの処理に比べてデジタルフィルタとアナログフィルタの組み合わせでは、デジタルフィルタのローパスフィルタとしての性能はそれほど要求されないのでタップ数を大幅に削減することができる。例えば、デジタルフィルタに1段の移動平均フィルタを用いる場合、フィルタ処理にアップダウンカウンタを用いることができるので、タップ数の削減に加えて回路も簡素化することができる。

【0028】

また、本発明の周波数の測定方法は、供給されるパルス列信号を短ゲートタイムカウンタで短いゲート時間で連続的に計数し、該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を得て、この一連のカウント値からローパスフィルタで高周波成分を除去し、上記供給されるパルス列信号の周波数に対応するレベル信号を得るものであり、上記短ゲートタイムカウンタとして、上記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(nは2以上の自然数)ビットカウンタを用いて上記一連のカウント値を出力する。好ましくは、上記nが2〜4ビットである。比較的に簡易な構成で周波数測定を行うことが可能となる。

【0029】

更に、上記供給されるパルス列信号を分周器で分周して前記短ゲートタイムカウンタ部に供給すると共に、上記ローパスフィルタから出力されるレベル信号を乗算器でスケーリングする。それにより、パルス列信号の見かけ上の周波数を下げることが可能となる。

【図面の簡単な説明】

【0030】

【図1】本願発明の概要を説明する図である。

【図2】短ゲートカウンタ部20の構成例を説明する図である。

【図3】短ゲートカウンタ部20の他の構成例を説明する図である。

【図4】短ゲートカウンタ部20によるカウント値の例を説明する図である。

【図5】ローパスフィルタ30の出力例を示す図である。

【図6】短ゲートタイム方式を説明する説明図である。

【図7】短ゲートタイム方式による出力例を説明する説明図である。

【図8】短ゲートタイム方式による効果例を説明する説明図である。

【図9】入力の不連続の影響を説明する図である。

【図10】ローパスフィルタ(アナログ)の例を説明する図である。

【図11】ローパスフィルタ(アナログ)の出力例を説明する図である。

【図12】ローパスフィルタ(移動平均)の例を説明する図である。

【図13】移動平均計算の例を説明する図であり、図中の2行目の数列が1段移動平均フィルタ出力値(1段目のタップ数10)に相当し、3行目の数列が2段移動平均フィルタ出力値(2段目のタップ数10)に相当する。

【図14】ローパスフィルタ(移動平均)のインパルス応答例を説明する図である。

【図15】ローパスフィルタ(移動平均)の出力例を説明する図である。

【図16】ローパスフィルタをデジタルフィルタとアナログフィルタとを組み合わせて構成する例を説明する図である。

【図17】参考例のデジタルフィルタ(移動平均フィルタ3段構成)の出力例を説明する図である。

【図18】参考例のアナログフィルタの出力例を説明する説明図である。

【図19】デジタルフィルタ(移動平均フィルタ1段構成)の出力をD/A変換した出力例を説明する図である。

【図20】D/A変換値をアナログフィルタによって処理した例を説明する図である。

【図21】短ゲートカウンタ部をnビットのカウンタで構成する例を説明する図である。

【図22】3ビットカウンタの出力例を説明する説明図である。

【図23】ローパスフィルタの出力例を説明する図である。

【図24】短ゲートカウンタ部20を2ビットカウンタで構成する例を説明する図である。

【図25】2ビットカウンタの出力例を説明する説明図である。

【図26】ローパスフィルタの出力例を示す図である。

【図27】2ビット出力の短ゲートカウンタ部の後段に2ビット出力を4ビット出力に変換する回路を設けた例を説明する図である。

【図28】2ビットカウンタの出力例を説明する説明図である。

【図29】ローパスフィルタへの4ビット入力値の例を説明する説明図である。

【図30】4ビット入力されローパスフィルタの出力例を示す図である。

【図31】1ビットカウンタで短ゲート部を構成した例を説明する図である。

【図32】1ビットカウンタで短ゲート部を構成した場合の出力例を示す図。

【図33】1ビットカウンタの出力が補数である場合の出力例を示す図である。

【図34】補数出力を補正した出力例を説明する図である。

【図35】短ゲートカウンタの前段に分周器を用いる例を説明する図である。

【図36】分周器を用いた場合の出力例を説明する図である。

【図37】4ビットカウンタの上位2ビットを出力に使用してプリスケーラとカウンタとして機能させる例を説明する説明図である。

【図38】4ビットカウンタの上位2ビットを使用した場合の出力例を示す図である。

【図39】センサアレイに本願を適用した例を説明する図である。

【図40】従来の方法によるセンサアレイの出力例を示す図である。

【図41】本願の方法によるセンサアレイの出力例を示す図である。

【発明を実施するための形態】

【0031】

以下、図面を参照して本発明の実施の形態について説明する。図1乃至図3は、本発明の周波数測定装置の概略を示している。各図において、対応する部分には、同一符号を付している。

【0032】

図1において、信号源10はパルス列信号を発生する。信号源10は、例えば、発振周波数f0が30MHzの水晶発振器であり、後述のニオイセンサ、ガスセンサ、バイオセンサなどの検出部に相当する。ニオイ物質などが水晶振動子に付着すると付着量に応じて発振周波数が低下する。このパルス列信号は短ゲートタイムカウンタ(以下、単に「短ゲートカウンタ」と称する。)部20に供給される。短ゲートカウンタ20は、供給されるパルス列信号のパルス計数を短いゲート時間で途切れることなく行う。カウント値はパルス列信号の周波数と対応関係にあり、ローパスフィルタ(LPF)30に逐次供給される。

【0033】

図4はカウント値の例を示している。この例では、サンプリング周波数100Hz(ゲート時間0.01秒)でパルス列信号を計数した場合を示している。サンプリング周波数100Hzの場合には、周波数分解能も100Hzまで低下するため、1つの計数値のみからは供給パルス列信号の100Hz以下の情報を検出できないが、1秒間に100個の計数値が得られることになる。計数値の100倍である周波数は、30,072,300Hzと30,072,400Hzの間に時間軸上にパルス状に分布している。

【0034】

ここで、サンプリングにおける量子化誤差(±1カウント誤差)について説明する。例えば、直接カウント方式のカウンタで123.34Hzで安定しているパルス列信号を測定する場合について検討する。

【0035】

ゲート時間10秒の場合: 10秒ごとに1233カウント又は1234カウント

【0036】

これを1/10倍した、123.3Hzもしくは123.4Hzの表示(10秒ごと)となる。(測定誤差は0.1Hz)

【0037】

ゲート時間1秒の場合: 1秒ごとに123カウント又は124カウント

【0038】

123Hzもしくは124Hzの表示(1秒ごと)となる。(測定誤差は1Hz)

【0039】

ゲート時間0.1秒の場合: 0.1秒ごとに12カウント又は13カウント

【0040】

これを10倍した、120Hzもしくは130Hzの表示(0.1秒ごと)となる。(測定誤差は10Hz)

【0041】

ゲート時間0.01秒の場合: 0.01秒ごとに1カウント又は0カウント

【0042】

これを100倍した、100Hzもしくは200Hzの表示(0.01秒ごと)となる。(測定誤差は100Hz)

【0043】

このように、ある一点の周波数で安定しているパルス列信号をカウントした場合は

ゲート時間に対応した量子化誤差が生じ、計数値はゲート時間によって定まる2つの値間を振幅とするパルス列状に分布する。一方、カウントするパルス列信号の周波数が変動する場合でも、変動が上記測定誤差に収まる範囲であれば、計数値は2つの値間を振幅とするパルス列状に分布するのに変わりない。例えばゲート時間0.01秒の場合、カウントするパルス列信号の周波数の変動が100〜200Hzの間で収まっている限り、100Hzもしくは200Hzの表示が得られる。

【0044】

図4に示すように、1秒未満の短いゲート時間でサンプリングを行う方式(以下、「短ゲートタイムカウント方式」という。)では、カウント値がパルス列として振る舞い、被測定周波数の変化に応じパルス列の頻度(粗密)が変化する。振動周波数の大小が当該パルス列の密度の大小に対応する。カウントするパルス列信号の周波数に関する情報は、パルス列として振る舞うカウント値の周波数スペクトルの低域成分に存在する。そこで、ローパスフィルタによってカウント値から低域成分を抽出する(量子化誤差に起因する高調波成分を除去する)ことによってカウントするパルス列信号の周波数の情報を復調することが出来る。

【0045】

図5は、上述した図4のカウント値の列をタップ数512の(デジタル)ローパスフィルタ30に与えて高周波成分を除去した例を示している。同図に示されるように供給されたパルス列信号の周波数の変化が連続的な(アナログ的)な曲線として出力される。100Hzのサンプリング周期の計数では測定不能な領域まで、特に、1Hz以下の周波数変化まで検出することが可能となっている。

【0046】

次に、短ゲートタイムカウント方式と直接カウント方式との比較について図6及び図7を参照して説明する。

【0047】

図6のグラフにおいて、縦軸は周波数、横軸は時間を表している。図中の曲線Aは、直接カウント方式でゲート時間を1秒に設定してサンプリングを行った場合を示している。曲線Bは、直接カウント方式でゲート時間を0.1秒に設定してサンプリングを行った場合を示している。曲線Cは、直接カウント方式でゲート時間を0.01秒に設定してサンプリングを行った場合を示している。なお、曲線Cは、時間軸の単位(桁)が異なり同一グラフ上に波形を表せないので下方に別途表示されている。曲線Dは、直接カウント方式でゲート時間を0.01秒+ローパスフィルタに設定してサンプリングを行った場合(短ゲートタイムカウント方式)を示している。図7は、図6の周波数軸のレンジを拡大して、曲線A及び曲線Dを比較している。本願の曲線Dは数10mHzオーダーまで読み取ることが出来る。

【0048】

図6より、ゲート時間が1秒未満であることによって、カウントするパルス列信号の周波数変化が測定誤差内に収まるためカウント値が2値のいずれかとなりパルス列状になることが判る。パルス頻度(パルス密度)は周波数の変化の大小に応じて変化することが判る。すなわち、パルス列状に振る舞うカウント値は時間軸方向にカウントするパルス列信号の周波数情報を含んでいることが判る。したがって、ゲート時間を短くしたことにより一つの計測値に含まれる測定誤差は拡大するが、ローパスフィルタによりこの影響は取り除かれ、SN比は改善される。ゲート時間が1秒の場合には、曲線がジグザクとなって1Hz以下の周波数が判らないが、これをローパスフィルタによって高周波成分を除去する処理を行えば本願の特性に類似する滑らかな特性を同様に得ることが出来る。したがって、ゲート時間が1Hzでも周波数変化の帯域が1Hzよるも低くゆっくりした変化の場合には本方式を適用することが可能である。

【0049】

このように、短ゲートタイムカウント方式では、ゲート時間を短くする(サンプリング周波数を高くする)と、各々の測定誤差は大きくなるがたくさんの測定値の列が得られ、ローパスフィルタによって高域成分を取り除くことが出来、図8に示すように、周波数測定分解能は向上する。回路規模を小さく抑えることができるため、マルチチャンネル化が容易である。アナログローパスフィルタを用いることによってアナログ出力にも対応することが可能である。

【0050】

図2は、上述した短ゲートカウンタ部20の第1の構成例を示している。短ゲートカウンタ部20は、信号源から供給されるパルス列信号を途切れることなく計数する(入力信号に対して不感期間を設けないように)ことが望まれる。

【0051】

図9は、計数が途切れた場合(ローパスフィルタへの計数値列が欠けた場合)のローパスフィルタの周波数出力例を示している。同図中に点線の円で示されるように外乱となることが判る。

【0052】

そこで、第1の実施例では、第1カウンタ21と第2カウンタ22の2つのカウンタを備える構成とする。パルス列信号は第1カウンタ21と第2カウンタ22の両方に供給される。制御部23は両カウンタにゲート信号、リセット信号を夫々送り、両カウンタの出力をスイッチを介してローパスフィルタ30に供給する。両カウンタから計数値を交互に出力し、一方が計数しているときに他方がリセットやデータ転送などをすることによって、カウンタのリセットやデータ転送時に生ずる不感期間を回避する。なお、制御部23はハードウエアとして構成しても良いし、パソコンなどによってソフトウェアで構成しても良い。

【0053】

図3は、短ゲートカウンタ部20の第2の構成例を示している。この実施例では1つのカウンタ24を用いている。カウンタ24は直接カウント方式のカウンタであり、サンプリングしたパルス信号を常時計数し累積値を出力する(リセットしない)。カウンタ24の出力は減算器25と前回累積値を保持するレジスタ26に送られる。減算器25はカウンタ24から出力される今回累積値から前回累積値を減じて今回計数値を得て、ローパスフィルタ30に供給する。装置全体の動作は図1の測定装置の場合と同様である。

【0054】

図10は、ローパスフィルタ30をアナログ回路で構成した例を示す。この例では、抵抗R1〜R3、キャパシタC1,C2、オペアンプOP1からなるローパスフィルタを二段接続としている。短ゲートカウンタ20から1ビットシリアルで出力される場合には、そのままローパスフィルタ30に入力することが出来る。短ゲートカウンタ20からnビットで出力される場合には、D−A変換器を介して入力することが出来る。

【0055】

図11は、サンプリング周波数を1000Hzとした場合のアナログローパスフィルタ30の出力例を示している。

【0056】

図12は、ローパスフィルタ30を移動平均フィルタによって構成した例を示す。同図において、31は加算器、32はシフトレジスタ、33は減算器、34はインバータ、35は各部に動作タイミングクロックを供給する制御部。36は割算器である。

【0057】

カウンタから出力された計数値は、加算器31とタップ数相当の記憶領域を備えるシフトレジスタ32の両方に与えられる。シフトレジスタ32内を平均値計算の対象となるN個のデータが他と同期して順次移動する。加算器31の他方には前回計算のトータル値が供給されており、加算器は新計数値と前回のトータル値とを加算する。この累積加算値からシフトレジスタ32で先頭の(旧い)データの計数値を減算器33で除き、これを新トータル値とする。新トータル値を前回トータル値として加算器に戻し、新トータル値を除算器36で対象データ数Nで割り算する。このような計算を全データについて行うことによって移動平均値が求められる。ここで、割算器は出力値を周波数(Hz)にスケーリングする機能を持つが、スケーリングを気にしなくても良い場合は省略することができる。また、移動平均フィルタを多段の構成とする場合、最終段にのみ割算器を配しても良い。

【0058】

図13は、移動平均フィルタの出力を概略的に説明する図である。この例では、計測の対象となるパルス列信号の周波数が123.34Hzを維持している状態から124.7Hzに徐々に変化するものとする。まず、ゲート時間0.1秒でサンプリングすると、カウンタ20から、12または13の計数値がある割合で送られる。10個のデータのトータルの3つの組は124、123、125…となって124.7Hz方向に値が移動する。ここで、12または13の計数値の10個(タップ数10)を移動平均計算の対象とする(一段目の移動平均)。一段目の移動平均値より、右方向に移動するにつれて数値が増えたデータの出現が増加することがわかる。更に、一段目の移動平均値を入力として2段目の移動平均(タップ数10)の計算を行うとこの傾向は強められ、精度も向上する。移動平均フィルタを多段用いることは、ローパスフィルタの特性である減衰傾度を急峻にすることに相当し、同時に12または13からなるパルス列の周波数スペクトルから高域成分を取り除くことに相当する。

【0059】

実施例では、移動平均フィルタ(ローパスフィルタ)を三段接続している(タップ数全体4096、タップ数818(一段)、1640(二段)、1640(三段)の三段移動平均フィルタ)。

【0060】

図14は、上記三段移動平均フィルタのインパルス応答を示している。図15は、上記三段移動平均フィルタの出力例を示している。このように、1Hz以下の周波数変化を測定することが出来る。なお、移動平均フィルタは所望の特性を得るために多段構成とすることができる。

【0061】

次に、デジタルフィルタとアナログフィルタとの組み合わせによってローパスフィルタ30を構成する場合について図16乃至図20を参照して説明する。

【0062】

図16は、ローパスフィルタ30をデジタルフィルタ(ローパスフィルタ)30a、D/A変換器30b及びアナログフィルタ(ローパスフィルタ)30cによって構成した例を示している。この構成には以下のような利点がある。

【0063】

まず、サンプリング周波数が高く、被測定周波数の信号変化がサンプリング周波数に対して小さいとき、デジタルフィルタ処理では問題なく復調することができる場合でも、アナログフィルタ処理ではSN比が低下する場合がある。これは、被測定周波数の信号変化に対応するフィルタ処理後の出力の変化が、パルスの振幅に比べて小さいために見掛けのダイナミックレンジが縮小することによる。デジタルフィルタ処理の場合には、量子化されたカウント値の情報は劣化しないので、このような問題は生じない。

【0064】

例えば、1000Hzのサンプリング周波数を用い、100Hzの周波数変化を観測しようとした場合であれば、1000mVのパルスをアナログフィルタ処理すると100mVの電圧変化を観察することになる。同様の条件で、0.1Hzの周波数変化を観察しようとした場合、電圧変化は0.1mVとなる。そのため、例えば、測定に1mVのノイズが存在する環境では0.1Hzの信号を検出することができない。

【0065】

一方、カウント値として量子化された周波数の情報は、デジタル処理により劣化することはないので、デジタルフィルタ処理の場合はこのような問題は生じない。したがって、デジタルフィルタと組み合わせることでSN比を改善することができる。具体的には、上述のようにデジタルフィルタ30aの出力をDA変換器30bによってD−A変換し、アナログフィルタ30cに入力する構成とする。

【0066】

デジタルフィルタのみの処理に比べ、デジタルフィルタ30aとアナログフィルタ30cの組み合わせでは、デジタルフィルタ30aのローパスフィルタとしての性能はそれほど要求されないのでタップ数を大幅に削減することができる。特に、デジタルフィルタ30aとして1段移動平均フィルタを用いる場合、フィルタ処理にアップダウンカウンタを用いることができるので、タップ数の削減に加えて回路も簡素化することができる。

【0067】

図17乃至図20を参照して、ローパスフィルタ30をデジタルフィルタとアナログフィルタの組み合わせで構成し、1000Hzのサンプリング周波数によるカウントを行った場合の特性例を説明する。

【0068】

まず、図17は、比較例としてのデジタルフィルタ処理(3段移動平均フィルタ、タップ数4096)のみによるローパスフィルタ30の出力例を示す。また、図18は、比較例としてのアナログフィルタ処理のみによるローパスフィルタ30の出力例を示す。アナログフィルタではノイズの影響が大きい(SN比が低下する)ことが判る。

【0069】

図19は、図16に示すように、ローパスフィルタ30をデジタルフィルタ30a(1段移動平均フィルタ、タップ数128)、D/A変換器30b及びアナログフィルタ30cの組み合わせで構成した場合の、デジタルフィルタ30aの出力のDA変換値の出力例を示している。デジタルフィルタ30aのタップ数(1段移動平均フィルタ、タップ数128)は、比較例(3段移動平均フィルタ、タップ数4096)に比べて大幅に減少している。

【0070】

図20は、図19のD/A変換器出力をローパスフィルタ30cによってアナログ処理した例を示している。なお、アナログローパスフィルタの構成例は図10に示されている。図20に示されるように、図18のアナログローパスフィルタ単独の場合に比べ、SN比が改善されており、図17に示されたデジタルフィルタのみを用いた場合と同様に信号を検出できることがわかる。既述のように、デジタルフィルタ30aのタップ数は大幅に削減されている。

【0071】

このように、ローパスフィルタをデジタルフィルタとアナログフィルタで構成することによってSN比の低下を防止しつつデジタルフィルタのタップ数の削減(演算量の減少)と回路の簡素化を図ることが可能となる。

【0072】

次に、短ゲートカウンタ部20のカウンタ回路構成の簡素化(桁数の減少)等に関して説明する。上述の実施例では、短ゲートカウンタ部20は、計数値を表示するに足りるビット数(桁数)の回路規模で構成し、ローパスフィルタを介してパルス列信号の周波数を検出することができる。

【0073】

しかしながら、周波数の絶対的な値を測定するのではなく、周波数の時間変動分(差分)を計測すればよい場合がある。上述した短ゲートタイムカウント方式を用いると、カウンタ回路出力の下位ビットの数ビット部分に変化分が現れるので、これに対応したnビット分のカウンタを使用することでカウンタ回路構成を簡単に構成することが可能となる。

【0074】

図21は、このような回路を簡易に構成する実施例を示しており、同図において、図1と対応する部分には、同一符号を付している。

【0075】

既述したように、信号源10はパルス列信号を発生する。このパルス列信号は短ゲートタイムカウンタ部20に供給される。短ゲートタイムカウンタ部20は、供給されるパルス列信号のパルス計数を短いゲート時間(サンプリング周波数)で途切れることなく行う。カウント値はローパスフィルタ30に逐次供給される。短ゲートカウンタ20は、パルス列信号の周波数(例えば、30MHz)を表示するに必要なビット数(桁数)よりも少ない、nビットのカウンタで構成されている。

【0076】

図22は、nビットのカウンタとして3ビットカウンタを使用した出力値例を示している。サンプリング周波数は、10Hzである。この例では、3ビットカウンタの出力値は6〜2の範囲内(10進数表示)で変化しており、桁上がり、桁下がりが生じていない。このような場合には、短ゲートカウンタ部20を3ビットカウンタで構成することができる。

【0077】

図23は、上記3ビットカウンタのカウント値列からローパスフィルタ30(タップ数64)で高調波成分を除いて周波数成分を復調した例を示している。このデータだけでは、絶対的な周波数を把握することは出来ないが、パルス列信号の周波数変化を十分に把握することが出来る。

【0078】

図24は、上述した短ゲートカウンタ部20のnビットカウンタとして2ビットカウンタを使用する例を示している。同図において、図21と対応する部分には同一符号を付し、かかる部分の説明は省略する。

供給されるパルス列信号を短いゲート時間でサンプリングし、カウント値に桁上がり、桁下がりが生じない場合には、2ビットのカウンタを使用することが出来る。

【0079】

図25は、100Hzでサンプリングされた2ビットカウンタの出力値の例を示している。同図において、縦軸はカウント値(10進数表示)、横軸は時間を表している。同図では、2ビット出力のカウンタ部20は、「1」と「2」のカウント値を交互にパルス列状に出力している。

【0080】

図26は、2ビットカウンタのカウント値列からローパスフィルタ30(タップ数512)で周波数成分を抽出した状態を示している。同図において、縦軸は周波数、横軸は時間を表している。1Hz以下の周波数分解能で検出することが出来る。

【0081】

次に、nビットカウンタを用いた場合に、カウント値がnビットカウンタのカウント出力範囲外となる場合(桁上がり(オバーフロー)、桁下がり(アンダーフロー))について説明する。

【0082】

図27乃至図30は、2ビットカウンタの桁上がり、桁下がりの処理を行う実施例を示している。この実施例では、桁上がり、桁下がりに対応するため、2ビットカウンタのカウント値出力を4ビット出力に置き換えてローパスフィルタに供給している。

【0083】

この例では、短ゲートカウンタ部20は、2ビットのカウンタ24を用いている。カウンタ24は直接方式のカウンタであり、サンプリングしたパルス信号を常時計数して累積値を出力する(リセットしない)。カウンタ24の出力は減算器25と前回累積値を保持するレジスタ26に送られる。減算器25はカウンタ24から出力される今回累積値から前回累積値を減じて今回計数値を得る(図3参照)。

【0084】

減算器25の出力のカウント値(今回計数値)は2−4ビット変換部28に供給される。2-4ビット変換部28は、マイクロプロセッサ(MPU)によるデータ処理プログラムあるいはプログラマブルロジックなどによって構成され、連続な2ビットのカウント値列から、桁上がり、桁下がりの発生を判別し、桁上がり、桁下がりした値を表示した4ビット値でローパスフィルタ30に出力する。

【0085】

桁上がり、桁下がりの発生を判別は、例えば、2ビットカウンタ24は、10進数表示で「0」、「1」、「2」、「3」を出力するが、増加方向においてカウント値は「3」の次の「4」では「0」に戻る。また、減少方向においてカウント値は「0」の次の「−1」では「3」に戻る。したがって、カウント値が「2」、「3」(2進数で10,11)を繰り返している状態から「0」(2進数で00)に変化した場合には桁上がりが生じたと判別することが出来る。また、カウント値が「0」、「1」(2進数で00,01)を繰り返している状態から「3」(2進数で11、補数)に変化した場合には桁下がりが生じたと判別することが出来る。

【0086】

なお、減算器25と2−4ビット変換部28の機能を持つ、2ビット入力4ビット出力の減算器を用いることとしても良い。

【0087】

図28及び図29は、それぞれ2-4ビット変換部28への入力値の例と2-4ビット変換部28の出力値の例とを示している(サンプリング周波数10Hz)。2-4ビット変換部28は、2ビットカウンタが1と0(10進数)を交互に出力しているとき、これに対応して1と0(10進数)を出力する。次に、図28中に示すように第1の桁下がりが生じると、2-4ビット変換部28は出力を−1、0の交互出力状態とする。更に、カウント値3、2の交互入力状態、2、1の交互入力状態、1、0の交互入力状態への各レベル低下に対応して2-4ビット変換部28の出力を−1、−2の交互出力状態、−2、−3の交互出力状態、−3、−4の交互出力状値とする。更に、2ビットカウンタ出力の第2の桁下がりに対応して2-4ビット変換部28の出力を−4、−5の交互出力状態とする。次に、2ビットカウント値の0、1の交互入力状態に対応して−3、−4の交互出力状態とする。以下同様に、カウント値1、2の交互入力状態、カウント値2、3の交互入力状態、カウント値3、0の交互入力(第1の桁上がり発生)、0、1の交互入力状態への各レベル低下に対応して2-4ビット変換部28の出力を−3、−2の交互出力状態、−2、−1の交互出力状態、−1、0の交互出力状態、0、1の交互出力状態とする。

【0088】

図30は、図29に示す4ビットのカウント値列からローパスフィルタ30(タップ数64)によって高周波成分を除いて周波数成分を抽出した例を示している。周波数の変化を十分に把握することが出来る。

【0089】

図31は、短ゲートカウンタ部20を1ビットカウンタで構成した他の実施例を示している。同図において、図1と対応する部分にはは同一符号を付し、かかる部分の説明は省略する。

【0090】

既述したように、信号源の周波数変化範囲が既知である場合、短ゲートカウンタ部20のサンプリング周波数を上げることによって1ビットのカウンタにおいて桁上がりの生じない条件に設定することが可能である。この場合には、1ビットのカウンタで上述した実施例と同様の測定結果を得ることが出来る。

【0091】

しかしながら、1ビットの情報では、カウント値の0と1の出力がカウント値の大小に対応しているのか、補数の関係なのかを判断することが出来ない。そこで、この実施例では、ビット判別部70を設けている。ビット判別部70は、信号源10の発振周波数を増減させ、これに対応してローパスフィルタの出力が増減する場合には、カウント値の0と1の出力がカウント値の大小に対応していると判別する。また、信号源10の発振周波数を増減させ、これに対応してローパスフィルタの出力が減増する場合には、カウント値の0と1の出力が補数の関係(出力が逆)になっていると判別する。補数の関係になっている場合には、ローパスフィルタ30の出力を正逆反転部60によって出力特性を反転させる。

【0092】

図32乃至図34は、上記1ビットカウンタを用いた実施例におけるローパスフィルタ(各例タップ数2048)の出力例を示している。図33は、カウント値が補数の場合の周波数の出力波形を示している。図34は、ローパスフィルタを通過後の周波数出力を反転させたものである。反転させることで元の波形に補正されることが判る。

【0093】

図35は、短ゲートカウンタ20の前段に分周器を設けてスケーリングを行うようにした例を示している。同図において、図1と対応する部分には同一符号を付し、かかる部分の説明は省略する。

同図に示す例では、信号源10からのパルス列信号を分周器40でm分周し、短ゲートカウンタ20に供給する。短ゲートカウンタ20が1秒よりも小さいゲート時間の短ゲート信号によって計数を行い、一連のカウント値列をローパスフィルタ30に供給する。ローパスフィルタ30で抽出された周波数信号を乗算器50でm倍にすることで元のパルス列信号の周波数情報が得られる。

【0094】

図36は、上記実施例の構成で分周器40の分周率m、乗算器50の乗率mを16とし、ローパスフィルタ30(タップ数2048)で処理した場合の周波数出力の例を示している。他の例と同様に1Hz以下の平滑な周波数出力を得ることが出来る。

かかる分周器(プリスケーラ)を短ゲートカウンタ部の前に設けることにより、被測定周波数が高い周波数である場合、分周器のみを高速化すればよく、カウンタ部以降の回路を相対的に低い周波数で駆動することが可能となって具合がよい。

【0095】

図37は、図35に示す実施例の応用例であり、図35と対応する部分には同一符号を付し、かかる部分の説明は省略する。

【0096】

この実施例では、分周器40と短ゲートカウンタ部20とを4ビットカウンタで構成している。例えば、4ビットカウンタの上位2ビットを使用することで、4分周する分周器と2ビットカウンタとを組み合わせた場合と同様の出力が得られる。すなわち、mビットカウンタの上位ビットp(例えば、上位2ビット)を出力ビットに使用し、下位(m−p)ビットをプリスケーラとして使用することが出来る。他の構成は図35の場合と同様である。

【0097】

図38は、4ビットカウンタの上位2ビットを使用した例の周波数の出力例であり、サンプリング周波数は1000Hz、ローパスフィルタのタップ数は2048である。1Hz以下の周波数を識別可能な滑らかな出力が得られる。

【0098】

図39は、本願の周波数測定装置を多数のニオイセンサ10a〜10nを備えた信号源10としてのニオイセンサアレイに設けた例を示している。短ゲートセンサ部20、ローパスフィルタ30については既に説明したので省略する。

【0099】

図40は、従来法の直接カウント方式でサンプリング周波数1Hzでセンサアレイの8チャンネル分の出力例を示している。途中時間軸上の矢印部分でニオイ成分を数秒間供給した。ニオイ成分がセンサに付着することで周波数が減少し、付着したニオイ物質は10秒程度で脱離した。

【0100】

図41は、同じ条件で本発明の短ゲートタイムカウント方式で測定した例を示している。時間分解能および周波数分解能ともに改善されていることが判る。また、短ゲートタイムカウント方式では回路が複雑にならないのでマルチセンサモジュール(あるいは基板)等に使用して好都合である。

【0101】

上述した本願の実施例によれば、短ゲートカウント部を2ビットカウンタで構成するので、カウンタ回路が簡素化され、消費電力を抑制することが可能となる。

【0102】

また、カウント値をインクリメントやディクリメントする機能を設けたことによって、使用しているカウンタのビットにおいて桁上がりや桁下がりの生じる周波数変動にも対応することが可能となって具合がよい。

【0103】

また、表示出力外に桁上げ、桁下げの生じないnビットのカウンタで短ゲートカウント部を構成することによって、桁上げ、桁下げの発生に対応してカウント値を増減する補正回路が不要となって具合がよい。

【0104】

また、1ビットカウンタで短ゲートカウンタ部を構成した場合には、カウンタ回路が簡素化される。

【0105】

また、mビットカウンタの上位2ビットを使用することで、プリスケーラとカウンタとしての機能を内蔵することが可能となって具合がよい。

【0106】

なお、上述した各実施は適宜に組み合わせることが出来る。

【0107】

以上説明したように、短ゲートタイムでカウントを行い、ローパスフィルタを通す方式とすることにより、レシプロカル方式に比べ回路が複雑にならない。時間・周波数分解能を同時に改善できる。サンプリング周波数が被測定信号に対してオーバーサンプリングとなるような条件下で測定する場合に好適である。また、従来の直接カウント方式では、デューティサイクル変調の影響を受けやすいので、この影響が無視できない場合は工夫が必要であるが、本方式では、サンプリング周波数を高めることで影響が低減されるため、特別な工夫を要しない。

【0108】

また、短ゲートタイムカウント方式は、ゲートタイムを短くして測定点を増やし、データ列の高域スペクトル成分を取り除くことでカウント値を得る方式であり、周波数分解能が著しく改善される。しかしながら、測定値1つ1つが持つ量子化誤差が大きいため、1つの測定点の欠如が分解能に与える影響が相対的に大きくなる。従って、パルス信号を途切れないようにカウントすることの出来るカウンタを使用することで、測定誤差を低減することができる。

【0109】

実施例で提案しているリセットの必要がないカウンタを使用することは有効である。リセット動作やデータ読み込み等により生じる不感時間を設けない構造にするために、2つのカウンタを切り替えて使用する方法があるが、回路規模が大きくなる。この方式は、2つのラッチ回路を用意し、それを切り替えて使用することで代用することができる。この場合、カウント値は測定値から前回の測定値を減じることで算出される。カウンタの動作周波数よりもサンプリング周波数が低い場合は、計算時間に余裕を持たせることができる。このようにすることで、カウンタは1つで済み、回路規模は大きくならない。

【0110】

本発明の方式を備えた装置を使用すれば、カウント方式の別によらず従来の周波数カウンタから得られる測定値に対し本信号処理を適用することで、測定系に変更を加えることなくセンサの分解能が改善される。本方式を念頭に設計されたカウンタは、同じ性能を持つ従来方式のカウンタに比べ回路規模が小さく、マルチチャネル化も容易である。本発明の短ゲートタイムカウント方式は、ニオイセンサ、ガスセンサ、バイオセンサ、周波数変化を利用したA−D変換素子などに使用して好都合である。

【符号の説明】

【0111】

10 信号源、20 短ゲートカウンタ部、30 ローパスフィルタ

【特許請求の範囲】

【請求項1】

供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、

前記一連のカウント値から高周波成分を除去して前記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、を備え、

前記短ゲートタイムカウンタ部は、前記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(nは2以上の自然数)ビットカウンタで前記一連のカウント値を出力する、ことを特徴とする周波数測定装置。

【請求項2】

前記nが2〜4ビットである請求項1に記載の周波数測定装置。

【請求項3】

更に、前記供給されるパルス列信号を分周して前記短ゲートタイムカウンタ部に供給する分周器と、を含む、請求項1又は2に記載の周波数測定装置。

【請求項4】

更に、前記ローパスフィルタから出力されるレベル信号をスケーリングする乗算器と、を含む、請求項1乃至3のいずれかに記載の周波数測定装置。

【請求項5】

供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、

前記一連のカウント値から高周波成分を除去して前記供給されるパルス列信号の周波数に対応するレベル信号を得るローパスフィルタと、を備え、

前記短ゲートタイムカウンタ部は、前記パルス列信号が供給される1ビットカウンタである、ことを特徴とする周波数測定装置。

【請求項6】

更に、前記短ゲートタイムカウンタ部は、

前記パルス列信号の周波数を増加又は減少させると共にこれに対応して前記1ビットカウンタから出力されるカウント値の増減方向を判別し、該判別結果に基づいて該1ビットカウンタのカウント値の正逆を決定する極性判別回路、を含む、

ことを特徴とする請求項5に記載の周波数測定装置。

【請求項7】

供給されるパルス列信号を分周する分周器と、

分周されたパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、

前記一連のカウント値から高周波成分を除去して前記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、

を備える周波数測定装置。

【請求項8】

更に、前記ローパスフィルタから出力されるレベル信号をスケーリングする乗算器、

を備える請求項7に記載の周波数測定装置。

【請求項9】

前記nビットカウンタの上位pビットをカウンタ出力とし、その下位(m−p)ビットを分周器として使用する、請求項1に記載の周波数測定装置。

【請求項10】

前記ゲート時間は1秒よりも小さく装置の動作限界よりも大きい時間である、請求項1乃至9のいずれかに記載の周波数測定装置。

【請求項11】

前記短ゲートタイムカウンタ部は、前記パルス列信号に対して不感期間を生じないカウンタを備える。請求項1乃至10のいずれかに記載の周波数測定装置。

【請求項12】

前記ローパスフィルタが、アナログフィルタ又はデジタルフィルタである、請求項1乃至11のいずれかに記載の周波数測定装置。

【請求項13】

前記ローパスフィルタが、デジタルフィルタとアナログフィルタとを組み合わせたものである、請求項1乃至11のいずれかに記載の周波数測定装置。

【請求項14】

前記デジタルフィルタが、多段構成の移動平均フィルタである請求項12又は13に記載の周波数測定装置。

【請求項15】

請求項1乃至14のいずれかに記載の周波数測定装置を使用した機器。

【請求項1】

供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、

前記一連のカウント値から高周波成分を除去して前記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、を備え、

前記短ゲートタイムカウンタ部は、前記パルス列信号の最大周波数の表示に必要なビット数よりも少ないビット数のn(nは2以上の自然数)ビットカウンタで前記一連のカウント値を出力する、ことを特徴とする周波数測定装置。

【請求項2】

前記nが2〜4ビットである請求項1に記載の周波数測定装置。

【請求項3】

更に、前記供給されるパルス列信号を分周して前記短ゲートタイムカウンタ部に供給する分周器と、を含む、請求項1又は2に記載の周波数測定装置。

【請求項4】

更に、前記ローパスフィルタから出力されるレベル信号をスケーリングする乗算器と、を含む、請求項1乃至3のいずれかに記載の周波数測定装置。

【請求項5】

供給されるパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、

前記一連のカウント値から高周波成分を除去して前記供給されるパルス列信号の周波数に対応するレベル信号を得るローパスフィルタと、を備え、

前記短ゲートタイムカウンタ部は、前記パルス列信号が供給される1ビットカウンタである、ことを特徴とする周波数測定装置。

【請求項6】

更に、前記短ゲートタイムカウンタ部は、

前記パルス列信号の周波数を増加又は減少させると共にこれに対応して前記1ビットカウンタから出力されるカウント値の増減方向を判別し、該判別結果に基づいて該1ビットカウンタのカウント値の正逆を決定する極性判別回路、を含む、

ことを特徴とする請求項5に記載の周波数測定装置。

【請求項7】

供給されるパルス列信号を分周する分周器と、

分周されたパルス列信号を短いゲート時間で連続的に計数して該パルス列信号の周波数に対応したパルス列状に振る舞う一連のカウント値を出力する短ゲートタイムカウンタ部と、

前記一連のカウント値から高周波成分を除去して前記供給されるパルス列信号の周波数に対応するレベル信号を出力するローパスフィルタと、

を備える周波数測定装置。

【請求項8】

更に、前記ローパスフィルタから出力されるレベル信号をスケーリングする乗算器、

を備える請求項7に記載の周波数測定装置。

【請求項9】

前記nビットカウンタの上位pビットをカウンタ出力とし、その下位(m−p)ビットを分周器として使用する、請求項1に記載の周波数測定装置。

【請求項10】

前記ゲート時間は1秒よりも小さく装置の動作限界よりも大きい時間である、請求項1乃至9のいずれかに記載の周波数測定装置。

【請求項11】

前記短ゲートタイムカウンタ部は、前記パルス列信号に対して不感期間を生じないカウンタを備える。請求項1乃至10のいずれかに記載の周波数測定装置。

【請求項12】

前記ローパスフィルタが、アナログフィルタ又はデジタルフィルタである、請求項1乃至11のいずれかに記載の周波数測定装置。

【請求項13】

前記ローパスフィルタが、デジタルフィルタとアナログフィルタとを組み合わせたものである、請求項1乃至11のいずれかに記載の周波数測定装置。

【請求項14】

前記デジタルフィルタが、多段構成の移動平均フィルタである請求項12又は13に記載の周波数測定装置。

【請求項15】

請求項1乃至14のいずれかに記載の周波数測定装置を使用した機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【公開番号】特開2013−68626(P2013−68626A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2012−263101(P2012−263101)

【出願日】平成24年11月30日(2012.11.30)

【分割の表示】特願2008−99728(P2008−99728)の分割

【原出願日】平成20年4月7日(2008.4.7)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成24年11月30日(2012.11.30)

【分割の表示】特願2008−99728(P2008−99728)の分割

【原出願日】平成20年4月7日(2008.4.7)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]