回路モジュール

【課題】シールド層の厚みを大きくしなくても、低い周波数をシールドできる回路モジュールを提供する。

【解決手段】回路モジュール100は、内部導電層2a、2bが形成された、直方体からなる基板1と、基板1の主面に実装された電子部品7と、電子部品7を被覆した状態で、基板の主面に形成された絶縁層8と、絶縁層8の表面に形成されたシールド層9を備え、内部導電層2a、2bは、それぞれ、シールド層9と直接接続されるようにした。

【解決手段】回路モジュール100は、内部導電層2a、2bが形成された、直方体からなる基板1と、基板1の主面に実装された電子部品7と、電子部品7を被覆した状態で、基板の主面に形成された絶縁層8と、絶縁層8の表面に形成されたシールド層9を備え、内部導電層2a、2bは、それぞれ、シールド層9と直接接続されるようにした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路モジュールに関し、更に詳しくは、基板上に実装された電子部品を被覆した絶縁層の表面に形成されたシールド層の厚みが小さい回路モジュールに関する。

【背景技術】

【0002】

基板上に電子部品を実装し、その電子部品を被覆するように絶縁層を形成した回路モジュールにおいて、絶縁層の表面にシールド層を形成することがおこなわれている。シールド層のシールド効果により、基板上に実装された電子部品が、外部から静電ノイズを受けて誤作動したり、逆に外部に静電ノイズを与えたりすることを防止するようにしたものである。

【0003】

そのような回路モジュールが、特許文献1(特開2004‐172176号公報)に開示されている。図7に、特許文献1に開示された回路モジュール300を示す。

【0004】

回路モジュール300は、基板101を備える。基板101の内部には、内部導電層102、ビア導体103が形成されている。また、基板101の一方の主面には、接続電極104が形成され、基板101の他方の主面には、端子電極105、接地用電極106が形成されている。そして、接続電極104と内部導電層102、内部導電層102と接地用電極106は、それぞれビア導体103により接続されている。

【0005】

基板101の一方の主面には、複数の電子部品107が実装されている。複数の電子部品107は、所定の配線(図示せず)を介して接続されて、電子回路を構成している。電子回路の所定の個所は、端子電極105や接地用電極106に引き出されている。

【0006】

基板101の一方の主面には、電子部品107を覆うように、樹脂からなる絶縁層108が形成されている。絶縁層108は、基板101の一方の主面の全面にではなく、部分的に形成されている。

【0007】

絶縁層108の表面には、シールド層109が形成されている。シールド層109は、たとえば、導電性樹脂をモールドすることにより形成されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004‐172176号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、上述した従来の回路モジュール300には、シールド層109および内部導電層102により形成される合成抵抗が大きく、シールド層109が外部から受けた静電ノイズを十分にグランドに落とすことができず、内部回路が静電ノイズの影響を受けるおそれがあるという問題があった。また、回路モジュール300の内部回路で発生した静電ノイズを十分にグランドに落とすことができず、外部に静電ノイズの影響を与えるおそれがあるという問題があった。

【課題を解決するための手段】

【0010】

本発明は、上述した従来の問題を解決するためになされたものである。

【0011】

その手段として、本発明の回路モジュールは、内部導電層が形成された、直方体からなる基板と、基板の主面に実装された電子部品と、電子部品を被覆した状態で、前記基板の主面に形成された絶縁層と、絶縁層の表面に形成されたシールド層と、内部導電層と接続された接地用電極を備え、内部導電層は、基板の内部に2層以上形成され、内部導電層の少なくとも2層が、それぞれ、シールド層と直接接続されるようにした。

【0012】

内部導電層とシールド層の接続は、たとえば、内部導電層を基板の相対向する両端面から露出させ、その露出された部分を、シールド層と直接接続するようにしておこなうことができる。また、内部導電層を基板の3つの端面または4つの端面から露出させ、その露出された部分を、シールド層と直接接続するようにしても良い。

【0013】

また、絶縁層は、基板の一方の主面の全面にわたって形成するようにしても良い。

【0014】

また、接地用電極は、基板の、前記電子部品が実装されていない側の主面に形成するようにしても良い。

【0015】

あるいは、基板の、電子部品が実装されていない側の主面に、更に別の電子部品を実装し、その電子部品を被覆した状態で、基板の当該主面に更に別の絶縁層を形成し、その絶縁層の表面に、接地用電極を形成するようにしても良い。この場合には、基板により多くの電子部品を実装することが可能になり、より高度化した、より複雑な回路を有する電子回路を備えた回路モジュールを構成することができる。

【0016】

更に、シールド層と直接接続されている、少なくとも2層からなる内部導電層を、基板の内部において導電ビアにより相互に接続するようにしても良い。この場合には、内部導電層の電位が、内部導電層の各部分において均一になると共に、内部導電層の抵抗率を下げることができる。

【発明の効果】

【0017】

本発明の回路モジュールは、上述したとおり、内部導電層が基板の内部に2層以上形成され、内部導電層の少なくとも2層が、それぞれ、シールド層と直接接続されるようにしたため、シールド層およびこれに直接接続された内部導電層で構成される合成抵抗(R)が小さくなっている。

【0018】

すなわち、合成抵抗(R)は、次の式1で示される。

【0019】

《式1》 R=1/(1/RS+1/RIE1+1/RIE2+・・・RIEN)

式1において、Rは合成抵抗、RSはシールド層の抵抗、RIE1は1層目の内部導電層の抵抗、RIE2は2層目の内部導電層の抵抗、RIENはN層目の抵抗である。

【0020】

式1から分かるように、合成抵抗Rは、より多くの内部導電層がシールド層と接続されるほど小さくなる。本発明の回路モジュールにおいては、内部導電層の少なくとも2層が、それぞれ、シールド層と直接接続されるようになっているため、シールド層およびこれに直接接続された内部導電層で構成される合成抵抗Rが小さくなっている。

【0021】

この結果、本発明の回路モジュールは、シールド層が外部から受けた静電ノイズを十分にグランドに落とすことができ、内部回路が静電ノイズの影響を受けるおそれがない。また、回路モジュールの内部回路で発生した静電ノイズを十分にグランドに落とすことができ、外部に静電ノイズの影響を与えるおそれがない。

【図面の簡単な説明】

【0022】

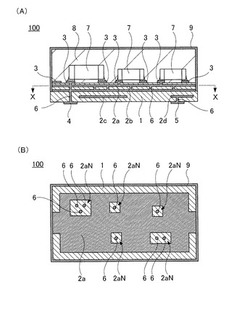

【図1】図1(A)は、本発明の第1実施形態にかかる回路モジュール100を示す断面図である。図1(B)は、図1(A)の破線矢印X−X部分を示す断面図である。

【図2】図2(A)〜(C)は、それぞれ、本発明の第1実施形態にかかる回路モジュール100の製造方法の一例において適用される工程を示す断面図である。

【図3】図3(D)〜(F)は、それぞれ、図2の続きの工程を示す断面図である。

【図4】図4(A)〜(C)は、それぞれ、本発明の第1実施形態にかかる回路モジュール100の変形例を示す断面図である。

【図5】図5(A)〜(C)は、それぞれ、本発明の第1実施形態にかかる回路モジュール100の更に別の変形例を示す断面図である。

【図6】本発明の第2実施形態にかかる回路モジュール200を示す断面図である。

【図7】従来の回路モジュール300を示す断面図である。

【発明を実施するための形態】

【0023】

以下、図面とともに、本発明を実施するための形態について説明する。

【0024】

[第1実施形態]

図1(A)および(B)に、本発明の第1実施形態にかかる回路モジュール100を示す。ただし、図1(A)は回路モジュール100の断面図、図1(B)は図1(A)の破線矢印X−X部分の断面図である。

【0025】

回路モジュール100は、基板1を備える。

【0026】

基板1の材質は任意であるが、たとえば、アルミナとガラスを混合してなる低温焼結セラミックを用いることができる。

【0027】

基板1の内部には、複数の内部導電層2a、2b、2c、2dが形成されている。また、基板1の一方の主面には、複数のランド電極3が形成され、基板1の他方の主面には、接地用電極4と端子電極5が形成されている。また、基板1の内部には、複数のビア導体6が形成され、ビア導体6により、内部導電層2a〜2d、ランド電極3、接地用電極4、端子電極5の所定の個所間が相互に接続されている。特に、内部導電層2aと2bは、複数のビア導体6により、相互に接続されている。内部導電層2a〜2d、ランド電極3、接地用電極4、端子電極5、ビア導体6の材質は任意であるが、たとえば、銀、銀合金などを用いることができる。

【0028】

図1(B)は、上述のとおり、図1(A)の破線矢印X−X部分を示しており、この部分には、内部導電層2aが形成されている。図1(B)から分かるように、内部導電層2aの外縁は、基板1の外縁よりも一回り小さい。また、内部導電層2aは、基板1の相対向する両端面(図における左右の端面)から外部に露出されている。また、内部導電層2aは、その内部に、上下間の導通をはかるためのビア導体6を通過させるための、複数の非形成部2aNが形成されている。内部導電層9bも、内部導電層9aと同じ、または類似した構造からなる。

【0029】

基板1の一方の主面のランド電極3には、はんだにより、複数の電子部品7が実装されている。複数の電子部品7は、基板1の内部において、ビア導体6、内部導電層2で構成される配線を介して接続されて、電子回路を構成している。電子回路の所定の個所は、接地用電極4や端子電極5に引き出されている。

【0030】

基板1の一方の主面には、電子部品7を覆うように、樹脂からなる絶縁層8が形成されている。絶縁層8は、基板1の一方の主面のほぼ全面に形成されている。絶縁層8を構成する樹脂の種類は任意であるが、たとえば、エポキシ系の樹脂などを用いることができる。

【0031】

絶縁層8の表面および基板1の端面の一部分には、シールド層9が形成されている。そして、基板1の両端面から露出された内部導電層2a、および基板1の両端面から露出された内部導電層2bが、それぞれ、基板1の両端面において、シールド層9に直接接続されている。なお、本実施形態においては、基板1の一方の主面に形成されたランド電極3の一部のもの(図1(A)において最も左側に形成されたもの)も、シールド層9に直接接続されている。シールド層9は、たとえば、銀ペーストなどからなる。

【0032】

第1実施形態にかかる回路モジュール100は、2層の内部導電層2aと2bがシールド層9と接続されており、シールド層9および内部導電層2a、2bで構成される合成抵抗が小さくなっている。その結果、シールド層9が外部から受けた静電ノイズを十分にグランドに落とすことができ、内部回路が静電ノイズの影響を受けるおそれがない。また、回路モジュールの内部回路で発生した静電ノイズをシールド層9を経由して十分にグランドに落とすことができ、外部に静電ノイズの影響を与えるおそれがない。

【0033】

以上のような構造からなる、第1実施形態にかかる回路モジュール100は、たとえば、図2(A)〜図3(F)に示す各工程を経て製造される。なお、ここでは、マザー基板を用いて、多数個の回路モジュール100を一括して製造する方法を示す。

【0034】

まず、図2(A)に示すように、多数個の基板1がマトリックス状に形成されたマザー基板11を準備する。なお、図においては、マザー基板11の各基板1の境界部分を破線で示している。マザー基板11は、たとえば、複数枚の所定のセラミックグリーンシート(図示せず)を積層し、加圧し、所定のプロファイルで焼成することにより作製する。なお、各セラミックグリーンシートには、積層前に、予め、必要に応じて、両主面間を貫通して、導電ビア6を形成するための、内部に導電性ペーストが充填された貫通孔を設けておく。また、必要に応じて、表面に、内部導電層2a〜2d、ランド電極3、接地用電極4、端子電極5を形成するための、導電性ペーストを印刷しておく。

【0035】

次に、図2(B)に示すように、マザー基板11の各基板1のランド電極3に電子部品7を実装する。電子部品7の実装は、たとえば、ランド電極3の表面に予めクリームはんだを塗布し、電子部品7を載置し、全体を加熱し、クリームはんだをリフローさせ、全体を冷却し、電子部品7の端子電極をランド電極3に接合することによりおこなう。

【0036】

次に、図2(C)に示すように、マザー基板11の一方の主面に、電子部品7を被覆するように、マザー絶縁層18を形成する。マザー絶縁層18は、同時に製造される多数個の回路モジュール100の各絶縁層8を一体的に形成したものである。なお、図においては、マザー絶縁層18の各絶縁層8の境界部分を破線で示している。マザー絶縁層18は、たとえば、加熱して半溶融状態となった樹脂シートを、マザー基板11の一方の主面上に載置し、電子部品7の周囲に回り込ませ、更に加熱して硬化させることにより形成する。

【0037】

次に、図3(D)に示すように、同時に製造される各回路モジュール100の境界部分に溝Sを形成する。溝Sは、マザー絶縁層18を、絶縁層8と絶縁層8に完全に分離する。しかし、溝Sは、マザー基板11を、基板1と基板1に完全には分離しない。すなわち、隣接する基板1と基板1は、部分的につながった状態になる。この結果、各基板1の相対向する両端面には、内部導電体2a、2bが露出する。溝Sは、たとえば、ダイシングで形成する。

【0038】

次に、図3(E)に示すように、各絶縁層8の表面、および各溝Sの内部に、導電物質19を形成する。導電物質19は、各回路モジュール100において、各シールド層9を形成するためのものである。なお、図においては、導電物質19の各シールド層9の境界部分を破線で示している。導電物質19の形成は、たとえば、導電性ペーストをスピンコートして、絶縁層8の表面に塗布し、また溝Sの内部に充填し、加熱して硬化させることによりおこなう。なお、導電物質19は、各基板1の相対向する両端面から露出した、内部導電体2a、2bと接続される。

【0039】

最後に、図3(F)に示すように、導電物質19とマザー基板11を切断して、絶縁層8の表面および基板1の端面の一部分にシールド層9が形成された、個々の回路モジュール100を完成させる。導電物質19とマザー基板11の切断は、たとえば、ダイシングによりおこなう。

【0040】

以上、本発明の第1実施形態にかかる回路モジュール100の構造、および製造方法の一例について説明した。しかしながら、本発明が上述した内容に限定されることはなく、本発明の趣旨に沿って、種々の変更をなすことができる。

【0041】

例えば、回路モジュール100では、内部導電層2a、2bの2層がシールド層9に直接接続されているが、3層またはそれよりも多くの内部導電層をシールド層9に直接接続するようにしても良い。

【0042】

また、回路モジュール100では、図1(B)に示すように、内部導電層2aが、基板1の相対向する両端面から所定の幅で露出されてシールド層9に直接接続されているが、接続方法や接続個所はこれには限定されない。

【0043】

たとえば、図4(A)に示すように、内部導電層2aの、基板1の相対向する端面からの露出幅を小さくしても良い。

【0044】

あるいは逆に、図4(B)に示すように、内部導電層2aの、基板1の相対向する端面からの露出幅を大きくしても良い。

【0045】

また、図4(C)に示すように、内部導電層2aを、基板1の4つの端面から露出させ、それらの露出部分をシールド層9と直接接続するようにしても良い。

【0046】

更に、図5(A)に示すように、図4(C)に示した接続方法に変更を加え、内部導電層2aの、基板1の端面からの露出幅を大きくしても良い。

【0047】

また、図5(B)に示すように、内部導電層2aを、基板1の3つの端面から露出させ、それらの露出部分をシールド層9と直接接続するようにしても良い。

【0048】

また、図5(C)に示すように、内部導電層2aを、基板1の端面全周から露出させ、その露出部分をシールド層9と直接接続するようにしても良い。

【0049】

このように、内部導電層2aを、基板1の3つの端面あるいは4つの端面から露出させ、シールド層9と接続させるようにすれば、実装部品7がシールド層9および内部導電層2aに囲まれるため、実装部品7が外部のノイズ信号からを影響を受けにくくなるとともに、回路モジュールの外部へノイズ信号を放出することもなくなる。

【0050】

[第2実施形態]

図6に、本発明の第2実施形態にかかる回路モジュール200を示す。ただし、図6は、回路モジュール200の断面図である。

【0051】

第2実施形態にかかる回路モジュール200は、図1(A)、(B)に示した第1実施形態にかかる回路モジュール100の基板1の実装面側の主面(図1(A)における下側の主面)に、更に別の電子部品を実装し、それらの電子部品を被覆した状態で更に別の絶縁層を形成するようにした。

【0052】

すなわち、図6に示すように、回路モジュール200は、回路モジュール100の基板1の実装面側の主面にランド電極13を設け、ランド電極13に電子部品17を実装し、電子部品17を被覆するように絶縁層28を形成している。そして、絶縁層28の表面に、接地用電極14と端子電極15を形成している。

【0053】

なお、基板1への電子部品17の実装や絶縁層28の形成は、たとえば、第1実施形態における製造方法の一例において説明した、図2(C)や図3(D)に示すように、個々の基板1がまだマザー基板11の状態である段階でおこなっても良いし、あるいは、図3(F)に示すように、導電物質19、マザー基板11を個々の回路モジュール100に切断した後の段階でおこなっても良い。

【0054】

第2実施形態にかかる回路モジュール200においては、基板により多くの電子部品を実装することが可能になり、より高度化した、より複雑な回路を有する電子回路を備えた回路モジュールを構成することができる。

【符号の説明】

【0055】

1:基板

2a、2b、2c、2d:内部導電層

(2aN:内部導電層2aの内部に形成された非形成部)

3、13:ランド電極

4、14:接地用電極

5、15:端子電極

6:ビア導体

7、17:電子部品

8、28:絶縁層

9:シールド層

【技術分野】

【0001】

本発明は、回路モジュールに関し、更に詳しくは、基板上に実装された電子部品を被覆した絶縁層の表面に形成されたシールド層の厚みが小さい回路モジュールに関する。

【背景技術】

【0002】

基板上に電子部品を実装し、その電子部品を被覆するように絶縁層を形成した回路モジュールにおいて、絶縁層の表面にシールド層を形成することがおこなわれている。シールド層のシールド効果により、基板上に実装された電子部品が、外部から静電ノイズを受けて誤作動したり、逆に外部に静電ノイズを与えたりすることを防止するようにしたものである。

【0003】

そのような回路モジュールが、特許文献1(特開2004‐172176号公報)に開示されている。図7に、特許文献1に開示された回路モジュール300を示す。

【0004】

回路モジュール300は、基板101を備える。基板101の内部には、内部導電層102、ビア導体103が形成されている。また、基板101の一方の主面には、接続電極104が形成され、基板101の他方の主面には、端子電極105、接地用電極106が形成されている。そして、接続電極104と内部導電層102、内部導電層102と接地用電極106は、それぞれビア導体103により接続されている。

【0005】

基板101の一方の主面には、複数の電子部品107が実装されている。複数の電子部品107は、所定の配線(図示せず)を介して接続されて、電子回路を構成している。電子回路の所定の個所は、端子電極105や接地用電極106に引き出されている。

【0006】

基板101の一方の主面には、電子部品107を覆うように、樹脂からなる絶縁層108が形成されている。絶縁層108は、基板101の一方の主面の全面にではなく、部分的に形成されている。

【0007】

絶縁層108の表面には、シールド層109が形成されている。シールド層109は、たとえば、導電性樹脂をモールドすることにより形成されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004‐172176号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、上述した従来の回路モジュール300には、シールド層109および内部導電層102により形成される合成抵抗が大きく、シールド層109が外部から受けた静電ノイズを十分にグランドに落とすことができず、内部回路が静電ノイズの影響を受けるおそれがあるという問題があった。また、回路モジュール300の内部回路で発生した静電ノイズを十分にグランドに落とすことができず、外部に静電ノイズの影響を与えるおそれがあるという問題があった。

【課題を解決するための手段】

【0010】

本発明は、上述した従来の問題を解決するためになされたものである。

【0011】

その手段として、本発明の回路モジュールは、内部導電層が形成された、直方体からなる基板と、基板の主面に実装された電子部品と、電子部品を被覆した状態で、前記基板の主面に形成された絶縁層と、絶縁層の表面に形成されたシールド層と、内部導電層と接続された接地用電極を備え、内部導電層は、基板の内部に2層以上形成され、内部導電層の少なくとも2層が、それぞれ、シールド層と直接接続されるようにした。

【0012】

内部導電層とシールド層の接続は、たとえば、内部導電層を基板の相対向する両端面から露出させ、その露出された部分を、シールド層と直接接続するようにしておこなうことができる。また、内部導電層を基板の3つの端面または4つの端面から露出させ、その露出された部分を、シールド層と直接接続するようにしても良い。

【0013】

また、絶縁層は、基板の一方の主面の全面にわたって形成するようにしても良い。

【0014】

また、接地用電極は、基板の、前記電子部品が実装されていない側の主面に形成するようにしても良い。

【0015】

あるいは、基板の、電子部品が実装されていない側の主面に、更に別の電子部品を実装し、その電子部品を被覆した状態で、基板の当該主面に更に別の絶縁層を形成し、その絶縁層の表面に、接地用電極を形成するようにしても良い。この場合には、基板により多くの電子部品を実装することが可能になり、より高度化した、より複雑な回路を有する電子回路を備えた回路モジュールを構成することができる。

【0016】

更に、シールド層と直接接続されている、少なくとも2層からなる内部導電層を、基板の内部において導電ビアにより相互に接続するようにしても良い。この場合には、内部導電層の電位が、内部導電層の各部分において均一になると共に、内部導電層の抵抗率を下げることができる。

【発明の効果】

【0017】

本発明の回路モジュールは、上述したとおり、内部導電層が基板の内部に2層以上形成され、内部導電層の少なくとも2層が、それぞれ、シールド層と直接接続されるようにしたため、シールド層およびこれに直接接続された内部導電層で構成される合成抵抗(R)が小さくなっている。

【0018】

すなわち、合成抵抗(R)は、次の式1で示される。

【0019】

《式1》 R=1/(1/RS+1/RIE1+1/RIE2+・・・RIEN)

式1において、Rは合成抵抗、RSはシールド層の抵抗、RIE1は1層目の内部導電層の抵抗、RIE2は2層目の内部導電層の抵抗、RIENはN層目の抵抗である。

【0020】

式1から分かるように、合成抵抗Rは、より多くの内部導電層がシールド層と接続されるほど小さくなる。本発明の回路モジュールにおいては、内部導電層の少なくとも2層が、それぞれ、シールド層と直接接続されるようになっているため、シールド層およびこれに直接接続された内部導電層で構成される合成抵抗Rが小さくなっている。

【0021】

この結果、本発明の回路モジュールは、シールド層が外部から受けた静電ノイズを十分にグランドに落とすことができ、内部回路が静電ノイズの影響を受けるおそれがない。また、回路モジュールの内部回路で発生した静電ノイズを十分にグランドに落とすことができ、外部に静電ノイズの影響を与えるおそれがない。

【図面の簡単な説明】

【0022】

【図1】図1(A)は、本発明の第1実施形態にかかる回路モジュール100を示す断面図である。図1(B)は、図1(A)の破線矢印X−X部分を示す断面図である。

【図2】図2(A)〜(C)は、それぞれ、本発明の第1実施形態にかかる回路モジュール100の製造方法の一例において適用される工程を示す断面図である。

【図3】図3(D)〜(F)は、それぞれ、図2の続きの工程を示す断面図である。

【図4】図4(A)〜(C)は、それぞれ、本発明の第1実施形態にかかる回路モジュール100の変形例を示す断面図である。

【図5】図5(A)〜(C)は、それぞれ、本発明の第1実施形態にかかる回路モジュール100の更に別の変形例を示す断面図である。

【図6】本発明の第2実施形態にかかる回路モジュール200を示す断面図である。

【図7】従来の回路モジュール300を示す断面図である。

【発明を実施するための形態】

【0023】

以下、図面とともに、本発明を実施するための形態について説明する。

【0024】

[第1実施形態]

図1(A)および(B)に、本発明の第1実施形態にかかる回路モジュール100を示す。ただし、図1(A)は回路モジュール100の断面図、図1(B)は図1(A)の破線矢印X−X部分の断面図である。

【0025】

回路モジュール100は、基板1を備える。

【0026】

基板1の材質は任意であるが、たとえば、アルミナとガラスを混合してなる低温焼結セラミックを用いることができる。

【0027】

基板1の内部には、複数の内部導電層2a、2b、2c、2dが形成されている。また、基板1の一方の主面には、複数のランド電極3が形成され、基板1の他方の主面には、接地用電極4と端子電極5が形成されている。また、基板1の内部には、複数のビア導体6が形成され、ビア導体6により、内部導電層2a〜2d、ランド電極3、接地用電極4、端子電極5の所定の個所間が相互に接続されている。特に、内部導電層2aと2bは、複数のビア導体6により、相互に接続されている。内部導電層2a〜2d、ランド電極3、接地用電極4、端子電極5、ビア導体6の材質は任意であるが、たとえば、銀、銀合金などを用いることができる。

【0028】

図1(B)は、上述のとおり、図1(A)の破線矢印X−X部分を示しており、この部分には、内部導電層2aが形成されている。図1(B)から分かるように、内部導電層2aの外縁は、基板1の外縁よりも一回り小さい。また、内部導電層2aは、基板1の相対向する両端面(図における左右の端面)から外部に露出されている。また、内部導電層2aは、その内部に、上下間の導通をはかるためのビア導体6を通過させるための、複数の非形成部2aNが形成されている。内部導電層9bも、内部導電層9aと同じ、または類似した構造からなる。

【0029】

基板1の一方の主面のランド電極3には、はんだにより、複数の電子部品7が実装されている。複数の電子部品7は、基板1の内部において、ビア導体6、内部導電層2で構成される配線を介して接続されて、電子回路を構成している。電子回路の所定の個所は、接地用電極4や端子電極5に引き出されている。

【0030】

基板1の一方の主面には、電子部品7を覆うように、樹脂からなる絶縁層8が形成されている。絶縁層8は、基板1の一方の主面のほぼ全面に形成されている。絶縁層8を構成する樹脂の種類は任意であるが、たとえば、エポキシ系の樹脂などを用いることができる。

【0031】

絶縁層8の表面および基板1の端面の一部分には、シールド層9が形成されている。そして、基板1の両端面から露出された内部導電層2a、および基板1の両端面から露出された内部導電層2bが、それぞれ、基板1の両端面において、シールド層9に直接接続されている。なお、本実施形態においては、基板1の一方の主面に形成されたランド電極3の一部のもの(図1(A)において最も左側に形成されたもの)も、シールド層9に直接接続されている。シールド層9は、たとえば、銀ペーストなどからなる。

【0032】

第1実施形態にかかる回路モジュール100は、2層の内部導電層2aと2bがシールド層9と接続されており、シールド層9および内部導電層2a、2bで構成される合成抵抗が小さくなっている。その結果、シールド層9が外部から受けた静電ノイズを十分にグランドに落とすことができ、内部回路が静電ノイズの影響を受けるおそれがない。また、回路モジュールの内部回路で発生した静電ノイズをシールド層9を経由して十分にグランドに落とすことができ、外部に静電ノイズの影響を与えるおそれがない。

【0033】

以上のような構造からなる、第1実施形態にかかる回路モジュール100は、たとえば、図2(A)〜図3(F)に示す各工程を経て製造される。なお、ここでは、マザー基板を用いて、多数個の回路モジュール100を一括して製造する方法を示す。

【0034】

まず、図2(A)に示すように、多数個の基板1がマトリックス状に形成されたマザー基板11を準備する。なお、図においては、マザー基板11の各基板1の境界部分を破線で示している。マザー基板11は、たとえば、複数枚の所定のセラミックグリーンシート(図示せず)を積層し、加圧し、所定のプロファイルで焼成することにより作製する。なお、各セラミックグリーンシートには、積層前に、予め、必要に応じて、両主面間を貫通して、導電ビア6を形成するための、内部に導電性ペーストが充填された貫通孔を設けておく。また、必要に応じて、表面に、内部導電層2a〜2d、ランド電極3、接地用電極4、端子電極5を形成するための、導電性ペーストを印刷しておく。

【0035】

次に、図2(B)に示すように、マザー基板11の各基板1のランド電極3に電子部品7を実装する。電子部品7の実装は、たとえば、ランド電極3の表面に予めクリームはんだを塗布し、電子部品7を載置し、全体を加熱し、クリームはんだをリフローさせ、全体を冷却し、電子部品7の端子電極をランド電極3に接合することによりおこなう。

【0036】

次に、図2(C)に示すように、マザー基板11の一方の主面に、電子部品7を被覆するように、マザー絶縁層18を形成する。マザー絶縁層18は、同時に製造される多数個の回路モジュール100の各絶縁層8を一体的に形成したものである。なお、図においては、マザー絶縁層18の各絶縁層8の境界部分を破線で示している。マザー絶縁層18は、たとえば、加熱して半溶融状態となった樹脂シートを、マザー基板11の一方の主面上に載置し、電子部品7の周囲に回り込ませ、更に加熱して硬化させることにより形成する。

【0037】

次に、図3(D)に示すように、同時に製造される各回路モジュール100の境界部分に溝Sを形成する。溝Sは、マザー絶縁層18を、絶縁層8と絶縁層8に完全に分離する。しかし、溝Sは、マザー基板11を、基板1と基板1に完全には分離しない。すなわち、隣接する基板1と基板1は、部分的につながった状態になる。この結果、各基板1の相対向する両端面には、内部導電体2a、2bが露出する。溝Sは、たとえば、ダイシングで形成する。

【0038】

次に、図3(E)に示すように、各絶縁層8の表面、および各溝Sの内部に、導電物質19を形成する。導電物質19は、各回路モジュール100において、各シールド層9を形成するためのものである。なお、図においては、導電物質19の各シールド層9の境界部分を破線で示している。導電物質19の形成は、たとえば、導電性ペーストをスピンコートして、絶縁層8の表面に塗布し、また溝Sの内部に充填し、加熱して硬化させることによりおこなう。なお、導電物質19は、各基板1の相対向する両端面から露出した、内部導電体2a、2bと接続される。

【0039】

最後に、図3(F)に示すように、導電物質19とマザー基板11を切断して、絶縁層8の表面および基板1の端面の一部分にシールド層9が形成された、個々の回路モジュール100を完成させる。導電物質19とマザー基板11の切断は、たとえば、ダイシングによりおこなう。

【0040】

以上、本発明の第1実施形態にかかる回路モジュール100の構造、および製造方法の一例について説明した。しかしながら、本発明が上述した内容に限定されることはなく、本発明の趣旨に沿って、種々の変更をなすことができる。

【0041】

例えば、回路モジュール100では、内部導電層2a、2bの2層がシールド層9に直接接続されているが、3層またはそれよりも多くの内部導電層をシールド層9に直接接続するようにしても良い。

【0042】

また、回路モジュール100では、図1(B)に示すように、内部導電層2aが、基板1の相対向する両端面から所定の幅で露出されてシールド層9に直接接続されているが、接続方法や接続個所はこれには限定されない。

【0043】

たとえば、図4(A)に示すように、内部導電層2aの、基板1の相対向する端面からの露出幅を小さくしても良い。

【0044】

あるいは逆に、図4(B)に示すように、内部導電層2aの、基板1の相対向する端面からの露出幅を大きくしても良い。

【0045】

また、図4(C)に示すように、内部導電層2aを、基板1の4つの端面から露出させ、それらの露出部分をシールド層9と直接接続するようにしても良い。

【0046】

更に、図5(A)に示すように、図4(C)に示した接続方法に変更を加え、内部導電層2aの、基板1の端面からの露出幅を大きくしても良い。

【0047】

また、図5(B)に示すように、内部導電層2aを、基板1の3つの端面から露出させ、それらの露出部分をシールド層9と直接接続するようにしても良い。

【0048】

また、図5(C)に示すように、内部導電層2aを、基板1の端面全周から露出させ、その露出部分をシールド層9と直接接続するようにしても良い。

【0049】

このように、内部導電層2aを、基板1の3つの端面あるいは4つの端面から露出させ、シールド層9と接続させるようにすれば、実装部品7がシールド層9および内部導電層2aに囲まれるため、実装部品7が外部のノイズ信号からを影響を受けにくくなるとともに、回路モジュールの外部へノイズ信号を放出することもなくなる。

【0050】

[第2実施形態]

図6に、本発明の第2実施形態にかかる回路モジュール200を示す。ただし、図6は、回路モジュール200の断面図である。

【0051】

第2実施形態にかかる回路モジュール200は、図1(A)、(B)に示した第1実施形態にかかる回路モジュール100の基板1の実装面側の主面(図1(A)における下側の主面)に、更に別の電子部品を実装し、それらの電子部品を被覆した状態で更に別の絶縁層を形成するようにした。

【0052】

すなわち、図6に示すように、回路モジュール200は、回路モジュール100の基板1の実装面側の主面にランド電極13を設け、ランド電極13に電子部品17を実装し、電子部品17を被覆するように絶縁層28を形成している。そして、絶縁層28の表面に、接地用電極14と端子電極15を形成している。

【0053】

なお、基板1への電子部品17の実装や絶縁層28の形成は、たとえば、第1実施形態における製造方法の一例において説明した、図2(C)や図3(D)に示すように、個々の基板1がまだマザー基板11の状態である段階でおこなっても良いし、あるいは、図3(F)に示すように、導電物質19、マザー基板11を個々の回路モジュール100に切断した後の段階でおこなっても良い。

【0054】

第2実施形態にかかる回路モジュール200においては、基板により多くの電子部品を実装することが可能になり、より高度化した、より複雑な回路を有する電子回路を備えた回路モジュールを構成することができる。

【符号の説明】

【0055】

1:基板

2a、2b、2c、2d:内部導電層

(2aN:内部導電層2aの内部に形成された非形成部)

3、13:ランド電極

4、14:接地用電極

5、15:端子電極

6:ビア導体

7、17:電子部品

8、28:絶縁層

9:シールド層

【特許請求の範囲】

【請求項1】

内部導電層が形成された、直方体からなる基板と、

前記基板の主面に実装された電子部品と、

前記電子部品を被覆した状態で、前記基板の主面に形成された絶縁層と、

前記絶縁層の表面に形成されたシールド層と、

前記内部導電層と接続された接地用電極を備えた回路モジュールであって、

前記内部導電層は、前記基板の内部に2層以上形成され、

前記内部導電層の少なくとも2層が、それぞれ、前記シールド層と直接接続されている回路モジュール。

【請求項2】

前記シールド層と直接接続されている前記内部導電層が、前記基板の相対向する両端面から露出され、当該露出された部分が、前記シールド層と直接接続されている、請求項1に記載された回路モジュール。

【請求項3】

前記シールド層と直接接続されている前記内部導電層が、前記基板の3つの端面または4つの端面から露出され、当該露出された部分が、前記シールド層と直接接続されている、請求項2に記載された回路モジュール。

【請求項4】

前記絶縁層が、前記基板の一方の主面の全面にわたって形成されている、請求項1ないし3のいずれか1項に記載された回路モジュール。

【請求項5】

前記基板の、前記電子部品が実装されていない側の主面に、前記接地用電極が形成されている、請求項1ないし4のいずれか1項に記載された回路モジュール。

【請求項6】

前記基板の、前記電子部品が実装されていない側の主面に、更に別の電子部品が実装され、当該電子部品を被覆した状態で、前記基板の主面に更に別の絶縁層が形成され、当該絶縁層の表面に、前記接地用電極が形成されている、請求項1ないし4のいずれか1項に記載された回路モジュール。

【請求項7】

前記シールド層と直接接続されている、少なくとも2層からなる前記内部導電層が、前記基板の内部において導電ビアにより相互に接続されている、請求項1ないし6のいずれか1項に記載された回路モジュール。

【請求項1】

内部導電層が形成された、直方体からなる基板と、

前記基板の主面に実装された電子部品と、

前記電子部品を被覆した状態で、前記基板の主面に形成された絶縁層と、

前記絶縁層の表面に形成されたシールド層と、

前記内部導電層と接続された接地用電極を備えた回路モジュールであって、

前記内部導電層は、前記基板の内部に2層以上形成され、

前記内部導電層の少なくとも2層が、それぞれ、前記シールド層と直接接続されている回路モジュール。

【請求項2】

前記シールド層と直接接続されている前記内部導電層が、前記基板の相対向する両端面から露出され、当該露出された部分が、前記シールド層と直接接続されている、請求項1に記載された回路モジュール。

【請求項3】

前記シールド層と直接接続されている前記内部導電層が、前記基板の3つの端面または4つの端面から露出され、当該露出された部分が、前記シールド層と直接接続されている、請求項2に記載された回路モジュール。

【請求項4】

前記絶縁層が、前記基板の一方の主面の全面にわたって形成されている、請求項1ないし3のいずれか1項に記載された回路モジュール。

【請求項5】

前記基板の、前記電子部品が実装されていない側の主面に、前記接地用電極が形成されている、請求項1ないし4のいずれか1項に記載された回路モジュール。

【請求項6】

前記基板の、前記電子部品が実装されていない側の主面に、更に別の電子部品が実装され、当該電子部品を被覆した状態で、前記基板の主面に更に別の絶縁層が形成され、当該絶縁層の表面に、前記接地用電極が形成されている、請求項1ないし4のいずれか1項に記載された回路モジュール。

【請求項7】

前記シールド層と直接接続されている、少なくとも2層からなる前記内部導電層が、前記基板の内部において導電ビアにより相互に接続されている、請求項1ないし6のいずれか1項に記載された回路モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−26330(P2013−26330A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−158009(P2011−158009)

【出願日】平成23年7月19日(2011.7.19)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月19日(2011.7.19)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]