回路基板、アクティブマトリックス基板、表示装置および回路基板の製造方法

【課題】酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板を提供する。

【解決手段】絶縁基板2には、第1の電極4と、第1の電極4とは電気的に分離されている第2の電極6と、第1の電極4および第2の電極6と接するように形成された酸化物半導体層5と、を備えたトラップ準位測定用パターン3が設けられている。

【解決手段】絶縁基板2には、第1の電極4と、第1の電極4とは電気的に分離されている第2の電極6と、第1の電極4および第2の電極6と接するように形成された酸化物半導体層5と、を備えたトラップ準位測定用パターン3が設けられている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路基板と、回路基板の製造方法と、上記回路基板を備えたアクティブマトリックス基板および表示装置と、に関するものである。

【背景技術】

【0002】

液晶表示装置(LCD)や有機EL表示装置(OLED)などの分野においては、さらなる高画質化を実現するため、各画素毎にアクティブ素子として、例えば、薄膜トランジスタ素子(以下TFT素子と称する)を設けたアクティブマトリックス型の基板が用いられるのが一般化されている。

【0003】

そして、上記TFT素子に備えられる半導体層の材料としては、水素化アモルファスシリコン層(a−Si:H)やレーザーなどを用いて比較的低温工程で結晶化を行った低温ポリシリコン層(Low Temperature Poly Si;LTPS)が一般的に使用されてきた。

【0004】

しかしながら、水素化アモルファスシリコン層は移動度が小さいという問題があり、低温ポリシリコン層は結晶化の際に起こる局所不均一性の問題があるため、近年では、室温でも高い移動度が得られる、インジウム(In)・ガリウム(Ga)・亜鉛(Zn)を含む酸化物(IGZO)に代表される酸化物半導体が注目されている。

【0005】

このような酸化物半導体をTFT素子の活性層として用いる場合には、酸化物半導体中のキャリア濃度が重要なパラメータとなり、キャリア濃度が大きすぎると酸化物半導体が導体化し、TFT素子としての機能を失ってしまうという問題がある。

【0006】

図18の(a)は、キャリア濃度が適切な酸化物半導体膜を備えた正常TFT素子のI−V特性を示しており、図18の(b)は、キャリア濃度が大きすぎて導体化された酸化物半導体膜を備えた不良TFT素子のI−V特性を示している。

【0007】

酸化物半導体におけるキャリア濃度は、酸素欠損により発生したトラップ準位の影響を大きく受けるため、酸化物半導体のトラップ準位を評価することにより、TFT素子を完全に作り上げる前にも、酸化物半導体のキャリア濃度を把握し、このような酸化物半導体を用いて作製されるTFT素子の良否を予測することができると考えられる。

【0008】

しかしながら、酸化物半導体のトラップ準位の評価方法については、未だ確立されておらず、酸化物半導体を備えたTFT素子を完成させた後に電気特性を測定し、TFT素子の良否判定を行うしかないのが現状であるため、不良発生から不良発見までに大きなタイムラグが生じていた。

【0009】

すなわち、酸化物半導体膜の形成工程において、多数の酸素欠陥が生じ、導体化された酸化物半導体膜が形成されたとしても、酸化物半導体膜の形成工程の直後に、導体化された酸化物半導体膜が形成されたことに気付くことはできず、そのまま、TFT素子を形成する後工程を行い、TFT素子を完成させた後、TFT素子の電気特性を測定し、始めて導体化された酸化物半導体膜が形成されたことに気付くこととなる。

【0010】

このような酸化物半導体膜の評価方法は、後からTFT素子が不良であると判定された場合、材料や時間を無駄に使ったこととなるので、生産単価や生産効率を考慮すると好ましくない方法である。

【0011】

そこで、特許文献1には、非晶質または多結晶性の酸化物半導体層の膜質を非破壊で迅速に調べることのできる検査方法について開示されている。

【0012】

図19の(a)は、特許文献1に記載されている酸化物半導体層の膜質の検査方法を説明するための図であり、図19の(b)は、上記検査方法によって得られたフォトルミネッセンス光のスペクトルを示す図である。

【0013】

特許文献1には、図19の(a)に図示されているように、表面に検査しようとする非晶質又は多結晶性の被検査酸化物半導体層が形成された基板110に対して、レーザー光源などの励起光源101から出射された励起光102を照射し、被検査酸化物半導体層から反射される反射光103のうち、バンドギャップエネルギーに対応する波長よりも長い波長領域のフォトルミネッセンス光104の強度を光検出器105で測定し、図19の(b)に図示されているようなデータを得て、図示されてない計測機器に送る構成が開示されている。

【0014】

上記構成においては、上記被検査酸化物半導体層に対して、測定を行う前に、上記被検査酸化物半導体層と同じ工程で作製され、上記被検査酸化物半導体層と同じ元素組成と膜厚とを有する、非晶質又は多結晶性の参照用酸化物半導体層に対し、同じフォトルミネッセンス光強度の測定と、膜質の測定とを行い、フォトルミネッセンス光強度と膜質との関係を得て、この関係に基づいて上記被検査酸化物半導体層の膜質を推定することができる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2010−123872号(2010年6月3日公開)

【発明の概要】

【発明が解決しようとする課題】

【0016】

しかしながら、上記特許文献1に記載されている酸化物半導体層の膜質の検査方法は、単層で形成された酸化物半導体層の評価には有効であるが、実際のTFT素子の活性層として用いられた酸化物半導体層の状態を十分に反映できないという問題がある。

【0017】

すなわち、実際のTFT素子の活性層として用いられた酸化物半導体層の上層には、金属膜からなるソース電極およびドレイン電極や絶縁膜が形成され、これらの膜と上記酸化物半導体層との界面にも酸素欠損が生じ、このように界面で生じた酸素欠損が酸化物半導体層の特性に及ぼす影響も大きいことが知られているが、図19の(a)に図示されている上記特許文献1に記載の酸化物半導体層の膜質の検査方法においては、このように界面で生じる酸素欠損を反映することができず、この検査方法によるTFT素子の良否の予測は精度が低いため、有効に用いることができない。

【0018】

本発明は、上記の問題点に鑑みてなされたものであり、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板と、アクティブマトリックス基板と、表示装置と、上記回路基板の製造方法と、を提供することを目的とする。

【課題を解決するための手段】

【0019】

本発明の回路基板は、上記の課題を解決するために、絶縁基板の一方側の面に、酸化物半導体層が備えられている回路基板であって、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、上記第1の電極とは電気的に分離されている第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられていることを特徴としている。

【0020】

上記構成によれば、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、第2の電極と、上記第1の電極および上記第2の電極と接するように形成された酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられている。

【0021】

上記酸化物半導体層は、上記第1の電極および上記第2の電極と接するように形成されているので、上記トラップ準位測定用パターンを用いて、例えば、熱刺激電流測定を行えば、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0022】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板を実現することができる。

【0023】

本発明の回路基板は、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、上記絶縁基板の中心部を含む領域である第1の領域と、上記第1の領域の周辺領域であるとともに、上記絶縁基板の端部を含む領域である第2の領域と、が備えられており、上記第2の領域に、上記トラップ準位測定用パターンが設けられていることが好ましい。

【0024】

上記構成によれば、第1の電極と、第2の電極と、酸化物半導体層と、を備えたトラップ準位測定用パターンが、上記第1の領域の周辺領域であるとともに、上記絶縁基板の端部を含む領域である第2の領域に設けられているので、上記トラップ準位測定用パターンを見えなくする必要がある場合などに、第2の領域のみを覆うように遮光部材を設ければよいので、表示装置などに容易に用いることができる回路基板を実現することができる。

【0025】

また、必要に応じて、上記トラップ準位測定用パターンを除去する場合においても容易である。

【0026】

本発明の回路基板の上記トラップ準位測定用パターンにおいて、上記酸化物半導体層は、上記第1の電極と上記第2の電極との間に、介在されていることが好ましい。

【0027】

上記構成によれば、上記酸化物半導体層が上記第1の電極および上記第2の電極との間に介在されている上記トラップ準位測定用パターンを用いて、例えば、熱刺激電流測定を行えば、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0028】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板を実現することができる。

【0029】

本発明の回路基板の上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されていることが好ましい。

【0030】

上記構成によれば、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されている上記トラップ準位測定用パターンを用いて、例えば、熱刺激電流測定を行えば、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0031】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板を実現することができる。

【0032】

また、上記構成によれば、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方側に形成されているため、上記第1の電極と上記第2の電極との形成工程を一つの工程で行うことができる。

【0033】

したがって、上記トラップ準位測定用パターンの形成工程を短縮することができる。

【0034】

本発明の回路基板の上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されていることが好ましい。

【0035】

上記構成によれば、上記第1の電極と上記第2の電極とを用いて行うことができる熱刺激電流測定のみならず、上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層を備えたトラジスタ素子の特性を評価することができる。

【0036】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測をさらに精度高く行うことができる回路基板を実現することができる。

【0037】

本発明の回路基板における上記第1の電極および上記第2の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0038】

上記構成によれば、上記トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極は、別途の新たな導電性材料で形成する必要はなく、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0039】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極と、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成するある一つの導電層と、を同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0040】

本発明の回路基板において、上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0041】

上記構成によれば、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極は、別途の新たな導電性材料で形成する必要はなく、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0042】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極の各々を、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層の形成工程と、同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0043】

本発明の回路基板において、上記酸化物半導体層は、In、Ga、Znから選択される少なくとも一つの元素を含むことが好ましい。

【0044】

上記構成によれば、室温でも高い移動度を有する酸化物半導体層を備えた回路基板を実現することができる。

【0045】

本発明のアクティブマトリックス基板は、上記の課題を解決するために、上記回路基板を備え、上記回路基板上には、上記酸化物半導体層と同一層によって形成された半導体層を備えた複数のアクティブ素子が設けられており、上記アクティブ素子の各々には、画素電極が電気的に接続されており、複数の上記画素電極がマトリックス状に形成されていることを特徴としている。

【0046】

上記構成によれば、室温でも高い移動度を有する酸化物半導体層を備えたアクティブ素子と、上記アクティブ素子の各々に電気的に接続された画素電極がマトリックス状に形成されているアクティブマトリックス基板を実現することができる。

【0047】

本発明のアクティブマトリックス基板の上記トラップ準位測定用パターンにおいて、上記第1の電極および上記第2の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0048】

上記構成によれば、トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極は、別途の新たな導電性材料で形成する必要はなく、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0049】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極と、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成するある一つの導電層と、を同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0050】

本発明のアクティブマトリックス基板の上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0051】

上記構成によれば、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極は、別途の新たな導電性材料で形成する必要はなく、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0052】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極の各々を、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層の形成工程と、同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0053】

本発明の表示装置は、上記の課題を解決するために、上記アクティブマトリックス基板と、対向基板と、上記アクティブマトリックス基板と上記対向基板との間に介在された液晶層と、を備えていることを特徴としている。

【0054】

上記構成によれば、その製造工程において、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる液晶表示装置を実現することができる。

【0055】

本発明の表示装置は、上記の課題を解決するために、上記アクティブマトリックス基板と、上記アクティブマトリックス基板における上記画素電極が形成されている面側に形成された有機EL層と、を備えていることを特徴としている。

【0056】

上記構成によれば、その製造工程において、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる有機EL表示装置を実現することができる。

【0057】

本発明の回路基板の製造方法は、上記の課題を解決するために、絶縁基板の一方側の面に、酸化物半導体層が備えられた回路基板の製造方法であって、上記絶縁基板において上記酸化物半導体層が形成されている側の面に、第1の電極と、上記第1の電極とは電気的に分離された第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンを形成する工程と、熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程と、が含まれていることを特徴としている。

【0058】

上記製造方法によれば、第1の電極と、第2の電極と、上記第1の電極および上記第2の電極と接するように形成された酸化物半導体層と、を備えたトラップ準位測定用パターンを用いて、熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程が含まれている。

【0059】

上記酸化物半導体層は、上記第1の電極および上記第2の電極と接するように形成されているので、上記酸化物半導体層のトラップ準位の測定においては、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0060】

したがって、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板の製造方法を実現することができる。

【0061】

本発明の回路基板の製造方法において、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層のトラジスタ素子特性を評価する工程が含まれていることが好ましい。

【0062】

上記製造方法によれば、上記第1の電極と上記第2の電極とを用いて、熱刺激電流測定を行う工程のみならず、上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層のトラジスタ素子としての特性を評価する工程も含まれている。

【0063】

したがって、さらに精度高く酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を行うことができる回路基板の製造方法を実現することができる。

【発明の効果】

【0064】

本発明の回路基板は、以上のように、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、上記第1の電極とは電気的に分離されている第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられている構成である。

【0065】

また、本発明のアクティブマトリックス基板は、以上のように、上記回路基板を備え、上記回路基板上には、上記酸化物半導体層と同一層によって形成された半導体層を備えた複数のアクティブ素子が設けられており、上記アクティブ素子の各々には、画素電極が電気的に接続されており、複数の上記画素電極がマトリックス状に形成されている構成である。

【0066】

また、本発明の表示装置は、以上のように、上記アクティブマトリックス基板と、対向基板と、上記アクティブマトリックス基板と上記対向基板との間に介在された液晶層と、を備えている構成である。

【0067】

また、本発明の表示装置は、以上のように、上記アクティブマトリックス基板と、上記アクティブマトリックス基板における上記画素電極が形成されている面側に形成された有機EL層と、を備えている構成である。

【0068】

また、本発明の回路基板の製造方法は、以上のように、上記絶縁基板において上記酸化物半導体層が形成されている側の面に、第1の電極と、上記第1の電極とは電気的に分離された第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンを形成する工程と、熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程と、が含まれている方法である。

【0069】

それゆえ、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板と、アクティブマトリックス基板と、表示装置と、上記回路基板の製造方法と、を実現することができる。

【図面の簡単な説明】

【0070】

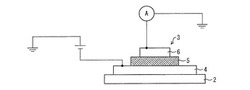

【図1】本発明の一実施の形態の回路基板に備えられたトラップ準位測定用パターンの断面構造を示すとともに、トラップ準位測定用パターンを用いて熱刺激電流計測システムを作製する場合を示す図である。

【図2】本発明の一実施の形態の回路基板の概略構成を示す図である。

【図3】本発明の一実施の形態の回路基板である大型アクティブマトリックス基板の一例を示す図である。

【図4】本発明の一実施の形態の回路基板である大型アクティブマトリックス基板のさらに他の一例を示す図である。

【図5】トラップ準位測定用パターンを用いて熱刺激電流測定を行う方法を説明するための図であり、(a)は、トラップ電圧の印加により、発生させた電子・正孔を酸化物半導体層5におけるトラップ準位に捕獲、凍結させた状態を示し、(b)は、昇温による熱的効果により、浅いトラップ準位から順に電子・正孔が解放される状態を示す。

【図6】トラップ準位測定用パターンに備えられた酸化物半導体層の正常膜および不良膜の熱刺激電流測定結果を示す図である。

【図7】従来から用いられている酸化物半導体層を備えたTFT素子が形成されたアクティブマトリックス基板の製造プロセスを示す図である。

【図8】本発明の一実施の形態の回路基板である大型アクティブマトリックス基板上に、酸化物半導体層を備えたトラップ準位測定用パターンと、酸化物半導体層を備えたTFT素子と、を形成する製造プロセスの一例を示す図である。

【図9】本発明の一実施の形態の回路基板である絶縁基板に酸化物半導体層を備えたトラップ準位測定用パターンを形成し、酸化物半導体層の形成条件を先に確定した後、この確定された酸化物半導体層の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層を備えたTFT素子を、従来の方法で形成する製造プロセスの一例を示す図である。

【図10】本発明の他の一実施の形態の回路基板である大型アクティブマトリックス基板の一例を示す図である。

【図11】本発明の他の一実施の形態の回路基板である大型アクティブマトリックス基板に備えられたトラップ準位測定用パターンの断面構造を示すとともに、トラップ準位測定用パターンを用いて熱刺激電流計測システムを作製する場合を示す図である。

【図12】本発明の他の一実施の形態の回路基板である絶縁基板に酸化物半導体層を備えたトラップ準位測定用パターンを形成し、酸化物半導体層の形成条件を先に確定した後、この確定された酸化物半導体層の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層を備えたTFT素子を、従来の方法で形成する製造プロセスの一例を示す図である。

【図13】本発明の他の一実施の形態の回路基板である大型アクティブマトリックス基板上に、酸化物半導体層を備えたトラップ準位測定用パターンと、酸化物半導体層を備えたTFT素子と、を形成する製造プロセスの一例を示す図である。

【図14】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板の一例を示す図である。

【図15】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板に備えられたトラップ準位測定用パターンの断面構造を示すとともに、トラップ準位測定用パターンを用いて熱刺激電流計測システムを作製する場合を示す図である。

【図16】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板に備えられたトラップ準位測定用パターンを用いて、TFT素子としての電気特性測定を行う場合の一例を示す図である。

【図17】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板上に、酸化物半導体層を備えたトラップ準位測定用パターンと、酸化物半導体層を備えたTFT素子と、を形成する製造プロセスの一例を示す図である。

【図18】TFT素子の電気特性測定の結果を示す図であり、(a)は、キャリア濃度が適切な酸化物半導体膜を備えた正常TFT素子のI−V特性を示し、(b)は、キャリア濃度が大きすぎて導体化された酸化物半導体膜を備えた不良TFT素子のI−V特性を示している。

【図19】特許文献1に記載されている酸化物半導体層の膜質の検査方法および上記検査方法によって得られたフォトルミネッセンス光のスペクトルを示す図である。

【発明を実施するための形態】

【0071】

以下、図面に基づいて本発明の実施の形態について詳しく説明する。ただし、この実施の形態に記載されている構成部品の寸法、材質、形状、その相対配置などはあくまで一実施形態に過ぎず、これらによってこの発明の範囲が限定解釈されるべきではない。

【0072】

〔実施の形態1〕

以下、図1から図9に基づいて、本発明の第1の実施形態について説明する。

【0073】

図2は、絶縁基板2上の任意の箇所に、トラップ準位測定用パターン3が設けられている回路基板1の概略構成を示す図である。

【0074】

回路基板1は、トラップ準位測定用パターン3と、トラップ準位測定用パターン3に備えられた酸化物半導体層5と同一層によって形成された酸化物半導体層と、を備えた半導体基板や表示装置に用いられるアクティブマトリックス基板などであることができる。

【0075】

なお、図示されているように、絶縁基板2には、絶縁基板2の中心部を含む領域である第1の領域R1と、第1の領域R1の周辺領域であるとともに、絶縁基板2の端部を含む領域である第2の領域R2と、が備えられており、トラップ準位測定用パターン3は、第2の領域R2に設けられていることが好ましい。

【0076】

そして、トラップ準位測定用パターン3に備えられた酸化物半導体層5と同一層によって形成された酸化物半導体層は、絶縁基板2の中心部を含む領域である第1の領域R1に形成されることになる。

【0077】

このような構成によれば、トラップ準位測定用パターン3が、絶縁基板2の端部を含む領域である第2の領域R2に設けられているので、トラップ準位測定用パターン3を見えなくする必要がある場合などに、第2の領域R2のみを覆うように遮光部材を設ければよいので、表示装置などに容易に用いることができる回路基板1を実現することができる。

【0078】

図1は、図2に示すトラップ準位測定用パターン3のA−A‘線の断面構造を示すとともに、トラップ準位測定用パターン3を用いて詳しくは後述する熱刺激電流計測システムを作製する場合を示す図である。

【0079】

図示されているように、トラップ準位測定用パターン3は、絶縁基板2上に第1の電極4を形成する第一の導電膜と、酸化物半導体層5と、第2の電極6を形成する第二の導電膜と、が順に積層された構造となっており、酸化物半導体層5が第1の電極4と第2の電極6との間に介在された構造となっている。

【0080】

トラップ準位測定用パターンの構造はこれに限定されることはなく、酸化物半導体層5が、第1の電極4および第2の電極6と接するように形成されていれば、例えば、後述する実施の形態2および実施の形態3に記載されているような構造であってもよい。

【0081】

このような構成によれば、絶縁基板2において酸化物半導体層5が形成されている側の面には、第1の電極4と、第2の電極6と、第1の電極4および第2の電極6と接するように形成された酸化物半導体層5と、を備えたトラップ準位測定用パターン3が設けられている。

【0082】

酸化物半導体層5は、第1の電極4および第2の電極6と接するように形成されているので、トラップ準位測定用パターン3を用いて、後述する熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極4および第2の電極6との界面における酸素欠損状態も反映することができる。

【0083】

したがって、酸化物半導体層5を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板1を実現することができる。

【0084】

なお、酸化物半導体層5としては、In、Ga、Znから選択される少なくとも一つの元素を含む酸化物を用いることができ、本実施の形態においては、In、GaおよびZnを全て含むIGZO系酸化物半導体層を用いているが、これに限定されることはなく、例えば、Zn−O系酸化物、In−Si−Zn−O系酸化物、In−Al−Zn−O系酸化物、In−Mg−Zn−O系酸化物などを半導体層として用いることもできる。

【0085】

また、酸化物半導体層5の結晶の状態は、特に限定されず、例えば、非結晶半導体層や多結晶半導体層や連続粒界結晶半導体層であることができる。

【0086】

第1の電極4を形成する第一の導電膜および第2の電極6を形成する第二の導電膜の材質としては、導電性がある材料であれば良いが、その一例としてタンタル(Ta)、モリブデン(Mo)、チタン(Ti)、銅(Cu)、アルミニウム(Al)、等があげられる。これらの材料は低抵抗であるため、熱刺激電流計測の際に微小な電流であっても正確に計測することができる。

【0087】

また、第1の電極4を形成する第一の導電膜および第2の電極6を形成する第二の導電膜の材質としては、上記導電性がある材料の積層膜を用いることもできる。

【0088】

なお、図2に図示されているように、絶縁基板2の中心部を含む領域である第1の領域R1には、トラップ準位測定用パターン3に備えられた酸化物半導体層5と同一層によって形成された酸化物半導体層を備えたアクティブ素子であるトラジスタ素子(以下TFT素子と称する)などが形成されるが、例えば、上記TFT素子がトップゲート型で形成される場合には、第2の電極6をゲート配線材料で形成し、第1の電極4をソース・ドレイン配線材料で形成し、ゲート配線材料やソース・ドレイン配線材料のパターン形成時に同時に第2の電極6や第1の電極4をパターンニングすればよい。

【0089】

一方、上記TFT素子がボトムゲート型で形成される場合には、第1の電極4をゲート配線材料で形成し、第2の電極6をソース・ドレイン配線材料で形成し、ゲート配線材料やソース・ドレイン配線材料のパターン形成時に同時に第1の電極4や第2の電極6をパターンニングすればよい。

【0090】

このようにすれば、新たな材料を使用したり工程数を増やしたりすることなく、トラップ準位測定用パターン3を形成できる。

【0091】

また、第2の電極6を上記TFT素子に接続された画素電極の形成層で形成することもできる。画素電極が反射型の画素電極である場合、アルミニウム(Al)等で形成されるため、好適に用いることができる。

【0092】

また、トラップ準位測定用パターン3は、図2に図示されている第1の領域R1に形成される上記TFT素子と電気的に接続されている配線パターンとリークすると誤動作を引き起こすため、図2に図示されているように、第2の領域R2に浮島構造で形成する必要がある。

【0093】

また、詳しくは後述するが、トラップ準位測定用パターン3は、図2に図示されている第1の領域R1に上記TFT素子を形成する工程より先に形成することもできる。

【0094】

なお、トラップ準位測定用パターン3における酸化物半導体層5の膜厚は特に限定されないが、図2に図示されている第1の領域R1に形成されるTFT素子に備えられる酸化物半導体層の膜厚と同じであってもよく、例えば、50nm程度であればよい。

【0095】

また、トラップ準位測定用パターン3を用いて熱刺激電流計測を行うためには、トラップ準位測定用パターン3における第1の電極4と第2の電極6との何れか一方に電圧源を接続させ、他方に熱刺激電流計を接続させればよく、本実施の形態においては、図1に図示されているように、第1の電極4に電圧源を接続させ、第2の電極6に熱刺激電流計を接続させている。

【0096】

そして、第1の電極4と第2の電極6とには、熱刺激電流計測の際に電圧を印加するために、導電性ワイヤーを接続する必要があるので、第1の電極4と第2の電極6とは5mm×1mm程度以上の大きさで形成されることが好ましい。

【0097】

また、図1に図示されているように、第1の電極4の表面は、5mm×1mm程度以上の大きさが露出されるように、酸化物半導体層5と第2の電極6とが形成されることが好ましい。

【0098】

第1の電極4と第2の電極6との膜厚は特に限定されないが、図2に図示されている第1の領域R1に形成されるTFT素子のゲート電極やソース・ドレイン電極や配線の膜厚と同一に形成してもよく、例えば、400nm程度で形成することができる。

【0099】

以上のように形成したトラップ準位測定用パターン3を用いて、熱刺激電流測定を実施することができるが、この測定には2〜3時間程度の時間を要するため、抜き取りで行うことが好ましい。

【0100】

また、トラップ準位測定用パターン3および図2に図示されている第1の領域R1に形成されるTFT素子に備えられる酸化物半導体層5の形成に用いられる膜蒸着装置のメンテナンス後などに、トラップ準位測定用パターン3を用いて、熱刺激電流測定を実施し、酸化物半導体層5の膜質評価を行うと、メンテナンスによる膜質変化を早期に発見できる。

【0101】

また、熱刺激電流測定において、トラップ準位によって生じる熱刺激電流が大きく観測されると、このような酸化物半導体層を備えたTFT素子は不良となるため、酸化物半導体層の蒸着時に酸素分圧を上げて酸素欠損の発生を抑えるなどの対策を迅速に実施することができる。

【0102】

トラップ準位測定用パターン3を用いることによって、TFT素子を完成する前にも、熱刺激電流測定を実施できるため、不良品を流出させることなく迅速に酸化物半導体層の不具合に対応することができる。

【0103】

以下、図3および図4に基づいて、回路基板がトラップ準位測定用パターン3を備えた大型アクティブマトリックス基板である場合について説明する。

【0104】

図3は、絶縁基板2上にトラップ準位測定用パターン3を備えた大型アクティブマトリックス基板1aの一例を示す図である。

【0105】

図示されているように、大型アクティブマトリックス基板1aは分断すると、9個のTFT基板11(図中において点線で表示)を得ることができる。

【0106】

そして、TFT基板11には、表示領域R1と非表示領域R2が備えられており、TFT基板11とは離れた位置である絶縁基板2の端部に存在する端部領域R3には、トラップ準位測定用パターン3が設けられている。

【0107】

トラップ準位測定用パターン3をこのような位置に配置することにより、大型アクティブマトリックス基板1aを分断する際に、不要となったトラップ準位測定用パターン3を取り除くことができる。

【0108】

TFT基板11の表示領域R1には、各画素毎に画素電極10を備えた画素TFT素子7が設けられている。

【0109】

画素TFT素子7は、トラップ準位測定用パターン3の第1の電極4と同一層によって形成されたゲート電極4Gと、ゲート絶縁膜8と、トラップ準位測定用パターン3の酸化物半導体層5と同一層によって形成された酸化物半導体層5と、トラップ準位測定用パターン3の第2の電極6と同一層によって形成されたソース・ドレイン電極6S・6Dと、を備えた構成となっている。

【0110】

そして、ドレイン電極6Dは、層間絶縁膜9に形成されたコンタクトホールを介して、画素電極10と電気的に接続されている。

【0111】

図4は、大型アクティブマトリックス基板において、トラップ準位測定用パターン3を設ける位置や数を変えた一例を示す図である。

【0112】

図3に図示されているように、大型アクティブマトリックス基板において、トラップ準位測定用パターン3を設ける位置や数は、絶縁基板2の端部に存在する端部領域R3や一つに限定されることはなく、例えば、図4に図示されているように、トラップ準位測定用パターン3をTFT基板11の非表示領域R2毎に設けることもできる。

【0113】

図4に図示されているように、トラップ準位測定用パターン3を配置することにより、大型アクティブマトリックス基板1bに酸化物半導体層5を形成する際に、形成位置毎にバラツキが生じたとしでも、各TFT基板11に設けられたトラップ準位測定用パターン3を用いて、熱刺激電流測定を行うことができるので、酸化物半導体層5を備えたTFT素子の良否の予測を精度高く行うことができる。

【0114】

また、大型アクティブマトリックス基板1bをTFT基板11に分断した後にも、各TFT基板11には、トラップ準位測定用パターン3が残るので、大型アクティブマトリックス基板1bの分断工程後に、必要に応じて、トラップ準位測定用パターン3を用いて測定を行うことができる。

【0115】

以下、図5および図6に基づいて、熱刺激電流測定を行う方法について詳しく説明する。

【0116】

先ず、図2、図3および図4に図示した回路基板1やアクティブマトリックス基板1a・1bを試料とし、上記試料における少なくともトラップ準位測定用パターン3を液体窒素を用いて冷却する。

【0117】

また、上記液体窒素を用いた冷却においては、トラップ準位測定用パターン3のみを冷却してもよいし、これが困難である場合には、回路基板1やアクティブマトリックス基板1a・1b全体を冷却してもよい。

【0118】

図5(a)は、トラップ電圧の印加により、発生させた電子・正孔を酸化物半導体層5におけるトラップ準位に捕獲、凍結させた状態を示す図であり、図5(b)は、昇温による熱的効果により、浅いトラップ準位から順に電子・正孔が解放される状態を示す図である。

【0119】

トラップ準位測定用パターン3を液体窒素領域まで冷却後に、第1の電極4にトラップ電圧を印加し、電子・正孔を発生させ、図5(a)に図示されているように、酸化物半導体層5におけるトラップ準位に電子・正孔を捕獲、凍結させる(図1参照)。

【0120】

なお、電子・正孔は、光照射により発生させることもできる。

【0121】

次に、トラップ準位測定用パターン3を一定速度で昇温すると、熱的効果により、図5(b)に図示されているように、浅いトラップ準位から順に電子・正孔が解放される。

【0122】

これらの解放は熱刺激電流として、第2の電極6を介して観測される。このようにして観測した熱刺激電流値を解析することにより、酸化物半導体層5におけるバンドギャップ中のトラップ準位に関する情報を得ることができる。

【0123】

酸化物半導体層5においては、トラップ準位は酸素欠損に大きく依存して発生されることから、熱刺激電流値を解析することで、トラップ準位および酸素欠損についての情報を得ることができる。

【0124】

なお、本実施の形態において用いた熱刺激電流測定の測定条件は、以下の通りである。

【0125】

測定雰囲気は、不活性気体であるHe下(封じ切り)で行っており、昇温速度は10℃/minに、測定温度範囲は−180℃〜350℃に、トラップ電圧は30Vに、光は520nm波長の光を基準に100μW/cm2となるような強度とし、2分間照射されるようにそれぞれの条件を設定した。

【0126】

なお、本実施の形態においては、電子・正孔を発生させる方法として、トラップ電圧の印加と光照射の両方を用いている。

【0127】

上記測定条件は、一例であり、必要に応じて測定条件は適宜変えることができる。

【0128】

図6は、酸化物半導体層5の正常膜および不良膜の熱刺激電流測定結果を示す図である。

【0129】

図6(a)は、正常な酸化物半導体層5の熱刺激電流測定結果を示しており、図6(b)は、トラップ準位が存在する不良な酸化物半導体層5の熱刺激電流測定結果を示している。

【0130】

図6(a)に図示されているように、正常な酸化物半導体層5においては、−200℃〜100℃の範囲内では電流値のピークは見られないが、図6(b)に図示されているように、トラップ準位が存在する不良な酸化物半導体層5においては、0℃付近にトラップ準位の存在を示す電流値のピークが確認される。

【0131】

熱刺激電流値がピークを示す温度Tと、トラップ準位の深さEには、下記式1で示す関係がある。

【0132】

E=kT・ln(T4/β) (式1)

上記式1において、kはボルツマン定数であり、βは昇温速度であり、Tは絶対温度である。

【0133】

上記式1から、0℃付近にピークを有する熱刺激電流値は、0.57eVの深さにトラップ準位が存在することを意味している。

【0134】

以上のように、熱刺激電流測定によって酸化物半導体層5の膜質に大きな影響を及ぼすトラップ準位の評価を行うことができる。

【0135】

以下、図7から図9に基づいて、大型アクティブマトリックス基板1a・1b上に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスについて説明する。

【0136】

図7は、従来から用いられている酸化物半導体層を備えたTFT素子が形成されたアクティブマトリックス基板の製造プロセスを示す。

【0137】

図示されているように、この従来の製造プロセスにおいては、S101〜S106までの工程を経て、画素電極を有するTFT素子を完成させた後に、この完成されたTFT素子の電気的特性の測定(S107)を行い、良不判定を行っているため、酸化物半導体層に起因して不良が生じているか、TFT素子に備えられた他の層によって不良が生じているか、を特定することが困難であった。

【0138】

また、TFT素子を完成させた後に、電気的特性の測定(S107)を行った結果が不良であり、その原因を解析した後に、上記TFT素子に備えられた各層の成膜工程などに問題があったことを気付くことになるので、材料や時間を無駄に使ったこととなり、生産単価や生産効率を考慮すると好ましくない製造プロセスである。

【0139】

なお、以下に説明する図8に示す製造プロセスは、同一基板内に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスの一例であり、図9に示す製造プロセスは、異なる2つの基板に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、のそれぞれを形成する製造プロセスの一例を示す。

【0140】

図8は、大型アクティブマトリックス基板1a・1b上に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスの一例を示す図である。

【0141】

先ず、トラップ準位測定用パターン3に備えられた第1の電極4と、TFT素子7に備えられたゲート電極4Gとを、同一層を用いて一つの形成工程で形成する(S11)。

【0142】

そして、トラップ準位測定用パターン3が形成されている領域以外にゲート絶縁膜8を形成する(S12)。

【0143】

それから、トラップ準位測定用パターン3とTFT素子7とに備えられた酸化物半導体層5を、同一層を用いて一つの形成工程で形成する(S13)。

【0144】

そして、トラップ準位測定用パターン3に備えられた第2の電極6と、TFT素子7に備えられたソース・ドレイン電極6S・6Dとを、同一層を用いて一つの形成工程で形成する(S14)。

【0145】

第1の電極4および第2の電極6と接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン3を用いて、熱刺激電流測定(S15)を行うことができる。

【0146】

熱刺激電流測定の結果が良判定であれば、次工程である層間絶縁膜9の形成工程(S16)と画素電極10パターン形成工程(S17)とを行い、TFT素子7を完成させる。

【0147】

一方、熱刺激電流測定の結果が不良判定であれば、酸化物半導体層5の形成工程(S13)において問題があったこととなるので、酸化物半導体層5の形成条件を見直し、新しい基板にS11〜S14の工程を行い、再び、熱刺激電流測定(S15)を行う。

【0148】

このような製造プロセスを用いることにより、TFT素子7を完成させる前にも、TFT素子7に備えられた酸化物半導体層5が正常に形成されているかを精度高く把握することができる。

【0149】

また、TFT素子7を完成させる前の中間の段階で、酸化物半導体層5が正常に形成されているかを把握することができるので、TFT素子7を完成させた後に、TFT素子7が不良であると判定された場合には、酸化物半導体層5以外の部分で問題が生じた可能性が高いと推定することができる。

【0150】

したがって、TFT素子7の不良の原因が、酸化物半導体層5に起因して生じているか、TFT素子7に備えられた他の層によって不生じているか、を特定するのが容易になる。

【0151】

また、このような製造プロセスを用いることにより、酸化物半導体層5の蒸着工程において、突発的なトラブルが生じ、膜質に不具合が発生したとしても、酸化物半導体層5におけるトラップ準位の評価を行うことで、迅速に対応ができ、製造プロセスへの早急なフィードバックを行うことができる。

【0152】

したがって、早急なトラブル解消が可能となり、結果、生産効率や歩留りの向上を期待できる。

【0153】

また、このような製造プロセスにおいては、第1の電極4および第2の電極6の各々は、酸化物半導体層5を半導体層として備えたTFT素子7の電極層および配線を形成する導電層と同一材料で形成されているので、新たな材料や工程を追加する必要がなく、製造コストを抑えることが可能となる。

【0154】

図9は、絶縁基板に酸化物半導体層5を備えたトラップ準位測定用パターン3を形成し、酸化物半導体層5の形成条件を先に確定した後、この確定された酸化物半導体層5の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、従来の方法で形成する製造プロセスの一例を示す図である。

【0155】

図示されているように、先ず、絶縁基板上に、第1の電極4を形成し(S21)、その後、酸化物半導体層5を形成し(S22)、最後に第2の電極6を形成し(S23)、トラップ準位測定用パターン3を完成させ、第1の電極4および第2の電極6と接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン3を用いて、熱刺激電流測定(S24)を行う。

【0156】

この熱刺激電流測定(S24)の結果が良判定であれば、酸化物半導体層5を形成する工程(S22)で用いた条件をそのまま用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、S101〜S106の工程で構成される従来の方法で形成する。

【0157】

一方、熱刺激電流測定(S24)の結果が不良判定であれば、酸化物半導体層5を形成する工程(S22)で用いた条件を見直し、再び、新たな絶縁基板にS21〜S23の工程を行い、トラップ準位測定用パターン3を完成させ、このトラップ準位測定用パターン3を用いて、熱刺激電流測定(S24)を行う。

【0158】

このような製造プロセスを用いることにより、酸化物半導体層5の形成条件を、比較的に容易に形成することができるとともに、精度高く酸化物半導体層5のトラップ準位を把握することができるトラップ準位測定用パターン3を用いて、確定することができる。

【0159】

なお、TFT基板11は、液晶表示装置や有機EL表示装置などの各種表示装置用に好適に用いることができる。

【0160】

〔実施の形態2〕

次に、図10から図13に基づいて、本発明の第2の実施形態について説明する。本実施の形態においては、絶縁基板2上にトラップ準位測定用パターンを形成することは実施の形態1と同様であるが、トラップ準位測定用パターン12の構造が、実施の形態1で用いたトラップ準位測定用パターン3とは異なる。その他の構成については実施の形態1において説明したとおりである。説明の便宜上、上記の実施の形態1の図面に示した部材と同じ機能を有する部材については、同じ符号を付し、その説明を省略する。

【0161】

図10は、絶縁基板2上にトラップ準位測定用パターン12を備えた大型アクティブマトリックス基板1cの一例を示す図である。

【0162】

図示されているように、大型アクティブマトリックス基板1cは分断すると、9個のTFT基板11(図中において点線で表示)を得ることができる。

【0163】

そして、TFT基板11には、表示領域R1と非表示領域R2が備えられており、TFT基板11とは離れた位置である絶縁基板2の端部に存在する端部領域R3には、トラップ準位測定用パターン12が設けられている。

【0164】

トラップ準位測定用パターン12は、酸化物半導体層5上に2個の独立した電極である第1の電極6Aと第2の電極6Bとの両方が形成された構造を有する。

【0165】

そして、第1の電極6Aと第2の電極6Bとは、同一層で形成されているとともに、本実施の形態においては、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、同一層を用いて一つの形成工程で形成した。

【0166】

図11は、図10に示すトラップ準位測定用パターン12のB−B‘線の断面構造を示すとともに、トラップ準位測定用パターン12を用いて熱刺激電流計測システムを作製する場合を示す図である。

【0167】

図示されているように、本実施の形態においては、第1の電極6Aに電圧源を接続させ、第2の電極6Bに熱刺激電流計を接続させている。

【0168】

そして、第1の電極6Aと第2の電極6Bとには、熱刺激電流計測の際に電圧を印加するために、導電性ワイヤーを接続する必要があるので、第1の電極6Aと第2の電極6Bとは5mm×1mm程度以上の大きさで形成されることが好ましい。

【0169】

また、第1の電極6Aと第2の電極6Bとの間の距離は特に限定されないが、一例として1mm程度で形成することができる。

【0170】

また、第1の電極6Aと第2の電極6Bとは、TFT素子7に接続された画素電極10の形成層で形成することもできる。画素電極10が反射型の画素電極である場合、アルミニウム(Al)等で形成されるため、好適に用いることができる。

【0171】

なお、以下に説明する図12に示す製造プロセスは、異なる2つの基板に、酸化物半導体層5を備えたトラップ準位測定用パターン12と、酸化物半導体層5を備えたTFT素子7と、のそれぞれを形成する製造プロセスの一例を示し、図13に示す製造プロセスは、同一基板内に、酸化物半導体層5を備えたトラップ準位測定用パターン12と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスの一例を示す。

【0172】

図12は、絶縁基板に酸化物半導体層5を備えたトラップ準位測定用パターン12を形成し、酸化物半導体層5の形成条件を先に確定した後、この確定された酸化物半導体層5の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、従来の方法で形成する製造プロセスの一例を示す図である。

【0173】

図示されているように、先ず、酸化物半導体層5を形成し(S31)、その後、酸化物半導体層5上に、第1の電極6Aと第2の電極6Bとを同一層を用いた一つの工程で形成し(S32)、トラップ準位測定用パターン12を完成させ、第1の電極6Aおよび第2の電極6Bと接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン12を用いて、熱刺激電流測定(S33)を行う。

【0174】

トラップ準位測定用パターン12において、酸化物半導体層5は、第1の電極6Aおよび第2の電極6Bと接するように形成されているので、トラップ準位測定用パターン12を用いて、熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極6Aおよび第2の電極6Bとの界面における酸素欠損状態も反映することができる。

【0175】

以上のように、トラップ準位測定用パターン12の製造プロセスが、実施の形態1で用いたトラップ準位測定用パターン3の製造プロセスより、短縮されており、酸化物半導体層5の形成条件を、さらに容易に形成することができるとともに、精度高く酸化物半導体層5のトラップ準位を把握することができるトラップ準位測定用パターン12を用いて、確定することができる。

【0176】

その他の工程については、実施の形態1で既に説明しているため、その説明を省略する。

【0177】

図13は、大型アクティブマトリックス基板1c上に、酸化物半導体層5を備えたトラップ準位測定用パターン12と、酸化物半導体層5を備えたTFT素子7と、を同時に形成する製造プロセスの一例を示す図である。

【0178】

先ず、TFT素子7に備えられたゲート電極4Gを形成し(S41)、その後、ゲート絶縁膜8を基板全面に形成する(S42)。

【0179】

そして、トラップ準位測定用パターン12とTFT素子7とに備えられた酸化物半導体層5を、同一層を用いて一つの形成工程で形成する(S43)。

【0180】

それから、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、トラップ準位測定用パターン12に備えられた第1の電極6Aと第2の電極6Bと、を同一層を用いた一つの工程で形成し(S44)、トラップ準位測定用パターン12を完成させる。

【0181】

第1の電極6Aおよび第2の電極6Bと接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン12を用いて、熱刺激電流測定(S45)を行うことができる。

【0182】

トラップ準位測定用パターン12において、酸化物半導体層5は、第1の電極6Aおよび第2の電極6Bと接するように形成されているので、トラップ準位測定用パターン12を用いて、熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極6Aおよび第2の電極6Bとの界面における酸素欠損状態も反映することができる。

【0183】

熱刺激電流測定の結果が良判定であれば、次工程である層間絶縁膜9の形成工程(S46)と画素電極10パターン形成工程(S47)とを行い、TFT素子7を完成させる。

【0184】

一方、熱刺激電流測定の結果が不良判定であれば、酸化物半導体層5の形成工程(S43)において問題があったこととなるので、酸化物半導体層5の形成条件を見直し、新しい基板にS41〜S44の工程を行い、再び、熱刺激電流測定(S45)を行う。

【0185】

このような製造プロセスを用いることにより、TFT素子7を完成させる前にも、TFT素子7に備えられた酸化物半導体層5が正常に形成されているかを把握することができる。

【0186】

また、TFT素子7を完成させる前の中間の段階で、酸化物半導体層5が正常に形成されているかを把握することができるので、TFT素子7を完成させた後に、TFT素子7が不良であると判定された場合には、酸化物半導体層5以外の部分で問題が生じた可能性が高いと推定することができる。

【0187】

したがって、TFT素子7の不良の原因が、酸化物半導体層5に起因して生じているか、TFT素子7に備えられた他の層によって不生じているか、を特定するのが容易になる。

【0188】

また、このような製造プロセスを用いることにより、酸化物半導体層5の蒸着工程において、突発的なトラブルが生じ、膜質に不具合が発生したとしても、酸化物半導体層5におけるトラップ準位の評価を行うことで、迅速に対応ができ、製造プロセスへの早急なフィードバックを行うことができる。

【0189】

したがって、早急なトラブル解消が可能となり、結果、生産効率や歩留りの向上を期待できる。

【0190】

また、このような製造プロセスにおいては、第1の電極6Aおよび第2の電極6Bの各々は、酸化物半導体層5を半導体層として備えたTFT素子7の電極層および配線を形成する導電層と同一材料で形成されているので、新たな材料や工程を追加する必要がなく、製造コストを抑えることが可能となる。

【0191】

〔実施の形態3〕

次に、図14から図17に基づいて、本発明の第3の実施形態について説明する。本実施の形態においては、絶縁基板2上にトラップ準位測定用パターンを形成することは実施の形態1および実施の形態2と同様であるが、トラップ準位測定用パターン13の構造が、実施の形態1で用いたトラップ準位測定用パターン3および実施の形態2で用いたトラップ準位測定用パターン12とは異なる。その他の構成については実施の形態1および実施の形態2において説明したとおりである。説明の便宜上、上記の実施の形態1および実施の形態2の図面に示した部材と同じ機能を有する部材については、同じ符号を付し、その説明を省略する。

【0192】

図14は、絶縁基板2上にトラップ準位測定用パターン13を備えた大型アクティブマトリックス基板1dの一例を示す図である。

【0193】

図示されているように、大型アクティブマトリックス基板1dは分断すると、9個のTFT基板11(図中において点線で表示)を得ることができる。

【0194】

そして、TFT基板11には、表示領域R1と非表示領域R2が備えられており、TFT基板11とは離れた位置である絶縁基板2の端部に存在する端部領域R3には、トラップ準位測定用パターン13が設けられている。

【0195】

図15は、図14に示すトラップ準位測定用パターン13のC−C‘線の断面構造を示すとともに、トラップ準位測定用パターン13を用いて熱刺激電流計測システムを作製する場合を示す図である。

【0196】

図15に図示されているように、トラップ準位測定用パターン13は、酸化物半導体層5上に2個の独立した電極である第1の電極6Aと第2の電極6Bとの両方が備えられており、酸化物半導体層5の下層には、絶縁層8Aを介して第3の電極4Aが備えられた構造を有している。

【0197】

そして、第1の電極6Aと第2の電極6Bとは、同一層で形成されているとともに、本実施の形態においては、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、同一層を用いて一つの形成工程で形成した。

【0198】

また、本実施の形態においては、第3の電極4Aは、TFT素子7に備えられたゲート電極4Gと、同一層を用いて一つの形成工程で形成した。

【0199】

図示されているように、本実施の形態においては、第1の電極6Aに電圧源を接続させ、第2の電極6Bに熱刺激電流計を接続させている。

【0200】

図16は、トラップ準位測定用パターン13を用いて、TFT素子としての電気特性測定を行う場合の一例を示す図である。

【0201】

図示されているように、第3の電極4Aをゲート電極として作用させ、第1の電極6Aと第2の電極6Bとの何れか一方をソース電極として作用させ、他方をドレイン電極として作用させると、トラップ準位測定用パターン13をTFT素子として動作させることができる。

【0202】

したがって、酸化物半導体層5のトラップ準位の評価に用いたトラップ準位測定用パターン13をそのまま用いて、TFT素子としての電気特性の評価も可能となる。

【0203】

図17は、大型アクティブマトリックス基板1d上に、酸化物半導体層5を備えたトラップ準位測定用パターン13と、酸化物半導体層5を備えたTFT素子7と、を同時に形成する製造プロセスの一例を示す図である。

【0204】

先ず、TFT素子7に備えられたゲート電極4Gと、トラップ準位測定用パターン12に備えられた第3の電極4Aと、を同一層を用いて一つの形成工程で形成する(S51)。その後、ゲート絶縁膜8を基板全面に形成する(S52)。

【0205】

そして、トラップ準位測定用パターン13とTFT素子7とに備えられた酸化物半導体層5を、同一層を用いて一つの形成工程で形成する(S53)。

【0206】

それから、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、トラップ準位測定用パターン13に備えられた第1の電極6Aと第2の電極6Bと、を同一層を用いた一つの工程で形成し(S54)、トラップ準位測定用パターン13を完成させる。

【0207】

そして、図15に図示されているように、第1の電極6Aおよび第2の電極6Bと接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン13を用いて熱刺激電流計測システムを作製し、熱刺激電流測定(S55)を行うことができる。

【0208】

トラップ準位測定用パターン13において、酸化物半導体層5は、第1の電極6Aおよび第2の電極6Bと接するように形成されているので、トラップ準位測定用パターン13を用いて、熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極6Aおよび第2の電極6Bとの界面における酸素欠損状態も反映することができる。

【0209】

また、図16に図示されているように、トラップ準位測定用パターン13を用いて、TFT素子としての電気特性測定(S55)を行うことができる。

【0210】

熱刺激電流測定および電気特性測定(S55)の結果が良判定であれば、次工程である層間絶縁膜9の形成工程(S56)と画素電極10パターン形成工程(S57)とを行い、TFT素子7を完成させる。

【0211】

一方、熱刺激電流測定(S55)の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)において問題があったこととなるので、酸化物半導体層5の形成条件を見直し、新しい基板にS51〜S54の工程を行い、再び、熱刺激電流測定および電気特性測定(S55)を行う。

【0212】

また、熱刺激電流測定(S55)の結果が良判定であり、電気特性測定(S55)の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)以外の工程(S51・S52・S54)において問題があったこととなるので、このような工程(S51・S52・S54)の形成条件を見直し、新しい基板にS51〜S54の工程を行い、再び、熱刺激電流測定および電気特性測定(S55)を行う。

【0213】

このような製造プロセスを用いることにより、TFT素子7を完成させる前にも、TFT素子7に備えられた酸化物半導体層5やその他の層が正常に形成されているかを把握することができる。

【0214】

また、TFT素子7を完成させる前の中間の段階で、熱刺激電流測定および電気特性測定(S55)を行うことができ、熱刺激電流測定の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)において問題があったと推定することができ、熱刺激電流測定(S55)の結果が良判定であり、電気特性測定(S55)の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)以外の工程(S51・S52・S54)において問題があったと推定することができるので、TFT素子7の不良の原因の特定が容易になる。

【0215】

また、このような製造プロセスを用いることにより、酸化物半導体層5の蒸着工程において、突発的なトラブルが生じ、膜質に不具合が発生したとしても、酸化物半導体層5におけるトラップ準位の評価を行うことで、迅速に対応ができ、製造プロセスへの早急なフィードバックを行うことができる。

【0216】

したがって、早急なトラブル解消が可能となり、結果、生産効率や歩留りの向上を期待できる。

【0217】

また、このような製造プロセスにおいては、第1の電極6A、第2の電極6Bおよび第3の電極4Aの各々は、酸化物半導体層5を半導体層として備えたTFT素子7の電極層および配線を形成する導電層と同一材料で形成されているので、新たな材料や工程を追加する必要がなく、製造コストを抑えることが可能となる。

【0218】

また、図示は省略するが、実施の形態1および実施の形態2において、既に説明したように、絶縁基板に酸化物半導体層5を備えたトラップ準位測定用パターン13のみを形成し、トラップ準位測定用パターン13を用いて熱刺激電流測定および電気特性測定を行い、酸化物半導体層5やその他の層の形成条件を先に確定した後、この確定された形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、従来の方法で形成することもできる。

【0219】

本発明は上記した各実施の形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施の形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施の形態についても本発明の技術的範囲に含まれる。

【産業上の利用可能性】

【0220】

本発明は、回路基板、アクティブマトリックス基板および表示装置などの分野に好適に用いることができる。

【符号の説明】

【0221】

1 回路基板

1a、1b、1c、1d アクティブマトリックス基板

2 絶縁基板

3 トラップ準位測定用パターン

4 第1の電極

4A 第3の電極

4G ゲート電極

5 酸化物半導体層

6 第2の電極

6A 第1の電極

6B 第2の電極

6S ソース電極

6D ドレイン電極

7 TFT素子

8 ゲート絶縁膜

9 層間絶縁膜

10 画素電極

11 TFT基板

12 トラップ準位測定用パターン

13 トラップ準位測定用パターン

R1 表示領域

R2 非表示領域

R3 端部領域

【技術分野】

【0001】

本発明は、回路基板と、回路基板の製造方法と、上記回路基板を備えたアクティブマトリックス基板および表示装置と、に関するものである。

【背景技術】

【0002】

液晶表示装置(LCD)や有機EL表示装置(OLED)などの分野においては、さらなる高画質化を実現するため、各画素毎にアクティブ素子として、例えば、薄膜トランジスタ素子(以下TFT素子と称する)を設けたアクティブマトリックス型の基板が用いられるのが一般化されている。

【0003】

そして、上記TFT素子に備えられる半導体層の材料としては、水素化アモルファスシリコン層(a−Si:H)やレーザーなどを用いて比較的低温工程で結晶化を行った低温ポリシリコン層(Low Temperature Poly Si;LTPS)が一般的に使用されてきた。

【0004】

しかしながら、水素化アモルファスシリコン層は移動度が小さいという問題があり、低温ポリシリコン層は結晶化の際に起こる局所不均一性の問題があるため、近年では、室温でも高い移動度が得られる、インジウム(In)・ガリウム(Ga)・亜鉛(Zn)を含む酸化物(IGZO)に代表される酸化物半導体が注目されている。

【0005】

このような酸化物半導体をTFT素子の活性層として用いる場合には、酸化物半導体中のキャリア濃度が重要なパラメータとなり、キャリア濃度が大きすぎると酸化物半導体が導体化し、TFT素子としての機能を失ってしまうという問題がある。

【0006】

図18の(a)は、キャリア濃度が適切な酸化物半導体膜を備えた正常TFT素子のI−V特性を示しており、図18の(b)は、キャリア濃度が大きすぎて導体化された酸化物半導体膜を備えた不良TFT素子のI−V特性を示している。

【0007】

酸化物半導体におけるキャリア濃度は、酸素欠損により発生したトラップ準位の影響を大きく受けるため、酸化物半導体のトラップ準位を評価することにより、TFT素子を完全に作り上げる前にも、酸化物半導体のキャリア濃度を把握し、このような酸化物半導体を用いて作製されるTFT素子の良否を予測することができると考えられる。

【0008】

しかしながら、酸化物半導体のトラップ準位の評価方法については、未だ確立されておらず、酸化物半導体を備えたTFT素子を完成させた後に電気特性を測定し、TFT素子の良否判定を行うしかないのが現状であるため、不良発生から不良発見までに大きなタイムラグが生じていた。

【0009】

すなわち、酸化物半導体膜の形成工程において、多数の酸素欠陥が生じ、導体化された酸化物半導体膜が形成されたとしても、酸化物半導体膜の形成工程の直後に、導体化された酸化物半導体膜が形成されたことに気付くことはできず、そのまま、TFT素子を形成する後工程を行い、TFT素子を完成させた後、TFT素子の電気特性を測定し、始めて導体化された酸化物半導体膜が形成されたことに気付くこととなる。

【0010】

このような酸化物半導体膜の評価方法は、後からTFT素子が不良であると判定された場合、材料や時間を無駄に使ったこととなるので、生産単価や生産効率を考慮すると好ましくない方法である。

【0011】

そこで、特許文献1には、非晶質または多結晶性の酸化物半導体層の膜質を非破壊で迅速に調べることのできる検査方法について開示されている。

【0012】

図19の(a)は、特許文献1に記載されている酸化物半導体層の膜質の検査方法を説明するための図であり、図19の(b)は、上記検査方法によって得られたフォトルミネッセンス光のスペクトルを示す図である。

【0013】

特許文献1には、図19の(a)に図示されているように、表面に検査しようとする非晶質又は多結晶性の被検査酸化物半導体層が形成された基板110に対して、レーザー光源などの励起光源101から出射された励起光102を照射し、被検査酸化物半導体層から反射される反射光103のうち、バンドギャップエネルギーに対応する波長よりも長い波長領域のフォトルミネッセンス光104の強度を光検出器105で測定し、図19の(b)に図示されているようなデータを得て、図示されてない計測機器に送る構成が開示されている。

【0014】

上記構成においては、上記被検査酸化物半導体層に対して、測定を行う前に、上記被検査酸化物半導体層と同じ工程で作製され、上記被検査酸化物半導体層と同じ元素組成と膜厚とを有する、非晶質又は多結晶性の参照用酸化物半導体層に対し、同じフォトルミネッセンス光強度の測定と、膜質の測定とを行い、フォトルミネッセンス光強度と膜質との関係を得て、この関係に基づいて上記被検査酸化物半導体層の膜質を推定することができる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2010−123872号(2010年6月3日公開)

【発明の概要】

【発明が解決しようとする課題】

【0016】

しかしながら、上記特許文献1に記載されている酸化物半導体層の膜質の検査方法は、単層で形成された酸化物半導体層の評価には有効であるが、実際のTFT素子の活性層として用いられた酸化物半導体層の状態を十分に反映できないという問題がある。

【0017】

すなわち、実際のTFT素子の活性層として用いられた酸化物半導体層の上層には、金属膜からなるソース電極およびドレイン電極や絶縁膜が形成され、これらの膜と上記酸化物半導体層との界面にも酸素欠損が生じ、このように界面で生じた酸素欠損が酸化物半導体層の特性に及ぼす影響も大きいことが知られているが、図19の(a)に図示されている上記特許文献1に記載の酸化物半導体層の膜質の検査方法においては、このように界面で生じる酸素欠損を反映することができず、この検査方法によるTFT素子の良否の予測は精度が低いため、有効に用いることができない。

【0018】

本発明は、上記の問題点に鑑みてなされたものであり、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板と、アクティブマトリックス基板と、表示装置と、上記回路基板の製造方法と、を提供することを目的とする。

【課題を解決するための手段】

【0019】

本発明の回路基板は、上記の課題を解決するために、絶縁基板の一方側の面に、酸化物半導体層が備えられている回路基板であって、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、上記第1の電極とは電気的に分離されている第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられていることを特徴としている。

【0020】

上記構成によれば、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、第2の電極と、上記第1の電極および上記第2の電極と接するように形成された酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられている。

【0021】

上記酸化物半導体層は、上記第1の電極および上記第2の電極と接するように形成されているので、上記トラップ準位測定用パターンを用いて、例えば、熱刺激電流測定を行えば、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0022】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板を実現することができる。

【0023】

本発明の回路基板は、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、上記絶縁基板の中心部を含む領域である第1の領域と、上記第1の領域の周辺領域であるとともに、上記絶縁基板の端部を含む領域である第2の領域と、が備えられており、上記第2の領域に、上記トラップ準位測定用パターンが設けられていることが好ましい。

【0024】

上記構成によれば、第1の電極と、第2の電極と、酸化物半導体層と、を備えたトラップ準位測定用パターンが、上記第1の領域の周辺領域であるとともに、上記絶縁基板の端部を含む領域である第2の領域に設けられているので、上記トラップ準位測定用パターンを見えなくする必要がある場合などに、第2の領域のみを覆うように遮光部材を設ければよいので、表示装置などに容易に用いることができる回路基板を実現することができる。

【0025】

また、必要に応じて、上記トラップ準位測定用パターンを除去する場合においても容易である。

【0026】

本発明の回路基板の上記トラップ準位測定用パターンにおいて、上記酸化物半導体層は、上記第1の電極と上記第2の電極との間に、介在されていることが好ましい。

【0027】

上記構成によれば、上記酸化物半導体層が上記第1の電極および上記第2の電極との間に介在されている上記トラップ準位測定用パターンを用いて、例えば、熱刺激電流測定を行えば、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0028】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板を実現することができる。

【0029】

本発明の回路基板の上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されていることが好ましい。

【0030】

上記構成によれば、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されている上記トラップ準位測定用パターンを用いて、例えば、熱刺激電流測定を行えば、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0031】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板を実現することができる。

【0032】

また、上記構成によれば、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方側に形成されているため、上記第1の電極と上記第2の電極との形成工程を一つの工程で行うことができる。

【0033】

したがって、上記トラップ準位測定用パターンの形成工程を短縮することができる。

【0034】

本発明の回路基板の上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されていることが好ましい。

【0035】

上記構成によれば、上記第1の電極と上記第2の電極とを用いて行うことができる熱刺激電流測定のみならず、上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層を備えたトラジスタ素子の特性を評価することができる。

【0036】

したがって、上記酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測をさらに精度高く行うことができる回路基板を実現することができる。

【0037】

本発明の回路基板における上記第1の電極および上記第2の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0038】

上記構成によれば、上記トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極は、別途の新たな導電性材料で形成する必要はなく、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0039】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極と、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成するある一つの導電層と、を同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0040】

本発明の回路基板において、上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0041】

上記構成によれば、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極は、別途の新たな導電性材料で形成する必要はなく、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0042】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極の各々を、上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層の形成工程と、同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0043】

本発明の回路基板において、上記酸化物半導体層は、In、Ga、Znから選択される少なくとも一つの元素を含むことが好ましい。

【0044】

上記構成によれば、室温でも高い移動度を有する酸化物半導体層を備えた回路基板を実現することができる。

【0045】

本発明のアクティブマトリックス基板は、上記の課題を解決するために、上記回路基板を備え、上記回路基板上には、上記酸化物半導体層と同一層によって形成された半導体層を備えた複数のアクティブ素子が設けられており、上記アクティブ素子の各々には、画素電極が電気的に接続されており、複数の上記画素電極がマトリックス状に形成されていることを特徴としている。

【0046】

上記構成によれば、室温でも高い移動度を有する酸化物半導体層を備えたアクティブ素子と、上記アクティブ素子の各々に電気的に接続された画素電極がマトリックス状に形成されているアクティブマトリックス基板を実現することができる。

【0047】

本発明のアクティブマトリックス基板の上記トラップ準位測定用パターンにおいて、上記第1の電極および上記第2の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0048】

上記構成によれば、トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極は、別途の新たな導電性材料で形成する必要はなく、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0049】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極および上記第2の電極と、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成するある一つの導電層と、を同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0050】

本発明のアクティブマトリックス基板の上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることが好ましい。

【0051】

上記構成によれば、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極は、別途の新たな導電性材料で形成する必要はなく、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されている。

【0052】

したがって、必要に応じて、上記トラップ準位測定用パターンにおける上記第1の電極、上記第2の電極および上記第3の電極の各々を、上記画素電極を含む上記酸化物半導体層を備えたアクティブ素子の電極層および配線を形成する導電層の形成工程と、同一工程で形成することができるので、上記回路基板の製造工数を短縮することができる。

【0053】

本発明の表示装置は、上記の課題を解決するために、上記アクティブマトリックス基板と、対向基板と、上記アクティブマトリックス基板と上記対向基板との間に介在された液晶層と、を備えていることを特徴としている。

【0054】

上記構成によれば、その製造工程において、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる液晶表示装置を実現することができる。

【0055】

本発明の表示装置は、上記の課題を解決するために、上記アクティブマトリックス基板と、上記アクティブマトリックス基板における上記画素電極が形成されている面側に形成された有機EL層と、を備えていることを特徴としている。

【0056】

上記構成によれば、その製造工程において、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる有機EL表示装置を実現することができる。

【0057】

本発明の回路基板の製造方法は、上記の課題を解決するために、絶縁基板の一方側の面に、酸化物半導体層が備えられた回路基板の製造方法であって、上記絶縁基板において上記酸化物半導体層が形成されている側の面に、第1の電極と、上記第1の電極とは電気的に分離された第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンを形成する工程と、熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程と、が含まれていることを特徴としている。

【0058】

上記製造方法によれば、第1の電極と、第2の電極と、上記第1の電極および上記第2の電極と接するように形成された酸化物半導体層と、を備えたトラップ準位測定用パターンを用いて、熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程が含まれている。

【0059】

上記酸化物半導体層は、上記第1の電極および上記第2の電極と接するように形成されているので、上記酸化物半導体層のトラップ準位の測定においては、上記酸化物半導体層中の酸素欠損状態のみでなく、上記酸化物半導体層と上記第1の電極および上記第2の電極との界面における酸素欠損状態も反映することができる。

【0060】

したがって、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板の製造方法を実現することができる。

【0061】

本発明の回路基板の製造方法において、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層のトラジスタ素子特性を評価する工程が含まれていることが好ましい。

【0062】

上記製造方法によれば、上記第1の電極と上記第2の電極とを用いて、熱刺激電流測定を行う工程のみならず、上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層のトラジスタ素子としての特性を評価する工程も含まれている。

【0063】

したがって、さらに精度高く酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を行うことができる回路基板の製造方法を実現することができる。

【発明の効果】

【0064】

本発明の回路基板は、以上のように、上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、上記第1の電極とは電気的に分離されている第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられている構成である。

【0065】

また、本発明のアクティブマトリックス基板は、以上のように、上記回路基板を備え、上記回路基板上には、上記酸化物半導体層と同一層によって形成された半導体層を備えた複数のアクティブ素子が設けられており、上記アクティブ素子の各々には、画素電極が電気的に接続されており、複数の上記画素電極がマトリックス状に形成されている構成である。

【0066】

また、本発明の表示装置は、以上のように、上記アクティブマトリックス基板と、対向基板と、上記アクティブマトリックス基板と上記対向基板との間に介在された液晶層と、を備えている構成である。

【0067】

また、本発明の表示装置は、以上のように、上記アクティブマトリックス基板と、上記アクティブマトリックス基板における上記画素電極が形成されている面側に形成された有機EL層と、を備えている構成である。

【0068】

また、本発明の回路基板の製造方法は、以上のように、上記絶縁基板において上記酸化物半導体層が形成されている側の面に、第1の電極と、上記第1の電極とは電気的に分離された第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンを形成する工程と、熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程と、が含まれている方法である。

【0069】

それゆえ、酸化物半導体層を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板と、アクティブマトリックス基板と、表示装置と、上記回路基板の製造方法と、を実現することができる。

【図面の簡単な説明】

【0070】

【図1】本発明の一実施の形態の回路基板に備えられたトラップ準位測定用パターンの断面構造を示すとともに、トラップ準位測定用パターンを用いて熱刺激電流計測システムを作製する場合を示す図である。

【図2】本発明の一実施の形態の回路基板の概略構成を示す図である。

【図3】本発明の一実施の形態の回路基板である大型アクティブマトリックス基板の一例を示す図である。

【図4】本発明の一実施の形態の回路基板である大型アクティブマトリックス基板のさらに他の一例を示す図である。

【図5】トラップ準位測定用パターンを用いて熱刺激電流測定を行う方法を説明するための図であり、(a)は、トラップ電圧の印加により、発生させた電子・正孔を酸化物半導体層5におけるトラップ準位に捕獲、凍結させた状態を示し、(b)は、昇温による熱的効果により、浅いトラップ準位から順に電子・正孔が解放される状態を示す。

【図6】トラップ準位測定用パターンに備えられた酸化物半導体層の正常膜および不良膜の熱刺激電流測定結果を示す図である。

【図7】従来から用いられている酸化物半導体層を備えたTFT素子が形成されたアクティブマトリックス基板の製造プロセスを示す図である。

【図8】本発明の一実施の形態の回路基板である大型アクティブマトリックス基板上に、酸化物半導体層を備えたトラップ準位測定用パターンと、酸化物半導体層を備えたTFT素子と、を形成する製造プロセスの一例を示す図である。

【図9】本発明の一実施の形態の回路基板である絶縁基板に酸化物半導体層を備えたトラップ準位測定用パターンを形成し、酸化物半導体層の形成条件を先に確定した後、この確定された酸化物半導体層の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層を備えたTFT素子を、従来の方法で形成する製造プロセスの一例を示す図である。

【図10】本発明の他の一実施の形態の回路基板である大型アクティブマトリックス基板の一例を示す図である。

【図11】本発明の他の一実施の形態の回路基板である大型アクティブマトリックス基板に備えられたトラップ準位測定用パターンの断面構造を示すとともに、トラップ準位測定用パターンを用いて熱刺激電流計測システムを作製する場合を示す図である。

【図12】本発明の他の一実施の形態の回路基板である絶縁基板に酸化物半導体層を備えたトラップ準位測定用パターンを形成し、酸化物半導体層の形成条件を先に確定した後、この確定された酸化物半導体層の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層を備えたTFT素子を、従来の方法で形成する製造プロセスの一例を示す図である。

【図13】本発明の他の一実施の形態の回路基板である大型アクティブマトリックス基板上に、酸化物半導体層を備えたトラップ準位測定用パターンと、酸化物半導体層を備えたTFT素子と、を形成する製造プロセスの一例を示す図である。

【図14】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板の一例を示す図である。

【図15】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板に備えられたトラップ準位測定用パターンの断面構造を示すとともに、トラップ準位測定用パターンを用いて熱刺激電流計測システムを作製する場合を示す図である。

【図16】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板に備えられたトラップ準位測定用パターンを用いて、TFT素子としての電気特性測定を行う場合の一例を示す図である。

【図17】本発明のさらに他の一実施の形態の回路基板である大型アクティブマトリックス基板上に、酸化物半導体層を備えたトラップ準位測定用パターンと、酸化物半導体層を備えたTFT素子と、を形成する製造プロセスの一例を示す図である。

【図18】TFT素子の電気特性測定の結果を示す図であり、(a)は、キャリア濃度が適切な酸化物半導体膜を備えた正常TFT素子のI−V特性を示し、(b)は、キャリア濃度が大きすぎて導体化された酸化物半導体膜を備えた不良TFT素子のI−V特性を示している。

【図19】特許文献1に記載されている酸化物半導体層の膜質の検査方法および上記検査方法によって得られたフォトルミネッセンス光のスペクトルを示す図である。

【発明を実施するための形態】

【0071】

以下、図面に基づいて本発明の実施の形態について詳しく説明する。ただし、この実施の形態に記載されている構成部品の寸法、材質、形状、その相対配置などはあくまで一実施形態に過ぎず、これらによってこの発明の範囲が限定解釈されるべきではない。

【0072】

〔実施の形態1〕

以下、図1から図9に基づいて、本発明の第1の実施形態について説明する。

【0073】

図2は、絶縁基板2上の任意の箇所に、トラップ準位測定用パターン3が設けられている回路基板1の概略構成を示す図である。

【0074】

回路基板1は、トラップ準位測定用パターン3と、トラップ準位測定用パターン3に備えられた酸化物半導体層5と同一層によって形成された酸化物半導体層と、を備えた半導体基板や表示装置に用いられるアクティブマトリックス基板などであることができる。

【0075】

なお、図示されているように、絶縁基板2には、絶縁基板2の中心部を含む領域である第1の領域R1と、第1の領域R1の周辺領域であるとともに、絶縁基板2の端部を含む領域である第2の領域R2と、が備えられており、トラップ準位測定用パターン3は、第2の領域R2に設けられていることが好ましい。

【0076】

そして、トラップ準位測定用パターン3に備えられた酸化物半導体層5と同一層によって形成された酸化物半導体層は、絶縁基板2の中心部を含む領域である第1の領域R1に形成されることになる。

【0077】

このような構成によれば、トラップ準位測定用パターン3が、絶縁基板2の端部を含む領域である第2の領域R2に設けられているので、トラップ準位測定用パターン3を見えなくする必要がある場合などに、第2の領域R2のみを覆うように遮光部材を設ければよいので、表示装置などに容易に用いることができる回路基板1を実現することができる。

【0078】

図1は、図2に示すトラップ準位測定用パターン3のA−A‘線の断面構造を示すとともに、トラップ準位測定用パターン3を用いて詳しくは後述する熱刺激電流計測システムを作製する場合を示す図である。

【0079】

図示されているように、トラップ準位測定用パターン3は、絶縁基板2上に第1の電極4を形成する第一の導電膜と、酸化物半導体層5と、第2の電極6を形成する第二の導電膜と、が順に積層された構造となっており、酸化物半導体層5が第1の電極4と第2の電極6との間に介在された構造となっている。

【0080】

トラップ準位測定用パターンの構造はこれに限定されることはなく、酸化物半導体層5が、第1の電極4および第2の電極6と接するように形成されていれば、例えば、後述する実施の形態2および実施の形態3に記載されているような構造であってもよい。

【0081】

このような構成によれば、絶縁基板2において酸化物半導体層5が形成されている側の面には、第1の電極4と、第2の電極6と、第1の電極4および第2の電極6と接するように形成された酸化物半導体層5と、を備えたトラップ準位測定用パターン3が設けられている。

【0082】

酸化物半導体層5は、第1の電極4および第2の電極6と接するように形成されているので、トラップ準位測定用パターン3を用いて、後述する熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極4および第2の電極6との界面における酸素欠損状態も反映することができる。

【0083】

したがって、酸化物半導体層5を備えたTFT素子などのアクティブ素子の良否の予測を精度高く行うことができる回路基板1を実現することができる。

【0084】

なお、酸化物半導体層5としては、In、Ga、Znから選択される少なくとも一つの元素を含む酸化物を用いることができ、本実施の形態においては、In、GaおよびZnを全て含むIGZO系酸化物半導体層を用いているが、これに限定されることはなく、例えば、Zn−O系酸化物、In−Si−Zn−O系酸化物、In−Al−Zn−O系酸化物、In−Mg−Zn−O系酸化物などを半導体層として用いることもできる。

【0085】

また、酸化物半導体層5の結晶の状態は、特に限定されず、例えば、非結晶半導体層や多結晶半導体層や連続粒界結晶半導体層であることができる。

【0086】

第1の電極4を形成する第一の導電膜および第2の電極6を形成する第二の導電膜の材質としては、導電性がある材料であれば良いが、その一例としてタンタル(Ta)、モリブデン(Mo)、チタン(Ti)、銅(Cu)、アルミニウム(Al)、等があげられる。これらの材料は低抵抗であるため、熱刺激電流計測の際に微小な電流であっても正確に計測することができる。

【0087】

また、第1の電極4を形成する第一の導電膜および第2の電極6を形成する第二の導電膜の材質としては、上記導電性がある材料の積層膜を用いることもできる。

【0088】

なお、図2に図示されているように、絶縁基板2の中心部を含む領域である第1の領域R1には、トラップ準位測定用パターン3に備えられた酸化物半導体層5と同一層によって形成された酸化物半導体層を備えたアクティブ素子であるトラジスタ素子(以下TFT素子と称する)などが形成されるが、例えば、上記TFT素子がトップゲート型で形成される場合には、第2の電極6をゲート配線材料で形成し、第1の電極4をソース・ドレイン配線材料で形成し、ゲート配線材料やソース・ドレイン配線材料のパターン形成時に同時に第2の電極6や第1の電極4をパターンニングすればよい。

【0089】

一方、上記TFT素子がボトムゲート型で形成される場合には、第1の電極4をゲート配線材料で形成し、第2の電極6をソース・ドレイン配線材料で形成し、ゲート配線材料やソース・ドレイン配線材料のパターン形成時に同時に第1の電極4や第2の電極6をパターンニングすればよい。

【0090】

このようにすれば、新たな材料を使用したり工程数を増やしたりすることなく、トラップ準位測定用パターン3を形成できる。

【0091】

また、第2の電極6を上記TFT素子に接続された画素電極の形成層で形成することもできる。画素電極が反射型の画素電極である場合、アルミニウム(Al)等で形成されるため、好適に用いることができる。

【0092】

また、トラップ準位測定用パターン3は、図2に図示されている第1の領域R1に形成される上記TFT素子と電気的に接続されている配線パターンとリークすると誤動作を引き起こすため、図2に図示されているように、第2の領域R2に浮島構造で形成する必要がある。

【0093】

また、詳しくは後述するが、トラップ準位測定用パターン3は、図2に図示されている第1の領域R1に上記TFT素子を形成する工程より先に形成することもできる。

【0094】

なお、トラップ準位測定用パターン3における酸化物半導体層5の膜厚は特に限定されないが、図2に図示されている第1の領域R1に形成されるTFT素子に備えられる酸化物半導体層の膜厚と同じであってもよく、例えば、50nm程度であればよい。

【0095】

また、トラップ準位測定用パターン3を用いて熱刺激電流計測を行うためには、トラップ準位測定用パターン3における第1の電極4と第2の電極6との何れか一方に電圧源を接続させ、他方に熱刺激電流計を接続させればよく、本実施の形態においては、図1に図示されているように、第1の電極4に電圧源を接続させ、第2の電極6に熱刺激電流計を接続させている。

【0096】

そして、第1の電極4と第2の電極6とには、熱刺激電流計測の際に電圧を印加するために、導電性ワイヤーを接続する必要があるので、第1の電極4と第2の電極6とは5mm×1mm程度以上の大きさで形成されることが好ましい。

【0097】

また、図1に図示されているように、第1の電極4の表面は、5mm×1mm程度以上の大きさが露出されるように、酸化物半導体層5と第2の電極6とが形成されることが好ましい。

【0098】

第1の電極4と第2の電極6との膜厚は特に限定されないが、図2に図示されている第1の領域R1に形成されるTFT素子のゲート電極やソース・ドレイン電極や配線の膜厚と同一に形成してもよく、例えば、400nm程度で形成することができる。

【0099】

以上のように形成したトラップ準位測定用パターン3を用いて、熱刺激電流測定を実施することができるが、この測定には2〜3時間程度の時間を要するため、抜き取りで行うことが好ましい。

【0100】

また、トラップ準位測定用パターン3および図2に図示されている第1の領域R1に形成されるTFT素子に備えられる酸化物半導体層5の形成に用いられる膜蒸着装置のメンテナンス後などに、トラップ準位測定用パターン3を用いて、熱刺激電流測定を実施し、酸化物半導体層5の膜質評価を行うと、メンテナンスによる膜質変化を早期に発見できる。

【0101】

また、熱刺激電流測定において、トラップ準位によって生じる熱刺激電流が大きく観測されると、このような酸化物半導体層を備えたTFT素子は不良となるため、酸化物半導体層の蒸着時に酸素分圧を上げて酸素欠損の発生を抑えるなどの対策を迅速に実施することができる。

【0102】

トラップ準位測定用パターン3を用いることによって、TFT素子を完成する前にも、熱刺激電流測定を実施できるため、不良品を流出させることなく迅速に酸化物半導体層の不具合に対応することができる。

【0103】

以下、図3および図4に基づいて、回路基板がトラップ準位測定用パターン3を備えた大型アクティブマトリックス基板である場合について説明する。

【0104】

図3は、絶縁基板2上にトラップ準位測定用パターン3を備えた大型アクティブマトリックス基板1aの一例を示す図である。

【0105】

図示されているように、大型アクティブマトリックス基板1aは分断すると、9個のTFT基板11(図中において点線で表示)を得ることができる。

【0106】

そして、TFT基板11には、表示領域R1と非表示領域R2が備えられており、TFT基板11とは離れた位置である絶縁基板2の端部に存在する端部領域R3には、トラップ準位測定用パターン3が設けられている。

【0107】

トラップ準位測定用パターン3をこのような位置に配置することにより、大型アクティブマトリックス基板1aを分断する際に、不要となったトラップ準位測定用パターン3を取り除くことができる。

【0108】

TFT基板11の表示領域R1には、各画素毎に画素電極10を備えた画素TFT素子7が設けられている。

【0109】

画素TFT素子7は、トラップ準位測定用パターン3の第1の電極4と同一層によって形成されたゲート電極4Gと、ゲート絶縁膜8と、トラップ準位測定用パターン3の酸化物半導体層5と同一層によって形成された酸化物半導体層5と、トラップ準位測定用パターン3の第2の電極6と同一層によって形成されたソース・ドレイン電極6S・6Dと、を備えた構成となっている。

【0110】

そして、ドレイン電極6Dは、層間絶縁膜9に形成されたコンタクトホールを介して、画素電極10と電気的に接続されている。

【0111】

図4は、大型アクティブマトリックス基板において、トラップ準位測定用パターン3を設ける位置や数を変えた一例を示す図である。

【0112】

図3に図示されているように、大型アクティブマトリックス基板において、トラップ準位測定用パターン3を設ける位置や数は、絶縁基板2の端部に存在する端部領域R3や一つに限定されることはなく、例えば、図4に図示されているように、トラップ準位測定用パターン3をTFT基板11の非表示領域R2毎に設けることもできる。

【0113】

図4に図示されているように、トラップ準位測定用パターン3を配置することにより、大型アクティブマトリックス基板1bに酸化物半導体層5を形成する際に、形成位置毎にバラツキが生じたとしでも、各TFT基板11に設けられたトラップ準位測定用パターン3を用いて、熱刺激電流測定を行うことができるので、酸化物半導体層5を備えたTFT素子の良否の予測を精度高く行うことができる。

【0114】

また、大型アクティブマトリックス基板1bをTFT基板11に分断した後にも、各TFT基板11には、トラップ準位測定用パターン3が残るので、大型アクティブマトリックス基板1bの分断工程後に、必要に応じて、トラップ準位測定用パターン3を用いて測定を行うことができる。

【0115】

以下、図5および図6に基づいて、熱刺激電流測定を行う方法について詳しく説明する。

【0116】

先ず、図2、図3および図4に図示した回路基板1やアクティブマトリックス基板1a・1bを試料とし、上記試料における少なくともトラップ準位測定用パターン3を液体窒素を用いて冷却する。

【0117】

また、上記液体窒素を用いた冷却においては、トラップ準位測定用パターン3のみを冷却してもよいし、これが困難である場合には、回路基板1やアクティブマトリックス基板1a・1b全体を冷却してもよい。

【0118】

図5(a)は、トラップ電圧の印加により、発生させた電子・正孔を酸化物半導体層5におけるトラップ準位に捕獲、凍結させた状態を示す図であり、図5(b)は、昇温による熱的効果により、浅いトラップ準位から順に電子・正孔が解放される状態を示す図である。

【0119】

トラップ準位測定用パターン3を液体窒素領域まで冷却後に、第1の電極4にトラップ電圧を印加し、電子・正孔を発生させ、図5(a)に図示されているように、酸化物半導体層5におけるトラップ準位に電子・正孔を捕獲、凍結させる(図1参照)。

【0120】

なお、電子・正孔は、光照射により発生させることもできる。

【0121】

次に、トラップ準位測定用パターン3を一定速度で昇温すると、熱的効果により、図5(b)に図示されているように、浅いトラップ準位から順に電子・正孔が解放される。

【0122】

これらの解放は熱刺激電流として、第2の電極6を介して観測される。このようにして観測した熱刺激電流値を解析することにより、酸化物半導体層5におけるバンドギャップ中のトラップ準位に関する情報を得ることができる。

【0123】

酸化物半導体層5においては、トラップ準位は酸素欠損に大きく依存して発生されることから、熱刺激電流値を解析することで、トラップ準位および酸素欠損についての情報を得ることができる。

【0124】

なお、本実施の形態において用いた熱刺激電流測定の測定条件は、以下の通りである。

【0125】

測定雰囲気は、不活性気体であるHe下(封じ切り)で行っており、昇温速度は10℃/minに、測定温度範囲は−180℃〜350℃に、トラップ電圧は30Vに、光は520nm波長の光を基準に100μW/cm2となるような強度とし、2分間照射されるようにそれぞれの条件を設定した。

【0126】

なお、本実施の形態においては、電子・正孔を発生させる方法として、トラップ電圧の印加と光照射の両方を用いている。

【0127】

上記測定条件は、一例であり、必要に応じて測定条件は適宜変えることができる。

【0128】

図6は、酸化物半導体層5の正常膜および不良膜の熱刺激電流測定結果を示す図である。

【0129】

図6(a)は、正常な酸化物半導体層5の熱刺激電流測定結果を示しており、図6(b)は、トラップ準位が存在する不良な酸化物半導体層5の熱刺激電流測定結果を示している。

【0130】

図6(a)に図示されているように、正常な酸化物半導体層5においては、−200℃〜100℃の範囲内では電流値のピークは見られないが、図6(b)に図示されているように、トラップ準位が存在する不良な酸化物半導体層5においては、0℃付近にトラップ準位の存在を示す電流値のピークが確認される。

【0131】

熱刺激電流値がピークを示す温度Tと、トラップ準位の深さEには、下記式1で示す関係がある。

【0132】

E=kT・ln(T4/β) (式1)

上記式1において、kはボルツマン定数であり、βは昇温速度であり、Tは絶対温度である。

【0133】

上記式1から、0℃付近にピークを有する熱刺激電流値は、0.57eVの深さにトラップ準位が存在することを意味している。

【0134】

以上のように、熱刺激電流測定によって酸化物半導体層5の膜質に大きな影響を及ぼすトラップ準位の評価を行うことができる。

【0135】

以下、図7から図9に基づいて、大型アクティブマトリックス基板1a・1b上に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスについて説明する。

【0136】

図7は、従来から用いられている酸化物半導体層を備えたTFT素子が形成されたアクティブマトリックス基板の製造プロセスを示す。

【0137】

図示されているように、この従来の製造プロセスにおいては、S101〜S106までの工程を経て、画素電極を有するTFT素子を完成させた後に、この完成されたTFT素子の電気的特性の測定(S107)を行い、良不判定を行っているため、酸化物半導体層に起因して不良が生じているか、TFT素子に備えられた他の層によって不良が生じているか、を特定することが困難であった。

【0138】

また、TFT素子を完成させた後に、電気的特性の測定(S107)を行った結果が不良であり、その原因を解析した後に、上記TFT素子に備えられた各層の成膜工程などに問題があったことを気付くことになるので、材料や時間を無駄に使ったこととなり、生産単価や生産効率を考慮すると好ましくない製造プロセスである。

【0139】

なお、以下に説明する図8に示す製造プロセスは、同一基板内に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスの一例であり、図9に示す製造プロセスは、異なる2つの基板に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、のそれぞれを形成する製造プロセスの一例を示す。

【0140】

図8は、大型アクティブマトリックス基板1a・1b上に、酸化物半導体層5を備えたトラップ準位測定用パターン3と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスの一例を示す図である。

【0141】

先ず、トラップ準位測定用パターン3に備えられた第1の電極4と、TFT素子7に備えられたゲート電極4Gとを、同一層を用いて一つの形成工程で形成する(S11)。

【0142】

そして、トラップ準位測定用パターン3が形成されている領域以外にゲート絶縁膜8を形成する(S12)。

【0143】

それから、トラップ準位測定用パターン3とTFT素子7とに備えられた酸化物半導体層5を、同一層を用いて一つの形成工程で形成する(S13)。

【0144】

そして、トラップ準位測定用パターン3に備えられた第2の電極6と、TFT素子7に備えられたソース・ドレイン電極6S・6Dとを、同一層を用いて一つの形成工程で形成する(S14)。

【0145】

第1の電極4および第2の電極6と接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン3を用いて、熱刺激電流測定(S15)を行うことができる。

【0146】

熱刺激電流測定の結果が良判定であれば、次工程である層間絶縁膜9の形成工程(S16)と画素電極10パターン形成工程(S17)とを行い、TFT素子7を完成させる。

【0147】

一方、熱刺激電流測定の結果が不良判定であれば、酸化物半導体層5の形成工程(S13)において問題があったこととなるので、酸化物半導体層5の形成条件を見直し、新しい基板にS11〜S14の工程を行い、再び、熱刺激電流測定(S15)を行う。

【0148】

このような製造プロセスを用いることにより、TFT素子7を完成させる前にも、TFT素子7に備えられた酸化物半導体層5が正常に形成されているかを精度高く把握することができる。

【0149】

また、TFT素子7を完成させる前の中間の段階で、酸化物半導体層5が正常に形成されているかを把握することができるので、TFT素子7を完成させた後に、TFT素子7が不良であると判定された場合には、酸化物半導体層5以外の部分で問題が生じた可能性が高いと推定することができる。

【0150】

したがって、TFT素子7の不良の原因が、酸化物半導体層5に起因して生じているか、TFT素子7に備えられた他の層によって不生じているか、を特定するのが容易になる。

【0151】

また、このような製造プロセスを用いることにより、酸化物半導体層5の蒸着工程において、突発的なトラブルが生じ、膜質に不具合が発生したとしても、酸化物半導体層5におけるトラップ準位の評価を行うことで、迅速に対応ができ、製造プロセスへの早急なフィードバックを行うことができる。

【0152】

したがって、早急なトラブル解消が可能となり、結果、生産効率や歩留りの向上を期待できる。

【0153】

また、このような製造プロセスにおいては、第1の電極4および第2の電極6の各々は、酸化物半導体層5を半導体層として備えたTFT素子7の電極層および配線を形成する導電層と同一材料で形成されているので、新たな材料や工程を追加する必要がなく、製造コストを抑えることが可能となる。

【0154】

図9は、絶縁基板に酸化物半導体層5を備えたトラップ準位測定用パターン3を形成し、酸化物半導体層5の形成条件を先に確定した後、この確定された酸化物半導体層5の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、従来の方法で形成する製造プロセスの一例を示す図である。

【0155】

図示されているように、先ず、絶縁基板上に、第1の電極4を形成し(S21)、その後、酸化物半導体層5を形成し(S22)、最後に第2の電極6を形成し(S23)、トラップ準位測定用パターン3を完成させ、第1の電極4および第2の電極6と接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン3を用いて、熱刺激電流測定(S24)を行う。

【0156】

この熱刺激電流測定(S24)の結果が良判定であれば、酸化物半導体層5を形成する工程(S22)で用いた条件をそのまま用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、S101〜S106の工程で構成される従来の方法で形成する。

【0157】

一方、熱刺激電流測定(S24)の結果が不良判定であれば、酸化物半導体層5を形成する工程(S22)で用いた条件を見直し、再び、新たな絶縁基板にS21〜S23の工程を行い、トラップ準位測定用パターン3を完成させ、このトラップ準位測定用パターン3を用いて、熱刺激電流測定(S24)を行う。

【0158】

このような製造プロセスを用いることにより、酸化物半導体層5の形成条件を、比較的に容易に形成することができるとともに、精度高く酸化物半導体層5のトラップ準位を把握することができるトラップ準位測定用パターン3を用いて、確定することができる。

【0159】

なお、TFT基板11は、液晶表示装置や有機EL表示装置などの各種表示装置用に好適に用いることができる。

【0160】

〔実施の形態2〕

次に、図10から図13に基づいて、本発明の第2の実施形態について説明する。本実施の形態においては、絶縁基板2上にトラップ準位測定用パターンを形成することは実施の形態1と同様であるが、トラップ準位測定用パターン12の構造が、実施の形態1で用いたトラップ準位測定用パターン3とは異なる。その他の構成については実施の形態1において説明したとおりである。説明の便宜上、上記の実施の形態1の図面に示した部材と同じ機能を有する部材については、同じ符号を付し、その説明を省略する。

【0161】

図10は、絶縁基板2上にトラップ準位測定用パターン12を備えた大型アクティブマトリックス基板1cの一例を示す図である。

【0162】

図示されているように、大型アクティブマトリックス基板1cは分断すると、9個のTFT基板11(図中において点線で表示)を得ることができる。

【0163】

そして、TFT基板11には、表示領域R1と非表示領域R2が備えられており、TFT基板11とは離れた位置である絶縁基板2の端部に存在する端部領域R3には、トラップ準位測定用パターン12が設けられている。

【0164】

トラップ準位測定用パターン12は、酸化物半導体層5上に2個の独立した電極である第1の電極6Aと第2の電極6Bとの両方が形成された構造を有する。

【0165】

そして、第1の電極6Aと第2の電極6Bとは、同一層で形成されているとともに、本実施の形態においては、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、同一層を用いて一つの形成工程で形成した。

【0166】

図11は、図10に示すトラップ準位測定用パターン12のB−B‘線の断面構造を示すとともに、トラップ準位測定用パターン12を用いて熱刺激電流計測システムを作製する場合を示す図である。

【0167】

図示されているように、本実施の形態においては、第1の電極6Aに電圧源を接続させ、第2の電極6Bに熱刺激電流計を接続させている。

【0168】

そして、第1の電極6Aと第2の電極6Bとには、熱刺激電流計測の際に電圧を印加するために、導電性ワイヤーを接続する必要があるので、第1の電極6Aと第2の電極6Bとは5mm×1mm程度以上の大きさで形成されることが好ましい。

【0169】

また、第1の電極6Aと第2の電極6Bとの間の距離は特に限定されないが、一例として1mm程度で形成することができる。

【0170】

また、第1の電極6Aと第2の電極6Bとは、TFT素子7に接続された画素電極10の形成層で形成することもできる。画素電極10が反射型の画素電極である場合、アルミニウム(Al)等で形成されるため、好適に用いることができる。

【0171】

なお、以下に説明する図12に示す製造プロセスは、異なる2つの基板に、酸化物半導体層5を備えたトラップ準位測定用パターン12と、酸化物半導体層5を備えたTFT素子7と、のそれぞれを形成する製造プロセスの一例を示し、図13に示す製造プロセスは、同一基板内に、酸化物半導体層5を備えたトラップ準位測定用パターン12と、酸化物半導体層5を備えたTFT素子7と、を形成する製造プロセスの一例を示す。

【0172】

図12は、絶縁基板に酸化物半導体層5を備えたトラップ準位測定用パターン12を形成し、酸化物半導体層5の形成条件を先に確定した後、この確定された酸化物半導体層5の形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、従来の方法で形成する製造プロセスの一例を示す図である。

【0173】

図示されているように、先ず、酸化物半導体層5を形成し(S31)、その後、酸化物半導体層5上に、第1の電極6Aと第2の電極6Bとを同一層を用いた一つの工程で形成し(S32)、トラップ準位測定用パターン12を完成させ、第1の電極6Aおよび第2の電極6Bと接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン12を用いて、熱刺激電流測定(S33)を行う。

【0174】

トラップ準位測定用パターン12において、酸化物半導体層5は、第1の電極6Aおよび第2の電極6Bと接するように形成されているので、トラップ準位測定用パターン12を用いて、熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極6Aおよび第2の電極6Bとの界面における酸素欠損状態も反映することができる。

【0175】

以上のように、トラップ準位測定用パターン12の製造プロセスが、実施の形態1で用いたトラップ準位測定用パターン3の製造プロセスより、短縮されており、酸化物半導体層5の形成条件を、さらに容易に形成することができるとともに、精度高く酸化物半導体層5のトラップ準位を把握することができるトラップ準位測定用パターン12を用いて、確定することができる。

【0176】

その他の工程については、実施の形態1で既に説明しているため、その説明を省略する。

【0177】

図13は、大型アクティブマトリックス基板1c上に、酸化物半導体層5を備えたトラップ準位測定用パターン12と、酸化物半導体層5を備えたTFT素子7と、を同時に形成する製造プロセスの一例を示す図である。

【0178】

先ず、TFT素子7に備えられたゲート電極4Gを形成し(S41)、その後、ゲート絶縁膜8を基板全面に形成する(S42)。

【0179】

そして、トラップ準位測定用パターン12とTFT素子7とに備えられた酸化物半導体層5を、同一層を用いて一つの形成工程で形成する(S43)。

【0180】

それから、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、トラップ準位測定用パターン12に備えられた第1の電極6Aと第2の電極6Bと、を同一層を用いた一つの工程で形成し(S44)、トラップ準位測定用パターン12を完成させる。

【0181】

第1の電極6Aおよび第2の電極6Bと接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン12を用いて、熱刺激電流測定(S45)を行うことができる。

【0182】

トラップ準位測定用パターン12において、酸化物半導体層5は、第1の電極6Aおよび第2の電極6Bと接するように形成されているので、トラップ準位測定用パターン12を用いて、熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極6Aおよび第2の電極6Bとの界面における酸素欠損状態も反映することができる。

【0183】

熱刺激電流測定の結果が良判定であれば、次工程である層間絶縁膜9の形成工程(S46)と画素電極10パターン形成工程(S47)とを行い、TFT素子7を完成させる。

【0184】

一方、熱刺激電流測定の結果が不良判定であれば、酸化物半導体層5の形成工程(S43)において問題があったこととなるので、酸化物半導体層5の形成条件を見直し、新しい基板にS41〜S44の工程を行い、再び、熱刺激電流測定(S45)を行う。

【0185】

このような製造プロセスを用いることにより、TFT素子7を完成させる前にも、TFT素子7に備えられた酸化物半導体層5が正常に形成されているかを把握することができる。

【0186】

また、TFT素子7を完成させる前の中間の段階で、酸化物半導体層5が正常に形成されているかを把握することができるので、TFT素子7を完成させた後に、TFT素子7が不良であると判定された場合には、酸化物半導体層5以外の部分で問題が生じた可能性が高いと推定することができる。

【0187】

したがって、TFT素子7の不良の原因が、酸化物半導体層5に起因して生じているか、TFT素子7に備えられた他の層によって不生じているか、を特定するのが容易になる。

【0188】

また、このような製造プロセスを用いることにより、酸化物半導体層5の蒸着工程において、突発的なトラブルが生じ、膜質に不具合が発生したとしても、酸化物半導体層5におけるトラップ準位の評価を行うことで、迅速に対応ができ、製造プロセスへの早急なフィードバックを行うことができる。

【0189】

したがって、早急なトラブル解消が可能となり、結果、生産効率や歩留りの向上を期待できる。

【0190】

また、このような製造プロセスにおいては、第1の電極6Aおよび第2の電極6Bの各々は、酸化物半導体層5を半導体層として備えたTFT素子7の電極層および配線を形成する導電層と同一材料で形成されているので、新たな材料や工程を追加する必要がなく、製造コストを抑えることが可能となる。

【0191】

〔実施の形態3〕

次に、図14から図17に基づいて、本発明の第3の実施形態について説明する。本実施の形態においては、絶縁基板2上にトラップ準位測定用パターンを形成することは実施の形態1および実施の形態2と同様であるが、トラップ準位測定用パターン13の構造が、実施の形態1で用いたトラップ準位測定用パターン3および実施の形態2で用いたトラップ準位測定用パターン12とは異なる。その他の構成については実施の形態1および実施の形態2において説明したとおりである。説明の便宜上、上記の実施の形態1および実施の形態2の図面に示した部材と同じ機能を有する部材については、同じ符号を付し、その説明を省略する。

【0192】

図14は、絶縁基板2上にトラップ準位測定用パターン13を備えた大型アクティブマトリックス基板1dの一例を示す図である。

【0193】

図示されているように、大型アクティブマトリックス基板1dは分断すると、9個のTFT基板11(図中において点線で表示)を得ることができる。

【0194】

そして、TFT基板11には、表示領域R1と非表示領域R2が備えられており、TFT基板11とは離れた位置である絶縁基板2の端部に存在する端部領域R3には、トラップ準位測定用パターン13が設けられている。

【0195】

図15は、図14に示すトラップ準位測定用パターン13のC−C‘線の断面構造を示すとともに、トラップ準位測定用パターン13を用いて熱刺激電流計測システムを作製する場合を示す図である。

【0196】

図15に図示されているように、トラップ準位測定用パターン13は、酸化物半導体層5上に2個の独立した電極である第1の電極6Aと第2の電極6Bとの両方が備えられており、酸化物半導体層5の下層には、絶縁層8Aを介して第3の電極4Aが備えられた構造を有している。

【0197】

そして、第1の電極6Aと第2の電極6Bとは、同一層で形成されているとともに、本実施の形態においては、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、同一層を用いて一つの形成工程で形成した。

【0198】

また、本実施の形態においては、第3の電極4Aは、TFT素子7に備えられたゲート電極4Gと、同一層を用いて一つの形成工程で形成した。

【0199】

図示されているように、本実施の形態においては、第1の電極6Aに電圧源を接続させ、第2の電極6Bに熱刺激電流計を接続させている。

【0200】

図16は、トラップ準位測定用パターン13を用いて、TFT素子としての電気特性測定を行う場合の一例を示す図である。

【0201】

図示されているように、第3の電極4Aをゲート電極として作用させ、第1の電極6Aと第2の電極6Bとの何れか一方をソース電極として作用させ、他方をドレイン電極として作用させると、トラップ準位測定用パターン13をTFT素子として動作させることができる。

【0202】

したがって、酸化物半導体層5のトラップ準位の評価に用いたトラップ準位測定用パターン13をそのまま用いて、TFT素子としての電気特性の評価も可能となる。

【0203】

図17は、大型アクティブマトリックス基板1d上に、酸化物半導体層5を備えたトラップ準位測定用パターン13と、酸化物半導体層5を備えたTFT素子7と、を同時に形成する製造プロセスの一例を示す図である。

【0204】

先ず、TFT素子7に備えられたゲート電極4Gと、トラップ準位測定用パターン12に備えられた第3の電極4Aと、を同一層を用いて一つの形成工程で形成する(S51)。その後、ゲート絶縁膜8を基板全面に形成する(S52)。

【0205】

そして、トラップ準位測定用パターン13とTFT素子7とに備えられた酸化物半導体層5を、同一層を用いて一つの形成工程で形成する(S53)。

【0206】

それから、TFT素子7に備えられたソース・ドレイン電極6S・6Dと、トラップ準位測定用パターン13に備えられた第1の電極6Aと第2の電極6Bと、を同一層を用いた一つの工程で形成し(S54)、トラップ準位測定用パターン13を完成させる。

【0207】

そして、図15に図示されているように、第1の電極6Aおよび第2の電極6Bと接するように形成された酸化物半導体層5を備えたトラップ準位測定用パターン13を用いて熱刺激電流計測システムを作製し、熱刺激電流測定(S55)を行うことができる。

【0208】

トラップ準位測定用パターン13において、酸化物半導体層5は、第1の電極6Aおよび第2の電極6Bと接するように形成されているので、トラップ準位測定用パターン13を用いて、熱刺激電流測定を行えば、酸化物半導体層5中(酸化物半導体層5の深さ方向)の酸素欠損状態のみでなく、酸化物半導体層5と第1の電極6Aおよび第2の電極6Bとの界面における酸素欠損状態も反映することができる。

【0209】

また、図16に図示されているように、トラップ準位測定用パターン13を用いて、TFT素子としての電気特性測定(S55)を行うことができる。

【0210】

熱刺激電流測定および電気特性測定(S55)の結果が良判定であれば、次工程である層間絶縁膜9の形成工程(S56)と画素電極10パターン形成工程(S57)とを行い、TFT素子7を完成させる。

【0211】

一方、熱刺激電流測定(S55)の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)において問題があったこととなるので、酸化物半導体層5の形成条件を見直し、新しい基板にS51〜S54の工程を行い、再び、熱刺激電流測定および電気特性測定(S55)を行う。

【0212】

また、熱刺激電流測定(S55)の結果が良判定であり、電気特性測定(S55)の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)以外の工程(S51・S52・S54)において問題があったこととなるので、このような工程(S51・S52・S54)の形成条件を見直し、新しい基板にS51〜S54の工程を行い、再び、熱刺激電流測定および電気特性測定(S55)を行う。

【0213】

このような製造プロセスを用いることにより、TFT素子7を完成させる前にも、TFT素子7に備えられた酸化物半導体層5やその他の層が正常に形成されているかを把握することができる。

【0214】

また、TFT素子7を完成させる前の中間の段階で、熱刺激電流測定および電気特性測定(S55)を行うことができ、熱刺激電流測定の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)において問題があったと推定することができ、熱刺激電流測定(S55)の結果が良判定であり、電気特性測定(S55)の結果が不良判定であれば、酸化物半導体層5の形成工程(S53)以外の工程(S51・S52・S54)において問題があったと推定することができるので、TFT素子7の不良の原因の特定が容易になる。

【0215】

また、このような製造プロセスを用いることにより、酸化物半導体層5の蒸着工程において、突発的なトラブルが生じ、膜質に不具合が発生したとしても、酸化物半導体層5におけるトラップ準位の評価を行うことで、迅速に対応ができ、製造プロセスへの早急なフィードバックを行うことができる。

【0216】

したがって、早急なトラブル解消が可能となり、結果、生産効率や歩留りの向上を期待できる。

【0217】

また、このような製造プロセスにおいては、第1の電極6A、第2の電極6Bおよび第3の電極4Aの各々は、酸化物半導体層5を半導体層として備えたTFT素子7の電極層および配線を形成する導電層と同一材料で形成されているので、新たな材料や工程を追加する必要がなく、製造コストを抑えることが可能となる。

【0218】

また、図示は省略するが、実施の形態1および実施の形態2において、既に説明したように、絶縁基板に酸化物半導体層5を備えたトラップ準位測定用パターン13のみを形成し、トラップ準位測定用パターン13を用いて熱刺激電流測定および電気特性測定を行い、酸化物半導体層5やその他の層の形成条件を先に確定した後、この確定された形成条件を用いて、上記絶縁基板とは異なる大型基板上に、酸化物半導体層5を備えたTFT素子7を、従来の方法で形成することもできる。

【0219】

本発明は上記した各実施の形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施の形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施の形態についても本発明の技術的範囲に含まれる。

【産業上の利用可能性】

【0220】

本発明は、回路基板、アクティブマトリックス基板および表示装置などの分野に好適に用いることができる。

【符号の説明】

【0221】

1 回路基板

1a、1b、1c、1d アクティブマトリックス基板

2 絶縁基板

3 トラップ準位測定用パターン

4 第1の電極

4A 第3の電極

4G ゲート電極

5 酸化物半導体層

6 第2の電極

6A 第1の電極

6B 第2の電極

6S ソース電極

6D ドレイン電極

7 TFT素子

8 ゲート絶縁膜

9 層間絶縁膜

10 画素電極

11 TFT基板

12 トラップ準位測定用パターン

13 トラップ準位測定用パターン

R1 表示領域

R2 非表示領域

R3 端部領域

【特許請求の範囲】

【請求項1】

絶縁基板の一方側の面に、酸化物半導体層が備えられている回路基板であって、

上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、上記第1の電極とは電気的に分離されている第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられていることを特徴とする回路基板。

【請求項2】

上記絶縁基板において上記酸化物半導体層が形成されている側の面には、上記絶縁基板の中心部を含む領域である第1の領域と、上記第1の領域の周辺領域であるとともに、上記絶縁基板の端部を含む領域である第2の領域と、が備えられており、

上記第2の領域に、上記トラップ準位測定用パターンが設けられていることを特徴とする請求項1に記載の回路基板。

【請求項3】

上記トラップ準位測定用パターンにおいて、上記酸化物半導体層は、上記第1の電極と上記第2の電極との間に、介在されていることを特徴とする請求項1または2に記載の回路基板。

【請求項4】

上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されていることを特徴とする請求項1または2に記載の回路基板。

【請求項5】

上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、

第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されていることを特徴とする請求項4に記載の回路基板。

【請求項6】

上記第1の電極および上記第2の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項1から5の何れか1項に記載の回路基板。

【請求項7】

上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項5に記載の回路基板。

【請求項8】

上記酸化物半導体層は、In、Ga、Znから選択される少なくとも一つの元素を含むことを特徴とする請求項1から7の何れか1項に記載の回路基板。

【請求項9】

上記請求項1から8の何れか1項に記載の回路基板を備え、

上記回路基板上には、上記酸化物半導体層と同一層によって形成された半導体層を備えた複数のアクティブ素子が設けられており、

上記アクティブ素子の各々には、画素電極が電気的に接続されており、

複数の上記画素電極がマトリックス状に形成されていることを特徴とするアクティブマトリックス基板。

【請求項10】

上記トラップ準位測定用パターンにおいて、上記第1の電極および上記第2の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項9に記載のアクティブマトリックス基板。

【請求項11】

上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、

第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、

上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項9に記載のアクティブマトリックス基板。

【請求項12】

上記請求項9から11の何れか1項に記載のアクティブマトリックス基板と、対向基板と、上記アクティブマトリックス基板と上記対向基板との間に介在された液晶層と、を備えていることを特徴とする表示装置。

【請求項13】

上記請求項9から11の何れか1項に記載のアクティブマトリックス基板と、上記アクティブマトリックス基板における上記画素電極が形成されている面側に形成された有機EL層と、を備えていることを特徴とする表示装置。

【請求項14】

絶縁基板の一方側の面に、酸化物半導体層が備えられた回路基板の製造方法であって、

上記絶縁基板において上記酸化物半導体層が形成されている側の面に、第1の電極と、上記第1の電極とは電気的に分離された第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンを形成する工程と、

熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程と、が含まれていることを特徴とする回路基板の製造方法。

【請求項15】

上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、

第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、

上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層のトラジスタ素子特性を評価する工程が含まれていることを特徴とする請求項14に記載の回路基板の製造方法。

【請求項1】

絶縁基板の一方側の面に、酸化物半導体層が備えられている回路基板であって、

上記絶縁基板において上記酸化物半導体層が形成されている側の面には、第1の電極と、上記第1の電極とは電気的に分離されている第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンが設けられていることを特徴とする回路基板。

【請求項2】

上記絶縁基板において上記酸化物半導体層が形成されている側の面には、上記絶縁基板の中心部を含む領域である第1の領域と、上記第1の領域の周辺領域であるとともに、上記絶縁基板の端部を含む領域である第2の領域と、が備えられており、

上記第2の領域に、上記トラップ準位測定用パターンが設けられていることを特徴とする請求項1に記載の回路基板。

【請求項3】

上記トラップ準位測定用パターンにおいて、上記酸化物半導体層は、上記第1の電極と上記第2の電極との間に、介在されていることを特徴とする請求項1または2に記載の回路基板。

【請求項4】

上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されていることを特徴とする請求項1または2に記載の回路基板。

【請求項5】

上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、

第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されていることを特徴とする請求項4に記載の回路基板。

【請求項6】

上記第1の電極および上記第2の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項1から5の何れか1項に記載の回路基板。

【請求項7】

上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記酸化物半導体層を半導体層として備えた上記絶縁基板上に形成されるアクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項5に記載の回路基板。

【請求項8】

上記酸化物半導体層は、In、Ga、Znから選択される少なくとも一つの元素を含むことを特徴とする請求項1から7の何れか1項に記載の回路基板。

【請求項9】

上記請求項1から8の何れか1項に記載の回路基板を備え、

上記回路基板上には、上記酸化物半導体層と同一層によって形成された半導体層を備えた複数のアクティブ素子が設けられており、

上記アクティブ素子の各々には、画素電極が電気的に接続されており、

複数の上記画素電極がマトリックス状に形成されていることを特徴とするアクティブマトリックス基板。

【請求項10】

上記トラップ準位測定用パターンにおいて、上記第1の電極および上記第2の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項9に記載のアクティブマトリックス基板。

【請求項11】

上記トラップ準位測定用パターンにおいて、上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、

第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、

上記第1の電極、上記第2の電極および上記第3の電極の各々は、上記画素電極を含む上記アクティブ素子の電極層および配線を形成する導電層と同一材料で形成されていることを特徴とする請求項9に記載のアクティブマトリックス基板。

【請求項12】

上記請求項9から11の何れか1項に記載のアクティブマトリックス基板と、対向基板と、上記アクティブマトリックス基板と上記対向基板との間に介在された液晶層と、を備えていることを特徴とする表示装置。

【請求項13】

上記請求項9から11の何れか1項に記載のアクティブマトリックス基板と、上記アクティブマトリックス基板における上記画素電極が形成されている面側に形成された有機EL層と、を備えていることを特徴とする表示装置。

【請求項14】

絶縁基板の一方側の面に、酸化物半導体層が備えられた回路基板の製造方法であって、

上記絶縁基板において上記酸化物半導体層が形成されている側の面に、第1の電極と、上記第1の電極とは電気的に分離された第2の電極と、上記第1の電極および上記第2の電極と接するように形成された上記酸化物半導体層と、を備えたトラップ準位測定用パターンを形成する工程と、

熱刺激電流測定により、上記酸化物半導体層のトラップ準位を測定する工程と、が含まれていることを特徴とする回路基板の製造方法。

【請求項15】

上記第1の電極と上記第2の電極とは何れも、上記酸化物半導体層の上部および下部の何れか一方に形成されており、

第3の電極は、上記一方とは反対側の面である上記酸化物半導体層の他方に絶縁層を介して形成されており、

上記第1の電極および上記第2の電極の何れか一方をソース電極として作用させ、他方をドレイン電極として作用させ、上記第3の電極をゲート電極として作用させ、上記酸化物半導体層のトラジスタ素子特性を評価する工程が含まれていることを特徴とする請求項14に記載の回路基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−93470(P2013−93470A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−235378(P2011−235378)

【出願日】平成23年10月26日(2011.10.26)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月26日(2011.10.26)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]