回路基板、半導体パワーモジュール、製造方法

【課題】半導体素子から多層基板への熱拡散性能の向上、および、多層基板と半導体素子との接合強度の向上。

【解決手段】半導体パワーモジュール10は、セラミックス多層基板100と、接合層110と、拡散層120と、半導体素子130を備える。接合層110は、セラミックス多層基板100の第1の面105上に配置され、半導体素子130とセラミックス多層基板100とを電気的に接続する導電接合部111と、半導体素子130とセラミックス多層基板100とを絶縁する絶縁接合部112とを備える平面状の薄膜層である。こうすれば、半導体素子130とセラミックス多層基板100との間における空隙の発生を抑制しつつ接合することができ、半導体素子130からセラミックス多層基板100への熱拡散性能、および、セラミックス多層基板100と半導体素子130との接合強度を向上できる。

【解決手段】半導体パワーモジュール10は、セラミックス多層基板100と、接合層110と、拡散層120と、半導体素子130を備える。接合層110は、セラミックス多層基板100の第1の面105上に配置され、半導体素子130とセラミックス多層基板100とを電気的に接続する導電接合部111と、半導体素子130とセラミックス多層基板100とを絶縁する絶縁接合部112とを備える平面状の薄膜層である。こうすれば、半導体素子130とセラミックス多層基板100との間における空隙の発生を抑制しつつ接合することができ、半導体素子130からセラミックス多層基板100への熱拡散性能、および、セラミックス多層基板100と半導体素子130との接合強度を向上できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多層基板により構成される回路基板、回路基板に半導体素子が搭載された半導体パワーモジュール、および、それらの製造方法に関する。

【背景技術】

【0002】

近年パワーモジュールパッケージにおいては小型、低背、高密度実装化が進み、その実現のために、従来のワイヤーボンドによる実装方式から、セラミックス多層基板等を用いて半導体素子をフリップチップ接続する実装方式を用いた半導体モジュールが提案されている。フリップチップ接続とは、半導体素子上にバンプと呼ばれる導電性の突起を配置し、セラミックス多層基板上の半導体素子を搭載する位置に、バンプを合わせて、セラミックス多層基板に直接接合する接合方法であり、半導体素子の実装に必要な面積を20〜30%程度減らす事ができ、高密度実装に寄与する事ができる。

【0003】

このようなフリップチップ実装方式を用いた半導体モジュールには、セラミックス多層基板と半導体素子との間のバンプ間の空隙に、従来の有機材料を封止材として用いたものに加えて、無機系材料が充填されたものがある(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−253579号公報

【特許文献2】特開2006−066582号公報

【特許文献3】特開2010−287869号公報

【特許文献4】特開2009−170930号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

フリップチップ実装により更に高密度実装化が進む半導体素子パワーモジュールにおいては、放熱面積の低下によりサイズ効果による放熱特性が劣化するため、半導体素子からセラミック多層基板への更なる熱拡散性能の向上が必要である。しかしながら、従来の半導体素子パワーモジュールでは、封止材充填工程における気泡の発生や、使用時の熱応力に起因する接合部分へのクラックの発生などによりセラミックス多層基板と半導体素子との間に空間が発生し、空気が入り込むなどの問題がある。そのため、従来の半導体素子パワーモジュールでは、半導体素子からセラミックス多層基板への熱拡散性能の低下による半導体素子の放熱性能の低下、および、セラミックス多層基板と半導体素子との間の接合強度の低下を招くおそれがある。

【0006】

本発明は上述の課題に鑑みてなされたものであり、半導体素子からセラミックス多層基板への熱拡散性能の向上、および、セラミックス多層基板と半導体素子との接合強度の向上を目的とする。

【課題を解決するための手段】

【0007】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は適用例として実現することが可能である。

【0008】

[適用例1]

半導体パワーモジュールであって、ビアおよび配線パターンが形成された多層基板と、前記多層基板の第1の面側に配置される半導体素子と、前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置されている平面状の導電接合部であって、前記半導体素子に形成されている電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする平面状の絶縁接合部と、 を有する半導体パワーモジュール。

【0009】

適用例1の半導体パワーモジュールによれば、接合層が平面状に形成されているので、多層基板と半導体素子との接合時に、多層基板と半導体素子との間における空隙の発生を抑制できる。従って、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0010】

[適用例2]

適用例1記載の半導体パワーモジュールであって、前記多層基板と前記接合層および前記半導体素子と前記接合層とは、拡散接合により接合され、前記半導体パワーモジュールは、更に、前記多層基板と前記接合層および前記半導体素子と前記接合層との間に、前記拡散接合時に形成される拡散層を備える、半導体パワーモジュール。

【0011】

適用例2の半導体パワーモジュールによれば、多層基板と接合層、および、接合層と半導体素子との拡散接合時に、多層基板と接合層の接合面、および、接合層と半導体素子との接合面で発生する原子の拡散により拡散層が形成される。従って、多層基板と接合層、および、接合層と半導体素子との接合強度を向上できる。

【0012】

[適用例3]

適用例1記載の半導体パワーモジュールであって、前記絶縁接合部には、金属フィラーもしくは無機系フィラーが含まれる、半導体パワーモジュール。

【0013】

適用例1の半導体パワーモジュールによれば、絶縁接合部に金属フィラーもしくは無機系フィラーが含まれるので、半導体素子から多層基板への熱拡散性能を向上できる。

【0014】

[適用例4]

適用例2記載の半導体パワーモジュールであって、

前記絶縁接合部および前記拡散層には、金属フィラーもしくは無機系フィラーが含まれる、

半導体パワーモジュール。

【0015】

適用例4の半導体パワーモジュールによれば、絶縁接合部および拡散層に金属フィラーもしくは無機系フィラーが含まれるので、半導体素子から多層基板への熱拡散性能を向上できる。

【0016】

[適用例5]

適用例1ないし適用例4いずれか記載の半導体パワーモジュールであって、前記導電接合部を構成する材料の接合開始温度である第1の接合開始温度は、前記絶縁接合部を構成する材料の接合開始温度である第2の接合開始温度よりも低いことを特徴とする、半導体パワーモジュール。

【0017】

適用例5の半導体パワーモジュールによれば、絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接続部と半導体素子の電極パッド、および、導電接合部と配線基板とが接合された状態、すなわち、導電接続部と半導体素子の電極パッドの間、および、導電接合部と配線基板の間に空隙が存在しない状態で、絶縁接合部の軟化変形が開始され、絶縁接合部と半導体素子、および、絶縁接合部と配線基板との接合が行われる。よって、絶縁接合部を構成する材料が、導電接続部と電極パッドの間へ侵入すること、導電接合部に混入することによる、導電接合部の導電性能の低下を抑制できる。

【0018】

[適用例6]

適用例5記載の半導体パワーモジュールにおいて、前記第1の接合開始温度は、前記導電接合部が焼結反応を開始する焼結開始温度以上であり、前記第2の接合開始温度は、前記絶縁接合部が焼結反応を開始する焼結開始温度以上であることを特徴とする、半導体パワーモジュール。

【0019】

適用例6の半導体パワーモジュールによれば、第1の接合開始温度は、導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされ、第2の接合開始温度は、絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされている。従って、導電接合部、絶縁接合部の各々について、融点まで加熱することなく他部材との接合を行うことができる。また、第1の接合開始温度を、導電接合部を構成する材料の溶融開始温度とし、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度としてもよい。こうすれば、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0020】

[適用例7]

回路基板であって、ビアおよび配線パターンが形成された多層基板と、前記多層基板の第1の面上に配置され、前記多層基板に半導体素子を接合するための接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置され、前記配線パターンと前記半導体素子と導通し、少なくとも前記第1の面側が平面状に形成されている導電接続部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とし、少なくとも前記第1の面側が平面状に形成されている絶縁接合部と、を有する回路基板。

【0021】

適用例7の回路基板によれば、半導体素子と多層基板とが平面で接合されるので、多層基板と半導体素子との間における空隙の発生を抑制できる。従って、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0022】

[適用例8]

適用例7記載の回路基板であって、前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度である第1の接合開始温度は、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度である第2の接合開始温度よりも低いことを特徴とする、回路基板。

【0023】

適用例8の半導体パワーモジュールによれば、絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接合部と半導体素子の電極パッド、および、導電接合部と配線基板が接合された状態、すなわち、導電接合部と半導体素子の電極パッドの間、および、導電接合部と配線基板の間に空隙が存在しない状態で、絶縁接合部の軟化変形が開始され、絶縁接合部と半導体素子、および、絶縁接合部と配線基板との接合が行われる。よって、絶縁接合部を構成する材料が導電接続部と電極パッドの間へ侵入すること、導電接合部に混入することによる、導電接合部の導電性能の低下を抑制できる。

【0024】

[適用例9]

適用例8記載の回路基板おいて、前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、回路基板。

【0025】

適用例9の半導体パワーモジュールによれば、第1の接合開始温度は、導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされ、第2の接合開始温度は、絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされている。従って、導電接合部、絶縁接合部の各々について、融点まで加熱することなく他部材との接合を行うことができる。また、第1の接合開始温度を、導電接合部を構成する材料の溶融開始温度とし、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度としてもよい。こうすれば、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0026】

[適用例10]

半導体パワーモジュールであって、ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面側に配置される半導体素子と、前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置され、前記半導体素子の電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、を有し、前記電極パッドと前記導電接続部とが導通可能となるように、前記半導体素子が前記接合層上に積層され、前記多層基板、前記接合層および前記半導体素子が接合された状態で、前記多層基板と前記接合層との界面、および、前記接合層と前記半導体素子との界面の、積層方向の断面が、略直線状に形成されている、半導体パワーモジュール。

【0027】

適用例10の半導体パワーモジュールによれば、多層基板と接合層との接合界面、および、接合層と半導体素子との接合界面の、積層方向の断面が、略直線状となるように形成されている。略直線状とは、本明細書では、多層基板と接合層との接合界面、および、接合層と半導体素子との接合界面に、気泡等による空隙が存在しない状態を含む。従って、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0028】

[適用例11]

回路基板であって、ビアおよび配線パターンが形成された多層基板と、前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置され、前記配線パターンに前記半導体素子を導通させるための導電接続部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、を有し、前記多層基板と前記接合層が接着された状態で、前記多層基板と前記接合層との界面の、積層方向の断面は、略直線状である、回路基板。

【0029】

適用例11の回路基板によれば、多層基板と接合層との接合界面は、積層方向の断面が、略直線状となるように形成されている。従って、多層基板と接合層との接合強度を向上することができ、半導体素子から多層基板への熱拡散性能を向上できる。

【0030】

[適用例12]

半導体パワーモジュールの製造方法であって、ビアおよび配線パターンを有する多層基板を製作し、前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する平面状の導電接続部を有し、前記第1の部位とは異なる第2の部位に平面状の絶縁接合部を有する接合部を、前記多層基板の第1の面上に配置し、前記接合部上に、前記半導体素子を、前記半導体素子に形成されている電極パッドと前記導電接続部とが導通可能となるように配置し、前記多層基板、前記接合部および前記半導体素子を、加熱圧着し、前記多層基板と前記接合層、および、前記接合層と前記半導体素子を拡散接合する、半導体パワーモジュールの製造方法。

【0031】

適用例12の半導体パワーモジュールの製造方法によれば、多層基板と半導体素子との間に、接合部と電極パッドにより、多層基板と半導体素子とを接合するための平面状の接合層が形成される。従って、多層基板と半導体素子との間における空隙の発生を抑制できる。よって、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上できる。

【0032】

[適用例13]

適用例12記載の半導体パワーモジュールの製造方法であって、前記拡散接合において、 前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度を第1の接合開始温度とし、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、前記多層基板、前記接合部および前記半導体素子を、前記第1の接合開始温度で加熱圧着することにより、前記導電接合部と前記半導体素子の前記電極パッド、および、前記導電接合部と前記配線基板とを接合し、前記導電接合部と前記半導体素子の前記電極パッドとの接合後に、前記多層基板、前記接合部および前記半導体素子を、前記第2の接合開始温度で加熱圧着することにより、前記多層基板と前記絶縁接合部、および、前記絶縁接合部と前記半導体素子とを接合する、半導体パワーモジュールの製造方法。

【0033】

適用例13の半導体パワーモジュールの製造方法によれば、 絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接合部と半導体素子の電極パッド、および、導電接合部と配線基板が接合された状態、すなわち、導電接合部と半導体素子の電極パッドの間、および、導電接合部と配線基板の間に空隙が存在しない状態で、絶縁接合部の軟化変形が開始され、絶縁接合部と半導体素子、および、絶縁接合部と配線基板との接合が行われる。よって、絶縁接合部を構成する材料が、導電接続部と電極パッドの間へ侵入すること、導電接合部に混入することによる、導電接合部の導電性能の低下を抑制できる。

【0034】

[適用例14]

適用例13記載の半導体パワーモジュールの製造方法において、前記第1の接合開始温度は、前記導電接続部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、前記第2の接合開始温度は、前記絶縁接続部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、半導体パワーモジュールの製造方法。

【0035】

適用例14の半導体パワーモジュールの製造方法によれば、第1の接合開始温度は、導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされ、第2の接合開始温度は、絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされている。従って、導電接合部、絶縁接合部の各々について、融点まで加熱することなく他部材との接合を行うことができる。また、第1の接合開始温度を、導電接合部を構成する材料の溶融開始温度とし、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度としてもよい。こうすれば、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0036】

[適用例15]

適用例12記載の半導体パワーモジュールの製造方法であって、前記拡散接合において、 前記導電接続部を構成する材料と前記電極パッドを構成する材料とが接合を開始する温度を第1の接合開始温度とし、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、前記第1の接合開始温度が、所定時間保持された後、前記第2の接合開始温度が所定時間保持されるように設定されている温度プロファイルに基づき、前記加熱を行う、半導体パワーモジュールの製造方法。

【0037】

適用例15の半導体パワーモジュールの製造方法によれば、段階的な温度変化を有する温度プロファイルに基づいて、接合部、配線基板および半導体素子の接合が行われる。従って、簡易な構成で、多段階の温度変化を行いつつ拡散接合を行うことができ、製造効率を向上できる。

【0038】

[適用例16]

回路基板の製造方法であって、ビアおよび配線パターンを有する多層基板を製作し、前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する導電接続部を有し、前記第1の部位とは異なる第2の部位に絶縁接合部を有し、少なくとも、前記第1の面側が平面状に形成されている接合層を、前記多層基板の第1の面上に配置し、前記多層基板と前記接合層とを、前記接合層に含まれる有機成分の粘着力により接着する、回路基板の製造方法。

【0039】

適用例16の回路基板の製造方法によれば、多層基板の第1の面側が平面状に形成された、多層基板と半導体素子とを接合するための接合層が、多層基板の第1の面上に形成される。従って、多層基板と接合層との間における空隙の発生を抑制できる。よって、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0040】

本発明において、上述した種々の態様は、適宜、組み合わせたり、一部を省略したりして適用することができる。

【図面の簡単な説明】

【0041】

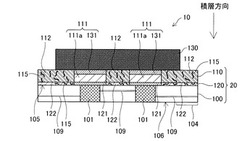

【図1】第1実施例における半導体パワーモジュール10の概略構成を示す断面図。

【図2】第1実施例における回路基板20について説明する説明図。

【図3】第1実施例における半導体パワーモジュール10の製造方法を説明する工程図。

【図4】ステップS12における導電接続部111aの配置工程を説明する説明図。

【図5】ステップS14における絶縁接合部112のスクリーン印刷について説明する説明図。

【図6】第1実施例における半導体パワーモジュール10の接合工程を説明する説明図。

【図7】第2実施例における半導体パワーモジュール30を示す平面図。

【図8】第2実施例における半導体パワーモジュール30を示す断面図。

【図9】変形例における半導体パワーモジュール40を示す断面図。

【発明を実施するための形態】

【0042】

A.第1実施例:

A1.半導体パワーモジュールの概略構成:

図1は、第1実施例における半導体パワーモジュール10の概略構成を示す断面図である。図2は、第1実施例における回路基板20について説明する説明図である。半導体パワーモジュール10は、回路基板20と、半導体素子130とを備える。回路基板20は、セラミックス多層基板100と、接合層110と、拡散層120とを備える。

【0043】

セラミックス多層基板100は、セラミックス材料により形成されている。セラミックス材料としては、例えば、酸化アルミナ(Al2O3)、窒化アルミニウム(AlN)、窒化珪素(Si3N4)などが用いられる。セラミックス多層基板100は、半導体素子が実装される第1の面105と、該面と対向し、制御回路やコンデンサなどのその他の電子部品が搭載され得るもう一方の第2の面106間を電気的に接続するための内層ビアホール101と、配線パターン109と、第2の面106上に配置された外部接続用の電極端子104を備える。配線パターン109は、セラミックス多層基板100の表面、内部の層の表面に形成されている。図1では、セラミックス多層基板100の表面に形成された配線パターンは省略されている。また、セラミックス多層基板100の第1の面105上、および第2の面106上には、半導体素子130やその他の電子部品を搭載するための電極ランド(図示省略)が形成されている。半導体素子130は、内層ビアホール101および配線パターン109を介して、第2の面106上に配置されている電極端子104と電気的に接続されている。

【0044】

接合層110は、セラミックス多層基板100の第1の面105上に配置され、導電接合部111と、絶縁接合部112とを備える平面状の薄膜層である。

【0045】

導電接合部111は、導電接続部111aと半導体素子130の電極パッド131とから構成され、半導体素子130とセラミックス多層基板100とを電気的に接続する。導電接続部111aは、導電性の金属を主成分として形成されており、図2に示すように、セラミックス多層基板100の第1の面105上であって、内層ビアホール101に対応する第1の部位107(太実線で示す)上に配置されている。導電性の金属として、例えば、銅、銀、アルミニウム金属などを用いてもよい。導電接続部111aは、後述する絶縁接合部112よりも薄く形成されており、絶縁接合部112と導電接続部111aとにより窪みが形成される。該窪みに、電極パッド131が嵌りこむように配置されることによって、導電接合部111が形成される。

【0046】

絶縁接合部112は、半導体素子130とセラミックス多層基板100とを絶縁する。絶縁接合部112は、図2に示すように、セラミックス多層基板100の第1の面105上であって、第1の部位107とは異なる第2の部位108(太破線で示す)に配置されている。絶縁性の無機系材料を主成分とし、半導体素子の実装時の加熱工程により軟化する粉末ガラスにより形成されている。粉末ガラスは、例えば、ZnO−B2O3−SiO2、など、酸化ケイ素、酸化亜鉛、酸化ホウ素、酸化ビスマスなどの混相として形成される。

【0047】

第1実施例において、第2の部位108とは、第1の部位107である導電接合部111が配置されている部位を除く部分を含む。接合層110が均一な平面となるように、導電接合部111と絶縁接合部112は、ほぼ同一の厚みを有している。また、接合層110の、半導体素子130側に対向する面も、均一な平面となるように形成されている。

【0048】

なお、本実施例において、均一な平面とは、微少な湾曲や凹凸を含んでおり、接合層110が均一な平面を有しているとは、接合層110の、セラミック多層基板の第1の面105に対向する面が、第1の面105の形状に沿って形成され、導電接合部111と絶縁接合部112が連続して平坦に形成されていること、および、接合層110の、半導体素子130側に対向する面が、半導体素子130の、接合層110に対向する面の形状に沿って形成されていること、を含む。

【0049】

絶縁接合部112は、絶縁性能が低下しない程度に、フィラー115を含むことが望ましい。ここで、フィラー115は、銅やアルミニウム粉末などよりなる金属フィラーもしくは無機系フィラーを含む。無機系フィラーとしては酸化ホウ素やアルミナ、窒化珪素、窒化アルミニウムなどよりなるセラミックスなどの、高放熱特性フィラーであることが望ましい。フィラー115が含有されていることにより、絶縁接合部112の伝熱性能が向上する。

【0050】

拡散層120は、セラミックス多層基板100と接合層110との拡散接合により形成される層である。拡散層120は、導電拡散部121と絶縁拡散部122を備える。導電拡散部121は、セラミックス多層基板100と接合層110の導電接続部111aとの拡散接合により形成される。絶縁拡散部122は、セラミックス多層基板100と、接合層110の絶縁接合部112との拡散接合により形成される。絶縁拡散部122には、絶縁接合部112と同様に、フィラー115が含有されてもよい。なお、図1では、説明の便宜上、導電拡散部121と絶縁拡散部122の境界は明確に記載されているが、導電拡散部121と絶縁拡散部122の境界は曖昧であってもよい。

【0051】

半導体素子130は、電極パッド131を備える。電極パッド131は、例えば、金(Au)を主成分として形成されている。半導体素子130は、電極パッド131が、接合層110の導電接続部111aに接するように、接合層110上に配置されている。半導体素子130は、電極パッド131および導電接続部111a(すなわち、導電接合部111)を介してセラミックス多層基板100と電気的に接続されている。

【0052】

A2.製造方法:

半導体パワーモジュール10の製造方法を、図3〜図6を用いて説明する。図3は、第1実施例における半導体パワーモジュール10の製造方法を説明する工程図である。

【0053】

内層ビアホール101および配線パターン109が形成されたセラミックス多層基板100を作製する(ステップS10)。セラミックス多層基板100の作製には、セラミックス多層基板100の表面に、半導体素子130および他の電子部品を実装するための薄膜状の電極ランドを形成することを含む。電極ランドは、導電ペーストを用いた印刷法、物理蒸着(PVD:Physical Vapor Deposition)や化学蒸着(CVD: Chemical Vapor Deposition)により形成される。

【0054】

セラミックス多層基板100の第1の面105上であって、内層ビアホール101に対応する第1の部位に、導電接続部111aを配置する(ステップS12)。図3は、ステップS12における導電接続部111aの配置工程を説明する説明図である。図3に示すように、後述するステップS18における加熱工程により溶融する金属種を主成分とする金属の突起を導電接続部111aとして形成する。この金属の突起はバンプとも呼ばれる。バンプは、所望の位置にボール状に形成された金属を配置し、加熱処理により柱状形状とするボール搭載法により形成しても良いし、セラミックス多層基板100の第1の面105の第1の部位107に、予め対応する位置にバンプとなる金属を転写する方法や導電接続部111aの材料として既述した金属種を主成分とするペーストを、スクリーン印刷により印刷する方法、セラミックス多層基板100の第1の面105の第1の部位107にフォトリソパターンによりマスキングを施しメッキ法により所望の位置に金属バンプを形成してもよい。

【0055】

導電接続部111aを配置したセラミックス多層基板100の第1の面105上の、第1の部位とは異なる第2の部位に絶縁接合部112を配置する(ステップS14)。具体的には、粉末ガラスと熱分解性の有機結着剤とを、有機溶媒や水などの溶媒を用いて混練してガラス粉末ペーストを生成し、ガラス粉末ペーストを、セラミックス多層基板100の第1の面105上の、導電接続部111aの空隙を埋めるようにスクリーン印刷によりに印刷する。

【0056】

図5は、ステップS14における絶縁接合部112のスクリーン印刷について説明する説明図である。スクリーン印刷機200は、スクリーン202と、スキージ203と、スキージホルダー204とを備える。スクリーン202には、導電接続部111aに対応する部位を除く部位、すなわち、絶縁接合部112に対応する部位にのみ開口部が形成されている。ガラス粉末ペースト250をスクリーン202に載せ、スクリーン202上からスキージ203を摺動させる。こうすることにより、ガラス粉末ペースト250は開口部を通過し、セラミックス多層基板100の第1の面105上の、導電接続部111aが配置されている部位を除いた部位、すなわち、絶縁接合部112が配置される部位に転写される。この結果、導電接続部111aと絶縁接合部112とからなり、セラミックス多層基板100の第1の面105側が平面上に形成された接合部110a(図2)が形成される。なお、ステップS12,S14の順序は、逆であってもよい。なお、接合部110aの結着に用いられる有機成分(有機結着剤)は、後述する加熱処理工程において、分解、除去される。

【0057】

形成された接合部110a上に、半導体素子130を配置する(ステップS16)。具体的には、導電接続部111aと絶縁接合部112とから形成される窪みに、電極パッド131を嵌め込むように半導体素子130を配置する。導電接続部111aと電極パッド131とが接触することにより、半導体素子130と導電接続部111aとの導通が確保される。

【0058】

セラミックス多層基板100、接合層110および半導体素子130を加熱圧着して、半導体パワーモジュールを製造する(ステップS18)。図6は、第1実施例における半導体パワーモジュール10の接合工程を説明する説明図である。図6に示すように、セラミックス多層基板100、接合層110および半導体素子130を、加圧するとともに、導電接続部111aと絶縁接合部112とが熱融着する温度に加熱する。こうすることにより、導電接続部111a、絶縁接合部112、セラミックス多層基板100の第1の面105および導電接合部111及び絶縁保護膜よりなる半導体素子130の表面が溶融し、セラミックス多層基板100と接合層110の間、および、接合層110と半導体素子130の間は、空隙の存在しない均一な平面で拡散接合される。導電接続部111aと絶縁接合部112とが熱融着する温度とは、例えば、導電接続部111aの材料として、融点660℃のアルミニウム金属を用い、絶縁接合部112の材料として軟化点640℃のZnO−B2O3−SiO2ガラスを用いた場合には、両材料が熱融着する温度670℃で加熱する。

【0059】

以上説明したように、少なくとも2段階の温度変化が行われるように設定されている温度プロファイルに基づいて、加圧および加熱を行うことにより、セラミックス多層基板100と接合層110との接合面で原子の拡散が生じ、拡散層120が形成され、セラミックス多層基板100と接合層110とは接合される。

【0060】

セラミックス多層基板100、接合層110、半導体素子130と直行する方向(セラミックス多層基板100、接合層110および半導体素子130の積層方向)に切断した切断面は、化合物半導体とその表面の保護層よりなる半導体素子130と接合層110との界面、ならびに接合層110とセラミックス成分(アルミナ、窒化珪素、窒化アルミニウムなど)よりなるセラミックス多層基板100の表面との界面が、図6に太実線で示すように、それぞれ略一直線状になるよう配置されており、気泡等の微少な欠陥を含まない。ミクロンオーダーの不可避なボイド等は、実施例における欠陥には含まれない。実施例において、欠陥と判断される気泡のサイズは、例えば、100μm以上としてもよい。

【0061】

また微視的に見た時、上記それぞれの界面は半導体素子130、セラミックス多層基板100に対して、それぞれ接合層110の構成成分が拡散して形成される拡散層120を持つ。これらの層はEDS、EPMA等によるマッピング分析により、それぞれ半導体素子130の表面成分(ZrやTiなどの保護膜の形成成分)、セラミックス多層基板100のセラミックス成分(アルミや窒素など)が混在する層が形成されている層と定義される。

【0062】

以上説明した第1実施例の半導体パワーモジュール10によれば、接合層110が平面状に形成されている、すなわち、接合層110の、セラミックス多層基板100に対する対向面は、セラミックス多層基板100の第1の面105の面形状に沿って平面状に形成されており、接合層110の、半導体素子130に対抗する面も、半導体素子130の接合層110側の面形状に沿って平面状に形成されている。従って、セラミックス多層基板100と半導体素子130との接合時に、セラミックス多層基板100と接合層110、接合層110と半導体素子130との間における空隙の発生を抑制できる。従って、半導体素子130からセラミックス多層基板100への熱拡散性能、および、セラミックス多層基板100と半導体素子130との接合強度を向上することができる。

【0063】

また、第1実施例のセラミックス多層基板100によれば、接合層110の絶縁接合部112は、有機系材料に比して熱伝導性能の高いガラス等の無機系材料を主成分として形成されているので、半導体素子130からセラミックス多層基板100への熱拡散性能を向上できる。

【0064】

半導体パワーモジュール10の接合時の加熱(図3のステップS18の工程)により、各部材は熱膨張し、セラミックス多層基板100と接合層110、接合層110と半導体素子130との間に応力が発生する。第1実施例では、絶縁接合部112の主成分であるガラス成分の線熱膨張係数は、導電接続部111aの主成分である金属の線熱膨張係数よりもセラミックス多層基板100や半導体素子130の線熱膨張係数に近い。このため、導電接続部111aとセラミックス多層基板100および半導体素子130との境界に生じる応力は、絶縁接合部112とセラミックス多層基板100および半導体素子130との境界に生じる応力よりも大きくなる。

【0065】

第1実施例の半導体パワーモジュール10によれば、導電接続部111aが絶縁接合部112の周囲に配置されているので、導電接続部111aの変形を、絶縁接合部112によって抑制できる。従って、導電接続部111aとセラミックス多層基板100および半導体素子130との間に生じる応力を、導電接続部111aと絶縁接合部112の界面に分散できる。よって、接合層110とセラミックス多層基板100および半導体素子130との間に集中して生じる応力を分散できるので、半導体パワーモジュール10の損傷を抑制でき、半導体パワーモジュール10の信頼性を向上できる。

【0066】

また、第1実施例の半導体パワーモジュール10によれば、セラミックス多層基板100と接合層110の拡散接合時に、セラミックス多層基板100と接合層110の間に、拡散層120が形成される。従って、セラミックス多層基板100と接合層110との接合強度を向上できる。

【0067】

また、第1実施例の半導体パワーモジュール10によれば、接合層110の絶縁接合部112および拡散層120の絶縁拡散部122に、伝熱性能、放熱性能を有するフィラー115が含まれるので、半導体素子130からセラミックス多層基板100への熱拡散性能を向上できる。

【0068】

B.第2実施例:

第1実施例では、半導体素子130が一つのみ搭載された半導体パワーモジュール10について説明した。第2実施例では、複数の半導体素子が搭載された半導体パワーモジュールについて、図7および図8を参照して説明する。

【0069】

B1.半導体パワーモジュール概略構成:

図7は、第2実施例における半導体パワーモジュール30を示す平面図である。図8は、第2実施例における半導体パワーモジュール30を示す断面図である。図8は、図7におけるA−A断面で切断した断面を示す。

【0070】

第2実施例の半導体パワーモジュール30は、図7および図8に示すように、セラミックス多層基板300と、接合層310と、拡散層320および複数(第2実施例では6個)の半導体素子330を備える。接合層310は、導電接続部311aと半導体素子330の電極パッド331とからなる導電接合部311と、絶縁接合部312とを備え、拡散層320は、導電拡散部321と絶縁拡散部322を備える。第2実施例において、セラミックス多層基板300、接合層310、導電接合部311、絶縁接合部312、拡散層320、導電拡散部321、絶縁拡散部322および各半導体素子330は、それぞれ、第1実施例のセラミックス多層基板100、接合層110、導電接合部111、絶縁接合部112、拡散層120、導電拡散部121、絶縁拡散部122および半導体素子130と同様の構成を備える。

【0071】

一般的に、従来のSi系半導体素子からSiC等の化合物半導体素子を用いる事による半導体素子の発熱許容量の増大に対応するために、半導体素子の周辺部材に対する高耐熱性、一方でモジュールとして放熱部品の小型化要求などへの対応のために高熱拡散性が求められている。第2実施例の半導体パワーモジュール30は、接合層310が平面状に形成されているので、半導体素子330とセラミックス多層基板300とは耐熱特性や熱拡散性が低い有機系材料を介さず、耐熱特性や熱拡散性に優れる無機系材料を主成分として形成された平面で接合される。従って、半導体素子330からセラミックス多層基板300への熱拡散性能が向上されるので、300℃以下程度の高温域で使用される化合物半導体素子(半導体素子330)を、高密度に複数搭載した信頼性の高い半導体パワーモジュール30を提供できる。

【0072】

C.第3実施例:

第3実施例では、導電接合部は、導電接続部と半導体素子の電極パッドとが接合を開始する温度である第1の接合開始温度を有し、絶縁接合部は、配線基板や半導体素子と接合を開始する温度であって、第1の接合開始温度よりも高い第2の接合開始温度を有する。なお、第3実施例において、接合層を構成する導電接合部、絶縁接合部は、接合開始温度以外は、第1実施例の各々と同様の作用・機能を有するので、第1実施例における符号(接合部110、導電接合部111、導電接続部111a、電極パッド131、絶縁接合部112)を用いて説明する。

【0073】

C1.接合層:

接合層110の導電接合部111は、導電接続部111aと電極パッド131とが接合を開始する温度である第1の接合開始温度を有する。第1の接合開始温度とは、導電接続部111aもしくは電極パッド131を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上の温度である。焼結開始温度とは、導電接続部111aまたは電極パッド131を構成する成分の少なくとも一部による液相の形成、もしくは、固相での接着界面の反応による焼結反応の開始温度である。第1の接合開始温度を焼結開始温度以上とした理由は次の通りである。すなわち、導電接合部111が溶融していなくとも、ごく一部の成分の液相発生によって、焼結固着が進行し、部材間の接合が開始されるからである。

【0074】

第3実施例では、導電接続部111aは錫によって形成され、電極パッド131は、銅、錫を材料として形成されているので、導電接続部111aおよび電極パッド131が溶融、軟化して拡散接合が進行する温度、例えば、300℃を第1の接合開始温度とする。

【0075】

絶縁接合部112は、絶縁接合部112とセラミックス多層基板100および半導体素子130とが接合を開始する温度であって、第1の接合開始温度より高い第2の接合開始温度を有する。第2の接合開始温度とは、絶縁接合部112を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上の温度である。絶縁接合部112を構成する材料の少なくとも一部が焼結反応を開始する温度とは、絶縁接合部112を構成する成分の少なくとも一部による液相の形成、もしくは、固相での接着界面の反応による焼結反応の開始温度である。第2の接合開始温度を焼結開始温度以上とした理由は次の通りである。すなわち、絶縁接合部112が溶融していなくとも、ごく一部の成分の液相発生によって、焼結固着が進行し、他の部材との接合が開始されるからである。

【0076】

第3実施例では、絶縁接合部112は、Bi2O3とB2O3とからなる粉末ガラス(軟化点:357℃)によって形成されているので、第1の接合開始温度(300℃)より高く、絶縁接合部112が軟化して拡散接合が十分に進行する温度、例えば、450℃を第2の接合開始温度とする。

【0077】

C2.製造工程

第3実施例では、多段階の温度変化を有する温度プロファイルを用いて、段階的な

接合工程を有する拡散接合処理によって、セラミックス多層基板100、接合層110および半導体素子130が接合される。半導体パワーモジュール10の製造工程の概略は、第1実施例において説明した図3と同様である。ただし、ステップS18における加熱圧着による拡散接合の工程が異なる。ステップS18における拡散接合工程について、以下に説明する。

【0078】

第3実施例においても、図3において説明したステップS16までの処理が行われると、セラミックス多層基板100、接合層110および半導体素子130を加熱圧着して拡散接合し、半導体パワーモジュールが製造される(ステップS18:図1)。第3実施例では、当該加熱圧着処理において、セラミックス多層基板100、接合層110および半導体素子130が加圧されるとともに、拡散接合時の加熱温度が多段階で変化されるように設定された温度プロファイルに基づき、加熱処理が行われる。温度プロファイルに基づき行われる加熱処理を含む拡散接合処理は、第1の接合開始温度で加熱温度を所定時間保持した後(第1接合工程)、第2の接合開始温度で加熱温度を所定時間保持すること(第2接合工程)を含む。また、第3実施例では、半導体素子130の裏面の面積よりも若干小さい面積を有する押し当て治具により、半導体素子130がセラミックス多層基板100に押しつけられるように加圧される。第1、第2接合工程は、具体的には以下の通りである。

【0079】

まず、第1接合工程において、第1の接合開始温度(300℃)を所定時間(例えば、約10分)保持しつつ加熱処理が行われ、導電接続部111aと電極パッド131との間で生じる拡散接合が進行し、導電接合部111が形成される。絶縁接合部112の軟化点(357℃)は、第1の接合開始温度よりも高いので、第1接合工程では、絶縁接合部112は軟化していないので、絶縁接合部112を構成する材料が導電接続部111aと電極パッド131の間に侵入することはなく、導電接続部111aと電極パッド131が拡散接合して形成された導電接合部111に絶縁接合部112を構成する材料が混入することはない。

【0080】

導電接続部111aと電極パッド131との拡散接合が十分に進行し、導電接続部111aと電極パッド131との一体化が保障されると、第2接合工程が行われる。第2接合工程において、第2の接合開始温度(450℃)で加熱処理が行われる。加熱処理により、絶縁接合部112、セラミックス多層基板100の第1の面105および絶縁保護膜よりなる半導体素子130の表面が十分に溶融・軟化する。軟化した絶縁接合部112は、半導体素子130がセラミックス多層基板100に密着するように印加される押し当て治具の加圧力により、半導体素子130と接合層110との間に存在する空隙、および、接合層110とセラミックス多層基板100との間に存在する空隙を充填するように変形しながら拡散接合が進行する。この結果、セラミックス多層基板100と絶縁接合部112の間、および、絶縁接合部112と半導体素子130の表面との間では、空隙の存在しない均一な平面で拡散接合される。以上説明したように、半導体パワーモジュール10が製造される。

【0081】

以上説明した第3実施例の半導体パワーモジュールによれば、導電接合部の形成時に、絶縁接合部が焼結反応を開始する温度よりも低い第1の接合開始温度で加熱されるので、絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接続部111aと半導体素子の電極パッド131、および、導電接合部111とセラミックス多層基板100が接合された状態、すなわち、導電接続部111aと半導体素子の電極パッド131の間、および、導電接合部111とセラミックス多層基板100の間に空隙が存在しない状態で、絶縁接合部112の軟化変形が開始し、絶縁接合部112と半導体素子130、および、絶縁接合部112とセラミックス多層基板100との接合が行われる。よって、絶縁接合部112を構成する材料が、導電接続部111aと電極パッド131との間へ侵入すること、導電接合部111に混入することによる、導電接合部111の導電性能の低下を抑制できる。

【0082】

また、第3実施例の半導体パワーモジュールによれば、第1の接合開始温度は、導電接合部を構成する材料の溶融開始温度であり、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度とされている。従って、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0083】

D.変形例:

D1.変形例1:

図9は、変形例における半導体パワーモジュール40を示す断面図である。図9に示すように、変形例1の半導体パワーモジュール40は、第1実施例の半導体パワーモジュール10と同様に、セラミックス多層基板400と、接合層410と、拡散層420を備える。拡散層420は、導電拡散部421と絶縁拡散部422を備える。変形例1において、セラミックス多層基板400、拡散層420、導電拡散部421,絶縁拡散部422および半導体素子430は、それぞれ、第1実施例のセラミックス多層基板100、拡散層120、導電拡散部121、絶縁拡散部122および半導体素子130と同様の構成を備える。

【0084】

変形例1の半導体パワーモジュール40は、第1実施例の半導体パワーモジュール10と、接合層410の構成が異なる。接合層410は、平面状の薄膜であり、導電接続部411aと、半導体素子430の電極パッド431とからなる導電接合部411と、絶縁接合部412とを備える。絶縁接合部412は、図9の円Bに示すように、セラミックス多層基板400側の面の面積よりも半導体素子430側の面の面積が広いテーパ形状に形成されている。導電接続部411aは、絶縁接合部412のテーパ形状に対応する形状となるように形成されている。なお、絶縁接合部412は、テーパ形状に限られず、セラミックス多層基板400側の面の面積よりも半導体素子430側の面の面積が広い形状であればよい。例えば、階段形状や湾曲形状でもよい。

【0085】

半導体パワーモジュール40は、接合層410の配置工程(図3のステップS12、S14に対応)を除き、第1実施例の半導体パワーモジュール10と同様の方法により製造できる。変形例1の接合層410の配置工程は、例えば、以下の方法を用いて配置してもよい。

【0086】

導電接続部411aより先に絶縁接合部412をスクリーン印刷により配置する。この際、半導体素子430側の面積が広いテーパ形状となる開口部を有するスクリーンを用い、絶縁接合部412の材料であるガラス粉末のペーストを印刷する。

【0087】

次に、導電接続部411aに対応する部位に開口部を有するスクリーンを用いて、導電接続部411aの材料となる金属種を主成分とするペーストを印刷する。この時用いるペーストの粘度を調整し、半導体素子430へペースト塗布後にペースト自重により、開口部表面よりも半導体素子430側の広い面積に対しペーストが塗り広げられる。こうすることにより、テーパ形状の絶縁接合部412と、絶縁接合部412のテーパ形状に対応する形状を有する導電接続部411aを備える接合部が作成される。導電接続部411aと絶縁接合部412とから形成される窪みに半導体素子430の電極パッド431が嵌りこむように半導体素子430が配置されることにより、平面状の接合層410が形成される。

【0088】

変形例1によれば、接合層410の絶縁接合部412は、セラミックス多層基板100側の面の面積よりも半導体素子430側の面の面積が広いテーパ形状に形成されているので、第1実施例の絶縁接合部112に比して、絶縁接合部412と半導体素子430との接触面積が広い。従って、第1実施例の半導体パワーモジュール10に比して、半導体素子430から接合層410への熱拡散性能が高くなる。よって、セラミックス多層基板400と半導体素子430との絶縁性能を確保しつつ、熱拡散性能を向上でき、半導体素子430の放熱を促進できる。

【0089】

D2.変形例2:

第1実施例における、半導体パワーモジュール10の製造方法(図3)に変えて、以下の方法によって、半導体パワーモジュール10を製造してもよい。以下に、ステップS10に続く処理を説明する。なお、各部材の符号は、第1実施例の符号を用いる。

【0090】

絶縁接合部112を形成する。具体的には、粉末ガラスと熱分解性の有機結着剤(例えば80℃程度の温度で軟化し、250℃程度の温度で熱分解するブチラール系バインダ)とを、有機溶媒や水などの溶媒を用いて混練してスラリーを形成し、スラリーを、ドクターブレード法によるシートキャスティング、押し出し成型などの手法により、シート形状に成型する。シートの、導電接合部111に対応する部位に、レーザーまたはマイコンパンチなどの機械加工により貫通孔を形成する。このように、絶縁接合部112は、貫通孔が形成されたガラスシートとして作製される。

【0091】

絶縁接合部112の所望の面に、セラミックス多層基板100の第1の面105が対向するように、セラミックス多層基板100を配置し、両者を絶縁接合部シートに含まれる有機結着材の軟化温度以上に加熱、加圧することでシート状に形成された絶縁接合部112に含まれる有機結着材の結合力により仮接着させる。

【0092】

次に、導電接続部111aを形成する。具体的には、上記作製された絶縁接合部112の貫通孔に、導電接続部111aを形成するペーストをスクリーン印刷により充填する。ペーストは、金属を主成分としており、例えば、アルミニウム金属や酸化銀、銅、ナノ金属、ハンダ合金のような、図3のステップS18における加熱工程により溶融する金属種と、熱分解性の有機結着剤とを、有機溶媒や水などの溶媒を用いて混練することにより形成される。なお、ペーストの充填には、スクリーン印刷に限られず、例えば、ディスペンサーによる吐出などの方法を用いてもよい。

【0093】

以上の通り積層されたセラミックス多層基板100、導電接続部111a、絶縁接合部112に対し、半導体素子130を絶縁接合部112および導電接続部111aを構成する主成分であるガラス、金属の融点以上の温度に加熱の上、加圧接合して、絶縁接合部112に含まれる有機結着材成分を熱分解により除去した上で、拡散層120が形成された半導体パワーモジュール10を製造する(図1のステップS18)。

【0094】

以上説明した製造方法によっても、平面状の接合層110を作製できる。従って、半導体素子130と接合層110、接合層110とセラミックス多層基板100とを面で接合することができ、半導体素子130からセラミックス多層基板100への熱伝導性能、および、セラミックス多層基板100と半導体素子130との接合強度を向上することができる。

【0095】

D3.変形例3:

第1実施例では、セラミックス多層基板100と接合層110を予め有機結着材の接合力により仮積層した上で半導体素子130を積層して、加圧および加熱を行い接合しているが、例えば、シート状に形成された絶縁接合部112に形成された空孔を導電接続部111aで予め穴埋めして形成されたシートを作製し、セラミックス多層基板100と半導体素子130で矜持した上で加熱、圧着する事で、半導体パワーモジュール10を作製してもよい。こうすれば、接合層110に含まれる有機結着材の添加量を減少させる事が可能となり、有機残渣による接合層110の劣化などを防ぐ事ができる。

【0096】

D4.変形例4:

第1実施例では、第1の接合開始温度として、導電接合部111を構成する材料が十分に融解する温度を用い、第2の接合開始温度として、絶縁接合部112を構成する材料が十分に軟化する温度を用いているが、それぞれ、構成材料の少なくとも一部が焼結反応を開始する温度以上であればよい。こうすれば、導電接合部111、絶縁接合部112の各々について、融点まで加熱することなく他部材との接合を行うことができる。よって、製造工程の低温化を図ることができる。例えば、絶縁接合部112がNa2O3とB2O3とSiO2とからなる粉末ガラスから構成されている場合、第2の接合開始温度は、当該粉末ガラスの焼結反応の開始温度である495℃以上であればよい。

【0097】

以上、本発明の種々の実施例について説明したが、本発明はこれらの実施例に限定されず、その趣旨を逸脱しない範囲で種々の構成をとることができる。

【符号の説明】

【0098】

10、30、40…半導体パワーモジュール

100…セラミックス多層基板

101…内層ビアホール

104…電極端子

109…配線パターン

110…接合層

110a…接合部

111…導電接合部

111a…導電接続部

112…絶縁接合部

120…拡散層

121…導電拡散部

122…絶縁拡散部

130…半導体素子

131…電極パッド

202…スクリーン

203…スキージ

204…スキージホルダー

250…ガラス粉末ペースト

300…セラミックス多層基板

310…接合層

320…拡散層

330…半導体素子

400…セラミックス多層基板

410…接合層

411…導電接合部

412…絶縁接合部

420…拡散層

430…半導体素子

【技術分野】

【0001】

本発明は、多層基板により構成される回路基板、回路基板に半導体素子が搭載された半導体パワーモジュール、および、それらの製造方法に関する。

【背景技術】

【0002】

近年パワーモジュールパッケージにおいては小型、低背、高密度実装化が進み、その実現のために、従来のワイヤーボンドによる実装方式から、セラミックス多層基板等を用いて半導体素子をフリップチップ接続する実装方式を用いた半導体モジュールが提案されている。フリップチップ接続とは、半導体素子上にバンプと呼ばれる導電性の突起を配置し、セラミックス多層基板上の半導体素子を搭載する位置に、バンプを合わせて、セラミックス多層基板に直接接合する接合方法であり、半導体素子の実装に必要な面積を20〜30%程度減らす事ができ、高密度実装に寄与する事ができる。

【0003】

このようなフリップチップ実装方式を用いた半導体モジュールには、セラミックス多層基板と半導体素子との間のバンプ間の空隙に、従来の有機材料を封止材として用いたものに加えて、無機系材料が充填されたものがある(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−253579号公報

【特許文献2】特開2006−066582号公報

【特許文献3】特開2010−287869号公報

【特許文献4】特開2009−170930号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

フリップチップ実装により更に高密度実装化が進む半導体素子パワーモジュールにおいては、放熱面積の低下によりサイズ効果による放熱特性が劣化するため、半導体素子からセラミック多層基板への更なる熱拡散性能の向上が必要である。しかしながら、従来の半導体素子パワーモジュールでは、封止材充填工程における気泡の発生や、使用時の熱応力に起因する接合部分へのクラックの発生などによりセラミックス多層基板と半導体素子との間に空間が発生し、空気が入り込むなどの問題がある。そのため、従来の半導体素子パワーモジュールでは、半導体素子からセラミックス多層基板への熱拡散性能の低下による半導体素子の放熱性能の低下、および、セラミックス多層基板と半導体素子との間の接合強度の低下を招くおそれがある。

【0006】

本発明は上述の課題に鑑みてなされたものであり、半導体素子からセラミックス多層基板への熱拡散性能の向上、および、セラミックス多層基板と半導体素子との接合強度の向上を目的とする。

【課題を解決するための手段】

【0007】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は適用例として実現することが可能である。

【0008】

[適用例1]

半導体パワーモジュールであって、ビアおよび配線パターンが形成された多層基板と、前記多層基板の第1の面側に配置される半導体素子と、前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置されている平面状の導電接合部であって、前記半導体素子に形成されている電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする平面状の絶縁接合部と、 を有する半導体パワーモジュール。

【0009】

適用例1の半導体パワーモジュールによれば、接合層が平面状に形成されているので、多層基板と半導体素子との接合時に、多層基板と半導体素子との間における空隙の発生を抑制できる。従って、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0010】

[適用例2]

適用例1記載の半導体パワーモジュールであって、前記多層基板と前記接合層および前記半導体素子と前記接合層とは、拡散接合により接合され、前記半導体パワーモジュールは、更に、前記多層基板と前記接合層および前記半導体素子と前記接合層との間に、前記拡散接合時に形成される拡散層を備える、半導体パワーモジュール。

【0011】

適用例2の半導体パワーモジュールによれば、多層基板と接合層、および、接合層と半導体素子との拡散接合時に、多層基板と接合層の接合面、および、接合層と半導体素子との接合面で発生する原子の拡散により拡散層が形成される。従って、多層基板と接合層、および、接合層と半導体素子との接合強度を向上できる。

【0012】

[適用例3]

適用例1記載の半導体パワーモジュールであって、前記絶縁接合部には、金属フィラーもしくは無機系フィラーが含まれる、半導体パワーモジュール。

【0013】

適用例1の半導体パワーモジュールによれば、絶縁接合部に金属フィラーもしくは無機系フィラーが含まれるので、半導体素子から多層基板への熱拡散性能を向上できる。

【0014】

[適用例4]

適用例2記載の半導体パワーモジュールであって、

前記絶縁接合部および前記拡散層には、金属フィラーもしくは無機系フィラーが含まれる、

半導体パワーモジュール。

【0015】

適用例4の半導体パワーモジュールによれば、絶縁接合部および拡散層に金属フィラーもしくは無機系フィラーが含まれるので、半導体素子から多層基板への熱拡散性能を向上できる。

【0016】

[適用例5]

適用例1ないし適用例4いずれか記載の半導体パワーモジュールであって、前記導電接合部を構成する材料の接合開始温度である第1の接合開始温度は、前記絶縁接合部を構成する材料の接合開始温度である第2の接合開始温度よりも低いことを特徴とする、半導体パワーモジュール。

【0017】

適用例5の半導体パワーモジュールによれば、絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接続部と半導体素子の電極パッド、および、導電接合部と配線基板とが接合された状態、すなわち、導電接続部と半導体素子の電極パッドの間、および、導電接合部と配線基板の間に空隙が存在しない状態で、絶縁接合部の軟化変形が開始され、絶縁接合部と半導体素子、および、絶縁接合部と配線基板との接合が行われる。よって、絶縁接合部を構成する材料が、導電接続部と電極パッドの間へ侵入すること、導電接合部に混入することによる、導電接合部の導電性能の低下を抑制できる。

【0018】

[適用例6]

適用例5記載の半導体パワーモジュールにおいて、前記第1の接合開始温度は、前記導電接合部が焼結反応を開始する焼結開始温度以上であり、前記第2の接合開始温度は、前記絶縁接合部が焼結反応を開始する焼結開始温度以上であることを特徴とする、半導体パワーモジュール。

【0019】

適用例6の半導体パワーモジュールによれば、第1の接合開始温度は、導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされ、第2の接合開始温度は、絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされている。従って、導電接合部、絶縁接合部の各々について、融点まで加熱することなく他部材との接合を行うことができる。また、第1の接合開始温度を、導電接合部を構成する材料の溶融開始温度とし、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度としてもよい。こうすれば、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0020】

[適用例7]

回路基板であって、ビアおよび配線パターンが形成された多層基板と、前記多層基板の第1の面上に配置され、前記多層基板に半導体素子を接合するための接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置され、前記配線パターンと前記半導体素子と導通し、少なくとも前記第1の面側が平面状に形成されている導電接続部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とし、少なくとも前記第1の面側が平面状に形成されている絶縁接合部と、を有する回路基板。

【0021】

適用例7の回路基板によれば、半導体素子と多層基板とが平面で接合されるので、多層基板と半導体素子との間における空隙の発生を抑制できる。従って、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0022】

[適用例8]

適用例7記載の回路基板であって、前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度である第1の接合開始温度は、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度である第2の接合開始温度よりも低いことを特徴とする、回路基板。

【0023】

適用例8の半導体パワーモジュールによれば、絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接合部と半導体素子の電極パッド、および、導電接合部と配線基板が接合された状態、すなわち、導電接合部と半導体素子の電極パッドの間、および、導電接合部と配線基板の間に空隙が存在しない状態で、絶縁接合部の軟化変形が開始され、絶縁接合部と半導体素子、および、絶縁接合部と配線基板との接合が行われる。よって、絶縁接合部を構成する材料が導電接続部と電極パッドの間へ侵入すること、導電接合部に混入することによる、導電接合部の導電性能の低下を抑制できる。

【0024】

[適用例9]

適用例8記載の回路基板おいて、前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、回路基板。

【0025】

適用例9の半導体パワーモジュールによれば、第1の接合開始温度は、導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされ、第2の接合開始温度は、絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされている。従って、導電接合部、絶縁接合部の各々について、融点まで加熱することなく他部材との接合を行うことができる。また、第1の接合開始温度を、導電接合部を構成する材料の溶融開始温度とし、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度としてもよい。こうすれば、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0026】

[適用例10]

半導体パワーモジュールであって、ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面側に配置される半導体素子と、前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置され、前記半導体素子の電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、を有し、前記電極パッドと前記導電接続部とが導通可能となるように、前記半導体素子が前記接合層上に積層され、前記多層基板、前記接合層および前記半導体素子が接合された状態で、前記多層基板と前記接合層との界面、および、前記接合層と前記半導体素子との界面の、積層方向の断面が、略直線状に形成されている、半導体パワーモジュール。

【0027】

適用例10の半導体パワーモジュールによれば、多層基板と接合層との接合界面、および、接合層と半導体素子との接合界面の、積層方向の断面が、略直線状となるように形成されている。略直線状とは、本明細書では、多層基板と接合層との接合界面、および、接合層と半導体素子との接合界面に、気泡等による空隙が存在しない状態を含む。従って、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0028】

[適用例11]

回路基板であって、ビアおよび配線パターンが形成された多層基板と、前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、を備え、前記接合層は、前記ビアに対応する第1の部位に配置され、前記配線パターンに前記半導体素子を導通させるための導電接続部と、前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、を有し、前記多層基板と前記接合層が接着された状態で、前記多層基板と前記接合層との界面の、積層方向の断面は、略直線状である、回路基板。

【0029】

適用例11の回路基板によれば、多層基板と接合層との接合界面は、積層方向の断面が、略直線状となるように形成されている。従って、多層基板と接合層との接合強度を向上することができ、半導体素子から多層基板への熱拡散性能を向上できる。

【0030】

[適用例12]

半導体パワーモジュールの製造方法であって、ビアおよび配線パターンを有する多層基板を製作し、前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する平面状の導電接続部を有し、前記第1の部位とは異なる第2の部位に平面状の絶縁接合部を有する接合部を、前記多層基板の第1の面上に配置し、前記接合部上に、前記半導体素子を、前記半導体素子に形成されている電極パッドと前記導電接続部とが導通可能となるように配置し、前記多層基板、前記接合部および前記半導体素子を、加熱圧着し、前記多層基板と前記接合層、および、前記接合層と前記半導体素子を拡散接合する、半導体パワーモジュールの製造方法。

【0031】

適用例12の半導体パワーモジュールの製造方法によれば、多層基板と半導体素子との間に、接合部と電極パッドにより、多層基板と半導体素子とを接合するための平面状の接合層が形成される。従って、多層基板と半導体素子との間における空隙の発生を抑制できる。よって、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上できる。

【0032】

[適用例13]

適用例12記載の半導体パワーモジュールの製造方法であって、前記拡散接合において、 前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度を第1の接合開始温度とし、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、前記多層基板、前記接合部および前記半導体素子を、前記第1の接合開始温度で加熱圧着することにより、前記導電接合部と前記半導体素子の前記電極パッド、および、前記導電接合部と前記配線基板とを接合し、前記導電接合部と前記半導体素子の前記電極パッドとの接合後に、前記多層基板、前記接合部および前記半導体素子を、前記第2の接合開始温度で加熱圧着することにより、前記多層基板と前記絶縁接合部、および、前記絶縁接合部と前記半導体素子とを接合する、半導体パワーモジュールの製造方法。

【0033】

適用例13の半導体パワーモジュールの製造方法によれば、 絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接合部と半導体素子の電極パッド、および、導電接合部と配線基板が接合された状態、すなわち、導電接合部と半導体素子の電極パッドの間、および、導電接合部と配線基板の間に空隙が存在しない状態で、絶縁接合部の軟化変形が開始され、絶縁接合部と半導体素子、および、絶縁接合部と配線基板との接合が行われる。よって、絶縁接合部を構成する材料が、導電接続部と電極パッドの間へ侵入すること、導電接合部に混入することによる、導電接合部の導電性能の低下を抑制できる。

【0034】

[適用例14]

適用例13記載の半導体パワーモジュールの製造方法において、前記第1の接合開始温度は、前記導電接続部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、前記第2の接合開始温度は、前記絶縁接続部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、半導体パワーモジュールの製造方法。

【0035】

適用例14の半導体パワーモジュールの製造方法によれば、第1の接合開始温度は、導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされ、第2の接合開始温度は、絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度以上とされている。従って、導電接合部、絶縁接合部の各々について、融点まで加熱することなく他部材との接合を行うことができる。また、第1の接合開始温度を、導電接合部を構成する材料の溶融開始温度とし、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度としてもよい。こうすれば、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0036】

[適用例15]

適用例12記載の半導体パワーモジュールの製造方法であって、前記拡散接合において、 前記導電接続部を構成する材料と前記電極パッドを構成する材料とが接合を開始する温度を第1の接合開始温度とし、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、前記第1の接合開始温度が、所定時間保持された後、前記第2の接合開始温度が所定時間保持されるように設定されている温度プロファイルに基づき、前記加熱を行う、半導体パワーモジュールの製造方法。

【0037】

適用例15の半導体パワーモジュールの製造方法によれば、段階的な温度変化を有する温度プロファイルに基づいて、接合部、配線基板および半導体素子の接合が行われる。従って、簡易な構成で、多段階の温度変化を行いつつ拡散接合を行うことができ、製造効率を向上できる。

【0038】

[適用例16]

回路基板の製造方法であって、ビアおよび配線パターンを有する多層基板を製作し、前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する導電接続部を有し、前記第1の部位とは異なる第2の部位に絶縁接合部を有し、少なくとも、前記第1の面側が平面状に形成されている接合層を、前記多層基板の第1の面上に配置し、前記多層基板と前記接合層とを、前記接合層に含まれる有機成分の粘着力により接着する、回路基板の製造方法。

【0039】

適用例16の回路基板の製造方法によれば、多層基板の第1の面側が平面状に形成された、多層基板と半導体素子とを接合するための接合層が、多層基板の第1の面上に形成される。従って、多層基板と接合層との間における空隙の発生を抑制できる。よって、半導体素子から多層基板への熱拡散性能、および、多層基板と半導体素子との接合強度を向上することができる。

【0040】

本発明において、上述した種々の態様は、適宜、組み合わせたり、一部を省略したりして適用することができる。

【図面の簡単な説明】

【0041】

【図1】第1実施例における半導体パワーモジュール10の概略構成を示す断面図。

【図2】第1実施例における回路基板20について説明する説明図。

【図3】第1実施例における半導体パワーモジュール10の製造方法を説明する工程図。

【図4】ステップS12における導電接続部111aの配置工程を説明する説明図。

【図5】ステップS14における絶縁接合部112のスクリーン印刷について説明する説明図。

【図6】第1実施例における半導体パワーモジュール10の接合工程を説明する説明図。

【図7】第2実施例における半導体パワーモジュール30を示す平面図。

【図8】第2実施例における半導体パワーモジュール30を示す断面図。

【図9】変形例における半導体パワーモジュール40を示す断面図。

【発明を実施するための形態】

【0042】

A.第1実施例:

A1.半導体パワーモジュールの概略構成:

図1は、第1実施例における半導体パワーモジュール10の概略構成を示す断面図である。図2は、第1実施例における回路基板20について説明する説明図である。半導体パワーモジュール10は、回路基板20と、半導体素子130とを備える。回路基板20は、セラミックス多層基板100と、接合層110と、拡散層120とを備える。

【0043】

セラミックス多層基板100は、セラミックス材料により形成されている。セラミックス材料としては、例えば、酸化アルミナ(Al2O3)、窒化アルミニウム(AlN)、窒化珪素(Si3N4)などが用いられる。セラミックス多層基板100は、半導体素子が実装される第1の面105と、該面と対向し、制御回路やコンデンサなどのその他の電子部品が搭載され得るもう一方の第2の面106間を電気的に接続するための内層ビアホール101と、配線パターン109と、第2の面106上に配置された外部接続用の電極端子104を備える。配線パターン109は、セラミックス多層基板100の表面、内部の層の表面に形成されている。図1では、セラミックス多層基板100の表面に形成された配線パターンは省略されている。また、セラミックス多層基板100の第1の面105上、および第2の面106上には、半導体素子130やその他の電子部品を搭載するための電極ランド(図示省略)が形成されている。半導体素子130は、内層ビアホール101および配線パターン109を介して、第2の面106上に配置されている電極端子104と電気的に接続されている。

【0044】

接合層110は、セラミックス多層基板100の第1の面105上に配置され、導電接合部111と、絶縁接合部112とを備える平面状の薄膜層である。

【0045】

導電接合部111は、導電接続部111aと半導体素子130の電極パッド131とから構成され、半導体素子130とセラミックス多層基板100とを電気的に接続する。導電接続部111aは、導電性の金属を主成分として形成されており、図2に示すように、セラミックス多層基板100の第1の面105上であって、内層ビアホール101に対応する第1の部位107(太実線で示す)上に配置されている。導電性の金属として、例えば、銅、銀、アルミニウム金属などを用いてもよい。導電接続部111aは、後述する絶縁接合部112よりも薄く形成されており、絶縁接合部112と導電接続部111aとにより窪みが形成される。該窪みに、電極パッド131が嵌りこむように配置されることによって、導電接合部111が形成される。

【0046】

絶縁接合部112は、半導体素子130とセラミックス多層基板100とを絶縁する。絶縁接合部112は、図2に示すように、セラミックス多層基板100の第1の面105上であって、第1の部位107とは異なる第2の部位108(太破線で示す)に配置されている。絶縁性の無機系材料を主成分とし、半導体素子の実装時の加熱工程により軟化する粉末ガラスにより形成されている。粉末ガラスは、例えば、ZnO−B2O3−SiO2、など、酸化ケイ素、酸化亜鉛、酸化ホウ素、酸化ビスマスなどの混相として形成される。

【0047】

第1実施例において、第2の部位108とは、第1の部位107である導電接合部111が配置されている部位を除く部分を含む。接合層110が均一な平面となるように、導電接合部111と絶縁接合部112は、ほぼ同一の厚みを有している。また、接合層110の、半導体素子130側に対向する面も、均一な平面となるように形成されている。

【0048】

なお、本実施例において、均一な平面とは、微少な湾曲や凹凸を含んでおり、接合層110が均一な平面を有しているとは、接合層110の、セラミック多層基板の第1の面105に対向する面が、第1の面105の形状に沿って形成され、導電接合部111と絶縁接合部112が連続して平坦に形成されていること、および、接合層110の、半導体素子130側に対向する面が、半導体素子130の、接合層110に対向する面の形状に沿って形成されていること、を含む。

【0049】

絶縁接合部112は、絶縁性能が低下しない程度に、フィラー115を含むことが望ましい。ここで、フィラー115は、銅やアルミニウム粉末などよりなる金属フィラーもしくは無機系フィラーを含む。無機系フィラーとしては酸化ホウ素やアルミナ、窒化珪素、窒化アルミニウムなどよりなるセラミックスなどの、高放熱特性フィラーであることが望ましい。フィラー115が含有されていることにより、絶縁接合部112の伝熱性能が向上する。

【0050】

拡散層120は、セラミックス多層基板100と接合層110との拡散接合により形成される層である。拡散層120は、導電拡散部121と絶縁拡散部122を備える。導電拡散部121は、セラミックス多層基板100と接合層110の導電接続部111aとの拡散接合により形成される。絶縁拡散部122は、セラミックス多層基板100と、接合層110の絶縁接合部112との拡散接合により形成される。絶縁拡散部122には、絶縁接合部112と同様に、フィラー115が含有されてもよい。なお、図1では、説明の便宜上、導電拡散部121と絶縁拡散部122の境界は明確に記載されているが、導電拡散部121と絶縁拡散部122の境界は曖昧であってもよい。

【0051】

半導体素子130は、電極パッド131を備える。電極パッド131は、例えば、金(Au)を主成分として形成されている。半導体素子130は、電極パッド131が、接合層110の導電接続部111aに接するように、接合層110上に配置されている。半導体素子130は、電極パッド131および導電接続部111a(すなわち、導電接合部111)を介してセラミックス多層基板100と電気的に接続されている。

【0052】

A2.製造方法:

半導体パワーモジュール10の製造方法を、図3〜図6を用いて説明する。図3は、第1実施例における半導体パワーモジュール10の製造方法を説明する工程図である。

【0053】

内層ビアホール101および配線パターン109が形成されたセラミックス多層基板100を作製する(ステップS10)。セラミックス多層基板100の作製には、セラミックス多層基板100の表面に、半導体素子130および他の電子部品を実装するための薄膜状の電極ランドを形成することを含む。電極ランドは、導電ペーストを用いた印刷法、物理蒸着(PVD:Physical Vapor Deposition)や化学蒸着(CVD: Chemical Vapor Deposition)により形成される。

【0054】

セラミックス多層基板100の第1の面105上であって、内層ビアホール101に対応する第1の部位に、導電接続部111aを配置する(ステップS12)。図3は、ステップS12における導電接続部111aの配置工程を説明する説明図である。図3に示すように、後述するステップS18における加熱工程により溶融する金属種を主成分とする金属の突起を導電接続部111aとして形成する。この金属の突起はバンプとも呼ばれる。バンプは、所望の位置にボール状に形成された金属を配置し、加熱処理により柱状形状とするボール搭載法により形成しても良いし、セラミックス多層基板100の第1の面105の第1の部位107に、予め対応する位置にバンプとなる金属を転写する方法や導電接続部111aの材料として既述した金属種を主成分とするペーストを、スクリーン印刷により印刷する方法、セラミックス多層基板100の第1の面105の第1の部位107にフォトリソパターンによりマスキングを施しメッキ法により所望の位置に金属バンプを形成してもよい。

【0055】

導電接続部111aを配置したセラミックス多層基板100の第1の面105上の、第1の部位とは異なる第2の部位に絶縁接合部112を配置する(ステップS14)。具体的には、粉末ガラスと熱分解性の有機結着剤とを、有機溶媒や水などの溶媒を用いて混練してガラス粉末ペーストを生成し、ガラス粉末ペーストを、セラミックス多層基板100の第1の面105上の、導電接続部111aの空隙を埋めるようにスクリーン印刷によりに印刷する。

【0056】

図5は、ステップS14における絶縁接合部112のスクリーン印刷について説明する説明図である。スクリーン印刷機200は、スクリーン202と、スキージ203と、スキージホルダー204とを備える。スクリーン202には、導電接続部111aに対応する部位を除く部位、すなわち、絶縁接合部112に対応する部位にのみ開口部が形成されている。ガラス粉末ペースト250をスクリーン202に載せ、スクリーン202上からスキージ203を摺動させる。こうすることにより、ガラス粉末ペースト250は開口部を通過し、セラミックス多層基板100の第1の面105上の、導電接続部111aが配置されている部位を除いた部位、すなわち、絶縁接合部112が配置される部位に転写される。この結果、導電接続部111aと絶縁接合部112とからなり、セラミックス多層基板100の第1の面105側が平面上に形成された接合部110a(図2)が形成される。なお、ステップS12,S14の順序は、逆であってもよい。なお、接合部110aの結着に用いられる有機成分(有機結着剤)は、後述する加熱処理工程において、分解、除去される。

【0057】

形成された接合部110a上に、半導体素子130を配置する(ステップS16)。具体的には、導電接続部111aと絶縁接合部112とから形成される窪みに、電極パッド131を嵌め込むように半導体素子130を配置する。導電接続部111aと電極パッド131とが接触することにより、半導体素子130と導電接続部111aとの導通が確保される。

【0058】

セラミックス多層基板100、接合層110および半導体素子130を加熱圧着して、半導体パワーモジュールを製造する(ステップS18)。図6は、第1実施例における半導体パワーモジュール10の接合工程を説明する説明図である。図6に示すように、セラミックス多層基板100、接合層110および半導体素子130を、加圧するとともに、導電接続部111aと絶縁接合部112とが熱融着する温度に加熱する。こうすることにより、導電接続部111a、絶縁接合部112、セラミックス多層基板100の第1の面105および導電接合部111及び絶縁保護膜よりなる半導体素子130の表面が溶融し、セラミックス多層基板100と接合層110の間、および、接合層110と半導体素子130の間は、空隙の存在しない均一な平面で拡散接合される。導電接続部111aと絶縁接合部112とが熱融着する温度とは、例えば、導電接続部111aの材料として、融点660℃のアルミニウム金属を用い、絶縁接合部112の材料として軟化点640℃のZnO−B2O3−SiO2ガラスを用いた場合には、両材料が熱融着する温度670℃で加熱する。

【0059】

以上説明したように、少なくとも2段階の温度変化が行われるように設定されている温度プロファイルに基づいて、加圧および加熱を行うことにより、セラミックス多層基板100と接合層110との接合面で原子の拡散が生じ、拡散層120が形成され、セラミックス多層基板100と接合層110とは接合される。

【0060】

セラミックス多層基板100、接合層110、半導体素子130と直行する方向(セラミックス多層基板100、接合層110および半導体素子130の積層方向)に切断した切断面は、化合物半導体とその表面の保護層よりなる半導体素子130と接合層110との界面、ならびに接合層110とセラミックス成分(アルミナ、窒化珪素、窒化アルミニウムなど)よりなるセラミックス多層基板100の表面との界面が、図6に太実線で示すように、それぞれ略一直線状になるよう配置されており、気泡等の微少な欠陥を含まない。ミクロンオーダーの不可避なボイド等は、実施例における欠陥には含まれない。実施例において、欠陥と判断される気泡のサイズは、例えば、100μm以上としてもよい。

【0061】

また微視的に見た時、上記それぞれの界面は半導体素子130、セラミックス多層基板100に対して、それぞれ接合層110の構成成分が拡散して形成される拡散層120を持つ。これらの層はEDS、EPMA等によるマッピング分析により、それぞれ半導体素子130の表面成分(ZrやTiなどの保護膜の形成成分)、セラミックス多層基板100のセラミックス成分(アルミや窒素など)が混在する層が形成されている層と定義される。

【0062】

以上説明した第1実施例の半導体パワーモジュール10によれば、接合層110が平面状に形成されている、すなわち、接合層110の、セラミックス多層基板100に対する対向面は、セラミックス多層基板100の第1の面105の面形状に沿って平面状に形成されており、接合層110の、半導体素子130に対抗する面も、半導体素子130の接合層110側の面形状に沿って平面状に形成されている。従って、セラミックス多層基板100と半導体素子130との接合時に、セラミックス多層基板100と接合層110、接合層110と半導体素子130との間における空隙の発生を抑制できる。従って、半導体素子130からセラミックス多層基板100への熱拡散性能、および、セラミックス多層基板100と半導体素子130との接合強度を向上することができる。

【0063】

また、第1実施例のセラミックス多層基板100によれば、接合層110の絶縁接合部112は、有機系材料に比して熱伝導性能の高いガラス等の無機系材料を主成分として形成されているので、半導体素子130からセラミックス多層基板100への熱拡散性能を向上できる。

【0064】

半導体パワーモジュール10の接合時の加熱(図3のステップS18の工程)により、各部材は熱膨張し、セラミックス多層基板100と接合層110、接合層110と半導体素子130との間に応力が発生する。第1実施例では、絶縁接合部112の主成分であるガラス成分の線熱膨張係数は、導電接続部111aの主成分である金属の線熱膨張係数よりもセラミックス多層基板100や半導体素子130の線熱膨張係数に近い。このため、導電接続部111aとセラミックス多層基板100および半導体素子130との境界に生じる応力は、絶縁接合部112とセラミックス多層基板100および半導体素子130との境界に生じる応力よりも大きくなる。

【0065】

第1実施例の半導体パワーモジュール10によれば、導電接続部111aが絶縁接合部112の周囲に配置されているので、導電接続部111aの変形を、絶縁接合部112によって抑制できる。従って、導電接続部111aとセラミックス多層基板100および半導体素子130との間に生じる応力を、導電接続部111aと絶縁接合部112の界面に分散できる。よって、接合層110とセラミックス多層基板100および半導体素子130との間に集中して生じる応力を分散できるので、半導体パワーモジュール10の損傷を抑制でき、半導体パワーモジュール10の信頼性を向上できる。

【0066】

また、第1実施例の半導体パワーモジュール10によれば、セラミックス多層基板100と接合層110の拡散接合時に、セラミックス多層基板100と接合層110の間に、拡散層120が形成される。従って、セラミックス多層基板100と接合層110との接合強度を向上できる。

【0067】

また、第1実施例の半導体パワーモジュール10によれば、接合層110の絶縁接合部112および拡散層120の絶縁拡散部122に、伝熱性能、放熱性能を有するフィラー115が含まれるので、半導体素子130からセラミックス多層基板100への熱拡散性能を向上できる。

【0068】

B.第2実施例:

第1実施例では、半導体素子130が一つのみ搭載された半導体パワーモジュール10について説明した。第2実施例では、複数の半導体素子が搭載された半導体パワーモジュールについて、図7および図8を参照して説明する。

【0069】

B1.半導体パワーモジュール概略構成:

図7は、第2実施例における半導体パワーモジュール30を示す平面図である。図8は、第2実施例における半導体パワーモジュール30を示す断面図である。図8は、図7におけるA−A断面で切断した断面を示す。

【0070】

第2実施例の半導体パワーモジュール30は、図7および図8に示すように、セラミックス多層基板300と、接合層310と、拡散層320および複数(第2実施例では6個)の半導体素子330を備える。接合層310は、導電接続部311aと半導体素子330の電極パッド331とからなる導電接合部311と、絶縁接合部312とを備え、拡散層320は、導電拡散部321と絶縁拡散部322を備える。第2実施例において、セラミックス多層基板300、接合層310、導電接合部311、絶縁接合部312、拡散層320、導電拡散部321、絶縁拡散部322および各半導体素子330は、それぞれ、第1実施例のセラミックス多層基板100、接合層110、導電接合部111、絶縁接合部112、拡散層120、導電拡散部121、絶縁拡散部122および半導体素子130と同様の構成を備える。

【0071】

一般的に、従来のSi系半導体素子からSiC等の化合物半導体素子を用いる事による半導体素子の発熱許容量の増大に対応するために、半導体素子の周辺部材に対する高耐熱性、一方でモジュールとして放熱部品の小型化要求などへの対応のために高熱拡散性が求められている。第2実施例の半導体パワーモジュール30は、接合層310が平面状に形成されているので、半導体素子330とセラミックス多層基板300とは耐熱特性や熱拡散性が低い有機系材料を介さず、耐熱特性や熱拡散性に優れる無機系材料を主成分として形成された平面で接合される。従って、半導体素子330からセラミックス多層基板300への熱拡散性能が向上されるので、300℃以下程度の高温域で使用される化合物半導体素子(半導体素子330)を、高密度に複数搭載した信頼性の高い半導体パワーモジュール30を提供できる。

【0072】

C.第3実施例:

第3実施例では、導電接合部は、導電接続部と半導体素子の電極パッドとが接合を開始する温度である第1の接合開始温度を有し、絶縁接合部は、配線基板や半導体素子と接合を開始する温度であって、第1の接合開始温度よりも高い第2の接合開始温度を有する。なお、第3実施例において、接合層を構成する導電接合部、絶縁接合部は、接合開始温度以外は、第1実施例の各々と同様の作用・機能を有するので、第1実施例における符号(接合部110、導電接合部111、導電接続部111a、電極パッド131、絶縁接合部112)を用いて説明する。

【0073】

C1.接合層:

接合層110の導電接合部111は、導電接続部111aと電極パッド131とが接合を開始する温度である第1の接合開始温度を有する。第1の接合開始温度とは、導電接続部111aもしくは電極パッド131を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上の温度である。焼結開始温度とは、導電接続部111aまたは電極パッド131を構成する成分の少なくとも一部による液相の形成、もしくは、固相での接着界面の反応による焼結反応の開始温度である。第1の接合開始温度を焼結開始温度以上とした理由は次の通りである。すなわち、導電接合部111が溶融していなくとも、ごく一部の成分の液相発生によって、焼結固着が進行し、部材間の接合が開始されるからである。

【0074】

第3実施例では、導電接続部111aは錫によって形成され、電極パッド131は、銅、錫を材料として形成されているので、導電接続部111aおよび電極パッド131が溶融、軟化して拡散接合が進行する温度、例えば、300℃を第1の接合開始温度とする。

【0075】

絶縁接合部112は、絶縁接合部112とセラミックス多層基板100および半導体素子130とが接合を開始する温度であって、第1の接合開始温度より高い第2の接合開始温度を有する。第2の接合開始温度とは、絶縁接合部112を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上の温度である。絶縁接合部112を構成する材料の少なくとも一部が焼結反応を開始する温度とは、絶縁接合部112を構成する成分の少なくとも一部による液相の形成、もしくは、固相での接着界面の反応による焼結反応の開始温度である。第2の接合開始温度を焼結開始温度以上とした理由は次の通りである。すなわち、絶縁接合部112が溶融していなくとも、ごく一部の成分の液相発生によって、焼結固着が進行し、他の部材との接合が開始されるからである。

【0076】

第3実施例では、絶縁接合部112は、Bi2O3とB2O3とからなる粉末ガラス(軟化点:357℃)によって形成されているので、第1の接合開始温度(300℃)より高く、絶縁接合部112が軟化して拡散接合が十分に進行する温度、例えば、450℃を第2の接合開始温度とする。

【0077】

C2.製造工程

第3実施例では、多段階の温度変化を有する温度プロファイルを用いて、段階的な

接合工程を有する拡散接合処理によって、セラミックス多層基板100、接合層110および半導体素子130が接合される。半導体パワーモジュール10の製造工程の概略は、第1実施例において説明した図3と同様である。ただし、ステップS18における加熱圧着による拡散接合の工程が異なる。ステップS18における拡散接合工程について、以下に説明する。

【0078】

第3実施例においても、図3において説明したステップS16までの処理が行われると、セラミックス多層基板100、接合層110および半導体素子130を加熱圧着して拡散接合し、半導体パワーモジュールが製造される(ステップS18:図1)。第3実施例では、当該加熱圧着処理において、セラミックス多層基板100、接合層110および半導体素子130が加圧されるとともに、拡散接合時の加熱温度が多段階で変化されるように設定された温度プロファイルに基づき、加熱処理が行われる。温度プロファイルに基づき行われる加熱処理を含む拡散接合処理は、第1の接合開始温度で加熱温度を所定時間保持した後(第1接合工程)、第2の接合開始温度で加熱温度を所定時間保持すること(第2接合工程)を含む。また、第3実施例では、半導体素子130の裏面の面積よりも若干小さい面積を有する押し当て治具により、半導体素子130がセラミックス多層基板100に押しつけられるように加圧される。第1、第2接合工程は、具体的には以下の通りである。

【0079】

まず、第1接合工程において、第1の接合開始温度(300℃)を所定時間(例えば、約10分)保持しつつ加熱処理が行われ、導電接続部111aと電極パッド131との間で生じる拡散接合が進行し、導電接合部111が形成される。絶縁接合部112の軟化点(357℃)は、第1の接合開始温度よりも高いので、第1接合工程では、絶縁接合部112は軟化していないので、絶縁接合部112を構成する材料が導電接続部111aと電極パッド131の間に侵入することはなく、導電接続部111aと電極パッド131が拡散接合して形成された導電接合部111に絶縁接合部112を構成する材料が混入することはない。

【0080】

導電接続部111aと電極パッド131との拡散接合が十分に進行し、導電接続部111aと電極パッド131との一体化が保障されると、第2接合工程が行われる。第2接合工程において、第2の接合開始温度(450℃)で加熱処理が行われる。加熱処理により、絶縁接合部112、セラミックス多層基板100の第1の面105および絶縁保護膜よりなる半導体素子130の表面が十分に溶融・軟化する。軟化した絶縁接合部112は、半導体素子130がセラミックス多層基板100に密着するように印加される押し当て治具の加圧力により、半導体素子130と接合層110との間に存在する空隙、および、接合層110とセラミックス多層基板100との間に存在する空隙を充填するように変形しながら拡散接合が進行する。この結果、セラミックス多層基板100と絶縁接合部112の間、および、絶縁接合部112と半導体素子130の表面との間では、空隙の存在しない均一な平面で拡散接合される。以上説明したように、半導体パワーモジュール10が製造される。

【0081】

以上説明した第3実施例の半導体パワーモジュールによれば、導電接合部の形成時に、絶縁接合部が焼結反応を開始する温度よりも低い第1の接合開始温度で加熱されるので、絶縁接合部よりも先に導電接合部の接合が行われる。従って、導電接続部111aと半導体素子の電極パッド131、および、導電接合部111とセラミックス多層基板100が接合された状態、すなわち、導電接続部111aと半導体素子の電極パッド131の間、および、導電接合部111とセラミックス多層基板100の間に空隙が存在しない状態で、絶縁接合部112の軟化変形が開始し、絶縁接合部112と半導体素子130、および、絶縁接合部112とセラミックス多層基板100との接合が行われる。よって、絶縁接合部112を構成する材料が、導電接続部111aと電極パッド131との間へ侵入すること、導電接合部111に混入することによる、導電接合部111の導電性能の低下を抑制できる。

【0082】

また、第3実施例の半導体パワーモジュールによれば、第1の接合開始温度は、導電接合部を構成する材料の溶融開始温度であり、第2の接合開始温度は、絶縁接合部を構成する材料の溶融開始温度とされている。従って、導電接合部および絶縁接合部を確実に溶融させることができ、導電接合部および絶縁接合部の各々と他の部材との接合強度を向上できる。

【0083】

D.変形例:

D1.変形例1:

図9は、変形例における半導体パワーモジュール40を示す断面図である。図9に示すように、変形例1の半導体パワーモジュール40は、第1実施例の半導体パワーモジュール10と同様に、セラミックス多層基板400と、接合層410と、拡散層420を備える。拡散層420は、導電拡散部421と絶縁拡散部422を備える。変形例1において、セラミックス多層基板400、拡散層420、導電拡散部421,絶縁拡散部422および半導体素子430は、それぞれ、第1実施例のセラミックス多層基板100、拡散層120、導電拡散部121、絶縁拡散部122および半導体素子130と同様の構成を備える。

【0084】

変形例1の半導体パワーモジュール40は、第1実施例の半導体パワーモジュール10と、接合層410の構成が異なる。接合層410は、平面状の薄膜であり、導電接続部411aと、半導体素子430の電極パッド431とからなる導電接合部411と、絶縁接合部412とを備える。絶縁接合部412は、図9の円Bに示すように、セラミックス多層基板400側の面の面積よりも半導体素子430側の面の面積が広いテーパ形状に形成されている。導電接続部411aは、絶縁接合部412のテーパ形状に対応する形状となるように形成されている。なお、絶縁接合部412は、テーパ形状に限られず、セラミックス多層基板400側の面の面積よりも半導体素子430側の面の面積が広い形状であればよい。例えば、階段形状や湾曲形状でもよい。

【0085】

半導体パワーモジュール40は、接合層410の配置工程(図3のステップS12、S14に対応)を除き、第1実施例の半導体パワーモジュール10と同様の方法により製造できる。変形例1の接合層410の配置工程は、例えば、以下の方法を用いて配置してもよい。

【0086】

導電接続部411aより先に絶縁接合部412をスクリーン印刷により配置する。この際、半導体素子430側の面積が広いテーパ形状となる開口部を有するスクリーンを用い、絶縁接合部412の材料であるガラス粉末のペーストを印刷する。

【0087】

次に、導電接続部411aに対応する部位に開口部を有するスクリーンを用いて、導電接続部411aの材料となる金属種を主成分とするペーストを印刷する。この時用いるペーストの粘度を調整し、半導体素子430へペースト塗布後にペースト自重により、開口部表面よりも半導体素子430側の広い面積に対しペーストが塗り広げられる。こうすることにより、テーパ形状の絶縁接合部412と、絶縁接合部412のテーパ形状に対応する形状を有する導電接続部411aを備える接合部が作成される。導電接続部411aと絶縁接合部412とから形成される窪みに半導体素子430の電極パッド431が嵌りこむように半導体素子430が配置されることにより、平面状の接合層410が形成される。

【0088】

変形例1によれば、接合層410の絶縁接合部412は、セラミックス多層基板100側の面の面積よりも半導体素子430側の面の面積が広いテーパ形状に形成されているので、第1実施例の絶縁接合部112に比して、絶縁接合部412と半導体素子430との接触面積が広い。従って、第1実施例の半導体パワーモジュール10に比して、半導体素子430から接合層410への熱拡散性能が高くなる。よって、セラミックス多層基板400と半導体素子430との絶縁性能を確保しつつ、熱拡散性能を向上でき、半導体素子430の放熱を促進できる。

【0089】

D2.変形例2:

第1実施例における、半導体パワーモジュール10の製造方法(図3)に変えて、以下の方法によって、半導体パワーモジュール10を製造してもよい。以下に、ステップS10に続く処理を説明する。なお、各部材の符号は、第1実施例の符号を用いる。

【0090】

絶縁接合部112を形成する。具体的には、粉末ガラスと熱分解性の有機結着剤(例えば80℃程度の温度で軟化し、250℃程度の温度で熱分解するブチラール系バインダ)とを、有機溶媒や水などの溶媒を用いて混練してスラリーを形成し、スラリーを、ドクターブレード法によるシートキャスティング、押し出し成型などの手法により、シート形状に成型する。シートの、導電接合部111に対応する部位に、レーザーまたはマイコンパンチなどの機械加工により貫通孔を形成する。このように、絶縁接合部112は、貫通孔が形成されたガラスシートとして作製される。

【0091】

絶縁接合部112の所望の面に、セラミックス多層基板100の第1の面105が対向するように、セラミックス多層基板100を配置し、両者を絶縁接合部シートに含まれる有機結着材の軟化温度以上に加熱、加圧することでシート状に形成された絶縁接合部112に含まれる有機結着材の結合力により仮接着させる。

【0092】

次に、導電接続部111aを形成する。具体的には、上記作製された絶縁接合部112の貫通孔に、導電接続部111aを形成するペーストをスクリーン印刷により充填する。ペーストは、金属を主成分としており、例えば、アルミニウム金属や酸化銀、銅、ナノ金属、ハンダ合金のような、図3のステップS18における加熱工程により溶融する金属種と、熱分解性の有機結着剤とを、有機溶媒や水などの溶媒を用いて混練することにより形成される。なお、ペーストの充填には、スクリーン印刷に限られず、例えば、ディスペンサーによる吐出などの方法を用いてもよい。

【0093】

以上の通り積層されたセラミックス多層基板100、導電接続部111a、絶縁接合部112に対し、半導体素子130を絶縁接合部112および導電接続部111aを構成する主成分であるガラス、金属の融点以上の温度に加熱の上、加圧接合して、絶縁接合部112に含まれる有機結着材成分を熱分解により除去した上で、拡散層120が形成された半導体パワーモジュール10を製造する(図1のステップS18)。

【0094】

以上説明した製造方法によっても、平面状の接合層110を作製できる。従って、半導体素子130と接合層110、接合層110とセラミックス多層基板100とを面で接合することができ、半導体素子130からセラミックス多層基板100への熱伝導性能、および、セラミックス多層基板100と半導体素子130との接合強度を向上することができる。

【0095】

D3.変形例3:

第1実施例では、セラミックス多層基板100と接合層110を予め有機結着材の接合力により仮積層した上で半導体素子130を積層して、加圧および加熱を行い接合しているが、例えば、シート状に形成された絶縁接合部112に形成された空孔を導電接続部111aで予め穴埋めして形成されたシートを作製し、セラミックス多層基板100と半導体素子130で矜持した上で加熱、圧着する事で、半導体パワーモジュール10を作製してもよい。こうすれば、接合層110に含まれる有機結着材の添加量を減少させる事が可能となり、有機残渣による接合層110の劣化などを防ぐ事ができる。

【0096】

D4.変形例4:

第1実施例では、第1の接合開始温度として、導電接合部111を構成する材料が十分に融解する温度を用い、第2の接合開始温度として、絶縁接合部112を構成する材料が十分に軟化する温度を用いているが、それぞれ、構成材料の少なくとも一部が焼結反応を開始する温度以上であればよい。こうすれば、導電接合部111、絶縁接合部112の各々について、融点まで加熱することなく他部材との接合を行うことができる。よって、製造工程の低温化を図ることができる。例えば、絶縁接合部112がNa2O3とB2O3とSiO2とからなる粉末ガラスから構成されている場合、第2の接合開始温度は、当該粉末ガラスの焼結反応の開始温度である495℃以上であればよい。

【0097】

以上、本発明の種々の実施例について説明したが、本発明はこれらの実施例に限定されず、その趣旨を逸脱しない範囲で種々の構成をとることができる。

【符号の説明】

【0098】

10、30、40…半導体パワーモジュール

100…セラミックス多層基板

101…内層ビアホール

104…電極端子

109…配線パターン

110…接合層

110a…接合部

111…導電接合部

111a…導電接続部

112…絶縁接合部

120…拡散層

121…導電拡散部

122…絶縁拡散部

130…半導体素子

131…電極パッド

202…スクリーン

203…スキージ

204…スキージホルダー

250…ガラス粉末ペースト

300…セラミックス多層基板

310…接合層

320…拡散層

330…半導体素子

400…セラミックス多層基板

410…接合層

411…導電接合部

412…絶縁接合部

420…拡散層

430…半導体素子

【特許請求の範囲】

【請求項1】

半導体パワーモジュールであって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面側に配置される半導体素子と、

前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置されている平面状の導電接合部であって、前記半導体素子に形成されている電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする平面状の絶縁接合部と、

を有する半導体パワーモジュール。

【請求項2】

請求項1記載の半導体パワーモジュールであって、

前記多層基板と前記接合層および前記半導体素子と前記接合層とは、拡散接合により接合され、

前記半導体パワーモジュールは、更に、

前記多層基板と前記接合層および前記半導体素子と前記接合層との間に、前記拡散接合時に形成される拡散層を備える、

半導体パワーモジュール。

【請求項3】

請求項1記載の半導体パワーモジュールであって、

前記絶縁接合部には、金属フィラーもしくは無機系フィラーが含まれる、

半導体パワーモジュール。

【請求項4】

請求項2記載の半導体パワーモジュールであって、

前記絶縁接合部および前記拡散層には、金属フィラーもしくは無機系フィラーが含まれる、

半導体パワーモジュール。

【請求項5】

請求項1ないし請求項4いずれか記載の半導体パワーモジュールであって、

前記導電接合部を構成する材料の接合開始温度である第1の接合開始温度は、前記絶縁接合部を構成する材料の接合開始温度である第2の接合開始温度よりも低いことを特徴とする、

半導体パワーモジュール。

【請求項6】

請求項5記載の半導体パワーモジュールにおいて、

前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度である焼結開始温度以上であり、

前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度である焼結開始温度以上であることを特徴とする、

半導体パワーモジュール。

【請求項7】

回路基板であって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面上に配置され、前記多層基板に半導体素子を接合するための接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置され、前記配線パターンと前記半導体素子と導通し、少なくとも前記第1の面側が平面状に形成されている導電接続部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とし、少なくとも前記第1の面側が平面状に形成されている絶縁接合部と、

を有する回路基板。

【請求項8】

請求項7記載の回路基板であって、

前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度である第1の接合開始温度は、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度である第2の接合開始温度よりも低いことを特徴とする、

回路基板。

【請求項9】

請求項8記載の回路基板おいて、

前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、

前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、

回路基板。

【請求項10】

半導体パワーモジュールであって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面側に配置される半導体素子と、

前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置され、前記半導体素子の電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、

を有し、

前記電極パッドと前記導電接続部とが導通可能となるように、前記半導体素子が前記接合層上に積層され、前記多層基板、前記接合層および前記半導体素子が接合された状態で、前記多層基板と前記接合層との界面、および、前記接合層と前記半導体素子との界面の、積層方向の断面が、略直線状に形成されている、

半導体パワーモジュール。

【請求項11】

回路基板であって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置され、前記配線パターンに前記半導体素子を導通させるための導電接続部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、

を有し、

前記多層基板と前記接合層が接着された状態で、前記多層基板と前記接合層との界面の、積層方向の断面は、略直線状である、

回路基板。

【請求項12】

半導体パワーモジュールの製造方法であって、

ビアおよび配線パターンを有する多層基板を製作し、

前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する平面状の導電接続部を有し、前記第1の部位とは異なる第2の部位に、平面状の絶縁接合部を有する接合部を、前記多層基板の第1の面上に配置し、

前記接合部上に、前記半導体素子を、前記半導体素子に形成されている電極パッドと前記導電接続部とが導通可能となるように配置し、

前記多層基板、前記接合部および前記半導体素子を、加熱圧着し、前記多層基板と前記接合層、および、前記接合部と前記半導体素子を拡散接合する、

半導体パワーモジュールの製造方法。

【請求項13】

請求項12記載の半導体パワーモジュールの製造方法であって、

前記拡散接合において、

前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度を第1の接合開始温度とし、

前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、

前記多層基板、前記接合部および前記半導体素子を、前記第1の接合開始温度で加熱圧着することにより、前記導電接合部と前記半導体素子の前記電極パッドとを接合し、

前記導電接合部と前記半導体素子の前記電極パッドとの接合後に、前記多層基板、前記接合部および前記半導体素子を、前記第2の接合開始温度で加熱圧着することにより、前記多層基板と前記接合部、および、前記接合部と前記半導体素子とを接合する、

半導体パワーモジュールの製造方法。

【請求項14】

請求項13記載の半導体パワーモジュールの製造方法において、

前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、

前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、

半導体パワーモジュールの製造方法。

【請求項15】

請求項12記載の半導体パワーモジュールの製造方法であって、

前記拡散接合において、

前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度を第1の接合開始温度とし、

前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、

前記第1の接合開始温度が、所定時間、保持された後、前記第2の接合開始温度が所定時間保持されるように設定されている温度プロファイルに基づき、前記加熱を行う、

半導体パワーモジュールの製造方法。

【請求項16】

回路基板の製造方法であって、

ビアおよび配線パターンを有する多層基板を製作し、

前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する導電接続部を有し、前記第1の部位とは異なる第2の部位に絶縁接合部を有し、少なくとも、前記第1の面側が平面状に形成されている接合層を、前記多層基板の第1の面上に配置し、

前記多層基板と前記接合層とを、前記接合層に含まれる有機成分の粘着力により接着する、

回路基板の製造方法。

【請求項1】

半導体パワーモジュールであって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面側に配置される半導体素子と、

前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置されている平面状の導電接合部であって、前記半導体素子に形成されている電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする平面状の絶縁接合部と、

を有する半導体パワーモジュール。

【請求項2】

請求項1記載の半導体パワーモジュールであって、

前記多層基板と前記接合層および前記半導体素子と前記接合層とは、拡散接合により接合され、

前記半導体パワーモジュールは、更に、

前記多層基板と前記接合層および前記半導体素子と前記接合層との間に、前記拡散接合時に形成される拡散層を備える、

半導体パワーモジュール。

【請求項3】

請求項1記載の半導体パワーモジュールであって、

前記絶縁接合部には、金属フィラーもしくは無機系フィラーが含まれる、

半導体パワーモジュール。

【請求項4】

請求項2記載の半導体パワーモジュールであって、

前記絶縁接合部および前記拡散層には、金属フィラーもしくは無機系フィラーが含まれる、

半導体パワーモジュール。

【請求項5】

請求項1ないし請求項4いずれか記載の半導体パワーモジュールであって、

前記導電接合部を構成する材料の接合開始温度である第1の接合開始温度は、前記絶縁接合部を構成する材料の接合開始温度である第2の接合開始温度よりも低いことを特徴とする、

半導体パワーモジュール。

【請求項6】

請求項5記載の半導体パワーモジュールにおいて、

前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する温度である焼結開始温度以上であり、

前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する温度である焼結開始温度以上であることを特徴とする、

半導体パワーモジュール。

【請求項7】

回路基板であって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面上に配置され、前記多層基板に半導体素子を接合するための接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置され、前記配線パターンと前記半導体素子と導通し、少なくとも前記第1の面側が平面状に形成されている導電接続部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とし、少なくとも前記第1の面側が平面状に形成されている絶縁接合部と、

を有する回路基板。

【請求項8】

請求項7記載の回路基板であって、

前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度である第1の接合開始温度は、前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度である第2の接合開始温度よりも低いことを特徴とする、

回路基板。

【請求項9】

請求項8記載の回路基板おいて、

前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、

前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、

回路基板。

【請求項10】

半導体パワーモジュールであって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面側に配置される半導体素子と、

前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置され、前記半導体素子の電極パッドと、前記電極パッドと前記多層基板とを導通する導電接続部と、からなる導電接合部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、

を有し、

前記電極パッドと前記導電接続部とが導通可能となるように、前記半導体素子が前記接合層上に積層され、前記多層基板、前記接合層および前記半導体素子が接合された状態で、前記多層基板と前記接合層との界面、および、前記接合層と前記半導体素子との界面の、積層方向の断面が、略直線状に形成されている、

半導体パワーモジュール。

【請求項11】

回路基板であって、

ビアおよび配線パターンが形成された多層基板と、

前記多層基板の第1の面上に形成され、前記多層基板と半導体素子とを接合する接合層と、

を備え、

前記接合層は、

前記ビアに対応する第1の部位に配置され、前記配線パターンに前記半導体素子を導通させるための導電接続部と、

前記第1の部位とは異なる第2の部位に配置され、無機系材料を主成分とする絶縁接合部と、

を有し、

前記多層基板と前記接合層が接着された状態で、前記多層基板と前記接合層との界面の、積層方向の断面は、略直線状である、

回路基板。

【請求項12】

半導体パワーモジュールの製造方法であって、

ビアおよび配線パターンを有する多層基板を製作し、

前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する平面状の導電接続部を有し、前記第1の部位とは異なる第2の部位に、平面状の絶縁接合部を有する接合部を、前記多層基板の第1の面上に配置し、

前記接合部上に、前記半導体素子を、前記半導体素子に形成されている電極パッドと前記導電接続部とが導通可能となるように配置し、

前記多層基板、前記接合部および前記半導体素子を、加熱圧着し、前記多層基板と前記接合層、および、前記接合部と前記半導体素子を拡散接合する、

半導体パワーモジュールの製造方法。

【請求項13】

請求項12記載の半導体パワーモジュールの製造方法であって、

前記拡散接合において、

前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度を第1の接合開始温度とし、

前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、

前記多層基板、前記接合部および前記半導体素子を、前記第1の接合開始温度で加熱圧着することにより、前記導電接合部と前記半導体素子の前記電極パッドとを接合し、

前記導電接合部と前記半導体素子の前記電極パッドとの接合後に、前記多層基板、前記接合部および前記半導体素子を、前記第2の接合開始温度で加熱圧着することにより、前記多層基板と前記接合部、および、前記接合部と前記半導体素子とを接合する、

半導体パワーモジュールの製造方法。

【請求項14】

請求項13記載の半導体パワーモジュールの製造方法において、

前記第1の接合開始温度は、前記導電接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であり、

前記第2の接合開始温度は、前記絶縁接合部を構成する材料の少なくとも一部が焼結反応を開始する焼結開始温度以上であることを特徴とする、

半導体パワーモジュールの製造方法。

【請求項15】

請求項12記載の半導体パワーモジュールの製造方法であって、

前記拡散接合において、

前記導電接合部を構成する材料が前記半導体素子と接合を開始する温度を第1の接合開始温度とし、

前記絶縁接合部を構成する材料が前記多層基板および前記半導体素子と接合を開始する温度であって、前記第1の接合開始温度よりも高い温度を第2の接合開始温度とし、

前記第1の接合開始温度が、所定時間、保持された後、前記第2の接合開始温度が所定時間保持されるように設定されている温度プロファイルに基づき、前記加熱を行う、

半導体パワーモジュールの製造方法。

【請求項16】

回路基板の製造方法であって、

ビアおよび配線パターンを有する多層基板を製作し、

前記ビアに対応する第1の部位に、前記配線パターンと半導体素子とを導通する導電接続部を有し、前記第1の部位とは異なる第2の部位に絶縁接合部を有し、少なくとも、前記第1の面側が平面状に形成されている接合層を、前記多層基板の第1の面上に配置し、

前記多層基板と前記接合層とを、前記接合層に含まれる有機成分の粘着力により接着する、

回路基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−51389(P2013−51389A)

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願番号】特願2012−61859(P2012−61859)

【出願日】平成24年3月19日(2012.3.19)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願日】平成24年3月19日(2012.3.19)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

[ Back to top ]