回路基板の製造方法および回路基板

【課題】切断時のバリの発生、あるいは、切断面からのダスト発生を招くことなく、形状の制約なしに、基板上に、めっき加工によって高精度の回路パターンを有する回路基板を形成する。

【解決手段】本発明の回路基板の製造方法は、少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程と、絶縁性基体表面に下地層を形成する工程と、下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、輪郭を形成する輪郭形成工程と、パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程と、表面に露呈する前記下地層を選択的に除去する工程とを含み、前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆されたことを特徴とする。

【解決手段】本発明の回路基板の製造方法は、少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程と、絶縁性基体表面に下地層を形成する工程と、下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、輪郭を形成する輪郭形成工程と、パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程と、表面に露呈する前記下地層を選択的に除去する工程とを含み、前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆されたことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路基板の製造方法および回路基板に係り、特にその配線パターンの形成に関する。

【背景技術】

【0002】

絶縁性基体の表面に回路部を形成して回路基板を製造するにあたり、回路部と、回路部の絶縁部となる非回路部との境界領域にレーザ等を照射することによってこの箇所にめっきがおこなわれないように処理し、そしてこの後に回路形成用のめっきを施すようにした技術が提案されている。

【0003】

しかしながら、これらの技術においては、非回路部となる領域全面にめっきがなされないように、レーザや紫外線などを非回路部の領域全面に照射している。

このため非回路部となる領域全面にレーザなどを照射しようとすると照射処理時間が長くなり、回路基板の生産性が低下するという問題があった。

【0004】

そこで、本出願人は、めっき用の下地層を絶縁性基体の全面に形成した後、回路部と非回路部の境界領域に、レーザなどの電磁波を照射することによって、非照射部を残して下地層を選択的に除去する。そして、電気めっきにより、非照射部の下地層の内、回路部となる部分に給電し、電界をかけることで、選択的にめっきを施したのちに、非回路部の下地層をエッチング除去するという方法を提案している(特許文献1)。

特許文献1の方法では、回路部に囲まれた内側領域に独立回路を形成するには、個々の独立回路に相当する領域の下地層にそれぞれ給電回路を設けて給電する必要があるため、製造が困難である。また、給電回路が回路パターン設計の制約となることがある。また、一体的に回路部を形成してからこの回路部をパターニングし、独立回路を形成する方法も考えられる。このように回路部を一体形成した後に、独立回路を形成しようとすると、めっき層の形成後に、レジストパターンを塗布し、選択的にめっき層及び下地層を除去する必要がある。この場合に、レジストが濡れ拡がり、不要部分まで覆ってしまい、めっき断線やかけを生じることがある。

【0005】

しかしながら、電気的に分離された複数の独立回路を形成する場合、個々の独立回路に対応する下地層に、電気めっきのためだけに、給電用の回路を個別に形成するのは作業性が悪い。そこで、回路部を分離して独立回路を形成するために、基体表面に凹部を形成しこの凹部に被覆材を通過させて、下地層を形成し、めっき層形成後に被覆材上の通過部を被覆材の少なくとも一部と共に除去することで、回路パターンの切り離しを行う方法が提案されている(特許文献2)。

【0006】

また、回路部を分離して独立回路を形成するために、基体表面に凸部を形成しこの凸部に被覆材を通過させて、下地層を形成し、めっき層形成後に被覆材上の通過部を被覆材の少なくとも一部と共に除去することで、回路パターンの切り離しを行う方法も提案されている(特許文献3)。

一方、特許文献2及び3の方法では、回路部に囲まれた内側領域にも独立回路を形成することはできるが、めっき後に回路部を構成するめっき層及び下地層の一部を除去して、独立回路を形成する際に、回路が剥離したり、めっき加工後に加工ばりが発生したりするという問題があった。

【0007】

さらにまた、このような回路基板の製造に際しては、個々の部品に給電用電極を形成するのは、専有面積の増大を招くため、連続的に形成し、めっき終了後に、個々の部品に分断するという方法が、通常であった。つまり、ある特定の大きさの外形を有する成型シート内に製品形状を作り込み、回路形成後に切断することで製品を個別化していた。この方法であれば、個片部の回路をシート部に引き出し、最終的に製品外となる部分で回路をひとつながりにしておけば、そのひとつながりになった部分に給電することで、すべての回路に一括して給電することが可能である。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特許第315682号公報

【特許文献2】特許第4131094号公報

【特許文献3】特許第4207399号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、回路パターン形成後、個々の部品に分割するという方法を用いる場合、以下のような問題があった。

(1)個片内の回路をシート部まで引き出さなければならない。

(2)個片化するために、何らかの方法で切り分けなければならないため、端部近傍では肉薄領域を形成するなど、設計上の制約があった。

(1)については、個片外に回路を引き出すため、製品機能上は不要な回路が製品に残るという問題があった。たとえば図16に示すように、基体110上に回路部(第1の配線層120)を形成する場合、図17に示すように、個片内の回路を端部まで引き出さなければならず、不要なパターンを形成したりするなどパターンの制約が多い。また複雑な回路の場合では、個片外に回路を引き出すためのスペースが不足し、設計上給電が成立しないという問題もあった。

(2)については、例えば、図18に一例を示すように切断位置のばらつきの関係上、切断部分にはある程度のスペースの余裕が必要となり、切断刃112によって切断した後に、図19に示すように製品外形に不要な突出部111が発生してしまい、これが、専有面積の増大などの問題の原因となることもあった。また、切断時のバリや、切断面からのダスト発生が問題となることがあった。

一方、下地層121と、めっき層で形成されたニッケル層122と金層123とからなる第1の配線層120においても図20に示すように、回路部の端部で下地層121、あるいはニッケル層122が露呈することになる。このため、下地層が銅層である場合には、腐食による劣化をもたらすこともあった。

【0010】

本発明は、前記実情に鑑みてなされたもので、切断時のバリの発生、あるいは、切断面からのダスト発生を招くことなく、形状の制約なしに、基板上に、めっき加工によって高精度の回路パターンを有する回路基板を形成することを目的とする。

【課題を解決するための手段】

【0011】

そこで本発明の回路基板の製造方法は、少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程と、絶縁性基体表面に下地層を形成する工程と、下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、輪郭を形成する輪郭形成工程と、パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程と、表面に露呈する前記下地層を選択的に除去する工程とを含み、前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆されたことを特徴とする。

また本発明は、上記回路基板の製造方法において、絶縁性基体を用意する工程が、表面に凹凸を有する立体構造の基体を用意する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、絶縁性基体を用意する工程は、側壁が回路基板表面に対して垂直となる立体構造の基体を用意する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、輪郭形成工程は、回路部および給電用のパッド領域が絶縁性基体の端面から所定の間隔を隔てるように、輪郭線を形成する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、下地層を形成する工程は、スパッタリング工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、スパッタリング工程は、銅薄膜を成膜する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、めっき工程は、銅薄膜上に、ニッケル層を形成するニッケルめっき工程と、ニッケル層上に金層を形成する金めっき工程とを含むことを特徴とする。

また本発明は、上記回路基板の製造方法において、絶縁性基体と、絶縁性基体上に形成された回路部と、給電用のパッド領域とを具備し、回路部および給電用のパッド領域の端面が、絶縁性基体の端面から所定の距離を隔てて形成され、回路部及び給電用のパッド領域において、下地層表面全体がめっき層で被覆されたことを特徴とする。

【発明の効果】

【0012】

本発明の回路基板の製造方法によれば、三次元立体配線技術を用いて、個片に対して回路を形成する技術であり、個片の回路部に対して給電部を介して給電することで、電気めっきにより回路部を構成しているため、設計上の制約が低減される。従って、切断時のバリの発生、あるいは、切断面からのダスト発生を招くことなく、形状の制約なしに、基板上に、めっき加工によって高精度の回路パターンを有する回路部を形成することが可能となる。

また、給電部を介して効率よく給電を行うことができるため、個片内に浮島(アイランド)の様な独立回路を形成することが可能となる。

なお、三次元立体基板だけでなく、平板構造の回路基板にも適用可能であることはいうまでもない。

【図面の簡単な説明】

【0013】

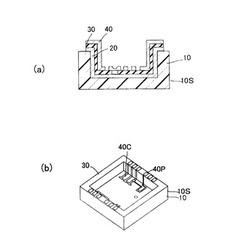

【図1】本発明の実施の形態1の立体基板を示す図であり、(a)は断面図、(b)は斜視図

【図2】同立体基板の配線部の要部拡大説明図

【図3】同立体基板の配線部端部の要部拡大説明図であり、(a)は断面図、(b)は斜視図

【図4】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図5】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図6】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図7】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図8】(a)乃至(d)は同立体基板の第1の配線層の形成工程を示す図

【図9】(a)乃至(e)は第2の配線層の形成工程を示す説明図

【図10】本発明の実施の形態2の実装基板を示す断面図

【図11】本発明の実施の形態2の実装基板の斜視図

【図12】本発明の実施の形態2の回路モジュール1を実装基板上に実装した状態を示す断面図

【図13】本発明の実施の形態2の回路モジュール1を実装基板上に実装した状態を示す斜視図

【図14】本発明の実施の形態2の回路基板の要部拡大断面図

【図15】(a)乃至(e)は本発明の実施の形態2の回路基板の製造工程を示す図

【図16】回路基板を示す図

【図17】回路基板を示す図

【図18】従来例の回路基板の製造工程の一部を示す図

【図19】従来例の回路基板を示す図

【図20】従来例の回路基板を示す図

【0014】

以下、図面を参照して、本発明の実施の形態について説明する。

【0015】

(実施の形態1)

図1(a)および(b)、ならびに図2は、本発明の実施の形態1の三次元立体基板である回路基板を示す図である。図1(a)は断面図、図1(b)は斜視図であり、図2は配線部の拡大説明図、図3は同配線部の端部を示す拡大図であり、(a)は断面図、(b)は斜視図である。また、図4乃至7は同立体基板の製造工程を示す図である。図4乃至図7においても(a)は断面図、(b)は斜視図である。図8(a)乃至(d)は第1の配線層の形成工程を示す説明図、図9(a)乃至(e)は第2の配線層の形成工程を示す説明図である。

本実施の形態の方法は、個片として形成された絶縁性基体としての三次元立体基板に下地層を形成し、この下地層に少なくとも一つのパッド領域を形成しておくこのパッドから通電することで電解めっきを行うようにしたことを特徴とするものである。

すなわち、

(1)少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程

(2)この絶縁性基体表面に下地層を形成する工程

(3)下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、輪郭を形成する輪郭形成工程

(4)パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程

(5)表面に露呈する前記下地層を選択的に除去する工程

とを含む。

【0016】

この立体基板は、少なくとも表面が絶縁性を呈する絶縁性基体10表面に形成された第1の配線層20上に、一定の膜厚を有する電着塗装膜30を有し、この上層に第2の配線層40とを含む回路部と、を備え、回路部40Cおよび給電用のパッド領域40Pの端面が、絶縁性基体の端面から所定の距離を隔てて形成され、回路部及び給電用のパッド領域において、下地層表面全体がめっき層で被覆されたたことを特徴とする。ここで絶縁性基体としては窒化アルミセラミック基板(AlN)が用いられる。そしてこの立体基板の回路部の要部拡大断面図を、図2に示す。そして第2の配線層40からなる回路部40Cは、相対向する2辺に沿って、パッド領域40Pの端面が、絶縁性基体10の端面から所定の距離を隔てて形成されている。また、図3(a)および(b)に示すように、回路部10C及び給電用のパッド領域40Pにおいて、下地層41表面全体がめっき層42、43で被覆されている。

このように、回路部は、絶縁性基体10上に形成された第1の配線層20を接地層とし、この上層に電着塗装法で形成された電着塗装膜30としてのポリイミド膜と、この上層に形成された、信号線を構成する第2の配線層40とで、グランドコプラナ構造の高周波回路を構成する。回路部においては、第1の配線層20は膜厚t1=6−20μmであり、全面に形成されて接地層を構成する。また、この上層に、電着塗装法で膜厚t2=15−20μmの電着塗装膜30としてのポリイミド膜が形成されている。さらに、この上層に、L/S(ラインアンドスペース)が100/100μm、膜厚t3=6−20μmの信号線を構成する第2の配線層40が形成されている。なお、L/Sは基板の大きさに応じて50/50μm以上で自由に調整することができる。

すなわち、回路部は、第1の配線層を接地層とし、第2の配線層を信号線とするマイクロストリップ回路を構成する。この構成においては、電着塗装膜30が、均一かつ高精度に膜厚制御のなされた構造を有するため、信号線と接地層との距離を高精度に確保することができる。従って、高周波回路においてもインピーダンス整合のなされた高周波回路が形成される。なお、第1の配線層についても接地層だけでなく回路部を構成するようにパターニングしてもよい。

【0017】

次に、この立体基板の製造工程について説明する。

まず、加圧成形により、窒化アルミセラミック基板からなる絶縁性基体10を用意する。

こののち、絶縁性基体10上に第1の配線層20を形成する(図4(a)及び(b))。形成に際しては、図8(a)乃至(d)に要部拡大断面図を示す方法によって形成される。まず、図8(a)に示すように、絶縁性基体10上にスパッタリング法により、膜厚100nm程度の銅薄膜21sを形成する。この後、図8(b)に示すように、めっき法により膜厚3〜10μm程度の銅層21を形成する。そしてさらに図8(c)に示すように、めっき法により順次膜厚3〜10μm程度のニッケル層22、膜厚0.1〜0.5μm程度の金層23を形成し、第1の配線層20を得る(図8(d))。

【0018】

そして、全面にレジストを塗布し、フォトリソグラフィによりパターニングし、第1の配線層20と第2の配線層40との接続部に相当する領域にレジスト膜R1を形成する(図5(a)及び(b))。

【0019】

次いで、被塗物を陰極とするカチオン型電着塗装を用いてこの第1の配線層20上にポリイミド膜からなる電着塗装膜30を形成する(図6(a)及び(b))。電着塗装工程は、電解液の充填された容器中に、第1の配線層の形成された絶縁性基体を浸漬するとともにこの第1の配線層を陰極に接続して、電着塗装を行う。

【0020】

このようにして電着塗装膜30を形成したのち、レジスト膜R1を除去し、ホールHを形成する(図7(a)及び(b))。

そして最後に第2の配線層40を形成し、図1(a)及び(b)に示した立体基板が完成する。

【0021】

第2の配線層の形成に際しては、図9(a)乃至(e)に要部拡大断面図を示す方法がとられる。まず、図9(a)に示すように、電着塗装膜30上にスパッタリング法により、再度、膜厚100nm程度の銅薄膜41sを形成する。この後、図9(b)に示すように、回路部と非回路部の境界をレーザ描画により除去し、輪郭線を形成する。そして図9(c)に示すように、めっき法により回路部の銅薄膜41s上に膜厚3〜10μm程度の銅層41を形成する。そしてさらに図9(d)に示すように、めっき法により順次膜厚3〜10μm程度のニッケル層42、膜厚0.1〜0.5μm程度の金層43を形成し、最後に、めっき層の形成されなかった、非回路部の銅薄膜41sをエッチング除去し、第2の配線層40を得る(図9(e))。

【0022】

このようにして、絶縁性基体10表面に、第1の配線層20、電着塗装膜30、第2の配線層40の形成された立体基板が完成する。

【0023】

上記方法によれば、絶縁性基体10としての窒化アルミニウム基板は、表面に凹凸部を有するものであるが、三次元立体配線技術を用いて、個片に対して回路を形成する技術であり、個片の回路部に対して給電部を介して給電することで、電気めっきにより回路部を構成しているため、設計上の制約が低減される。従って、切断時のバリの発生、あるいは、切断面からのダスト発生を招くことなく、形状の制約なしに、基板上に、めっき加工によって高精度の回路パターンを有する回路部を形成することが可能となる。

また、給電部を介して効率よく給電を行うことができるため、個片内に浮島の様な独立回路を形成することが可能となる。

なお、三次元立体基板だけでなく、平板構造の回路基板にも適用可能であることはいうまでもない。

さらにまた、本実施の形態では、電着塗装法により、ポリイミドからなる電着塗装膜30を形成しているため、膜厚を高精度に制御することができるとともに、均一な膜厚を得ることが可能となる。なお、前記実施の形態ではポリイミドを用いたがポリアミドイミドなど他の材料を用いてもよい。

【0024】

また、電着塗装工程は、第1の配線層20上に、レジストパターンを形成し電着塗装膜30を形成するため、極めて容易に電着塗装膜の形成されない領域を形成することができ、所望の接続部を形成することが可能となる。

【0025】

また、本発明によれば、数μmオーダーで絶縁層の膜厚制御を行うことができるため、接地線に対して電着塗装膜からなる絶縁層を介して信号線を形成したグランドコプラナ配線構造を得ることができる。このように、高周波回路を形成する際、グランドコプラナ構造の配線に用いることで、絶縁層の膜厚を高精度に調整することができ、インピーダンスマッチングを容易に実現することができる。従って、より高周波帯域への適用が可能な立体基板を提供することが可能となる。

【0026】

このように、同一層内で、接地線と信号線を所定のギャップを隔てて形成した従来のプラナー構造の配線とした場合には、マッチング精度がパターン精度に左右されることになり、現状の数十μmオーダーの精度では数百Gbpsを超える領域においてもインピーダンス整合を得ることは困難であったのに対し、本実施の形態では、高周波帯域においても容易に高精度のインピーダンス整合を得ることが可能となる。

【0027】

また、本実施の形態では、接地線に接続される接地層を第1の配線層20とし、電着塗装膜30を介してこの上層に信号線を構成する第2の配線層40を形成している。このため、下層側に凹凸が少なく、より平坦な構造をとることができるため、膜厚が均一で、信頼性の高い配線構造をとることができる。

【0028】

また本発明は、スパッタリング法により下地層を形成し、下地層のうち、回路部と、回路部の絶縁部となる非回路部の境界領域を選択的に除去して、輪郭を形成したのち、下地層をめっき用下地として、めっきを行うようにしているため、極めて作業性よく回路部を形成することが可能となる。なお、銅薄膜から成長せしめられためっき層は、電気化学的反応を経て形成されるため、密着性が良好で界面特性の優れた膜となっている。

【0029】

この下地層は膜厚100から500nm程度、望ましくは100−300nm程度の銅薄膜で構成することにより、密着性も良好である。そしてこの状態で銅薄膜からめっき層が成長するため、密着性に優れためっき層の形成が可能となる。

【0030】

なお、絶縁性基体として平板構造の基板を用いてもよいし、立体構造の基板を用いてもよい。つまり、回路部、特に高周波回路部を、本実施の形態の構成をとるようにすればよく、絶縁性基体自体としては、平板構造にも立体構造にも適用可能であることはいうまでもない。

【0031】

また、このめっき用下地としてはスパッタリングで形成した銅薄膜に限定されることなく、クロム薄膜、チタン薄膜など、他の導電性薄膜を用いてもよい事は言うまでもない。また1層の薄膜だけでなく、多層薄膜を用いるようにしてもよい。

【0032】

まためっき層としても、銅層とニッケル層と金層との3層膜に限定されることなく適宜変形可能であり、膜厚については、3層の合計膜厚が10μm〜15μm程度が望ましい。

【0033】

電着塗装膜としては、カチオン型電着塗装、アニオン型電着塗装のいずれを用いてもよい。材料としては、ポリイミド、ポリアミドイミドなどが有効である。

【0034】

さらにまた、前記実施の形態では、回路基板を構成する絶縁性基体として、放熱性の良好な窒化アルミニウムセラミックスを構成したが、これに限定されるものではない。たとえば、グリーンシートを用いた積層基板および射出成形によって形成した樹脂製の立体基板など、種々の基板材料が適用可能である。

例えば1000℃以下で低温焼結が可能なセラミック誘電体材料LTCC(低温温同時焼成セラミック:Low Temperature Co-fired Ceramics)を用いてグリーンシートとして形成してもよい。すなわち、厚さが10μm〜200μmのこのLTCCのグリーンシートに、低抵抗率のAgやCu等の導電ペーストを印刷して所定のパターンを形成する。そしてこの、複数のグリーンシートを絶縁層として用いて、適宜一体的に積層し、焼結することにより、内部導体層を備えた絶縁層(誘電体層)として製造することが出来る。これらの誘電体材料としては、例えばAl、Si、Srを主成分として、Ti、Bi、Cu、Mn、Na、Kを副成分とする材料、Al、Mg、Si、Gdを含む材料、Al、Si、Zr、Mgを含む材料などが適用可能である。ここで、誘電率は5〜15程度の材料を用いる。

なお、セラミック誘電体材料の他に、樹脂積層基板や樹脂とセラミック誘電体粉末を混合してなる複合材料を用いてなる積層基板を用いることも可能である。また、このセラミック基板を、HTCC(高温同時焼成セラミック:High Temperature Co-fired Ceramics)技術を用いてもよい。この、HTCCセラミック基板上に、誘電体材料をAl2O3を主体とするもので構成し、内部導体層として伝送線路等をタングステンやモリブデン等の高温で焼結可能な金属導体として構成しても良い。

また金属基板を用いた場合、表面を覆う絶縁膜を電着塗装膜で構成し、膜厚を均一にすることで、金属基板自体を接地線として用いることも可能である。

【0035】

また、絶縁性基板としては、セラミックのほか、ガラスエポキシ樹脂、ポリイミド樹脂、ポリエステル樹脂、ポリエチレンテレフタレート樹脂などの樹脂基板を用いた場合、プリプレグを用いた積層基板などにも適用可能である。

【0036】

さらにまた、回路部の構成及び材料についても、適宜変更可能である。

【0037】

また、前記実施の形態においても、絶縁性基体は、表面に凹凸を有するか否か、あるいは、その形状に、限定されることなく適宜変形可能である。表面に凹凸がある場合には、スプレー塗布、刷毛塗り、印刷などの方法では、均一な膜厚を得るのが困難であるが、この構成をとること制御性よく膜厚の均一な電着塗布膜を形成することができる。また配線層についても、制御性よく安定して形成するのが困難であるが、本発明によれば均一で安定した配線層を形成することができ、特に有効である。しかしながら平坦部においても、本発明の方法は有効である。

【0038】

また、前記実施の形態では、回路部の形成は、下地層を形成し、この下地層のうち、回路部と、回路部の絶縁部となる非回路部の境界領域を選択的に除去して、輪郭を形成し、めっき層の形成後に、めっき層をマスクとして下地層をエッチングするという方法をとったが、これに限定されるものではない。たとえば、非回路部と回路部との境界領域を選択的に除去して、銅薄膜41sに輪郭を形成し、銅めっき層の形成後に、全面エッチングを行うようにしてもよい。これにより、非回路部の輪郭で囲まれた領域には銅めっき層は形成されないため、銅薄膜41sは薄い膜のままであり、エッチングで除去され、回路部の銅めっき層の形成された領域のみが銅層41として残留し、この銅めっき層上に金めっき層を形成することで、所望のパターンを形成することができる。これはいわゆる1ショットレーザー法と呼ばれるものである。またこの他、LDS法、あるいは2ショット法など、適宜変更可能であることはいうまでもない。

ここでLDS法は、導電性粒子を含む樹脂基板にレーザ照射を行い導電性粒子を露出せしめて、この導電性粒子のパターン上にめっきを行い回路部を形成する方法である。

2ショット法は、無電解めっきの触媒を含む材料で一次成形した後、触媒を含まない材料で2次成形を行う。そして露出した一次成形の表面にのみ選択的に無電解めっきを施し、立体基板を形成する方法である。

【0039】

また、多層配線構造において絶縁層の膜厚を高精度に制御することができるため、高周波回路に限定されることなく、絶縁層を容量絶縁膜として用いる場合など、種々の立体基板に適用可能である。

【0040】

(実施の形態2)

図10は本発明の実施の形態2の実装基板を示す断面図である。図11は同斜視図、図12は、この実装基板上にセンサチップ(素子チップ)80A,80Bを搭載した、回路モジュール1を実装基板上に実装した状態を示す断面図、図13は同回路モジュールを実装基板上に実装した状態を示す斜視図である。図14は同回路基板の要部拡大断面図である。図15(a)乃至(e)は同回路基板の製造工程を示す図である。

【0041】

本実施の形態の回路モジュール1は、ジャイロセンサ用の回路基板であり、図13に示すように、実装面を構成する主表面である第1の面10Aおよびこれと対向する第2の面10Bが、実装基板50に対して垂直となるように実装されるものである。実装基板50への実装は配線部51に対して半田60を介して行われる。このため、回路基板を構成する絶縁性基体10には、この第1の面10Aおよび第2の面10Bから側面に伸張する接続用のパッド領域20Pが形成されている。そして、素子搭載領域20D、回路部20Cおよび給電用のパッド領域20Pの端面が、バリのない平滑な面をもつ個片状の絶縁性基体で構成されている。そして、この回路基板においては、図14に要部拡大図を示すように、回路部及び給電用のパッド領域において、下地層を構成する銅層21表面全体がめっき層22,23で被覆されている。なお、この回路基板においては、絶縁性基体10の端面から所定の距離を隔てて形成されているパッド領域20Pもあるが、実装面には第1及び第2の面から実装面10Sにかけて配線層が形成され、パッド領域20Pを構成している。図10及び図11に示すように、主表面である第1の面10Aおよび第2の面10Bに形成された凹部に素子搭載領域20Dを有する。そしてこれら素子搭載領域20D、回路部20Cおよびパッド領域20Pは、第1の配線層20として同一の導電性層で構成される。このパッド領域20Pが、製造時のめっき工程で給電用のパッドとしても用いられる。

【0042】

そして、この回路モジュール1は、図12及び図13に示すように、垂直実装用の回路基板を構成する絶縁性基体10と、この絶縁性基体10の、素子搭載領域20Dに搭載される素子チップ80A,80Bとを有し、実装面10Sの中心を通りかつ、絶縁性基体10の素子搭載領域20D形成面に平行な中心面10C上に、回路モジュールの重心Gが位置するように形成されている。ここでこの回路基板は、第1の面10Aおよび第2の面10Bに素子搭載領域を構成する凹部が形成された立体基板である。そして、実装基板(マザーボード)50上に形成されたパッド51上に、半田60を介して垂直実装される。ここで実装基板50上の実装面のパッド51に接続されるパッド領域20P(配線導体層20)、素子チップ実装面に形成されるダイパッド(素子搭載領域20D)及びパッド領域20Pを含む配線導体層は、樹脂基板上にスパッタリング法で下地層を形成し、この下地層上にめっき層を形成して、得られる。この配線導体層は、実装基板50上の実装面のパッド51に接続されるパッド領域20P(配線導体層20)、素子チップ実装面に形成されるダイパッド(素子搭載領域20D)及びパッド領域20Pを含む。25はボンディングワイヤである。

【0043】

ここでは、回路基板を構成する絶縁性基体10の中心面10Cに対して、対称となるように、第1の面10A側と、この第1の面10Aに対向する第2の面10B側とに、同一のジャイロセンサを構成する素子チップ80A,80Bが搭載される。

【0044】

製造に際しては、第1の面及び第2の面10Aおよび10Bに同一のジャイロセンサを構成する素子チップ80A,80Bが搭載されるため、素子チップ80A,80Bの方向性を高精度に保持できる構成とする必要がある。ちなみに、回路基板を構成する絶縁性基体10については、第1及び第2の面の中心面に対して対称な形状を持つように設計され、製造される。すなわち、実装面10Sの中心を通りかつ、絶縁性基体10の前記素子搭載領域20D形成面に平行な中心面10C上に、回路モジュールの重心Gが位置するように形状を設計し、加工することで得られる。このため、多数個の回路基板を一体形成し、個片に分割する構成とし、切断面に接続片を持たないように形成することで、実装面にばりや突起を残すことのない、平滑面をもつ回路基板を形成することができる。そしてこの絶縁性基体10の実装面10Sには第1及び第2の面から実装面10Sにかけて配線層が形成され、パッド領域20Pを構成している。

【0045】

ここで回路基板を構成する立体基板上に配線導体層を形成するに際しては、図15(a)乃至(e)に要部拡大断面図を示す方法がとられる。まず、図15(a)に示すように、個片を構成する窒化アルミ(ALN)セラミックからなり、第1及び第2の面に凹部を有する絶縁性基体10を成形する。絶縁性基体10の表面の全面に、無電解めっきあるいはCVDやスパッタリング等を行うことにより導電性薄膜からなる下地層を形成する。ここではこの後、図15(b)に示すように、無電解の銅めっきあるいはスパッタリングによる銅薄膜を形成する。そして、図15(c)に示すように、絶縁性基体10の表面にレーザビームを照射することで当該照射部分の下地層をパターニングし選択的に除去する。ここでレーザビームは、ガルバノミラー等で走査することにより形成すべき配線導体層の輪郭に沿って絶縁性基体10の表面を移動しつつ照射され、下地層のうち配線導体層のパターンに一致した部分(以下、「下地層」と呼ぶ。)と配線導体層のパターンに一致しない部分との境界領域の下地層を除去する。従って、絶縁性基体10の表面にはレーザビームが照射された輪郭内側の下地層(配線導体層のパターンに一致した下地層)と、下地層の輪郭に沿った部分のみがレーザビーム照射で除去された下地層(図示せず)とが残ることになる。但し、隣接する配線導体層の間隔が狭い場合においては、上述のように輪郭部分だけでなく配線導体層間の下地層を全てレーザビーム照射で除去することも可能である。

【0046】

続いて、配線導体層のパターンに一致した下地層の上に、電気めっきにより銅めっき層を厚付けする。このときパッド領域となる部分を介して通電することで電解めっきを行う。そして全面エッチングを行うことで、図15(d)に示すように、不要な銅薄膜及銅めっき層の表面をエッチングで除去する。

そして図15(e)に示すように、残った銅層21上にめっきによりニッケル層22、金層23を形成すれば、所望の回路パターンが形成された回路基板を得ることができる。

【0047】

このように、表面に配線導体層を有する回路基板を設計し、回路基板上に素子チップを配することで形成されるが、個片で形成されているため、全面が平滑面であり、いかなる面を実装面とすることも可能である。本発明では、回路基板および回路モジュールの設計に際し、回路モジュールの実装基板上への、実装面の中心を通りかつ、前記回路基板の前記素子搭載領域形成面に平行な中心面上に、回路モジュールの重心が位置するように、回路基板のバランス調整を行う。

【0048】

特に、本実施の形態の回路モジュールでは、回路モジュールの重心が実装面の中心を通りかつ、前記回路基板の前記素子搭載領域形成面に平行な中心面上に、回路モジュールの重心が位置するように形成されたことで、接着時に半田60などの接着剤の収縮による力を受けたとしても、重心を含む面を中心として振動し、元の位置に戻るため、より信頼性の高い実装が可能となる。

【0049】

このように、回路基板の設計においてバランス調整を行うことで、別途付加部品を追加することなく、極めて高精度で信頼性の高いバランス構造を得ることが可能となる。

【0050】

立体基板を垂直実装しようとすると、凹部の存在により、重心位置が変動し易く、不安定であるが、この構成をとることにより、より安定した実装が可能となる。

【0051】

また、素子チップが回路基板の両面に対称に配置されているため、安定な実装が可能となる。

さらにまた、何ら特別な部品を用いることなく、容易に製造可能である。

【0052】

加えて上記構成によれば、ジャイロセンサなど、方向性がきわめて重要なセンサデバイスの実装においても高精度の角度を維持することが可能となる。

【0053】

また、前記回路基板の第1及び第2の主面10A,10Bに、同一のセンサチップが搭載されているため、2つの素子チップ80A,80Bによって、距離を測定する場合にも、極めて高精度の測定を実現することができる。

【0054】

なお、前記実施の形態1の回路モジュール1では、回路基板の第1および第2の面10A,10Bに同一の素子チップ80A,80Bを搭載したが、別の素子チップを搭載してもよく、素子チップの重量が異なっていたり、あるいは、設置位置によって重心位置が上述したように中心面上にない場合は、中心面上にくるように、別の部品を付加したり、別の部品の位置を変えたりするなどの手段により調整してもよい。

【0055】

以上、本発明者らによってなされた発明を適用した実施の形態について説明したが、この実施の形態による本発明の開示の一部をなす記述及び図面により本発明は限定されることはない。すなわち、上記実施の形態に基づいて当業者等によりなされる他の実施の形態、実施例及び運用技術等は全て本発明の範疇に含まれることは勿論である。

【符号の説明】

【0056】

10 絶縁性基体

20,120,220 第1の配線層

30,130,230 電着塗装膜

40,140,240 第2の配線層

【技術分野】

【0001】

本発明は、回路基板の製造方法および回路基板に係り、特にその配線パターンの形成に関する。

【背景技術】

【0002】

絶縁性基体の表面に回路部を形成して回路基板を製造するにあたり、回路部と、回路部の絶縁部となる非回路部との境界領域にレーザ等を照射することによってこの箇所にめっきがおこなわれないように処理し、そしてこの後に回路形成用のめっきを施すようにした技術が提案されている。

【0003】

しかしながら、これらの技術においては、非回路部となる領域全面にめっきがなされないように、レーザや紫外線などを非回路部の領域全面に照射している。

このため非回路部となる領域全面にレーザなどを照射しようとすると照射処理時間が長くなり、回路基板の生産性が低下するという問題があった。

【0004】

そこで、本出願人は、めっき用の下地層を絶縁性基体の全面に形成した後、回路部と非回路部の境界領域に、レーザなどの電磁波を照射することによって、非照射部を残して下地層を選択的に除去する。そして、電気めっきにより、非照射部の下地層の内、回路部となる部分に給電し、電界をかけることで、選択的にめっきを施したのちに、非回路部の下地層をエッチング除去するという方法を提案している(特許文献1)。

特許文献1の方法では、回路部に囲まれた内側領域に独立回路を形成するには、個々の独立回路に相当する領域の下地層にそれぞれ給電回路を設けて給電する必要があるため、製造が困難である。また、給電回路が回路パターン設計の制約となることがある。また、一体的に回路部を形成してからこの回路部をパターニングし、独立回路を形成する方法も考えられる。このように回路部を一体形成した後に、独立回路を形成しようとすると、めっき層の形成後に、レジストパターンを塗布し、選択的にめっき層及び下地層を除去する必要がある。この場合に、レジストが濡れ拡がり、不要部分まで覆ってしまい、めっき断線やかけを生じることがある。

【0005】

しかしながら、電気的に分離された複数の独立回路を形成する場合、個々の独立回路に対応する下地層に、電気めっきのためだけに、給電用の回路を個別に形成するのは作業性が悪い。そこで、回路部を分離して独立回路を形成するために、基体表面に凹部を形成しこの凹部に被覆材を通過させて、下地層を形成し、めっき層形成後に被覆材上の通過部を被覆材の少なくとも一部と共に除去することで、回路パターンの切り離しを行う方法が提案されている(特許文献2)。

【0006】

また、回路部を分離して独立回路を形成するために、基体表面に凸部を形成しこの凸部に被覆材を通過させて、下地層を形成し、めっき層形成後に被覆材上の通過部を被覆材の少なくとも一部と共に除去することで、回路パターンの切り離しを行う方法も提案されている(特許文献3)。

一方、特許文献2及び3の方法では、回路部に囲まれた内側領域にも独立回路を形成することはできるが、めっき後に回路部を構成するめっき層及び下地層の一部を除去して、独立回路を形成する際に、回路が剥離したり、めっき加工後に加工ばりが発生したりするという問題があった。

【0007】

さらにまた、このような回路基板の製造に際しては、個々の部品に給電用電極を形成するのは、専有面積の増大を招くため、連続的に形成し、めっき終了後に、個々の部品に分断するという方法が、通常であった。つまり、ある特定の大きさの外形を有する成型シート内に製品形状を作り込み、回路形成後に切断することで製品を個別化していた。この方法であれば、個片部の回路をシート部に引き出し、最終的に製品外となる部分で回路をひとつながりにしておけば、そのひとつながりになった部分に給電することで、すべての回路に一括して給電することが可能である。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特許第315682号公報

【特許文献2】特許第4131094号公報

【特許文献3】特許第4207399号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、回路パターン形成後、個々の部品に分割するという方法を用いる場合、以下のような問題があった。

(1)個片内の回路をシート部まで引き出さなければならない。

(2)個片化するために、何らかの方法で切り分けなければならないため、端部近傍では肉薄領域を形成するなど、設計上の制約があった。

(1)については、個片外に回路を引き出すため、製品機能上は不要な回路が製品に残るという問題があった。たとえば図16に示すように、基体110上に回路部(第1の配線層120)を形成する場合、図17に示すように、個片内の回路を端部まで引き出さなければならず、不要なパターンを形成したりするなどパターンの制約が多い。また複雑な回路の場合では、個片外に回路を引き出すためのスペースが不足し、設計上給電が成立しないという問題もあった。

(2)については、例えば、図18に一例を示すように切断位置のばらつきの関係上、切断部分にはある程度のスペースの余裕が必要となり、切断刃112によって切断した後に、図19に示すように製品外形に不要な突出部111が発生してしまい、これが、専有面積の増大などの問題の原因となることもあった。また、切断時のバリや、切断面からのダスト発生が問題となることがあった。

一方、下地層121と、めっき層で形成されたニッケル層122と金層123とからなる第1の配線層120においても図20に示すように、回路部の端部で下地層121、あるいはニッケル層122が露呈することになる。このため、下地層が銅層である場合には、腐食による劣化をもたらすこともあった。

【0010】

本発明は、前記実情に鑑みてなされたもので、切断時のバリの発生、あるいは、切断面からのダスト発生を招くことなく、形状の制約なしに、基板上に、めっき加工によって高精度の回路パターンを有する回路基板を形成することを目的とする。

【課題を解決するための手段】

【0011】

そこで本発明の回路基板の製造方法は、少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程と、絶縁性基体表面に下地層を形成する工程と、下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、輪郭を形成する輪郭形成工程と、パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程と、表面に露呈する前記下地層を選択的に除去する工程とを含み、前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆されたことを特徴とする。

また本発明は、上記回路基板の製造方法において、絶縁性基体を用意する工程が、表面に凹凸を有する立体構造の基体を用意する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、絶縁性基体を用意する工程は、側壁が回路基板表面に対して垂直となる立体構造の基体を用意する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、輪郭形成工程は、回路部および給電用のパッド領域が絶縁性基体の端面から所定の間隔を隔てるように、輪郭線を形成する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、下地層を形成する工程は、スパッタリング工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、スパッタリング工程は、銅薄膜を成膜する工程であることを特徴とする。

また本発明は、上記回路基板の製造方法において、めっき工程は、銅薄膜上に、ニッケル層を形成するニッケルめっき工程と、ニッケル層上に金層を形成する金めっき工程とを含むことを特徴とする。

また本発明は、上記回路基板の製造方法において、絶縁性基体と、絶縁性基体上に形成された回路部と、給電用のパッド領域とを具備し、回路部および給電用のパッド領域の端面が、絶縁性基体の端面から所定の距離を隔てて形成され、回路部及び給電用のパッド領域において、下地層表面全体がめっき層で被覆されたことを特徴とする。

【発明の効果】

【0012】

本発明の回路基板の製造方法によれば、三次元立体配線技術を用いて、個片に対して回路を形成する技術であり、個片の回路部に対して給電部を介して給電することで、電気めっきにより回路部を構成しているため、設計上の制約が低減される。従って、切断時のバリの発生、あるいは、切断面からのダスト発生を招くことなく、形状の制約なしに、基板上に、めっき加工によって高精度の回路パターンを有する回路部を形成することが可能となる。

また、給電部を介して効率よく給電を行うことができるため、個片内に浮島(アイランド)の様な独立回路を形成することが可能となる。

なお、三次元立体基板だけでなく、平板構造の回路基板にも適用可能であることはいうまでもない。

【図面の簡単な説明】

【0013】

【図1】本発明の実施の形態1の立体基板を示す図であり、(a)は断面図、(b)は斜視図

【図2】同立体基板の配線部の要部拡大説明図

【図3】同立体基板の配線部端部の要部拡大説明図であり、(a)は断面図、(b)は斜視図

【図4】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図5】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図6】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図7】同立体基板の製造工程を示す図であり、(a)は断面図、(b)は斜視図

【図8】(a)乃至(d)は同立体基板の第1の配線層の形成工程を示す図

【図9】(a)乃至(e)は第2の配線層の形成工程を示す説明図

【図10】本発明の実施の形態2の実装基板を示す断面図

【図11】本発明の実施の形態2の実装基板の斜視図

【図12】本発明の実施の形態2の回路モジュール1を実装基板上に実装した状態を示す断面図

【図13】本発明の実施の形態2の回路モジュール1を実装基板上に実装した状態を示す斜視図

【図14】本発明の実施の形態2の回路基板の要部拡大断面図

【図15】(a)乃至(e)は本発明の実施の形態2の回路基板の製造工程を示す図

【図16】回路基板を示す図

【図17】回路基板を示す図

【図18】従来例の回路基板の製造工程の一部を示す図

【図19】従来例の回路基板を示す図

【図20】従来例の回路基板を示す図

【0014】

以下、図面を参照して、本発明の実施の形態について説明する。

【0015】

(実施の形態1)

図1(a)および(b)、ならびに図2は、本発明の実施の形態1の三次元立体基板である回路基板を示す図である。図1(a)は断面図、図1(b)は斜視図であり、図2は配線部の拡大説明図、図3は同配線部の端部を示す拡大図であり、(a)は断面図、(b)は斜視図である。また、図4乃至7は同立体基板の製造工程を示す図である。図4乃至図7においても(a)は断面図、(b)は斜視図である。図8(a)乃至(d)は第1の配線層の形成工程を示す説明図、図9(a)乃至(e)は第2の配線層の形成工程を示す説明図である。

本実施の形態の方法は、個片として形成された絶縁性基体としての三次元立体基板に下地層を形成し、この下地層に少なくとも一つのパッド領域を形成しておくこのパッドから通電することで電解めっきを行うようにしたことを特徴とするものである。

すなわち、

(1)少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程

(2)この絶縁性基体表面に下地層を形成する工程

(3)下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、輪郭を形成する輪郭形成工程

(4)パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程

(5)表面に露呈する前記下地層を選択的に除去する工程

とを含む。

【0016】

この立体基板は、少なくとも表面が絶縁性を呈する絶縁性基体10表面に形成された第1の配線層20上に、一定の膜厚を有する電着塗装膜30を有し、この上層に第2の配線層40とを含む回路部と、を備え、回路部40Cおよび給電用のパッド領域40Pの端面が、絶縁性基体の端面から所定の距離を隔てて形成され、回路部及び給電用のパッド領域において、下地層表面全体がめっき層で被覆されたたことを特徴とする。ここで絶縁性基体としては窒化アルミセラミック基板(AlN)が用いられる。そしてこの立体基板の回路部の要部拡大断面図を、図2に示す。そして第2の配線層40からなる回路部40Cは、相対向する2辺に沿って、パッド領域40Pの端面が、絶縁性基体10の端面から所定の距離を隔てて形成されている。また、図3(a)および(b)に示すように、回路部10C及び給電用のパッド領域40Pにおいて、下地層41表面全体がめっき層42、43で被覆されている。

このように、回路部は、絶縁性基体10上に形成された第1の配線層20を接地層とし、この上層に電着塗装法で形成された電着塗装膜30としてのポリイミド膜と、この上層に形成された、信号線を構成する第2の配線層40とで、グランドコプラナ構造の高周波回路を構成する。回路部においては、第1の配線層20は膜厚t1=6−20μmであり、全面に形成されて接地層を構成する。また、この上層に、電着塗装法で膜厚t2=15−20μmの電着塗装膜30としてのポリイミド膜が形成されている。さらに、この上層に、L/S(ラインアンドスペース)が100/100μm、膜厚t3=6−20μmの信号線を構成する第2の配線層40が形成されている。なお、L/Sは基板の大きさに応じて50/50μm以上で自由に調整することができる。

すなわち、回路部は、第1の配線層を接地層とし、第2の配線層を信号線とするマイクロストリップ回路を構成する。この構成においては、電着塗装膜30が、均一かつ高精度に膜厚制御のなされた構造を有するため、信号線と接地層との距離を高精度に確保することができる。従って、高周波回路においてもインピーダンス整合のなされた高周波回路が形成される。なお、第1の配線層についても接地層だけでなく回路部を構成するようにパターニングしてもよい。

【0017】

次に、この立体基板の製造工程について説明する。

まず、加圧成形により、窒化アルミセラミック基板からなる絶縁性基体10を用意する。

こののち、絶縁性基体10上に第1の配線層20を形成する(図4(a)及び(b))。形成に際しては、図8(a)乃至(d)に要部拡大断面図を示す方法によって形成される。まず、図8(a)に示すように、絶縁性基体10上にスパッタリング法により、膜厚100nm程度の銅薄膜21sを形成する。この後、図8(b)に示すように、めっき法により膜厚3〜10μm程度の銅層21を形成する。そしてさらに図8(c)に示すように、めっき法により順次膜厚3〜10μm程度のニッケル層22、膜厚0.1〜0.5μm程度の金層23を形成し、第1の配線層20を得る(図8(d))。

【0018】

そして、全面にレジストを塗布し、フォトリソグラフィによりパターニングし、第1の配線層20と第2の配線層40との接続部に相当する領域にレジスト膜R1を形成する(図5(a)及び(b))。

【0019】

次いで、被塗物を陰極とするカチオン型電着塗装を用いてこの第1の配線層20上にポリイミド膜からなる電着塗装膜30を形成する(図6(a)及び(b))。電着塗装工程は、電解液の充填された容器中に、第1の配線層の形成された絶縁性基体を浸漬するとともにこの第1の配線層を陰極に接続して、電着塗装を行う。

【0020】

このようにして電着塗装膜30を形成したのち、レジスト膜R1を除去し、ホールHを形成する(図7(a)及び(b))。

そして最後に第2の配線層40を形成し、図1(a)及び(b)に示した立体基板が完成する。

【0021】

第2の配線層の形成に際しては、図9(a)乃至(e)に要部拡大断面図を示す方法がとられる。まず、図9(a)に示すように、電着塗装膜30上にスパッタリング法により、再度、膜厚100nm程度の銅薄膜41sを形成する。この後、図9(b)に示すように、回路部と非回路部の境界をレーザ描画により除去し、輪郭線を形成する。そして図9(c)に示すように、めっき法により回路部の銅薄膜41s上に膜厚3〜10μm程度の銅層41を形成する。そしてさらに図9(d)に示すように、めっき法により順次膜厚3〜10μm程度のニッケル層42、膜厚0.1〜0.5μm程度の金層43を形成し、最後に、めっき層の形成されなかった、非回路部の銅薄膜41sをエッチング除去し、第2の配線層40を得る(図9(e))。

【0022】

このようにして、絶縁性基体10表面に、第1の配線層20、電着塗装膜30、第2の配線層40の形成された立体基板が完成する。

【0023】

上記方法によれば、絶縁性基体10としての窒化アルミニウム基板は、表面に凹凸部を有するものであるが、三次元立体配線技術を用いて、個片に対して回路を形成する技術であり、個片の回路部に対して給電部を介して給電することで、電気めっきにより回路部を構成しているため、設計上の制約が低減される。従って、切断時のバリの発生、あるいは、切断面からのダスト発生を招くことなく、形状の制約なしに、基板上に、めっき加工によって高精度の回路パターンを有する回路部を形成することが可能となる。

また、給電部を介して効率よく給電を行うことができるため、個片内に浮島の様な独立回路を形成することが可能となる。

なお、三次元立体基板だけでなく、平板構造の回路基板にも適用可能であることはいうまでもない。

さらにまた、本実施の形態では、電着塗装法により、ポリイミドからなる電着塗装膜30を形成しているため、膜厚を高精度に制御することができるとともに、均一な膜厚を得ることが可能となる。なお、前記実施の形態ではポリイミドを用いたがポリアミドイミドなど他の材料を用いてもよい。

【0024】

また、電着塗装工程は、第1の配線層20上に、レジストパターンを形成し電着塗装膜30を形成するため、極めて容易に電着塗装膜の形成されない領域を形成することができ、所望の接続部を形成することが可能となる。

【0025】

また、本発明によれば、数μmオーダーで絶縁層の膜厚制御を行うことができるため、接地線に対して電着塗装膜からなる絶縁層を介して信号線を形成したグランドコプラナ配線構造を得ることができる。このように、高周波回路を形成する際、グランドコプラナ構造の配線に用いることで、絶縁層の膜厚を高精度に調整することができ、インピーダンスマッチングを容易に実現することができる。従って、より高周波帯域への適用が可能な立体基板を提供することが可能となる。

【0026】

このように、同一層内で、接地線と信号線を所定のギャップを隔てて形成した従来のプラナー構造の配線とした場合には、マッチング精度がパターン精度に左右されることになり、現状の数十μmオーダーの精度では数百Gbpsを超える領域においてもインピーダンス整合を得ることは困難であったのに対し、本実施の形態では、高周波帯域においても容易に高精度のインピーダンス整合を得ることが可能となる。

【0027】

また、本実施の形態では、接地線に接続される接地層を第1の配線層20とし、電着塗装膜30を介してこの上層に信号線を構成する第2の配線層40を形成している。このため、下層側に凹凸が少なく、より平坦な構造をとることができるため、膜厚が均一で、信頼性の高い配線構造をとることができる。

【0028】

また本発明は、スパッタリング法により下地層を形成し、下地層のうち、回路部と、回路部の絶縁部となる非回路部の境界領域を選択的に除去して、輪郭を形成したのち、下地層をめっき用下地として、めっきを行うようにしているため、極めて作業性よく回路部を形成することが可能となる。なお、銅薄膜から成長せしめられためっき層は、電気化学的反応を経て形成されるため、密着性が良好で界面特性の優れた膜となっている。

【0029】

この下地層は膜厚100から500nm程度、望ましくは100−300nm程度の銅薄膜で構成することにより、密着性も良好である。そしてこの状態で銅薄膜からめっき層が成長するため、密着性に優れためっき層の形成が可能となる。

【0030】

なお、絶縁性基体として平板構造の基板を用いてもよいし、立体構造の基板を用いてもよい。つまり、回路部、特に高周波回路部を、本実施の形態の構成をとるようにすればよく、絶縁性基体自体としては、平板構造にも立体構造にも適用可能であることはいうまでもない。

【0031】

また、このめっき用下地としてはスパッタリングで形成した銅薄膜に限定されることなく、クロム薄膜、チタン薄膜など、他の導電性薄膜を用いてもよい事は言うまでもない。また1層の薄膜だけでなく、多層薄膜を用いるようにしてもよい。

【0032】

まためっき層としても、銅層とニッケル層と金層との3層膜に限定されることなく適宜変形可能であり、膜厚については、3層の合計膜厚が10μm〜15μm程度が望ましい。

【0033】

電着塗装膜としては、カチオン型電着塗装、アニオン型電着塗装のいずれを用いてもよい。材料としては、ポリイミド、ポリアミドイミドなどが有効である。

【0034】

さらにまた、前記実施の形態では、回路基板を構成する絶縁性基体として、放熱性の良好な窒化アルミニウムセラミックスを構成したが、これに限定されるものではない。たとえば、グリーンシートを用いた積層基板および射出成形によって形成した樹脂製の立体基板など、種々の基板材料が適用可能である。

例えば1000℃以下で低温焼結が可能なセラミック誘電体材料LTCC(低温温同時焼成セラミック:Low Temperature Co-fired Ceramics)を用いてグリーンシートとして形成してもよい。すなわち、厚さが10μm〜200μmのこのLTCCのグリーンシートに、低抵抗率のAgやCu等の導電ペーストを印刷して所定のパターンを形成する。そしてこの、複数のグリーンシートを絶縁層として用いて、適宜一体的に積層し、焼結することにより、内部導体層を備えた絶縁層(誘電体層)として製造することが出来る。これらの誘電体材料としては、例えばAl、Si、Srを主成分として、Ti、Bi、Cu、Mn、Na、Kを副成分とする材料、Al、Mg、Si、Gdを含む材料、Al、Si、Zr、Mgを含む材料などが適用可能である。ここで、誘電率は5〜15程度の材料を用いる。

なお、セラミック誘電体材料の他に、樹脂積層基板や樹脂とセラミック誘電体粉末を混合してなる複合材料を用いてなる積層基板を用いることも可能である。また、このセラミック基板を、HTCC(高温同時焼成セラミック:High Temperature Co-fired Ceramics)技術を用いてもよい。この、HTCCセラミック基板上に、誘電体材料をAl2O3を主体とするもので構成し、内部導体層として伝送線路等をタングステンやモリブデン等の高温で焼結可能な金属導体として構成しても良い。

また金属基板を用いた場合、表面を覆う絶縁膜を電着塗装膜で構成し、膜厚を均一にすることで、金属基板自体を接地線として用いることも可能である。

【0035】

また、絶縁性基板としては、セラミックのほか、ガラスエポキシ樹脂、ポリイミド樹脂、ポリエステル樹脂、ポリエチレンテレフタレート樹脂などの樹脂基板を用いた場合、プリプレグを用いた積層基板などにも適用可能である。

【0036】

さらにまた、回路部の構成及び材料についても、適宜変更可能である。

【0037】

また、前記実施の形態においても、絶縁性基体は、表面に凹凸を有するか否か、あるいは、その形状に、限定されることなく適宜変形可能である。表面に凹凸がある場合には、スプレー塗布、刷毛塗り、印刷などの方法では、均一な膜厚を得るのが困難であるが、この構成をとること制御性よく膜厚の均一な電着塗布膜を形成することができる。また配線層についても、制御性よく安定して形成するのが困難であるが、本発明によれば均一で安定した配線層を形成することができ、特に有効である。しかしながら平坦部においても、本発明の方法は有効である。

【0038】

また、前記実施の形態では、回路部の形成は、下地層を形成し、この下地層のうち、回路部と、回路部の絶縁部となる非回路部の境界領域を選択的に除去して、輪郭を形成し、めっき層の形成後に、めっき層をマスクとして下地層をエッチングするという方法をとったが、これに限定されるものではない。たとえば、非回路部と回路部との境界領域を選択的に除去して、銅薄膜41sに輪郭を形成し、銅めっき層の形成後に、全面エッチングを行うようにしてもよい。これにより、非回路部の輪郭で囲まれた領域には銅めっき層は形成されないため、銅薄膜41sは薄い膜のままであり、エッチングで除去され、回路部の銅めっき層の形成された領域のみが銅層41として残留し、この銅めっき層上に金めっき層を形成することで、所望のパターンを形成することができる。これはいわゆる1ショットレーザー法と呼ばれるものである。またこの他、LDS法、あるいは2ショット法など、適宜変更可能であることはいうまでもない。

ここでLDS法は、導電性粒子を含む樹脂基板にレーザ照射を行い導電性粒子を露出せしめて、この導電性粒子のパターン上にめっきを行い回路部を形成する方法である。

2ショット法は、無電解めっきの触媒を含む材料で一次成形した後、触媒を含まない材料で2次成形を行う。そして露出した一次成形の表面にのみ選択的に無電解めっきを施し、立体基板を形成する方法である。

【0039】

また、多層配線構造において絶縁層の膜厚を高精度に制御することができるため、高周波回路に限定されることなく、絶縁層を容量絶縁膜として用いる場合など、種々の立体基板に適用可能である。

【0040】

(実施の形態2)

図10は本発明の実施の形態2の実装基板を示す断面図である。図11は同斜視図、図12は、この実装基板上にセンサチップ(素子チップ)80A,80Bを搭載した、回路モジュール1を実装基板上に実装した状態を示す断面図、図13は同回路モジュールを実装基板上に実装した状態を示す斜視図である。図14は同回路基板の要部拡大断面図である。図15(a)乃至(e)は同回路基板の製造工程を示す図である。

【0041】

本実施の形態の回路モジュール1は、ジャイロセンサ用の回路基板であり、図13に示すように、実装面を構成する主表面である第1の面10Aおよびこれと対向する第2の面10Bが、実装基板50に対して垂直となるように実装されるものである。実装基板50への実装は配線部51に対して半田60を介して行われる。このため、回路基板を構成する絶縁性基体10には、この第1の面10Aおよび第2の面10Bから側面に伸張する接続用のパッド領域20Pが形成されている。そして、素子搭載領域20D、回路部20Cおよび給電用のパッド領域20Pの端面が、バリのない平滑な面をもつ個片状の絶縁性基体で構成されている。そして、この回路基板においては、図14に要部拡大図を示すように、回路部及び給電用のパッド領域において、下地層を構成する銅層21表面全体がめっき層22,23で被覆されている。なお、この回路基板においては、絶縁性基体10の端面から所定の距離を隔てて形成されているパッド領域20Pもあるが、実装面には第1及び第2の面から実装面10Sにかけて配線層が形成され、パッド領域20Pを構成している。図10及び図11に示すように、主表面である第1の面10Aおよび第2の面10Bに形成された凹部に素子搭載領域20Dを有する。そしてこれら素子搭載領域20D、回路部20Cおよびパッド領域20Pは、第1の配線層20として同一の導電性層で構成される。このパッド領域20Pが、製造時のめっき工程で給電用のパッドとしても用いられる。

【0042】

そして、この回路モジュール1は、図12及び図13に示すように、垂直実装用の回路基板を構成する絶縁性基体10と、この絶縁性基体10の、素子搭載領域20Dに搭載される素子チップ80A,80Bとを有し、実装面10Sの中心を通りかつ、絶縁性基体10の素子搭載領域20D形成面に平行な中心面10C上に、回路モジュールの重心Gが位置するように形成されている。ここでこの回路基板は、第1の面10Aおよび第2の面10Bに素子搭載領域を構成する凹部が形成された立体基板である。そして、実装基板(マザーボード)50上に形成されたパッド51上に、半田60を介して垂直実装される。ここで実装基板50上の実装面のパッド51に接続されるパッド領域20P(配線導体層20)、素子チップ実装面に形成されるダイパッド(素子搭載領域20D)及びパッド領域20Pを含む配線導体層は、樹脂基板上にスパッタリング法で下地層を形成し、この下地層上にめっき層を形成して、得られる。この配線導体層は、実装基板50上の実装面のパッド51に接続されるパッド領域20P(配線導体層20)、素子チップ実装面に形成されるダイパッド(素子搭載領域20D)及びパッド領域20Pを含む。25はボンディングワイヤである。

【0043】

ここでは、回路基板を構成する絶縁性基体10の中心面10Cに対して、対称となるように、第1の面10A側と、この第1の面10Aに対向する第2の面10B側とに、同一のジャイロセンサを構成する素子チップ80A,80Bが搭載される。

【0044】

製造に際しては、第1の面及び第2の面10Aおよび10Bに同一のジャイロセンサを構成する素子チップ80A,80Bが搭載されるため、素子チップ80A,80Bの方向性を高精度に保持できる構成とする必要がある。ちなみに、回路基板を構成する絶縁性基体10については、第1及び第2の面の中心面に対して対称な形状を持つように設計され、製造される。すなわち、実装面10Sの中心を通りかつ、絶縁性基体10の前記素子搭載領域20D形成面に平行な中心面10C上に、回路モジュールの重心Gが位置するように形状を設計し、加工することで得られる。このため、多数個の回路基板を一体形成し、個片に分割する構成とし、切断面に接続片を持たないように形成することで、実装面にばりや突起を残すことのない、平滑面をもつ回路基板を形成することができる。そしてこの絶縁性基体10の実装面10Sには第1及び第2の面から実装面10Sにかけて配線層が形成され、パッド領域20Pを構成している。

【0045】

ここで回路基板を構成する立体基板上に配線導体層を形成するに際しては、図15(a)乃至(e)に要部拡大断面図を示す方法がとられる。まず、図15(a)に示すように、個片を構成する窒化アルミ(ALN)セラミックからなり、第1及び第2の面に凹部を有する絶縁性基体10を成形する。絶縁性基体10の表面の全面に、無電解めっきあるいはCVDやスパッタリング等を行うことにより導電性薄膜からなる下地層を形成する。ここではこの後、図15(b)に示すように、無電解の銅めっきあるいはスパッタリングによる銅薄膜を形成する。そして、図15(c)に示すように、絶縁性基体10の表面にレーザビームを照射することで当該照射部分の下地層をパターニングし選択的に除去する。ここでレーザビームは、ガルバノミラー等で走査することにより形成すべき配線導体層の輪郭に沿って絶縁性基体10の表面を移動しつつ照射され、下地層のうち配線導体層のパターンに一致した部分(以下、「下地層」と呼ぶ。)と配線導体層のパターンに一致しない部分との境界領域の下地層を除去する。従って、絶縁性基体10の表面にはレーザビームが照射された輪郭内側の下地層(配線導体層のパターンに一致した下地層)と、下地層の輪郭に沿った部分のみがレーザビーム照射で除去された下地層(図示せず)とが残ることになる。但し、隣接する配線導体層の間隔が狭い場合においては、上述のように輪郭部分だけでなく配線導体層間の下地層を全てレーザビーム照射で除去することも可能である。

【0046】

続いて、配線導体層のパターンに一致した下地層の上に、電気めっきにより銅めっき層を厚付けする。このときパッド領域となる部分を介して通電することで電解めっきを行う。そして全面エッチングを行うことで、図15(d)に示すように、不要な銅薄膜及銅めっき層の表面をエッチングで除去する。

そして図15(e)に示すように、残った銅層21上にめっきによりニッケル層22、金層23を形成すれば、所望の回路パターンが形成された回路基板を得ることができる。

【0047】

このように、表面に配線導体層を有する回路基板を設計し、回路基板上に素子チップを配することで形成されるが、個片で形成されているため、全面が平滑面であり、いかなる面を実装面とすることも可能である。本発明では、回路基板および回路モジュールの設計に際し、回路モジュールの実装基板上への、実装面の中心を通りかつ、前記回路基板の前記素子搭載領域形成面に平行な中心面上に、回路モジュールの重心が位置するように、回路基板のバランス調整を行う。

【0048】

特に、本実施の形態の回路モジュールでは、回路モジュールの重心が実装面の中心を通りかつ、前記回路基板の前記素子搭載領域形成面に平行な中心面上に、回路モジュールの重心が位置するように形成されたことで、接着時に半田60などの接着剤の収縮による力を受けたとしても、重心を含む面を中心として振動し、元の位置に戻るため、より信頼性の高い実装が可能となる。

【0049】

このように、回路基板の設計においてバランス調整を行うことで、別途付加部品を追加することなく、極めて高精度で信頼性の高いバランス構造を得ることが可能となる。

【0050】

立体基板を垂直実装しようとすると、凹部の存在により、重心位置が変動し易く、不安定であるが、この構成をとることにより、より安定した実装が可能となる。

【0051】

また、素子チップが回路基板の両面に対称に配置されているため、安定な実装が可能となる。

さらにまた、何ら特別な部品を用いることなく、容易に製造可能である。

【0052】

加えて上記構成によれば、ジャイロセンサなど、方向性がきわめて重要なセンサデバイスの実装においても高精度の角度を維持することが可能となる。

【0053】

また、前記回路基板の第1及び第2の主面10A,10Bに、同一のセンサチップが搭載されているため、2つの素子チップ80A,80Bによって、距離を測定する場合にも、極めて高精度の測定を実現することができる。

【0054】

なお、前記実施の形態1の回路モジュール1では、回路基板の第1および第2の面10A,10Bに同一の素子チップ80A,80Bを搭載したが、別の素子チップを搭載してもよく、素子チップの重量が異なっていたり、あるいは、設置位置によって重心位置が上述したように中心面上にない場合は、中心面上にくるように、別の部品を付加したり、別の部品の位置を変えたりするなどの手段により調整してもよい。

【0055】

以上、本発明者らによってなされた発明を適用した実施の形態について説明したが、この実施の形態による本発明の開示の一部をなす記述及び図面により本発明は限定されることはない。すなわち、上記実施の形態に基づいて当業者等によりなされる他の実施の形態、実施例及び運用技術等は全て本発明の範疇に含まれることは勿論である。

【符号の説明】

【0056】

10 絶縁性基体

20,120,220 第1の配線層

30,130,230 電着塗装膜

40,140,240 第2の配線層

【特許請求の範囲】

【請求項1】

少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程と、

前記絶縁性基体表面に下地層を形成する工程と、

前記下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、回路部の輪郭を形成する輪郭形成工程と、

前記パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程と、

表面に露呈する前記下地層を選択的に除去する工程とを含み、

前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、

前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆された回路基板の製造方法。

【請求項2】

請求項1に記載の回路基板の製造方法であって、

前記絶縁性基体を用意する工程は、表面に凹凸を有する立体構造の基体を用意する工程である回路基板の製造方法。

【請求項3】

請求項1または2に記載の回路基板の製造方法であって、

前記絶縁性基体を用意する工程は、側壁が前記回路基板表面に対して垂直となる立体構造の基体を用意する工程である回路基板の製造方法。

【請求項4】

請求項1に記載の回路基板の製造方法であって、

前記輪郭形成工程は、前記回路部および給電用のパッド領域が前記絶縁性基体の端面から所定の間隔を隔てるように、前記輪郭線を形成する工程である回路基板の製造方法。

【請求項5】

請求項1乃至4のいずれか1項に記載の回路基板の製造方法であって、

前記下地層を形成する工程は、スパッタリング工程である回路基板の製造方法。

【請求項6】

請求項5に記載の回路基板の製造方法であって、

前記スパッタリング工程は、銅薄膜を成膜する工程である回路基板の製造方法。

【請求項7】

請求項6に記載の回路基板の製造方法であって、

前記めっき工程は、前記銅薄膜上に、ニッケル層を形成するニッケルめっき工程と、

前記ニッケル層上に金層を形成する金めっき工程とを含む回路基板の製造方法。

【請求項8】

請求項1乃至7のいずれか1項に記載の回路基板の製造方法で得られる回路基板であって、

絶縁性基体と、前記絶縁性基体上に形成された回路部と、給電用のパッド領域とを具備し、

前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、

前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆された回路基板。

【請求項1】

少なくとも表面が絶縁性を呈する、個片状の絶縁性基体を用意する工程と、

前記絶縁性基体表面に下地層を形成する工程と、

前記下地層のうち、回路部と、給電用のパッド領域を残して、回路部の絶縁部となる非回路部の境界領域を選択的に除去し、回路部の輪郭を形成する輪郭形成工程と、

前記パッド領域の下地層を給電部としてめっきを行い、めっき層を形成するめっき工程と、

表面に露呈する前記下地層を選択的に除去する工程とを含み、

前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、

前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆された回路基板の製造方法。

【請求項2】

請求項1に記載の回路基板の製造方法であって、

前記絶縁性基体を用意する工程は、表面に凹凸を有する立体構造の基体を用意する工程である回路基板の製造方法。

【請求項3】

請求項1または2に記載の回路基板の製造方法であって、

前記絶縁性基体を用意する工程は、側壁が前記回路基板表面に対して垂直となる立体構造の基体を用意する工程である回路基板の製造方法。

【請求項4】

請求項1に記載の回路基板の製造方法であって、

前記輪郭形成工程は、前記回路部および給電用のパッド領域が前記絶縁性基体の端面から所定の間隔を隔てるように、前記輪郭線を形成する工程である回路基板の製造方法。

【請求項5】

請求項1乃至4のいずれか1項に記載の回路基板の製造方法であって、

前記下地層を形成する工程は、スパッタリング工程である回路基板の製造方法。

【請求項6】

請求項5に記載の回路基板の製造方法であって、

前記スパッタリング工程は、銅薄膜を成膜する工程である回路基板の製造方法。

【請求項7】

請求項6に記載の回路基板の製造方法であって、

前記めっき工程は、前記銅薄膜上に、ニッケル層を形成するニッケルめっき工程と、

前記ニッケル層上に金層を形成する金めっき工程とを含む回路基板の製造方法。

【請求項8】

請求項1乃至7のいずれか1項に記載の回路基板の製造方法で得られる回路基板であって、

絶縁性基体と、前記絶縁性基体上に形成された回路部と、給電用のパッド領域とを具備し、

前記回路部および前記給電用のパッド領域の端面が、前記絶縁性基体の端面から所定の距離を隔てて形成され、

前記回路部及び前記給電用のパッド領域において、前記下地層表面全体が前記めっき層で被覆された回路基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図13】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図11】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図13】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図11】

【図15】

【公開番号】特開2012−94606(P2012−94606A)

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願番号】特願2010−238966(P2010−238966)

【出願日】平成22年10月25日(2010.10.25)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願日】平成22年10月25日(2010.10.25)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]