回路基板

【課題】接続端子の間隔が小さな電子部品を内蔵できる回路基板及びその製造方法を提供する。

【解決手段】電子部品を内蔵するための空白領域が設けられた第1の絶縁体層と、空白領域が設けられた第2の絶縁体層とが積層されて構成されている積層体と、第2の絶縁体層に設けられ、一端が複数の接続端子にそれぞれ接続されている複数の導体層と、積層体内に設けられ、かつ、複数の導体層の他端にそれぞれ接続されている複数のビアホール導体と、を備えており、第1の絶縁体層および第2の絶縁体層は、熱可塑性樹脂によって構成されており、積層体は、熱可塑性樹脂の軟化・流動によって第1の絶縁体層及び第2の絶縁体層が接合されてなり、第1の絶縁体層の空白領域は、電子部品よりも大きく、複数のビアホール導体は、第1の絶縁体層において空白領域の周りに配置されていること、を特徴とする。

【解決手段】電子部品を内蔵するための空白領域が設けられた第1の絶縁体層と、空白領域が設けられた第2の絶縁体層とが積層されて構成されている積層体と、第2の絶縁体層に設けられ、一端が複数の接続端子にそれぞれ接続されている複数の導体層と、積層体内に設けられ、かつ、複数の導体層の他端にそれぞれ接続されている複数のビアホール導体と、を備えており、第1の絶縁体層および第2の絶縁体層は、熱可塑性樹脂によって構成されており、積層体は、熱可塑性樹脂の軟化・流動によって第1の絶縁体層及び第2の絶縁体層が接合されてなり、第1の絶縁体層の空白領域は、電子部品よりも大きく、複数のビアホール導体は、第1の絶縁体層において空白領域の周りに配置されていること、を特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路基板に関し、より特定的には、複数の絶縁体層が積層されてなる積層体を備えた回路基板に関する。

【背景技術】

【0002】

従来の回路基板としては、例えば、特許文献1に記載のプリント基板が知られている。該プリント基板では、導体パターン及び導電性組成物が絶縁基材内に設けられている。絶縁基材は、複数の樹脂フィルムが積層されて構成されている。導体パターンは、樹脂フィルム上に設けられている導体層である。導電性組成物は、樹脂フィルムを貫通するビアホールに導電ペーストを充填して焼結させて得られたビアホール導体であり、その一端において導体パターンと接続されている。

【0003】

更に、回路基板では、絶縁基材内に設けられている空洞内に電気素子が収容されている。電気素子は、導電性組成物の他端上に実装されている。これにより、電気素子と導体パターンとは、導電性組成物により電気的に接続されている。

【0004】

ところで、特許文献1に記載のプリント基板は、以下に説明するように、接続端子の間隔が小さな電子素子を導電性組成物上に実装することが困難であるという問題を有している。より詳細には、プリント基板では、ビアホール導体である導電性組成物に電子素子の接続端子が直接に接続されている。そして、導電性組成物は、以下の工程により作成される。

【0005】

まず、導電性組成物が接続されている導体パターンに孔が空かないように、導体パターンが設けられている主面の反対側の主面から、樹脂フィルムに対してビームを照射し、ビアホールを形成する。次に、ビアホールに対して、導電ペーストを充填する。最後に、導電ペーストを焼結して、導電性組成物を得る。

【0006】

前記導電性組成物では、ビアホールの形成時に、導体パターンに孔が空かないように、比較的に強度が弱いビームを複数回照射することが一般的である。このように、比較的に強度が弱いビームを複数回照射すると、ビームの照射の度にビアホールの径は、広がってしまう。したがって、特許文献1に記載のプリント基板では、大きな径の導電性組成物しか得ることができない。そのため、該プリント基板では、小さな間隔で導電性組成物を配置することが困難である。その結果、接続端子の間隔が小さな電子素子を導電性組成物上に実装することが困難である。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3867593号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

そこで、本発明の目的は、接続端子の間隔が小さな電子部品を実装できる回路基板を提供することである。

【課題を解決するための手段】

【0009】

本発明の一形態に係る回路基板は、複数の接続端子を有する電子部品と、前記電子部品を内蔵するための空白領域が設けられた第1の絶縁体層と、該空白領域が設けられた第2の絶縁体層とが積層されて構成されている積層体と、前記第2の絶縁体層に設けられ、一端が前記複数の接続端子にそれぞれ接続されている複数の導体層と、前記積層体内に設けられ、かつ、前記複数の導体層の他端にそれぞれ接続されている複数のビアホール導体と、を備えており、前記第1の絶縁体層および前記第2の絶縁体層は、熱可塑性樹脂によって構成されており、前記積層体は、前記熱可塑性樹脂の軟化・流動によって前記第1の絶縁体層及び前記第2の絶縁体層が接合されてなり、前記第1の絶縁体層の前記空白領域は、積層方向から平面視したときに、前記電子部品よりも大きく、前記複数のビアホール導体は、前記第1の絶縁体層において前記空白領域の周りに配置されていること、を特徴とする。

【発明の効果】

【0010】

本発明によれば、接続端子の間隔が小さな電子部品を実装することができる。

【図面の簡単な説明】

【0011】

【図1】図1(a)は、本発明の一実施形態に係る回路基板の断面構造図である。図1(b)は、回路基板の拡大図である。

【図2】図1の回路基板の分解図である。

【図3】図2のフレキシブルシート及び電子部品を平面視した図である。

【図4】回路基板の製造工程を示した断面構造図である。

【図5】回路基板の製造工程を示した断面構造図である。

【図6】第1の変形例に係る回路基板の拡大図である。

【図7】第2の変形例に係る回路基板の分解図である。

【図8】第3の変形例に係る回路基板のフレキシブルシート及び電子部品を平面視した図である。

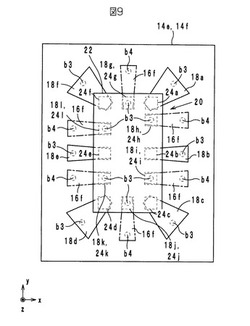

【図9】第4の変形例に係る回路基板のフレキシブルシート及び電子部品を平面視した図である。

【図10】第5の変形例に係る回路基板のフレキシブルシート及び電子部品を平面視した図である。

【発明を実施するための形態】

【0012】

以下に、本発明の実施形態に係る回路基板について図面を参照しながら説明する。

【0013】

(回路基板の構成)

以下に、本発明の一実施形態に係る回路基板の構成について図面を参照しながら説明する。図1(a)は、本発明の一実施形態に係る回路基板10の断面構造図である。図1(b)は、回路基板10の拡大図である。図2は、図1の回路基板10の分解図である。図3は、図2のフレキシブルシート14e及び電子部品20を平面視した図である。以下では、回路基板10の積層方向をz軸方向と定義し、図1の紙面の左右方向をx軸方向と定義し、図1の紙面の垂直方向をy軸方向と定義する。また、フレキシブルシート14の表面とは、z軸方向の正方向側に位置する面を指し、フレキシブルシート14の裏面とは、z軸方向の負方向側に位置する面を指す。

【0014】

回路基板10は、図1(a)及び図3に示すように、積層体12、導体層16(16b〜16g),18(18a〜18g)、電子部品20及びビアホール導体b1〜b5を備えている。

【0015】

積層体12は、図2に示すように、複数(図2では7枚)のフレキシブルシート(絶縁体層)14(14a〜14g)が積層されて構成され、直方体状をなしている。積層体12は、外力により変形することができる。

【0016】

フレキシブルシート14は、可撓性材料(例えば、液晶ポリマーやポリイミド等の熱可塑性樹脂)からなり、長方形状をなしている。また、フレキシブルシート14の厚みは、25μm〜100μm程度である。フレキシブルシート14c,14dには、図2に示すように、後述する電子部品20を収容する空洞を形成するための空白領域B1,B2が設けられている。空白領域B1,B2は、フレキシブルシート14c,14dの中央部分を長方形状に打ち抜いて形成されている。空白領域B1,B2は、z軸方向から平面視したときに、電子部品20よりも僅かに大きくなるように形成されている。なお、図1では、各フレキシブルシート14の主面同士が密接に接合しているので、その境界を図示していない。また、以下では、フレキシブルシート14のz軸方向の正方向側の主面を表面と称し、フレキシブルシート14のz軸方向の負方向側の主面を裏面と称す。

【0017】

導体層16は、図2に示すように、積層体12内に設けられており、配線導体、コイル導体又はコンデンサ導体等である。より詳細には、導体層16b〜16fはそれぞれ、フレキシブルシート14b〜14fの表面に設けられており、例えば、銅箔により作製されている。また、導体層16gは、フレキシブルシート14gの裏面に設けられており、例えば、銅箔により作製されている。なお、導体層16については、図面が煩雑になることを避けるために、代表的なものにのみ参照符号を付してある。

【0018】

導体層18は、図2及び図3に示すように、積層体12内に設けられており、電子部品20が実装されるランドとして機能する。導体層18は、フレキシブルシート14eの表面に設けられており、例えば、銅箔により作製されている。導体層18a,18b,18d〜18gは、z軸方向から平面視したときに、電子部品20と全体において重なるように設けられている。一方、導体層18cは、z軸方向から平面視したときに、電子部品20と一部において重なるように設けられている。よって、導体層18cの残余の部分は、z軸方向から平面視したときに、本体22からはみ出している。

【0019】

ビアホール導体b1〜b5はそれぞれ、図2に示すように、積層体12内に設けられており、フレキシブルシート14b,14c,14e〜14gをz軸方向に貫通するように設けられている。ビアホール導体b1〜b5は、z軸方向の両側に位置する導体層16,18を電気的に接続している。以上のように、導体層16,18及びビアホール導体b1〜b5は、互いに接続されることにより、回路を構成している。なお、ビアホール導体b1〜b5については、図面が煩雑になることを避けるために、代表的なものにのみ参照符号を付してある。

【0020】

電子部品20は、積層体12に内蔵されており、RFID(Radio Frequency IDentification)用の無線ICチップや、デジタルスチルカメラに用いられる画像処理用のICチップ等の半導体チップ(能動部品)、或いは、チップコンデンサやチップ抵抗などの受動部品である。電子部品20は、図1ないし図3に示すように、基板22及び接続端子24(24a〜24g)を有している。基板22は、シリコンやセラミックのような比較的に硬い材料により構成されており、積層体12のように容易に変形することができない。また、電子部品20が例えば半導体チップである場合、基板22の内部には半導体集積回路が形成されている。

【0021】

接続端子24は、基板22のz軸方向の負方向側の主面に設けられており、例えば、AuやCu等により作製されている。接続端子24a〜24gは、図3に示すように、電子部品20が導体層18a〜18gに実装された際に、対応する導体層18a〜18gと電気的に接続されている。具体的には、接続端子24a,24b,24d〜24gは、z軸方向から平面視したときに、導体層18a,18b,18d〜18gと一致した状態で重なっている。また、接続端子24cは、z軸方向から平面視したときに、導体層18cの一部と重なっている。そして、導体層18cは、x軸方向の正方向側に向かって伸びているので、接続端子24cからはみ出している。

【0022】

ここで、導体層18と接続端子24との接続状態について、図1(b)を参照しながら説明する。導体層18a〜18gと接続端子24a〜24gとは、互いに接触することにより、互いに電気的に接続されている。より詳細には、導体層18における接続端子24との接触面は、導体層18cの接触面以外の部分(すなわち、接続端子24cからはみ出している部分)よりも粗い表面粗さを有している。すなわち、導体層18における接続端子24との接触面は、粗面化されている。具体的には、導体層18における接続端子24との接触面は、Ra=1μm〜10μm程度の表面粗さを有している。そして、導体層18と接続端子24とが押し付けられている。導体層18はCuにより作製され、接続端子24はAuにより作製されている。よって、導体層18の方が接続端子24よりも硬い材料により構成されている。したがって、導体層18は、図1(b)に示すように、接続端子24に対して減り込む。その結果、導体層18と接続端子24とが強固に接続されるようになる。

【0023】

ところで、回路基板10は、接続端子24の間隔が小さな電子部品20を実装することができる構成を有している。以下に、かかる構成について説明する。

【0024】

導体層18a〜18gにはそれぞれ、図3に示すように、ビアホール導体b3が接続されている。ただし、導体層18と接続されているビアホール導体b3の内の少なくとも一部は、z軸方向から平面視したときに、接続端子24と重なっていない。より詳細には、導体層18a,18b,18d〜18gと接続されているビアホール導体b3は、z軸方向から平面視したときに、接続端子24a,24b,24d〜24gと重なっている。一方、導体層18cと接続されているビアホール導体b3は、z軸方向から平面視したときに、接続端子24cとは重なっていない。すなわち、回路基板10では、複数の接続端子24の内、最も近接している2つの接続端子24b,24cに対応する2つの導体層18b,18cと接続されている2つビアホール導体b3の少なくともいずれか一方は、z軸方向から平面視したときに、最も近接している2つの接続端子24b,24cと重なっていない。そして、導体層18cと接続されているビアホール導体b3は、z軸方向から平面視したときに、導体層18cが電子部品20からはみ出している部分において該導体層18cと接続されている。

【0025】

(回路基板の製造方法)

以下に、回路基板10の製造方法について図面を参照しながら説明する。以下では、一つの回路基板10が作製される場合を例にとって説明するが、実際には、大判のフレキシブルシートが積層及びカットされることにより、同時に複数の回路基板10が作製される。図4及び図5は、回路基板10の製造工程を示した断面構造図である。

【0026】

まず、フレキシブルシート14b〜14gに対して、図2に示す導体層16、導体層18及びビアホール導体b1〜b5を形成する。以下では、フレキシブルシート14eに導体層16e、導体層18及びビアホール導体b3を形成する工程を例にとって説明する。

【0027】

図4(a)に示すように、厚さが5μm〜50μmの銅箔116eが表面の全面に形成された複数のフレキシブルシート14eを準備する。

【0028】

次に、図4(b)に示すように、フレキシブルシート14eのビアホール導体b3が形成される位置に対して、裏面側からレーザービームを照射して、ビアホールhを形成する。この際、ビアホールhが銅箔116eを貫通しないように、比較的に強度の弱いレーザービームを複数回照射することにより、ビアホールhを形成する。

【0029】

次に、図4(c)に示すように、フレキシブルシート14eに形成したビアホールhに対して、錫及び銀の合金を主成分とする導電性ペーストを充填し、ビアホール導体b3を形成する。

【0030】

次に、図4(d)に示すように、フォトリソグラフィ工程により、導体層16e及び導体層18をフレキシブルシート14eの表面に形成する。具体的には、フレキシブルシート14eの銅箔116e上に、導体層16e及び導体層18と同じ形状のレジストを印刷する。そして、銅箔116eに対してエッチング処理を施すことにより、レジストにより覆われていない部分の銅箔116eを除去する。その後、レジストを除去する。これにより、導体層16e及び導体層18がフレキシブルシート14eの表面に形成される。以上の工程により、導体層18が設けられたフレキシブルシート14eが準備される。

【0031】

なお、フレキシブルシート14b〜14d,14f,14gに対して、図2に示す導体層16及びビアホール導体b1,b2,b4,b5を形成する工程については、フレキシブルシート14eに導体層16e、導体層18及びビアホール導体b3を形成する工程と同じであるので説明を省略する。ただし、フレキシブルシート14gについては、その裏面に導体層16gが設けられている。そのため、フレキシブルシート14gに導体層16gを形成する工程については、フレキシブルシート14eに導体層16e及び導体層18を形成する工程の表裏を反転させて行う必要がある。また、フレキシブルシート14c,14dには、打ち抜き加工により空白領域B1,B2を形成する必要がある。

【0032】

次に、図4(e)に示すように、フェノール系樹脂又はアクリル系樹脂(例えば、アクリレート又はメタクリレート)等のバインダー樹脂を主成分とする接着剤130を導体層18に塗布する。

【0033】

次に、図4(f)に示すように、導体層18と接続端子24を対向させて、フレキシブルシート14e上に電子部品20を実装する。これにより、導体層18と接続端子24とは、接着剤130を介して仮固定される。

【0034】

次に、図5に示すように、フレキシブルシート14a〜14gをz軸方向の正方向側から負方向側へとこの順に並ぶように積層する。この際、図5に示すように、電子部品20は、空洞B内に収容され、電子部品20の周囲(x軸方向の両側及びz軸方向の正方向側)には隙間が存在している。そして、フレキシブルシート14a〜14gに対してz軸方向の両側から圧力を加えると共に、フレキシブルシート14a〜14gに対して加熱を施す。本実施形態では、150℃の温度及び2ニュートン(N)×接続端子24の数(本実施形態では、7個)の大きさの力で5秒間、フレキシブルシート14を加熱及び圧着する。すなわち、フレキシブルシート14の135mm×135mmの面を2×7/(0.135×0.135)=768Paの圧力でプレスする。これにより、更に、接着剤130は、加熱により消失し、導体層18は、接続端子24に対して減り込む。その結果、導体層18と接続端子24とが強固に接続される。更に、フレキシブルシート14の主面が軟化・流動し、隣接するフレキシブルシート14同士が強固に接合して、積層体12が得られる。更に、軟化・流動したフレキシブルシート14は、電子部品20の周囲の空洞Bを埋める。これにより、電子部品20がフレキシブルシート14により保持される。以上の工程を経て、図1に示す回路基板10が得られる。

【0035】

なお、前記の通り、フレキシブルシート14の圧着時において、フレキシブルシート14の一部が軟化・流動し、接着剤130が消失する。よって、接着剤130の消失温度は、フレキシブルシート14の軟化・流動開始温度よりも低いことが望ましい。

【0036】

(効果)

回路基板10は、接続端子24の間隔が小さな電子部品20を実装できる。より詳細には、特許文献1に記載のプリント基板では、導電性組成物に対して導体パターンが接続されているので、大きな径の導電性組成物しか得ることができない。そのため、該プリント基板では、小さな間隔で導電性組成物を配置することが困難である。その結果、接続端子の間隔が小さな電子素子を導電性組成物上に実装することが困難である。

【0037】

そこで、回路基板10では、複数の接続端子24の内、最も近接している2つの接続端子24b,24cに対応する2つの導体層18b,18cと接続されている2つビアホール導体b3の少なくともいずれか一方は、z軸方向から平面視したときに、最も近接している2つの接続端子24b,24cと重なっていない。そして、導体層18cと接続されているビアホール導体b3は、z軸方向から平面視したときに、導体層18cが電子部品20からはみ出している部分において該導体層18cと接続されている。これにより、導体層18bと接続されているビアホール導体b3と導体層18cと接続されているビアホール導体b3との間隔を、接続端子24b,24cの間隔よりも大きくできる。その結果、回路基板10は、接続端子24b,24cの間隔が2つのビアホール導体b3を最も近接させることができる間隔よりも小さい場合であっても、電子部品20を実装できる。

【0038】

また、回路基板10では、導体層18がCuにより作製され、接続端子24がAuにより作製されている。これにより、導体層18の方が接続端子24よりも硬くなる。更に、導体層18における接続端子24との接触面は、粗面化されている。これにより、フレキシブルシート14の圧着時に、導体層18は、接続端子24に対して減り込むようになる。その結果、導体層18と接続端子24とがより確実に接続されるようになる。

【0039】

また、回路基板10では、導体層18は、接続端子24に対して減り込んでいる。故に、導体層18と接続端子24とは、金属結合をしているのではなく、接触しているだけである。故に、外力が加わって積層体12が変形させられた場合には、導体層18と接続端子24とは、接触したままで僅かにずれることができる。よって、回路基板10では、積層体12が変形させられた場合であっても、導体層18と接続端子24との接続が切れることを抑制できる。

【0040】

また、回路基板10の製造方法では、接着剤130により、導体層18と接続端子24とが仮固定されている。そのため、導体層18と接続端子24との接続が、圧着時の外力や真空引き等によってずれてしまうことが防止される。その結果、電子部品20をフレキシブルシート14eに対して正確に実装することが可能となるので、接続端子24の間隔が狭い電子部品20を回路基板10に実装させることが可能となる。

【0041】

更に、回路基板10の製造方法では、空洞Bが電子部品20よりも僅かに大きく形成されることにより、積層・圧着時に電子部品20がフレキシブルシート14により押さえつけられて、接続端子24が導体層18からずれてしまうことが防止される。

【0042】

(変形例)

以下に、変形例に係る回路基板について図面を参照しながら説明する。図6は、第1の変形例に係る回路基板10の拡大図である。図6は、図1(b)の拡大図に相当するものである。

【0043】

第1の変形例に係る回路基板10では、導体層18fと接続端子24fとの境界部分40において、導体層18fの材料(Cu)と接続端子24fの材料(Au)とが合金化されている。これにより、導体層18fと接続端子24fとが接続されている。なお、他の導体層18gと他の接続端子24gとも、導体層18fと接続端子24fと同様に、境界部分40が合金化されることにより接続されている。

【0044】

導体層18と接続端子24とを合金化により接続する場合には、フレキシブルシート14の圧着時における温度、圧力及び時間を調整すればよい。具体的には、190℃の温度及び1N×接続端子24の数(本実施形態では、7個)の大きさの力で15秒間、フレキシブルシート14を加熱及び圧着すればよい。

【0045】

第1の変形例に係る回路基板10では、導体層18及び接続端子24が合金化した境界部分40は、非常に薄い。そのため、導体層18と接続端子24との境界部分40において、不要なインピーダンスが発生しにくい。

【0046】

また、第1の変形例に係る回路基板10では、導体層18と接続端子24とは、境界部分40が合金化することにより接続されている。よって、第1の変形例に係る回路基板10では、前記実施形態に係る回路基板10に比べて、より強固に導体層18と接続端子24とが接続されるようになる。

【0047】

なお、前記説明では、導体層18が接続端子24に対して減り込むことにより、導体層18と接続端子24とが接続されることと、導体層18と接続端子24との境界部分40が合金化されることにより、導体層18と接続端子24とが接続されることとを別々に説明した。しかしながら、回路基板10では、2つの接続方式が混在していてもよい。

【0048】

次に、第2の変形例に係る回路基板について図面を参照しながら説明する。図7は、第2の変形例に係る回路基板10aの分解図である。

【0049】

回路基板10では、図2に示すように、導体層18と接続されているビアホール導体b3は、該導体層18が設けられているフレキシブルシート14eに設けられている。一方、回路基板10aでは、図7に示すように、電子部品20が実装されているフレキシブルシート14eは、z軸方向の最も負方向側に位置している。よって、この場合には、導体層18は、図7に示すように、電子部品20が実装されているフレキシブルシート14eのz軸方向の正方向側に位置するフレキシブルシート14dに設けられているビアホール導体b6と接続されている。以上のような構成を有する回路基板10aにおいても、回路基板10と同様に、接続端子24の間隔が小さな電子部品20を実装できる。

【0050】

次に、第3の変形例に係る回路基板について図面を参照しながら説明する。図8は、第3の変形例に係る回路基板10のフレキシブルシート14e及び電子部品20を平面視した図である。

【0051】

図8に示すように、電子部品20は、z軸方向から平面視したときに、長方形状をなしている。そして、電子部品20の角は、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重なっている。

【0052】

なお、第3の変形例に係る回路基板10では、接続端子24bと接続端子24cとが最も近接している。そして、接続端子24bに対応する導体層18bに接続されているビアホール導体b3が、z軸方向から平面視したときに、接続端子24bと重なっていない。

【0053】

電子部品20の角には応力が集中しやすい。そこで、第3の変形例に係る回路基板10では、電子部品20の角を、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重ねることにより、回路基板10を補強している。

【0054】

次に、第4の変形例に係る回路基板について図面を参照しながら説明する。図9は、第4の変形例に係る回路基板10のフレキシブルシート14e,14f及び電子部品20を平面視した図である。なお、図9では、ビアホール導体b3が接続されている導体層16fのみを図示し、その他の導体層16fについては省略した。また、導体層16eについても、図面が煩雑になることを防止するために省略した。

【0055】

図9に示すように、導体層18a〜18fは、z軸方向から平面視したときに、電子部品20からはみ出している。そして、複数の導体層18a〜18fは、電子部品20から離れるにしたがって線幅が太くなる形状をなしている。

【0056】

第4の変形例に係る回路基板10によれば、導体層18a〜18fが前記構造をなしていることにより、接続端子24の間隔が小さい場合であっても、導体層18を接続することが可能となる。

【0057】

次に、第5の変形例に係る回路基板について図面を参照しながら説明する。図10は、第5の変形例に係る回路基板10のフレキシブルシート14e,14f及び電子部品20を平面視した図である。なお、図10では、ビアホール導体b3が接続されている導体層16fのみを図示し、その他の導体層16fについては省略した。

【0058】

図10に示すように、電子部品20は、z軸方向から平面視したときに、長方形状をなしている。そして、電子部品20の角は、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重なっている。

【0059】

なお、第5の変形例に係る回路基板10では、接続端子24bと接続端子24cとが最も近接している。そして、接続端子24bに対応する導体層18bに接続されているビアホール導体b3が、z軸方向から平面視したときに、接続端子24bと重なっていない。

【0060】

また、4つの導体層16fはそれぞれ、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重なっており、ビアホール導体b3により接続されている。該4つの導体層16fは、配線として用いられている。

【0061】

以上のような第5の変形例に係る電子部品10によれば、配線として用いられる導体層16fは、導体層18a,18b,18f,18gと重なっている。これにより、導体層16fは、導体層18a,18b,18f,18gにより、外部からの応力によって破損することが抑制されている。

【0062】

なお、回路基板10では、導体層18cと接続されているビアホール導体b3のみが、z軸方向から平面視したときに、接続端子24cと重なっていない。しかしながら、導体層18c以外の導体層18と接続されているビアホール導体b3も、z軸方向から平面視したときに、接続端子24と重なっていなくてもよい。回路基板10では、所定間隔以下の間隔で配置されている2つの接続端子24に対応する導体層18と接続されているビアホール導体b3の少なくとも一方が、2つの接続端子24と重なっていなければよい。なお、所定間隔とは、2つのビアホール導体b3を最も近接させることができる間隔である。

【0063】

なお、回路基板10では、電子部品20を収容するための空洞Bを形成するために、フレキシブルシート14の一部が打ち抜かれて空白領域B1,B2が形成されていた。しかしながら、電子部品20のz軸方向の厚みが20μm〜100μm程度であるときには、フレキシブルシート14は、その可撓性により電子部品20による段差を吸収することができる場合がある。よって、この場合には、フレキシブルシート14に空白領域B1,B2を形成する必要がない。また、フレキシブルシート14c,14dに空白領域B1,B2を設けることなく、フレキシブルシート14c,14dの軟化・流動を利用して、電子部品20に実装してもよい。

【0064】

なお、回路基板10において、接続端子24における導体層18との接触面は、導体層18cの接触面以外の部分よりも粗い表面粗さを有していてもよい。また、導体層18における接続端子24との接触面及び接続端子24における導体層18との接触面が、導体層18cの接触面以外の部分よりも粗い表面粗さを有していてもよい。

【0065】

なお、回路基板10の製造方法では、接着剤130は、導体層18のz軸方向の正方向側の主面のみを覆うように塗布されている。しかしながら、接着剤130は、導体層18の側面も覆っていてもよい。これにより、導体層18が外気にさらされることによって酸化されることが抑制される。

【産業上の利用可能性】

【0066】

以上のように、本発明は、回路基板に有用であり、特に、接続端子の間隔が小さな電子部品を実装することができる点において優れている。

【符号の説明】

【0067】

b1〜b6 ビアホール導体

10,10a 回路基板

12 積層体

14a〜14g フレキシブルシート

16b〜16g,18a〜18g 導体層

24 接続端子

20 電子部品

22 基板

40 境界部分

130 接着剤

【技術分野】

【0001】

本発明は、回路基板に関し、より特定的には、複数の絶縁体層が積層されてなる積層体を備えた回路基板に関する。

【背景技術】

【0002】

従来の回路基板としては、例えば、特許文献1に記載のプリント基板が知られている。該プリント基板では、導体パターン及び導電性組成物が絶縁基材内に設けられている。絶縁基材は、複数の樹脂フィルムが積層されて構成されている。導体パターンは、樹脂フィルム上に設けられている導体層である。導電性組成物は、樹脂フィルムを貫通するビアホールに導電ペーストを充填して焼結させて得られたビアホール導体であり、その一端において導体パターンと接続されている。

【0003】

更に、回路基板では、絶縁基材内に設けられている空洞内に電気素子が収容されている。電気素子は、導電性組成物の他端上に実装されている。これにより、電気素子と導体パターンとは、導電性組成物により電気的に接続されている。

【0004】

ところで、特許文献1に記載のプリント基板は、以下に説明するように、接続端子の間隔が小さな電子素子を導電性組成物上に実装することが困難であるという問題を有している。より詳細には、プリント基板では、ビアホール導体である導電性組成物に電子素子の接続端子が直接に接続されている。そして、導電性組成物は、以下の工程により作成される。

【0005】

まず、導電性組成物が接続されている導体パターンに孔が空かないように、導体パターンが設けられている主面の反対側の主面から、樹脂フィルムに対してビームを照射し、ビアホールを形成する。次に、ビアホールに対して、導電ペーストを充填する。最後に、導電ペーストを焼結して、導電性組成物を得る。

【0006】

前記導電性組成物では、ビアホールの形成時に、導体パターンに孔が空かないように、比較的に強度が弱いビームを複数回照射することが一般的である。このように、比較的に強度が弱いビームを複数回照射すると、ビームの照射の度にビアホールの径は、広がってしまう。したがって、特許文献1に記載のプリント基板では、大きな径の導電性組成物しか得ることができない。そのため、該プリント基板では、小さな間隔で導電性組成物を配置することが困難である。その結果、接続端子の間隔が小さな電子素子を導電性組成物上に実装することが困難である。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3867593号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

そこで、本発明の目的は、接続端子の間隔が小さな電子部品を実装できる回路基板を提供することである。

【課題を解決するための手段】

【0009】

本発明の一形態に係る回路基板は、複数の接続端子を有する電子部品と、前記電子部品を内蔵するための空白領域が設けられた第1の絶縁体層と、該空白領域が設けられた第2の絶縁体層とが積層されて構成されている積層体と、前記第2の絶縁体層に設けられ、一端が前記複数の接続端子にそれぞれ接続されている複数の導体層と、前記積層体内に設けられ、かつ、前記複数の導体層の他端にそれぞれ接続されている複数のビアホール導体と、を備えており、前記第1の絶縁体層および前記第2の絶縁体層は、熱可塑性樹脂によって構成されており、前記積層体は、前記熱可塑性樹脂の軟化・流動によって前記第1の絶縁体層及び前記第2の絶縁体層が接合されてなり、前記第1の絶縁体層の前記空白領域は、積層方向から平面視したときに、前記電子部品よりも大きく、前記複数のビアホール導体は、前記第1の絶縁体層において前記空白領域の周りに配置されていること、を特徴とする。

【発明の効果】

【0010】

本発明によれば、接続端子の間隔が小さな電子部品を実装することができる。

【図面の簡単な説明】

【0011】

【図1】図1(a)は、本発明の一実施形態に係る回路基板の断面構造図である。図1(b)は、回路基板の拡大図である。

【図2】図1の回路基板の分解図である。

【図3】図2のフレキシブルシート及び電子部品を平面視した図である。

【図4】回路基板の製造工程を示した断面構造図である。

【図5】回路基板の製造工程を示した断面構造図である。

【図6】第1の変形例に係る回路基板の拡大図である。

【図7】第2の変形例に係る回路基板の分解図である。

【図8】第3の変形例に係る回路基板のフレキシブルシート及び電子部品を平面視した図である。

【図9】第4の変形例に係る回路基板のフレキシブルシート及び電子部品を平面視した図である。

【図10】第5の変形例に係る回路基板のフレキシブルシート及び電子部品を平面視した図である。

【発明を実施するための形態】

【0012】

以下に、本発明の実施形態に係る回路基板について図面を参照しながら説明する。

【0013】

(回路基板の構成)

以下に、本発明の一実施形態に係る回路基板の構成について図面を参照しながら説明する。図1(a)は、本発明の一実施形態に係る回路基板10の断面構造図である。図1(b)は、回路基板10の拡大図である。図2は、図1の回路基板10の分解図である。図3は、図2のフレキシブルシート14e及び電子部品20を平面視した図である。以下では、回路基板10の積層方向をz軸方向と定義し、図1の紙面の左右方向をx軸方向と定義し、図1の紙面の垂直方向をy軸方向と定義する。また、フレキシブルシート14の表面とは、z軸方向の正方向側に位置する面を指し、フレキシブルシート14の裏面とは、z軸方向の負方向側に位置する面を指す。

【0014】

回路基板10は、図1(a)及び図3に示すように、積層体12、導体層16(16b〜16g),18(18a〜18g)、電子部品20及びビアホール導体b1〜b5を備えている。

【0015】

積層体12は、図2に示すように、複数(図2では7枚)のフレキシブルシート(絶縁体層)14(14a〜14g)が積層されて構成され、直方体状をなしている。積層体12は、外力により変形することができる。

【0016】

フレキシブルシート14は、可撓性材料(例えば、液晶ポリマーやポリイミド等の熱可塑性樹脂)からなり、長方形状をなしている。また、フレキシブルシート14の厚みは、25μm〜100μm程度である。フレキシブルシート14c,14dには、図2に示すように、後述する電子部品20を収容する空洞を形成するための空白領域B1,B2が設けられている。空白領域B1,B2は、フレキシブルシート14c,14dの中央部分を長方形状に打ち抜いて形成されている。空白領域B1,B2は、z軸方向から平面視したときに、電子部品20よりも僅かに大きくなるように形成されている。なお、図1では、各フレキシブルシート14の主面同士が密接に接合しているので、その境界を図示していない。また、以下では、フレキシブルシート14のz軸方向の正方向側の主面を表面と称し、フレキシブルシート14のz軸方向の負方向側の主面を裏面と称す。

【0017】

導体層16は、図2に示すように、積層体12内に設けられており、配線導体、コイル導体又はコンデンサ導体等である。より詳細には、導体層16b〜16fはそれぞれ、フレキシブルシート14b〜14fの表面に設けられており、例えば、銅箔により作製されている。また、導体層16gは、フレキシブルシート14gの裏面に設けられており、例えば、銅箔により作製されている。なお、導体層16については、図面が煩雑になることを避けるために、代表的なものにのみ参照符号を付してある。

【0018】

導体層18は、図2及び図3に示すように、積層体12内に設けられており、電子部品20が実装されるランドとして機能する。導体層18は、フレキシブルシート14eの表面に設けられており、例えば、銅箔により作製されている。導体層18a,18b,18d〜18gは、z軸方向から平面視したときに、電子部品20と全体において重なるように設けられている。一方、導体層18cは、z軸方向から平面視したときに、電子部品20と一部において重なるように設けられている。よって、導体層18cの残余の部分は、z軸方向から平面視したときに、本体22からはみ出している。

【0019】

ビアホール導体b1〜b5はそれぞれ、図2に示すように、積層体12内に設けられており、フレキシブルシート14b,14c,14e〜14gをz軸方向に貫通するように設けられている。ビアホール導体b1〜b5は、z軸方向の両側に位置する導体層16,18を電気的に接続している。以上のように、導体層16,18及びビアホール導体b1〜b5は、互いに接続されることにより、回路を構成している。なお、ビアホール導体b1〜b5については、図面が煩雑になることを避けるために、代表的なものにのみ参照符号を付してある。

【0020】

電子部品20は、積層体12に内蔵されており、RFID(Radio Frequency IDentification)用の無線ICチップや、デジタルスチルカメラに用いられる画像処理用のICチップ等の半導体チップ(能動部品)、或いは、チップコンデンサやチップ抵抗などの受動部品である。電子部品20は、図1ないし図3に示すように、基板22及び接続端子24(24a〜24g)を有している。基板22は、シリコンやセラミックのような比較的に硬い材料により構成されており、積層体12のように容易に変形することができない。また、電子部品20が例えば半導体チップである場合、基板22の内部には半導体集積回路が形成されている。

【0021】

接続端子24は、基板22のz軸方向の負方向側の主面に設けられており、例えば、AuやCu等により作製されている。接続端子24a〜24gは、図3に示すように、電子部品20が導体層18a〜18gに実装された際に、対応する導体層18a〜18gと電気的に接続されている。具体的には、接続端子24a,24b,24d〜24gは、z軸方向から平面視したときに、導体層18a,18b,18d〜18gと一致した状態で重なっている。また、接続端子24cは、z軸方向から平面視したときに、導体層18cの一部と重なっている。そして、導体層18cは、x軸方向の正方向側に向かって伸びているので、接続端子24cからはみ出している。

【0022】

ここで、導体層18と接続端子24との接続状態について、図1(b)を参照しながら説明する。導体層18a〜18gと接続端子24a〜24gとは、互いに接触することにより、互いに電気的に接続されている。より詳細には、導体層18における接続端子24との接触面は、導体層18cの接触面以外の部分(すなわち、接続端子24cからはみ出している部分)よりも粗い表面粗さを有している。すなわち、導体層18における接続端子24との接触面は、粗面化されている。具体的には、導体層18における接続端子24との接触面は、Ra=1μm〜10μm程度の表面粗さを有している。そして、導体層18と接続端子24とが押し付けられている。導体層18はCuにより作製され、接続端子24はAuにより作製されている。よって、導体層18の方が接続端子24よりも硬い材料により構成されている。したがって、導体層18は、図1(b)に示すように、接続端子24に対して減り込む。その結果、導体層18と接続端子24とが強固に接続されるようになる。

【0023】

ところで、回路基板10は、接続端子24の間隔が小さな電子部品20を実装することができる構成を有している。以下に、かかる構成について説明する。

【0024】

導体層18a〜18gにはそれぞれ、図3に示すように、ビアホール導体b3が接続されている。ただし、導体層18と接続されているビアホール導体b3の内の少なくとも一部は、z軸方向から平面視したときに、接続端子24と重なっていない。より詳細には、導体層18a,18b,18d〜18gと接続されているビアホール導体b3は、z軸方向から平面視したときに、接続端子24a,24b,24d〜24gと重なっている。一方、導体層18cと接続されているビアホール導体b3は、z軸方向から平面視したときに、接続端子24cとは重なっていない。すなわち、回路基板10では、複数の接続端子24の内、最も近接している2つの接続端子24b,24cに対応する2つの導体層18b,18cと接続されている2つビアホール導体b3の少なくともいずれか一方は、z軸方向から平面視したときに、最も近接している2つの接続端子24b,24cと重なっていない。そして、導体層18cと接続されているビアホール導体b3は、z軸方向から平面視したときに、導体層18cが電子部品20からはみ出している部分において該導体層18cと接続されている。

【0025】

(回路基板の製造方法)

以下に、回路基板10の製造方法について図面を参照しながら説明する。以下では、一つの回路基板10が作製される場合を例にとって説明するが、実際には、大判のフレキシブルシートが積層及びカットされることにより、同時に複数の回路基板10が作製される。図4及び図5は、回路基板10の製造工程を示した断面構造図である。

【0026】

まず、フレキシブルシート14b〜14gに対して、図2に示す導体層16、導体層18及びビアホール導体b1〜b5を形成する。以下では、フレキシブルシート14eに導体層16e、導体層18及びビアホール導体b3を形成する工程を例にとって説明する。

【0027】

図4(a)に示すように、厚さが5μm〜50μmの銅箔116eが表面の全面に形成された複数のフレキシブルシート14eを準備する。

【0028】

次に、図4(b)に示すように、フレキシブルシート14eのビアホール導体b3が形成される位置に対して、裏面側からレーザービームを照射して、ビアホールhを形成する。この際、ビアホールhが銅箔116eを貫通しないように、比較的に強度の弱いレーザービームを複数回照射することにより、ビアホールhを形成する。

【0029】

次に、図4(c)に示すように、フレキシブルシート14eに形成したビアホールhに対して、錫及び銀の合金を主成分とする導電性ペーストを充填し、ビアホール導体b3を形成する。

【0030】

次に、図4(d)に示すように、フォトリソグラフィ工程により、導体層16e及び導体層18をフレキシブルシート14eの表面に形成する。具体的には、フレキシブルシート14eの銅箔116e上に、導体層16e及び導体層18と同じ形状のレジストを印刷する。そして、銅箔116eに対してエッチング処理を施すことにより、レジストにより覆われていない部分の銅箔116eを除去する。その後、レジストを除去する。これにより、導体層16e及び導体層18がフレキシブルシート14eの表面に形成される。以上の工程により、導体層18が設けられたフレキシブルシート14eが準備される。

【0031】

なお、フレキシブルシート14b〜14d,14f,14gに対して、図2に示す導体層16及びビアホール導体b1,b2,b4,b5を形成する工程については、フレキシブルシート14eに導体層16e、導体層18及びビアホール導体b3を形成する工程と同じであるので説明を省略する。ただし、フレキシブルシート14gについては、その裏面に導体層16gが設けられている。そのため、フレキシブルシート14gに導体層16gを形成する工程については、フレキシブルシート14eに導体層16e及び導体層18を形成する工程の表裏を反転させて行う必要がある。また、フレキシブルシート14c,14dには、打ち抜き加工により空白領域B1,B2を形成する必要がある。

【0032】

次に、図4(e)に示すように、フェノール系樹脂又はアクリル系樹脂(例えば、アクリレート又はメタクリレート)等のバインダー樹脂を主成分とする接着剤130を導体層18に塗布する。

【0033】

次に、図4(f)に示すように、導体層18と接続端子24を対向させて、フレキシブルシート14e上に電子部品20を実装する。これにより、導体層18と接続端子24とは、接着剤130を介して仮固定される。

【0034】

次に、図5に示すように、フレキシブルシート14a〜14gをz軸方向の正方向側から負方向側へとこの順に並ぶように積層する。この際、図5に示すように、電子部品20は、空洞B内に収容され、電子部品20の周囲(x軸方向の両側及びz軸方向の正方向側)には隙間が存在している。そして、フレキシブルシート14a〜14gに対してz軸方向の両側から圧力を加えると共に、フレキシブルシート14a〜14gに対して加熱を施す。本実施形態では、150℃の温度及び2ニュートン(N)×接続端子24の数(本実施形態では、7個)の大きさの力で5秒間、フレキシブルシート14を加熱及び圧着する。すなわち、フレキシブルシート14の135mm×135mmの面を2×7/(0.135×0.135)=768Paの圧力でプレスする。これにより、更に、接着剤130は、加熱により消失し、導体層18は、接続端子24に対して減り込む。その結果、導体層18と接続端子24とが強固に接続される。更に、フレキシブルシート14の主面が軟化・流動し、隣接するフレキシブルシート14同士が強固に接合して、積層体12が得られる。更に、軟化・流動したフレキシブルシート14は、電子部品20の周囲の空洞Bを埋める。これにより、電子部品20がフレキシブルシート14により保持される。以上の工程を経て、図1に示す回路基板10が得られる。

【0035】

なお、前記の通り、フレキシブルシート14の圧着時において、フレキシブルシート14の一部が軟化・流動し、接着剤130が消失する。よって、接着剤130の消失温度は、フレキシブルシート14の軟化・流動開始温度よりも低いことが望ましい。

【0036】

(効果)

回路基板10は、接続端子24の間隔が小さな電子部品20を実装できる。より詳細には、特許文献1に記載のプリント基板では、導電性組成物に対して導体パターンが接続されているので、大きな径の導電性組成物しか得ることができない。そのため、該プリント基板では、小さな間隔で導電性組成物を配置することが困難である。その結果、接続端子の間隔が小さな電子素子を導電性組成物上に実装することが困難である。

【0037】

そこで、回路基板10では、複数の接続端子24の内、最も近接している2つの接続端子24b,24cに対応する2つの導体層18b,18cと接続されている2つビアホール導体b3の少なくともいずれか一方は、z軸方向から平面視したときに、最も近接している2つの接続端子24b,24cと重なっていない。そして、導体層18cと接続されているビアホール導体b3は、z軸方向から平面視したときに、導体層18cが電子部品20からはみ出している部分において該導体層18cと接続されている。これにより、導体層18bと接続されているビアホール導体b3と導体層18cと接続されているビアホール導体b3との間隔を、接続端子24b,24cの間隔よりも大きくできる。その結果、回路基板10は、接続端子24b,24cの間隔が2つのビアホール導体b3を最も近接させることができる間隔よりも小さい場合であっても、電子部品20を実装できる。

【0038】

また、回路基板10では、導体層18がCuにより作製され、接続端子24がAuにより作製されている。これにより、導体層18の方が接続端子24よりも硬くなる。更に、導体層18における接続端子24との接触面は、粗面化されている。これにより、フレキシブルシート14の圧着時に、導体層18は、接続端子24に対して減り込むようになる。その結果、導体層18と接続端子24とがより確実に接続されるようになる。

【0039】

また、回路基板10では、導体層18は、接続端子24に対して減り込んでいる。故に、導体層18と接続端子24とは、金属結合をしているのではなく、接触しているだけである。故に、外力が加わって積層体12が変形させられた場合には、導体層18と接続端子24とは、接触したままで僅かにずれることができる。よって、回路基板10では、積層体12が変形させられた場合であっても、導体層18と接続端子24との接続が切れることを抑制できる。

【0040】

また、回路基板10の製造方法では、接着剤130により、導体層18と接続端子24とが仮固定されている。そのため、導体層18と接続端子24との接続が、圧着時の外力や真空引き等によってずれてしまうことが防止される。その結果、電子部品20をフレキシブルシート14eに対して正確に実装することが可能となるので、接続端子24の間隔が狭い電子部品20を回路基板10に実装させることが可能となる。

【0041】

更に、回路基板10の製造方法では、空洞Bが電子部品20よりも僅かに大きく形成されることにより、積層・圧着時に電子部品20がフレキシブルシート14により押さえつけられて、接続端子24が導体層18からずれてしまうことが防止される。

【0042】

(変形例)

以下に、変形例に係る回路基板について図面を参照しながら説明する。図6は、第1の変形例に係る回路基板10の拡大図である。図6は、図1(b)の拡大図に相当するものである。

【0043】

第1の変形例に係る回路基板10では、導体層18fと接続端子24fとの境界部分40において、導体層18fの材料(Cu)と接続端子24fの材料(Au)とが合金化されている。これにより、導体層18fと接続端子24fとが接続されている。なお、他の導体層18gと他の接続端子24gとも、導体層18fと接続端子24fと同様に、境界部分40が合金化されることにより接続されている。

【0044】

導体層18と接続端子24とを合金化により接続する場合には、フレキシブルシート14の圧着時における温度、圧力及び時間を調整すればよい。具体的には、190℃の温度及び1N×接続端子24の数(本実施形態では、7個)の大きさの力で15秒間、フレキシブルシート14を加熱及び圧着すればよい。

【0045】

第1の変形例に係る回路基板10では、導体層18及び接続端子24が合金化した境界部分40は、非常に薄い。そのため、導体層18と接続端子24との境界部分40において、不要なインピーダンスが発生しにくい。

【0046】

また、第1の変形例に係る回路基板10では、導体層18と接続端子24とは、境界部分40が合金化することにより接続されている。よって、第1の変形例に係る回路基板10では、前記実施形態に係る回路基板10に比べて、より強固に導体層18と接続端子24とが接続されるようになる。

【0047】

なお、前記説明では、導体層18が接続端子24に対して減り込むことにより、導体層18と接続端子24とが接続されることと、導体層18と接続端子24との境界部分40が合金化されることにより、導体層18と接続端子24とが接続されることとを別々に説明した。しかしながら、回路基板10では、2つの接続方式が混在していてもよい。

【0048】

次に、第2の変形例に係る回路基板について図面を参照しながら説明する。図7は、第2の変形例に係る回路基板10aの分解図である。

【0049】

回路基板10では、図2に示すように、導体層18と接続されているビアホール導体b3は、該導体層18が設けられているフレキシブルシート14eに設けられている。一方、回路基板10aでは、図7に示すように、電子部品20が実装されているフレキシブルシート14eは、z軸方向の最も負方向側に位置している。よって、この場合には、導体層18は、図7に示すように、電子部品20が実装されているフレキシブルシート14eのz軸方向の正方向側に位置するフレキシブルシート14dに設けられているビアホール導体b6と接続されている。以上のような構成を有する回路基板10aにおいても、回路基板10と同様に、接続端子24の間隔が小さな電子部品20を実装できる。

【0050】

次に、第3の変形例に係る回路基板について図面を参照しながら説明する。図8は、第3の変形例に係る回路基板10のフレキシブルシート14e及び電子部品20を平面視した図である。

【0051】

図8に示すように、電子部品20は、z軸方向から平面視したときに、長方形状をなしている。そして、電子部品20の角は、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重なっている。

【0052】

なお、第3の変形例に係る回路基板10では、接続端子24bと接続端子24cとが最も近接している。そして、接続端子24bに対応する導体層18bに接続されているビアホール導体b3が、z軸方向から平面視したときに、接続端子24bと重なっていない。

【0053】

電子部品20の角には応力が集中しやすい。そこで、第3の変形例に係る回路基板10では、電子部品20の角を、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重ねることにより、回路基板10を補強している。

【0054】

次に、第4の変形例に係る回路基板について図面を参照しながら説明する。図9は、第4の変形例に係る回路基板10のフレキシブルシート14e,14f及び電子部品20を平面視した図である。なお、図9では、ビアホール導体b3が接続されている導体層16fのみを図示し、その他の導体層16fについては省略した。また、導体層16eについても、図面が煩雑になることを防止するために省略した。

【0055】

図9に示すように、導体層18a〜18fは、z軸方向から平面視したときに、電子部品20からはみ出している。そして、複数の導体層18a〜18fは、電子部品20から離れるにしたがって線幅が太くなる形状をなしている。

【0056】

第4の変形例に係る回路基板10によれば、導体層18a〜18fが前記構造をなしていることにより、接続端子24の間隔が小さい場合であっても、導体層18を接続することが可能となる。

【0057】

次に、第5の変形例に係る回路基板について図面を参照しながら説明する。図10は、第5の変形例に係る回路基板10のフレキシブルシート14e,14f及び電子部品20を平面視した図である。なお、図10では、ビアホール導体b3が接続されている導体層16fのみを図示し、その他の導体層16fについては省略した。

【0058】

図10に示すように、電子部品20は、z軸方向から平面視したときに、長方形状をなしている。そして、電子部品20の角は、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重なっている。

【0059】

なお、第5の変形例に係る回路基板10では、接続端子24bと接続端子24cとが最も近接している。そして、接続端子24bに対応する導体層18bに接続されているビアホール導体b3が、z軸方向から平面視したときに、接続端子24bと重なっていない。

【0060】

また、4つの導体層16fはそれぞれ、z軸方向から平面視したときに、導体層18a,18b,18f,18gと重なっており、ビアホール導体b3により接続されている。該4つの導体層16fは、配線として用いられている。

【0061】

以上のような第5の変形例に係る電子部品10によれば、配線として用いられる導体層16fは、導体層18a,18b,18f,18gと重なっている。これにより、導体層16fは、導体層18a,18b,18f,18gにより、外部からの応力によって破損することが抑制されている。

【0062】

なお、回路基板10では、導体層18cと接続されているビアホール導体b3のみが、z軸方向から平面視したときに、接続端子24cと重なっていない。しかしながら、導体層18c以外の導体層18と接続されているビアホール導体b3も、z軸方向から平面視したときに、接続端子24と重なっていなくてもよい。回路基板10では、所定間隔以下の間隔で配置されている2つの接続端子24に対応する導体層18と接続されているビアホール導体b3の少なくとも一方が、2つの接続端子24と重なっていなければよい。なお、所定間隔とは、2つのビアホール導体b3を最も近接させることができる間隔である。

【0063】

なお、回路基板10では、電子部品20を収容するための空洞Bを形成するために、フレキシブルシート14の一部が打ち抜かれて空白領域B1,B2が形成されていた。しかしながら、電子部品20のz軸方向の厚みが20μm〜100μm程度であるときには、フレキシブルシート14は、その可撓性により電子部品20による段差を吸収することができる場合がある。よって、この場合には、フレキシブルシート14に空白領域B1,B2を形成する必要がない。また、フレキシブルシート14c,14dに空白領域B1,B2を設けることなく、フレキシブルシート14c,14dの軟化・流動を利用して、電子部品20に実装してもよい。

【0064】

なお、回路基板10において、接続端子24における導体層18との接触面は、導体層18cの接触面以外の部分よりも粗い表面粗さを有していてもよい。また、導体層18における接続端子24との接触面及び接続端子24における導体層18との接触面が、導体層18cの接触面以外の部分よりも粗い表面粗さを有していてもよい。

【0065】

なお、回路基板10の製造方法では、接着剤130は、導体層18のz軸方向の正方向側の主面のみを覆うように塗布されている。しかしながら、接着剤130は、導体層18の側面も覆っていてもよい。これにより、導体層18が外気にさらされることによって酸化されることが抑制される。

【産業上の利用可能性】

【0066】

以上のように、本発明は、回路基板に有用であり、特に、接続端子の間隔が小さな電子部品を実装することができる点において優れている。

【符号の説明】

【0067】

b1〜b6 ビアホール導体

10,10a 回路基板

12 積層体

14a〜14g フレキシブルシート

16b〜16g,18a〜18g 導体層

24 接続端子

20 電子部品

22 基板

40 境界部分

130 接着剤

【特許請求の範囲】

【請求項1】

複数の接続端子を有する電子部品と、

前記電子部品を内蔵するための空白領域が設けられた第1の絶縁体層と、該空白領域が設けられた第2の絶縁体層とが積層されて構成されている積層体と、

前記第2の絶縁体層に設けられ、一端が前記複数の接続端子にそれぞれ接続されている複数の導体層と、

前記積層体内に設けられ、かつ、前記複数の導体層の他端にそれぞれ接続されている複数のビアホール導体と、

を備えており、

前記第1の絶縁体層および前記第2の絶縁体層は、熱可塑性樹脂によって構成されており、

前記積層体は、前記熱可塑性樹脂の軟化・流動によって前記第1の絶縁体層及び前記第2の絶縁体層が接合されてなり、

前記第1の絶縁体層の前記空白領域は、積層方向から平面視したときに、前記電子部品よりも大きく、

前記複数のビアホール導体は、前記第1の絶縁体層において前記空白領域の周りに配置されていること、

を特徴とする回路基板。

【請求項2】

前記複数の導体層は、積層方向から平面視したときに、前記電子部品の角と重なるように配置されていること、

を特徴とする請求項1に記載の回路基板。

【請求項3】

前記複数の導体層の線幅は、積層方向から平面視したときに、前記電子部品から離れるにしたがって太くなること、

を特徴とする請求項1に記載の回路基板。

【請求項1】

複数の接続端子を有する電子部品と、

前記電子部品を内蔵するための空白領域が設けられた第1の絶縁体層と、該空白領域が設けられた第2の絶縁体層とが積層されて構成されている積層体と、

前記第2の絶縁体層に設けられ、一端が前記複数の接続端子にそれぞれ接続されている複数の導体層と、

前記積層体内に設けられ、かつ、前記複数の導体層の他端にそれぞれ接続されている複数のビアホール導体と、

を備えており、

前記第1の絶縁体層および前記第2の絶縁体層は、熱可塑性樹脂によって構成されており、

前記積層体は、前記熱可塑性樹脂の軟化・流動によって前記第1の絶縁体層及び前記第2の絶縁体層が接合されてなり、

前記第1の絶縁体層の前記空白領域は、積層方向から平面視したときに、前記電子部品よりも大きく、

前記複数のビアホール導体は、前記第1の絶縁体層において前記空白領域の周りに配置されていること、

を特徴とする回路基板。

【請求項2】

前記複数の導体層は、積層方向から平面視したときに、前記電子部品の角と重なるように配置されていること、

を特徴とする請求項1に記載の回路基板。

【請求項3】

前記複数の導体層の線幅は、積層方向から平面視したときに、前記電子部品から離れるにしたがって太くなること、

を特徴とする請求項1に記載の回路基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−85006(P2013−85006A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2013−26366(P2013−26366)

【出願日】平成25年2月14日(2013.2.14)

【分割の表示】特願2011−535427(P2011−535427)の分割

【原出願日】平成22年10月6日(2010.10.6)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成25年2月14日(2013.2.14)

【分割の表示】特願2011−535427(P2011−535427)の分割

【原出願日】平成22年10月6日(2010.10.6)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]