回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路装置及び電子機器等に関する。

【背景技術】

【0002】

従来より、TCXO(temperature compensated crystal oscillator)と呼ばれる温度補償型水晶発振器が知られている。このTCXOは、例えば携帯端末などの無線機器のRF回路の基準信号源等として用いられている。TCXOを実現する回路装置の従来技術としては例えば特許文献1に開示される技術がある。

【0003】

さて、TCXO等の発振器では、多出力機能を要求されるケースが増えて来ている。即ち、1つの出力信号だけではなく、2つ以上の出力信号を出力する機能が発振器に要求されている。

【0004】

このように複数の出力信号を出力する多出力発振器の回路装置を実現する場合には、発振回路からの信号をバッファリングするバッファー回路に、プリバッファーと、プリバッファーの出力に接続される複数の出力バッファーを設ける手法が考えられる。

【0005】

しかしながら、この手法を採用した場合に、プリバッファーに対しては、最終段の複数の出力バッファーが常時接続される構成になるため、ユーザーの使用条件に関わらずに、最終段の複数の出力バッファーからは、常に出力信号が出力されるようになってしまう。そして、例えば多出力発振器の複数の出力信号のうちの一部しかユーザーが使用していないのに、全ての出力信号が多出力発振器が出力されてしまうと、無駄に電力が消費されたり、EMI(電磁妨害)の要因等になるおそれがある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−7036号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の幾つかの態様によれば、無駄な電力消費やノイズによる悪影響等を抑制できる回路装置及び電子機器等を提供できる。

【課題を解決するための手段】

【0008】

本発明の一態様は、振動子に接続される発振回路と、前記発振回路からの発振信号をバッファリングするバッファー回路とを含み、前記バッファー回路は、前記発振回路からの前記発振信号が入力されるプリバッファーと、前記プリバッファーからの信号が入力され、第1の出力信号を出力する第1の出力バッファーと、前記プリバッファーからの信号が入力され、第2の出力信号を出力する第2の出力バッファーとを含み、第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファーが動作ディスエーブル状態に設定され、第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定される回路装置に関係する。

【0009】

本発明の一態様によれば、発振回路からの発信信号がプリバッファーによりバッファリングされて、第1、第2の出力バッファーに対して出力される。そして第2のモードでは、第1、第2の出力バッファーが共に動作イネーブル状態に設定される。一方、第1のモードでは、第1の出力バッファーが動作イネーブル状態に設定され、第2の出力バッファーが動作ディスエーブル状態に設定されると共に、プリバッファーの駆動能力が第2のモードに比べて低い駆動能力に設定される。従って、プリバッファーの駆動能力を、出力バッファーの負荷容量に応じた適切な駆動能力に設定できるようになる。これにより、例えばプリバッファー等において無駄な電力が消費されたり、ノイズによる悪影響等を抑制することが可能になる。

【0010】

また本発明の一態様では、前記バッファー回路は、前記プリバッファーの出力ノードと前記第2の出力バッファーの入力ノードとの間に設けられるスイッチ回路を含み、前記スイッチ回路は、前記第1のモードではオフ状態に設定され、前記第2のモードではオン状態に設定されてもよい。

【0011】

このようにすれば、第2の出力バッファーが動作ディスエーブル状態に設定される第1のモードでは、スイッチ回路がオフ状態になることで、プリバッファーの出力ノードから第2の出力バッファーが切り離されるようになる。従って、プリバッファー側から見た負荷容量を減らすことができ、無駄な電力消費等を抑制できるようになる。

【0012】

また本発明の一態様では、前記第1の出力バッファー、或いは前記第1の出力バッファー及び前記第2の出力バッファーが、クリップドサイン波の信号を出力するクリップドサイン波出力回路により構成されてもよい。

【0013】

このようにすれば、第1の出力バッファー又は第1及び第2の出力バッファーがクリップドサイン波を出力する回路である場合に、第1のモードにおいてプリバッファーの駆動能力が低く設定されることで、高調波ノイズの発生等を低減できるようになる。

【0014】

また本発明の一態様では、前記クリップドサイン波出力回路は、高電位側電源ノードと出力ノードとの間に設けられる第1のトランジスターと、前記出力ノードと低電位側電源ノードとの間に設けられる第2のトランジスターと、前記第1のトランジスターのゲートノードである第1のゲートノードに対してバイアス電圧を設定する第1のバイアス電圧設定回路と、前記第2のトランジスターのゲートノードである第2のゲートノードに対してバイアス電圧を設定する第2のバイアス電圧設定回路と、前記プリバッファーからの信号が入力される入力ノードと前記第1のゲートノードとの間に設けられる第1のキャパシターと、前記入力ノードと前記第2のゲートノードとの間に設けられる第2のキャパシターとを含んでもよい。

【0015】

このようにすれば、第1のトランジスターの第1のゲートノードのバイアス電圧、第2のトランジスターの第2のゲートノードのバイアス電圧を、各々、第1、第2のバイアス電圧設定回路により設定することで、適切なクリップドサイン波を出力することが可能になる。

【0016】

また本発明の一態様では、前記第1のバイアス電圧設定回路は、前記高電位側電源ノードと前記第1のゲートノードとの間に直列に設けれる第1の抵抗素子及び第1のスイッチ素子と、前記第1のゲートノードと前記低電位側電源ノードとの間に設けられる第2の抵抗素子を含み、前記第2のバイアス電圧設定回路は、前記高電位側電源ノードと前記第2のゲートノードとの間に直列に設けれる第3の抵抗素子及び第2のスイッチ素子と、前記第2のゲートノードと前記低電位側電源ノードとの間に設けられる第4の抵抗素子及び第3のスイッチ素子を含み、動作イネーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオン状態に設定され、前記第2のスイッチ素子がオフ状態に設定され、動作ディスエーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオフ状態に設定され、前記第2のスイッチ素子がオン状態に設定されてもよい。

【0017】

このようにすれば、例えば第1のモードにおいてクリップドサイン波出力回路が動作ディスエーブル状態に設定されると、第1、第3のスイッチ素子がオフ状態に設定され、第2のスイッチ素子がオン状態に設定される。これにより、第1、第2のトランジスターをオフ状態に設定できるようになり、出力信号を非出力状態に設定することが可能になる。

【0018】

また本発明の一態様では、前記第1のキャパシター及び前記第2のキャパシターは、MIM(Metal-Insulator-Metal)構造のキャパシターにより構成され、MIM構造の前記第1のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第1のゲートノードに接続され、MIM構造の前記第2のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第2のゲートノードに接続されてもよい。

【0019】

このようにすれば、クリップドサイン波出力回路の入力ノードの寄生容量を減少させることができ、プリバッファーの充放電電力を減らすことができるため、無駄な電力の消費を抑えることが可能になる。

【0020】

また本発明の一態様では、前記第1の出力バッファーがクリップドサイン波の信号を出力するクリップドサイン波出力回路により構成され、前記第2の出力バッファーが、矩形波の信号を出力する矩形波出力回路により構成されてもよい。

【0021】

このようにすれば、第1の出力バッファーによりクリップドサイン波の信号を外部に供給すると共に、第2の出力バッファーにより矩形波の信号を外部に供給できるようになり、利便性を向上できる。

【0022】

また本発明の一態様では、前記第1の出力バッファー及び前記第2の出力バッファーが動作ディスエーブル状態に設定された場合に、前記プリバッファーが動作ディスエーブル状態に設定されてもよい。

【0023】

このようにすれば、第1、第2の出力バッファーが動作ディスエーブル状態に設定され、第1、第2の出力信号が出力されていない場合に、プリバッファーが動作ディスエーブル状態に設定され、無駄な電力の消費を抑制できるようになる。

【0024】

また本発明の一態様では、前記バッファー回路は、前記プリバッファーからの信号が入力され、第3の出力信号を出力する第3の出力バッファーを含み、前記第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファー及び前記第3の出力バッファーが動作ディスエーブル状態に設定され、前記第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、前記第3の出力バッファーが動作ディスエーブル状態に設定され、第3のモードでは、前記第1の出力バッファー、前記第2の出力バッファー及び前記第3の出力バッファーが動作イネーブル状態に設定され、前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定され、前記第2のモードでは、前記プリバッファーの駆動能力が、前記第3のモードに比べて低い駆動能力に設定されてもよい。

【0025】

このようにすれば、第3のモードでは、第1、第2、第3の出力バッファーが共に動作イネーブル状態に設定される。一方、第2のモードでは、第1、第2の出力バッファーが動作イネーブル状態に設定され、第3の出力バッファーが動作ディスエーブル状態に設定されると共に、プリバッファーの駆動能力が第3のモードに比べて低い駆動能力に設定される。従って、プリバッファーの駆動能力を、出力バッファーの負荷容量に応じた適切な駆動能力に設定でき、無駄な電力の消費やノイズによる悪影響等を抑制できるようになる。

【0026】

また本発明の一態様では、回路装置の対向する第1の辺及び第2の辺の間の境界線により区分される一方の領域を第1の領域とし、他方の領域を第2の領域とした場合に、前記振動子を接続するための第1の振動子用端子及び第2の振動子用端子が、前記第1の領域に配置され、前記第1の出力バッファーからの前記第1の出力信号が出力される第1の出力端子と、前記第2の出力バッファーからの前記第2の出力信号が出力される第2の出力端子が、前記第2の領域に配置され、前記発振回路及び前記バッファー回路が、前記第1の領域に配置されてもよい。

【0027】

このようなレイアウト配置によれば、第1、第2の出力端子と発振回路等の間の距離を離すことが可能になる。従って、第1、第2の出力端子の信号ノイズ等が、発振回路等の動作に悪影響を与える事態を抑制することが可能になる。

【0028】

また本発明の一態様では、回路装置の前記第1の辺及び前記第2の辺に交差する辺を第3の辺及び第4の辺とした場合に、前記第1の振動子用端子は、前記第3の辺に沿った第1の端子配置領域に配置され、前記第2の振動子用端子は、前記第4の辺に沿った第2の端子配置領域に配置され、前記第1の出力端子は、前記第3の辺に沿った前記第1の端子配置領域に配置され、前記第2の出力端子は、前記第4の辺に沿った前記第2の端子配置領域に配置されてもよい。

【0029】

このようにすれば、第1の端子配置領域に配置される第1の振動子用端子と第1の出力端子との間の距離や、第2の端子配置領域に配置される第2の振動子用端子と第2の出力端子との間の距離を離すことが可能になる。従って、第1、第2の出力端子の信号ノイズ等が、第1、第2の振動子用端子の発振信号に対して悪影響を及ぼす事態等を抑制できるようになる。

【0030】

また本発明の一態様では、前記第1の端子配置領域では、前記第1の振動子用端子と前記第1の出力端子の間に、高電位側電源及び低電位側電源の一方の電源用の第1の電源端子が配置され、前記第2の端子配置領域では、前記第2の振動子用端子と前記第2の出力端子の間に、前記一方とは異なる他方の電源用の第2の電源端子が配置されてもよい。

【0031】

このようにすれば、第1の振動子用端子と第1の出力端子の間に第1の電源端子が配置され、第2の振動子用端子と第2の出力端の間に第2の電源端子が配置されるようになる。従って、第1の振動子用端子と第1の出力端子の間の距離や、第2の振動子用端子と第2の出力端子の間の距離を離して信号ノイズの悪影響等を低減できるようになる。

【0032】

また本発明の他の態様は、上記のいずれかに記載の回路装置を含む電子機器に関係する。

【図面の簡単な説明】

【0033】

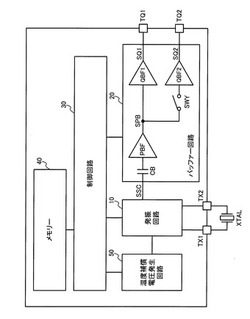

【図1】本実施形態の回路装置の第1の構成例。

【図2】本実施形態の回路装置の第2の構成例。

【図3】各モードでのプリバッファーや出力バッファーの制御手法の説明図。

【図4】図4(A)〜図4(C)は出力バッファーの出力信号の種々の態様の説明図。

【図5】図5(A)、図5(B)は出力信号の高調波特性例。

【図6】クリップドサイン波出力回路により構成される出力バッファーの詳細な構成例。

【図7】図7(A)〜図7(D)はクリップドサイン波出力回路により構成される出力バッファーの各ノードの信号波形例。

【図8】図8(A)、図8(B)は、クリップドサイン波出力回路により構成される出力バッファーの更に詳細な構成例及び動作説明図。

【図9】MIM構造のキャパシターを用いる手法の説明図。

【図10】プリバッファーの詳細な構成例。

【図11】矩形波出力回路により構成される出力バッファーの詳細な構成例。

【図12】本実施形態の回路装置の詳細なレイアウト配置例。

【図13】本実施形態の電子機器の構成例。

【発明を実施するための形態】

【0034】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0035】

1.構成

図1に本実施形態の回路装置(IC)の第1の構成例を示す。この回路装置は発振回路10、バッファー回路20を含む。また制御回路30、メモリー40、温度補償電圧発生回路50を含むことができる。なお回路装置の構成は図1の構成には限定されず、その一部の構成要素(例えば温度補償電圧発生回路)を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0036】

発振回路10は、振動子XTAL(圧電振動子、水晶振動子)に接続される。具体的には第1、第2の振動子用端子TX1、TX2(振動子用パッド)を介して振動子XTALに接続される。発振回路10は、電圧を印加することで固有振動を起こす振動子XTALを一定の周波数で発振させるための回路である。この発振回路10は、端子TX1が入力ノードに接続され、端子TX2が出力ノードに接続される増幅回路などにより実現できる。

【0037】

バッファー回路20は、発振回路10からの発振信号SSCをバッファリングする回路である。即ち外部の負荷を十分に駆動できるように信号のバッファリングを行う。バッファー回路20により、バッファリングされた信号は、第1、第2の出力信号SQ1、SQ2として第1、第2の出力端子TQ1、TQ2を介して外部に出力される。

【0038】

制御回路30は、発振回路10、バッファー回路20、メモリー40、温度補償電圧発生回路50の制御を行う。また外部とのインターフェース処理なども行う。この制御回路30は、例えばスタンダードセルやゲートアレイ等のロジック回路により実現される。

【0039】

メモリー40は、回路装置の動作に必要な各種の情報を記憶する。例えば温度補償電圧発生回路50が温度補償処理を行うために必要な情報等を記憶する。

【0040】

温度補償電圧発生回路50は、TCXOを実現するための温度補償電圧を発生して、発振回路10に出力する。これにより発振周波数の温度補償が実現される。

【0041】

バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。

【0042】

プリバッファーPBFには、発振回路10からの発振信号SSCが入力される。具体的には、発振回路10からの正弦波の発振信号SSCは、DCカット用のキャパシターCBを介してプリバッファーPBFに入力される。そしてプリバッファーPBFは、バッファリングした信号を第1、第2の出力バッファーQBF1、QBF2に出力する。

【0043】

第1の出力バッファーQBF1は、プリバッファーPBFからの信号SPBが入力され、第1の出力信号SQ1を出力する。具体的には第1の出力信号SQ1を第1の出力端子TQ1を介して外部(回路装置の外部デバイス)に出力する。第2の出力バッファーQBF2は、プリバッファーPBFからの信号SPBが入力され、第2の出力信号SQ2を出力する。具体的には第2の出力バッファーQBF2には、プリバッファーPBFからの信号SPBがスイッチ回路SWYを介して入力され、第2の出力信号SQ2を第2の出力端子TQ2を介して外部に出力する。

【0044】

そして本実施形態では、第1のモード(第1の状態)では、第1の出力バッファーQBF1が動作イネーブル状態(信号出力状態)に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態(信号非出力状態)に設定される。一方、第2のモード(第2の状態)では、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。そして第1のモードでは、プリバッファーPBFの駆動能力(電流駆動能力)が、第2のモードに比べて低い駆動能力に設定される。

【0045】

出力バッファーQBF1、QBF2が動作イネーブル状態に設定されると、QBF1、QBF2が出力信号SQ1、SQ2を出力するようになる。一方、出力バッファーQBF1、QBF2が動作ディスエーブル状態に設定されると、QBF1、QBF2が出力信号SQ1、SQ2を出力しなくなる。この動作イネーブル状態、動作ディスエーブル状態の制御は、制御回路30からの制御信号により実現される。またプリバッファーPBFの駆動能力の制御も、制御回路30からの制御信号により実現される。例えばプリバッファーPBFの駆動能力の制御は、PBFの出力トランジスターの駆動能力(電流駆動能力、W/L)を制御することで実現される。

【0046】

またバッファー回路20はスイッチ回路SWYを含む。このスイッチ回路SWYは、プリバッファーPBFの出力ノードと第2の出力バッファーQBF2の入力ノードとの間に設けられる。そしてスイッチ回路SWYは、第1のモードではオフ状態に設定され、第2のモードではオン状態に設定される。即ち、第1のモードでは、出力バッファーQBF2が動作ディスエーブル状態に設定されると共に、スイッチ回路SWYがオフ状態になる。これにより、プリバッファーPBFの出力ノードから出力バッファーQBF2が切り離される。この時、プリバッファーPBFの駆動能力は低い駆動能力に設定される。一方、第2のモードでは、出力バッファーQBF2が動作イネーブル状態に設定されると共に、スイッチ回路SWYがオン状態になる。これにより、プリバッファーPBFの出力ノードに出力バッファーQBF2が接続されるようになる。

【0047】

なお、プリバッファーPBFの出力ノードと出力バッファーQBF1の間にスイッチ回路を設けてもよい。

【0048】

また図1において、出力バッファーQBF1、QBF2が共に動作ディスエーブル状態に設定された場合には、プリバッファーPBFも動作ディスエーブル状態に設定されることが望ましい。このようにプリバッファーPBFを動作ディスエーブル状態に設定すれば、動作ディスエーブル状態に設定された出力バッファーQBF1、QBF2のみならず、プリバッファーPBFにおいても、無駄に電力が消費されたり、EMIノイズ等を発生してしまう事態を抑制できる。即ち、出力バッファーQBF1、QBF2が共に動作ディスエーブル状態に設定された場合には、出力信号SQ1、SQ2を外部に出力する必要がない。このため、出力バッファーQBF1、QBF2に信号SPBを供給するプリバッファーPBFについても動作ディスエーブル状態に設定することで、無駄な電力消費を抑制する。

【0049】

図2に本実施形態の回路装置の第2の構成例を示す。図1の第1の構成例との相違点は、図2ではバッファー回路20に更に第3の出力バッファーQBF3が設けられている点である。

【0050】

第3の出力バッファーQBF3は、プリバッファーPBFからの信号SPBが入力され、第3の出力信号SQ3を出力する。具体的には第3の出力バッファーQBF3は、プリバッファーPBFからの信号SPBがスイッチ回路SWZを介して入力され、第3の出力信号SQ3を第3の出力端子TQ3を介して外部に出力する。

【0051】

図3は、図2の第2の構成例の動作を説明する図である。図3に示すように、第1のモードM1では、出力バッファーQBF1が動作イネーブル状態に設定され、出力バッファーQBF2及びQBF3が動作ディスエーブル状態に設定される。一方、第2のモードM2では、出力バッファーQBF1及びQBF2が動作イネーブル状態に設定され、出力バッファーQBF3が動作ディスエーブル状態に設定される。また、第3のモードM3では、出力バッファーQBF1、QBF2及びQBF3が動作イネーブル状態に設定される。

【0052】

なお、第1、第2、第3のモードの選択は、不図示の設定用外部端子で設定してもよいし、メモリーブロック内の不揮発領域の記憶した値で設定してもよい。

【0053】

そして第1のモードM1では、プリバッファーPBFの駆動能力が、第2のモードM2に比べて低い駆動能力に設定される。また、第2のモードM2では、プリバッファーPBFの駆動能力が、第3のモードM3に比べて低い駆動能力に設定される。

【0054】

即ち、全ての出力バッファーQBF1、QBF2、QBF3が動作イネーブル状態に設定される第3のモードM3では、プリバッファーPBFの駆動能力が最も大きくなる。一方、出力バッファーQBF1のみが動作イネーブル状態に設定される第1のモードM1では、プリバッファーPBFの駆動能力が最も小さくなる。そして出力バッファーQBF1、QBF2が動作イネーブル状態に設定され、出力バッファーQBF3が動作ディスエーブル状態に設定される第2のモードM2では、プリバッファーPBFの駆動能力は、第1のモードM1と第3のモードM3の駆動能力の中間の駆動能力になる。

【0055】

なおバッファー回路20が含むスイッチ回路SWZは、プリバッファーPBFの出力ノードと出力バッファーQBF3の入力ノードとの間に設けられる。そしてスイッチ回路SWZは、第1、第2のモードM1、M2ではオフ状態に設定され、第3のモードM3ではオン状態に設定される。即ち、第1、第2のモードM1、M2では、出力バッファーQBF3が動作ディスエーブル状態に設定されると共に、スイッチ回路SWZがオフ状態になることで、プリバッファーPBFの出力ノードから出力バッファーQBF3が切り離される。一方、第3のモードM3では、出力バッファーQBF3が動作イネーブル状態に設定されると共に、スイッチ回路SWZがオン状態になることで、プリバッファーPBFの出力ノードに出力バッファーQBF3が接続されるようになる。

【0056】

また図2において、出力バッファーQBF1、QBF2、QBF3が共に動作ディスエーブル状態に設定された場合には、プリバッファーPBFも動作ディスエーブル状態に設定されることが望ましい。こうすることで、動作ディスエーブル状態に設定された出力バッファーQBF1、QBF2、QBF3のみならず、プリバッファーPBFにおいても、無駄に電力が消費されたり、EMIノイズ等が発生してしまう事態を抑制できる。

【0057】

図4(A)〜図4(C)に出力バッファーの出力信号の信号波形例を示す。図4(A)では、出力バッファーQBF1は、クリップドサイン波出力回路により構成され、クリップドサイン波の出力信号SQ1を出力している。同様に出力バッファーQBF2もクリップドサイン波出力回路により構成され、クリップドサイン波の出力信号SQ2を出力している。ここでクリップドサイン波は、正弦波の高電位側(上端)と低電位側(下端)を電圧クリップさせた波形(振幅制限波形)である。このクリップドサイン波を用いれば、上下に電圧クリップされた電圧部分が余裕となって、外部デバイス側の負荷が変動しても、出力信号の電圧振幅の変動を最小限に抑えることができるというメリットがある。

【0058】

一方、図4(B)では、出力バッファーQBF1は、クリップドサイン波出力回路により構成され、クリップドサイン波の出力信号SQ1を出力しているのに対して、出力バッファーQBF2は、矩形波出力回路により構成され、矩形波(方形波)の信号SQ2を出力している。例えばクリップドサイン波は矩形波に比べると高調波成分が少ない。従って、回路装置が実装される回路基板等において、クリップドサイン波の信号線を引き回しても、矩形波の信号線を引き回す場合に比べて、EMIノイズ等の発生を抑えることを期待できる。しかしながら、EMIノイズの発生等がそれほど問題にならない信号経路では、クリップドサイン波ではなく矩形波の信号の出力を、ユーザーが望む場合もある。従って、図4(B)のように、クリップドサイン波の出力信号SQ1と矩形波の出力信号SQ2の両方を出力可能にすることで、このようなユーザーの要望に応えることができる。

【0059】

また図4(C)では、出力バッファーQBF1、QBF2はクリップドサイン波の出力信号SQ1を出力し、出力バッファーQBF3は矩形波の信号SQ3を出力している。こうすることで、2本のクリップドサイン波の信号出力と1本の矩形波の信号出力を必要とするユーザーの要望に応えることができる。なお図4(C)において、出力バッファーQBF3もクリップドサイン波の信号SQ3を出力するようにしてもよい。

【0060】

以上の本実施形態の回路装置によれば以下のような効果が得られる。前述のようにTCXOなどの発振器では、多出力機能への要望が高まっている。このような発振器の多出力機能を実現する比較例の手法として、プリバッファーPBFに複数の出力バッファーQBF1〜QBF3を接続する一方で、スイッチ回路SWY、SWZを設けずに、プリバッファーPBFの駆動能力についても変更しない手法が考えられる。

【0061】

しかしながら、この比較例の手法では、図3に示すようにモードM1〜M3が切り替わった場合にも、プリバッファーPBFに対して全ての出力バッファーQBF1〜QBF3が常時接続され、ユーザーの使用条件に関わらずに、出力バッファーQBF1〜QBF3から信号SQ1〜SQ3が出力されることになる。

【0062】

この場合に、比較例の手法では、例えば出力バッファーQBF1〜QBF3に動作イネーブル/動作ディスエーブルの機能を設けたとしても、プリバッファーPBFの駆動能力は、全ての出力バッファーQBF1〜QBF3を駆動できる能力に設定される。このようなプリバッファーPBFの大きな駆動能力は、図3のモードM3のように全ての出力バッファーQBF1〜QBF3が動作イネーブル状態に設定されている場合には、ユーザーの仕様に適合した信号SQ1〜SQ3を出力するために必要となる。即ち、全ての出力バッファーQBF1〜QBF3から信号SQ1〜SQ3が出力される場合に、プリバッファーPBFの駆動能力が低いと、プリバッファーPBFが、出力バッファーQBF1〜QBF3の入力負荷を十分に駆動できなくなり、信号SQ1〜SQ3に対して要求される仕様を満たすことができないおそれがあるからである。

【0063】

しかしながら、モードM1、M2のように、出力バッファーQBF2やQBF3が動作ディスエーブル状態に設定され、信号SQ2、SQ3が出力されていない状況で、プリバッファーPBFの駆動能力が高すぎると、無駄な電力が消費されてしまう。即ち、出力バッファーQBF2やQBF3が動作ディスエーブル状態に設定されていても、プリバッファーPBFから見た負荷は変わらず、プリバッファーPBFは、全出力バッファーを駆動できる能力で出力バッファーの入力負荷を駆動することになり、不要な電力消費を招く。

【0064】

この点、本実施形態によれば、図3のモードM1、M2のように出力バッファーQBF2やQBF3が動作ディスエーブル状態の場合には、プリバッファーPBFの駆動能力が低く設定される。従って、プリバッファーPBFは、モードM1、M2では、モードM3のような最大の駆動能力で駆動しなくても済むようになり、無駄な電力の消費を抑えることができる。

【0065】

また、モードM1、M2では、アナログのスイッチ回路SWYやSWZがオフ状態になるため、プリバッファーPBFの出力から出力バッファーQBF2やQBF3の入力ラインが切り離される。このように入力ラインが切り離されることで、プリバッファーPBFから見た負荷が軽くなるため、図3のようにプリバッファーPBFの駆動能力を低くしても、駆動能力が不十分になってしまう問題は生じなくなる。即ちアナログのスイッチ回路SWYやSWZのオン・オフに連動してプリバッファーPBFの駆動能力を調整することで、最適な負荷及び駆動能力でのプリバッファーPBFの駆動が可能になる。

【0066】

またプリバッファーPBFの駆動能力と、出力バッファーQBF1〜QBF3の負荷容量とが整合していないと、出力信号に高調波が発生する問題が生じる。これは、特に図4(A)〜図4(C)で説明したようなクリップドサイン波の出力信号の場合に深刻な問題になる。

【0067】

例えば図5(A)は、モードM1〜M3の切換に応じてプリバッファーPBFの駆動能力を変化させなかった場合の出力信号の高調波特性である。図5(A)のようにプリバッファーPBFの駆動能力を変化させなかった場合には、偶数次の高調波が大きくなってしまう。

【0068】

これに対して、図5(B)は、モードM1〜M3の切換に応じて図3に示すようにプリバッファーPBFの駆動能力を変化させた場合の出力信号の高調波特性である。図5(B)に示すように、プリバッファーPBFの駆動能力を変化させることで、図5(A)の場合に比べて偶数次の高調波を抑制できる。従って、モードM1〜M3に応じてプリバッファーPBFの駆動能力を変化させることで、EMIノイズの低減等を図れるようになる。

【0069】

以上のように本実施形態によれば、複数の出力バッファーを設け、非動作となる出力バッファーについては、その入力側に設けられたアナログのスイッチ回路をオフさせると共に、それに連動してプリバッファーの能力も調整している。これにより、回路動作の無駄をなくして低消費電力化を図ると共に、プリバッファーから出力バッファーへの信号供給も安定して行うことができることから、発振器としての安定した出力を得ることが可能になる。

【0070】

2.具体的回路構成

次に出力バッファーやプリバッファーの具体的な回路構成例について説明する。図6にクリップドサイン波出力回路により構成される出力バッファーQBF1や、プリバッファーPBFの回路構成例を示す。なお出力バッファーQBF2がクリップドサイン波出力回路により構成される場合には、図6のQBF1と同様の構成になる。

【0071】

図6に示すように、出力バッファーQBF1を構成するクリップドサイン波出力回路は、第1、第2のトランジスターTA1、TA2、第1、第2のバイアス電圧設定回路BAS1、BAS2、第1、第2のキャパシターCA1、CA2を含む。

【0072】

トランジスターTA1は、VDDノード(広義には高電位側電源ノード)と出力ノードNAQとの間に設けられる。トランジスターTA2は、出力ノードNAQとVSSノード(広義には低電位側電源ノード)との間に設けられる。例えばトランジスターTA1はN型トランジスター(第1導電型トランジスター)であり、トランジスターTA2はP型トランジスターである。なおVDDノードとトランジスターTA1の間に電圧調整回路等を設けてもよい。

【0073】

バイアス電圧設定回路BAS1は、トランジスターTA1のゲートノードである第1のゲートノードNG1に対してバイアス電圧を設定する回路である。このバイアス電圧設定回路BAS1は、例えばVDDノードとVSSノードの間に直列に設けられる第1、第2の抵抗素子RA1、RA2を含む。これによりVDD−VSS間を抵抗素子RA1、RA2で抵抗分割した電圧が、バイアス電圧としてゲートノードNG1に印加されるようになる。

【0074】

バイアス電圧設定回路BAS2は、トランジスターTA2のゲートノードである第2のゲートノードNG2に対してバイアス電圧を設定する回路である。このバイアス電圧設定回路BAS2は、例えばゲートノードNG2とVSSノードの間に設けられる第4の抵抗素子RA4を含む。

【0075】

キャパシターCA1は、プリバッファーPBFからの信号が入力される入力ノードNAIとゲートノードNG1との間に設けられる。キャパシターCA2は、入力ノードNAIとゲートノードNG2との間に設けられる。これらのキャパシターCA1、CA2はDCカット用(ACカップリング用)のキャパシターである。

【0076】

スイッチ回路SWXは、プリバッファーPBFの出力ノードNBQと出力バッファーQBF1の入力ノードNAIの間に設けられる。スイッチ回路SWXはトランスファーゲートにより構成され、トランスファーゲートのN型トランジスターのゲートにはスイッチ制御信号SXが入力され、P型トランジスターのゲートにはスイッチ制御信号XSXが入力される。なお信号XSXの先頭の「X」は負論理の信号であることを意味する。

【0077】

スイッチ回路SWYは、プリバッファーPBFの出力ノードNBQと出力バッファーQBF2の入力ノードの間に設けられる。スイッチ回路SWYはトランスファーゲートにより構成され、トランスファーゲートのN型トランジスターのゲートにはスイッチ制御信号SYが入力され、P型トランジスターのゲートには負論理のスイッチ制御信号XSYが入力される。

【0078】

プリバッファーPBFは、インバーター回路IVB1とIVB2を含む。インバーター回路IVB1の出力は抵抗素子RBを介してIVB1の入力に帰還される。これにより、発振回路10からキャパシターCBを介して入力されるACの信号の増幅処理が行われるようになる。

【0079】

なお出力端子TQ1と外部ノードNCの間にはキャパシターCC1(例えば0.01μF)が設けられる。ノードNCに接続される抵抗素子RC(例えば10kΩ)、キャパシターCC2(例えば10pF)は外部負荷を表すものである。また出力バッファーQBF2がクリップドサイン波を出力する場合には、QBF2もQBF1と同様の構成のクリップドサイン波出力回路により構成されることになる。

【0080】

図7(A)〜図7(D)は、図6の回路の動作を説明するための信号波形例である。図7(A)、図7(B)、図7(C)、図7(D)には、各々、図6のノードNAI、NG1、NG2、NAQの信号波形(電圧波形)が示されている。

【0081】

例えばノードNA1の電圧が図7(A)のように変化すると、ノードNG1の電圧は、バイアス電圧設定回路BAS1によるバイアス電圧を基準として図7(B)のように変化する。またノードNG1の電圧は、バイアス電圧設定回路BAS2によるバイアス電圧を基準として図7(C)のように変化する。これにより出力ノードNAQには、図7(D)に示すようなクリップドサイン波の信号が出力されるようになる。

【0082】

図8(A)は、出力バッファーQBF1等を構成するクリップドサイン波出力回路の更に具体的な回路構成例である。

【0083】

図8(A)に示すように、バイアス電圧設定回路BAS1は、VDDノード(高電位側電源ノード)とゲートノードNG1との間に直列に設けれる第1の抵抗素子RA1及び第1のスイッチ素子SWA1を含む。またゲートノードNG1とVSSノード(低電位側電源ノード)との間に設けられる第2の抵抗素子RA2を含む。なお図8(A)ではゲートノードNG1側にスイッチ素子SWA1が設けられているが、VDDノード側にSWA1を設けてもよい。

【0084】

バイアス電圧設定回路BAS2は、VDDノードとゲートノードNG2との間に直列に設けれる第3の抵抗素子RA3及び第2のスイッチ素子SWA2を含む。またゲートノードNG2とVSSノードとの間に設けられる第4の抵抗素子RA4及び第3のスイッチ素子SWA3を含む。なお図8(A)ではVDDノード側にスイッチ素子SWA2が設けられ、ゲートノードNG2側にスイッチ素子SWA3が設けられているが、ゲートノードNG2側にSWA2を設け、VSSノード側にSWA3を設けてもよい。

【0085】

そして図8(A)に示すように、クリップドサイン波出力回路の動作イネーブル状態(通常動作状態)では、スイッチ素子SWA1及びSWA3がオン状態に設定され、スイッチ素子SWA2がオフ状態に設定される。これにより、VDDとVSSを抵抗素子RA1、RA2で抵抗分割した電圧が、バイアス電圧としてゲートノードNG1に設定される。またVSS(GND)の電圧が、バイアス電圧としてゲートノードNG2に設定される。

【0086】

一方、動作ディスエーブル状態では、図8(B)に示すように、スイッチ素子SWA1及びSWA3がオフ状態に設定され、スイッチ素子SWA2がオン状態に設定される。スイッチ素子SWA1がオフ状態になることで、ノードNG1から抵抗素子RA1が切り離され、ノードNG1がVSSの電圧(GND電圧=0V)に設定(プルダウン)される。これにより、N型のトランジスターTA1がオフ状態に設定される。

【0087】

またスイッチ素子SWA3がオフ状態になることで、ゲートノードNG2から抵抗素子RA4が切り離される。そしてスイッチ素子SWA2がオン状態になることで、ゲートノードNG2がVDDの電圧に設定(プルアップ)される。これにより、P型のトランジスターTA2がオフ状態に設定される。

【0088】

以上のように、クリップドサイン波出力回路の動作イネーブル状態では、バイアス電圧設定回路BAS1、BAS2により、トランジスターTA1、TA2のゲートノードNG1、NG2に適切なバイアス電圧が設定され、これにより図4(A)等に示すように、出力ノードNAQからクリップドサイン波の信号が出力されるようになる。一方、動作ディスエーブル状態では、トランジスターTA1、TA2のゲートノードNG1、NG2が、各々、VDD、VSSの電圧が設定され、TA1、TA2がオフになる。従って、出力ノードNAQからはクリップドサイン波の信号が出力されないようになり、クリップドサイン波出力回路の動作ディスエーブルを実現できるようになる。

【0089】

図9は、図6、図8(A)、図8(B)のCA1、CA2のキャパシター構造例を示す図である。図9に示すように、キャパシターCA1、CA2は、MIM(Metal-Insulator-Metal)構造のキャパシターにより構成される。具体的には、メタル層META、METBと、META、METBの間に設けられる絶縁層によりなるMIM構造のキャパシターにより、CA1、CA2が構成される。

【0090】

そしてMIM構造のキャパシターCA1の上部電極ELT(METB)が図6、図8(A)、図8(B)の出力バッファーの入力ノードNAIに接続される。一方、下部電極ELB(META)がゲートノードNG1に接続される。同様に、MIM構造のキャパシターCA2の上部電極ELTが入力ノードNAIに接続され、下部電極ELBがゲートノードNG2に接続される。このようにすることで、出力バッファーの入力ノードNAIの負荷容量を減少させることができ、プリバッファーPBFの充放電電力を減らすことができるため、無駄な電力の消費を抑制できる。

【0091】

即ち、下部電極ELBには、基板等の間の寄生容量CSが大きい。従って、下部電極ELBが出力バッファーの入力ノードNAIに接続されると、この寄生容量CSの容量値の分だけ、出力バッファーの負荷容量が増えてしまう。

【0092】

この点、本実施形態では図9に示すように、出力バッファーの入力ノードNAIは、下部電極ELBではなく上部電極ELTに接続される。従って、入力ノードNAIに、基板との寄生容量CSが寄生する事態を抑制でき、プリバッファーPBFの無駄な電力消費を抑制できるようになる。

【0093】

図10にプリバッファーPBFの構成例を示す。なおプリバッファーPBFは図10の構成には限定されず、その一部の構成要素を省略したり、他の構成要素を通過するなどの種々の変形実施が可能である。

【0094】

図10に示すようにプリバッファーPBFは、インバーター回路IVB1と、IVB1の出力ノードに入力ノードが接続されるインバーター回路IVB2を含む。

【0095】

インバーター回路IVB1は、VDDノードとVSSノードの間に直列に設けられたP型トランジスターTB1、N型トランジスターTB2を含む。そしてインバーター回路IVB1の出力は抵抗素子RBを介してIVB1の入力に帰還される。

【0096】

駆動能力調整用のインバーター回路IVB2は、VDDノードとVSSノードの間に直列に設けられたP型トランジスターTB3、N型トランジスターTB4を含む。またVDDノードと出力ノードNBQの間に直列に設けられた駆動能力調整用のP型トランジスターTB5及びスイッチ素子SWB1と、P型トランジスターTB7及びスイッチ素子SWB3を含む。また出力ノードNBQとVSSノードとの間に直列に設けられた駆動能力調整用のスイッチ素子SWB2及びN型トランジスターTB6と、スイッチ素子SWB4及びN型トランジスターTB8を含む。なおP型トランジスターTB3、TB5、TB7は例えば同じ電流供給能力(W/L)を有し、N型トランジスターTB4、TB6、TB8は例えば同じ電流供給能力(W/L)を有する。但しトランジスターTB3、TB4の電流供給能力を他のトランジスターよりも大きくしてもよい。

【0097】

プリバッファーPBFの駆動能力の制御は、制御回路30がスイッチ素子SWB1〜SWB4のスイッチ制御を行うことで実現される。

【0098】

例えば図3のモードM3では、制御回路30は、スイッチ素子SWB1、SWB2、SWB3、SWB4をオン状態に設定する。これにより、駆動能力調整用のトランジスターTB5、TB6、TB7、TB8のドレインが出力ノードNBQに接続され、プリバッファーPBFの駆動能力は、トランジスターTB3、TB4、TB5、TB6、TB7、TB8を並列接続した駆動能力になる。この結果、モードM3でのプリバッファーPBFの駆動能力は、他のモードM1、M2に比べて高い駆動能力に設定される。

【0099】

またモードM2では、制御回路30は、例えばスイッチ素子SWB1、SWB2をオン状態に設定し、SWB3、SWB4をオフ状態に設定する。これにより、駆動能力調整用のトランジスターTB7、TB8のドレインが出力ノードNBQから切り離され、プリバッファーPBFの駆動能力は、トランジスターTB3、TB4、TB5、TB6を並列接続した駆動能力になる。この結果、モードM2でのプリバッファーPBFの駆動能力は、モードM3に比べて低い駆動能力に設定される。

【0100】

またモードM3では、制御回路30は、例えばスイッチ素子SWB1、SWB2、SWB3、SWB4をオフ状態に設定する。これにより、駆動能力調整用のトランジスターTB5、TB6、TB7、TB8のドレインが出力ノードNBQから切り離され、プリバッファーPBFの駆動能力はトランジスターTB3、TB4の駆動能力になる。この結果、モードM1でのプリバッファーPBFの駆動能力は、モードM2に比べて低い駆動能力に設定される。

【0101】

以上のようにすれば、モードM1、M2、M3において出力バッファーQBF1〜QBF3の動作イネーブル/動作ディスエーブルが設定された場合に、その設定状態に応じた駆動能力に、プリバッファーPBFの駆動能力も設定されるようになる。従って、プリバッファーPBFで無駄に電力が消費されたり、図5(A)のように高調波が増加することによりEMIノイズが生じるなどの事態の発生を抑制できるようになる。

【0102】

なお、プリバッファーPBFの構成は図10の構成に限定されず、種々の変形実施が可能である。例えば図10では、駆動能力調整用のトランジスター及びスイッチ素子のペアーを2組設けているが、駆動能力調整用のトランジスター及びスイッチ素子のペアーを1組にしたり、3組以上にしてもよい。

【0103】

図11に、図4(B)、図4(C)のように出力バッファーを矩形波出力回路で実現した場合の回路構成例を示す。図11の構成は、図10のプリバッファーPBFの駆動能力調整用のインバーター回路IVB2と同様の構成である。図11では、出力端子TQ2に接続される外部負荷の大きさに応じて、スイッチ素子SWD1〜SWD4のオン・オフ制御が行われ、外部負荷の大きさに応じた出力バッファーの最適な駆動能力の設定が可能になる。

【0104】

また図11では、入力ノードNDIとVSSノードの間にスイッチ素子SWD5及び抵抗素子RDが直列に設けられている。そして出力バッファーを動作イネーブル状態に設定する場合には、スイッチ素子SWD5をオフ状態に設定する。これにより出力端子TQ2から矩形波の信号が出力されるようになる。一方、出力バッファーを動作ディスエーブル状態に設定する場合には、スイッチ素子SWD5をオン状態に設定にして、入力ノードNDIをプルダウンする。これにより、出力端子TQ2の電圧がローレベルに固定され、TQ2を信号非出力状態に設定できるようになる。

【0105】

3.レイアウト配置

図12に本実施形態の回路装置のレイアウト配置例を示す。図12は、回路装置のチップを平面視で見た図である。なお本実施形態の回路装置のレイアウト配置は図12の配置例に限定されず、種々の変形実施が可能である。

【0106】

図12において、回路装置の対向する辺を第1の辺SD1、第2の辺SD2とする。また回路装置の辺SD1、SD2に交差(例えば直交)する辺を第3の辺SD3、第4の辺SD4とする。図12では辺SD1、SD2が短辺となり、辺SD3、SD4が長辺となっている。

【0107】

また図12において、回路装置の対向する辺SD1、SD2の間の境界線BDLにより区分される一方の領域を第1の領域AR1とし、他方の領域を第2の領域AR2とする。例えば境界線BDLは、辺SD1、SD2に平行な線であり、辺SD1、SD2の中線に沿った線になる。そして領域AR1は、境界線BDLを基準として辺SD1側の領域であり、領域AR2は、境界線BDLを基準として辺SD2側の領域である。

【0108】

この場合に図12では、振動子XTALを接続するための第1の振動子用端子TX1及び第2の振動子用端子TX2が、第1の領域AR1に配置される。即ち、振動子用端子TX1、TX2は、辺SD1と境界BDLの間の領域AR1に配置されており、辺SD1側に配置されている。

【0109】

一方、出力バッファーQB1からの出力信号SQ1が出力される出力端子TQ1と、出力バッファーかQB2からの出力信号SQ2が出力される出力端子TQ2は、第2の領域AR2に配置される。即ち、出力端子TQ1、TQ2は、辺SD2と境界BDLの間の領域AR2に配置されており、辺SD2側に配置されている。また出力バッファーQB3からの出力信号SQ3が出力される出力端子TQ3も領域AR2に配置される。具体的には出力端子TQ3は出力端子TQ1(又はTQ2)と辺SD2の間に配置される。

【0110】

そして本実施形態では、発振回路10及びバッファー回路20が、領域AR1に配置される。即ち、発振回路10及びバッファー回路20が、辺SD2側の領域AR2ではなく、辺SD1側の領域AR1に配置される。例えば発振回路10及びバッファー回路20が、制御回路30と辺SD1の間に配置される。

【0111】

このようにすれば、出力端子TQ1、TQ2、TQ3の出力信号SQ1、SQ2、SQ3からのノイズが、発振回路10等の動作に悪影響を与える事態を抑制できる。即ち図5(A)、図5(B)のような高調波が発振回路10の動作に悪影響を与えて、発振回路10の動作が不安定になったり、発振周波数が変動等してしまう事態を抑制できるようになる。特に、出力端子TQ3から矩形波の出力信号が出力される場合に、この出力端子TQ3を発振回路10から最も遠い位置に配置することで、矩形波の信号の高調波等が発振回路10の動作等に悪影響を与える事態を抑制できる。

【0112】

そして、このようなレイアウト配置では、バッファー回路20と出力端子TQ1〜TQ3の距離が離れてしまうという問題もある。しかしながら、バッファー回路20は、外部の大きな負荷を駆動できる十分な駆動能力を有しているため、このように距離が離れてもそれほど問題は生じないことになる。例えば、出力バッファーに比べて駆動能力が小さなプリバッファーの出力信号線を、長い距離に亘って配線すると、プリバッファーの信号にノイズ等が重畳されて、出力端子TQ1〜TQ3からの信号にもノイズ等が重畳される事態が生じるおそれがある。この点、図12では、プリバッファーではなく、出力バッファーの出力信号線が、バッファー回路20から出力端子TQ1〜TQ3に配線されるため、上記のような事態の発生を抑止できる。

【0113】

また図12では、振動子用端子TX1は、辺SD3に沿った第1の端子配置領域IO1に配置され、振動子用端子TX2は、辺SD4に沿った第2の端子配置領域IO2に配置される。また出力端子TQ1は、辺SD3に沿った端子配置領域IO1に配置され、出力端子TQ2は、辺SD4に沿った端子配置領域IO2に配置される。また出力端子TQ3は端子配置領域IO1(或いはIO2)に配置される。

【0114】

ここで端子配置領域IO1、IO2は、外部デバイスを接続するための端子(パッド)が配置される領域である。例えば端子配置領域IO1は、発振回路10、制御回路30等の内部回路と辺SD3との間に設けられ、所定幅を有するI/O領域である。端子配置領域IO2は、内部回路と辺SD4との間に設けられ、所定幅を有するI/O領域である。

【0115】

このようにすれば、振動子用端子TX1、TX2は、回路装置の端子配置領域IO1又はIO2の辺SD1側(AR1側)に配置されるようになる。また、出力端子TQ1、TQ2、TQ3は、端子配置領域IO1又はIO2の辺SD2側(AR2側)に配置されるようになる。従って、振動子用端子TX1、TX2と出力端子TQ1、TQ2、TQ3の間の距離を離すことが可能になり、出力端子TQ1、TQ2、TQ3の信号ノイズ等が、振動子用端子TX1、TX2の発振信号に対して悪影響を及ぼす事態を抑制できるようになる。また、回路装置のICを回路基板等に実装した場合に、振動子XTALの実装や、出力端子TQ1〜TQ3からの信号線の回路基板上での配線を、簡素化することなどが可能になる。

【0116】

また端子配置領域IO1では、振動子用端子TX1と出力端子TQ1の間に、電源VDD用(広義には高電位側電源及び低電位側電源の一方の電源用)の電源端子TVDDが配置される。また端子配置領域IO1では、振動子用端子TX1と出力端子TQ1の間に、回路装置の制御用端子TCT1も配置される。

【0117】

一方、端子配置領域IO2では、振動子用端子TX2と出力端子TQ2の間に、電源VSS用(広義には一方とは異なる他方の電源用)の電源端子TVSSが配置される。また端子配置領域IO2では、振動子用端子TX2と出力端子TQ2の間に、回路装置の制御用端子TCT2も配置される。なお制御用端子TCT1、TCT2は、発振周波数を可変設定するための端子や、図3に示すモードM1〜M3を切り替えるための端子である。

【0118】

このような端子配置にすれば、振動子用端子TX1と出力端子TQ1、TQ3の間に、電源端子TVDDや制御用端子TCT1が配置されるようになる。従って、振動子用端子TX1と出力端子TQ1、TQ3の間の距離を離して信号ノイズの悪影響を低減できると共に、端子配置領域IO1の領域を有効活用した効率的な端子配置を実現できるようになる。また、このような端子配置にすれば、振動子用端子TX2と出力端子TQ2の間に、電源端子TVSSや制御用端子TCT2が配置されるようになる。従って、振動子用端子TX2と出力端子TQ2の間の距離を離して信号ノイズの悪影響を低減できると共に、端子配置領域IO2の領域を有効活用した効率的な端子配置を実現できるようになる。

【0119】

以上のように図12のレイアウト配置によれば、信号ノイズが発振信号に重畳されるのを抑制しながら効率的なレイアウト配置を実現できる。

【0120】

4.電子機器

図13に本実施形態の回路装置を含む電子機器の構成例を示す。この電子機器は、本実施形態の回路装置500、水晶振動子等の振動子XTAL、アンテナATN、通信部510、処理部520を含む。また操作部530、表示部540、記憶部550を含むことができる。なおこれらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0121】

図13の電子機器としては、例えば携帯型情報端末(携帯電話、スマートフォーン)、生体計測機器(脈拍計、歩数計等)、映像機器(デジタルカメラ、ビデオカメラ)などの種々の機器を想定できる。

【0122】

通信部510(無線回路)は、アンテナANTを介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部520は、電子機器の制御処理や、通信部510を介して送受信されるデータの種々のデジタル処理などを行う。この処理部520の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現される。

【0123】

操作部530は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部540は、各種の情報を表示するものであり、液晶や有機ELなどのディスプレイにより実現できる。なお操作部530としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが表示部540の機能を兼ねることになる。記憶部550は、データを記憶するものであり、その機能はRAMやROMなどの半導体メモリーやHDD(ハードディスクドライブ)などにより実現できる。

【0124】

図13の電子機器によれば、ユーザーの使用条件に応じた適切な出力信号を回路装置500から出力して、電子機器の各部に対して供給できるようになる。そして、この場合に図3に示すように各モードに応じた適切な駆動能力にプリバッファーの駆動能力を設定することで、信号品質の高い出力信号を電子機器の各部に対して供給できるようになる。また回路装置が発生するEMIノイズも低減されるため、電子機器のEMI性能やノイズ耐性を向上できるようになる。

【0125】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また回路装置、電子機器の構成・動作や、プリバッファーの駆動能力の設定手法、動作イネーブル/ディスエーブルの設定手法、信号のバッファリング手法、スイッチの制御手法等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。

【符号の説明】

【0126】

PBF プリバッファー、QBF1、QBF2、QBF3 第1〜第3の出力バッファー、

SWX、SWY、SWZ スイッチ回路、CB キャパシター、XTAL 振動子、

TX1、TX2 第1、第2の振動子用端子、TQ1〜TQ3 第1〜第3の出力端子、

TA1、TA2、TB1〜TB8、TD3〜TD8 トランジスター、

CA1、CA2 第1、第2のキャパシター、RA1〜RA4、RB 抵抗素子、

BAS1、BAS2 第1、第2のバイアス電圧設定回路、

SWA1〜SWA3、SWB1〜SWB4、SWD1〜SWD4 スイッチ素子、

BDL 境界線、AR1、AR2 第1、第2の領域、

SD1〜SD4 第1〜第4の辺、IO1、IO2 第1、第2の端子配置領域、

10 発振回路、20 バッファー回路、30 制御回路、40 メモリー、

50 温度補償電圧発生回路、500 回路装置、510 通信部、520 処理部、

530 操作部、540 表示部、550 記憶部

【技術分野】

【0001】

本発明は、回路装置及び電子機器等に関する。

【背景技術】

【0002】

従来より、TCXO(temperature compensated crystal oscillator)と呼ばれる温度補償型水晶発振器が知られている。このTCXOは、例えば携帯端末などの無線機器のRF回路の基準信号源等として用いられている。TCXOを実現する回路装置の従来技術としては例えば特許文献1に開示される技術がある。

【0003】

さて、TCXO等の発振器では、多出力機能を要求されるケースが増えて来ている。即ち、1つの出力信号だけではなく、2つ以上の出力信号を出力する機能が発振器に要求されている。

【0004】

このように複数の出力信号を出力する多出力発振器の回路装置を実現する場合には、発振回路からの信号をバッファリングするバッファー回路に、プリバッファーと、プリバッファーの出力に接続される複数の出力バッファーを設ける手法が考えられる。

【0005】

しかしながら、この手法を採用した場合に、プリバッファーに対しては、最終段の複数の出力バッファーが常時接続される構成になるため、ユーザーの使用条件に関わらずに、最終段の複数の出力バッファーからは、常に出力信号が出力されるようになってしまう。そして、例えば多出力発振器の複数の出力信号のうちの一部しかユーザーが使用していないのに、全ての出力信号が多出力発振器が出力されてしまうと、無駄に電力が消費されたり、EMI(電磁妨害)の要因等になるおそれがある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−7036号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の幾つかの態様によれば、無駄な電力消費やノイズによる悪影響等を抑制できる回路装置及び電子機器等を提供できる。

【課題を解決するための手段】

【0008】

本発明の一態様は、振動子に接続される発振回路と、前記発振回路からの発振信号をバッファリングするバッファー回路とを含み、前記バッファー回路は、前記発振回路からの前記発振信号が入力されるプリバッファーと、前記プリバッファーからの信号が入力され、第1の出力信号を出力する第1の出力バッファーと、前記プリバッファーからの信号が入力され、第2の出力信号を出力する第2の出力バッファーとを含み、第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファーが動作ディスエーブル状態に設定され、第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定される回路装置に関係する。

【0009】

本発明の一態様によれば、発振回路からの発信信号がプリバッファーによりバッファリングされて、第1、第2の出力バッファーに対して出力される。そして第2のモードでは、第1、第2の出力バッファーが共に動作イネーブル状態に設定される。一方、第1のモードでは、第1の出力バッファーが動作イネーブル状態に設定され、第2の出力バッファーが動作ディスエーブル状態に設定されると共に、プリバッファーの駆動能力が第2のモードに比べて低い駆動能力に設定される。従って、プリバッファーの駆動能力を、出力バッファーの負荷容量に応じた適切な駆動能力に設定できるようになる。これにより、例えばプリバッファー等において無駄な電力が消費されたり、ノイズによる悪影響等を抑制することが可能になる。

【0010】

また本発明の一態様では、前記バッファー回路は、前記プリバッファーの出力ノードと前記第2の出力バッファーの入力ノードとの間に設けられるスイッチ回路を含み、前記スイッチ回路は、前記第1のモードではオフ状態に設定され、前記第2のモードではオン状態に設定されてもよい。

【0011】

このようにすれば、第2の出力バッファーが動作ディスエーブル状態に設定される第1のモードでは、スイッチ回路がオフ状態になることで、プリバッファーの出力ノードから第2の出力バッファーが切り離されるようになる。従って、プリバッファー側から見た負荷容量を減らすことができ、無駄な電力消費等を抑制できるようになる。

【0012】

また本発明の一態様では、前記第1の出力バッファー、或いは前記第1の出力バッファー及び前記第2の出力バッファーが、クリップドサイン波の信号を出力するクリップドサイン波出力回路により構成されてもよい。

【0013】

このようにすれば、第1の出力バッファー又は第1及び第2の出力バッファーがクリップドサイン波を出力する回路である場合に、第1のモードにおいてプリバッファーの駆動能力が低く設定されることで、高調波ノイズの発生等を低減できるようになる。

【0014】

また本発明の一態様では、前記クリップドサイン波出力回路は、高電位側電源ノードと出力ノードとの間に設けられる第1のトランジスターと、前記出力ノードと低電位側電源ノードとの間に設けられる第2のトランジスターと、前記第1のトランジスターのゲートノードである第1のゲートノードに対してバイアス電圧を設定する第1のバイアス電圧設定回路と、前記第2のトランジスターのゲートノードである第2のゲートノードに対してバイアス電圧を設定する第2のバイアス電圧設定回路と、前記プリバッファーからの信号が入力される入力ノードと前記第1のゲートノードとの間に設けられる第1のキャパシターと、前記入力ノードと前記第2のゲートノードとの間に設けられる第2のキャパシターとを含んでもよい。

【0015】

このようにすれば、第1のトランジスターの第1のゲートノードのバイアス電圧、第2のトランジスターの第2のゲートノードのバイアス電圧を、各々、第1、第2のバイアス電圧設定回路により設定することで、適切なクリップドサイン波を出力することが可能になる。

【0016】

また本発明の一態様では、前記第1のバイアス電圧設定回路は、前記高電位側電源ノードと前記第1のゲートノードとの間に直列に設けれる第1の抵抗素子及び第1のスイッチ素子と、前記第1のゲートノードと前記低電位側電源ノードとの間に設けられる第2の抵抗素子を含み、前記第2のバイアス電圧設定回路は、前記高電位側電源ノードと前記第2のゲートノードとの間に直列に設けれる第3の抵抗素子及び第2のスイッチ素子と、前記第2のゲートノードと前記低電位側電源ノードとの間に設けられる第4の抵抗素子及び第3のスイッチ素子を含み、動作イネーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオン状態に設定され、前記第2のスイッチ素子がオフ状態に設定され、動作ディスエーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオフ状態に設定され、前記第2のスイッチ素子がオン状態に設定されてもよい。

【0017】

このようにすれば、例えば第1のモードにおいてクリップドサイン波出力回路が動作ディスエーブル状態に設定されると、第1、第3のスイッチ素子がオフ状態に設定され、第2のスイッチ素子がオン状態に設定される。これにより、第1、第2のトランジスターをオフ状態に設定できるようになり、出力信号を非出力状態に設定することが可能になる。

【0018】

また本発明の一態様では、前記第1のキャパシター及び前記第2のキャパシターは、MIM(Metal-Insulator-Metal)構造のキャパシターにより構成され、MIM構造の前記第1のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第1のゲートノードに接続され、MIM構造の前記第2のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第2のゲートノードに接続されてもよい。

【0019】

このようにすれば、クリップドサイン波出力回路の入力ノードの寄生容量を減少させることができ、プリバッファーの充放電電力を減らすことができるため、無駄な電力の消費を抑えることが可能になる。

【0020】

また本発明の一態様では、前記第1の出力バッファーがクリップドサイン波の信号を出力するクリップドサイン波出力回路により構成され、前記第2の出力バッファーが、矩形波の信号を出力する矩形波出力回路により構成されてもよい。

【0021】

このようにすれば、第1の出力バッファーによりクリップドサイン波の信号を外部に供給すると共に、第2の出力バッファーにより矩形波の信号を外部に供給できるようになり、利便性を向上できる。

【0022】

また本発明の一態様では、前記第1の出力バッファー及び前記第2の出力バッファーが動作ディスエーブル状態に設定された場合に、前記プリバッファーが動作ディスエーブル状態に設定されてもよい。

【0023】

このようにすれば、第1、第2の出力バッファーが動作ディスエーブル状態に設定され、第1、第2の出力信号が出力されていない場合に、プリバッファーが動作ディスエーブル状態に設定され、無駄な電力の消費を抑制できるようになる。

【0024】

また本発明の一態様では、前記バッファー回路は、前記プリバッファーからの信号が入力され、第3の出力信号を出力する第3の出力バッファーを含み、前記第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファー及び前記第3の出力バッファーが動作ディスエーブル状態に設定され、前記第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、前記第3の出力バッファーが動作ディスエーブル状態に設定され、第3のモードでは、前記第1の出力バッファー、前記第2の出力バッファー及び前記第3の出力バッファーが動作イネーブル状態に設定され、前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定され、前記第2のモードでは、前記プリバッファーの駆動能力が、前記第3のモードに比べて低い駆動能力に設定されてもよい。

【0025】

このようにすれば、第3のモードでは、第1、第2、第3の出力バッファーが共に動作イネーブル状態に設定される。一方、第2のモードでは、第1、第2の出力バッファーが動作イネーブル状態に設定され、第3の出力バッファーが動作ディスエーブル状態に設定されると共に、プリバッファーの駆動能力が第3のモードに比べて低い駆動能力に設定される。従って、プリバッファーの駆動能力を、出力バッファーの負荷容量に応じた適切な駆動能力に設定でき、無駄な電力の消費やノイズによる悪影響等を抑制できるようになる。

【0026】

また本発明の一態様では、回路装置の対向する第1の辺及び第2の辺の間の境界線により区分される一方の領域を第1の領域とし、他方の領域を第2の領域とした場合に、前記振動子を接続するための第1の振動子用端子及び第2の振動子用端子が、前記第1の領域に配置され、前記第1の出力バッファーからの前記第1の出力信号が出力される第1の出力端子と、前記第2の出力バッファーからの前記第2の出力信号が出力される第2の出力端子が、前記第2の領域に配置され、前記発振回路及び前記バッファー回路が、前記第1の領域に配置されてもよい。

【0027】

このようなレイアウト配置によれば、第1、第2の出力端子と発振回路等の間の距離を離すことが可能になる。従って、第1、第2の出力端子の信号ノイズ等が、発振回路等の動作に悪影響を与える事態を抑制することが可能になる。

【0028】

また本発明の一態様では、回路装置の前記第1の辺及び前記第2の辺に交差する辺を第3の辺及び第4の辺とした場合に、前記第1の振動子用端子は、前記第3の辺に沿った第1の端子配置領域に配置され、前記第2の振動子用端子は、前記第4の辺に沿った第2の端子配置領域に配置され、前記第1の出力端子は、前記第3の辺に沿った前記第1の端子配置領域に配置され、前記第2の出力端子は、前記第4の辺に沿った前記第2の端子配置領域に配置されてもよい。

【0029】

このようにすれば、第1の端子配置領域に配置される第1の振動子用端子と第1の出力端子との間の距離や、第2の端子配置領域に配置される第2の振動子用端子と第2の出力端子との間の距離を離すことが可能になる。従って、第1、第2の出力端子の信号ノイズ等が、第1、第2の振動子用端子の発振信号に対して悪影響を及ぼす事態等を抑制できるようになる。

【0030】

また本発明の一態様では、前記第1の端子配置領域では、前記第1の振動子用端子と前記第1の出力端子の間に、高電位側電源及び低電位側電源の一方の電源用の第1の電源端子が配置され、前記第2の端子配置領域では、前記第2の振動子用端子と前記第2の出力端子の間に、前記一方とは異なる他方の電源用の第2の電源端子が配置されてもよい。

【0031】

このようにすれば、第1の振動子用端子と第1の出力端子の間に第1の電源端子が配置され、第2の振動子用端子と第2の出力端の間に第2の電源端子が配置されるようになる。従って、第1の振動子用端子と第1の出力端子の間の距離や、第2の振動子用端子と第2の出力端子の間の距離を離して信号ノイズの悪影響等を低減できるようになる。

【0032】

また本発明の他の態様は、上記のいずれかに記載の回路装置を含む電子機器に関係する。

【図面の簡単な説明】

【0033】

【図1】本実施形態の回路装置の第1の構成例。

【図2】本実施形態の回路装置の第2の構成例。

【図3】各モードでのプリバッファーや出力バッファーの制御手法の説明図。

【図4】図4(A)〜図4(C)は出力バッファーの出力信号の種々の態様の説明図。

【図5】図5(A)、図5(B)は出力信号の高調波特性例。

【図6】クリップドサイン波出力回路により構成される出力バッファーの詳細な構成例。

【図7】図7(A)〜図7(D)はクリップドサイン波出力回路により構成される出力バッファーの各ノードの信号波形例。

【図8】図8(A)、図8(B)は、クリップドサイン波出力回路により構成される出力バッファーの更に詳細な構成例及び動作説明図。

【図9】MIM構造のキャパシターを用いる手法の説明図。

【図10】プリバッファーの詳細な構成例。

【図11】矩形波出力回路により構成される出力バッファーの詳細な構成例。

【図12】本実施形態の回路装置の詳細なレイアウト配置例。

【図13】本実施形態の電子機器の構成例。

【発明を実施するための形態】

【0034】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0035】

1.構成

図1に本実施形態の回路装置(IC)の第1の構成例を示す。この回路装置は発振回路10、バッファー回路20を含む。また制御回路30、メモリー40、温度補償電圧発生回路50を含むことができる。なお回路装置の構成は図1の構成には限定されず、その一部の構成要素(例えば温度補償電圧発生回路)を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0036】

発振回路10は、振動子XTAL(圧電振動子、水晶振動子)に接続される。具体的には第1、第2の振動子用端子TX1、TX2(振動子用パッド)を介して振動子XTALに接続される。発振回路10は、電圧を印加することで固有振動を起こす振動子XTALを一定の周波数で発振させるための回路である。この発振回路10は、端子TX1が入力ノードに接続され、端子TX2が出力ノードに接続される増幅回路などにより実現できる。

【0037】

バッファー回路20は、発振回路10からの発振信号SSCをバッファリングする回路である。即ち外部の負荷を十分に駆動できるように信号のバッファリングを行う。バッファー回路20により、バッファリングされた信号は、第1、第2の出力信号SQ1、SQ2として第1、第2の出力端子TQ1、TQ2を介して外部に出力される。

【0038】

制御回路30は、発振回路10、バッファー回路20、メモリー40、温度補償電圧発生回路50の制御を行う。また外部とのインターフェース処理なども行う。この制御回路30は、例えばスタンダードセルやゲートアレイ等のロジック回路により実現される。

【0039】

メモリー40は、回路装置の動作に必要な各種の情報を記憶する。例えば温度補償電圧発生回路50が温度補償処理を行うために必要な情報等を記憶する。

【0040】

温度補償電圧発生回路50は、TCXOを実現するための温度補償電圧を発生して、発振回路10に出力する。これにより発振周波数の温度補償が実現される。

【0041】

バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。

【0042】

プリバッファーPBFには、発振回路10からの発振信号SSCが入力される。具体的には、発振回路10からの正弦波の発振信号SSCは、DCカット用のキャパシターCBを介してプリバッファーPBFに入力される。そしてプリバッファーPBFは、バッファリングした信号を第1、第2の出力バッファーQBF1、QBF2に出力する。

【0043】

第1の出力バッファーQBF1は、プリバッファーPBFからの信号SPBが入力され、第1の出力信号SQ1を出力する。具体的には第1の出力信号SQ1を第1の出力端子TQ1を介して外部(回路装置の外部デバイス)に出力する。第2の出力バッファーQBF2は、プリバッファーPBFからの信号SPBが入力され、第2の出力信号SQ2を出力する。具体的には第2の出力バッファーQBF2には、プリバッファーPBFからの信号SPBがスイッチ回路SWYを介して入力され、第2の出力信号SQ2を第2の出力端子TQ2を介して外部に出力する。

【0044】

そして本実施形態では、第1のモード(第1の状態)では、第1の出力バッファーQBF1が動作イネーブル状態(信号出力状態)に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態(信号非出力状態)に設定される。一方、第2のモード(第2の状態)では、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。そして第1のモードでは、プリバッファーPBFの駆動能力(電流駆動能力)が、第2のモードに比べて低い駆動能力に設定される。

【0045】

出力バッファーQBF1、QBF2が動作イネーブル状態に設定されると、QBF1、QBF2が出力信号SQ1、SQ2を出力するようになる。一方、出力バッファーQBF1、QBF2が動作ディスエーブル状態に設定されると、QBF1、QBF2が出力信号SQ1、SQ2を出力しなくなる。この動作イネーブル状態、動作ディスエーブル状態の制御は、制御回路30からの制御信号により実現される。またプリバッファーPBFの駆動能力の制御も、制御回路30からの制御信号により実現される。例えばプリバッファーPBFの駆動能力の制御は、PBFの出力トランジスターの駆動能力(電流駆動能力、W/L)を制御することで実現される。

【0046】

またバッファー回路20はスイッチ回路SWYを含む。このスイッチ回路SWYは、プリバッファーPBFの出力ノードと第2の出力バッファーQBF2の入力ノードとの間に設けられる。そしてスイッチ回路SWYは、第1のモードではオフ状態に設定され、第2のモードではオン状態に設定される。即ち、第1のモードでは、出力バッファーQBF2が動作ディスエーブル状態に設定されると共に、スイッチ回路SWYがオフ状態になる。これにより、プリバッファーPBFの出力ノードから出力バッファーQBF2が切り離される。この時、プリバッファーPBFの駆動能力は低い駆動能力に設定される。一方、第2のモードでは、出力バッファーQBF2が動作イネーブル状態に設定されると共に、スイッチ回路SWYがオン状態になる。これにより、プリバッファーPBFの出力ノードに出力バッファーQBF2が接続されるようになる。

【0047】

なお、プリバッファーPBFの出力ノードと出力バッファーQBF1の間にスイッチ回路を設けてもよい。

【0048】

また図1において、出力バッファーQBF1、QBF2が共に動作ディスエーブル状態に設定された場合には、プリバッファーPBFも動作ディスエーブル状態に設定されることが望ましい。このようにプリバッファーPBFを動作ディスエーブル状態に設定すれば、動作ディスエーブル状態に設定された出力バッファーQBF1、QBF2のみならず、プリバッファーPBFにおいても、無駄に電力が消費されたり、EMIノイズ等を発生してしまう事態を抑制できる。即ち、出力バッファーQBF1、QBF2が共に動作ディスエーブル状態に設定された場合には、出力信号SQ1、SQ2を外部に出力する必要がない。このため、出力バッファーQBF1、QBF2に信号SPBを供給するプリバッファーPBFについても動作ディスエーブル状態に設定することで、無駄な電力消費を抑制する。

【0049】

図2に本実施形態の回路装置の第2の構成例を示す。図1の第1の構成例との相違点は、図2ではバッファー回路20に更に第3の出力バッファーQBF3が設けられている点である。

【0050】

第3の出力バッファーQBF3は、プリバッファーPBFからの信号SPBが入力され、第3の出力信号SQ3を出力する。具体的には第3の出力バッファーQBF3は、プリバッファーPBFからの信号SPBがスイッチ回路SWZを介して入力され、第3の出力信号SQ3を第3の出力端子TQ3を介して外部に出力する。

【0051】

図3は、図2の第2の構成例の動作を説明する図である。図3に示すように、第1のモードM1では、出力バッファーQBF1が動作イネーブル状態に設定され、出力バッファーQBF2及びQBF3が動作ディスエーブル状態に設定される。一方、第2のモードM2では、出力バッファーQBF1及びQBF2が動作イネーブル状態に設定され、出力バッファーQBF3が動作ディスエーブル状態に設定される。また、第3のモードM3では、出力バッファーQBF1、QBF2及びQBF3が動作イネーブル状態に設定される。

【0052】

なお、第1、第2、第3のモードの選択は、不図示の設定用外部端子で設定してもよいし、メモリーブロック内の不揮発領域の記憶した値で設定してもよい。

【0053】

そして第1のモードM1では、プリバッファーPBFの駆動能力が、第2のモードM2に比べて低い駆動能力に設定される。また、第2のモードM2では、プリバッファーPBFの駆動能力が、第3のモードM3に比べて低い駆動能力に設定される。

【0054】

即ち、全ての出力バッファーQBF1、QBF2、QBF3が動作イネーブル状態に設定される第3のモードM3では、プリバッファーPBFの駆動能力が最も大きくなる。一方、出力バッファーQBF1のみが動作イネーブル状態に設定される第1のモードM1では、プリバッファーPBFの駆動能力が最も小さくなる。そして出力バッファーQBF1、QBF2が動作イネーブル状態に設定され、出力バッファーQBF3が動作ディスエーブル状態に設定される第2のモードM2では、プリバッファーPBFの駆動能力は、第1のモードM1と第3のモードM3の駆動能力の中間の駆動能力になる。

【0055】

なおバッファー回路20が含むスイッチ回路SWZは、プリバッファーPBFの出力ノードと出力バッファーQBF3の入力ノードとの間に設けられる。そしてスイッチ回路SWZは、第1、第2のモードM1、M2ではオフ状態に設定され、第3のモードM3ではオン状態に設定される。即ち、第1、第2のモードM1、M2では、出力バッファーQBF3が動作ディスエーブル状態に設定されると共に、スイッチ回路SWZがオフ状態になることで、プリバッファーPBFの出力ノードから出力バッファーQBF3が切り離される。一方、第3のモードM3では、出力バッファーQBF3が動作イネーブル状態に設定されると共に、スイッチ回路SWZがオン状態になることで、プリバッファーPBFの出力ノードに出力バッファーQBF3が接続されるようになる。

【0056】

また図2において、出力バッファーQBF1、QBF2、QBF3が共に動作ディスエーブル状態に設定された場合には、プリバッファーPBFも動作ディスエーブル状態に設定されることが望ましい。こうすることで、動作ディスエーブル状態に設定された出力バッファーQBF1、QBF2、QBF3のみならず、プリバッファーPBFにおいても、無駄に電力が消費されたり、EMIノイズ等が発生してしまう事態を抑制できる。

【0057】

図4(A)〜図4(C)に出力バッファーの出力信号の信号波形例を示す。図4(A)では、出力バッファーQBF1は、クリップドサイン波出力回路により構成され、クリップドサイン波の出力信号SQ1を出力している。同様に出力バッファーQBF2もクリップドサイン波出力回路により構成され、クリップドサイン波の出力信号SQ2を出力している。ここでクリップドサイン波は、正弦波の高電位側(上端)と低電位側(下端)を電圧クリップさせた波形(振幅制限波形)である。このクリップドサイン波を用いれば、上下に電圧クリップされた電圧部分が余裕となって、外部デバイス側の負荷が変動しても、出力信号の電圧振幅の変動を最小限に抑えることができるというメリットがある。

【0058】

一方、図4(B)では、出力バッファーQBF1は、クリップドサイン波出力回路により構成され、クリップドサイン波の出力信号SQ1を出力しているのに対して、出力バッファーQBF2は、矩形波出力回路により構成され、矩形波(方形波)の信号SQ2を出力している。例えばクリップドサイン波は矩形波に比べると高調波成分が少ない。従って、回路装置が実装される回路基板等において、クリップドサイン波の信号線を引き回しても、矩形波の信号線を引き回す場合に比べて、EMIノイズ等の発生を抑えることを期待できる。しかしながら、EMIノイズの発生等がそれほど問題にならない信号経路では、クリップドサイン波ではなく矩形波の信号の出力を、ユーザーが望む場合もある。従って、図4(B)のように、クリップドサイン波の出力信号SQ1と矩形波の出力信号SQ2の両方を出力可能にすることで、このようなユーザーの要望に応えることができる。

【0059】

また図4(C)では、出力バッファーQBF1、QBF2はクリップドサイン波の出力信号SQ1を出力し、出力バッファーQBF3は矩形波の信号SQ3を出力している。こうすることで、2本のクリップドサイン波の信号出力と1本の矩形波の信号出力を必要とするユーザーの要望に応えることができる。なお図4(C)において、出力バッファーQBF3もクリップドサイン波の信号SQ3を出力するようにしてもよい。

【0060】

以上の本実施形態の回路装置によれば以下のような効果が得られる。前述のようにTCXOなどの発振器では、多出力機能への要望が高まっている。このような発振器の多出力機能を実現する比較例の手法として、プリバッファーPBFに複数の出力バッファーQBF1〜QBF3を接続する一方で、スイッチ回路SWY、SWZを設けずに、プリバッファーPBFの駆動能力についても変更しない手法が考えられる。

【0061】

しかしながら、この比較例の手法では、図3に示すようにモードM1〜M3が切り替わった場合にも、プリバッファーPBFに対して全ての出力バッファーQBF1〜QBF3が常時接続され、ユーザーの使用条件に関わらずに、出力バッファーQBF1〜QBF3から信号SQ1〜SQ3が出力されることになる。

【0062】

この場合に、比較例の手法では、例えば出力バッファーQBF1〜QBF3に動作イネーブル/動作ディスエーブルの機能を設けたとしても、プリバッファーPBFの駆動能力は、全ての出力バッファーQBF1〜QBF3を駆動できる能力に設定される。このようなプリバッファーPBFの大きな駆動能力は、図3のモードM3のように全ての出力バッファーQBF1〜QBF3が動作イネーブル状態に設定されている場合には、ユーザーの仕様に適合した信号SQ1〜SQ3を出力するために必要となる。即ち、全ての出力バッファーQBF1〜QBF3から信号SQ1〜SQ3が出力される場合に、プリバッファーPBFの駆動能力が低いと、プリバッファーPBFが、出力バッファーQBF1〜QBF3の入力負荷を十分に駆動できなくなり、信号SQ1〜SQ3に対して要求される仕様を満たすことができないおそれがあるからである。

【0063】

しかしながら、モードM1、M2のように、出力バッファーQBF2やQBF3が動作ディスエーブル状態に設定され、信号SQ2、SQ3が出力されていない状況で、プリバッファーPBFの駆動能力が高すぎると、無駄な電力が消費されてしまう。即ち、出力バッファーQBF2やQBF3が動作ディスエーブル状態に設定されていても、プリバッファーPBFから見た負荷は変わらず、プリバッファーPBFは、全出力バッファーを駆動できる能力で出力バッファーの入力負荷を駆動することになり、不要な電力消費を招く。

【0064】

この点、本実施形態によれば、図3のモードM1、M2のように出力バッファーQBF2やQBF3が動作ディスエーブル状態の場合には、プリバッファーPBFの駆動能力が低く設定される。従って、プリバッファーPBFは、モードM1、M2では、モードM3のような最大の駆動能力で駆動しなくても済むようになり、無駄な電力の消費を抑えることができる。

【0065】

また、モードM1、M2では、アナログのスイッチ回路SWYやSWZがオフ状態になるため、プリバッファーPBFの出力から出力バッファーQBF2やQBF3の入力ラインが切り離される。このように入力ラインが切り離されることで、プリバッファーPBFから見た負荷が軽くなるため、図3のようにプリバッファーPBFの駆動能力を低くしても、駆動能力が不十分になってしまう問題は生じなくなる。即ちアナログのスイッチ回路SWYやSWZのオン・オフに連動してプリバッファーPBFの駆動能力を調整することで、最適な負荷及び駆動能力でのプリバッファーPBFの駆動が可能になる。

【0066】

またプリバッファーPBFの駆動能力と、出力バッファーQBF1〜QBF3の負荷容量とが整合していないと、出力信号に高調波が発生する問題が生じる。これは、特に図4(A)〜図4(C)で説明したようなクリップドサイン波の出力信号の場合に深刻な問題になる。

【0067】

例えば図5(A)は、モードM1〜M3の切換に応じてプリバッファーPBFの駆動能力を変化させなかった場合の出力信号の高調波特性である。図5(A)のようにプリバッファーPBFの駆動能力を変化させなかった場合には、偶数次の高調波が大きくなってしまう。

【0068】

これに対して、図5(B)は、モードM1〜M3の切換に応じて図3に示すようにプリバッファーPBFの駆動能力を変化させた場合の出力信号の高調波特性である。図5(B)に示すように、プリバッファーPBFの駆動能力を変化させることで、図5(A)の場合に比べて偶数次の高調波を抑制できる。従って、モードM1〜M3に応じてプリバッファーPBFの駆動能力を変化させることで、EMIノイズの低減等を図れるようになる。

【0069】

以上のように本実施形態によれば、複数の出力バッファーを設け、非動作となる出力バッファーについては、その入力側に設けられたアナログのスイッチ回路をオフさせると共に、それに連動してプリバッファーの能力も調整している。これにより、回路動作の無駄をなくして低消費電力化を図ると共に、プリバッファーから出力バッファーへの信号供給も安定して行うことができることから、発振器としての安定した出力を得ることが可能になる。

【0070】

2.具体的回路構成

次に出力バッファーやプリバッファーの具体的な回路構成例について説明する。図6にクリップドサイン波出力回路により構成される出力バッファーQBF1や、プリバッファーPBFの回路構成例を示す。なお出力バッファーQBF2がクリップドサイン波出力回路により構成される場合には、図6のQBF1と同様の構成になる。

【0071】

図6に示すように、出力バッファーQBF1を構成するクリップドサイン波出力回路は、第1、第2のトランジスターTA1、TA2、第1、第2のバイアス電圧設定回路BAS1、BAS2、第1、第2のキャパシターCA1、CA2を含む。

【0072】

トランジスターTA1は、VDDノード(広義には高電位側電源ノード)と出力ノードNAQとの間に設けられる。トランジスターTA2は、出力ノードNAQとVSSノード(広義には低電位側電源ノード)との間に設けられる。例えばトランジスターTA1はN型トランジスター(第1導電型トランジスター)であり、トランジスターTA2はP型トランジスターである。なおVDDノードとトランジスターTA1の間に電圧調整回路等を設けてもよい。

【0073】

バイアス電圧設定回路BAS1は、トランジスターTA1のゲートノードである第1のゲートノードNG1に対してバイアス電圧を設定する回路である。このバイアス電圧設定回路BAS1は、例えばVDDノードとVSSノードの間に直列に設けられる第1、第2の抵抗素子RA1、RA2を含む。これによりVDD−VSS間を抵抗素子RA1、RA2で抵抗分割した電圧が、バイアス電圧としてゲートノードNG1に印加されるようになる。

【0074】

バイアス電圧設定回路BAS2は、トランジスターTA2のゲートノードである第2のゲートノードNG2に対してバイアス電圧を設定する回路である。このバイアス電圧設定回路BAS2は、例えばゲートノードNG2とVSSノードの間に設けられる第4の抵抗素子RA4を含む。

【0075】

キャパシターCA1は、プリバッファーPBFからの信号が入力される入力ノードNAIとゲートノードNG1との間に設けられる。キャパシターCA2は、入力ノードNAIとゲートノードNG2との間に設けられる。これらのキャパシターCA1、CA2はDCカット用(ACカップリング用)のキャパシターである。

【0076】

スイッチ回路SWXは、プリバッファーPBFの出力ノードNBQと出力バッファーQBF1の入力ノードNAIの間に設けられる。スイッチ回路SWXはトランスファーゲートにより構成され、トランスファーゲートのN型トランジスターのゲートにはスイッチ制御信号SXが入力され、P型トランジスターのゲートにはスイッチ制御信号XSXが入力される。なお信号XSXの先頭の「X」は負論理の信号であることを意味する。

【0077】

スイッチ回路SWYは、プリバッファーPBFの出力ノードNBQと出力バッファーQBF2の入力ノードの間に設けられる。スイッチ回路SWYはトランスファーゲートにより構成され、トランスファーゲートのN型トランジスターのゲートにはスイッチ制御信号SYが入力され、P型トランジスターのゲートには負論理のスイッチ制御信号XSYが入力される。

【0078】

プリバッファーPBFは、インバーター回路IVB1とIVB2を含む。インバーター回路IVB1の出力は抵抗素子RBを介してIVB1の入力に帰還される。これにより、発振回路10からキャパシターCBを介して入力されるACの信号の増幅処理が行われるようになる。

【0079】

なお出力端子TQ1と外部ノードNCの間にはキャパシターCC1(例えば0.01μF)が設けられる。ノードNCに接続される抵抗素子RC(例えば10kΩ)、キャパシターCC2(例えば10pF)は外部負荷を表すものである。また出力バッファーQBF2がクリップドサイン波を出力する場合には、QBF2もQBF1と同様の構成のクリップドサイン波出力回路により構成されることになる。

【0080】

図7(A)〜図7(D)は、図6の回路の動作を説明するための信号波形例である。図7(A)、図7(B)、図7(C)、図7(D)には、各々、図6のノードNAI、NG1、NG2、NAQの信号波形(電圧波形)が示されている。

【0081】

例えばノードNA1の電圧が図7(A)のように変化すると、ノードNG1の電圧は、バイアス電圧設定回路BAS1によるバイアス電圧を基準として図7(B)のように変化する。またノードNG1の電圧は、バイアス電圧設定回路BAS2によるバイアス電圧を基準として図7(C)のように変化する。これにより出力ノードNAQには、図7(D)に示すようなクリップドサイン波の信号が出力されるようになる。

【0082】

図8(A)は、出力バッファーQBF1等を構成するクリップドサイン波出力回路の更に具体的な回路構成例である。

【0083】

図8(A)に示すように、バイアス電圧設定回路BAS1は、VDDノード(高電位側電源ノード)とゲートノードNG1との間に直列に設けれる第1の抵抗素子RA1及び第1のスイッチ素子SWA1を含む。またゲートノードNG1とVSSノード(低電位側電源ノード)との間に設けられる第2の抵抗素子RA2を含む。なお図8(A)ではゲートノードNG1側にスイッチ素子SWA1が設けられているが、VDDノード側にSWA1を設けてもよい。

【0084】

バイアス電圧設定回路BAS2は、VDDノードとゲートノードNG2との間に直列に設けれる第3の抵抗素子RA3及び第2のスイッチ素子SWA2を含む。またゲートノードNG2とVSSノードとの間に設けられる第4の抵抗素子RA4及び第3のスイッチ素子SWA3を含む。なお図8(A)ではVDDノード側にスイッチ素子SWA2が設けられ、ゲートノードNG2側にスイッチ素子SWA3が設けられているが、ゲートノードNG2側にSWA2を設け、VSSノード側にSWA3を設けてもよい。

【0085】

そして図8(A)に示すように、クリップドサイン波出力回路の動作イネーブル状態(通常動作状態)では、スイッチ素子SWA1及びSWA3がオン状態に設定され、スイッチ素子SWA2がオフ状態に設定される。これにより、VDDとVSSを抵抗素子RA1、RA2で抵抗分割した電圧が、バイアス電圧としてゲートノードNG1に設定される。またVSS(GND)の電圧が、バイアス電圧としてゲートノードNG2に設定される。

【0086】

一方、動作ディスエーブル状態では、図8(B)に示すように、スイッチ素子SWA1及びSWA3がオフ状態に設定され、スイッチ素子SWA2がオン状態に設定される。スイッチ素子SWA1がオフ状態になることで、ノードNG1から抵抗素子RA1が切り離され、ノードNG1がVSSの電圧(GND電圧=0V)に設定(プルダウン)される。これにより、N型のトランジスターTA1がオフ状態に設定される。

【0087】

またスイッチ素子SWA3がオフ状態になることで、ゲートノードNG2から抵抗素子RA4が切り離される。そしてスイッチ素子SWA2がオン状態になることで、ゲートノードNG2がVDDの電圧に設定(プルアップ)される。これにより、P型のトランジスターTA2がオフ状態に設定される。

【0088】

以上のように、クリップドサイン波出力回路の動作イネーブル状態では、バイアス電圧設定回路BAS1、BAS2により、トランジスターTA1、TA2のゲートノードNG1、NG2に適切なバイアス電圧が設定され、これにより図4(A)等に示すように、出力ノードNAQからクリップドサイン波の信号が出力されるようになる。一方、動作ディスエーブル状態では、トランジスターTA1、TA2のゲートノードNG1、NG2が、各々、VDD、VSSの電圧が設定され、TA1、TA2がオフになる。従って、出力ノードNAQからはクリップドサイン波の信号が出力されないようになり、クリップドサイン波出力回路の動作ディスエーブルを実現できるようになる。

【0089】

図9は、図6、図8(A)、図8(B)のCA1、CA2のキャパシター構造例を示す図である。図9に示すように、キャパシターCA1、CA2は、MIM(Metal-Insulator-Metal)構造のキャパシターにより構成される。具体的には、メタル層META、METBと、META、METBの間に設けられる絶縁層によりなるMIM構造のキャパシターにより、CA1、CA2が構成される。

【0090】

そしてMIM構造のキャパシターCA1の上部電極ELT(METB)が図6、図8(A)、図8(B)の出力バッファーの入力ノードNAIに接続される。一方、下部電極ELB(META)がゲートノードNG1に接続される。同様に、MIM構造のキャパシターCA2の上部電極ELTが入力ノードNAIに接続され、下部電極ELBがゲートノードNG2に接続される。このようにすることで、出力バッファーの入力ノードNAIの負荷容量を減少させることができ、プリバッファーPBFの充放電電力を減らすことができるため、無駄な電力の消費を抑制できる。

【0091】

即ち、下部電極ELBには、基板等の間の寄生容量CSが大きい。従って、下部電極ELBが出力バッファーの入力ノードNAIに接続されると、この寄生容量CSの容量値の分だけ、出力バッファーの負荷容量が増えてしまう。

【0092】

この点、本実施形態では図9に示すように、出力バッファーの入力ノードNAIは、下部電極ELBではなく上部電極ELTに接続される。従って、入力ノードNAIに、基板との寄生容量CSが寄生する事態を抑制でき、プリバッファーPBFの無駄な電力消費を抑制できるようになる。

【0093】

図10にプリバッファーPBFの構成例を示す。なおプリバッファーPBFは図10の構成には限定されず、その一部の構成要素を省略したり、他の構成要素を通過するなどの種々の変形実施が可能である。

【0094】

図10に示すようにプリバッファーPBFは、インバーター回路IVB1と、IVB1の出力ノードに入力ノードが接続されるインバーター回路IVB2を含む。

【0095】

インバーター回路IVB1は、VDDノードとVSSノードの間に直列に設けられたP型トランジスターTB1、N型トランジスターTB2を含む。そしてインバーター回路IVB1の出力は抵抗素子RBを介してIVB1の入力に帰還される。

【0096】

駆動能力調整用のインバーター回路IVB2は、VDDノードとVSSノードの間に直列に設けられたP型トランジスターTB3、N型トランジスターTB4を含む。またVDDノードと出力ノードNBQの間に直列に設けられた駆動能力調整用のP型トランジスターTB5及びスイッチ素子SWB1と、P型トランジスターTB7及びスイッチ素子SWB3を含む。また出力ノードNBQとVSSノードとの間に直列に設けられた駆動能力調整用のスイッチ素子SWB2及びN型トランジスターTB6と、スイッチ素子SWB4及びN型トランジスターTB8を含む。なおP型トランジスターTB3、TB5、TB7は例えば同じ電流供給能力(W/L)を有し、N型トランジスターTB4、TB6、TB8は例えば同じ電流供給能力(W/L)を有する。但しトランジスターTB3、TB4の電流供給能力を他のトランジスターよりも大きくしてもよい。

【0097】

プリバッファーPBFの駆動能力の制御は、制御回路30がスイッチ素子SWB1〜SWB4のスイッチ制御を行うことで実現される。

【0098】

例えば図3のモードM3では、制御回路30は、スイッチ素子SWB1、SWB2、SWB3、SWB4をオン状態に設定する。これにより、駆動能力調整用のトランジスターTB5、TB6、TB7、TB8のドレインが出力ノードNBQに接続され、プリバッファーPBFの駆動能力は、トランジスターTB3、TB4、TB5、TB6、TB7、TB8を並列接続した駆動能力になる。この結果、モードM3でのプリバッファーPBFの駆動能力は、他のモードM1、M2に比べて高い駆動能力に設定される。

【0099】

またモードM2では、制御回路30は、例えばスイッチ素子SWB1、SWB2をオン状態に設定し、SWB3、SWB4をオフ状態に設定する。これにより、駆動能力調整用のトランジスターTB7、TB8のドレインが出力ノードNBQから切り離され、プリバッファーPBFの駆動能力は、トランジスターTB3、TB4、TB5、TB6を並列接続した駆動能力になる。この結果、モードM2でのプリバッファーPBFの駆動能力は、モードM3に比べて低い駆動能力に設定される。

【0100】

またモードM3では、制御回路30は、例えばスイッチ素子SWB1、SWB2、SWB3、SWB4をオフ状態に設定する。これにより、駆動能力調整用のトランジスターTB5、TB6、TB7、TB8のドレインが出力ノードNBQから切り離され、プリバッファーPBFの駆動能力はトランジスターTB3、TB4の駆動能力になる。この結果、モードM1でのプリバッファーPBFの駆動能力は、モードM2に比べて低い駆動能力に設定される。

【0101】

以上のようにすれば、モードM1、M2、M3において出力バッファーQBF1〜QBF3の動作イネーブル/動作ディスエーブルが設定された場合に、その設定状態に応じた駆動能力に、プリバッファーPBFの駆動能力も設定されるようになる。従って、プリバッファーPBFで無駄に電力が消費されたり、図5(A)のように高調波が増加することによりEMIノイズが生じるなどの事態の発生を抑制できるようになる。

【0102】

なお、プリバッファーPBFの構成は図10の構成に限定されず、種々の変形実施が可能である。例えば図10では、駆動能力調整用のトランジスター及びスイッチ素子のペアーを2組設けているが、駆動能力調整用のトランジスター及びスイッチ素子のペアーを1組にしたり、3組以上にしてもよい。

【0103】

図11に、図4(B)、図4(C)のように出力バッファーを矩形波出力回路で実現した場合の回路構成例を示す。図11の構成は、図10のプリバッファーPBFの駆動能力調整用のインバーター回路IVB2と同様の構成である。図11では、出力端子TQ2に接続される外部負荷の大きさに応じて、スイッチ素子SWD1〜SWD4のオン・オフ制御が行われ、外部負荷の大きさに応じた出力バッファーの最適な駆動能力の設定が可能になる。

【0104】

また図11では、入力ノードNDIとVSSノードの間にスイッチ素子SWD5及び抵抗素子RDが直列に設けられている。そして出力バッファーを動作イネーブル状態に設定する場合には、スイッチ素子SWD5をオフ状態に設定する。これにより出力端子TQ2から矩形波の信号が出力されるようになる。一方、出力バッファーを動作ディスエーブル状態に設定する場合には、スイッチ素子SWD5をオン状態に設定にして、入力ノードNDIをプルダウンする。これにより、出力端子TQ2の電圧がローレベルに固定され、TQ2を信号非出力状態に設定できるようになる。

【0105】

3.レイアウト配置

図12に本実施形態の回路装置のレイアウト配置例を示す。図12は、回路装置のチップを平面視で見た図である。なお本実施形態の回路装置のレイアウト配置は図12の配置例に限定されず、種々の変形実施が可能である。

【0106】

図12において、回路装置の対向する辺を第1の辺SD1、第2の辺SD2とする。また回路装置の辺SD1、SD2に交差(例えば直交)する辺を第3の辺SD3、第4の辺SD4とする。図12では辺SD1、SD2が短辺となり、辺SD3、SD4が長辺となっている。

【0107】

また図12において、回路装置の対向する辺SD1、SD2の間の境界線BDLにより区分される一方の領域を第1の領域AR1とし、他方の領域を第2の領域AR2とする。例えば境界線BDLは、辺SD1、SD2に平行な線であり、辺SD1、SD2の中線に沿った線になる。そして領域AR1は、境界線BDLを基準として辺SD1側の領域であり、領域AR2は、境界線BDLを基準として辺SD2側の領域である。

【0108】

この場合に図12では、振動子XTALを接続するための第1の振動子用端子TX1及び第2の振動子用端子TX2が、第1の領域AR1に配置される。即ち、振動子用端子TX1、TX2は、辺SD1と境界BDLの間の領域AR1に配置されており、辺SD1側に配置されている。

【0109】

一方、出力バッファーQB1からの出力信号SQ1が出力される出力端子TQ1と、出力バッファーかQB2からの出力信号SQ2が出力される出力端子TQ2は、第2の領域AR2に配置される。即ち、出力端子TQ1、TQ2は、辺SD2と境界BDLの間の領域AR2に配置されており、辺SD2側に配置されている。また出力バッファーQB3からの出力信号SQ3が出力される出力端子TQ3も領域AR2に配置される。具体的には出力端子TQ3は出力端子TQ1(又はTQ2)と辺SD2の間に配置される。

【0110】

そして本実施形態では、発振回路10及びバッファー回路20が、領域AR1に配置される。即ち、発振回路10及びバッファー回路20が、辺SD2側の領域AR2ではなく、辺SD1側の領域AR1に配置される。例えば発振回路10及びバッファー回路20が、制御回路30と辺SD1の間に配置される。

【0111】

このようにすれば、出力端子TQ1、TQ2、TQ3の出力信号SQ1、SQ2、SQ3からのノイズが、発振回路10等の動作に悪影響を与える事態を抑制できる。即ち図5(A)、図5(B)のような高調波が発振回路10の動作に悪影響を与えて、発振回路10の動作が不安定になったり、発振周波数が変動等してしまう事態を抑制できるようになる。特に、出力端子TQ3から矩形波の出力信号が出力される場合に、この出力端子TQ3を発振回路10から最も遠い位置に配置することで、矩形波の信号の高調波等が発振回路10の動作等に悪影響を与える事態を抑制できる。

【0112】

そして、このようなレイアウト配置では、バッファー回路20と出力端子TQ1〜TQ3の距離が離れてしまうという問題もある。しかしながら、バッファー回路20は、外部の大きな負荷を駆動できる十分な駆動能力を有しているため、このように距離が離れてもそれほど問題は生じないことになる。例えば、出力バッファーに比べて駆動能力が小さなプリバッファーの出力信号線を、長い距離に亘って配線すると、プリバッファーの信号にノイズ等が重畳されて、出力端子TQ1〜TQ3からの信号にもノイズ等が重畳される事態が生じるおそれがある。この点、図12では、プリバッファーではなく、出力バッファーの出力信号線が、バッファー回路20から出力端子TQ1〜TQ3に配線されるため、上記のような事態の発生を抑止できる。

【0113】

また図12では、振動子用端子TX1は、辺SD3に沿った第1の端子配置領域IO1に配置され、振動子用端子TX2は、辺SD4に沿った第2の端子配置領域IO2に配置される。また出力端子TQ1は、辺SD3に沿った端子配置領域IO1に配置され、出力端子TQ2は、辺SD4に沿った端子配置領域IO2に配置される。また出力端子TQ3は端子配置領域IO1(或いはIO2)に配置される。

【0114】

ここで端子配置領域IO1、IO2は、外部デバイスを接続するための端子(パッド)が配置される領域である。例えば端子配置領域IO1は、発振回路10、制御回路30等の内部回路と辺SD3との間に設けられ、所定幅を有するI/O領域である。端子配置領域IO2は、内部回路と辺SD4との間に設けられ、所定幅を有するI/O領域である。

【0115】

このようにすれば、振動子用端子TX1、TX2は、回路装置の端子配置領域IO1又はIO2の辺SD1側(AR1側)に配置されるようになる。また、出力端子TQ1、TQ2、TQ3は、端子配置領域IO1又はIO2の辺SD2側(AR2側)に配置されるようになる。従って、振動子用端子TX1、TX2と出力端子TQ1、TQ2、TQ3の間の距離を離すことが可能になり、出力端子TQ1、TQ2、TQ3の信号ノイズ等が、振動子用端子TX1、TX2の発振信号に対して悪影響を及ぼす事態を抑制できるようになる。また、回路装置のICを回路基板等に実装した場合に、振動子XTALの実装や、出力端子TQ1〜TQ3からの信号線の回路基板上での配線を、簡素化することなどが可能になる。

【0116】

また端子配置領域IO1では、振動子用端子TX1と出力端子TQ1の間に、電源VDD用(広義には高電位側電源及び低電位側電源の一方の電源用)の電源端子TVDDが配置される。また端子配置領域IO1では、振動子用端子TX1と出力端子TQ1の間に、回路装置の制御用端子TCT1も配置される。

【0117】

一方、端子配置領域IO2では、振動子用端子TX2と出力端子TQ2の間に、電源VSS用(広義には一方とは異なる他方の電源用)の電源端子TVSSが配置される。また端子配置領域IO2では、振動子用端子TX2と出力端子TQ2の間に、回路装置の制御用端子TCT2も配置される。なお制御用端子TCT1、TCT2は、発振周波数を可変設定するための端子や、図3に示すモードM1〜M3を切り替えるための端子である。

【0118】

このような端子配置にすれば、振動子用端子TX1と出力端子TQ1、TQ3の間に、電源端子TVDDや制御用端子TCT1が配置されるようになる。従って、振動子用端子TX1と出力端子TQ1、TQ3の間の距離を離して信号ノイズの悪影響を低減できると共に、端子配置領域IO1の領域を有効活用した効率的な端子配置を実現できるようになる。また、このような端子配置にすれば、振動子用端子TX2と出力端子TQ2の間に、電源端子TVSSや制御用端子TCT2が配置されるようになる。従って、振動子用端子TX2と出力端子TQ2の間の距離を離して信号ノイズの悪影響を低減できると共に、端子配置領域IO2の領域を有効活用した効率的な端子配置を実現できるようになる。

【0119】

以上のように図12のレイアウト配置によれば、信号ノイズが発振信号に重畳されるのを抑制しながら効率的なレイアウト配置を実現できる。

【0120】

4.電子機器

図13に本実施形態の回路装置を含む電子機器の構成例を示す。この電子機器は、本実施形態の回路装置500、水晶振動子等の振動子XTAL、アンテナATN、通信部510、処理部520を含む。また操作部530、表示部540、記憶部550を含むことができる。なおこれらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0121】

図13の電子機器としては、例えば携帯型情報端末(携帯電話、スマートフォーン)、生体計測機器(脈拍計、歩数計等)、映像機器(デジタルカメラ、ビデオカメラ)などの種々の機器を想定できる。

【0122】

通信部510(無線回路)は、アンテナANTを介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部520は、電子機器の制御処理や、通信部510を介して送受信されるデータの種々のデジタル処理などを行う。この処理部520の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現される。

【0123】

操作部530は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部540は、各種の情報を表示するものであり、液晶や有機ELなどのディスプレイにより実現できる。なお操作部530としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが表示部540の機能を兼ねることになる。記憶部550は、データを記憶するものであり、その機能はRAMやROMなどの半導体メモリーやHDD(ハードディスクドライブ)などにより実現できる。

【0124】

図13の電子機器によれば、ユーザーの使用条件に応じた適切な出力信号を回路装置500から出力して、電子機器の各部に対して供給できるようになる。そして、この場合に図3に示すように各モードに応じた適切な駆動能力にプリバッファーの駆動能力を設定することで、信号品質の高い出力信号を電子機器の各部に対して供給できるようになる。また回路装置が発生するEMIノイズも低減されるため、電子機器のEMI性能やノイズ耐性を向上できるようになる。

【0125】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また回路装置、電子機器の構成・動作や、プリバッファーの駆動能力の設定手法、動作イネーブル/ディスエーブルの設定手法、信号のバッファリング手法、スイッチの制御手法等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。

【符号の説明】

【0126】

PBF プリバッファー、QBF1、QBF2、QBF3 第1〜第3の出力バッファー、

SWX、SWY、SWZ スイッチ回路、CB キャパシター、XTAL 振動子、

TX1、TX2 第1、第2の振動子用端子、TQ1〜TQ3 第1〜第3の出力端子、

TA1、TA2、TB1〜TB8、TD3〜TD8 トランジスター、

CA1、CA2 第1、第2のキャパシター、RA1〜RA4、RB 抵抗素子、

BAS1、BAS2 第1、第2のバイアス電圧設定回路、

SWA1〜SWA3、SWB1〜SWB4、SWD1〜SWD4 スイッチ素子、

BDL 境界線、AR1、AR2 第1、第2の領域、

SD1〜SD4 第1〜第4の辺、IO1、IO2 第1、第2の端子配置領域、

10 発振回路、20 バッファー回路、30 制御回路、40 メモリー、

50 温度補償電圧発生回路、500 回路装置、510 通信部、520 処理部、

530 操作部、540 表示部、550 記憶部

【特許請求の範囲】

【請求項1】

振動子に接続される発振回路と、

前記発振回路からの発振信号をバッファリングするバッファー回路と、

を含み、

前記バッファー回路は、

前記発振回路からの前記発振信号が入力されるプリバッファーと、

前記プリバッファーからの信号が入力され、第1の出力信号を出力する第1の出力バッファーと、

前記プリバッファーからの信号が入力され、第2の出力信号を出力する第2の出力バッファーと、

を含み、

第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファーが動作ディスエーブル状態に設定され、

第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、

前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定されることを特徴とする回路装置。

【請求項2】

請求項1において、

前記バッファー回路は、

前記プリバッファーの出力ノードと前記第2の出力バッファーの入力ノードとの間に設けられるスイッチ回路を含み、

前記スイッチ回路は、前記第1のモードではオフ状態に設定され、前記第2のモードではオン状態に設定されることを特徴とする回路装置。

【請求項3】

請求項1又は2において、

前記第1の出力バッファー、或いは前記第1の出力バッファー及び前記第2の出力バッファーが、クリップドサイン波の信号を出力するクリップドサイン波出力回路により構成されることを特徴とする回路装置。

【請求項4】

請求項3において、

前記クリップドサイン波出力回路は、

高電位側電源ノードと出力ノードとの間に設けられる第1のトランジスターと、

前記出力ノードと低電位側電源ノードとの間に設けられる第2のトランジスターと、

前記第1のトランジスターのゲートノードである第1のゲートノードに対してバイアス電圧を設定する第1のバイアス電圧設定回路と、

前記第2のトランジスターのゲートノードである第2のゲートノードに対してバイアス電圧を設定する第2のバイアス電圧設定回路と、

前記プリバッファーからの信号が入力される入力ノードと前記第1のゲートノードとの間に設けられる第1のキャパシターと、

前記入力ノードと前記第2のゲートノードとの間に設けられる第2のキャパシターと、 を含むことを特徴とする回路装置。

【請求項5】

請求項4において、

前記第1のバイアス電圧設定回路は、

前記高電位側電源ノードと前記第1のゲートノードとの間に直列に設けれる第1の抵抗素子及び第1のスイッチ素子と、

前記第1のゲートノードと前記低電位側電源ノードとの間に設けられる第2の抵抗素子を含み、

前記第2のバイアス電圧設定回路は、

前記高電位側電源ノードと前記第2のゲートノードとの間に直列に設けれる第3の抵抗素子及び第2のスイッチ素子と、

前記第2のゲートノードと前記低電位側電源ノードとの間に設けられる第4の抵抗素子及び第3のスイッチ素子を含み、

動作イネーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオン状態に設定され、前記第2のスイッチ素子がオフ状態に設定され、

動作ディスエーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオフ状態に設定され、前記第2のスイッチ素子がオン状態に設定されることを特徴とする回路装置。

【請求項6】

請求項4又は5において、

前記第1のキャパシター及び前記第2のキャパシターは、MIM(Metal-Insulator-Metal)構造のキャパシターにより構成され、

MIM構造の前記第1のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第1のゲートノードに接続され、

MIM構造の前記第2のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第2のゲートノードに接続されることを特徴とする回路装置。

【請求項7】

請求項1又は2において、

前記第1の出力バッファーがクリップドサイン波の信号を出力するクリップドサイン波出力回路により構成され、前記第2の出力バッファーが、矩形波の信号を出力する矩形波出力回路により構成されることを特徴とする回路装置。

【請求項8】

請求項1乃至7のいずれかにおいて、

前記第1の出力バッファー及び前記第2の出力バッファーが動作ディスエーブル状態に設定された場合に、前記プリバッファーが動作ディスエーブル状態に設定されることを特徴とする回路装置。

【請求項9】

請求項1乃至8のいずれかにおいて、

前記バッファー回路は、

前記プリバッファーからの信号が入力され、第3の出力信号を出力する第3の出力バッファーを含み、

前記第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファー及び前記第3の出力バッファーが動作ディスエーブル状態に設定され、

前記第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、前記第3の出力バッファーが動作ディスエーブル状態に設定され、

第3のモードでは、前記第1の出力バッファー、前記第2の出力バッファー及び前記第3の出力バッファーが動作イネーブル状態に設定され、

前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定され、

前記第2のモードでは、前記プリバッファーの駆動能力が、前記第3のモードに比べて低い駆動能力に設定されることを特徴とする回路装置。

【請求項10】

請求項1乃至9のいずれかにおいて、

回路装置の対向する第1の辺及び第2の辺の間の境界線により区分される一方の領域を第1の領域とし、他方の領域を第2の領域とした場合に、

前記振動子を接続するための第1の振動子用端子及び第2の振動子用端子が、前記第1の領域に配置され、

前記第1の出力バッファーからの前記第1の出力信号が出力される第1の出力端子と、前記第2の出力バッファーからの前記第2の出力信号が出力される第2の出力端子が、前記第2の領域に配置され、

前記発振回路及び前記バッファー回路が、前記第1の領域に配置されることを特徴とする回路装置。

【請求項11】

請求項10において、

回路装置の前記第1の辺及び前記第2の辺に交差する辺を第3の辺及び第4の辺とした場合に、

前記第1の振動子用端子は、前記第3の辺に沿った第1の端子配置領域に配置され、

前記第2の振動子用端子は、前記第4の辺に沿った第2の端子配置領域に配置され、

前記第1の出力端子は、前記第3の辺に沿った前記第1の端子配置領域に配置され、

前記第2の出力端子は、前記第4の辺に沿った前記第2の端子配置領域に配置されることを特徴とする回路装置。

【請求項12】

請求項11において、

前記第1の端子配置領域では、

前記第1の振動子用端子と前記第1の出力端子の間に、高電位側電源及び低電位側電源の一方の電源用の第1の電源端子が配置され、

前記第2の端子配置領域では、

前記第2の振動子用端子と前記第2の出力端子の間に、前記一方とは異なる他方の電源用の第2の電源端子が配置されることを特徴とする回路装置。

【請求項13】

請求項1乃至12のいずれかに記載の回路装置を含むことを特徴とする電子機器。

【請求項1】

振動子に接続される発振回路と、

前記発振回路からの発振信号をバッファリングするバッファー回路と、

を含み、

前記バッファー回路は、

前記発振回路からの前記発振信号が入力されるプリバッファーと、

前記プリバッファーからの信号が入力され、第1の出力信号を出力する第1の出力バッファーと、

前記プリバッファーからの信号が入力され、第2の出力信号を出力する第2の出力バッファーと、

を含み、

第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファーが動作ディスエーブル状態に設定され、

第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、

前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定されることを特徴とする回路装置。

【請求項2】

請求項1において、

前記バッファー回路は、

前記プリバッファーの出力ノードと前記第2の出力バッファーの入力ノードとの間に設けられるスイッチ回路を含み、

前記スイッチ回路は、前記第1のモードではオフ状態に設定され、前記第2のモードではオン状態に設定されることを特徴とする回路装置。

【請求項3】

請求項1又は2において、

前記第1の出力バッファー、或いは前記第1の出力バッファー及び前記第2の出力バッファーが、クリップドサイン波の信号を出力するクリップドサイン波出力回路により構成されることを特徴とする回路装置。

【請求項4】

請求項3において、

前記クリップドサイン波出力回路は、

高電位側電源ノードと出力ノードとの間に設けられる第1のトランジスターと、

前記出力ノードと低電位側電源ノードとの間に設けられる第2のトランジスターと、

前記第1のトランジスターのゲートノードである第1のゲートノードに対してバイアス電圧を設定する第1のバイアス電圧設定回路と、

前記第2のトランジスターのゲートノードである第2のゲートノードに対してバイアス電圧を設定する第2のバイアス電圧設定回路と、

前記プリバッファーからの信号が入力される入力ノードと前記第1のゲートノードとの間に設けられる第1のキャパシターと、

前記入力ノードと前記第2のゲートノードとの間に設けられる第2のキャパシターと、 を含むことを特徴とする回路装置。

【請求項5】

請求項4において、

前記第1のバイアス電圧設定回路は、

前記高電位側電源ノードと前記第1のゲートノードとの間に直列に設けれる第1の抵抗素子及び第1のスイッチ素子と、

前記第1のゲートノードと前記低電位側電源ノードとの間に設けられる第2の抵抗素子を含み、

前記第2のバイアス電圧設定回路は、

前記高電位側電源ノードと前記第2のゲートノードとの間に直列に設けれる第3の抵抗素子及び第2のスイッチ素子と、

前記第2のゲートノードと前記低電位側電源ノードとの間に設けられる第4の抵抗素子及び第3のスイッチ素子を含み、

動作イネーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオン状態に設定され、前記第2のスイッチ素子がオフ状態に設定され、

動作ディスエーブル状態では、前記第1のスイッチ素子及び前記第3のスイッチ素子がオフ状態に設定され、前記第2のスイッチ素子がオン状態に設定されることを特徴とする回路装置。

【請求項6】

請求項4又は5において、

前記第1のキャパシター及び前記第2のキャパシターは、MIM(Metal-Insulator-Metal)構造のキャパシターにより構成され、

MIM構造の前記第1のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第1のゲートノードに接続され、

MIM構造の前記第2のキャパシターの上部電極が前記入力ノードに接続され、下部電極が前記第2のゲートノードに接続されることを特徴とする回路装置。

【請求項7】

請求項1又は2において、

前記第1の出力バッファーがクリップドサイン波の信号を出力するクリップドサイン波出力回路により構成され、前記第2の出力バッファーが、矩形波の信号を出力する矩形波出力回路により構成されることを特徴とする回路装置。

【請求項8】

請求項1乃至7のいずれかにおいて、

前記第1の出力バッファー及び前記第2の出力バッファーが動作ディスエーブル状態に設定された場合に、前記プリバッファーが動作ディスエーブル状態に設定されることを特徴とする回路装置。

【請求項9】

請求項1乃至8のいずれかにおいて、

前記バッファー回路は、

前記プリバッファーからの信号が入力され、第3の出力信号を出力する第3の出力バッファーを含み、

前記第1のモードでは、前記第1の出力バッファーが動作イネーブル状態に設定され、前記第2の出力バッファー及び前記第3の出力バッファーが動作ディスエーブル状態に設定され、

前記第2のモードでは、前記第1の出力バッファー及び前記第2の出力バッファーが動作イネーブル状態に設定され、前記第3の出力バッファーが動作ディスエーブル状態に設定され、

第3のモードでは、前記第1の出力バッファー、前記第2の出力バッファー及び前記第3の出力バッファーが動作イネーブル状態に設定され、

前記第1のモードでは、前記プリバッファーの駆動能力が、前記第2のモードに比べて低い駆動能力に設定され、

前記第2のモードでは、前記プリバッファーの駆動能力が、前記第3のモードに比べて低い駆動能力に設定されることを特徴とする回路装置。

【請求項10】

請求項1乃至9のいずれかにおいて、

回路装置の対向する第1の辺及び第2の辺の間の境界線により区分される一方の領域を第1の領域とし、他方の領域を第2の領域とした場合に、

前記振動子を接続するための第1の振動子用端子及び第2の振動子用端子が、前記第1の領域に配置され、

前記第1の出力バッファーからの前記第1の出力信号が出力される第1の出力端子と、前記第2の出力バッファーからの前記第2の出力信号が出力される第2の出力端子が、前記第2の領域に配置され、

前記発振回路及び前記バッファー回路が、前記第1の領域に配置されることを特徴とする回路装置。

【請求項11】

請求項10において、

回路装置の前記第1の辺及び前記第2の辺に交差する辺を第3の辺及び第4の辺とした場合に、

前記第1の振動子用端子は、前記第3の辺に沿った第1の端子配置領域に配置され、

前記第2の振動子用端子は、前記第4の辺に沿った第2の端子配置領域に配置され、

前記第1の出力端子は、前記第3の辺に沿った前記第1の端子配置領域に配置され、

前記第2の出力端子は、前記第4の辺に沿った前記第2の端子配置領域に配置されることを特徴とする回路装置。

【請求項12】

請求項11において、

前記第1の端子配置領域では、

前記第1の振動子用端子と前記第1の出力端子の間に、高電位側電源及び低電位側電源の一方の電源用の第1の電源端子が配置され、

前記第2の端子配置領域では、

前記第2の振動子用端子と前記第2の出力端子の間に、前記一方とは異なる他方の電源用の第2の電源端子が配置されることを特徴とする回路装置。

【請求項13】

請求項1乃至12のいずれかに記載の回路装置を含むことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−199631(P2012−199631A)

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願番号】特願2011−60824(P2011−60824)

【出願日】平成23年3月18日(2011.3.18)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願日】平成23年3月18日(2011.3.18)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]