固体撮像装置およびその製造方法

【課題】ランダムノイズを低減する。

【解決手段】固体撮像装置は、基板上に形成され、光電変換部(PD)と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の画素内トランジスタのうちの所定の画素内トランジスタの電極、具体的には、増幅トランジスタのゲート電極のみに接続されるコンタクトの基板に平行な面の形状は、略長方形または略楕円形に形成される。本技術は、CMOSイメージセンサに適用することができる。

【解決手段】固体撮像装置は、基板上に形成され、光電変換部(PD)と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の画素内トランジスタのうちの所定の画素内トランジスタの電極、具体的には、増幅トランジスタのゲート電極のみに接続されるコンタクトの基板に平行な面の形状は、略長方形または略楕円形に形成される。本技術は、CMOSイメージセンサに適用することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、固体撮像装置およびその製造方法に関し、特に、ランダムノイズを低減することができるようにする固体撮像装置およびその製造方法に関する。

【背景技術】

【0002】

近年、固体撮像装置において、画素サイズの縮小に伴い、ランダムノイズを低減することが難しくなってきた。

【0003】

ランダムノイズを低減するためには、増幅トランジスタにできるだけ多くの水素を供給して、ゲート酸化膜界面での電子トラップを少なくすることが行われる。

【0004】

例えば、半導体装置において、ホットキャリアの寿命を延ばすために、ゲート上にダミーコンタクトを設けることにより、水素供給を促進させるようにしたものがある(例えば、特許文献1参照)。

【0005】

一方、配線の自由度を低下させることなく、光の入射効率を向上させる目的で、画素内トランジスタ部分に、拡散層と画素内トランジスタのゲート電極とを接続するシェアードコンタクトを用いるようにした光電変換装置が提案されている(例えば、特許文献2参照)。

【0006】

また、コンタクトエッチングのストッパ用に窒化膜を形成し、コンタクト領域以外の窒化膜を除去することで、水素供給を促進するようにした固体撮像装置の製造方法が提案されている(例えば、特許文献3参照)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2002−343812号公報

【特許文献2】特開2008−210870号公報

【特許文献3】特開2004−165236号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献2の光電変換装置においては、シェアードコンタクトのコンタクトレイアウトは大きくなるものの、シェアードコンタクト下にサイドウォールが形成されているため、十分に水素供給を促進することができなかった。

【0009】

また、シェアードコンタクトを用いる場合、一般的に、コンタクトホール下の一部に絶縁膜として窒化膜が用いられるが、例えば、特許文献3に開示されているように、窒化膜は水素を通さない性質を有するので、窒化膜中の水素の拡散係数は低くなってしまう。

【0010】

一方、特許文献3の製造方法によれば、水素供給を促進することができるが、コンタクト領域以外の窒化膜を除去する必要があり、工数が増えてしまう。

【0011】

このように、固体撮像装置において、効率的に水素供給を促進させる構成については知られていなかった。

【0012】

本技術は、このような状況に鑑みてなされたものであり、ランダムノイズを低減することができるようにするものである。

【課題を解決するための手段】

【0013】

本技術の第1の側面の固体撮像装置は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される。

【0014】

前記所定の画素内トランジスタは、増幅トランジスタとすることができる。

【0015】

前記コンタクトは、前記所定の画素内トランジスタのゲート電極のみに接続されるようにすることができる。

【0016】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタの前記ゲート電極の側壁に形成されるサイドウォールに接しているようにすることができる。

【0017】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタを電気的に分離する領域に接しているようにすることができる。

【0018】

前記コンタクトの前記基板に平行な面の形状において、略長方形または略楕円形の長手方向は、複数の前記画素の前記光電変換部の間に形成される素子領域の延伸方向と同一であるようにすることができる。

【0019】

複数の前記画素内トランジスタのうちの他の画素内トランジスタの電極に接続されるコンタクトの前記基板に平行な面の形状は略正方形であり、前記所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、短辺の長さが前記正方形の1辺の長さに等しい略長方形か、または、短軸の長さが前記正方形の1辺の長さに等しい略楕円形であるようにすることができる。

【0020】

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成されるようにすることができる。

【0021】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられるようにすることができる。

【0022】

前記ダミーコンタクトは、金属配線に接続されているようにすることができる。

【0023】

前記金属配線には、0または負のバイアスが印加されるようにすることができる。

【0024】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成されるようにすることができる。

【0025】

本技術の第1の側面の固体撮像装置の製造方法は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状を、略長方形または略楕円形に形成する形成ステップを含む。

【0026】

本技術の第2の側面の固体撮像装置は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される。

【0027】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられるようにすることができる。

【0028】

前記ダミーコンタクトは、金属配線に接続されているようにすることができる。

【0029】

前記金属配線には、0または負のバイアスが印加されるようにすることができる。

【0030】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成されるようにすることができる。

【0031】

本技術の第2の側面の固体撮像装置の製造方法は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトを形成する形成ステップを含む。

【0032】

本技術の第1の側面においては、複数の画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの基板に平行な面の形状は、略長方形または略楕円形に形成される。

【0033】

本技術の第2の側面においては、複数の画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される。

【発明の効果】

【0034】

本技術の第1および第2の側面によれば、ランダムノイズを低減することが可能となる。

【図面の簡単な説明】

【0035】

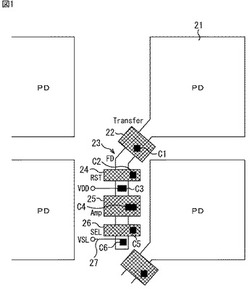

【図1】本技術を適用したCMOSイメージセンサの構成例を示す平面図である。

【図2】CMOSイメージセンサの第1の実施の形態の構成例を示す図である。

【図3】CMOSイメージセンサの第1の実施の形態の構成例を示す図である。

【図4】コンタクトの形状について説明する図である。

【図5】CMOSイメージセンサの第2の実施の形態の構成例を示す図である。

【図6】CMOSイメージセンサの第3の実施の形態の構成例を示す図である。

【図7】CMOSイメージセンサの第4の実施の形態の構成例を示す図である。

【図8】CMOSイメージセンサの第5の実施の形態の構成例を示す平面図である。

【図9】CMOSイメージセンサの製造処理について説明するフローチャートである。

【図10】CMOSイメージセンサの製造処理について説明するフローチャートである。

【図11】CMOSイメージセンサの製造処理について説明するフローチャートである。

【図12】CMOSイメージセンサの製造工程を示す図である。

【図13】CMOSイメージセンサの製造工程を示す図である。

【図14】CMOSイメージセンサの製造工程を示す図である。

【図15】CMOSイメージセンサの製造工程を示す図である。

【図16】CMOSイメージセンサの製造工程を示す図である。

【図17】CMOSイメージセンサの製造工程を示す図である。

【図18】CMOSイメージセンサの製造工程を示す図である。

【図19】CMOSイメージセンサの製造工程を示す図である。

【図20】CMOSイメージセンサの製造工程を示す図である。

【図21】CMOSイメージセンサの製造工程を示す図である。

【図22】CMOSイメージセンサの製造工程を示す図である。

【図23】CMOSイメージセンサの製造工程を示す図である。

【図24】CMOSイメージセンサの製造工程を示す図である。

【図25】CMOSイメージセンサの製造工程を示す図である。

【図26】CMOSイメージセンサの製造工程を示す図である。

【図27】CMOSイメージセンサの製造工程を示す図である。

【図28】CMOSイメージセンサの製造工程を示す図である。

【図29】CMOSイメージセンサの製造工程を示す図である。

【図30】CMOSイメージセンサの製造工程を示す図である。

【図31】CMOSイメージセンサの製造工程を示す図である。

【図32】CMOSイメージセンサの製造工程を示す図である。

【発明を実施するための形態】

【0036】

以下、本技術の実施の形態について図を参照して説明する。なお、説明は以下の順序で行う。

1.CMOSイメージセンサの構成例

2.第1の実施の形態

3.第2の実施の形態

4.第3の実施の形態

5.第4の実施の形態

6.第5の実施の形態

7.CMOSイメージセンサの製造工程

【0037】

<1.CMOSイメージセンサの構成例>

図1は、本技術を適用した固体撮像装置としてのCMOS(Complementary Metal Oxide Semiconductor)イメージセンサの構成例を示す平面図である。

【0038】

図1のCMOSイメージセンサは、入射光量に応じた電荷量の光電荷を発生して内部に蓄積する光電変換素子(光電変換部)と複数の画素内トランジスタを有する単位画素が行列状に2次元配列された画素アレイを備えている。

【0039】

図1のCMOSイメージセンサにおいて、単位画素(以下、単に、画素ともいう)は、PD(Photo Diode)21、転送トランジスタ22、FD(Floating Diffusion)23、リセットトランジスタ24、増幅トランジスタ25、選択トランジスタ26、および垂直信号線27から構成される。

【0040】

ここで、単位画素は、転送トランジスタ22、リセットトランジスタ24、増幅トランジスタ25、および選択トランジスタ26の4つのトランジスタ(以下、画素内トランジスタともいう)を備える構成としたが、3つの画素内トランジスタを備える構成としてもよいし、また、FD23や画素内トランジスタを、複数のPD21で共有する構成としてもよい。

【0041】

なお、図1における転送トランジスタ22、リセットトランジスタ24、増幅トランジスタ25、および選択トランジスタ26(画素内トランジスタ)は、実際には、ポリシリコンからなる、それぞれの画素内トランジスタのゲート電極を示しているが、必要に応じて、画素内トランジスタ自体を示すこととする。

【0042】

PD21は、被写体からの光を受光し、電荷を蓄積する。PD21に蓄積された電荷は、PD21に接続されている転送トランジスタ22に転送パルス(電圧)が印加されると、転送トランジスタ22を介してFD23に転送されて電圧に変換される。

【0043】

また、垂直信号線27に接続されている選択トランジスタ26に選択パルス(電圧)が印加されると、FD23の電圧が信号レベルとして、増幅トランジスタ25、選択トランジスタ26、および垂直信号線27を介して読み出される。

【0044】

さらに、その後、選択パルスが印加されたままの状態で、リセットトランジスタ24にリセットパルス(電圧)が印加されると、FD23の電圧が所定電圧にリセットされる。そして、リセット後のFD23の電圧がリセットレベルとして、増幅トランジスタ25から垂直信号線を介して読み出される。

【0045】

また、図1の単位画素には、画素内トランジスタの電極に電圧を印加するためのコンタクトC1乃至C6が設けられている。具体的には、コンタクトC1は、転送トランジスタ21のゲート電極に接続され、コンタクトC2は、リセットトランジスタ24のゲート電極に接続されている。また、コンタクトC3は、増幅トランジスタ25のドレイン電極に接続され、コンタクトC4は、増幅トランジスタ25のゲート電極に接続されている。なお、コンタクトC3は、増幅トランジスタ25のドレイン電極と電源VDDとを接続している。そして、コンタクトC5は、選択トランジスタ26のゲート電極に接続され、コンタクトC6は、選択トランジスタ26のソース電極に接続されている。なお、コンタクトC6は、選択トランジスタ26のソース電極と垂直信号線27とを接続している。

【0046】

ここで、図1の単位画素において、画素内トランジスタ(転送トランジスタ22、リセットトランジスタ24、増幅トランジスタ25、および選択トランジスタ26)に接続されるコンタクトについて、その断面(基板に対して平行な面)の形状は、略長方形または略楕円形に形成されているものとする。図1においては、コンタクトC3およびコンタクトC4の断面の形状が、略長方形または略楕円形に形成されている。なお、他のコンタクト(コンタクトC1,C2,C4,C5)の断面の形状は、正方形に形成されている。なお、コンタクトC1乃至C6は、いずれも画素内トランジスタの電極のみに接続されるものであり、いわゆるシェアードコンタクトのように、電極と拡散層(例えばFD23等)の両方に接続されるものではない。

【0047】

このように、コンタクトの断面の形状を略長方形または略楕円形に形成することで、その断面積を大きくすることができるので、コンタクト抵抗を下げることができる。

【0048】

また、CMOSイメージセンサにおいては、特に、増幅トランジスタ25がランダムノイズに大きく影響するため、図1のように、増幅トランジスタ25の電極に接続されるコンタクトの断面の形状を略長方形または略楕円形に形成することで、水素供給を促進させることができ、ランダムノイズを低減することができるようになる。

【0049】

さらに、画素内トランジスタのゲート電極部分や拡散層には、金属による白傷を抑えるために、サリサイド技術を用いないようにする。

【0050】

通常のコンタクトについて、サリサイド技術を用いた場合には、コンタクト抵抗はほとんど無視できるが、シリサイドがない場合には、オン電流に影響しそのコンタクト抵抗は大きくなる。例えば、90nmノードでは、シリサイドがない場合のコンタクト抵抗は、500Ω/個程度となる。一方、図1において、例えば増幅トランジスタ25のゲート長を0.5μm、ゲート幅を0.3μmとして、動作電圧を2.7Vとした場合のオン抵抗は、12kΩ程度となる。このように、オン抵抗に対して4,5%程度、コンタクト抵抗がオン抵抗に影響を及ぼす恐れがある。

【0051】

そこで、サリサイド技術を用いなくとも、コンタクトの断面の形状を略長方形または略楕円形に形成することで、その断面積を大きくすることができ、トランジスタの特性に対するコンタクト抵抗の影響を小さくすることが可能となる。

【0052】

また、PD21には十分に光を入射させる必要がある一方で、画素内トランジスタは遮光する必要があるが、コンタクトの断面の形状を略長方形または略楕円形に形成し、チャネル上に設けることで、画素内トランジスタの遮光を強化することができるようになる。

【0053】

さらに、コンタクトの断面の形状を略長方形または略楕円形に形成することで、その断面積を大きくすることができ、コンタクトがゲート電極に電気的に接続されない不良、いわゆるオープン不良を低減することができ、歩留りを上げることが可能となる。

【0054】

<2.第1の実施の形態>

[断面図1]

図2は、CMOSイメージセンサの第1の実施の形態の構成例を示す第1の図である。図2の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図2の下段には、図2の上段における直線L1での増幅トランジスタ25部分の断面図が示されている。

【0055】

図2の下段に示されるように、増幅トランジスタ25部分においては、基板を構成するP型層51およびN型層52の上に、増幅トランジスタ25の電極(ゲート電極)としてのポリシリコン53が形成されている。また、基板およびポリシリコン53の表面には、窒化膜(SiN)54が形成されているが、コンタクトが形成される部分のみ開口されている。また、窒化膜54の表面であって、ゲート電極としてのポリシリコン53の側壁には、側壁酸化膜(サイドウォール)55が形成されている。

【0056】

図2の断面図において、コンタクト(コンタクトC3,C4)は、バリアメタル膜56およびタングステン(W)57により構成されており、その上側には、CuやAlからなる配線58が設けられている。

【0057】

[断面図2]

図3は、CMOSイメージセンサの第1の実施の形態の構成例を示す第2の図である。図3の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図3の下段には、図3の上段における直線L2での増幅トランジスタ25部分(具体的には、コンタクトC3)の断面図が示されている。

【0058】

なお、図3下段の断面図において、図2下段の断面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0059】

酸化膜分離領域61は、画素内トランジスタを電気的に分離している。

【0060】

[コンタクトの基板に平行な面の形状]

ここで、図4を参照して、図2,3を参照して説明したコンタクトC3,C4の、基板に平行な面の形状の詳細について説明する。

【0061】

上述したように、コンタクトC3,C4の、基板に平行な面の形状は、図4Aに示されるような、4つの頂点が丸みを帯びた略長方形か、または、図4Bに示されるような、略楕円形に形成される。ここで、長方形の長辺の長さと短辺の長さとの比、および、楕円形の長軸の長さと短軸の長さとの比(以下、単に縦横比ともいう)は、1:1以外のいかなる比であってもよい。なお、基板上に形成されるコンタクトホールのレイアウトパターンは、実際には、4つの頂点を有する長方形とされる。

【0062】

また、コンタクトC3,C4以外のコンタクトの基板に平行な面の形状が、正方形である場合には、コンタクトC3,C4のコンタクトの基板に平行な面の形状を、短辺の長さが正方形の1辺の長さに等しい長方形か、または、短軸の長さが正方形の1辺の長さに等しい楕円形とするようにしてもよい。

【0063】

これにより、コンタクトC3,C4を形成する際、タングステン57を堆積させる条件を他のコンタクトと同一にしてもタングステン埋め込みが容易であり、製造工程数の増加を避けることができる。

【0064】

<3.第2の実施の形態>

図5は、CMOSイメージセンサの第2の実施の形態の構成例を示す図である。図5の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図5の下段には、図5の上段における直線L3での増幅トランジスタ25部分の断面図が示されている。

【0065】

なお、図5下段の断面図において、図2下段の断面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0066】

ただし、図5の構成において、図2の構成と異なるのは、コンタクトC4の基板側の一部(図5下段右側のバリアメタル膜56およびタングステン57)が、サイドウォール55の一部に接している点である。具体的には、図5の構成においては、窒化膜54をポリシリコン53表面全体で開口されるようにし、ポリシリコン53(ゲート電極)−コンタクト(バリアメタル膜56およびタングステン57)間のアライメントや線幅のばらつきを考慮して、コンタクトをサイドウォール55にかかるようにしている。

【0067】

これにより、図2の構成と比較して、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。また、チャネル上においては、画素内トランジスタの遮光をより強化することができるので、光によるトランジスタの特性のばらつきを抑えることができるようになる。

【0068】

<4.第3の実施の形態>

図6は、CMOSイメージセンサの第3の実施の形態の構成例を示す図である。図6の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図6の下段には、図6の上段における直線L4での増幅トランジスタ25部分(具体的には、コンタクトC3)の断面図が示されている。

【0069】

なお、図6下段の断面図において、図3下段の断面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0070】

ただし、図6の構成において、図3の構成と異なるのは、コンタクトC3の基板側の一部(図6下段のバリアメタル膜56およびタングステン57)が、酸化膜分離領域61の一部に接している点である。

【0071】

これにより、図3の構成と比較して、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。また、コンタクト抵抗を下げることができるとともに、チャネル上においては、画素内トランジスタの遮光をより強化することができるので、光によるトランジスタの特性のばらつきを抑えることができるようになる。なお、第2の実施の形態のコンタクトC4と、本実施の形態のコンタクトC3とを組み合わせることにより、水素供給の促進をより強化するとともに、画素内トランジスタの遮光特性をより強化することができるのは明らかである。

【0072】

<5.第4の実施の形態>

図7は、CMOSイメージセンサの第4の実施の形態の構成例を示す図である。図7Aには、図1の増幅トランジスタ25部分の拡大図が示されている。

【0073】

本実施の形態においては、図7Aに示されるように、コンタクトC4の基板に平行な面の形状において、略長方形または略楕円形の長手方向を、CMOSイメージセンサにおいて画素アレイを構成する複数の画素のPD21の間に形成される素子領域(アクティブともいう)の延伸方向(図中、上下方向)と同一とする。

【0074】

水素供給は、PD21にとって必ずしもよい影響を与えない。結晶欠陥が多く存在する場合には、ダングリングボンドを水素で終端することにより、白傷を抑制することができるが、結晶欠陥が十分少ない場合には、図7Bに示されるように、PD21の表面を形成するP型層(+P)のボロンを不活性化させ、逆に白傷を増やしてしまう恐れがある。

【0075】

そこで、図7Aに示されるような構成をとることで、増幅トランジスタ25に対しては、十分に水素を供給するとともに、PD21に対しては、できるだけ水素を供給しないようにすることができる。これにより、水素供給による白傷の悪化を抑制することができるようになる。

【0076】

<6.第5の実施の形態>

図8は、CMOSイメージセンサの第5の実施の形態の構成例を示す平面図である。

【0077】

なお、図8の平面図において、図1の平面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0078】

すなわち、図8の平面図において、図1の平面図と異なるのは、ダミーコンタクトC11乃至C14およびポリシリコン81を設けた点である。

【0079】

ダミーコンタクトC11乃至C14は、電気的な接続を目的としないコンタクトである。特に、ダミーコンタクトC14は、電気的な接続を目的としない電極としてのポリシリコン81に接続されている。

【0080】

このように、ダミーコンタクトC11乃至C14を設けることによって、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。特に、ダミーコンタクトC11乃至C14を、増幅トランジスタ25の近傍に設けることによって、より確実に増幅トランジスタ25への水素供給を促進させることが可能となる。

【0081】

また、ダミーコンタクトC14のように、画素内トランジスタのゲート電極上に設けるようにしてもよい。これにより、酸化膜分離領域の厚みが薄い場合に、基板とダミーコンタクトC14とがショートしてしまうのを防ぐことができる。

【0082】

さらに、ダミーコンタクトC11乃至C14に金属配線を接続し、その金属配線には、0または負のバイアスを印加するようにしてもよい。これにより、基板に対して電気的に不安定な状態を引き起こすことを避けることが可能となる。また、正のバイアスを印加した場合、ダミーコンタクトC11乃至C14下に電子が誘起され白傷が発生する恐れがあるが、0または負のバイアスを印加することによって、白傷の発生を抑制することができる。

【0083】

なお、上述したダミーコンタクトC11乃至C14は、図2乃至図8を参照して説明した第1乃至第4の実施の形態の構成に設けるようにしてもよく、また、ダミーコンタクトC11乃至C14の断面(基板に平行な面)の形状を略長方形または略楕円形に形成するようにしてもよい。これにより、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。

【0084】

<7.CMOSイメージセンサの製造工程>

次に、図9乃至図11のフローチャートを参照して、上述したCMOSイメージセンサの製造処理について説明する。

【0085】

ステップS11において、熱酸化により、Si基板表面を保護するためのパッド酸化膜を形成し、窒化膜を堆積させる。

【0086】

具体的には、まず、図12Aに示されるように、Si基板111表面に、例えば、厚さ約15nmのパッド酸化膜112を形成する。次に、LPCVD(Low Pressure Chemical Vapor Deposition)により、例えば、厚さ160nmの窒化膜113を堆積させる。なお、この例では、窒化膜およびパッド酸化膜の構造を形成するようにしたが、窒化膜およびポリシリコンの構造や、aシリコン(アモルファスシリコン)およびパッド酸化膜の構造を形成するようにしてもよい。

【0087】

ステップS12において、リソグラフィを行い、図12Bに示されるように、窒化膜113およびパッド酸化膜112を加工する。ここで、エッチング装置としては、RIE(Reactive Ion Etching)装置、または、ECR(Electron Cyclotron Resonance)装置等が用いられる。加工後、アッシング装置等により、レジスト除去を行う。

【0088】

ステップS13において、窒化膜マスクを用いて、トレンチエッチングを行う。エッチング装置としては、上述のRIE装置またはECR装置等が用いられる。これにより、図12Cに示されるように、トレンチ114が形成される。トレンチ114の深さは、約0.3μmとされる。その後、約800乃至900℃で、ライナー酸化膜用の熱酸化(ライナー酸化)を行う。ライナー酸化膜は、窒素を含んだ酸化膜、または、CVD酸化膜であってもよい。その膜厚は、約4乃至10nmとされる。

【0089】

ステップS14において、暗電流を抑制するために、リソグラフィを行い、画素部(PD部分)にボロン注入を行う。具体的には、10keV程度の加速エネルギーで、1e12乃至1e14cm-2のボロン(B)注入が行われる。画素内の素子分離領域周りのボロン濃度が高いほど、暗電流や寄生トランジスタの発生を抑制することができる。しかしながら、ボロン濃度が高すぎると、PDの面積が小さくなり、飽和電荷量Qsが小さくなってしまう。

【0090】

ステップS15において、図13Aに示されるように、トレンチ114(図12C)に、HDP(High Density Plasma)酸化膜116を堆積させる。HDP酸化膜116は、SOG(Spin On Glass)等の無機、または、有機酸化膜であってもよい。その後、CMP(Chemical Mechanical Polishing)を行う。CMPは窒化膜で止める。

【0091】

ステップS16において、Si基板表面からのトレンチ酸化膜の段差を調整するために、酸化膜にウェットエッチングを行う。酸化膜エッチの膜厚は、約40nm乃至100nmとされる。その後、ホットリン酸により、図13Bに示されるように、窒化膜113を除去する。

【0092】

ステップS17において、リソグラフィを行い、p-well注入とチャネル注入を行う。p-well注入としては、200keV程度の加速エネルギーで、約1e13cm-2のボロン(B)が注入される。チャネル注入としては、10keV乃至20keVの加速エネルギーで、約1e11乃至1e13cm-2のボロン(B)が注入される。レジスト除去後、リソグラフィを行い、n-well注入とチャネル注入を行う。n-well注入としては、200keV程度の加速エネルギーで、約1e13cm-2のリン(P)が注入される。チャネル注入としては、10keV乃至20keVの加速エネルギーで、約1e11乃至1e13cm-2のヒ素(As)が注入される。その後、レジストを除去する。このようにして、図14Aに示されるように、P型ウェル層とN型ウェル層とが形成される。

【0093】

ステップS18において、リソグラフィを行い、PD領域にイオン注入を行う。具体的には、PD領域の表面には、ボロン注入を行い、PD領域の深い領域には、AsまたはPを用いてN型層(N−)を形成する。その後、レジストを除去する。

【0094】

ステップS19において、パッド酸化膜をウェットエッチングにより除去し、図14Bに示される、高電圧用厚膜酸化膜121を形成する。高電圧用厚膜酸化膜121の膜厚は、電源電圧3.3V用トランジスタで約7.5nm、2.5V用トランジスタで約5.5nmとされる。

【0095】

ステップS20において、リソグラフィを行い、低電圧用トランジスタ領域に形成された厚膜酸化膜121を除去する。その後、レジスト除去を行い、図14Bに示される、薄膜酸化膜122を形成する。薄膜酸化膜122の膜厚は、1.0V用トランジスタで約1.2乃至1.8nmとされる。

【0096】

なお、ゲート酸化膜の材料は、熱酸化膜や、RTO(Rapid Thermal Oxidation)を用いた酸窒化膜であってもよい。また、ゲートリークを低減するために、ゲート酸化膜の材料は、Hf(ハフニウム)系やZr(ジルコニウム)系等の酸化膜を用いた高誘電体膜であってもよい。

【0097】

ステップS21において、LPCVDにより、ポリシリコンを堆積させる。

【0098】

図15は、CMOSイメージセンサの製造工程における画素領域および周辺(ロジック回路)領域の断面図を示している。

【0099】

図15の画素領域の断面図においては、N型基板上211上に形成されたP型ウェル層212に対して、P型層213−1を基板表面側に形成し、N型埋め込み層213−2を埋め込むことによってPDが形成される。その表面には、酸化膜214が形成され、素子分離領域215が設けられている。

【0100】

また、図15の周辺領域の断面図においては、N型基板上311上に形成されたP型ウェル層312の表面に、N型ウェル層313−1およびP型ウェル層313−2が形成され、その表面には、酸化膜314が形成され、素子分離領域315が設けられている。

【0101】

そして、ステップS21においては、図15の画素領域の断面図に示されるポリシリコン216、および、図15の周辺領域の断面図に示されるポリシリコン316が堆積される。

【0102】

ポリシリコン216およびポリシリコン316の膜厚は、例えば、90nmノードでは、約150乃至200nmとされる。また、この膜厚は、加工の制御性から、一般にゲートアスペクト比を大きくしないため、ノード毎に薄くなる傾向がある。また、ゲート空乏化(ゲート酸化膜の薄膜化に伴い、物理的なゲート酸化膜の膜厚だけでなく、ゲートポリシリコン内の空乏層の膜厚の影響が無視できなくなり、実効的なゲート膜厚が薄くならず、トランジスタの性能が低下してしまうこと)の対策として、ポリシリコンの代わりに、SiGeを含有したポリシリコンを用いるようにしてもよい。

【0103】

ステップS22において、リソグラフィを行い、ゲート空乏化対策として、図16に示されるように、NMOS領域にはPまたはAsを、また、図示はしないが、PMOS領域にはB、BF2、またはInを注入する。注入量は、それぞれ、約1e15乃至1e16cm-2とされる。また、不純物のゲート酸化膜直下の突き抜けを防ぐために、N2を合わせて注入するようにしてもよい。注入後、レジストRGを除去する。

【0104】

ステップS23において、図17Aに示されるように、ゲート加工時のマスクとなる絶縁膜401を堆積させる。マスク材料としては、酸化膜または窒化膜等が用いられ、その膜厚は、約10乃至100nmとされる。次に、リソグラフィを行い、RIE装置等を用いて、マスク用絶縁膜を加工する。その後、レジストRGを除去する。さらに、RIE装置等を用いて、ゲート加工を行う。加工後、例えばマスク材料が窒化膜である場合には、ウェットエッチングにより、マスク材料を除去する。これにより、図17Bに示されるように、ポリシリコンゲート411が形成される。

【0105】

ステップS24において、図18に示されるように、周辺領域に対して、PMOS領域にLDDイオン注入を行う。具体的には、リソグラフィを行い、ポケット注入およびLDDイオン注入を行う。PMOS領域へのポケット注入は、AsまたはPで、約1e12乃至1e14cm-2の注入濃度で行われる。また、エクステンション注入は、B、BF2、またはInで、約1e13乃至1e15cm-2の注入濃度で行われる。注入後、レジストRGを除去する。

【0106】

ステップS25において、図19に示されるように、周辺領域に対して、NMOS領域にLDDイオン注入を行う。具体的には、リソグラフィを行い、ポケット注入およびLDDイオン注入を行う。NMOS領域へのポケット注入は、B、BF2、またはInで、約1e12乃至1e14cm-2の注入濃度で行われる。また、LDDイオン注入は、AsまたはPで、約1e13乃至1e15cm-2の注入濃度で行われる。注入後、レジストRGを除去する。

【0107】

なお、ステップS24およびステップS25におけるポケット注入前に、注入のチャネリング抑制のために、Geを注入する等して、プリアモルファス化を行うようにしてもよい。また、エクステンション領域形成後、TED(Transient Enhanced Diffusion)等を引き起こす注入欠陥を小さくするために、800乃至900℃程度のRTA(Rapid Thermal Annealing)処理を行うようにしてもよい。

【0108】

ステップS26において、サイドウォールを形成する。具体的には、CVDによって、図20Aに示されるように、酸化膜421を10nm程度堆積させ、図20Bに示されるように、窒化膜422を50nm程度堆積させる。そして、RIE装置等を用いて、サイドウォールを形成する。サイドウォールの構造としては、SiO2およびSi3N4の2層構造ではなく、SiO2、Si3N4、およびSiO2の3層構造であってもよい。

【0109】

ステップS27において、リソグラフィを行い、図21に示されるように、周辺領域のサイドウォールを加工する。工数削減の観点から、リソグラフィを行わずに、画素領域のサイドウォールを加工するようにしてもよい。

【0110】

ステップS28において、サイドウォール膜(SW膜)として、図22に示されるように、例えば、酸化膜等の3層目の膜423を堆積させる。

【0111】

ステップS29において、図23に示されるように、3層目の膜423(SW膜)をエッチバックする。ここで、画素領域においては、エッチバックによるダメージを防ぐために窒化膜422でエッチバックを止める。これにより、暗電流を抑制することができる。

【0112】

ステップS30において、図24に示されるように、周辺領域に対して、PMOS領域にSD注入を行う。SD注入は、BまたはBF2で、約1e15乃至1e16cm-2の注入濃度で行われる。これにより、SD拡散層431が形成される。

【0113】

ステップS31において、図25に示されるように、周辺領域に対して、NMOS領域にSD注入を行う。SD注入は、AsまたはPで、約1e15乃至1e16cm-2の注入濃度で行われる。これにより、SD拡散層432が形成される。

【0114】

ステップS32において、図26に示されるように、画素領域に、窒化膜422および酸化膜421をスルーして、BまたはBF2を注入する。注入濃度は、約1e15乃至1e16cm-2とされる。これにより、拡散層433が形成される。

【0115】

ステップS33において、図27に示されるように、画素領域に、AsまたはPを注入する。注入濃度は、約1e15乃至1e16cm-2とされる。注入後、レジストを除去する。その後、RTA処理やSpike-RTA処理を行う装置を用いて、約800乃至1100℃で活性化アニールを行う。これにより、拡散層434が形成される。

【0116】

ステップS34において、図28に示されるように、周辺領域にシリサイド441を形成する。シリサイド441としては、CoSi2、NiSi、TiSi2、PtSi、WSi2等が用いられる。ここでは、NiSiを用いた場合について説明する。まず、スパッタリング装置を用いて、Niを約10nm堆積させる。次に、約300乃至400℃程度でアニールした後、Niをウェットエッチングする。これにより、絶縁膜以外のシリコンまたはポリシリコンの表面のみが、自己整合的にシリサイド形成される。その後、約500乃至600℃程度でアニールする。なお、画素領域は、SiNでシリサイドブロックすることで、シリサイドが形成されないようになされている。

【0117】

ステップS35において、図29に示されるように、SiN(層間絶縁膜442)を堆積させる。SiNとしては、LP-SiNまたはプラズマSiNが用いられる。層間絶縁膜442は、コンタクトエッチのオーバーエッチを最小限にする効果があり、エッチングダメージによる接合リークの増加を抑制することができる。コンタクトエッチにおいては、まず、層間絶縁膜442で止め、SiN上の酸化膜のばらつきを吸収する。次に、層間絶縁膜442をエッチングすることで、ゲート411および拡散層431乃至434の上側を開口する。層間絶縁膜442の膜厚は、10乃至100nmとされる。

【0118】

ステップS36において、図30に示されるように、酸化膜451をCVDによって堆積させる。酸化膜451としては、TEOS、PSG、BPSG、SOG等の膜が用いられ、その膜厚は、約100乃至1000nmとされる。その後、CMPを行い、平坦化させる。

【0119】

ステップS37において、リソグラフィを行い、RIE装置等を用いて、コンタクト部(コンタクトホール)を加工する。その後、レジストを除去する。

【0120】

ステップS38において、タングステン(W)のバリアメタル膜として、TiNまたはTiを、スパッタリングまたはCVDによって堆積させる。タングステン膜は、ストレスが大きく、シリコン酸化膜に直接堆積させると膜剥がれを引き起こす可能性があるため、図31に示されるように、バリアメタル膜452を堆積させる。その後、600℃程度でアニールを行う。

【0121】

ステップS39において、図31に示されるように、タングステン453をCVDによって堆積させる。タングステン453の堆積には、原料ガスとしてWF6を用い、還元剤としてH2またはSiH4を用いる。このとき、コンタクトホール内ではSiNが存在しないこと、および、タングステン453の堆積時にH2が用いられることにより、水素供給が容易となる。

【0122】

また、タングステン453の膜厚は、約100乃至500nmとされる。ここで、コンタクトのレイアウトパターン、言い換えると、コンタクトの基板に平行な面の形状を、略長方形または略楕円形に形成することにより、タングステン453の膜厚を薄くすることができ、コストを下げることができる。具体的には、コンタクトのレイアウトパターンの縦横比が1:1である場合、レイアウトパターンを大きくすると、その分を埋め込むための膜厚が大きくなってしまうが、レイアウトパターンを略長方形または略楕円形に形成することで、縦横比の小さい方の辺(または軸)の分の膜厚で、タングステン453を埋め込むことができる。

【0123】

ステップS40において、W(タングステン)のCMPを行い、コンタクトホールの内部のみにタングステンが埋め込まれるようにする。ここでは、CMPの代わりにエッチバックを行うようにしてもよい。

【0124】

ステップS41において、配線層を形成する。具体的には、Alをスパッタリングにより堆積させる。なお、材料としては、Alより低抵抗のCuを用いるようにしてもよい。次に、リソグラフィを行い、RIE装置等を用いて、配線を加工する。このようにして、図32に示される配線454が形成される。なお、配線層としては、1層に限らず、2層、3層、・・・と多層構造としてもよい。

【0125】

ステップS42において、プラズマ窒化膜を堆積させ、水素アニールを行うことにより水素を供給する。その後、パッド部(電極)をリソグラフィまたはエッチングにより開口する。また、PD上に、光を集光するためのレンズや導波路を形成してもよいし、光を分光するためのカラーフィルタを設けるようにしてもよい。

【0126】

以上の処理によれば、画素内トランジスタの電極に接続されるコンタクトの基板に平行な面の形状を、略長方形または略楕円形に形成することができる。したがって、CMOSイメージセンサにおいて、水素供給を促進させることができ、ランダムノイズを低減することができるようになる。

【0127】

なお、図8を参照して説明したダミーコンタクトを、上述したCMOSイメージセンサの製造処理におけるステップS37乃至ステップS40において形成するようにしてもよい。

【0128】

なお、本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

【0129】

さらに、本技術は以下のような構成をとることができる。

(1) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

固体撮像装置。

(2) 前記所定の画素内トランジスタは、増幅トランジスタである

(1)に記載の固体撮像装置。

(3) 前記コンタクトは、前記所定の画素内トランジスタのゲート電極に接続される

(1)または(2)に記載の固体撮像装置。

(4) 前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタの前記ゲート電極の側壁に形成されるサイドウォールに接している

(3)に記載の固体撮像装置。

(5) 前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタを電気的に分離する領域に接している

(1)または(2)に記載の固体撮像装置。

(6) 前記コンタクトの前記基板に平行な面の形状において、略長方形または略楕円形の長手方向は、複数の前記画素の前記光電変換部の間に形成される素子領域の延伸方向と同一である

(1)乃至(3)のいずれかに記載の固体撮像装置。

(7) 複数の前記画素内トランジスタのうちの他の画素内トランジスタの電極に接続されるコンタクトの前記基板に平行な面の形状は略正方形であり、

前記所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、短辺の長さが前記正方形の1辺の長さに等しい略長方形か、または、短軸の長さが前記正方形の1辺の長さに等しい略楕円形である

(1)乃至(3)のいずれかに記載の固体撮像装置。

(8) 複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

(1)乃至(7)のいずれかに記載の固体撮像装置。

(9) 前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

(8)に記載の固体撮像装置。

(10) 前記ダミーコンタクトは、金属配線に接続されている

(8)または(9)に記載の固体撮像装置。

(11) 前記金属配線には、0または負のバイアスが印加される

(10)に記載の固体撮像装置。

(12) 前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

(8)乃至(10)のいずれかに記載の固体撮像装置。

(13) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状を、略長方形または略楕円形に形成する形成ステップ

を含む固体撮像装置の製造方法。

(14) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

固体撮像装置。

(15) 前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

(14)に記載の固体撮像装置。

(16) 前記ダミーコンタクトは、金属配線に接続されている

(14)または(15)に記載の固体撮像装置。

(17) 前記金属配線には、0または負のバイアスが印加される

(16)に記載の固体撮像装置。

(18) 前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

(14)乃至(17)のいずれかに記載の固体撮像装置。

(19) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトを形成する形成ステップを

含む固体撮像装置の製造方法。

【符号の説明】

【0130】

21 PD, 22 転送トランジスタ, 24 リセットトランジスタ, 25 増幅トランジスタ, 26 選択トランジスタ, C1乃至C5 コンタクト, C11乃至C14 ダミーコンタクト

【技術分野】

【0001】

本技術は、固体撮像装置およびその製造方法に関し、特に、ランダムノイズを低減することができるようにする固体撮像装置およびその製造方法に関する。

【背景技術】

【0002】

近年、固体撮像装置において、画素サイズの縮小に伴い、ランダムノイズを低減することが難しくなってきた。

【0003】

ランダムノイズを低減するためには、増幅トランジスタにできるだけ多くの水素を供給して、ゲート酸化膜界面での電子トラップを少なくすることが行われる。

【0004】

例えば、半導体装置において、ホットキャリアの寿命を延ばすために、ゲート上にダミーコンタクトを設けることにより、水素供給を促進させるようにしたものがある(例えば、特許文献1参照)。

【0005】

一方、配線の自由度を低下させることなく、光の入射効率を向上させる目的で、画素内トランジスタ部分に、拡散層と画素内トランジスタのゲート電極とを接続するシェアードコンタクトを用いるようにした光電変換装置が提案されている(例えば、特許文献2参照)。

【0006】

また、コンタクトエッチングのストッパ用に窒化膜を形成し、コンタクト領域以外の窒化膜を除去することで、水素供給を促進するようにした固体撮像装置の製造方法が提案されている(例えば、特許文献3参照)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2002−343812号公報

【特許文献2】特開2008−210870号公報

【特許文献3】特開2004−165236号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献2の光電変換装置においては、シェアードコンタクトのコンタクトレイアウトは大きくなるものの、シェアードコンタクト下にサイドウォールが形成されているため、十分に水素供給を促進することができなかった。

【0009】

また、シェアードコンタクトを用いる場合、一般的に、コンタクトホール下の一部に絶縁膜として窒化膜が用いられるが、例えば、特許文献3に開示されているように、窒化膜は水素を通さない性質を有するので、窒化膜中の水素の拡散係数は低くなってしまう。

【0010】

一方、特許文献3の製造方法によれば、水素供給を促進することができるが、コンタクト領域以外の窒化膜を除去する必要があり、工数が増えてしまう。

【0011】

このように、固体撮像装置において、効率的に水素供給を促進させる構成については知られていなかった。

【0012】

本技術は、このような状況に鑑みてなされたものであり、ランダムノイズを低減することができるようにするものである。

【課題を解決するための手段】

【0013】

本技術の第1の側面の固体撮像装置は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される。

【0014】

前記所定の画素内トランジスタは、増幅トランジスタとすることができる。

【0015】

前記コンタクトは、前記所定の画素内トランジスタのゲート電極のみに接続されるようにすることができる。

【0016】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタの前記ゲート電極の側壁に形成されるサイドウォールに接しているようにすることができる。

【0017】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタを電気的に分離する領域に接しているようにすることができる。

【0018】

前記コンタクトの前記基板に平行な面の形状において、略長方形または略楕円形の長手方向は、複数の前記画素の前記光電変換部の間に形成される素子領域の延伸方向と同一であるようにすることができる。

【0019】

複数の前記画素内トランジスタのうちの他の画素内トランジスタの電極に接続されるコンタクトの前記基板に平行な面の形状は略正方形であり、前記所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、短辺の長さが前記正方形の1辺の長さに等しい略長方形か、または、短軸の長さが前記正方形の1辺の長さに等しい略楕円形であるようにすることができる。

【0020】

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成されるようにすることができる。

【0021】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられるようにすることができる。

【0022】

前記ダミーコンタクトは、金属配線に接続されているようにすることができる。

【0023】

前記金属配線には、0または負のバイアスが印加されるようにすることができる。

【0024】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成されるようにすることができる。

【0025】

本技術の第1の側面の固体撮像装置の製造方法は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状を、略長方形または略楕円形に形成する形成ステップを含む。

【0026】

本技術の第2の側面の固体撮像装置は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される。

【0027】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられるようにすることができる。

【0028】

前記ダミーコンタクトは、金属配線に接続されているようにすることができる。

【0029】

前記金属配線には、0または負のバイアスが印加されるようにすることができる。

【0030】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成されるようにすることができる。

【0031】

本技術の第2の側面の固体撮像装置の製造方法は、基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトを形成する形成ステップを含む。

【0032】

本技術の第1の側面においては、複数の画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの基板に平行な面の形状は、略長方形または略楕円形に形成される。

【0033】

本技術の第2の側面においては、複数の画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される。

【発明の効果】

【0034】

本技術の第1および第2の側面によれば、ランダムノイズを低減することが可能となる。

【図面の簡単な説明】

【0035】

【図1】本技術を適用したCMOSイメージセンサの構成例を示す平面図である。

【図2】CMOSイメージセンサの第1の実施の形態の構成例を示す図である。

【図3】CMOSイメージセンサの第1の実施の形態の構成例を示す図である。

【図4】コンタクトの形状について説明する図である。

【図5】CMOSイメージセンサの第2の実施の形態の構成例を示す図である。

【図6】CMOSイメージセンサの第3の実施の形態の構成例を示す図である。

【図7】CMOSイメージセンサの第4の実施の形態の構成例を示す図である。

【図8】CMOSイメージセンサの第5の実施の形態の構成例を示す平面図である。

【図9】CMOSイメージセンサの製造処理について説明するフローチャートである。

【図10】CMOSイメージセンサの製造処理について説明するフローチャートである。

【図11】CMOSイメージセンサの製造処理について説明するフローチャートである。

【図12】CMOSイメージセンサの製造工程を示す図である。

【図13】CMOSイメージセンサの製造工程を示す図である。

【図14】CMOSイメージセンサの製造工程を示す図である。

【図15】CMOSイメージセンサの製造工程を示す図である。

【図16】CMOSイメージセンサの製造工程を示す図である。

【図17】CMOSイメージセンサの製造工程を示す図である。

【図18】CMOSイメージセンサの製造工程を示す図である。

【図19】CMOSイメージセンサの製造工程を示す図である。

【図20】CMOSイメージセンサの製造工程を示す図である。

【図21】CMOSイメージセンサの製造工程を示す図である。

【図22】CMOSイメージセンサの製造工程を示す図である。

【図23】CMOSイメージセンサの製造工程を示す図である。

【図24】CMOSイメージセンサの製造工程を示す図である。

【図25】CMOSイメージセンサの製造工程を示す図である。

【図26】CMOSイメージセンサの製造工程を示す図である。

【図27】CMOSイメージセンサの製造工程を示す図である。

【図28】CMOSイメージセンサの製造工程を示す図である。

【図29】CMOSイメージセンサの製造工程を示す図である。

【図30】CMOSイメージセンサの製造工程を示す図である。

【図31】CMOSイメージセンサの製造工程を示す図である。

【図32】CMOSイメージセンサの製造工程を示す図である。

【発明を実施するための形態】

【0036】

以下、本技術の実施の形態について図を参照して説明する。なお、説明は以下の順序で行う。

1.CMOSイメージセンサの構成例

2.第1の実施の形態

3.第2の実施の形態

4.第3の実施の形態

5.第4の実施の形態

6.第5の実施の形態

7.CMOSイメージセンサの製造工程

【0037】

<1.CMOSイメージセンサの構成例>

図1は、本技術を適用した固体撮像装置としてのCMOS(Complementary Metal Oxide Semiconductor)イメージセンサの構成例を示す平面図である。

【0038】

図1のCMOSイメージセンサは、入射光量に応じた電荷量の光電荷を発生して内部に蓄積する光電変換素子(光電変換部)と複数の画素内トランジスタを有する単位画素が行列状に2次元配列された画素アレイを備えている。

【0039】

図1のCMOSイメージセンサにおいて、単位画素(以下、単に、画素ともいう)は、PD(Photo Diode)21、転送トランジスタ22、FD(Floating Diffusion)23、リセットトランジスタ24、増幅トランジスタ25、選択トランジスタ26、および垂直信号線27から構成される。

【0040】

ここで、単位画素は、転送トランジスタ22、リセットトランジスタ24、増幅トランジスタ25、および選択トランジスタ26の4つのトランジスタ(以下、画素内トランジスタともいう)を備える構成としたが、3つの画素内トランジスタを備える構成としてもよいし、また、FD23や画素内トランジスタを、複数のPD21で共有する構成としてもよい。

【0041】

なお、図1における転送トランジスタ22、リセットトランジスタ24、増幅トランジスタ25、および選択トランジスタ26(画素内トランジスタ)は、実際には、ポリシリコンからなる、それぞれの画素内トランジスタのゲート電極を示しているが、必要に応じて、画素内トランジスタ自体を示すこととする。

【0042】

PD21は、被写体からの光を受光し、電荷を蓄積する。PD21に蓄積された電荷は、PD21に接続されている転送トランジスタ22に転送パルス(電圧)が印加されると、転送トランジスタ22を介してFD23に転送されて電圧に変換される。

【0043】

また、垂直信号線27に接続されている選択トランジスタ26に選択パルス(電圧)が印加されると、FD23の電圧が信号レベルとして、増幅トランジスタ25、選択トランジスタ26、および垂直信号線27を介して読み出される。

【0044】

さらに、その後、選択パルスが印加されたままの状態で、リセットトランジスタ24にリセットパルス(電圧)が印加されると、FD23の電圧が所定電圧にリセットされる。そして、リセット後のFD23の電圧がリセットレベルとして、増幅トランジスタ25から垂直信号線を介して読み出される。

【0045】

また、図1の単位画素には、画素内トランジスタの電極に電圧を印加するためのコンタクトC1乃至C6が設けられている。具体的には、コンタクトC1は、転送トランジスタ21のゲート電極に接続され、コンタクトC2は、リセットトランジスタ24のゲート電極に接続されている。また、コンタクトC3は、増幅トランジスタ25のドレイン電極に接続され、コンタクトC4は、増幅トランジスタ25のゲート電極に接続されている。なお、コンタクトC3は、増幅トランジスタ25のドレイン電極と電源VDDとを接続している。そして、コンタクトC5は、選択トランジスタ26のゲート電極に接続され、コンタクトC6は、選択トランジスタ26のソース電極に接続されている。なお、コンタクトC6は、選択トランジスタ26のソース電極と垂直信号線27とを接続している。

【0046】

ここで、図1の単位画素において、画素内トランジスタ(転送トランジスタ22、リセットトランジスタ24、増幅トランジスタ25、および選択トランジスタ26)に接続されるコンタクトについて、その断面(基板に対して平行な面)の形状は、略長方形または略楕円形に形成されているものとする。図1においては、コンタクトC3およびコンタクトC4の断面の形状が、略長方形または略楕円形に形成されている。なお、他のコンタクト(コンタクトC1,C2,C4,C5)の断面の形状は、正方形に形成されている。なお、コンタクトC1乃至C6は、いずれも画素内トランジスタの電極のみに接続されるものであり、いわゆるシェアードコンタクトのように、電極と拡散層(例えばFD23等)の両方に接続されるものではない。

【0047】

このように、コンタクトの断面の形状を略長方形または略楕円形に形成することで、その断面積を大きくすることができるので、コンタクト抵抗を下げることができる。

【0048】

また、CMOSイメージセンサにおいては、特に、増幅トランジスタ25がランダムノイズに大きく影響するため、図1のように、増幅トランジスタ25の電極に接続されるコンタクトの断面の形状を略長方形または略楕円形に形成することで、水素供給を促進させることができ、ランダムノイズを低減することができるようになる。

【0049】

さらに、画素内トランジスタのゲート電極部分や拡散層には、金属による白傷を抑えるために、サリサイド技術を用いないようにする。

【0050】

通常のコンタクトについて、サリサイド技術を用いた場合には、コンタクト抵抗はほとんど無視できるが、シリサイドがない場合には、オン電流に影響しそのコンタクト抵抗は大きくなる。例えば、90nmノードでは、シリサイドがない場合のコンタクト抵抗は、500Ω/個程度となる。一方、図1において、例えば増幅トランジスタ25のゲート長を0.5μm、ゲート幅を0.3μmとして、動作電圧を2.7Vとした場合のオン抵抗は、12kΩ程度となる。このように、オン抵抗に対して4,5%程度、コンタクト抵抗がオン抵抗に影響を及ぼす恐れがある。

【0051】

そこで、サリサイド技術を用いなくとも、コンタクトの断面の形状を略長方形または略楕円形に形成することで、その断面積を大きくすることができ、トランジスタの特性に対するコンタクト抵抗の影響を小さくすることが可能となる。

【0052】

また、PD21には十分に光を入射させる必要がある一方で、画素内トランジスタは遮光する必要があるが、コンタクトの断面の形状を略長方形または略楕円形に形成し、チャネル上に設けることで、画素内トランジスタの遮光を強化することができるようになる。

【0053】

さらに、コンタクトの断面の形状を略長方形または略楕円形に形成することで、その断面積を大きくすることができ、コンタクトがゲート電極に電気的に接続されない不良、いわゆるオープン不良を低減することができ、歩留りを上げることが可能となる。

【0054】

<2.第1の実施の形態>

[断面図1]

図2は、CMOSイメージセンサの第1の実施の形態の構成例を示す第1の図である。図2の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図2の下段には、図2の上段における直線L1での増幅トランジスタ25部分の断面図が示されている。

【0055】

図2の下段に示されるように、増幅トランジスタ25部分においては、基板を構成するP型層51およびN型層52の上に、増幅トランジスタ25の電極(ゲート電極)としてのポリシリコン53が形成されている。また、基板およびポリシリコン53の表面には、窒化膜(SiN)54が形成されているが、コンタクトが形成される部分のみ開口されている。また、窒化膜54の表面であって、ゲート電極としてのポリシリコン53の側壁には、側壁酸化膜(サイドウォール)55が形成されている。

【0056】

図2の断面図において、コンタクト(コンタクトC3,C4)は、バリアメタル膜56およびタングステン(W)57により構成されており、その上側には、CuやAlからなる配線58が設けられている。

【0057】

[断面図2]

図3は、CMOSイメージセンサの第1の実施の形態の構成例を示す第2の図である。図3の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図3の下段には、図3の上段における直線L2での増幅トランジスタ25部分(具体的には、コンタクトC3)の断面図が示されている。

【0058】

なお、図3下段の断面図において、図2下段の断面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0059】

酸化膜分離領域61は、画素内トランジスタを電気的に分離している。

【0060】

[コンタクトの基板に平行な面の形状]

ここで、図4を参照して、図2,3を参照して説明したコンタクトC3,C4の、基板に平行な面の形状の詳細について説明する。

【0061】

上述したように、コンタクトC3,C4の、基板に平行な面の形状は、図4Aに示されるような、4つの頂点が丸みを帯びた略長方形か、または、図4Bに示されるような、略楕円形に形成される。ここで、長方形の長辺の長さと短辺の長さとの比、および、楕円形の長軸の長さと短軸の長さとの比(以下、単に縦横比ともいう)は、1:1以外のいかなる比であってもよい。なお、基板上に形成されるコンタクトホールのレイアウトパターンは、実際には、4つの頂点を有する長方形とされる。

【0062】

また、コンタクトC3,C4以外のコンタクトの基板に平行な面の形状が、正方形である場合には、コンタクトC3,C4のコンタクトの基板に平行な面の形状を、短辺の長さが正方形の1辺の長さに等しい長方形か、または、短軸の長さが正方形の1辺の長さに等しい楕円形とするようにしてもよい。

【0063】

これにより、コンタクトC3,C4を形成する際、タングステン57を堆積させる条件を他のコンタクトと同一にしてもタングステン埋め込みが容易であり、製造工程数の増加を避けることができる。

【0064】

<3.第2の実施の形態>

図5は、CMOSイメージセンサの第2の実施の形態の構成例を示す図である。図5の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図5の下段には、図5の上段における直線L3での増幅トランジスタ25部分の断面図が示されている。

【0065】

なお、図5下段の断面図において、図2下段の断面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0066】

ただし、図5の構成において、図2の構成と異なるのは、コンタクトC4の基板側の一部(図5下段右側のバリアメタル膜56およびタングステン57)が、サイドウォール55の一部に接している点である。具体的には、図5の構成においては、窒化膜54をポリシリコン53表面全体で開口されるようにし、ポリシリコン53(ゲート電極)−コンタクト(バリアメタル膜56およびタングステン57)間のアライメントや線幅のばらつきを考慮して、コンタクトをサイドウォール55にかかるようにしている。

【0067】

これにより、図2の構成と比較して、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。また、チャネル上においては、画素内トランジスタの遮光をより強化することができるので、光によるトランジスタの特性のばらつきを抑えることができるようになる。

【0068】

<4.第3の実施の形態>

図6は、CMOSイメージセンサの第3の実施の形態の構成例を示す図である。図6の上段には、図1の増幅トランジスタ25部分の拡大図が示されており、図6の下段には、図6の上段における直線L4での増幅トランジスタ25部分(具体的には、コンタクトC3)の断面図が示されている。

【0069】

なお、図6下段の断面図において、図3下段の断面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0070】

ただし、図6の構成において、図3の構成と異なるのは、コンタクトC3の基板側の一部(図6下段のバリアメタル膜56およびタングステン57)が、酸化膜分離領域61の一部に接している点である。

【0071】

これにより、図3の構成と比較して、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。また、コンタクト抵抗を下げることができるとともに、チャネル上においては、画素内トランジスタの遮光をより強化することができるので、光によるトランジスタの特性のばらつきを抑えることができるようになる。なお、第2の実施の形態のコンタクトC4と、本実施の形態のコンタクトC3とを組み合わせることにより、水素供給の促進をより強化するとともに、画素内トランジスタの遮光特性をより強化することができるのは明らかである。

【0072】

<5.第4の実施の形態>

図7は、CMOSイメージセンサの第4の実施の形態の構成例を示す図である。図7Aには、図1の増幅トランジスタ25部分の拡大図が示されている。

【0073】

本実施の形態においては、図7Aに示されるように、コンタクトC4の基板に平行な面の形状において、略長方形または略楕円形の長手方向を、CMOSイメージセンサにおいて画素アレイを構成する複数の画素のPD21の間に形成される素子領域(アクティブともいう)の延伸方向(図中、上下方向)と同一とする。

【0074】

水素供給は、PD21にとって必ずしもよい影響を与えない。結晶欠陥が多く存在する場合には、ダングリングボンドを水素で終端することにより、白傷を抑制することができるが、結晶欠陥が十分少ない場合には、図7Bに示されるように、PD21の表面を形成するP型層(+P)のボロンを不活性化させ、逆に白傷を増やしてしまう恐れがある。

【0075】

そこで、図7Aに示されるような構成をとることで、増幅トランジスタ25に対しては、十分に水素を供給するとともに、PD21に対しては、できるだけ水素を供給しないようにすることができる。これにより、水素供給による白傷の悪化を抑制することができるようになる。

【0076】

<6.第5の実施の形態>

図8は、CMOSイメージセンサの第5の実施の形態の構成例を示す平面図である。

【0077】

なお、図8の平面図において、図1の平面図と同様の構成については、同一名称および同一符号を付するものとし、その説明は、適宜省略するものとする。

【0078】

すなわち、図8の平面図において、図1の平面図と異なるのは、ダミーコンタクトC11乃至C14およびポリシリコン81を設けた点である。

【0079】

ダミーコンタクトC11乃至C14は、電気的な接続を目的としないコンタクトである。特に、ダミーコンタクトC14は、電気的な接続を目的としない電極としてのポリシリコン81に接続されている。

【0080】

このように、ダミーコンタクトC11乃至C14を設けることによって、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。特に、ダミーコンタクトC11乃至C14を、増幅トランジスタ25の近傍に設けることによって、より確実に増幅トランジスタ25への水素供給を促進させることが可能となる。

【0081】

また、ダミーコンタクトC14のように、画素内トランジスタのゲート電極上に設けるようにしてもよい。これにより、酸化膜分離領域の厚みが薄い場合に、基板とダミーコンタクトC14とがショートしてしまうのを防ぐことができる。

【0082】

さらに、ダミーコンタクトC11乃至C14に金属配線を接続し、その金属配線には、0または負のバイアスを印加するようにしてもよい。これにより、基板に対して電気的に不安定な状態を引き起こすことを避けることが可能となる。また、正のバイアスを印加した場合、ダミーコンタクトC11乃至C14下に電子が誘起され白傷が発生する恐れがあるが、0または負のバイアスを印加することによって、白傷の発生を抑制することができる。

【0083】

なお、上述したダミーコンタクトC11乃至C14は、図2乃至図8を参照して説明した第1乃至第4の実施の形態の構成に設けるようにしてもよく、また、ダミーコンタクトC11乃至C14の断面(基板に平行な面)の形状を略長方形または略楕円形に形成するようにしてもよい。これにより、より一層水素供給を促進させることができ、より効率的にランダムノイズを低減することができるようになる。

【0084】

<7.CMOSイメージセンサの製造工程>

次に、図9乃至図11のフローチャートを参照して、上述したCMOSイメージセンサの製造処理について説明する。

【0085】

ステップS11において、熱酸化により、Si基板表面を保護するためのパッド酸化膜を形成し、窒化膜を堆積させる。

【0086】

具体的には、まず、図12Aに示されるように、Si基板111表面に、例えば、厚さ約15nmのパッド酸化膜112を形成する。次に、LPCVD(Low Pressure Chemical Vapor Deposition)により、例えば、厚さ160nmの窒化膜113を堆積させる。なお、この例では、窒化膜およびパッド酸化膜の構造を形成するようにしたが、窒化膜およびポリシリコンの構造や、aシリコン(アモルファスシリコン)およびパッド酸化膜の構造を形成するようにしてもよい。

【0087】

ステップS12において、リソグラフィを行い、図12Bに示されるように、窒化膜113およびパッド酸化膜112を加工する。ここで、エッチング装置としては、RIE(Reactive Ion Etching)装置、または、ECR(Electron Cyclotron Resonance)装置等が用いられる。加工後、アッシング装置等により、レジスト除去を行う。

【0088】

ステップS13において、窒化膜マスクを用いて、トレンチエッチングを行う。エッチング装置としては、上述のRIE装置またはECR装置等が用いられる。これにより、図12Cに示されるように、トレンチ114が形成される。トレンチ114の深さは、約0.3μmとされる。その後、約800乃至900℃で、ライナー酸化膜用の熱酸化(ライナー酸化)を行う。ライナー酸化膜は、窒素を含んだ酸化膜、または、CVD酸化膜であってもよい。その膜厚は、約4乃至10nmとされる。

【0089】

ステップS14において、暗電流を抑制するために、リソグラフィを行い、画素部(PD部分)にボロン注入を行う。具体的には、10keV程度の加速エネルギーで、1e12乃至1e14cm-2のボロン(B)注入が行われる。画素内の素子分離領域周りのボロン濃度が高いほど、暗電流や寄生トランジスタの発生を抑制することができる。しかしながら、ボロン濃度が高すぎると、PDの面積が小さくなり、飽和電荷量Qsが小さくなってしまう。

【0090】

ステップS15において、図13Aに示されるように、トレンチ114(図12C)に、HDP(High Density Plasma)酸化膜116を堆積させる。HDP酸化膜116は、SOG(Spin On Glass)等の無機、または、有機酸化膜であってもよい。その後、CMP(Chemical Mechanical Polishing)を行う。CMPは窒化膜で止める。

【0091】

ステップS16において、Si基板表面からのトレンチ酸化膜の段差を調整するために、酸化膜にウェットエッチングを行う。酸化膜エッチの膜厚は、約40nm乃至100nmとされる。その後、ホットリン酸により、図13Bに示されるように、窒化膜113を除去する。

【0092】

ステップS17において、リソグラフィを行い、p-well注入とチャネル注入を行う。p-well注入としては、200keV程度の加速エネルギーで、約1e13cm-2のボロン(B)が注入される。チャネル注入としては、10keV乃至20keVの加速エネルギーで、約1e11乃至1e13cm-2のボロン(B)が注入される。レジスト除去後、リソグラフィを行い、n-well注入とチャネル注入を行う。n-well注入としては、200keV程度の加速エネルギーで、約1e13cm-2のリン(P)が注入される。チャネル注入としては、10keV乃至20keVの加速エネルギーで、約1e11乃至1e13cm-2のヒ素(As)が注入される。その後、レジストを除去する。このようにして、図14Aに示されるように、P型ウェル層とN型ウェル層とが形成される。

【0093】

ステップS18において、リソグラフィを行い、PD領域にイオン注入を行う。具体的には、PD領域の表面には、ボロン注入を行い、PD領域の深い領域には、AsまたはPを用いてN型層(N−)を形成する。その後、レジストを除去する。

【0094】

ステップS19において、パッド酸化膜をウェットエッチングにより除去し、図14Bに示される、高電圧用厚膜酸化膜121を形成する。高電圧用厚膜酸化膜121の膜厚は、電源電圧3.3V用トランジスタで約7.5nm、2.5V用トランジスタで約5.5nmとされる。

【0095】

ステップS20において、リソグラフィを行い、低電圧用トランジスタ領域に形成された厚膜酸化膜121を除去する。その後、レジスト除去を行い、図14Bに示される、薄膜酸化膜122を形成する。薄膜酸化膜122の膜厚は、1.0V用トランジスタで約1.2乃至1.8nmとされる。

【0096】

なお、ゲート酸化膜の材料は、熱酸化膜や、RTO(Rapid Thermal Oxidation)を用いた酸窒化膜であってもよい。また、ゲートリークを低減するために、ゲート酸化膜の材料は、Hf(ハフニウム)系やZr(ジルコニウム)系等の酸化膜を用いた高誘電体膜であってもよい。

【0097】

ステップS21において、LPCVDにより、ポリシリコンを堆積させる。

【0098】

図15は、CMOSイメージセンサの製造工程における画素領域および周辺(ロジック回路)領域の断面図を示している。

【0099】

図15の画素領域の断面図においては、N型基板上211上に形成されたP型ウェル層212に対して、P型層213−1を基板表面側に形成し、N型埋め込み層213−2を埋め込むことによってPDが形成される。その表面には、酸化膜214が形成され、素子分離領域215が設けられている。

【0100】

また、図15の周辺領域の断面図においては、N型基板上311上に形成されたP型ウェル層312の表面に、N型ウェル層313−1およびP型ウェル層313−2が形成され、その表面には、酸化膜314が形成され、素子分離領域315が設けられている。

【0101】

そして、ステップS21においては、図15の画素領域の断面図に示されるポリシリコン216、および、図15の周辺領域の断面図に示されるポリシリコン316が堆積される。

【0102】

ポリシリコン216およびポリシリコン316の膜厚は、例えば、90nmノードでは、約150乃至200nmとされる。また、この膜厚は、加工の制御性から、一般にゲートアスペクト比を大きくしないため、ノード毎に薄くなる傾向がある。また、ゲート空乏化(ゲート酸化膜の薄膜化に伴い、物理的なゲート酸化膜の膜厚だけでなく、ゲートポリシリコン内の空乏層の膜厚の影響が無視できなくなり、実効的なゲート膜厚が薄くならず、トランジスタの性能が低下してしまうこと)の対策として、ポリシリコンの代わりに、SiGeを含有したポリシリコンを用いるようにしてもよい。

【0103】

ステップS22において、リソグラフィを行い、ゲート空乏化対策として、図16に示されるように、NMOS領域にはPまたはAsを、また、図示はしないが、PMOS領域にはB、BF2、またはInを注入する。注入量は、それぞれ、約1e15乃至1e16cm-2とされる。また、不純物のゲート酸化膜直下の突き抜けを防ぐために、N2を合わせて注入するようにしてもよい。注入後、レジストRGを除去する。

【0104】

ステップS23において、図17Aに示されるように、ゲート加工時のマスクとなる絶縁膜401を堆積させる。マスク材料としては、酸化膜または窒化膜等が用いられ、その膜厚は、約10乃至100nmとされる。次に、リソグラフィを行い、RIE装置等を用いて、マスク用絶縁膜を加工する。その後、レジストRGを除去する。さらに、RIE装置等を用いて、ゲート加工を行う。加工後、例えばマスク材料が窒化膜である場合には、ウェットエッチングにより、マスク材料を除去する。これにより、図17Bに示されるように、ポリシリコンゲート411が形成される。

【0105】

ステップS24において、図18に示されるように、周辺領域に対して、PMOS領域にLDDイオン注入を行う。具体的には、リソグラフィを行い、ポケット注入およびLDDイオン注入を行う。PMOS領域へのポケット注入は、AsまたはPで、約1e12乃至1e14cm-2の注入濃度で行われる。また、エクステンション注入は、B、BF2、またはInで、約1e13乃至1e15cm-2の注入濃度で行われる。注入後、レジストRGを除去する。

【0106】

ステップS25において、図19に示されるように、周辺領域に対して、NMOS領域にLDDイオン注入を行う。具体的には、リソグラフィを行い、ポケット注入およびLDDイオン注入を行う。NMOS領域へのポケット注入は、B、BF2、またはInで、約1e12乃至1e14cm-2の注入濃度で行われる。また、LDDイオン注入は、AsまたはPで、約1e13乃至1e15cm-2の注入濃度で行われる。注入後、レジストRGを除去する。

【0107】

なお、ステップS24およびステップS25におけるポケット注入前に、注入のチャネリング抑制のために、Geを注入する等して、プリアモルファス化を行うようにしてもよい。また、エクステンション領域形成後、TED(Transient Enhanced Diffusion)等を引き起こす注入欠陥を小さくするために、800乃至900℃程度のRTA(Rapid Thermal Annealing)処理を行うようにしてもよい。

【0108】

ステップS26において、サイドウォールを形成する。具体的には、CVDによって、図20Aに示されるように、酸化膜421を10nm程度堆積させ、図20Bに示されるように、窒化膜422を50nm程度堆積させる。そして、RIE装置等を用いて、サイドウォールを形成する。サイドウォールの構造としては、SiO2およびSi3N4の2層構造ではなく、SiO2、Si3N4、およびSiO2の3層構造であってもよい。

【0109】

ステップS27において、リソグラフィを行い、図21に示されるように、周辺領域のサイドウォールを加工する。工数削減の観点から、リソグラフィを行わずに、画素領域のサイドウォールを加工するようにしてもよい。

【0110】

ステップS28において、サイドウォール膜(SW膜)として、図22に示されるように、例えば、酸化膜等の3層目の膜423を堆積させる。

【0111】

ステップS29において、図23に示されるように、3層目の膜423(SW膜)をエッチバックする。ここで、画素領域においては、エッチバックによるダメージを防ぐために窒化膜422でエッチバックを止める。これにより、暗電流を抑制することができる。

【0112】

ステップS30において、図24に示されるように、周辺領域に対して、PMOS領域にSD注入を行う。SD注入は、BまたはBF2で、約1e15乃至1e16cm-2の注入濃度で行われる。これにより、SD拡散層431が形成される。

【0113】

ステップS31において、図25に示されるように、周辺領域に対して、NMOS領域にSD注入を行う。SD注入は、AsまたはPで、約1e15乃至1e16cm-2の注入濃度で行われる。これにより、SD拡散層432が形成される。

【0114】

ステップS32において、図26に示されるように、画素領域に、窒化膜422および酸化膜421をスルーして、BまたはBF2を注入する。注入濃度は、約1e15乃至1e16cm-2とされる。これにより、拡散層433が形成される。

【0115】

ステップS33において、図27に示されるように、画素領域に、AsまたはPを注入する。注入濃度は、約1e15乃至1e16cm-2とされる。注入後、レジストを除去する。その後、RTA処理やSpike-RTA処理を行う装置を用いて、約800乃至1100℃で活性化アニールを行う。これにより、拡散層434が形成される。

【0116】

ステップS34において、図28に示されるように、周辺領域にシリサイド441を形成する。シリサイド441としては、CoSi2、NiSi、TiSi2、PtSi、WSi2等が用いられる。ここでは、NiSiを用いた場合について説明する。まず、スパッタリング装置を用いて、Niを約10nm堆積させる。次に、約300乃至400℃程度でアニールした後、Niをウェットエッチングする。これにより、絶縁膜以外のシリコンまたはポリシリコンの表面のみが、自己整合的にシリサイド形成される。その後、約500乃至600℃程度でアニールする。なお、画素領域は、SiNでシリサイドブロックすることで、シリサイドが形成されないようになされている。

【0117】

ステップS35において、図29に示されるように、SiN(層間絶縁膜442)を堆積させる。SiNとしては、LP-SiNまたはプラズマSiNが用いられる。層間絶縁膜442は、コンタクトエッチのオーバーエッチを最小限にする効果があり、エッチングダメージによる接合リークの増加を抑制することができる。コンタクトエッチにおいては、まず、層間絶縁膜442で止め、SiN上の酸化膜のばらつきを吸収する。次に、層間絶縁膜442をエッチングすることで、ゲート411および拡散層431乃至434の上側を開口する。層間絶縁膜442の膜厚は、10乃至100nmとされる。

【0118】

ステップS36において、図30に示されるように、酸化膜451をCVDによって堆積させる。酸化膜451としては、TEOS、PSG、BPSG、SOG等の膜が用いられ、その膜厚は、約100乃至1000nmとされる。その後、CMPを行い、平坦化させる。

【0119】

ステップS37において、リソグラフィを行い、RIE装置等を用いて、コンタクト部(コンタクトホール)を加工する。その後、レジストを除去する。

【0120】

ステップS38において、タングステン(W)のバリアメタル膜として、TiNまたはTiを、スパッタリングまたはCVDによって堆積させる。タングステン膜は、ストレスが大きく、シリコン酸化膜に直接堆積させると膜剥がれを引き起こす可能性があるため、図31に示されるように、バリアメタル膜452を堆積させる。その後、600℃程度でアニールを行う。

【0121】

ステップS39において、図31に示されるように、タングステン453をCVDによって堆積させる。タングステン453の堆積には、原料ガスとしてWF6を用い、還元剤としてH2またはSiH4を用いる。このとき、コンタクトホール内ではSiNが存在しないこと、および、タングステン453の堆積時にH2が用いられることにより、水素供給が容易となる。

【0122】

また、タングステン453の膜厚は、約100乃至500nmとされる。ここで、コンタクトのレイアウトパターン、言い換えると、コンタクトの基板に平行な面の形状を、略長方形または略楕円形に形成することにより、タングステン453の膜厚を薄くすることができ、コストを下げることができる。具体的には、コンタクトのレイアウトパターンの縦横比が1:1である場合、レイアウトパターンを大きくすると、その分を埋め込むための膜厚が大きくなってしまうが、レイアウトパターンを略長方形または略楕円形に形成することで、縦横比の小さい方の辺(または軸)の分の膜厚で、タングステン453を埋め込むことができる。

【0123】

ステップS40において、W(タングステン)のCMPを行い、コンタクトホールの内部のみにタングステンが埋め込まれるようにする。ここでは、CMPの代わりにエッチバックを行うようにしてもよい。

【0124】

ステップS41において、配線層を形成する。具体的には、Alをスパッタリングにより堆積させる。なお、材料としては、Alより低抵抗のCuを用いるようにしてもよい。次に、リソグラフィを行い、RIE装置等を用いて、配線を加工する。このようにして、図32に示される配線454が形成される。なお、配線層としては、1層に限らず、2層、3層、・・・と多層構造としてもよい。

【0125】

ステップS42において、プラズマ窒化膜を堆積させ、水素アニールを行うことにより水素を供給する。その後、パッド部(電極)をリソグラフィまたはエッチングにより開口する。また、PD上に、光を集光するためのレンズや導波路を形成してもよいし、光を分光するためのカラーフィルタを設けるようにしてもよい。

【0126】

以上の処理によれば、画素内トランジスタの電極に接続されるコンタクトの基板に平行な面の形状を、略長方形または略楕円形に形成することができる。したがって、CMOSイメージセンサにおいて、水素供給を促進させることができ、ランダムノイズを低減することができるようになる。

【0127】

なお、図8を参照して説明したダミーコンタクトを、上述したCMOSイメージセンサの製造処理におけるステップS37乃至ステップS40において形成するようにしてもよい。

【0128】

なお、本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

【0129】

さらに、本技術は以下のような構成をとることができる。

(1) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

固体撮像装置。

(2) 前記所定の画素内トランジスタは、増幅トランジスタである

(1)に記載の固体撮像装置。

(3) 前記コンタクトは、前記所定の画素内トランジスタのゲート電極に接続される

(1)または(2)に記載の固体撮像装置。

(4) 前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタの前記ゲート電極の側壁に形成されるサイドウォールに接している

(3)に記載の固体撮像装置。

(5) 前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタを電気的に分離する領域に接している

(1)または(2)に記載の固体撮像装置。

(6) 前記コンタクトの前記基板に平行な面の形状において、略長方形または略楕円形の長手方向は、複数の前記画素の前記光電変換部の間に形成される素子領域の延伸方向と同一である

(1)乃至(3)のいずれかに記載の固体撮像装置。

(7) 複数の前記画素内トランジスタのうちの他の画素内トランジスタの電極に接続されるコンタクトの前記基板に平行な面の形状は略正方形であり、

前記所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、短辺の長さが前記正方形の1辺の長さに等しい略長方形か、または、短軸の長さが前記正方形の1辺の長さに等しい略楕円形である

(1)乃至(3)のいずれかに記載の固体撮像装置。

(8) 複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

(1)乃至(7)のいずれかに記載の固体撮像装置。

(9) 前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

(8)に記載の固体撮像装置。

(10) 前記ダミーコンタクトは、金属配線に接続されている

(8)または(9)に記載の固体撮像装置。

(11) 前記金属配線には、0または負のバイアスが印加される

(10)に記載の固体撮像装置。

(12) 前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

(8)乃至(10)のいずれかに記載の固体撮像装置。

(13) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状を、略長方形または略楕円形に形成する形成ステップ

を含む固体撮像装置の製造方法。

(14) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

固体撮像装置。

(15) 前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

(14)に記載の固体撮像装置。

(16) 前記ダミーコンタクトは、金属配線に接続されている

(14)または(15)に記載の固体撮像装置。

(17) 前記金属配線には、0または負のバイアスが印加される

(16)に記載の固体撮像装置。

(18) 前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

(14)乃至(17)のいずれかに記載の固体撮像装置。

(19) 基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトを形成する形成ステップを

含む固体撮像装置の製造方法。

【符号の説明】

【0130】

21 PD, 22 転送トランジスタ, 24 リセットトランジスタ, 25 増幅トランジスタ, 26 選択トランジスタ, C1乃至C5 コンタクト, C11乃至C14 ダミーコンタクト

【特許請求の範囲】

【請求項1】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

固体撮像装置。

【請求項2】

前記所定の画素内トランジスタは、増幅トランジスタである

請求項1に記載の固体撮像装置。

【請求項3】

前記コンタクトは、前記所定の画素内トランジスタのゲート電極のみに接続される

請求項1に記載の固体撮像装置。

【請求項4】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタの前記ゲート電極の側壁に形成されるサイドウォールに接している

請求項3に記載の固体撮像装置。

【請求項5】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタを電気的に分離する領域に接している

請求項1に記載の固体撮像装置。

【請求項6】

前記コンタクトの前記基板に平行な面の形状において、略長方形または略楕円形の長手方向は、複数の前記画素の前記光電変換部の間に形成される素子領域の延伸方向と同一である

請求項1に記載の固体撮像装置。

【請求項7】

複数の前記画素内トランジスタのうちの他の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は略正方形であり、

前記所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、短辺の長さが前記正方形の1辺の長さに等しい略長方形か、または、短軸の長さが前記正方形の1辺の長さに等しい略楕円形である

請求項1に記載の固体撮像装置。

【請求項8】

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

請求項1に記載の固体撮像装置。

【請求項9】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

請求項8に記載の固体撮像装置。

【請求項10】

前記ダミーコンタクトは、金属配線に接続されている

請求項8に記載の固体撮像装置。

【請求項11】

前記金属配線には、0または負のバイアスが印加される

請求項10に記載の固体撮像装置。

【請求項12】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

請求項8に記載の固体撮像装置。

【請求項13】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状を、略長方形または略楕円形に形成する形成ステップ

を含む固体撮像装置の製造方法。

【請求項14】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

固体撮像装置。

【請求項15】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

請求項14に記載の固体撮像装置。

【請求項16】

前記ダミーコンタクトは、金属配線に接続されている

請求項14に記載の固体撮像装置。

【請求項17】

前記金属配線には、0または負のバイアスが印加される

請求項16に記載の固体撮像装置。

【請求項18】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

請求項14に記載の固体撮像装置。

【請求項19】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトを形成する形成ステップを

含む固体撮像装置の製造方法。

【請求項1】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

固体撮像装置。

【請求項2】

前記所定の画素内トランジスタは、増幅トランジスタである

請求項1に記載の固体撮像装置。

【請求項3】

前記コンタクトは、前記所定の画素内トランジスタのゲート電極のみに接続される

請求項1に記載の固体撮像装置。

【請求項4】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタの前記ゲート電極の側壁に形成されるサイドウォールに接している

請求項3に記載の固体撮像装置。

【請求項5】

前記コンタクトの前記基板側の少なくとも一部は、前記所定の画素内トランジスタを電気的に分離する領域に接している

請求項1に記載の固体撮像装置。

【請求項6】

前記コンタクトの前記基板に平行な面の形状において、略長方形または略楕円形の長手方向は、複数の前記画素の前記光電変換部の間に形成される素子領域の延伸方向と同一である

請求項1に記載の固体撮像装置。

【請求項7】

複数の前記画素内トランジスタのうちの他の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は略正方形であり、

前記所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状は、短辺の長さが前記正方形の1辺の長さに等しい略長方形か、または、短軸の長さが前記正方形の1辺の長さに等しい略楕円形である

請求項1に記載の固体撮像装置。

【請求項8】

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

請求項1に記載の固体撮像装置。

【請求項9】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

請求項8に記載の固体撮像装置。

【請求項10】

前記ダミーコンタクトは、金属配線に接続されている

請求項8に記載の固体撮像装置。

【請求項11】

前記金属配線には、0または負のバイアスが印加される

請求項10に記載の固体撮像装置。

【請求項12】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

請求項8に記載の固体撮像装置。

【請求項13】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタのうちの所定の画素内トランジスタの電極のみに接続されるコンタクトの前記基板に平行な面の形状を、略長方形または略楕円形に形成する形成ステップ

を含む固体撮像装置の製造方法。

【請求項14】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイ

を備え、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトが形成される

固体撮像装置。

【請求項15】

前記ダミーコンタクトは、前記画素内トランジスタのゲート電極上に設けられる

請求項14に記載の固体撮像装置。

【請求項16】

前記ダミーコンタクトは、金属配線に接続されている

請求項14に記載の固体撮像装置。

【請求項17】

前記金属配線には、0または負のバイアスが印加される

請求項16に記載の固体撮像装置。

【請求項18】

前記ダミーコンタクトの前記基板に平行な面の形状は、略長方形または略楕円形に形成される

請求項14に記載の固体撮像装置。

【請求項19】

基板上に形成され、光電変換部と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備える固体撮像装置の製造方法であって、

複数の前記画素内トランジスタの電極に接続されるコンタクト以外に、電気的に接続されないダミーコンタクトを形成する形成ステップを

含む固体撮像装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【公開番号】特開2013−89652(P2013−89652A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−226412(P2011−226412)

【出願日】平成23年10月14日(2011.10.14)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月14日(2011.10.14)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]