固体撮像装置および撮像装置

【課題】静止画撮影時間を短縮することができる固体撮像装置および撮像装置を提供する。

【解決手段】垂直走査回路1は、全画素の静止画用の露光期間が同一となるように画素の露光を制御し、全画素を複数に分割したフィールドの単位で静止画信号および動画信号の読み出しを制御する。さらに、垂直走査回路1は、1フィールドの静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において第1の出力部および第2の出力部の両方からフィールドの単位で静止画信号を読み出すよう静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において第1の出力部および第2の出力部の少なくとも一方からフィールドの単位で動画信号を読み出すよう動画信号の読み出しを制御する。

【解決手段】垂直走査回路1は、全画素の静止画用の露光期間が同一となるように画素の露光を制御し、全画素を複数に分割したフィールドの単位で静止画信号および動画信号の読み出しを制御する。さらに、垂直走査回路1は、1フィールドの静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において第1の出力部および第2の出力部の両方からフィールドの単位で静止画信号を読み出すよう静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において第1の出力部および第2の出力部の少なくとも一方からフィールドの単位で動画信号を読み出すよう動画信号の読み出しを制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デジタルスチルカメラ、デジタルビデオカメラなどに適用される固体撮像装置、およびその固体撮像装置を備えた撮像装置に関する。

【背景技術】

【0002】

近年、周辺回路をオンチップ化できるMOS型固体撮像素子の性能向上はめざましく、CCD型固体撮像素子に替わってMOS型固体撮像素子の普及が進んできている。MOS型撮像素子の撮像面には多数の画素が2次元状に配列されており、各画素は入射した光を信号電荷に変換して画素信号(画像信号)を生成する。MOS型固体撮像素子の駆動方法として、露光開始時刻および露光終了時刻が画素毎に異なるローリングシャッタ方式と、露光開始時刻および露光終了時刻が全画素で同一となるグローバルシャッタ方式とがある。

【0003】

グローバルシャッタ方式のMOS型固体撮像素子は、露光量に応じた信号電荷を発生するフォトダイオード等の光電変換部、光電変換部において発生した信号電荷を一時的に蓄積する電荷保持部(電荷蓄積部)、信号電荷の転送やリセットを行うためのスイッチ用途のトランジスタ等で構成される。

【0004】

図13は、グローバルシャッタ方式のMOS型固体撮像素子の撮像面に2次元状に配列される画素100の構成を示している。フォトダイオード(PD)101は、入射光を信号電荷に変換(光電変換)して蓄積する光電変換素子である。転送トランジスタ102は、フォトダイオード101で発生した信号電荷を電荷保持部(FD)103に転送するためのトランジスタである。電荷保持部103は、フォトダイオード101に蓄積された信号電荷を保持するためのフローティングディフュージョン(FD)である。FDリセットトランジスタ104は、電荷保持部103の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。

【0005】

増幅トランジスタ105は、電荷保持部103の電圧レベルを増幅して読み出すためのトランジスタである。選択トランジスタ106は、画素を選択し、垂直信号線114に増幅トランジスタ105の出力を伝えるためのトランジスタである。PDリセットトランジスタ107は、フォトダイオード101の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。フォトダイオード101以外は遮光されている。

【0006】

電源線110は、各画素に電源電圧VDDを供給するものであり、増幅トランジスタ105のドレイン端子、FDリセットトランジスタ104のドレイン端子、およびPDリセットトランジスタ107のドレイン端子に電気的に接続される。FDリセット線111は、1行分の画素の電荷保持部103をリセットするためのFDリセットパルスφRMi(iは行番号、以下同様)が印加される信号線であり、1行分の画素のFDリセットトランジスタ104のゲート端子に電気的に接続される。転送線112は、1行分の画素のフォトダイオード101で発生した信号電荷をそれぞれの画素の電荷保持部103に転送するための行転送パルスφTRiが印加される信号線であり、1行分の画素の転送トランジスタ102のゲート端子に電気的に接続される。

【0007】

PDリセット線115は、1行分の画素のフォトダイオード101をリセットするためのPDリセットパルスφRPDiが印加される信号線であり、1行分の画素のPDリセットトランジスタ107のゲート端子に電気的に接続される。選択線113は、1行分の画素を選択するための行選択パルスφSEiが印加される信号線であり、1行分の画素の選択トランジスタ106のゲート端子に電気的に接続される。このように5個のトランジスタを用いた画素構成により、光電変換機能、リセット機能、増幅読み出し機能、一時メモリ機能、及び選択機能を実現している。

【0008】

図14は、固体撮像素子の撮像面に、図13に示した画素を3行×3列に配列した構成を示している。図14において、画素部200は、画素100が3×3の2次元状に配列されて構成されている。画素100の構成は図13に示した通りである。

【0009】

垂直走査回路300は行単位で画素部200の駆動制御を行う。この駆動制御を行うために、垂直走査回路300は、行数と同じ数の単位回路301-1,301-2,301-3から構成されている。また、各単位回路は、制御部302-i,303-i,304-i,305-i(i=1,2,3)から構成されている。

【0010】

制御部302-i は、1行分の画素100の電荷保持部103をリセットするためのFDリセットパルスφRMi(i=1,2,3)を、FDリセット線111を介して行毎に独立して制御する。制御部303-i は、1行分の画素100の信号電荷をそれぞれの画素100の電荷保持部103 に転送するための行転送パルスφTRi(i=1,2,3)を、転送線112を介して行毎に独立して制御する。制御部304-i は、1行分の画素100のフォトダイオード101をリセットするためのPDリセットパルスφRPDi(i=1,2,3)を、PDリセット線115を介して行毎に独立して制御する。制御部305-i は、信号を読み出す1行分の画素100を選択するための行選択パルスφSEi(i=1,2,3)を、選択線113を介して行毎に独立して制御する。行選択パルスφSEiによって選択された行の画素100の信号は、列毎に設けられている垂直信号線114へ出力される。

【0011】

電流源150は、列毎に設けられており、垂直信号線114に接続され、画素100内の増幅トランジスタ105とソースフォロア回路を構成する。列処理回路350は、列毎に設けられており、垂直信号線114に出力される画素信号に対してクランプ動作や増幅動作を行う。水平読み出し回路400は、画素信号を読み出す画素列を選択して、その画素列に係る画素信号を出力端子410から出力する。AD(Analog to Digital)コンバータ500は、出力端子410から出力された画素信号をAD変換する。フレームメモリ600は、AD変換後の画素信号を保持する。差分回路700は、ADコンバータ500から出力された画素信号と、フレームメモリ600に保持されている画素信号との差分処理(減算処理)を行う。なお、電源電圧VDDを供給する電源線110は図14に示していない。

【0012】

図14に示したMOS型固体撮像素子を、デジタルカメラなどによる静止画の撮像に適用した場合にグローバルシャッタ方式で画素信号を読み出す動作を説明する。図15は、グローバルシャッタ方式による動作を示している。ただし、ここでは説明を簡単にするため、図14と同様に画素が3×3の2次元状に配置された固体撮像素子を用いて説明する。

【0013】

撮影開始を示す信号が入力されると、まず全行のPDリセットパルスφRPDiが“L”レベルから“H”レベルになることで全ての画素100のPDリセットトランジスタ107がオンになり、全ての画素100のフォトダイオード101がリセットされる。続いて、1行目のFDリセットパルスφRM1が“L”レベルから“H”レベルになることで1行目のFDリセットトランジスタ104がオンになり、1行目の電荷保持部103がリセットされる。

【0014】

続いて、1行目のFDリセットパルスφRM1が“H”レベルから“L”レベルになることでFDリセットトランジスタ104がオフになった後、1行目の行選択パルスφSE1が“L”レベルから“H”レベルになることで1行目の選択トランジスタ106がオンになり、1行目の電荷保持部103の電圧(リセットレベル)が、列処理回路350を介してリセット信号として水平読み出し回路400へ出力される。水平読み出し回路400はリセット信号を出力端子410から水平方向に順次出力する。

【0015】

出力された1行目の画素100のリセット信号はADコンバータ500によりAD変換されてフレームメモリ600に出力され、フレームメモリ600に保持される。2行目以降についても1行目と同様にリセット信号が読み出され、全ての画素100のリセット信号がフレームメモリ600に保持される。

【0016】

続いて、全行のPDリセットパルスφRPDiが“H”レベルから“L”レベルになることで全ての画素100のPDリセットトランジスタ107がオフになり、全ての画素100のフォトダイオード101が信号電荷の蓄積を開始する。これにより、全ての画素100の露光(電荷蓄積)が開始される。所望の蓄積時間が経過すると、全行の行転送パルスφTRiが“L”レベルから“H”レベルになることで全ての画素100の転送トランジスタ102がオンになり、全ての画素100のフォトダイオード101に蓄積された信号電荷が電荷保持部103に転送される。すなわち露光(電荷蓄積)が終了する。電荷蓄積開始から電荷蓄積終了までの期間が露光期間(蓄積期間)である。

【0017】

信号電荷の転送動作が終了した直後に、全行のPDリセットパルスφRPDiが“L”レベルから“H”レベルになることで全ての画素100のPDリセットトランジスタ107がオンになり、全ての画素100のフォトダイオード101がリセット状態となる。続いて、1行目の行選択パルスφSEiが“L”レベルから“H”レベルになることで1行目の選択トランジスタ106がオンになり、1行目の電荷保持部103の電圧(光信号レベル)が、列処理回路350を介して光信号として水平読み出し回路400へ出力される。水平読み出し回路400は光信号を出力端子410から水平方向に順次出力する。

【0018】

出力された1行目の画素100の光信号はADコンバータ500によりAD変換され、差分回路700へ出力される。差分回路700は、1行目の画素100の光信号と、フレームメモリ600に保持されている1行目の画素100のリセット信号との差分をとることにより、光信号成分のみを抽出し、撮像信号として後段の回路に出力する。この動作では、電荷保持部103のリセットノイズを除去することが可能であるので、高S/Nの信号を得ることができる。

【0019】

続いて、2行目以降についても1行目と同様な動作が行われ、全ての画素100の画素信号が読み出される。この信号は後段の画像処理回路(不図示)で処理され、静止画像が生成される。上述した動作により、全画素一括で露光および電荷の蓄積を行うグローバルシャッタ動作を実現することができる。このようなMOS型固体撮像素子についての技術が特許文献1に開示されている。

【0020】

一般的なデジタルカメラは、電源の投入後、フレーム単位で周期的に撮像を行って動画信号(動画像信号)を生成し、生成した動画信号に基づいてライブビュー画像(動画像)を表示部に表示する。ライブビュー画像の表示中にユーザが、静止画の取得指示である撮影指示を行うと、デジタルカメラは、動画信号の生成を停止し、撮像を行って静止画信号(静止画像信号)を生成し、生成した静止画信号を記録媒体に記録する。この静止画信号の生成時に、例えば上記のグローバルシャッタ動作が行われる。

【0021】

しかしながら、静止画の撮像時にはライブビュー画像の更新を行うことができないため、更新ができない期間に同一の画像が表示部に表示される、あるいは表示部がブラックアウトして画像が表示されないなどの現象が発生してしまう。また、上述したグローバルシャッタ動作においては、露光前のリセット信号用の読み出し動作と、露光後の光信号用の読み出し動作との両方が必要となるために、画素数の増加に応じて、1枚の静止画を撮影するために必要なシーケンス期間が長くなる。

【0022】

これらの問題を改善するために、固体撮像素子の画素を複数の画素群に分けると共に、静止画用と動画(ライブビュー)用の2つの出力系統を設け、静止画信号の読み出しに使用していない画素群を動画信号の読み出しに使用することにより、静止画信号の読み出しと動画信号の読み出しとを同時に行う方法が特許文献2(例えば、図18〜図21)に開示されている。

【先行技術文献】

【特許文献】

【0023】

【特許文献1】特開平11−261896号公報

【特許文献2】特開2010−183195号公報

【発明の概要】

【発明が解決しようとする課題】

【0024】

従来技術では、静止画の撮影中にライブビュー(動画)表示を行う場合に静止画信号と動画信号を同時に読み出すことで、ライブビュー画像の更新を行うことができない期間を短縮することが可能である。しかし、2つの出力系統の一方を静止画信号の読み出しに固定し、他方を動画信号の読み出しに固定しており、画素数の多い静止画信号の読み出しを、1つの出力系統のみを使用して行っているため、静止画撮影時間の短縮に限界があった。

【0025】

本発明は、上述した課題に鑑みてなされたものであって、静止画撮影時間を短縮することができる固体撮像装置および撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0026】

本発明は、上記の課題を解決するためになされたもので、光を信号電荷に変換し、信号電荷を蓄積する光電変換素子と、前記光電変換素子に蓄積された信号電荷を保持する電荷保持部と、前記光電変換素子に蓄積された信号電荷を前記電荷保持部に転送する転送部と、前記電荷保持部に保持された信号電荷に基づく画素信号を静止画信号または動画信号として出力する第1の出力部および第2の出力部とを備えた画素を2次元状に配列した画素部と、前記第1の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第1の処理部と、前記第2の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第2の処理部と、読み出し対象領域を構成する全画素の静止画用の露光期間が同一となるように前記画素の露光を制御し、前記読み出し対象領域を構成する全画素を複数に分割したフィールドの単位で前記静止画信号および前記動画信号の読み出しを制御し、さらに、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御する制御部と、を有することを特徴とする固体撮像装置である。

【0027】

また、本発明の固体撮像装置において、前記制御部は、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御することを特徴とする。

【0028】

また、本発明の固体撮像装置は、第1のモードおよび第2のモードの設定が可能な固体撮像装置であって、前記制御部は、前記第1のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の一方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の他方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御し、前記第2のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御することを特徴とする。

【0029】

また、本発明は、上記の固体撮像装置を備えた撮像装置である。

【発明の効果】

【0030】

本発明によれば、フィールド単位で静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において第1の出力部および第2の出力部の両方からフィールドの単位で静止画信号を読み出すよう静止画信号の読み出しを制御することによって、静止画撮影時間を短縮することができる。

【図面の簡単な説明】

【0031】

【図1】本発明の一実施形態による撮像装置の構成を示すブロック図である。

【図2】本発明の一実施形態による撮像装置が備える画素の構成を示す回路図である。

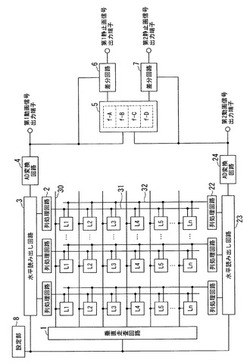

【図3】本発明の一実施形態による撮像装置が備える撮像部の構成を示すブロック図である。

【図4】本発明の一実施形態による撮像装置が備える撮像部のグローバルシャッタ動作を示すタイミングチャートである。

【図5】本発明の一実施形態による撮像装置が備える撮像部のグローバルシャッタ動作を示すタイミングチャートである。

【図6】本発明の一実施形態による撮像装置が備える画素をフィールドに分割した状態を示す参考図である。

【図7】本発明の一実施形態による撮像装置が備える撮像部のローリングシャッタ動作を示すタイミングチャートである。

【図8】本発明の一実施形態の動画表示動作時に画素信号を読み出す画素を示す参考図である。

【図9】本発明の一実施形態による撮像装置の動作を示すタイミングチャートである。

【図10】本発明の一実施形態による撮像装置が備える画素をフィールドに分割した状態を示す参考図である。

【図11】本発明の一実施形態による撮像装置の動作を示すタイミングチャートである。

【図12】本発明の一実施形態による撮像装置の動作を示すタイミングチャートである。

【図13】従来の画素の構成を示す回路図である。

【図14】従来の固体撮像装置の構成を示すブロック図である。

【図15】従来の固体撮像装置の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0032】

以下、図面を参照し、本発明の実施形態を説明する。図1は、本発明の一実施形態による撮像装置の構成を示している。図1に示す撮像装置は、レンズ201と、撮像部202と、画像処理部203と、表示部204と、駆動制御部205と、レンズ制御部206と、カメラ制御部207と、カメラ操作部208とを備えている。図1にはメモリカード209も示されているが、このメモリカード209を撮像装置に対して着脱可能に構成することによって、メモリカード209は撮像装置に固有の構成でなくても構わない。

【0033】

レンズ201は、固体撮像素子(固体撮像装置)を構成する撮像部202の撮像面に被写体の光学像を結像するための撮影レンズである。撮像部202は、レンズ201によって結像された被写体の光学像を光電変換によりデジタルの画像信号に変換して出力する。画像処理部203は、撮像部202から出力される画像信号に種々のデジタル的な画像処理を施す。この画像処理部203は、画像信号を記録用に処理する第1画像処理部203aと、画像信号を表示用に処理する第2画像処理部203bとを備えている。

【0034】

表示部204は、画像処理部203の第2画像処理部203bにより表示用に画像処理された画像信号に基づき画像を表示する。この表示部204は、静止画像を再生表示することができると共に、被撮像範囲の画像をリアルタイムに表示する動画(ライブビュー)表示を行うことができるようになっている。駆動制御部205は、カメラ制御部207からの指示に基づいて撮像部202の動作を制御する。レンズ制御部206は、カメラ制御部207からの指示に基づいて、レンズ201の絞りや焦点位置を制御する。

【0035】

カメラ制御部207は、撮像装置全体を制御する。カメラ操作部208は、ユーザが撮像装置に対する各種の操作入力を行うための操作用の各種部材を有し、操作入力の結果に基づく信号をカメラ制御部207へ出力する。カメラ操作部208の具体例として、撮像装置の電源をオン・オフするための電源スイッチ、静止画撮影を指示するためのレリーズボタン、静止画撮影モードを単写モードと連写モードの間で切り替えるための静止画撮影モードスイッチなどが挙げられる。メモリカード209は、第1画像処理部203aにより記録用に処理された画像信号を保存するための記録媒体である。

【0036】

次に、撮像部202の構成を説明する。図2は、撮像部202に用いられる画素の構成を示している。フォトダイオード(PD)10は、入射光を信号電荷に変換(光電変換)して蓄積する光電変換素子である。転送トランジスタ11(転送部)は、フォトダイオード101で発生した信号電荷を電荷保持部(FD)12に転送するためのトランジスタである。電荷保持部12は、フォトダイオード10に蓄積された信号電荷を保持するためのフローティングディフュージョン(FD)である。FDリセットトランジスタ13は、電荷保持部12の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。

【0037】

増幅トランジスタ14は、電荷保持部12の電圧レベルを増幅して読み出すためのトランジスタである。選択トランジスタ15,16(第1の出力部、第2の出力部)は、画素を選択し、垂直信号線31,32に増幅トランジスタ14の出力を伝えるためのトランジスタである。PDリセットトランジスタ17は、フォトダイオード10の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。フォトダイオード10以外は遮光されている。

【0038】

電源線33は、各画素に電源電圧VDDを供給するものであり、増幅トランジスタ14のドレイン端子、FDリセットトランジスタ13のドレイン端子、およびPDリセットトランジスタ17のドレイン端子に電気的に接続される。FDリセット線34は、1行分の画素の電荷保持部12をリセットするためのFDリセットパルスΦRMi(iは行番号、以下同様)が印加される信号線であり、1行分の画素のFDリセットトランジスタ13のゲート端子に電気的に接続される。転送線35は、1行分の画素のフォトダイオード10で発生した信号電荷をそれぞれの画素の電荷保持部12に転送するための行転送パルスΦTRiが印加される信号線であり、1行分の画素の転送トランジスタ11のゲート端子に電気的に接続される。

【0039】

PDリセット線36は、1行分の画素のフォトダイオード10をリセットするためのPDリセットパルスΦRPDiが印加される信号線であり、1行分の画素のPDリセットトランジスタ17のゲート端子に電気的に接続される。選択線37,38は、1行分の画素を選択するための行選択パルスΦSEi-1,ΦSEi-2が印加される信号線であり、1行分の画素の選択トランジスタ15,16のゲート端子に電気的に接続される。FDリセット線34、転送線35、PDリセット線36、および選択線37,38は制御線群30を構成する。

【0040】

図3は、撮像部202の構成を示している。撮像部202の撮像面には、図2に示した構成の画素L1〜Lnが2次元の行列状に配列されている。これらの画素L1〜Lnは画素部を構成する。本実施形態では、撮像部202が有する全画素からなる領域を画素信号の読み出し対象領域とするが、撮像部202が有する全画素からなる領域の一部を読み出し対象領域として、以下で説明する画素信号の読み出しを行ってもよい。図2に示す画素の配列は一例であり、行数および列数は2以上であればよい。

【0041】

垂直走査回路1(制御部)は行単位で画素の駆動制御を行うため、FDリセットパルスΦRMi、行転送パルスΦTRi、PDリセットパルスΦRPDi、行選択パルスΦSEi-1,ΦSEi-2を、制御線群30(図2のFDリセット線34、転送線35、PDリセット線36、選択線37,38)を介して行毎に独立して制御する。行選択パルスΦSEi-1,ΦSEi-2によって選択された行の画素の信号は、列毎に設けられている垂直信号線31,32へ出力される。なお、電源電圧VDDを供給する電源線33は図3に示していない。

【0042】

列処理回路2、水平読み出し回路3、AD変換回路4、フレームメモリ5、および差分回路6は、画素内の選択トランジスタ15から垂直信号線31に出力される画素信号を読み出して処理する第1出力系統(第1の処理部)を構成する。列処理回路2は、列毎の垂直信号線31に接続され、画素L1〜Lnから出力された画素信号に対してクランプ動作や増幅動作を行う。列処理回路2は、動画信号に関して、光信号とリセット信号との差分処理(減算処理)も行う(CDS動作)。水平読み出し回路3は、画素信号を読み出す画素列を選択して、その画素列に係る画素信号を順次AD変換回路4へ出力することにより画素信号を読み出す。

【0043】

AD変換回路4は、水平読み出し回路3によって読み出された画素信号をAD変換する。AD変換後の画素信号は、第1動画信号出力端子から出力されるかフレームメモリ5に保持される。なお、フレームメモリ5は、後述する4つのフィールド(f-A,f-B,f-C,f-D)毎に画素信号を保持できるように構成されている。差分回路6は、AD変換回路4から出力された画素信号と、フレームメモリ5に保持されている画素信号との差分処理(減算処理)を行い、処理結果の信号を第1静止画信号出力端子から出力する。

【0044】

列処理回路22、水平読み出し回路23、AD変換回路24、フレームメモリ5、および差分回路7は、画素内の選択トランジスタ16から垂直信号線32に出力される画素信号を読み出して処理する第2出力系統(第2の処理部)を構成する。列処理回路22は、列毎の垂直信号線32に接続され、画素L1〜Lnから出力された画素信号に対してクランプ動作や増幅動作を行う。列処理回路22は、動画信号に関して、光信号とリセット信号との差分処理(減算処理)も行う(CDS動作)。水平読み出し回路23は、画素信号を読み出す画素列を選択して、その画素列に係る画素信号を順次AD変換回路24へ出力することにより画素信号を読み出す。

【0045】

AD変換回路24は、水平読み出し回路23によって読み出された画素信号をAD変換する。AD変換後の画素信号は、第2動画信号出力端子から出力されるかフレームメモリ5に保持される。差分回路7は、AD変換回路24から出力された画素信号と、フレームメモリ5に保持されている画素信号との差分処理(減算処理)を行い、処理結果の信号を第2静止画信号出力端子から出力する。

【0046】

上記のように本実施形態では、画素から画素信号を読み出して処理を行い、処理後の画素信号を出力するための2つの出力系統が設けられている。これら2つの出力系統を用いることにより、異なる複数行の画素から同時に画素信号を読み出して出力することが可能となる。

【0047】

設定部8は、撮像部202における画素信号の読み出しモードを、後述する第1読み出しモードまたは第2読み出しモードに設定し、設定した読み出しモードに応じた動作を行うよう、垂直走査回路1、水平読み出し回路3,23を制御する。

【0048】

次に、撮像部202の動作を説明する。撮像部202は、グローバルシャッタ動作およびローリングシャッタ動作が可能である。以下では、それぞれの動作を説明する。

【0049】

図4は、静止画撮影動作時に用いられるグローバルシャッタ動作を示している。図4の横軸は時間を示している。破線DL1および実線SL1は、行毎の画素信号の読み出しのタイミングを示している。また、図4には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図4には、水平読み出し回路の出力信号も示されている。以下では、動作の説明を簡単にするため、2つの出力系統のうち第1出力系統を使用した場合の動作を説明する。第2出力系統を使用した場合の動作も同様である。

【0050】

グローバルシャッタ動作による光信号蓄積(露光)が行われる前に、リセット信号読み出し期間において、電荷保持部12をリセットしたときの電荷保持部12の電位(リセットレベル)の読み出しが行われる。このリセット信号読み出し期間では、まず1行目のFDリセットパルスΦRM1が“L”レベルから“H”レベルになることで、1行目の画素L1のFDリセットトランジスタ13がオンになり、1行目の画素L1の電荷保持部12のリセットが行われる。さらに、1行目の行選択パルスΦSE1-1が“L”レベルから“H”レベルになることで、選択トランジスタ15がオンになり、リセットレベルがリセット信号として垂直信号線31に出力され、列処理回路2、水平読み出し回路3、AD変換回路4をそれぞれ介してフレームメモリ5へ出力されてフレームメモリ5に記憶される。第1の出力系統または第2の出力系統を用いて、以上の動作と同様の動作が1行目からn行目(最終行)まで行われ、リセット信号読み出し期間が終了する。

【0051】

続いて、全画素のPDリセットパルスφRPDiが“L”レベルから“H”レベルになることで、全画素のPDリセットトランジスタ17が同時にオンになり、全画素のフォトダイオード10が一括でリセットされる。その後、全画素のPDリセットパルスφRPDiが“H”レベルから“L”レベルになることで、全画素のPDリセットトランジスタ17が同時にオフになり、全画素の露光(電荷蓄積)が開始される。露光を開始してから所定の露光期間(蓄積期間)が経過すると、全画素の行転送パルスΦTRiが“L”レベルから“H”レベルになることで、露光期間中にフォトダイオード10に蓄積された信号電荷が電荷保持部12に一括で転送される。つまり、全画素の露光が同時に終了する。

【0052】

露光の終了後、光信号読み出し期間において、電荷保持部12の電位(光信号レベル)の読み出しが行われる。この光信号読み出し期間では、まず1行目の行選択パルスΦSE1-1が“L”レベルから“H”レベルになることで、選択トランジスタ15がオンになり、光信号レベルが光信号として垂直信号線31に出力され、列処理回路2、水平読み出し回路3、AD変換回路4をそれぞれ介して差分回路6へ出力される。

【0053】

差分回路6は、1行目の画素L1の光信号と、フレームメモリ5に保持されている1行目の画素L1のリセット信号との差分をとることにより、光信号成分のみを抽出し、ノイズが除去された静止画信号として第1静止画信号出力端子から画像処理部203へ出力する。第1の出力系統または第2の出力系統を用いて、以上の動作と同様の動作が1行目からn行目(最終行)まで行われ、光信号読み出し期間が終了し、1枚の静止画信号が画像処理部203へ出力される。

【0054】

図5は、リセット信号読み出し期間と光信号読み出し期間における画素信号をフィールドの単位で読み出す場合の動作を示している。図5に示す動作は、全画素を3つのフィールドに分けた場合の動作である。図5に示す例では、全画素は、1行目、4行目、7行目・・・の画素群からなる第1フィールド(f-A)と、2行目、5行目、8行目・・・の画素群からなる第2フィールド(f-B)と、3行目、6行目、9行目・・・の画素群からなる第3フィールド(f-C)に分割されている(図6参照)。

【0055】

図5に示す動作では、リセット信号読み出し期間において第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)の順にリセット信号の読み出しが行われ、光信号読み出し期間において第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)の順に光信号の読み出しが行われる。すなわち、図5に示す動作は、図4に示す動作に対して、画素信号を読み出す画素の順番が異なるだけである。このように、グローバルシャッタ動作においては、必ずしも1行目から最終行まで、行の並び順に画素信号を読み出す必要はない。以下では、静止画信号の読み出しに関しては、図5に示す動作と同様の動作によって読み出しを行う場合について説明する。

【0056】

図7は、動画表示動作時に用いられるローリングシャッタ動作を示している。図7の横軸は時間を示している。破線DL2は、行毎に画素をリセットするための走査のタイミングを示し、実線SL2は、行毎の光信号の読み出しのタイミングを示している。また、図7では、水平読み出し回路の出力信号も示されている。ローリングシャッタ動作では、全画素同時に制御信号を印加する動作はないため、全画素の行転送パルスΦTRiおよびPDリセットパルスΦRPDiは図示していない。ローリングシャッタ動作では、行毎に時間をずらしてリセット信号の読み出しと光信号の読み出しが行われる。以下では、動作の説明を簡単にするため、2つの出力系統のうち第1出力系統を使用した場合の動作を説明する。第2出力系統を使用した場合の動作も同様である。

【0057】

1行目の画素L1のリセットは、以下のようにして行われる。まず、1行目のリセットパルスΦRM1が“L”レベルから“H”レベルになることで、1行目の画素L1のFDリセットトランジスタ13がオンになり、1行目の画素L1の電荷保持部12のリセットが行われる。さらに、1行目の行転送パルスΦTR1が“L”レベルから“H”レベルになることで、1行目の画素L1の転送トランジスタ11がオンになり、転送トランジスタ11およびFDリセットトランジスタ13を介してフォトダイオード10のリセットが行われる。その後、1行目の行転送パルスΦTR1が“H”レベルから“L”レベルになることで、1行目の画素L1の転送トランジスタ11がオフになり、1行目の画素L1の露光(電荷蓄積)が開始される。

【0058】

露光の開始から所定の露光期間が経過した後に光信号の読み出しが行われる。光信号の読み出しに先立って、露光期間中に1行目のリセットパルスΦRM1が“L”レベルから“H”レベルになることで、1行目の画素L1のFDリセットトランジスタ13がオンになり、1行目の画素L1の電荷保持部12のリセットが行われる。さらに、1行目の選択パルスΦSE1-1が“L”レベルから“H”レベルになることで、1行目の画素L1の選択トランジスタ15がオンになり、リセットレベルがリセット信号として垂直信号線31に出力される。

【0059】

1行目の露光期間の終了タイミングで1行目の行転送パルスΦTR1が“L”レベルから“H”レベルになることで、1行目の画素L1の転送トランジスタ11がオンになり、露光期間中にフォトダイオード10に蓄積された信号電荷が電荷保持部12に転送される。このとき、1行目の選択パルスΦSE1-1が“H”レベルであり、1行目の画素L1の選択トランジスタ15がオンであるため、電荷保持部12に保持された信号電荷に基づく光信号レベルが光信号として垂直信号線31に出力される。

【0060】

列処理回路2は、垂直信号線31に出力された光信号とリセット信号との差分をとることにより、光信号成分のみを抽出し、ノイズが除去された動画信号を出力する。この動画信号は、水平読み出し回路3、AD変換回路4、差分回路6をそれぞれ介して画像処理部203へ出力される。第1の出力系統または第2の出力系統を用いて、以上の動作と同様の動作が1行目からn行目(最終行)まで行われ、1枚の動画信号が画像処理部203へ出力される。

【0061】

なお、動画表示動作時には、全画素から画素信号を読み出すのではなく、図8に示すように、画素信号を読み出す行を間引くことによって、1フレームの画素信号の読み出しに必要な期間を短くすることが可能となる。

【0062】

次に、撮像装置の動作を説明する。本実施形態の撮像装置は、静止画信号の読み出しに第1出力系統を使用し、動画信号の読み出しに第2出力系統を使用する第1読み出しモードと、静止画信号と動画信号の少なくとも一方の読み出しに第1出力系統および第2出力系統の両方を使用する第2読み出しモードとを選択して動作することが可能である。ユーザは、カメラ操作部208を操作することによって、読み出しモードを選択することが可能である。撮像部202に対する読み出しモードの設定は、カメラ制御部207から読み出しモードの指示を受けた駆動制御部205によって行われる。また、撮像部202の内部における読み出しモードの設定は、駆動制御部205からの指示を受けた設定部8によって行われる。設定部8による読み出しモードの設定を受けて、垂直走査回路1、水平読み出し回路3,23は、各読み出しモードに応じた画素信号の読み出しを行う。

【0063】

図9は、第1読み出しモードの動作を示している。図9の横軸は時間を示している。図9では、第1出力系統を使用した画素信号の読み出しのタイミングと、第2出力系統を使用した画素信号の読み出しのタイミングとが示されている。また、図9には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図9には、第1出力系統を構成する水平読み出し回路3の出力信号と、第2出力系統を構成する水平読み出し回路23の出力信号も示されている。

【0064】

図9に示す動作は、全画素を4つのフィールドに分けた場合の動作である。図9に示す例では、全画素は、1行目、5行目、9行目・・・の画素群からなる第1フィールド(f-A)と、2行目、6行目、10行目・・・の画素群からなる第2フィールド(f-B)と、3行目、7行目、11行目・・・の画素群からなる第3フィールド(f-C)と、4行目、8行目、12行目・・・の画素群からなる第4フィールド(f-D)に分割されている(図10参照)。

【0065】

図9に示す第1読み出しモードでは、静止画信号と動画信号が並列に、異なる出力系統を使用して読み出される。図9に示す動作では、第1出力系統を使用して、図5に示したグローバルシャッタ動作により、リセット信号読み出し期間に第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の順に静止画用のリセット信号の読み出しが行われ、光信号読み出し期間に第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の順に静止画用の光信号の読み出しが行われる。差分回路6は、AD変換回路4から出力された各フィールドの光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第1静止画信号出力端子から出力する。第1静止画信号出力端子から出力された各フィールドの静止画信号は、画像処理部203の第1画像処理部203aで処理され、1枚の静止画信号がメモリカード209に記録される。

【0066】

一方、図9に示す動作では、第2出力系統を使用して、図7に示したローリングシャッタ動作により、静止画信号の読み出しに関係のないフィールドの画素を用いて、画素を間引きしながら動画信号の読み出しが行われる。静止画用のリセット信号を読み出した後の画素では、電荷保持部12を再度リセットして動画用のリセット信号を読み出すことは好ましくない。このため、リセット信号読み出し期間では、静止画用のリセット信号を最後に読み出すフィールドである第4フィールド(f-D)の画素から静止画用のリセット信号が読み出される前に、第4フィールド(f-D)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。

【0067】

また、光信号読み出し期間では、静止画用の光信号を読み出していない画素の電荷保持部12をリセットすることは好ましくないため、静止画用の光信号を最初に読み出したフィールドである第1フィールド(f-A)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。第2動画信号出力端子から出力された動画信号は、画像処理部203の第2画像処理部203bで処理され、表示部204へ出力され、表示部204に画像(ライブビュー画像)が表示される。

【0068】

図9に示す動作では、静止画撮影の1サイクルの期間において、1枚の静止画信号と6枚の動画信号が得られる。静止画撮影の1サイクルの期間を処理の単位として、処理が繰り返し行われている様子が図9に示されている。

【0069】

上記のように、図9に示した第1読み出しモードでは、垂直走査回路1が出力する制御信号によって、全画素の静止画用の露光期間が同一となるように画素の露光が制御され、フィールドの単位で静止画信号および動画信号の読み出しが制御される。さらに、第1読み出しモードでは、垂直走査回路1が出力する制御信号によって、第1出力系統を使用してフィールドの単位で静止画信号を読み出す制御が行われ、第2出力系統を使用してフィールドの単位で動画信号を読み出す制御が行われる。

【0070】

図11は、第2読み出しモードの動作を示している。図11の横軸は時間を示している。図11では、第1出力系統を使用した画素信号の読み出しのタイミングと、第2出力系統を使用した画素信号の読み出しのタイミングとが示されている。また、図11には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図11には、第1出力系統を構成する水平読み出し回路3の出力信号と、第2出力系統を構成する水平読み出し回路23の出力信号も示されている。図11に示す動作は、図9に示す動作と同様に、全画素を4つのフィールドに分けた場合の動作である。

【0071】

図11に示す第2読み出しモードでは、第1出力系統および第2出力系統を使用して静止画信号が読み出され、第2出力系統のみを使用して動画信号が読み出される。図11に示す動作では、第1出力系統を使用して、図5に示したグローバルシャッタ動作により、リセット信号読み出し期間に第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)の順に静止画用のリセット信号の読み出しが行われ、光信号読み出し期間に第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の順に静止画用の光信号の読み出しが行われる。

【0072】

一方、図11に示す動作では、第2出力系統を使用して、リセット信号読み出し期間において、図7に示したローリングシャッタ動作により、第4フィールド(f-D)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。続いて、図5に示したグローバルシャッタ動作により、第4フィールド(f-D)の画素を用いて静止画用のリセット信号の読み出しが行われる。

【0073】

また、第2出力系統を使用して、光信号読み出し期間において、図5に示したグローバルシャッタ動作により、第1フィールド(f-A)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、図7に示したローリングシャッタ動作により、第1フィールド(f-A)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。

【0074】

上記のようにして第2動画信号出力端子から出力された動画信号は、画像処理部203の第2画像処理部203bで処理され、表示部204へ出力され、表示部204に画像(ライブビュー画像)が表示される。

【0075】

また、差分回路6は、AD変換回路4から出力された第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第1静止画信号出力端子から出力する。差分回路7は、AD変換回路24から出力された第1フィールド(f-A)の光信号と、フレームメモリ5に保持されている第1フィールド(f-A)のリセット信号との差分をとった静止画信号を生成し、第2静止画信号出力端子から出力する。第1静止画信号出力端子および第2静止画信号出力端子から出力された各フィールドの静止画信号は、画像処理部203の第1画像処理部203aで処理され、1枚の静止画信号がメモリカード209に記録される。

【0076】

図11に示す動作では、静止画撮影の1サイクルの期間において、1枚の静止画信号と4枚の動画信号が得られる。静止画撮影の1サイクルの期間を処理の単位として、処理が繰り返し行われている様子が図11に示されている。

【0077】

上記のように、図11に示した第2読み出しモードでは、垂直走査回路1が出力する制御信号によって、全画素の静止画用の露光期間が同一となるように画素の露光が制御され、フィールドの単位で静止画信号および動画信号の読み出しが制御される。さらに、第2読み出しモードでは、垂直走査回路1が出力する制御信号によって、第1出力系統および第2出力系統を使用してフィールドの単位で静止画信号を読み出す制御が行われ、第2出力系統を使用してフィールドの単位で動画信号を読み出す制御が行われる。

【0078】

図11に示した第2読み出しモードでは、静止画用の複数フィールドのリセット信号と光信号を、2つの出力系統を用いて同時に読み出して出力することが可能なので、第1読み出しモードに比べて静止画撮影の1サイクル期間を短くすることができ、静止画撮影時間を短縮することが可能となる。前述したように、読み出しモードの設定は設定部8によって行われる。例えば、通常は第1読み出しモードが設定されるようにし、撮影スピードを優先する場合は第2読み出しモードが設定されるようにすればよい。

【0079】

次に、本実施形態の変形例を説明する。図12は、図11に示した動作とは異なる第2読み出しモードの動作を示している。図12の横軸は時間を示している。図12では、第1出力系統を使用した画素信号の読み出しのタイミングと、第2出力系統を使用した画素信号の読み出しのタイミングとが示されている。また、図12には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図12には、第1出力系統を構成する水平読み出し回路3の出力信号と、第2出力系統を構成する水平読み出し回路23の出力信号も示されている。

【0080】

図12に示す動作は、全画素を4つのフィールドに分けた場合の動作である。フィールドの分割形態は、図10に示した形態と同一である。図11に示した動作では、第2出力系統のみを使用して動画信号が読み出されているが、図12に示す動作では、動画信号を読み出すフィールドがさらに2分割されており、第1出力系統および第2出力系統を使用して各フィールドの動画信号が読み出される。

【0081】

図12に示す動作では、第1出力系統を使用して、リセット信号読み出し期間において、図7に示したローリングシャッタ動作により、第4フィールド(f-D)をさらに2分割したフィールドの一方であるフィールドf-D1の画素を用いて動画信号の読み出しが行われ、動画信号が第1動画信号出力端子から出力される。続いて、図5に示したグローバルシャッタ動作により、第1フィールド(f-A)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、フィールドf-D1の画素を用いて動画信号の読み出しが行われ、さらに第3フィールド(f-C)の画素を用いて静止画用のリセット信号の読み出しが行われる。

【0082】

また、第1出力系統を使用して、光信号読み出し期間において、図5に示したグローバルシャッタ動作により、第1フィールド(f-A)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、図7に示したローリングシャッタ動作により、第1フィールド(f-A)をさらに2分割したフィールドの一方であるフィールドf-A1の画素を用いて動画信号の読み出しが行われ、動画信号が第1動画信号出力端子から出力される。続いて、第3フィールド(f-C)の画素を用いて静止画用のリセット信号の読み出しが行われ、さらにフィールドf-A1の画素を用いて動画信号の読み出しが行われる。

【0083】

一方、図12に示す動作では、第2出力系統を使用して、リセット信号読み出し期間において、図7に示したローリングシャッタ動作により、第4フィールド(f-D)をさらに2分割したフィールドの他方であるフィールドf-D2の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。続いて、図5に示したグローバルシャッタ動作により、第2フィールド(f-B)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、フィールドf-D2の画素を用いて動画信号の読み出しが行われ、さらに第4フィールド(f-D)の画素を用いて静止画用のリセット信号の読み出しが行われる。

【0084】

また、第2出力系統を使用して、光信号読み出し期間において、図5に示したグローバルシャッタ動作により、第2フィールド(f-B)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、図7に示したローリングシャッタ動作により、第1フィールド(f-A)をさらに2分割したフィールドの他方であるフィールドf-A2の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。続いて、第4フィールド(f-D)の画素を用いて静止画用のリセット信号の読み出しが行われ、さらにフィールドf-A2の画素を用いて動画信号の読み出しが行われる。

【0085】

上記のようにして第1動画信号出力端子および第2動画信号出力端子から出力された動画信号は、画像処理部203の第2画像処理部203bで処理され、表示部204へ出力され、表示部204に画像(ライブビュー画像)が表示される。

【0086】

また、差分回路6は、AD変換回路4から出力された第1フィールド(f-A)、第3フィールド(f-C)の光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第1静止画信号出力端子から出力する。差分回路7は、AD変換回路24から出力された第2フィールド(f-B)、第4フィールド(f-D)の光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第2静止画信号出力端子から出力する。第1静止画信号出力端子および第2静止画信号出力端子から出力された各フィールドの静止画信号は、画像処理部203の第1画像処理部203aで処理され、1枚の静止画信号がメモリカード209に記録される。

【0087】

図12に示す動作では、静止画撮影の1サイクルの期間において、1枚の静止画信号と4枚の動画信号が得られる。静止画撮影の1サイクルの期間を処理の単位として、処理が繰り返し行われている様子が図12に示されている。

【0088】

図11に示した第2読み出しモードでは、静止画用の複数フィールドのリセット信号と光信号を、2つの出力系統を用いて同時に読み出して出力することに加えて、複数フィールドの動画信号を、2つの出力系統を用いて同時に読み出して出力することが可能なので、第1読み出しモードに比べて静止画撮影の1サイクル期間を短くすることができ、静止画撮影時間を短縮することが可能となる。

【0089】

なお、図9、図11、図12に示した動作では、静止画撮影の1サイクルの期間が複数回繰り返されているが、静止画撮影の1サイクルの期間の動作を1回だけ行ってもよい。また、静止画撮影の1サイクルの期間と次の静止画撮影の1サイクルの期間との間に、他の処理を行う期間を設けてもよい。また、フィールドの数や、画素信号を読み出すフィールドの順番、第1出力系統および第2出力系統で読み出すフィールドの組合せ等は適宜変更することが可能である。

【0090】

上述したように、本実施形態の第2読み出しモードでは、フィールド単位で静止画用のリセット信号および光信号の読み出しを行う複数の期間(フィールド毎に割り当てられた期間)のうちの少なくとも1つの期間において、第1出力系統および第2出力系統の両方を使用してフィールド単位でリセット信号および光信号を読み出すよう静止画信号の読み出しを制御することによって、静止画撮影時間を短縮することができる。

【0091】

以上、図面を参照して本発明の実施形態について詳述してきたが、具体的な構成は上記の実施形態に限られるものではなく、本発明の要旨を逸脱しない範囲の設計変更等も含まれる。

【符号の説明】

【0092】

1,300・・・垂直走査回路、2,22,350・・・列処理回路、3,23,400・・・水平読み出し回路、4,24・・・AD変換回路、5,600・・・フレームメモリ、6,7,700・・・差分回路、8・・・設定部、10,101・・・フォトダイオード、11,102・・・転送トランジスタ、12,103・・・電荷保持部、13,104・・・ FDリセットトランジスタ、14,105・・・増幅トランジスタ、15,16,106・・・選択トランジスタ、17,107・・・ PDリセットトランジスタ、100・・・画素、150・・・電流源、200・・・画素部、201・・・レンズ、202・・・撮像部、203・・・画像処理部、203a・・・第1画像処理部、203b・・・第2画像処理部、204・・・表示部、205・・・駆動制御部、206・・・レンズ制御部、207・・・カメラ制御部、208・・・カメラ操作部、209・・・メモリカード、500・・・ ADコンバータ、600・・・差分回路

【技術分野】

【0001】

本発明は、デジタルスチルカメラ、デジタルビデオカメラなどに適用される固体撮像装置、およびその固体撮像装置を備えた撮像装置に関する。

【背景技術】

【0002】

近年、周辺回路をオンチップ化できるMOS型固体撮像素子の性能向上はめざましく、CCD型固体撮像素子に替わってMOS型固体撮像素子の普及が進んできている。MOS型撮像素子の撮像面には多数の画素が2次元状に配列されており、各画素は入射した光を信号電荷に変換して画素信号(画像信号)を生成する。MOS型固体撮像素子の駆動方法として、露光開始時刻および露光終了時刻が画素毎に異なるローリングシャッタ方式と、露光開始時刻および露光終了時刻が全画素で同一となるグローバルシャッタ方式とがある。

【0003】

グローバルシャッタ方式のMOS型固体撮像素子は、露光量に応じた信号電荷を発生するフォトダイオード等の光電変換部、光電変換部において発生した信号電荷を一時的に蓄積する電荷保持部(電荷蓄積部)、信号電荷の転送やリセットを行うためのスイッチ用途のトランジスタ等で構成される。

【0004】

図13は、グローバルシャッタ方式のMOS型固体撮像素子の撮像面に2次元状に配列される画素100の構成を示している。フォトダイオード(PD)101は、入射光を信号電荷に変換(光電変換)して蓄積する光電変換素子である。転送トランジスタ102は、フォトダイオード101で発生した信号電荷を電荷保持部(FD)103に転送するためのトランジスタである。電荷保持部103は、フォトダイオード101に蓄積された信号電荷を保持するためのフローティングディフュージョン(FD)である。FDリセットトランジスタ104は、電荷保持部103の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。

【0005】

増幅トランジスタ105は、電荷保持部103の電圧レベルを増幅して読み出すためのトランジスタである。選択トランジスタ106は、画素を選択し、垂直信号線114に増幅トランジスタ105の出力を伝えるためのトランジスタである。PDリセットトランジスタ107は、フォトダイオード101の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。フォトダイオード101以外は遮光されている。

【0006】

電源線110は、各画素に電源電圧VDDを供給するものであり、増幅トランジスタ105のドレイン端子、FDリセットトランジスタ104のドレイン端子、およびPDリセットトランジスタ107のドレイン端子に電気的に接続される。FDリセット線111は、1行分の画素の電荷保持部103をリセットするためのFDリセットパルスφRMi(iは行番号、以下同様)が印加される信号線であり、1行分の画素のFDリセットトランジスタ104のゲート端子に電気的に接続される。転送線112は、1行分の画素のフォトダイオード101で発生した信号電荷をそれぞれの画素の電荷保持部103に転送するための行転送パルスφTRiが印加される信号線であり、1行分の画素の転送トランジスタ102のゲート端子に電気的に接続される。

【0007】

PDリセット線115は、1行分の画素のフォトダイオード101をリセットするためのPDリセットパルスφRPDiが印加される信号線であり、1行分の画素のPDリセットトランジスタ107のゲート端子に電気的に接続される。選択線113は、1行分の画素を選択するための行選択パルスφSEiが印加される信号線であり、1行分の画素の選択トランジスタ106のゲート端子に電気的に接続される。このように5個のトランジスタを用いた画素構成により、光電変換機能、リセット機能、増幅読み出し機能、一時メモリ機能、及び選択機能を実現している。

【0008】

図14は、固体撮像素子の撮像面に、図13に示した画素を3行×3列に配列した構成を示している。図14において、画素部200は、画素100が3×3の2次元状に配列されて構成されている。画素100の構成は図13に示した通りである。

【0009】

垂直走査回路300は行単位で画素部200の駆動制御を行う。この駆動制御を行うために、垂直走査回路300は、行数と同じ数の単位回路301-1,301-2,301-3から構成されている。また、各単位回路は、制御部302-i,303-i,304-i,305-i(i=1,2,3)から構成されている。

【0010】

制御部302-i は、1行分の画素100の電荷保持部103をリセットするためのFDリセットパルスφRMi(i=1,2,3)を、FDリセット線111を介して行毎に独立して制御する。制御部303-i は、1行分の画素100の信号電荷をそれぞれの画素100の電荷保持部103 に転送するための行転送パルスφTRi(i=1,2,3)を、転送線112を介して行毎に独立して制御する。制御部304-i は、1行分の画素100のフォトダイオード101をリセットするためのPDリセットパルスφRPDi(i=1,2,3)を、PDリセット線115を介して行毎に独立して制御する。制御部305-i は、信号を読み出す1行分の画素100を選択するための行選択パルスφSEi(i=1,2,3)を、選択線113を介して行毎に独立して制御する。行選択パルスφSEiによって選択された行の画素100の信号は、列毎に設けられている垂直信号線114へ出力される。

【0011】

電流源150は、列毎に設けられており、垂直信号線114に接続され、画素100内の増幅トランジスタ105とソースフォロア回路を構成する。列処理回路350は、列毎に設けられており、垂直信号線114に出力される画素信号に対してクランプ動作や増幅動作を行う。水平読み出し回路400は、画素信号を読み出す画素列を選択して、その画素列に係る画素信号を出力端子410から出力する。AD(Analog to Digital)コンバータ500は、出力端子410から出力された画素信号をAD変換する。フレームメモリ600は、AD変換後の画素信号を保持する。差分回路700は、ADコンバータ500から出力された画素信号と、フレームメモリ600に保持されている画素信号との差分処理(減算処理)を行う。なお、電源電圧VDDを供給する電源線110は図14に示していない。

【0012】

図14に示したMOS型固体撮像素子を、デジタルカメラなどによる静止画の撮像に適用した場合にグローバルシャッタ方式で画素信号を読み出す動作を説明する。図15は、グローバルシャッタ方式による動作を示している。ただし、ここでは説明を簡単にするため、図14と同様に画素が3×3の2次元状に配置された固体撮像素子を用いて説明する。

【0013】

撮影開始を示す信号が入力されると、まず全行のPDリセットパルスφRPDiが“L”レベルから“H”レベルになることで全ての画素100のPDリセットトランジスタ107がオンになり、全ての画素100のフォトダイオード101がリセットされる。続いて、1行目のFDリセットパルスφRM1が“L”レベルから“H”レベルになることで1行目のFDリセットトランジスタ104がオンになり、1行目の電荷保持部103がリセットされる。

【0014】

続いて、1行目のFDリセットパルスφRM1が“H”レベルから“L”レベルになることでFDリセットトランジスタ104がオフになった後、1行目の行選択パルスφSE1が“L”レベルから“H”レベルになることで1行目の選択トランジスタ106がオンになり、1行目の電荷保持部103の電圧(リセットレベル)が、列処理回路350を介してリセット信号として水平読み出し回路400へ出力される。水平読み出し回路400はリセット信号を出力端子410から水平方向に順次出力する。

【0015】

出力された1行目の画素100のリセット信号はADコンバータ500によりAD変換されてフレームメモリ600に出力され、フレームメモリ600に保持される。2行目以降についても1行目と同様にリセット信号が読み出され、全ての画素100のリセット信号がフレームメモリ600に保持される。

【0016】

続いて、全行のPDリセットパルスφRPDiが“H”レベルから“L”レベルになることで全ての画素100のPDリセットトランジスタ107がオフになり、全ての画素100のフォトダイオード101が信号電荷の蓄積を開始する。これにより、全ての画素100の露光(電荷蓄積)が開始される。所望の蓄積時間が経過すると、全行の行転送パルスφTRiが“L”レベルから“H”レベルになることで全ての画素100の転送トランジスタ102がオンになり、全ての画素100のフォトダイオード101に蓄積された信号電荷が電荷保持部103に転送される。すなわち露光(電荷蓄積)が終了する。電荷蓄積開始から電荷蓄積終了までの期間が露光期間(蓄積期間)である。

【0017】

信号電荷の転送動作が終了した直後に、全行のPDリセットパルスφRPDiが“L”レベルから“H”レベルになることで全ての画素100のPDリセットトランジスタ107がオンになり、全ての画素100のフォトダイオード101がリセット状態となる。続いて、1行目の行選択パルスφSEiが“L”レベルから“H”レベルになることで1行目の選択トランジスタ106がオンになり、1行目の電荷保持部103の電圧(光信号レベル)が、列処理回路350を介して光信号として水平読み出し回路400へ出力される。水平読み出し回路400は光信号を出力端子410から水平方向に順次出力する。

【0018】

出力された1行目の画素100の光信号はADコンバータ500によりAD変換され、差分回路700へ出力される。差分回路700は、1行目の画素100の光信号と、フレームメモリ600に保持されている1行目の画素100のリセット信号との差分をとることにより、光信号成分のみを抽出し、撮像信号として後段の回路に出力する。この動作では、電荷保持部103のリセットノイズを除去することが可能であるので、高S/Nの信号を得ることができる。

【0019】

続いて、2行目以降についても1行目と同様な動作が行われ、全ての画素100の画素信号が読み出される。この信号は後段の画像処理回路(不図示)で処理され、静止画像が生成される。上述した動作により、全画素一括で露光および電荷の蓄積を行うグローバルシャッタ動作を実現することができる。このようなMOS型固体撮像素子についての技術が特許文献1に開示されている。

【0020】

一般的なデジタルカメラは、電源の投入後、フレーム単位で周期的に撮像を行って動画信号(動画像信号)を生成し、生成した動画信号に基づいてライブビュー画像(動画像)を表示部に表示する。ライブビュー画像の表示中にユーザが、静止画の取得指示である撮影指示を行うと、デジタルカメラは、動画信号の生成を停止し、撮像を行って静止画信号(静止画像信号)を生成し、生成した静止画信号を記録媒体に記録する。この静止画信号の生成時に、例えば上記のグローバルシャッタ動作が行われる。

【0021】

しかしながら、静止画の撮像時にはライブビュー画像の更新を行うことができないため、更新ができない期間に同一の画像が表示部に表示される、あるいは表示部がブラックアウトして画像が表示されないなどの現象が発生してしまう。また、上述したグローバルシャッタ動作においては、露光前のリセット信号用の読み出し動作と、露光後の光信号用の読み出し動作との両方が必要となるために、画素数の増加に応じて、1枚の静止画を撮影するために必要なシーケンス期間が長くなる。

【0022】

これらの問題を改善するために、固体撮像素子の画素を複数の画素群に分けると共に、静止画用と動画(ライブビュー)用の2つの出力系統を設け、静止画信号の読み出しに使用していない画素群を動画信号の読み出しに使用することにより、静止画信号の読み出しと動画信号の読み出しとを同時に行う方法が特許文献2(例えば、図18〜図21)に開示されている。

【先行技術文献】

【特許文献】

【0023】

【特許文献1】特開平11−261896号公報

【特許文献2】特開2010−183195号公報

【発明の概要】

【発明が解決しようとする課題】

【0024】

従来技術では、静止画の撮影中にライブビュー(動画)表示を行う場合に静止画信号と動画信号を同時に読み出すことで、ライブビュー画像の更新を行うことができない期間を短縮することが可能である。しかし、2つの出力系統の一方を静止画信号の読み出しに固定し、他方を動画信号の読み出しに固定しており、画素数の多い静止画信号の読み出しを、1つの出力系統のみを使用して行っているため、静止画撮影時間の短縮に限界があった。

【0025】

本発明は、上述した課題に鑑みてなされたものであって、静止画撮影時間を短縮することができる固体撮像装置および撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0026】

本発明は、上記の課題を解決するためになされたもので、光を信号電荷に変換し、信号電荷を蓄積する光電変換素子と、前記光電変換素子に蓄積された信号電荷を保持する電荷保持部と、前記光電変換素子に蓄積された信号電荷を前記電荷保持部に転送する転送部と、前記電荷保持部に保持された信号電荷に基づく画素信号を静止画信号または動画信号として出力する第1の出力部および第2の出力部とを備えた画素を2次元状に配列した画素部と、前記第1の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第1の処理部と、前記第2の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第2の処理部と、読み出し対象領域を構成する全画素の静止画用の露光期間が同一となるように前記画素の露光を制御し、前記読み出し対象領域を構成する全画素を複数に分割したフィールドの単位で前記静止画信号および前記動画信号の読み出しを制御し、さらに、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御する制御部と、を有することを特徴とする固体撮像装置である。

【0027】

また、本発明の固体撮像装置において、前記制御部は、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御することを特徴とする。

【0028】

また、本発明の固体撮像装置は、第1のモードおよび第2のモードの設定が可能な固体撮像装置であって、前記制御部は、前記第1のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の一方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の他方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御し、前記第2のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御することを特徴とする。

【0029】

また、本発明は、上記の固体撮像装置を備えた撮像装置である。

【発明の効果】

【0030】

本発明によれば、フィールド単位で静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において第1の出力部および第2の出力部の両方からフィールドの単位で静止画信号を読み出すよう静止画信号の読み出しを制御することによって、静止画撮影時間を短縮することができる。

【図面の簡単な説明】

【0031】

【図1】本発明の一実施形態による撮像装置の構成を示すブロック図である。

【図2】本発明の一実施形態による撮像装置が備える画素の構成を示す回路図である。

【図3】本発明の一実施形態による撮像装置が備える撮像部の構成を示すブロック図である。

【図4】本発明の一実施形態による撮像装置が備える撮像部のグローバルシャッタ動作を示すタイミングチャートである。

【図5】本発明の一実施形態による撮像装置が備える撮像部のグローバルシャッタ動作を示すタイミングチャートである。

【図6】本発明の一実施形態による撮像装置が備える画素をフィールドに分割した状態を示す参考図である。

【図7】本発明の一実施形態による撮像装置が備える撮像部のローリングシャッタ動作を示すタイミングチャートである。

【図8】本発明の一実施形態の動画表示動作時に画素信号を読み出す画素を示す参考図である。

【図9】本発明の一実施形態による撮像装置の動作を示すタイミングチャートである。

【図10】本発明の一実施形態による撮像装置が備える画素をフィールドに分割した状態を示す参考図である。

【図11】本発明の一実施形態による撮像装置の動作を示すタイミングチャートである。

【図12】本発明の一実施形態による撮像装置の動作を示すタイミングチャートである。

【図13】従来の画素の構成を示す回路図である。

【図14】従来の固体撮像装置の構成を示すブロック図である。

【図15】従来の固体撮像装置の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0032】

以下、図面を参照し、本発明の実施形態を説明する。図1は、本発明の一実施形態による撮像装置の構成を示している。図1に示す撮像装置は、レンズ201と、撮像部202と、画像処理部203と、表示部204と、駆動制御部205と、レンズ制御部206と、カメラ制御部207と、カメラ操作部208とを備えている。図1にはメモリカード209も示されているが、このメモリカード209を撮像装置に対して着脱可能に構成することによって、メモリカード209は撮像装置に固有の構成でなくても構わない。

【0033】

レンズ201は、固体撮像素子(固体撮像装置)を構成する撮像部202の撮像面に被写体の光学像を結像するための撮影レンズである。撮像部202は、レンズ201によって結像された被写体の光学像を光電変換によりデジタルの画像信号に変換して出力する。画像処理部203は、撮像部202から出力される画像信号に種々のデジタル的な画像処理を施す。この画像処理部203は、画像信号を記録用に処理する第1画像処理部203aと、画像信号を表示用に処理する第2画像処理部203bとを備えている。

【0034】

表示部204は、画像処理部203の第2画像処理部203bにより表示用に画像処理された画像信号に基づき画像を表示する。この表示部204は、静止画像を再生表示することができると共に、被撮像範囲の画像をリアルタイムに表示する動画(ライブビュー)表示を行うことができるようになっている。駆動制御部205は、カメラ制御部207からの指示に基づいて撮像部202の動作を制御する。レンズ制御部206は、カメラ制御部207からの指示に基づいて、レンズ201の絞りや焦点位置を制御する。

【0035】

カメラ制御部207は、撮像装置全体を制御する。カメラ操作部208は、ユーザが撮像装置に対する各種の操作入力を行うための操作用の各種部材を有し、操作入力の結果に基づく信号をカメラ制御部207へ出力する。カメラ操作部208の具体例として、撮像装置の電源をオン・オフするための電源スイッチ、静止画撮影を指示するためのレリーズボタン、静止画撮影モードを単写モードと連写モードの間で切り替えるための静止画撮影モードスイッチなどが挙げられる。メモリカード209は、第1画像処理部203aにより記録用に処理された画像信号を保存するための記録媒体である。

【0036】

次に、撮像部202の構成を説明する。図2は、撮像部202に用いられる画素の構成を示している。フォトダイオード(PD)10は、入射光を信号電荷に変換(光電変換)して蓄積する光電変換素子である。転送トランジスタ11(転送部)は、フォトダイオード101で発生した信号電荷を電荷保持部(FD)12に転送するためのトランジスタである。電荷保持部12は、フォトダイオード10に蓄積された信号電荷を保持するためのフローティングディフュージョン(FD)である。FDリセットトランジスタ13は、電荷保持部12の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。

【0037】

増幅トランジスタ14は、電荷保持部12の電圧レベルを増幅して読み出すためのトランジスタである。選択トランジスタ15,16(第1の出力部、第2の出力部)は、画素を選択し、垂直信号線31,32に増幅トランジスタ14の出力を伝えるためのトランジスタである。PDリセットトランジスタ17は、フォトダイオード10の電位(すなわち信号電荷)をリセット(初期化)するためのトランジスタである。フォトダイオード10以外は遮光されている。

【0038】

電源線33は、各画素に電源電圧VDDを供給するものであり、増幅トランジスタ14のドレイン端子、FDリセットトランジスタ13のドレイン端子、およびPDリセットトランジスタ17のドレイン端子に電気的に接続される。FDリセット線34は、1行分の画素の電荷保持部12をリセットするためのFDリセットパルスΦRMi(iは行番号、以下同様)が印加される信号線であり、1行分の画素のFDリセットトランジスタ13のゲート端子に電気的に接続される。転送線35は、1行分の画素のフォトダイオード10で発生した信号電荷をそれぞれの画素の電荷保持部12に転送するための行転送パルスΦTRiが印加される信号線であり、1行分の画素の転送トランジスタ11のゲート端子に電気的に接続される。

【0039】

PDリセット線36は、1行分の画素のフォトダイオード10をリセットするためのPDリセットパルスΦRPDiが印加される信号線であり、1行分の画素のPDリセットトランジスタ17のゲート端子に電気的に接続される。選択線37,38は、1行分の画素を選択するための行選択パルスΦSEi-1,ΦSEi-2が印加される信号線であり、1行分の画素の選択トランジスタ15,16のゲート端子に電気的に接続される。FDリセット線34、転送線35、PDリセット線36、および選択線37,38は制御線群30を構成する。

【0040】

図3は、撮像部202の構成を示している。撮像部202の撮像面には、図2に示した構成の画素L1〜Lnが2次元の行列状に配列されている。これらの画素L1〜Lnは画素部を構成する。本実施形態では、撮像部202が有する全画素からなる領域を画素信号の読み出し対象領域とするが、撮像部202が有する全画素からなる領域の一部を読み出し対象領域として、以下で説明する画素信号の読み出しを行ってもよい。図2に示す画素の配列は一例であり、行数および列数は2以上であればよい。

【0041】

垂直走査回路1(制御部)は行単位で画素の駆動制御を行うため、FDリセットパルスΦRMi、行転送パルスΦTRi、PDリセットパルスΦRPDi、行選択パルスΦSEi-1,ΦSEi-2を、制御線群30(図2のFDリセット線34、転送線35、PDリセット線36、選択線37,38)を介して行毎に独立して制御する。行選択パルスΦSEi-1,ΦSEi-2によって選択された行の画素の信号は、列毎に設けられている垂直信号線31,32へ出力される。なお、電源電圧VDDを供給する電源線33は図3に示していない。

【0042】

列処理回路2、水平読み出し回路3、AD変換回路4、フレームメモリ5、および差分回路6は、画素内の選択トランジスタ15から垂直信号線31に出力される画素信号を読み出して処理する第1出力系統(第1の処理部)を構成する。列処理回路2は、列毎の垂直信号線31に接続され、画素L1〜Lnから出力された画素信号に対してクランプ動作や増幅動作を行う。列処理回路2は、動画信号に関して、光信号とリセット信号との差分処理(減算処理)も行う(CDS動作)。水平読み出し回路3は、画素信号を読み出す画素列を選択して、その画素列に係る画素信号を順次AD変換回路4へ出力することにより画素信号を読み出す。

【0043】

AD変換回路4は、水平読み出し回路3によって読み出された画素信号をAD変換する。AD変換後の画素信号は、第1動画信号出力端子から出力されるかフレームメモリ5に保持される。なお、フレームメモリ5は、後述する4つのフィールド(f-A,f-B,f-C,f-D)毎に画素信号を保持できるように構成されている。差分回路6は、AD変換回路4から出力された画素信号と、フレームメモリ5に保持されている画素信号との差分処理(減算処理)を行い、処理結果の信号を第1静止画信号出力端子から出力する。

【0044】

列処理回路22、水平読み出し回路23、AD変換回路24、フレームメモリ5、および差分回路7は、画素内の選択トランジスタ16から垂直信号線32に出力される画素信号を読み出して処理する第2出力系統(第2の処理部)を構成する。列処理回路22は、列毎の垂直信号線32に接続され、画素L1〜Lnから出力された画素信号に対してクランプ動作や増幅動作を行う。列処理回路22は、動画信号に関して、光信号とリセット信号との差分処理(減算処理)も行う(CDS動作)。水平読み出し回路23は、画素信号を読み出す画素列を選択して、その画素列に係る画素信号を順次AD変換回路24へ出力することにより画素信号を読み出す。

【0045】

AD変換回路24は、水平読み出し回路23によって読み出された画素信号をAD変換する。AD変換後の画素信号は、第2動画信号出力端子から出力されるかフレームメモリ5に保持される。差分回路7は、AD変換回路24から出力された画素信号と、フレームメモリ5に保持されている画素信号との差分処理(減算処理)を行い、処理結果の信号を第2静止画信号出力端子から出力する。

【0046】

上記のように本実施形態では、画素から画素信号を読み出して処理を行い、処理後の画素信号を出力するための2つの出力系統が設けられている。これら2つの出力系統を用いることにより、異なる複数行の画素から同時に画素信号を読み出して出力することが可能となる。

【0047】

設定部8は、撮像部202における画素信号の読み出しモードを、後述する第1読み出しモードまたは第2読み出しモードに設定し、設定した読み出しモードに応じた動作を行うよう、垂直走査回路1、水平読み出し回路3,23を制御する。

【0048】

次に、撮像部202の動作を説明する。撮像部202は、グローバルシャッタ動作およびローリングシャッタ動作が可能である。以下では、それぞれの動作を説明する。

【0049】

図4は、静止画撮影動作時に用いられるグローバルシャッタ動作を示している。図4の横軸は時間を示している。破線DL1および実線SL1は、行毎の画素信号の読み出しのタイミングを示している。また、図4には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図4には、水平読み出し回路の出力信号も示されている。以下では、動作の説明を簡単にするため、2つの出力系統のうち第1出力系統を使用した場合の動作を説明する。第2出力系統を使用した場合の動作も同様である。

【0050】

グローバルシャッタ動作による光信号蓄積(露光)が行われる前に、リセット信号読み出し期間において、電荷保持部12をリセットしたときの電荷保持部12の電位(リセットレベル)の読み出しが行われる。このリセット信号読み出し期間では、まず1行目のFDリセットパルスΦRM1が“L”レベルから“H”レベルになることで、1行目の画素L1のFDリセットトランジスタ13がオンになり、1行目の画素L1の電荷保持部12のリセットが行われる。さらに、1行目の行選択パルスΦSE1-1が“L”レベルから“H”レベルになることで、選択トランジスタ15がオンになり、リセットレベルがリセット信号として垂直信号線31に出力され、列処理回路2、水平読み出し回路3、AD変換回路4をそれぞれ介してフレームメモリ5へ出力されてフレームメモリ5に記憶される。第1の出力系統または第2の出力系統を用いて、以上の動作と同様の動作が1行目からn行目(最終行)まで行われ、リセット信号読み出し期間が終了する。

【0051】

続いて、全画素のPDリセットパルスφRPDiが“L”レベルから“H”レベルになることで、全画素のPDリセットトランジスタ17が同時にオンになり、全画素のフォトダイオード10が一括でリセットされる。その後、全画素のPDリセットパルスφRPDiが“H”レベルから“L”レベルになることで、全画素のPDリセットトランジスタ17が同時にオフになり、全画素の露光(電荷蓄積)が開始される。露光を開始してから所定の露光期間(蓄積期間)が経過すると、全画素の行転送パルスΦTRiが“L”レベルから“H”レベルになることで、露光期間中にフォトダイオード10に蓄積された信号電荷が電荷保持部12に一括で転送される。つまり、全画素の露光が同時に終了する。

【0052】

露光の終了後、光信号読み出し期間において、電荷保持部12の電位(光信号レベル)の読み出しが行われる。この光信号読み出し期間では、まず1行目の行選択パルスΦSE1-1が“L”レベルから“H”レベルになることで、選択トランジスタ15がオンになり、光信号レベルが光信号として垂直信号線31に出力され、列処理回路2、水平読み出し回路3、AD変換回路4をそれぞれ介して差分回路6へ出力される。

【0053】

差分回路6は、1行目の画素L1の光信号と、フレームメモリ5に保持されている1行目の画素L1のリセット信号との差分をとることにより、光信号成分のみを抽出し、ノイズが除去された静止画信号として第1静止画信号出力端子から画像処理部203へ出力する。第1の出力系統または第2の出力系統を用いて、以上の動作と同様の動作が1行目からn行目(最終行)まで行われ、光信号読み出し期間が終了し、1枚の静止画信号が画像処理部203へ出力される。

【0054】

図5は、リセット信号読み出し期間と光信号読み出し期間における画素信号をフィールドの単位で読み出す場合の動作を示している。図5に示す動作は、全画素を3つのフィールドに分けた場合の動作である。図5に示す例では、全画素は、1行目、4行目、7行目・・・の画素群からなる第1フィールド(f-A)と、2行目、5行目、8行目・・・の画素群からなる第2フィールド(f-B)と、3行目、6行目、9行目・・・の画素群からなる第3フィールド(f-C)に分割されている(図6参照)。

【0055】

図5に示す動作では、リセット信号読み出し期間において第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)の順にリセット信号の読み出しが行われ、光信号読み出し期間において第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)の順に光信号の読み出しが行われる。すなわち、図5に示す動作は、図4に示す動作に対して、画素信号を読み出す画素の順番が異なるだけである。このように、グローバルシャッタ動作においては、必ずしも1行目から最終行まで、行の並び順に画素信号を読み出す必要はない。以下では、静止画信号の読み出しに関しては、図5に示す動作と同様の動作によって読み出しを行う場合について説明する。

【0056】

図7は、動画表示動作時に用いられるローリングシャッタ動作を示している。図7の横軸は時間を示している。破線DL2は、行毎に画素をリセットするための走査のタイミングを示し、実線SL2は、行毎の光信号の読み出しのタイミングを示している。また、図7では、水平読み出し回路の出力信号も示されている。ローリングシャッタ動作では、全画素同時に制御信号を印加する動作はないため、全画素の行転送パルスΦTRiおよびPDリセットパルスΦRPDiは図示していない。ローリングシャッタ動作では、行毎に時間をずらしてリセット信号の読み出しと光信号の読み出しが行われる。以下では、動作の説明を簡単にするため、2つの出力系統のうち第1出力系統を使用した場合の動作を説明する。第2出力系統を使用した場合の動作も同様である。

【0057】

1行目の画素L1のリセットは、以下のようにして行われる。まず、1行目のリセットパルスΦRM1が“L”レベルから“H”レベルになることで、1行目の画素L1のFDリセットトランジスタ13がオンになり、1行目の画素L1の電荷保持部12のリセットが行われる。さらに、1行目の行転送パルスΦTR1が“L”レベルから“H”レベルになることで、1行目の画素L1の転送トランジスタ11がオンになり、転送トランジスタ11およびFDリセットトランジスタ13を介してフォトダイオード10のリセットが行われる。その後、1行目の行転送パルスΦTR1が“H”レベルから“L”レベルになることで、1行目の画素L1の転送トランジスタ11がオフになり、1行目の画素L1の露光(電荷蓄積)が開始される。

【0058】

露光の開始から所定の露光期間が経過した後に光信号の読み出しが行われる。光信号の読み出しに先立って、露光期間中に1行目のリセットパルスΦRM1が“L”レベルから“H”レベルになることで、1行目の画素L1のFDリセットトランジスタ13がオンになり、1行目の画素L1の電荷保持部12のリセットが行われる。さらに、1行目の選択パルスΦSE1-1が“L”レベルから“H”レベルになることで、1行目の画素L1の選択トランジスタ15がオンになり、リセットレベルがリセット信号として垂直信号線31に出力される。

【0059】

1行目の露光期間の終了タイミングで1行目の行転送パルスΦTR1が“L”レベルから“H”レベルになることで、1行目の画素L1の転送トランジスタ11がオンになり、露光期間中にフォトダイオード10に蓄積された信号電荷が電荷保持部12に転送される。このとき、1行目の選択パルスΦSE1-1が“H”レベルであり、1行目の画素L1の選択トランジスタ15がオンであるため、電荷保持部12に保持された信号電荷に基づく光信号レベルが光信号として垂直信号線31に出力される。

【0060】

列処理回路2は、垂直信号線31に出力された光信号とリセット信号との差分をとることにより、光信号成分のみを抽出し、ノイズが除去された動画信号を出力する。この動画信号は、水平読み出し回路3、AD変換回路4、差分回路6をそれぞれ介して画像処理部203へ出力される。第1の出力系統または第2の出力系統を用いて、以上の動作と同様の動作が1行目からn行目(最終行)まで行われ、1枚の動画信号が画像処理部203へ出力される。

【0061】

なお、動画表示動作時には、全画素から画素信号を読み出すのではなく、図8に示すように、画素信号を読み出す行を間引くことによって、1フレームの画素信号の読み出しに必要な期間を短くすることが可能となる。

【0062】

次に、撮像装置の動作を説明する。本実施形態の撮像装置は、静止画信号の読み出しに第1出力系統を使用し、動画信号の読み出しに第2出力系統を使用する第1読み出しモードと、静止画信号と動画信号の少なくとも一方の読み出しに第1出力系統および第2出力系統の両方を使用する第2読み出しモードとを選択して動作することが可能である。ユーザは、カメラ操作部208を操作することによって、読み出しモードを選択することが可能である。撮像部202に対する読み出しモードの設定は、カメラ制御部207から読み出しモードの指示を受けた駆動制御部205によって行われる。また、撮像部202の内部における読み出しモードの設定は、駆動制御部205からの指示を受けた設定部8によって行われる。設定部8による読み出しモードの設定を受けて、垂直走査回路1、水平読み出し回路3,23は、各読み出しモードに応じた画素信号の読み出しを行う。

【0063】

図9は、第1読み出しモードの動作を示している。図9の横軸は時間を示している。図9では、第1出力系統を使用した画素信号の読み出しのタイミングと、第2出力系統を使用した画素信号の読み出しのタイミングとが示されている。また、図9には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図9には、第1出力系統を構成する水平読み出し回路3の出力信号と、第2出力系統を構成する水平読み出し回路23の出力信号も示されている。

【0064】

図9に示す動作は、全画素を4つのフィールドに分けた場合の動作である。図9に示す例では、全画素は、1行目、5行目、9行目・・・の画素群からなる第1フィールド(f-A)と、2行目、6行目、10行目・・・の画素群からなる第2フィールド(f-B)と、3行目、7行目、11行目・・・の画素群からなる第3フィールド(f-C)と、4行目、8行目、12行目・・・の画素群からなる第4フィールド(f-D)に分割されている(図10参照)。

【0065】

図9に示す第1読み出しモードでは、静止画信号と動画信号が並列に、異なる出力系統を使用して読み出される。図9に示す動作では、第1出力系統を使用して、図5に示したグローバルシャッタ動作により、リセット信号読み出し期間に第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の順に静止画用のリセット信号の読み出しが行われ、光信号読み出し期間に第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の順に静止画用の光信号の読み出しが行われる。差分回路6は、AD変換回路4から出力された各フィールドの光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第1静止画信号出力端子から出力する。第1静止画信号出力端子から出力された各フィールドの静止画信号は、画像処理部203の第1画像処理部203aで処理され、1枚の静止画信号がメモリカード209に記録される。

【0066】

一方、図9に示す動作では、第2出力系統を使用して、図7に示したローリングシャッタ動作により、静止画信号の読み出しに関係のないフィールドの画素を用いて、画素を間引きしながら動画信号の読み出しが行われる。静止画用のリセット信号を読み出した後の画素では、電荷保持部12を再度リセットして動画用のリセット信号を読み出すことは好ましくない。このため、リセット信号読み出し期間では、静止画用のリセット信号を最後に読み出すフィールドである第4フィールド(f-D)の画素から静止画用のリセット信号が読み出される前に、第4フィールド(f-D)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。

【0067】

また、光信号読み出し期間では、静止画用の光信号を読み出していない画素の電荷保持部12をリセットすることは好ましくないため、静止画用の光信号を最初に読み出したフィールドである第1フィールド(f-A)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。第2動画信号出力端子から出力された動画信号は、画像処理部203の第2画像処理部203bで処理され、表示部204へ出力され、表示部204に画像(ライブビュー画像)が表示される。

【0068】

図9に示す動作では、静止画撮影の1サイクルの期間において、1枚の静止画信号と6枚の動画信号が得られる。静止画撮影の1サイクルの期間を処理の単位として、処理が繰り返し行われている様子が図9に示されている。

【0069】

上記のように、図9に示した第1読み出しモードでは、垂直走査回路1が出力する制御信号によって、全画素の静止画用の露光期間が同一となるように画素の露光が制御され、フィールドの単位で静止画信号および動画信号の読み出しが制御される。さらに、第1読み出しモードでは、垂直走査回路1が出力する制御信号によって、第1出力系統を使用してフィールドの単位で静止画信号を読み出す制御が行われ、第2出力系統を使用してフィールドの単位で動画信号を読み出す制御が行われる。

【0070】

図11は、第2読み出しモードの動作を示している。図11の横軸は時間を示している。図11では、第1出力系統を使用した画素信号の読み出しのタイミングと、第2出力系統を使用した画素信号の読み出しのタイミングとが示されている。また、図11には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図11には、第1出力系統を構成する水平読み出し回路3の出力信号と、第2出力系統を構成する水平読み出し回路23の出力信号も示されている。図11に示す動作は、図9に示す動作と同様に、全画素を4つのフィールドに分けた場合の動作である。

【0071】

図11に示す第2読み出しモードでは、第1出力系統および第2出力系統を使用して静止画信号が読み出され、第2出力系統のみを使用して動画信号が読み出される。図11に示す動作では、第1出力系統を使用して、図5に示したグローバルシャッタ動作により、リセット信号読み出し期間に第1フィールド(f-A)、第2フィールド(f-B)、第3フィールド(f-C)の順に静止画用のリセット信号の読み出しが行われ、光信号読み出し期間に第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の順に静止画用の光信号の読み出しが行われる。

【0072】

一方、図11に示す動作では、第2出力系統を使用して、リセット信号読み出し期間において、図7に示したローリングシャッタ動作により、第4フィールド(f-D)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。続いて、図5に示したグローバルシャッタ動作により、第4フィールド(f-D)の画素を用いて静止画用のリセット信号の読み出しが行われる。

【0073】

また、第2出力系統を使用して、光信号読み出し期間において、図5に示したグローバルシャッタ動作により、第1フィールド(f-A)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、図7に示したローリングシャッタ動作により、第1フィールド(f-A)の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。

【0074】

上記のようにして第2動画信号出力端子から出力された動画信号は、画像処理部203の第2画像処理部203bで処理され、表示部204へ出力され、表示部204に画像(ライブビュー画像)が表示される。

【0075】

また、差分回路6は、AD変換回路4から出力された第2フィールド(f-B)、第3フィールド(f-C)、第4フィールド(f-D)の光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第1静止画信号出力端子から出力する。差分回路7は、AD変換回路24から出力された第1フィールド(f-A)の光信号と、フレームメモリ5に保持されている第1フィールド(f-A)のリセット信号との差分をとった静止画信号を生成し、第2静止画信号出力端子から出力する。第1静止画信号出力端子および第2静止画信号出力端子から出力された各フィールドの静止画信号は、画像処理部203の第1画像処理部203aで処理され、1枚の静止画信号がメモリカード209に記録される。

【0076】

図11に示す動作では、静止画撮影の1サイクルの期間において、1枚の静止画信号と4枚の動画信号が得られる。静止画撮影の1サイクルの期間を処理の単位として、処理が繰り返し行われている様子が図11に示されている。

【0077】

上記のように、図11に示した第2読み出しモードでは、垂直走査回路1が出力する制御信号によって、全画素の静止画用の露光期間が同一となるように画素の露光が制御され、フィールドの単位で静止画信号および動画信号の読み出しが制御される。さらに、第2読み出しモードでは、垂直走査回路1が出力する制御信号によって、第1出力系統および第2出力系統を使用してフィールドの単位で静止画信号を読み出す制御が行われ、第2出力系統を使用してフィールドの単位で動画信号を読み出す制御が行われる。

【0078】

図11に示した第2読み出しモードでは、静止画用の複数フィールドのリセット信号と光信号を、2つの出力系統を用いて同時に読み出して出力することが可能なので、第1読み出しモードに比べて静止画撮影の1サイクル期間を短くすることができ、静止画撮影時間を短縮することが可能となる。前述したように、読み出しモードの設定は設定部8によって行われる。例えば、通常は第1読み出しモードが設定されるようにし、撮影スピードを優先する場合は第2読み出しモードが設定されるようにすればよい。

【0079】

次に、本実施形態の変形例を説明する。図12は、図11に示した動作とは異なる第2読み出しモードの動作を示している。図12の横軸は時間を示している。図12では、第1出力系統を使用した画素信号の読み出しのタイミングと、第2出力系統を使用した画素信号の読み出しのタイミングとが示されている。また、図12には、行転送パルスΦTRiおよびPDリセットパルスΦRPDiについて、全画素同時に印加されるタイミングが示されている。図12には、第1出力系統を構成する水平読み出し回路3の出力信号と、第2出力系統を構成する水平読み出し回路23の出力信号も示されている。

【0080】

図12に示す動作は、全画素を4つのフィールドに分けた場合の動作である。フィールドの分割形態は、図10に示した形態と同一である。図11に示した動作では、第2出力系統のみを使用して動画信号が読み出されているが、図12に示す動作では、動画信号を読み出すフィールドがさらに2分割されており、第1出力系統および第2出力系統を使用して各フィールドの動画信号が読み出される。

【0081】

図12に示す動作では、第1出力系統を使用して、リセット信号読み出し期間において、図7に示したローリングシャッタ動作により、第4フィールド(f-D)をさらに2分割したフィールドの一方であるフィールドf-D1の画素を用いて動画信号の読み出しが行われ、動画信号が第1動画信号出力端子から出力される。続いて、図5に示したグローバルシャッタ動作により、第1フィールド(f-A)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、フィールドf-D1の画素を用いて動画信号の読み出しが行われ、さらに第3フィールド(f-C)の画素を用いて静止画用のリセット信号の読み出しが行われる。

【0082】

また、第1出力系統を使用して、光信号読み出し期間において、図5に示したグローバルシャッタ動作により、第1フィールド(f-A)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、図7に示したローリングシャッタ動作により、第1フィールド(f-A)をさらに2分割したフィールドの一方であるフィールドf-A1の画素を用いて動画信号の読み出しが行われ、動画信号が第1動画信号出力端子から出力される。続いて、第3フィールド(f-C)の画素を用いて静止画用のリセット信号の読み出しが行われ、さらにフィールドf-A1の画素を用いて動画信号の読み出しが行われる。

【0083】

一方、図12に示す動作では、第2出力系統を使用して、リセット信号読み出し期間において、図7に示したローリングシャッタ動作により、第4フィールド(f-D)をさらに2分割したフィールドの他方であるフィールドf-D2の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。続いて、図5に示したグローバルシャッタ動作により、第2フィールド(f-B)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、フィールドf-D2の画素を用いて動画信号の読み出しが行われ、さらに第4フィールド(f-D)の画素を用いて静止画用のリセット信号の読み出しが行われる。

【0084】

また、第2出力系統を使用して、光信号読み出し期間において、図5に示したグローバルシャッタ動作により、第2フィールド(f-B)の画素を用いて静止画用のリセット信号の読み出しが行われる。続いて、図7に示したローリングシャッタ動作により、第1フィールド(f-A)をさらに2分割したフィールドの他方であるフィールドf-A2の画素を用いて動画信号の読み出しが行われ、動画信号が第2動画信号出力端子から出力される。続いて、第4フィールド(f-D)の画素を用いて静止画用のリセット信号の読み出しが行われ、さらにフィールドf-A2の画素を用いて動画信号の読み出しが行われる。

【0085】

上記のようにして第1動画信号出力端子および第2動画信号出力端子から出力された動画信号は、画像処理部203の第2画像処理部203bで処理され、表示部204へ出力され、表示部204に画像(ライブビュー画像)が表示される。

【0086】

また、差分回路6は、AD変換回路4から出力された第1フィールド(f-A)、第3フィールド(f-C)の光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第1静止画信号出力端子から出力する。差分回路7は、AD変換回路24から出力された第2フィールド(f-B)、第4フィールド(f-D)の光信号と、フレームメモリ5に保持されている、対応する各フィールドのリセット信号との差分をとった静止画信号を生成し、第2静止画信号出力端子から出力する。第1静止画信号出力端子および第2静止画信号出力端子から出力された各フィールドの静止画信号は、画像処理部203の第1画像処理部203aで処理され、1枚の静止画信号がメモリカード209に記録される。

【0087】

図12に示す動作では、静止画撮影の1サイクルの期間において、1枚の静止画信号と4枚の動画信号が得られる。静止画撮影の1サイクルの期間を処理の単位として、処理が繰り返し行われている様子が図12に示されている。

【0088】

図11に示した第2読み出しモードでは、静止画用の複数フィールドのリセット信号と光信号を、2つの出力系統を用いて同時に読み出して出力することに加えて、複数フィールドの動画信号を、2つの出力系統を用いて同時に読み出して出力することが可能なので、第1読み出しモードに比べて静止画撮影の1サイクル期間を短くすることができ、静止画撮影時間を短縮することが可能となる。

【0089】

なお、図9、図11、図12に示した動作では、静止画撮影の1サイクルの期間が複数回繰り返されているが、静止画撮影の1サイクルの期間の動作を1回だけ行ってもよい。また、静止画撮影の1サイクルの期間と次の静止画撮影の1サイクルの期間との間に、他の処理を行う期間を設けてもよい。また、フィールドの数や、画素信号を読み出すフィールドの順番、第1出力系統および第2出力系統で読み出すフィールドの組合せ等は適宜変更することが可能である。

【0090】

上述したように、本実施形態の第2読み出しモードでは、フィールド単位で静止画用のリセット信号および光信号の読み出しを行う複数の期間(フィールド毎に割り当てられた期間)のうちの少なくとも1つの期間において、第1出力系統および第2出力系統の両方を使用してフィールド単位でリセット信号および光信号を読み出すよう静止画信号の読み出しを制御することによって、静止画撮影時間を短縮することができる。

【0091】

以上、図面を参照して本発明の実施形態について詳述してきたが、具体的な構成は上記の実施形態に限られるものではなく、本発明の要旨を逸脱しない範囲の設計変更等も含まれる。

【符号の説明】

【0092】

1,300・・・垂直走査回路、2,22,350・・・列処理回路、3,23,400・・・水平読み出し回路、4,24・・・AD変換回路、5,600・・・フレームメモリ、6,7,700・・・差分回路、8・・・設定部、10,101・・・フォトダイオード、11,102・・・転送トランジスタ、12,103・・・電荷保持部、13,104・・・ FDリセットトランジスタ、14,105・・・増幅トランジスタ、15,16,106・・・選択トランジスタ、17,107・・・ PDリセットトランジスタ、100・・・画素、150・・・電流源、200・・・画素部、201・・・レンズ、202・・・撮像部、203・・・画像処理部、203a・・・第1画像処理部、203b・・・第2画像処理部、204・・・表示部、205・・・駆動制御部、206・・・レンズ制御部、207・・・カメラ制御部、208・・・カメラ操作部、209・・・メモリカード、500・・・ ADコンバータ、600・・・差分回路

【特許請求の範囲】

【請求項1】

光を信号電荷に変換し、信号電荷を蓄積する光電変換素子と、前記光電変換素子に蓄積された信号電荷を保持する電荷保持部と、前記光電変換素子に蓄積された信号電荷を前記電荷保持部に転送する転送部と、前記電荷保持部に保持された信号電荷に基づく画素信号を静止画信号または動画信号として出力する第1の出力部および第2の出力部とを備えた画素を2次元状に配列した画素部と、

前記第1の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第1の処理部と、

前記第2の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第2の処理部と、

読み出し対象領域を構成する全画素の静止画用の露光期間が同一となるように前記画素の露光を制御し、前記読み出し対象領域を構成する全画素を複数に分割したフィールドの単位で前記静止画信号および前記動画信号の読み出しを制御し、さらに、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御する制御部と、

を有することを特徴とする固体撮像装置。

【請求項2】

前記制御部は、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御することを特徴とする請求項1に記載の固体撮像装置。

【請求項3】

第1のモードおよび第2のモードの設定が可能な固体撮像装置であって、

前記制御部は、

前記第1のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の一方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の他方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御し、

前記第2のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御する

ことを特徴とする請求項1に記載の固体撮像装置。

【請求項4】

請求項1〜請求項3のいずれか一項に記載の固体撮像装置を備えた撮像装置。

【請求項1】

光を信号電荷に変換し、信号電荷を蓄積する光電変換素子と、前記光電変換素子に蓄積された信号電荷を保持する電荷保持部と、前記光電変換素子に蓄積された信号電荷を前記電荷保持部に転送する転送部と、前記電荷保持部に保持された信号電荷に基づく画素信号を静止画信号または動画信号として出力する第1の出力部および第2の出力部とを備えた画素を2次元状に配列した画素部と、

前記第1の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第1の処理部と、

前記第2の出力部から出力される前記静止画信号または前記動画信号を読み出して処理する第2の処理部と、

読み出し対象領域を構成する全画素の静止画用の露光期間が同一となるように前記画素の露光を制御し、前記読み出し対象領域を構成する全画素を複数に分割したフィールドの単位で前記静止画信号および前記動画信号の読み出しを制御し、さらに、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御する制御部と、

を有することを特徴とする固体撮像装置。

【請求項2】

前記制御部は、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御することを特徴とする請求項1に記載の固体撮像装置。

【請求項3】

第1のモードおよび第2のモードの設定が可能な固体撮像装置であって、

前記制御部は、

前記第1のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の一方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の他方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御し、

前記第2のモードが設定された場合には、1フィールドの前記静止画信号の読み出しを行う複数の期間のうちの少なくとも1つの期間において前記第1の出力部および前記第2の出力部の両方から前記フィールドの単位で前記静止画信号を読み出すよう前記静止画信号の読み出しを制御し、1フィールドの前記動画信号の読み出しを行う複数の期間において前記第1の出力部および前記第2の出力部の少なくとも一方から前記フィールドの単位で前記動画信号を読み出すよう前記動画信号の読み出しを制御する

ことを特徴とする請求項1に記載の固体撮像装置。

【請求項4】

請求項1〜請求項3のいずれか一項に記載の固体撮像装置を備えた撮像装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−151596(P2012−151596A)

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願番号】特願2011−7777(P2011−7777)

【出願日】平成23年1月18日(2011.1.18)

【出願人】(000000376)オリンパス株式会社 (11,466)

【Fターム(参考)】

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願日】平成23年1月18日(2011.1.18)

【出願人】(000000376)オリンパス株式会社 (11,466)

【Fターム(参考)】

[ Back to top ]