固体撮像装置及びその製造方法

【課題】フォトダイオードに蓄積された電荷をより正確に読み出す。

【解決手段】固体撮像装置は、半導体基板11と、半導体基板11内に設けられ、第1導電型の半導体層を有するフォトダイオード16と、フォトダイオード16上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層27と、半導体基板11に設けられ、フォトダイオード16に蓄積された電荷を浮遊拡散層に転送する転送トランジスタ20とを含む。シールド層27の上面は、半導体基板11の上面より高い。

【解決手段】固体撮像装置は、半導体基板11と、半導体基板11内に設けられ、第1導電型の半導体層を有するフォトダイオード16と、フォトダイオード16上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層27と、半導体基板11に設けられ、フォトダイオード16に蓄積された電荷を浮遊拡散層に転送する転送トランジスタ20とを含む。シールド層27の上面は、半導体基板11の上面より高い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、固体撮像装置及びその製造方法に関する。

【背景技術】

【0002】

近年、携帯電話のカメラ部品として需要が急増している。また、CMOSセンサーは、高画質化、高性能化が進んでおり、特に画素(ピクセル)数の増大要求を満たすための画素の微細化への要求は強い。この高画質化の要求に伴い、画素に発生する暗時ノイズや、白傷と呼ばれる画面上で白い点として認識される不良画素の低減要求が高まってきている。これは、フォトダイオード上のシリコン基板と層間絶縁膜との界面に形成された界面準位や、シリコン基板と層間絶縁膜との界面にトラップされた金属等の不純物によって暗電流やリーク電流が発生し、フォトダイオードが誤って白の信号を出してしまう不良モードであり、この不良の発生により画質は大きく損なわれることになる。

【0003】

これを防ぐには、フォトダイオードがシリコン基板と層間絶縁膜との界面に電気的に接触しないようにシリコン基板の少し深い領域にフォトダイオードを形成する手法が用いられる。この手法によって暗時ノイズや白傷が低減してCMOSセンサーの画質は大きく向上することになる。

【0004】

この構造を用いたフォトダイオードは、シリコンの中に埋め込まれた形になるので埋め込みフォトダイオードと呼ばれる。この構造を用いることで暗時ノイズや白傷は低減されることになったが、フォトダイオードの電荷蓄積拡散層自体は“埋め込み”の呼び名どおりシリコン基板表面からより深い位置に形成されることになる。

【0005】

フォトダイオードの電荷蓄積拡散層はフォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタの拡散層電極の一方を担っているので、フォトダイオードがシリコン基板表面から深い位置に形成されてしまうと、拡散層がゲート絶縁膜界面から垂直方向に距離をもって形成されたオフセット構造を有するトランジスタ構造になってしまう。このため、しきい値電圧の増大やオン電流の減少を招くことになり、トランジスタ特性としては劣化を招くことになる。その結果、フォトダイオードの電荷蓄積拡散層に蓄積された電荷が転送トランジスタをオンしても浮遊拡散層に出にくくなってしまうので、光センサーとしては性能が劣ったものになってしまう。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−91551号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

実施形態は、フォトダイオードに蓄積された電荷をより正確に読み出すことが可能な固体撮像装置及びその製造方法を提供する。

【課題を解決するための手段】

【0008】

実施形態に係る固体撮像装置は、半導体基板と、前記半導体基板内に設けられ、第1導電型の半導体層を有するフォトダイオードと、前記フォトダイオード上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層と、前記半導体基板に設けられ、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタとを具備し、前記シールド層の上面は、前記半導体基板の上面より高い。

【0009】

実施形態に係る固体撮像装置の製造方法は、半導体基板内に、第1導電型の半導体層を有するフォトダイオードを形成する工程と、前記フォトダイオード上方の半導体基板上に、エピタキシャル層を形成する工程と、前記エピタキシャル層に第2導電型の不純物を導入して、前記フォトダイオード上に上部又は全体が第2導電型の半導体層からなるシールド層を形成する工程と、前記半導体基板に、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタを形成する工程とを具備する。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態に係る固体撮像装置の断面図。

【図2】第1の実施形態に係る固体撮像装置の製造工程を示す断面図。

【図3】図2に続く固体撮像装置の製造工程を示す断面図。

【図4】図3に続く固体撮像装置の製造工程を示す断面図。

【図5】図4に続く固体撮像装置の製造工程を示す断面図。

【図6】図5に続く固体撮像装置の製造工程を示す断面図。

【図7】図6に続く固体撮像装置の製造工程を示す断面図。

【図8】図7に続く固体撮像装置の製造工程を示す断面図。

【図9】図8に続く固体撮像装置の製造工程を示す断面図。

【図10】図9に続く固体撮像装置の製造工程を示す断面図。

【図11】シールド層の他の構成例を示す断面図。

【図12】図10に続く固体撮像装置の製造工程を示す断面図。

【図13】図12に続く固体撮像装置の製造工程を示す断面図。

【図14】第2の実施形態に係る固体撮像装置の断面図。

【図15】第2の実施形態に係る固体撮像装置の製造工程を示す断面図。

【図16】図15に続く固体撮像装置の製造工程を示す断面図。

【図17】図16に続く固体撮像装置の製造工程を示す断面図。

【図18】図17に続く固体撮像装置の製造工程を示す断面図。

【図19】図18に続く固体撮像装置の製造工程を示す断面図。

【図20】図19に続く固体撮像装置の製造工程を示す断面図。

【図21】シールド層の他の構成例を示す断面図。

【図22】図20に続く固体撮像装置の製造工程を示す断面図。

【発明を実施するための形態】

【0011】

以下、実施形態について図面を参照して説明する。ただし、図面は模式的または概念的なものであり、各図面の寸法および比率などは必ずしも現実のものと同一とは限らない。以下に示す幾つかの実施形態は、本発明の技術思想を具体化するための装置および方法を例示したものであって、構成部品の形状、構造、配置などによって、本発明の技術思想が特定されるものではない。なお、以下の説明において、同一の機能及び構成を有する要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0012】

[第1の実施形態]

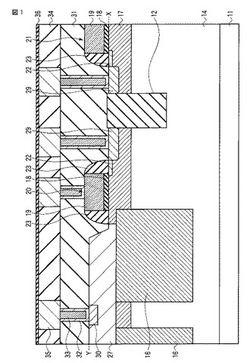

第1の実施形態に係る固体撮像装置は、CMOSセンサーから構成される。図1は、第1の実施形態に係る固体撮像装置の断面図である。

【0013】

固体撮像装置は、複数の画素からなる画素アレイを備えている。各画素は、入射した光を電荷に変換する光電変換素子(フォトダイオード)16、フォトダイオード16に蓄積された電荷を浮遊拡散層29に転送する転送トランジスタ20、及び浮遊拡散層29の電圧を信号レベルとして出力する増幅トランジスタ21などを備えている。

【0014】

図1において、符号“X”は、半導体基板(例えばシリコン基板)11の上面の位置を表している。シリコン基板11内には、隣接するフォトダイオード16を電気的に分離する分離層14が設けられている。分離層14は、P型半導体層から構成される。シリコン基板11の表面領域には、転送トランジスタ20及び増幅トランジスタ21用のチャネル領域17が設けられている。チャネル領域17は、P型半導体領域から構成される。転送トランジスタ20及び増幅トランジスタ21が駆動する際、転送トランジスタ20及び増幅トランジスタ21のチャネルがチャネル領域17に形成される。

【0015】

シリコン基板11内には、埋め込み型のフォトダイオード16が設けられている。すなわち、フォトダイオード16の上面は、シリコン基板11の上面Xより低くなっている。フォトダイオード16は、N型半導体領域から構成される。フォトダイオード16上には、P型半導体層からなるシールド層27が設けられている。シールド層27は、フォトダイオード16を保護する機能を有し、特に、暗時ノイズや白傷(暗電流やリーク電流に起因してフォトダイオードが誤って白の信号を出してしまう不良モード)を低減する機能を有する。そして、シールド層27の上面Yは、シリコン基板11の上面Xより高くなっている。

【0016】

このような構造を有することにより、フォトダイオード16上にシールド層27を備えつつ、フォトダイオード16をシリコン基板11の上面に近い位置に形成することが可能となる。フォトダイオード16は転送トランジスタ20のドレインとしても機能するため、転送トランジスタ20のゲート電極19とフォトダイオード16との垂直方向の距離を短くすることが可能となる。これにより、転送トランジスタ20のしきい値電圧及びオン電流を低減することができるため、転送トランジスタ20のトランジスタ特性を向上できる。

【0017】

(製造方法)

次に、図面を参照しながら第1の実施形態に係る固体撮像装置の製造方法について説明する。図2は、第1の実施形態に係る固体撮像装置の製造工程を示す断面図である。

【0018】

まず、半導体基板11、例えば、(100)面を表面に持ち、比抵抗1Ω・cm程度のP型シリコン基板11を準備する。このシリコン基板11内に、3000Å程度の深さの素子分離絶縁層12を形成する。素子分離絶縁層12は、例えばSTI(Shallow Trench Isolation)から構成される。シリコン基板11の表面領域のうち素子分離絶縁層12が形成されていない領域が、半導体素子が形成される素子領域となる。

【0019】

続いて、図3に示すように、例えばシリコン基板11の表面領域を酸化して、シリコン基板11の上面にシリコン酸化膜からなる保護膜13を形成する。続いて、シリコン基板11にP型不純物(例えばボロン(B))をイオン注入法によりドープし、1000℃程度の高温で数分間アニールを行う。これにより、隣接するフォトダイオードを電気的に分離し、かつP型半導体層からなる分離層14が形成される。分離層14は、後で形成されるフォトダイオードを全体的に包むことができるように、フォトダイオードよりも深い位置まで形成する必要がある。このため、P型不純物を多段階の加速電圧でドープし、さらにはP型不純物の十分な拡散距離が得られるようにアニール条件を調整して分離層14を形成する。

【0020】

続いて、リソグラフィ法を用いて、保護膜13上に、フォトダイオードを形成する領域以外を覆うレジスト層15を形成する。続いて、レジスト層15をマスクとして、分離層14にN型不純物(例えばリン(P))をイオン注入法によりドープする。そして、レジスト層15を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、分離層14内に、N型半導体領域からなるフォトダイオード16が形成される。フォトダイオード16は、例えば、シリコン基板11の上面からの深さが0.1μm以下になるように形成される。フォトダイオード16は、入射した光を電荷に変換する光電変換素子である。

【0021】

続いて、図4に示すように、シリコン基板11の画素領域にP型不純物(例えばボロン(B))をイオン注入法によりドープし、シリコン基板11の表面領域に、後で形成されるMOSFET用のチャネル領域17を形成する。チャネル領域17の不純物濃度を制御することで、MOSFETのしきい値電圧を制御することができる。この工程により、フォトダイオード16の上部にもP型半導体領域(チャネル領域17)が形成される。その後、保護膜13をエッチングする。

【0022】

続いて、図5に示すように、ゲート絶縁膜18を形成し、ゲート絶縁膜18上にゲート電極材料、例えば多結晶シリコン層19を1500Å程度堆積する。続いて、多結晶シリコン層19にN型不純物(例えばリン(P))をイオン注入法によりドープして多結晶シリコン層19をN型導電層にする。続いて、例えばリソグラフィ法及びRIE(Reactive Ion Etching)法を用いて、導電層19及びゲート絶縁膜18を所望の形状に加工して、各画素を構成するMOSFET(転送トランジスタ20及び増幅トランジスタ21などを含む)のゲート電極19を形成する。転送トランジスタ20は、フォトダイオード16に蓄積された信号電荷を浮遊拡散層に転送するためのMOSFETである。増幅トランジスタ21は、浮遊拡散層の電圧を増幅して信号レベルとして出力するためのMOSFETである。

【0023】

続いて、図6に示すように、リソグラフィ法を用いて、シリコン基板11上及びゲート電極19上に、MOSFETのLDD(Lightly Doped Drain)領域を形成する領域以外を覆うレジスト層(図示せず)を形成した後、チャネル領域17にN型不純物(例えばリン(P))をイオン注入法によりドープする。そして、レジスト層を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、転送トランジスタ20のソース用のLDD領域22、及び増幅トランジスタ21のソース及びドレイン用のLDD領域22が形成される。

【0024】

続いて、装置全面に絶縁膜(例えばシリコン窒化膜)を堆積し、例えばRIE法を用いてシリコン窒化膜をエッチバックする。これにより、MOSFETの側壁23が形成される。

【0025】

続いて、図7に示すように、装置全面に保護膜24(例えばTEOS(Tetra-Ethyl-Ortho-Silicate)膜)を厚さ5nm程度で堆積し、続いて、TEOS膜24上に、保護膜25(例えばシリコン窒化膜)を厚さ30nm程度で堆積する。続いて、リソグラフィ法を用いて、シリコン窒化膜25上に、フォトダイオード16の上方を露出するレジスト層26を形成する。続いて、レジスト層26をマスクとして例えばRIE法を用いて、シリコン窒化膜25をエッチングする。その後、レジスト層26を剥離する。

【0026】

続いて、図8に示すように、シリコン窒化膜25をマスクとして例えば希フッ酸を用いてTEOS膜24をウェットエッチングし、フォトダイオード16上方のシリコン基板11の上面を露出させる。

【0027】

本実施形態では、シリコン基板11上にTEOS膜24を形成している。そして、シリコン基板11の上面を露出させる工程では、希フッ酸を用いたウェットエッチングを行っている。このため、フォトダイオード16上方のシリコン基板11の上面を露出させる際にシリコン基板11の上面がRIE工程に晒されないので、シリコン基板11に界面準位や結晶欠陥が形成されるのを抑制することができる。なお、保護膜24及び25に替えてレジスト層を形成してもよい。この場合は、リソグラフィ法を用いてレジスト層を保護膜24及び25と同じ形状に加工する。

【0028】

続いて、図9に示すように、シリコン上にのみピタキシャル層が成長する選択性エピタキシャル成長法を装置全面に施し、フォトダイオード16上方のシリコン基板11上に厚さ1200Å程度のシリコン層27をエピタキシャル成長させる。この際、シリコン基板11の結晶欠陥が少ないため、結晶性の良好なエピタキシャル層を形成できる。その後、例えば高温のリン酸(H2PO3)を用いてシリコン窒化膜25のみウェットエッチングした後、例えば希フッ酸を用いてTEOS膜24をウェットエッチングする。

【0029】

続いて、図10に示すように、リソグラフィ法を用いて、シリコン層(エピタキシャル層)27のみを露出するレジスト層28を形成する。続いて、レジスト層28をマスクとしてエピタキシャル層27にP型不純物(例えばボロン(B))をイオン注入法によりドープする。そして、レジスト層28を剥離した後、P型不純物を活性化するためのアニールを行う。これにより、フォトダイオード16上に、P型半導体層からなるシールド層27が形成される。

【0030】

なお、図10では、フォトダイオード16上のシールド層27全体がP型半導体層で構成されているが、この構成に限定されるものではない。図11に示すように、イオン注入の条件によっては、エピタキシャル層27の上部にのみP型不純物がドープされることで、シールド層27の上部がP型半導体層27Aで構成され、シールド層27の下部がシリコン層27Bで構成されていてもよい。この場合は、フォトダイオード16とシリコン層27Bとの間には、チャネル領域17として形成されたP型半導体層が設けられる。

【0031】

続いて、図12に示すように、リソグラフィ法を用いてシールド層27を覆うレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシリコン基板11に、高濃度のN型不純物(例えばリン(P))をイオン注入法によりドープする。その後、レジスト層を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、MOSFETのソース領域及びドレイン領域として、LDD領域22より不純物濃度の高いN+型拡散領域29が形成される。N+型拡散領域29には、転送トランジスタ20のソース領域、増幅トランジスタ21のソース領域及びドレイン領域が含まれる。

【0032】

転送トランジスタ20のソース領域29は、浮遊拡散層として機能する。フォトダイオード16に蓄積された信号電荷は、転送トランジスタ20によって浮遊拡散層に転送される。その後、浮遊拡散層の電圧が増幅トランジスタ21よって信号レベルとして出力される。

【0033】

続いて、リソグラフィ法を用いて所望の形状を有するレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシールド層27に、高濃度のP型不純物(例えばボロン(B))をイオン注入法によりドープする。これにより、シールド層27の表面領域に、シールド層27とオーミックかつ良好なコンタクトをとるためのP+型拡散領域30が形成される。P+型拡散領域30は、例えば、隣接する画素のフォトダイオード間の境界部に形成される。続いて、レジスト層を剥離した後、不純物を活性化するためのアニールを行う。これにより、固体撮像装置の下地が完成する。

【0034】

続いて、図13に示すように、装置全面に第1の層間絶縁層31(例えばTEOS膜)を堆積し、CMP(Chemical Mechanical Polishing)法を用いて層間絶縁層31を平坦化する。続いて、例えばリソグラフィ法及びRIE法を用いて、P+型拡散領域30及びMOSFETの電極(ゲート、ソース、ドレイン)を露出するコンタクト孔を形成する。続いて、コンタクト孔内に、例えばチタン(Ti)/窒化チタン(TiN)の2層からなるバリア膜32を例えばスパッタ法を用いて形成する。続いて、例えばCVD(Chemical Vapor Deposition)法を用いてコンタクト孔内を導電体33(例えばタングステン(W))で埋め込み、上層の余分なW及びTi/TiNをCMP法を用いて除去する。これにより、P+型拡散領域30及びMOSFETの電極に電気的に接続されたコンタクトプラグ33が形成される。

【0035】

続いて、図1に示すように、装置全面に第2の層間絶縁層34(例えばTEOS膜)を堆積し、CMP法を用いて層間絶縁層34を平坦化する。続いて、例えばダマシン法を用いてコンタクトプラグ33に電気的に接続された配線層35(例えば銅(Cu)配線)を形成する。続いて、銅(Cu)の拡散を抑える保護膜36(例えばシリコン窒化膜)を装置全面に堆積する。このようにして、第1の実施形態に係る固体撮像装置(具体的には、固体撮像装置の画素アレイ)が完成する。

【0036】

(効果)

以上詳述したように第1の実施形態では、固体撮像装置(CMOSセンサー)は、シリコン基板11内に設けられ、N型半導体層を有するフォトダイオード16と、フォトダイオード16上に設けられ、上部又は全体がP型半導体層からなるシールド層27と、シリコン基板11に設けられ、フォトダイオード16に蓄積された電荷を浮遊拡散層に転送する転送トランジスタ20とを具備している。そして、シールド層27の上面Yは、シリコン基板11の上面Xより高くなっている。

【0037】

従って第1の実施形態によれば、埋め込み型のフォトダイオード16をシリコン基板11の上面近くに形成することが可能となる。これにより、転送トランジスタ20のゲート電極19と、転送トランジスタ20の片側の拡散層としての役目も果たしているフォトダイオード16との垂直方向の距離を縮めることができる。この結果、転送トランジスタ20のしきい値電圧を低下させることができ、またオン電流を増大させることができる。さらに、フォトダイオード16に蓄積された電荷をより正確に読み出すことが可能となる。

【0038】

また、フォトダイオード16内に界面準位や結晶欠陥が形成されるのを抑制することができる。これにより、フォトダイオード16のノイズを低減することが可能となる。この結果、CMOSセンサーの画質を向上させることができる。

【0039】

また、シールド層27を形成する工程において、不純物が拡散する分の距離をエピタキシャル層の膜厚を厚くすることで確保できる。このため、シールド層27及びフォトダイオード16の不純物濃度を高くすることができ、不純物濃度に対するデバイス設計の自由度が増す。これにより、シールド層27の不純物濃度を高くすればシールド性が増して界面準位起因のノイズや白傷を低減させることができ、フォトダイオード16の不純物濃度を高くすればフォトダイオード16に蓄積できる電荷量を増やすことができる。結果として、光が照射された際の電気信号量を増やすことができ、高性能なCMOSセンサーを提供することが可能になる。

【0040】

なお、本実施形態では、シリコン基板がP型、フォトダイオード16のキャリア蓄積層がN型の場合について説明しているが、半導体の導電型が反転した画素の構造でも同様な効果を得ることができる。

【0041】

また、本実施形態では、半導体基板とシールド層を形成するエピタキシャル層とをシリコン(Si)で形成しているが、これがガリウム(Ge)やGaAsなど他の半導体材料でも同様な効果を得ることができる。さらには、半導体基板とエピタキシャル層とが異なる半導体材料、例えばシリコン基板上にSiGe層を形成するようなヘテロ接合の形成条件であっても、基板と堆積膜との格子定数が破綻を来さない組み合わせでありかつシールド層が界面準位が形成される基板界面部を包み込む形で形成されていれば問題なく上記と同等な効果が得られる。

【0042】

[第2の実施形態]

第2の実施形態は、シールド層を構成する半導体層としてMOSFETのゲート電極を構成する半導体層と同じ半導体材料を用いている。そして、ゲート電極用の半導体層を形成する工程と同時にシールド層用の半導体層を形成するようにしている。

【0043】

図14は、第2の実施形態に係る固体撮像装置の断面図である。第1の実施形態と同様に、シリコン基板11内には、埋め込み型のフォトダイオード16が設けられている。すなわち、フォトダイオード16の上面は、シリコン基板11の上面Xより低くなっている。フォトダイオード16上には、シールド層27が設けられている。シールド層27の上面Yは、シリコン基板11の上面Xより高くなっている。また、シールド層27を構成する半導体層としては、MOSFET(転送トランジスタ20及び増幅トランジスタ21を含む)のゲート電極19を構成する半導体層と同じ半導体材料が用いられる。

【0044】

次に、図面を参照しながら第2の実施形態に係る固体撮像装置の製造方法について説明する。第1の実施形態の図4までの製造工程は、第2の実施形態も同じ工程を経る。

【0045】

続いて、図15に示すように、保護膜13をエッチングした後、ゲート絶縁膜18を形成する。続いて、リソグラフィ法を用いてシールド層27が形成される領域以外を覆うレジスト層(図示せず)を形成した後、レジスト層をマスクとして例えば希フッ酸を用いてゲート絶縁膜18をウェットエッチングする。これにより、シールド層27が形成される領域のシリコン基板11の上面が露出される。その後、レジストを剥離する。

【0046】

続いて、図16に示すように、例えばCVD法を用いて、装置全面に、MOSFETのゲート電極材料としての多結晶シリコン層19を1500Å程度堆積する。続いて、図17に示すように、リソグラフィ法を用いてシールド層27が形成される領域を覆うレジスト層40を形成する。続いて、レジスト層40をマスクとして多結晶シリコン層19にN型不純物(例えばリン(P))をイオン注入法によりドープして多結晶シリコン層19を部分的にN型導電層にする。その後、レジスト層40を剥離する。

【0047】

続いて、図18に示すように、リソグラフィ法を用いて、各画素を構成するMOSFETのゲート電極が形成される領域、及びシールド層27が形成される領域を覆うレジスト層(図示せず)を多結晶シリコン層19上に形成し、レジスト層をマスクとして例えばRIE法を用いて多結晶シリコン層19をパターニングする。これにより、各画素を構成するMOSFET(転送トランジスタ20及び増幅トランジスタ21などを含む)のゲート電極19が形成されると共に、シールド層となる多結晶シリコン層27が形成される。

【0048】

続いて、図19に示すように、リソグラフィ法を用いて、MOSFETのLDD領域を形成する領域以外を覆うレジスト層(図示せず)を形成した後、チャネル領域17にN型不純物(例えばリン(P))をイオン注入法によりドープする。そして、レジスト層を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、転送トランジスタ20のソース用のLDD領域22、及び増幅トランジスタ21のソース及びドレイン用のLDD領域22が形成される。

【0049】

続いて、装置全面に絶縁膜(例えばTEOS膜)を堆積し、例えばRIE法を用いてTEOS膜をエッチバックする。これにより、MOSFETの側壁23が形成される。また、転送トランジスタ20のゲート電極19と多結晶シリコン層27との間は、側壁23で埋め込まれる。

【0050】

続いて、図20に示すように、リソグラフィ法を用いて多結晶シリコン層27のみを露出するレジスト層41を形成する。続いて、レジスト層41をマスクとして多結晶シリコン層27にP型不純物(例えばボロン(B))をイオン注入法によりドープする。そして、レジスト層41を剥離した後、P型不純物を活性化するためのアニールを行う。これにより、フォトダイオード16上に、P型半導体層からなるシールド層27が形成される。

【0051】

なお、図20では、フォトダイオード16上のシールド層27全体がP型半導体層で構成されているが、この構成に限定されるものではない。図21に示すように、イオン注入の条件によっては、多結晶シリコン層27の上部にのみP型不純物がドープされることで、シールド層27の上部がP型半導体層27Aで構成され、シールド層27の下部が多結晶シリコン層27Bで構成されていてもよい。この場合は、フォトダイオード16と多結晶シリコン層27Bとの間には、チャネル領域17として形成されたP型半導体層が設けられる。

【0052】

続いて、図22に示すように、リソグラフィ法を用いてシールド層27を覆うレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシリコン基板11に、高濃度のN型不純物(例えばリン(P))をイオン注入法によりドープする。その後、レジスト層を剥離する。これにより、MOSFETのソース領域及びドレイン領域として、LDD領域22より不純物濃度の高いN+型拡散領域29が形成される。N+型拡散領域29には、転送トランジスタ20のソース領域、増幅トランジスタ21のソース領域及びドレイン領域が含まれる。

【0053】

続いて、リソグラフィ法を用いて所望の形状を有するレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシールド層27に、高濃度のP型不純物(例えばボロン(B))をイオン注入法によりドープする。これにより、シールド層27の表面領域に、シールド層27とオーミックかつ良好なコンタクトをとるためのP+型拡散領域30が形成される。P+型拡散領域30は、例えば、隣接する画素のフォトダイオード間の境界部に形成される。続いて、レジスト層を剥離した後、不純物を活性化するためのアニールを行う。これにより、固体撮像装置の下地が完成する。

【0054】

続いて、図14に示すように、第1の層間絶縁層31、バリア膜32、コンタクトプラグ33、第2の層間絶縁層34、配線層35、及び保護膜36を形成する。これらの製造工程は、第1の実施形態と同じである。このようにして、第2の実施形態に係る固体撮像装置(具体的には、固体撮像装置の画素アレイ)が完成する。

【0055】

(効果)

以上詳述したように第2の実施形態によれば、シールド層27の上面を、シリコン基板11の上面より高くしているため、埋め込み型のフォトダイオード16をシリコン基板11の上面近くに形成することが可能となる。これにより、転送トランジスタ20のゲート電極19とフォトダイオード16との垂直方向の距離を縮めることができる。この結果、転送トランジスタ20のしきい値電圧を低下させることができ、またオン電流を増大させることができる。その他の効果も第1の実施形態と同じである。

【0056】

また、MOSFETのゲート電極を形成する工程を利用してシールド層27を形成することができる。これにより、シールド層27を形成するための製造工程数が抑制でき、また製造コストが高くなるのを抑制できる。なお、シールド層27用のシリコン層は、ゲート電極とは別の工程で形成するようにしてもよい。

【0057】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0058】

11…半導体基板、12…素子分離絶縁層、13…保護膜、14…分離層、15,26,28,40,41…レジスト層、16…フォトダイオード、17…チャネル領域、18…ゲート絶縁膜、19…ゲート電極、20…転送トランジスタ、21…増幅トランジスタ、22…LDD領域、23…側壁、24…保護膜、25…保護膜、27…シールド層、29…ソース/ドレイン領域、30…P+型拡散領域、31,34…層間絶縁層、32…バリア膜、33…コンタクトプラグ、35…配線層、36…保護膜。

【技術分野】

【0001】

本発明の実施形態は、固体撮像装置及びその製造方法に関する。

【背景技術】

【0002】

近年、携帯電話のカメラ部品として需要が急増している。また、CMOSセンサーは、高画質化、高性能化が進んでおり、特に画素(ピクセル)数の増大要求を満たすための画素の微細化への要求は強い。この高画質化の要求に伴い、画素に発生する暗時ノイズや、白傷と呼ばれる画面上で白い点として認識される不良画素の低減要求が高まってきている。これは、フォトダイオード上のシリコン基板と層間絶縁膜との界面に形成された界面準位や、シリコン基板と層間絶縁膜との界面にトラップされた金属等の不純物によって暗電流やリーク電流が発生し、フォトダイオードが誤って白の信号を出してしまう不良モードであり、この不良の発生により画質は大きく損なわれることになる。

【0003】

これを防ぐには、フォトダイオードがシリコン基板と層間絶縁膜との界面に電気的に接触しないようにシリコン基板の少し深い領域にフォトダイオードを形成する手法が用いられる。この手法によって暗時ノイズや白傷が低減してCMOSセンサーの画質は大きく向上することになる。

【0004】

この構造を用いたフォトダイオードは、シリコンの中に埋め込まれた形になるので埋め込みフォトダイオードと呼ばれる。この構造を用いることで暗時ノイズや白傷は低減されることになったが、フォトダイオードの電荷蓄積拡散層自体は“埋め込み”の呼び名どおりシリコン基板表面からより深い位置に形成されることになる。

【0005】

フォトダイオードの電荷蓄積拡散層はフォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタの拡散層電極の一方を担っているので、フォトダイオードがシリコン基板表面から深い位置に形成されてしまうと、拡散層がゲート絶縁膜界面から垂直方向に距離をもって形成されたオフセット構造を有するトランジスタ構造になってしまう。このため、しきい値電圧の増大やオン電流の減少を招くことになり、トランジスタ特性としては劣化を招くことになる。その結果、フォトダイオードの電荷蓄積拡散層に蓄積された電荷が転送トランジスタをオンしても浮遊拡散層に出にくくなってしまうので、光センサーとしては性能が劣ったものになってしまう。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−91551号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

実施形態は、フォトダイオードに蓄積された電荷をより正確に読み出すことが可能な固体撮像装置及びその製造方法を提供する。

【課題を解決するための手段】

【0008】

実施形態に係る固体撮像装置は、半導体基板と、前記半導体基板内に設けられ、第1導電型の半導体層を有するフォトダイオードと、前記フォトダイオード上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層と、前記半導体基板に設けられ、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタとを具備し、前記シールド層の上面は、前記半導体基板の上面より高い。

【0009】

実施形態に係る固体撮像装置の製造方法は、半導体基板内に、第1導電型の半導体層を有するフォトダイオードを形成する工程と、前記フォトダイオード上方の半導体基板上に、エピタキシャル層を形成する工程と、前記エピタキシャル層に第2導電型の不純物を導入して、前記フォトダイオード上に上部又は全体が第2導電型の半導体層からなるシールド層を形成する工程と、前記半導体基板に、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタを形成する工程とを具備する。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態に係る固体撮像装置の断面図。

【図2】第1の実施形態に係る固体撮像装置の製造工程を示す断面図。

【図3】図2に続く固体撮像装置の製造工程を示す断面図。

【図4】図3に続く固体撮像装置の製造工程を示す断面図。

【図5】図4に続く固体撮像装置の製造工程を示す断面図。

【図6】図5に続く固体撮像装置の製造工程を示す断面図。

【図7】図6に続く固体撮像装置の製造工程を示す断面図。

【図8】図7に続く固体撮像装置の製造工程を示す断面図。

【図9】図8に続く固体撮像装置の製造工程を示す断面図。

【図10】図9に続く固体撮像装置の製造工程を示す断面図。

【図11】シールド層の他の構成例を示す断面図。

【図12】図10に続く固体撮像装置の製造工程を示す断面図。

【図13】図12に続く固体撮像装置の製造工程を示す断面図。

【図14】第2の実施形態に係る固体撮像装置の断面図。

【図15】第2の実施形態に係る固体撮像装置の製造工程を示す断面図。

【図16】図15に続く固体撮像装置の製造工程を示す断面図。

【図17】図16に続く固体撮像装置の製造工程を示す断面図。

【図18】図17に続く固体撮像装置の製造工程を示す断面図。

【図19】図18に続く固体撮像装置の製造工程を示す断面図。

【図20】図19に続く固体撮像装置の製造工程を示す断面図。

【図21】シールド層の他の構成例を示す断面図。

【図22】図20に続く固体撮像装置の製造工程を示す断面図。

【発明を実施するための形態】

【0011】

以下、実施形態について図面を参照して説明する。ただし、図面は模式的または概念的なものであり、各図面の寸法および比率などは必ずしも現実のものと同一とは限らない。以下に示す幾つかの実施形態は、本発明の技術思想を具体化するための装置および方法を例示したものであって、構成部品の形状、構造、配置などによって、本発明の技術思想が特定されるものではない。なお、以下の説明において、同一の機能及び構成を有する要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0012】

[第1の実施形態]

第1の実施形態に係る固体撮像装置は、CMOSセンサーから構成される。図1は、第1の実施形態に係る固体撮像装置の断面図である。

【0013】

固体撮像装置は、複数の画素からなる画素アレイを備えている。各画素は、入射した光を電荷に変換する光電変換素子(フォトダイオード)16、フォトダイオード16に蓄積された電荷を浮遊拡散層29に転送する転送トランジスタ20、及び浮遊拡散層29の電圧を信号レベルとして出力する増幅トランジスタ21などを備えている。

【0014】

図1において、符号“X”は、半導体基板(例えばシリコン基板)11の上面の位置を表している。シリコン基板11内には、隣接するフォトダイオード16を電気的に分離する分離層14が設けられている。分離層14は、P型半導体層から構成される。シリコン基板11の表面領域には、転送トランジスタ20及び増幅トランジスタ21用のチャネル領域17が設けられている。チャネル領域17は、P型半導体領域から構成される。転送トランジスタ20及び増幅トランジスタ21が駆動する際、転送トランジスタ20及び増幅トランジスタ21のチャネルがチャネル領域17に形成される。

【0015】

シリコン基板11内には、埋め込み型のフォトダイオード16が設けられている。すなわち、フォトダイオード16の上面は、シリコン基板11の上面Xより低くなっている。フォトダイオード16は、N型半導体領域から構成される。フォトダイオード16上には、P型半導体層からなるシールド層27が設けられている。シールド層27は、フォトダイオード16を保護する機能を有し、特に、暗時ノイズや白傷(暗電流やリーク電流に起因してフォトダイオードが誤って白の信号を出してしまう不良モード)を低減する機能を有する。そして、シールド層27の上面Yは、シリコン基板11の上面Xより高くなっている。

【0016】

このような構造を有することにより、フォトダイオード16上にシールド層27を備えつつ、フォトダイオード16をシリコン基板11の上面に近い位置に形成することが可能となる。フォトダイオード16は転送トランジスタ20のドレインとしても機能するため、転送トランジスタ20のゲート電極19とフォトダイオード16との垂直方向の距離を短くすることが可能となる。これにより、転送トランジスタ20のしきい値電圧及びオン電流を低減することができるため、転送トランジスタ20のトランジスタ特性を向上できる。

【0017】

(製造方法)

次に、図面を参照しながら第1の実施形態に係る固体撮像装置の製造方法について説明する。図2は、第1の実施形態に係る固体撮像装置の製造工程を示す断面図である。

【0018】

まず、半導体基板11、例えば、(100)面を表面に持ち、比抵抗1Ω・cm程度のP型シリコン基板11を準備する。このシリコン基板11内に、3000Å程度の深さの素子分離絶縁層12を形成する。素子分離絶縁層12は、例えばSTI(Shallow Trench Isolation)から構成される。シリコン基板11の表面領域のうち素子分離絶縁層12が形成されていない領域が、半導体素子が形成される素子領域となる。

【0019】

続いて、図3に示すように、例えばシリコン基板11の表面領域を酸化して、シリコン基板11の上面にシリコン酸化膜からなる保護膜13を形成する。続いて、シリコン基板11にP型不純物(例えばボロン(B))をイオン注入法によりドープし、1000℃程度の高温で数分間アニールを行う。これにより、隣接するフォトダイオードを電気的に分離し、かつP型半導体層からなる分離層14が形成される。分離層14は、後で形成されるフォトダイオードを全体的に包むことができるように、フォトダイオードよりも深い位置まで形成する必要がある。このため、P型不純物を多段階の加速電圧でドープし、さらにはP型不純物の十分な拡散距離が得られるようにアニール条件を調整して分離層14を形成する。

【0020】

続いて、リソグラフィ法を用いて、保護膜13上に、フォトダイオードを形成する領域以外を覆うレジスト層15を形成する。続いて、レジスト層15をマスクとして、分離層14にN型不純物(例えばリン(P))をイオン注入法によりドープする。そして、レジスト層15を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、分離層14内に、N型半導体領域からなるフォトダイオード16が形成される。フォトダイオード16は、例えば、シリコン基板11の上面からの深さが0.1μm以下になるように形成される。フォトダイオード16は、入射した光を電荷に変換する光電変換素子である。

【0021】

続いて、図4に示すように、シリコン基板11の画素領域にP型不純物(例えばボロン(B))をイオン注入法によりドープし、シリコン基板11の表面領域に、後で形成されるMOSFET用のチャネル領域17を形成する。チャネル領域17の不純物濃度を制御することで、MOSFETのしきい値電圧を制御することができる。この工程により、フォトダイオード16の上部にもP型半導体領域(チャネル領域17)が形成される。その後、保護膜13をエッチングする。

【0022】

続いて、図5に示すように、ゲート絶縁膜18を形成し、ゲート絶縁膜18上にゲート電極材料、例えば多結晶シリコン層19を1500Å程度堆積する。続いて、多結晶シリコン層19にN型不純物(例えばリン(P))をイオン注入法によりドープして多結晶シリコン層19をN型導電層にする。続いて、例えばリソグラフィ法及びRIE(Reactive Ion Etching)法を用いて、導電層19及びゲート絶縁膜18を所望の形状に加工して、各画素を構成するMOSFET(転送トランジスタ20及び増幅トランジスタ21などを含む)のゲート電極19を形成する。転送トランジスタ20は、フォトダイオード16に蓄積された信号電荷を浮遊拡散層に転送するためのMOSFETである。増幅トランジスタ21は、浮遊拡散層の電圧を増幅して信号レベルとして出力するためのMOSFETである。

【0023】

続いて、図6に示すように、リソグラフィ法を用いて、シリコン基板11上及びゲート電極19上に、MOSFETのLDD(Lightly Doped Drain)領域を形成する領域以外を覆うレジスト層(図示せず)を形成した後、チャネル領域17にN型不純物(例えばリン(P))をイオン注入法によりドープする。そして、レジスト層を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、転送トランジスタ20のソース用のLDD領域22、及び増幅トランジスタ21のソース及びドレイン用のLDD領域22が形成される。

【0024】

続いて、装置全面に絶縁膜(例えばシリコン窒化膜)を堆積し、例えばRIE法を用いてシリコン窒化膜をエッチバックする。これにより、MOSFETの側壁23が形成される。

【0025】

続いて、図7に示すように、装置全面に保護膜24(例えばTEOS(Tetra-Ethyl-Ortho-Silicate)膜)を厚さ5nm程度で堆積し、続いて、TEOS膜24上に、保護膜25(例えばシリコン窒化膜)を厚さ30nm程度で堆積する。続いて、リソグラフィ法を用いて、シリコン窒化膜25上に、フォトダイオード16の上方を露出するレジスト層26を形成する。続いて、レジスト層26をマスクとして例えばRIE法を用いて、シリコン窒化膜25をエッチングする。その後、レジスト層26を剥離する。

【0026】

続いて、図8に示すように、シリコン窒化膜25をマスクとして例えば希フッ酸を用いてTEOS膜24をウェットエッチングし、フォトダイオード16上方のシリコン基板11の上面を露出させる。

【0027】

本実施形態では、シリコン基板11上にTEOS膜24を形成している。そして、シリコン基板11の上面を露出させる工程では、希フッ酸を用いたウェットエッチングを行っている。このため、フォトダイオード16上方のシリコン基板11の上面を露出させる際にシリコン基板11の上面がRIE工程に晒されないので、シリコン基板11に界面準位や結晶欠陥が形成されるのを抑制することができる。なお、保護膜24及び25に替えてレジスト層を形成してもよい。この場合は、リソグラフィ法を用いてレジスト層を保護膜24及び25と同じ形状に加工する。

【0028】

続いて、図9に示すように、シリコン上にのみピタキシャル層が成長する選択性エピタキシャル成長法を装置全面に施し、フォトダイオード16上方のシリコン基板11上に厚さ1200Å程度のシリコン層27をエピタキシャル成長させる。この際、シリコン基板11の結晶欠陥が少ないため、結晶性の良好なエピタキシャル層を形成できる。その後、例えば高温のリン酸(H2PO3)を用いてシリコン窒化膜25のみウェットエッチングした後、例えば希フッ酸を用いてTEOS膜24をウェットエッチングする。

【0029】

続いて、図10に示すように、リソグラフィ法を用いて、シリコン層(エピタキシャル層)27のみを露出するレジスト層28を形成する。続いて、レジスト層28をマスクとしてエピタキシャル層27にP型不純物(例えばボロン(B))をイオン注入法によりドープする。そして、レジスト層28を剥離した後、P型不純物を活性化するためのアニールを行う。これにより、フォトダイオード16上に、P型半導体層からなるシールド層27が形成される。

【0030】

なお、図10では、フォトダイオード16上のシールド層27全体がP型半導体層で構成されているが、この構成に限定されるものではない。図11に示すように、イオン注入の条件によっては、エピタキシャル層27の上部にのみP型不純物がドープされることで、シールド層27の上部がP型半導体層27Aで構成され、シールド層27の下部がシリコン層27Bで構成されていてもよい。この場合は、フォトダイオード16とシリコン層27Bとの間には、チャネル領域17として形成されたP型半導体層が設けられる。

【0031】

続いて、図12に示すように、リソグラフィ法を用いてシールド層27を覆うレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシリコン基板11に、高濃度のN型不純物(例えばリン(P))をイオン注入法によりドープする。その後、レジスト層を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、MOSFETのソース領域及びドレイン領域として、LDD領域22より不純物濃度の高いN+型拡散領域29が形成される。N+型拡散領域29には、転送トランジスタ20のソース領域、増幅トランジスタ21のソース領域及びドレイン領域が含まれる。

【0032】

転送トランジスタ20のソース領域29は、浮遊拡散層として機能する。フォトダイオード16に蓄積された信号電荷は、転送トランジスタ20によって浮遊拡散層に転送される。その後、浮遊拡散層の電圧が増幅トランジスタ21よって信号レベルとして出力される。

【0033】

続いて、リソグラフィ法を用いて所望の形状を有するレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシールド層27に、高濃度のP型不純物(例えばボロン(B))をイオン注入法によりドープする。これにより、シールド層27の表面領域に、シールド層27とオーミックかつ良好なコンタクトをとるためのP+型拡散領域30が形成される。P+型拡散領域30は、例えば、隣接する画素のフォトダイオード間の境界部に形成される。続いて、レジスト層を剥離した後、不純物を活性化するためのアニールを行う。これにより、固体撮像装置の下地が完成する。

【0034】

続いて、図13に示すように、装置全面に第1の層間絶縁層31(例えばTEOS膜)を堆積し、CMP(Chemical Mechanical Polishing)法を用いて層間絶縁層31を平坦化する。続いて、例えばリソグラフィ法及びRIE法を用いて、P+型拡散領域30及びMOSFETの電極(ゲート、ソース、ドレイン)を露出するコンタクト孔を形成する。続いて、コンタクト孔内に、例えばチタン(Ti)/窒化チタン(TiN)の2層からなるバリア膜32を例えばスパッタ法を用いて形成する。続いて、例えばCVD(Chemical Vapor Deposition)法を用いてコンタクト孔内を導電体33(例えばタングステン(W))で埋め込み、上層の余分なW及びTi/TiNをCMP法を用いて除去する。これにより、P+型拡散領域30及びMOSFETの電極に電気的に接続されたコンタクトプラグ33が形成される。

【0035】

続いて、図1に示すように、装置全面に第2の層間絶縁層34(例えばTEOS膜)を堆積し、CMP法を用いて層間絶縁層34を平坦化する。続いて、例えばダマシン法を用いてコンタクトプラグ33に電気的に接続された配線層35(例えば銅(Cu)配線)を形成する。続いて、銅(Cu)の拡散を抑える保護膜36(例えばシリコン窒化膜)を装置全面に堆積する。このようにして、第1の実施形態に係る固体撮像装置(具体的には、固体撮像装置の画素アレイ)が完成する。

【0036】

(効果)

以上詳述したように第1の実施形態では、固体撮像装置(CMOSセンサー)は、シリコン基板11内に設けられ、N型半導体層を有するフォトダイオード16と、フォトダイオード16上に設けられ、上部又は全体がP型半導体層からなるシールド層27と、シリコン基板11に設けられ、フォトダイオード16に蓄積された電荷を浮遊拡散層に転送する転送トランジスタ20とを具備している。そして、シールド層27の上面Yは、シリコン基板11の上面Xより高くなっている。

【0037】

従って第1の実施形態によれば、埋め込み型のフォトダイオード16をシリコン基板11の上面近くに形成することが可能となる。これにより、転送トランジスタ20のゲート電極19と、転送トランジスタ20の片側の拡散層としての役目も果たしているフォトダイオード16との垂直方向の距離を縮めることができる。この結果、転送トランジスタ20のしきい値電圧を低下させることができ、またオン電流を増大させることができる。さらに、フォトダイオード16に蓄積された電荷をより正確に読み出すことが可能となる。

【0038】

また、フォトダイオード16内に界面準位や結晶欠陥が形成されるのを抑制することができる。これにより、フォトダイオード16のノイズを低減することが可能となる。この結果、CMOSセンサーの画質を向上させることができる。

【0039】

また、シールド層27を形成する工程において、不純物が拡散する分の距離をエピタキシャル層の膜厚を厚くすることで確保できる。このため、シールド層27及びフォトダイオード16の不純物濃度を高くすることができ、不純物濃度に対するデバイス設計の自由度が増す。これにより、シールド層27の不純物濃度を高くすればシールド性が増して界面準位起因のノイズや白傷を低減させることができ、フォトダイオード16の不純物濃度を高くすればフォトダイオード16に蓄積できる電荷量を増やすことができる。結果として、光が照射された際の電気信号量を増やすことができ、高性能なCMOSセンサーを提供することが可能になる。

【0040】

なお、本実施形態では、シリコン基板がP型、フォトダイオード16のキャリア蓄積層がN型の場合について説明しているが、半導体の導電型が反転した画素の構造でも同様な効果を得ることができる。

【0041】

また、本実施形態では、半導体基板とシールド層を形成するエピタキシャル層とをシリコン(Si)で形成しているが、これがガリウム(Ge)やGaAsなど他の半導体材料でも同様な効果を得ることができる。さらには、半導体基板とエピタキシャル層とが異なる半導体材料、例えばシリコン基板上にSiGe層を形成するようなヘテロ接合の形成条件であっても、基板と堆積膜との格子定数が破綻を来さない組み合わせでありかつシールド層が界面準位が形成される基板界面部を包み込む形で形成されていれば問題なく上記と同等な効果が得られる。

【0042】

[第2の実施形態]

第2の実施形態は、シールド層を構成する半導体層としてMOSFETのゲート電極を構成する半導体層と同じ半導体材料を用いている。そして、ゲート電極用の半導体層を形成する工程と同時にシールド層用の半導体層を形成するようにしている。

【0043】

図14は、第2の実施形態に係る固体撮像装置の断面図である。第1の実施形態と同様に、シリコン基板11内には、埋め込み型のフォトダイオード16が設けられている。すなわち、フォトダイオード16の上面は、シリコン基板11の上面Xより低くなっている。フォトダイオード16上には、シールド層27が設けられている。シールド層27の上面Yは、シリコン基板11の上面Xより高くなっている。また、シールド層27を構成する半導体層としては、MOSFET(転送トランジスタ20及び増幅トランジスタ21を含む)のゲート電極19を構成する半導体層と同じ半導体材料が用いられる。

【0044】

次に、図面を参照しながら第2の実施形態に係る固体撮像装置の製造方法について説明する。第1の実施形態の図4までの製造工程は、第2の実施形態も同じ工程を経る。

【0045】

続いて、図15に示すように、保護膜13をエッチングした後、ゲート絶縁膜18を形成する。続いて、リソグラフィ法を用いてシールド層27が形成される領域以外を覆うレジスト層(図示せず)を形成した後、レジスト層をマスクとして例えば希フッ酸を用いてゲート絶縁膜18をウェットエッチングする。これにより、シールド層27が形成される領域のシリコン基板11の上面が露出される。その後、レジストを剥離する。

【0046】

続いて、図16に示すように、例えばCVD法を用いて、装置全面に、MOSFETのゲート電極材料としての多結晶シリコン層19を1500Å程度堆積する。続いて、図17に示すように、リソグラフィ法を用いてシールド層27が形成される領域を覆うレジスト層40を形成する。続いて、レジスト層40をマスクとして多結晶シリコン層19にN型不純物(例えばリン(P))をイオン注入法によりドープして多結晶シリコン層19を部分的にN型導電層にする。その後、レジスト層40を剥離する。

【0047】

続いて、図18に示すように、リソグラフィ法を用いて、各画素を構成するMOSFETのゲート電極が形成される領域、及びシールド層27が形成される領域を覆うレジスト層(図示せず)を多結晶シリコン層19上に形成し、レジスト層をマスクとして例えばRIE法を用いて多結晶シリコン層19をパターニングする。これにより、各画素を構成するMOSFET(転送トランジスタ20及び増幅トランジスタ21などを含む)のゲート電極19が形成されると共に、シールド層となる多結晶シリコン層27が形成される。

【0048】

続いて、図19に示すように、リソグラフィ法を用いて、MOSFETのLDD領域を形成する領域以外を覆うレジスト層(図示せず)を形成した後、チャネル領域17にN型不純物(例えばリン(P))をイオン注入法によりドープする。そして、レジスト層を剥離した後、N型不純物を活性化するためのアニールを行う。これにより、転送トランジスタ20のソース用のLDD領域22、及び増幅トランジスタ21のソース及びドレイン用のLDD領域22が形成される。

【0049】

続いて、装置全面に絶縁膜(例えばTEOS膜)を堆積し、例えばRIE法を用いてTEOS膜をエッチバックする。これにより、MOSFETの側壁23が形成される。また、転送トランジスタ20のゲート電極19と多結晶シリコン層27との間は、側壁23で埋め込まれる。

【0050】

続いて、図20に示すように、リソグラフィ法を用いて多結晶シリコン層27のみを露出するレジスト層41を形成する。続いて、レジスト層41をマスクとして多結晶シリコン層27にP型不純物(例えばボロン(B))をイオン注入法によりドープする。そして、レジスト層41を剥離した後、P型不純物を活性化するためのアニールを行う。これにより、フォトダイオード16上に、P型半導体層からなるシールド層27が形成される。

【0051】

なお、図20では、フォトダイオード16上のシールド層27全体がP型半導体層で構成されているが、この構成に限定されるものではない。図21に示すように、イオン注入の条件によっては、多結晶シリコン層27の上部にのみP型不純物がドープされることで、シールド層27の上部がP型半導体層27Aで構成され、シールド層27の下部が多結晶シリコン層27Bで構成されていてもよい。この場合は、フォトダイオード16と多結晶シリコン層27Bとの間には、チャネル領域17として形成されたP型半導体層が設けられる。

【0052】

続いて、図22に示すように、リソグラフィ法を用いてシールド層27を覆うレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシリコン基板11に、高濃度のN型不純物(例えばリン(P))をイオン注入法によりドープする。その後、レジスト層を剥離する。これにより、MOSFETのソース領域及びドレイン領域として、LDD領域22より不純物濃度の高いN+型拡散領域29が形成される。N+型拡散領域29には、転送トランジスタ20のソース領域、増幅トランジスタ21のソース領域及びドレイン領域が含まれる。

【0053】

続いて、リソグラフィ法を用いて所望の形状を有するレジスト層(図示せず)を形成した後、レジスト層をマスクとしてシールド層27に、高濃度のP型不純物(例えばボロン(B))をイオン注入法によりドープする。これにより、シールド層27の表面領域に、シールド層27とオーミックかつ良好なコンタクトをとるためのP+型拡散領域30が形成される。P+型拡散領域30は、例えば、隣接する画素のフォトダイオード間の境界部に形成される。続いて、レジスト層を剥離した後、不純物を活性化するためのアニールを行う。これにより、固体撮像装置の下地が完成する。

【0054】

続いて、図14に示すように、第1の層間絶縁層31、バリア膜32、コンタクトプラグ33、第2の層間絶縁層34、配線層35、及び保護膜36を形成する。これらの製造工程は、第1の実施形態と同じである。このようにして、第2の実施形態に係る固体撮像装置(具体的には、固体撮像装置の画素アレイ)が完成する。

【0055】

(効果)

以上詳述したように第2の実施形態によれば、シールド層27の上面を、シリコン基板11の上面より高くしているため、埋め込み型のフォトダイオード16をシリコン基板11の上面近くに形成することが可能となる。これにより、転送トランジスタ20のゲート電極19とフォトダイオード16との垂直方向の距離を縮めることができる。この結果、転送トランジスタ20のしきい値電圧を低下させることができ、またオン電流を増大させることができる。その他の効果も第1の実施形態と同じである。

【0056】

また、MOSFETのゲート電極を形成する工程を利用してシールド層27を形成することができる。これにより、シールド層27を形成するための製造工程数が抑制でき、また製造コストが高くなるのを抑制できる。なお、シールド層27用のシリコン層は、ゲート電極とは別の工程で形成するようにしてもよい。

【0057】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0058】

11…半導体基板、12…素子分離絶縁層、13…保護膜、14…分離層、15,26,28,40,41…レジスト層、16…フォトダイオード、17…チャネル領域、18…ゲート絶縁膜、19…ゲート電極、20…転送トランジスタ、21…増幅トランジスタ、22…LDD領域、23…側壁、24…保護膜、25…保護膜、27…シールド層、29…ソース/ドレイン領域、30…P+型拡散領域、31,34…層間絶縁層、32…バリア膜、33…コンタクトプラグ、35…配線層、36…保護膜。

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板内に設けられ、第1導電型の半導体層を有するフォトダイオードと、

前記フォトダイオード上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層と、

前記半導体基板に設けられ、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタと、

を具備し、

前記シールド層の上面は、前記半導体基板の上面より高いことを特徴とする固体撮像装置。

【請求項2】

前記シールド層は、エピタキシャル層からなることを特徴とする請求項1に記載の固体撮像装置。

【請求項3】

前記シールド層は、前記転送トランジスタのゲート電極と同じ材料からなることを特徴とする請求項1に記載の固体撮像装置。

【請求項4】

半導体基板内に、第1導電型の半導体層を有するフォトダイオードを形成する工程と、

前記フォトダイオード上方の半導体基板上に、エピタキシャル層を形成する工程と、

前記エピタキシャル層に第2導電型の不純物を導入して、前記フォトダイオード上に上部又は全体が第2導電型の半導体層からなるシールド層を形成する工程と、

前記半導体基板に、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタを形成する工程と、

を具備することを特徴とする固体撮像装置の製造方法。

【請求項5】

半導体基板内に、第1導電型の半導体層を有するフォトダイオードを形成する工程と、

前記半導体基板上に、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタのゲート電極を形成する工程と、

前記フォトダイオード上方の半導体基板上に、前記ゲート電極と同じ材料からなる半導体層を形成する工程と、

前記半導体層に第2導電型の不純物を導入して、前記フォトダイオード上に上部又は全体が第2導電型の半導体層からなるシールド層を形成する工程と、

前記半導体基板に、前記転送トランジスタを形成する工程と、

を具備することを特徴とする固体撮像装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板内に設けられ、第1導電型の半導体層を有するフォトダイオードと、

前記フォトダイオード上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層と、

前記半導体基板に設けられ、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタと、

を具備し、

前記シールド層の上面は、前記半導体基板の上面より高いことを特徴とする固体撮像装置。

【請求項2】

前記シールド層は、エピタキシャル層からなることを特徴とする請求項1に記載の固体撮像装置。

【請求項3】

前記シールド層は、前記転送トランジスタのゲート電極と同じ材料からなることを特徴とする請求項1に記載の固体撮像装置。

【請求項4】

半導体基板内に、第1導電型の半導体層を有するフォトダイオードを形成する工程と、

前記フォトダイオード上方の半導体基板上に、エピタキシャル層を形成する工程と、

前記エピタキシャル層に第2導電型の不純物を導入して、前記フォトダイオード上に上部又は全体が第2導電型の半導体層からなるシールド層を形成する工程と、

前記半導体基板に、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタを形成する工程と、

を具備することを特徴とする固体撮像装置の製造方法。

【請求項5】

半導体基板内に、第1導電型の半導体層を有するフォトダイオードを形成する工程と、

前記半導体基板上に、前記フォトダイオードに蓄積された電荷を浮遊拡散層に転送する転送トランジスタのゲート電極を形成する工程と、

前記フォトダイオード上方の半導体基板上に、前記ゲート電極と同じ材料からなる半導体層を形成する工程と、

前記半導体層に第2導電型の不純物を導入して、前記フォトダイオード上に上部又は全体が第2導電型の半導体層からなるシールド層を形成する工程と、

前記半導体基板に、前記転送トランジスタを形成する工程と、

を具備することを特徴とする固体撮像装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2013−110250(P2013−110250A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253710(P2011−253710)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]