固体撮像装置

【課題】電子シャッタ変更命令を受け付け早く実施する。

【解決手段】IT−CCDを用いた撮像装置において、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加するか、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加するか、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加する。

【解決手段】IT−CCDを用いた撮像装置において、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加するか、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加するか、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固体撮像素子を有する撮像装置に関するものである。

【背景技術】

【0002】

シリコン製撮像素子は、基板(Substrate以下Sub)電圧(以下V-sub)等の電極電圧を可変することで、フォトダイオード(Photo-Diode以下PD)の飽和特性が可変する。Sub等のオーバーフロードレイン(Over-flow Drain以下OD)に正のパルス電圧を印可する事によりPD電荷を掃き捨てる。電荷転送型撮像素子(Charge Coupled Device以下CCDと略す)の中でもFIT(Frame

Interline Transfer)−CCDやIT(Interline Transfer)−CCDでは、基盤(Sub)がODとなり、縦型ODと呼ばれる。

【0003】

IT−CCDには、4相のIT−CCDと3相のIT−CCDがある。4相のIT−CCDと3相のIT−CCDとは、SUBに高圧の電子シャッタパルスを印加することにより信号電荷を掃き捨て、蓄積時間を制御し、V1等に読み出しパルスを印加することにより信号電荷を読み出し、V1−V4またはV1−V3に転送パルスを印加することにより信号電荷を垂直転送し、H1、H2,RGに転送パルスを印加することにより信号電荷を水平転送し、FDAから読み出す。(非特許文献1と非特許文献2参照)。

画像処理では、高速の電子シャッタで蓄積時間が短く、電子シャッタは垂直周期の終了付近であることが多い。

掃き捨て動作と読み出し動作の位相を工夫して画面の一部を高フレームレートで読み出すパーシャルスキャンも実施されている(特許文献1参照)。

【0004】

図6は、従来の撮像装置の構成を示すブロック図であり、IT−CCDを1つ用いたカメラである。図6は、IT−CCDと、VD前に電子シャッタタイミングによって定まる蓄積時間を読み込むタイミング発生(Timing Generator:以下TG)とOD掃き捨てと読み出しとを内蔵の垂直転送駆動部と、雑音を除去するCDS(Correlated Double Sampling)と暗電流補正と利得可変増幅回路(Automatic Gain Control以下AGC)とデジタル映像信号Viに変換するADC(Analog Digital Converter)と水平転送と電圧変換のリセットとCDSとAGCとADCとのTGを内蔵したFEP(Front End Processor)と雑音低減の平均化内蔵の信号処理回路とCPU(Central Processing Unit)とからなる。画像信号に雑音が飛び込まない様にCPUとTG間の通信は帰線期間(Blanking:BL)に行われる。

画面前に掃き捨て時間決定のCCDの掃き捨て時間決定のフローチャートの図4の様に、PCからカメラのCPUが受け取っておいた電子シャッタ変更命令に基づき、VD前に電子シャッタタイミングによって定まる蓄積時間をCPUからTGに読み込む。

その結果、従来のタイミングチャートの図5の様に、PCからカメラのCPUが電子シャッタ変更命令を受け取ってから、電子シャッタが変更された画像信号がCCDから読み出されるのは、2フレーム後となる。

【0005】

また、映像信号のスタジオ内伝送にはNRZ(Non−Return to Zero)スクランブル信号として低域成分のない高速シリアルデータのSDI(Serial Digital Interface)が用いられている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−42838 パーシャルスキャン

【非特許文献】

【0007】

【非特許文献1】ICX638AKAデータシートJ08Z21B99 ソニー(株)

【非特許文献2】ICX204データシートJ98809C3Z ソニー(株)

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、電子シャッタ変更命令を早く適応し、変更した電子シャッタの画像データを早く出力することにある。

【課題を解決するための手段】

【0009】

本発明は、上記課題を解決するため、IT−CCDを用い電子シャッタ変更命令に基づく画像データを出力する撮像装置において、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが来た水平周期で電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加すること、との少なくとも一方を行うこととを特徴とする固体撮像装置である。

【発明の効果】

【0010】

本発明によれば、電子シャッタ変更命令を早く適応し、変更した電子シャッタの画像データを早く出力する。

【図面の簡単な説明】

【0011】

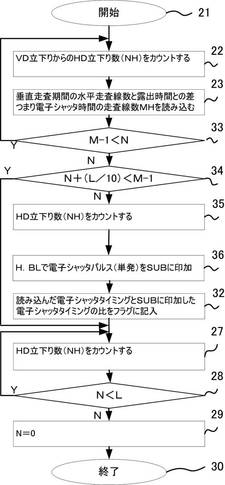

【図1A】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎてもH.BLで電子シャッタ)

【図1B】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたらH.BLで電子シャッタせず)

【図1C】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)

【図1D】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)

【図2A】本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング多少過ぎても電子シャッタ)

【図2B】本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング少しでも過ぎてたら電子シャッタせず)

【図2C】本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャート(タイミング多少過ぎても電子シャッタ)

【図2D】本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャート(タイミング少しでも過ぎてたら電子シャッタせず)

【図2E】本発明の1実施例の撮像装置の3相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャート

【図3A】本発明の1実施例の撮像装置の構成を示すブロック図(単板IT−CCD)

【図3B】本発明の1実施例の撮像装置の構成を示すブロック図(3板IT−CCD)

【図4】従来の撮像装置の電子シャッタの動作を示すフローチャート

【図5】従来の撮像装置の電子シャッタの動作を示すタイミングチャート

【図6】従来の撮像装置の構成を示すブロック図(単板IT−CCD)

【発明を実施するための形態】

【実施例1】

【0012】

以下、本発明による撮像装置の一実施例について、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎてもH.BLで電子シャッタ)の図1Aと、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたらH.BLで電子シャッタせず)の図1Bと、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)の図1Cと、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図1Dと、本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング多少過ぎても電子シャッタの図2Aと、本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図2Bと、本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャートの図2Cと、本発明の1実施例の撮像装置の構成を示すブロック図(単板IT−CCD)の図3Aと、本発明の1実施例の撮像装置の構成を示すブロック図(3板IT−CCD)の図3Bとを用いて説明する。

【0013】

IT−CCDには、4相のIT−CCDと3相のIT−CCDがある。4相のIT−CCDのV1と3相のIT−CCDのV2AとV2Bとの動作は同様である。図2Aと図2Bとは4相のIT−CCDのV1と3相のIT−CCDのV2AとV2Bとの動作を説明する。本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャートの図2CはSUBとV1からV4の動作を示し、本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャートの図2DはSUBとV1とV2AとV2BとV3とのの動作を示す。

【0014】

本発明の一実施例の撮像装置を示すブロック図である図1において、1と4は撮像装置、2は入射光を結像するレンズ部、3は入射光を赤(R)、緑(G)、青(B)に分解する色分解光学系、5はFEPから出力された信号Lに適応平均を含む種々の画像処理を施し所定方式の映像信号に変換する映像信号処理部、6は撮像装置1内の各部を制御するCPUであり、7,8,9はレンズ部2から入射した光を電気信号に変換するIT−CCDであり、10,11,12は雑音を除去するCDSと暗電流補正とAGCとデジタル映像信号Viに変換するADCと水平転送パルスを発生するFEPである。13は垂直読み出しと垂直転送パルスを発生しCCDを駆動する読出垂直転送駆動部である。

【0015】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)の図1Aにおいて、21は開始、22はVD立下りからのHD立下り数(NH)をカウントする、23は垂直走査期間の水平走査線数と露出時間との差つまり電子シャッタ時間の走査線数MHを読み込む、33はM−1<Nを判定しYES(Y)なら23に戻りNO(N)なら25に進む、34はN+(L/10)<M−1を判定しYES(Y)なら27に進みNO(N)なら35に進む、35はHD立下り数(NH)をカウントし26に進む、26は電子シャッタパルス(単発)をSUBに印加、27はHD立下り数(NH)をカウントする、28は、29はN<Lを判定しYES(Y)なら27に戻りNO(N)なら29に進む、29は垂直周期が終了したのでN=0にする、30は終わりである。

【0016】

つまり、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加する。

本発明によれば、画像処理では、高速の電子シャッタで蓄積時間が短く、電子シャッタは垂直周期の終了付近であることが多いことを利用し、垂直周期の終了付近の電子シャッタの近傍まで、電子シャッタ変更命令を受け付け実施する。

さらに、画像信号に雑音が混入することはないように、水平帰線期間(H.BL)にCPUとTG間の通信を行う工夫である。

【0017】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図1Bにおいて、図1Aとの相違点は、34はN+(L/10)<M−1を判定しYES(Y)なら27に進みNO(N)なら26に進む、の替わりに、36のN<Mを判定しYES(Y)なら27に進みNO(N)なら35に進む、となっていることである。

【0018】

つまり、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加する。

【0019】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)の図1Cにおいて、21は開始、22はVD立下りからのHD立下り数(NH)をカウントする、23は垂直走査期間の水平走査線数と露出時間との差つまり電子シャッタ時間の走査線数MHを読み込む、24はM<Nを判定しYES(Y)なら23に戻りNO(N)なら25に進む、25はN+(L/10)<Mを判定しYES(Y)なら27に進みNO(N)なら26に進む、26は電子シャッタパルス(単発)をSUBに印加、27はHD立下り数(NH)をカウントする、28は、29はN<Lを判定しYES(Y)なら27に戻りNO(N)なら29に進む、29は垂直周期が終了したのでN=0にする、30は終わりである。

【0020】

つまり、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、電子シャッタパルスをSUBに印加する。

水平帰線期間(H.BL)にCPUとTG間の通信を行っても、画像信号に雑音が混入することはないように、CPUとTGとをFPGAで統合するか、CPUとTG間の通信をNRZ(None Return to Zero)等の低域成分のない高速シリアルデータとして工夫をすれば良い。

【0021】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図1Dにおいて、図1Aとの相違点は、25はN+(L/10)<Mを判定しYES(Y)なら27に進みNO(N)なら26に進む、の替わりに、32のN<Mを判定しYES(Y)なら27に進みNO(N)なら26に進む、となっていることである。

つまり、IT−CCDを用い電子シャッタ変更命令に基づく画像データを出力する撮像装置において、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが来た水平周期で、電子シャッタパルスをSUBに印加する。

【0022】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャートの図1Aと図1Bにおいて、32として読み込んだ電子シャッタタイミングとSUBに印加した電子シャッタタイミングの比をフラグに記入する。

つまり、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加する。

【0023】

以上4相のIT−CCDについて詳細に動作を説明したが、3相のIT−CCDでもV1からV3の動作が異なるだけで、V1の動作は同様であり、本発明を適用できる。

【0024】

また、以上

【符号の説明】

【0025】

1,4,20,:撮像装置、2:レンズ部、

3:色分解光学系、5:映像信号処理部、6:CPU

7,8,9:IT−CCD、

10,11,12:CDSとAGCとA/D含むFEP

13:TGと読出含む読出垂直転送駆動部、

14:TGとOD駆動と読出含む読出垂直転送駆動部、

15:映像信号処理部、

【技術分野】

【0001】

本発明は、固体撮像素子を有する撮像装置に関するものである。

【背景技術】

【0002】

シリコン製撮像素子は、基板(Substrate以下Sub)電圧(以下V-sub)等の電極電圧を可変することで、フォトダイオード(Photo-Diode以下PD)の飽和特性が可変する。Sub等のオーバーフロードレイン(Over-flow Drain以下OD)に正のパルス電圧を印可する事によりPD電荷を掃き捨てる。電荷転送型撮像素子(Charge Coupled Device以下CCDと略す)の中でもFIT(Frame

Interline Transfer)−CCDやIT(Interline Transfer)−CCDでは、基盤(Sub)がODとなり、縦型ODと呼ばれる。

【0003】

IT−CCDには、4相のIT−CCDと3相のIT−CCDがある。4相のIT−CCDと3相のIT−CCDとは、SUBに高圧の電子シャッタパルスを印加することにより信号電荷を掃き捨て、蓄積時間を制御し、V1等に読み出しパルスを印加することにより信号電荷を読み出し、V1−V4またはV1−V3に転送パルスを印加することにより信号電荷を垂直転送し、H1、H2,RGに転送パルスを印加することにより信号電荷を水平転送し、FDAから読み出す。(非特許文献1と非特許文献2参照)。

画像処理では、高速の電子シャッタで蓄積時間が短く、電子シャッタは垂直周期の終了付近であることが多い。

掃き捨て動作と読み出し動作の位相を工夫して画面の一部を高フレームレートで読み出すパーシャルスキャンも実施されている(特許文献1参照)。

【0004】

図6は、従来の撮像装置の構成を示すブロック図であり、IT−CCDを1つ用いたカメラである。図6は、IT−CCDと、VD前に電子シャッタタイミングによって定まる蓄積時間を読み込むタイミング発生(Timing Generator:以下TG)とOD掃き捨てと読み出しとを内蔵の垂直転送駆動部と、雑音を除去するCDS(Correlated Double Sampling)と暗電流補正と利得可変増幅回路(Automatic Gain Control以下AGC)とデジタル映像信号Viに変換するADC(Analog Digital Converter)と水平転送と電圧変換のリセットとCDSとAGCとADCとのTGを内蔵したFEP(Front End Processor)と雑音低減の平均化内蔵の信号処理回路とCPU(Central Processing Unit)とからなる。画像信号に雑音が飛び込まない様にCPUとTG間の通信は帰線期間(Blanking:BL)に行われる。

画面前に掃き捨て時間決定のCCDの掃き捨て時間決定のフローチャートの図4の様に、PCからカメラのCPUが受け取っておいた電子シャッタ変更命令に基づき、VD前に電子シャッタタイミングによって定まる蓄積時間をCPUからTGに読み込む。

その結果、従来のタイミングチャートの図5の様に、PCからカメラのCPUが電子シャッタ変更命令を受け取ってから、電子シャッタが変更された画像信号がCCDから読み出されるのは、2フレーム後となる。

【0005】

また、映像信号のスタジオ内伝送にはNRZ(Non−Return to Zero)スクランブル信号として低域成分のない高速シリアルデータのSDI(Serial Digital Interface)が用いられている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−42838 パーシャルスキャン

【非特許文献】

【0007】

【非特許文献1】ICX638AKAデータシートJ08Z21B99 ソニー(株)

【非特許文献2】ICX204データシートJ98809C3Z ソニー(株)

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、電子シャッタ変更命令を早く適応し、変更した電子シャッタの画像データを早く出力することにある。

【課題を解決するための手段】

【0009】

本発明は、上記課題を解決するため、IT−CCDを用い電子シャッタ変更命令に基づく画像データを出力する撮像装置において、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが来た水平周期で電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、電子シャッタパルスをSUBに印加することと、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加すること、との少なくとも一方を行うこととを特徴とする固体撮像装置である。

【発明の効果】

【0010】

本発明によれば、電子シャッタ変更命令を早く適応し、変更した電子シャッタの画像データを早く出力する。

【図面の簡単な説明】

【0011】

【図1A】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎてもH.BLで電子シャッタ)

【図1B】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたらH.BLで電子シャッタせず)

【図1C】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)

【図1D】本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)

【図2A】本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング多少過ぎても電子シャッタ)

【図2B】本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング少しでも過ぎてたら電子シャッタせず)

【図2C】本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャート(タイミング多少過ぎても電子シャッタ)

【図2D】本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャート(タイミング少しでも過ぎてたら電子シャッタせず)

【図2E】本発明の1実施例の撮像装置の3相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャート

【図3A】本発明の1実施例の撮像装置の構成を示すブロック図(単板IT−CCD)

【図3B】本発明の1実施例の撮像装置の構成を示すブロック図(3板IT−CCD)

【図4】従来の撮像装置の電子シャッタの動作を示すフローチャート

【図5】従来の撮像装置の電子シャッタの動作を示すタイミングチャート

【図6】従来の撮像装置の構成を示すブロック図(単板IT−CCD)

【発明を実施するための形態】

【実施例1】

【0012】

以下、本発明による撮像装置の一実施例について、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎてもH.BLで電子シャッタ)の図1Aと、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたらH.BLで電子シャッタせず)の図1Bと、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)の図1Cと、本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図1Dと、本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング多少過ぎても電子シャッタの図2Aと、本発明の1実施例の撮像装置の電子シャッタの動作を示すタイミングチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図2Bと、本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャートの図2Cと、本発明の1実施例の撮像装置の構成を示すブロック図(単板IT−CCD)の図3Aと、本発明の1実施例の撮像装置の構成を示すブロック図(3板IT−CCD)の図3Bとを用いて説明する。

【0013】

IT−CCDには、4相のIT−CCDと3相のIT−CCDがある。4相のIT−CCDのV1と3相のIT−CCDのV2AとV2Bとの動作は同様である。図2Aと図2Bとは4相のIT−CCDのV1と3相のIT−CCDのV2AとV2Bとの動作を説明する。本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャートの図2CはSUBとV1からV4の動作を示し、本発明の1実施例の撮像装置の4相のIT−CCDの電子シャッタと垂直転送の動作を示すタイミングチャートの図2DはSUBとV1とV2AとV2BとV3とのの動作を示す。

【0014】

本発明の一実施例の撮像装置を示すブロック図である図1において、1と4は撮像装置、2は入射光を結像するレンズ部、3は入射光を赤(R)、緑(G)、青(B)に分解する色分解光学系、5はFEPから出力された信号Lに適応平均を含む種々の画像処理を施し所定方式の映像信号に変換する映像信号処理部、6は撮像装置1内の各部を制御するCPUであり、7,8,9はレンズ部2から入射した光を電気信号に変換するIT−CCDであり、10,11,12は雑音を除去するCDSと暗電流補正とAGCとデジタル映像信号Viに変換するADCと水平転送パルスを発生するFEPである。13は垂直読み出しと垂直転送パルスを発生しCCDを駆動する読出垂直転送駆動部である。

【0015】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)の図1Aにおいて、21は開始、22はVD立下りからのHD立下り数(NH)をカウントする、23は垂直走査期間の水平走査線数と露出時間との差つまり電子シャッタ時間の走査線数MHを読み込む、33はM−1<Nを判定しYES(Y)なら23に戻りNO(N)なら25に進む、34はN+(L/10)<M−1を判定しYES(Y)なら27に進みNO(N)なら35に進む、35はHD立下り数(NH)をカウントし26に進む、26は電子シャッタパルス(単発)をSUBに印加、27はHD立下り数(NH)をカウントする、28は、29はN<Lを判定しYES(Y)なら27に戻りNO(N)なら29に進む、29は垂直周期が終了したのでN=0にする、30は終わりである。

【0016】

つまり、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加する。

本発明によれば、画像処理では、高速の電子シャッタで蓄積時間が短く、電子シャッタは垂直周期の終了付近であることが多いことを利用し、垂直周期の終了付近の電子シャッタの近傍まで、電子シャッタ変更命令を受け付け実施する。

さらに、画像信号に雑音が混入することはないように、水平帰線期間(H.BL)にCPUとTG間の通信を行う工夫である。

【0017】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図1Bにおいて、図1Aとの相違点は、34はN+(L/10)<M−1を判定しYES(Y)なら27に進みNO(N)なら26に進む、の替わりに、36のN<Mを判定しYES(Y)なら27に進みNO(N)なら35に進む、となっていることである。

【0018】

つまり、電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加する。

【0019】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング多少過ぎても電子シャッタ)の図1Cにおいて、21は開始、22はVD立下りからのHD立下り数(NH)をカウントする、23は垂直走査期間の水平走査線数と露出時間との差つまり電子シャッタ時間の走査線数MHを読み込む、24はM<Nを判定しYES(Y)なら23に戻りNO(N)なら25に進む、25はN+(L/10)<Mを判定しYES(Y)なら27に進みNO(N)なら26に進む、26は電子シャッタパルス(単発)をSUBに印加、27はHD立下り数(NH)をカウントする、28は、29はN<Lを判定しYES(Y)なら27に戻りNO(N)なら29に進む、29は垂直周期が終了したのでN=0にする、30は終わりである。

【0020】

つまり、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、電子シャッタパルスをSUBに印加する。

水平帰線期間(H.BL)にCPUとTG間の通信を行っても、画像信号に雑音が混入することはないように、CPUとTGとをFPGAで統合するか、CPUとTG間の通信をNRZ(None Return to Zero)等の低域成分のない高速シリアルデータとして工夫をすれば良い。

【0021】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャート(タイミング少しでも過ぎてたら電子シャッタせず)の図1Dにおいて、図1Aとの相違点は、25はN+(L/10)<Mを判定しYES(Y)なら27に進みNO(N)なら26に進む、の替わりに、32のN<Mを判定しYES(Y)なら27に進みNO(N)なら26に進む、となっていることである。

つまり、IT−CCDを用い電子シャッタ変更命令に基づく画像データを出力する撮像装置において、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが来た水平周期で、電子シャッタパルスをSUBに印加する。

【0022】

本発明の1実施例の撮像装置の電子シャッタの動作を示すフローチャートの図1Aと図1Bにおいて、32として読み込んだ電子シャッタタイミングとSUBに印加した電子シャッタタイミングの比をフラグに記入する。

つまり、電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加する。

【0023】

以上4相のIT−CCDについて詳細に動作を説明したが、3相のIT−CCDでもV1からV3の動作が異なるだけで、V1の動作は同様であり、本発明を適用できる。

【0024】

また、以上

【符号の説明】

【0025】

1,4,20,:撮像装置、2:レンズ部、

3:色分解光学系、5:映像信号処理部、6:CPU

7,8,9:IT−CCD、

10,11,12:CDSとAGCとA/D含むFEP

13:TGと読出含む読出垂直転送駆動部、

14:TGとOD駆動と読出含む読出垂直転送駆動部、

15:映像信号処理部、

【特許請求の範囲】

【請求項1】

IT−CCDを用い電子シャッタ変更命令に基づく画像データを出力する撮像装置において、

電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが来た水平周期で電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加すること、

との少なくとも一方を行うこととを特徴とする固体撮像装置。

【請求項1】

IT−CCDを用い電子シャッタ変更命令に基づく画像データを出力する撮像装置において、

電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが来る1水平周期前の水平帰線期間に判定し電子シャッタタイミングが来た水平帰線期間で電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが来た水平周期で電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平帰線期間ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、水平帰線期間に電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングが過ぎていても画面内の水平周期の10分の一以下なら、電子シャッタパルスをSUBに印加することと、

電子シャッタ変更命令を毎水平周期ごとに受けつけ該変更命令の電子シャッタタイミングと印加した電子シャッタパルスタイミングとの比をフラグとして出力する画像データに付加すること、

との少なくとも一方を行うこととを特徴とする固体撮像装置。

【図1A】

【図1B】

【図1C】

【図1D】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図1B】

【図1C】

【図1D】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【公開番号】特開2011−188085(P2011−188085A)

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願番号】特願2010−49079(P2010−49079)

【出願日】平成22年3月5日(2010.3.5)

【出願人】(000001122)株式会社日立国際電気 (5,007)

【Fターム(参考)】

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願日】平成22年3月5日(2010.3.5)

【出願人】(000001122)株式会社日立国際電気 (5,007)

【Fターム(参考)】

[ Back to top ]