圧電発振器および電子機器

【課題】複数の出力端子からの信号の出力状態を制御した場合であっても、所望の出力特性を得ることができる圧電発振器および電子機器を提供すること。

【解決手段】実施形態の圧電発振器によれば、圧電振動素子と、回路素子と、素子搭載部材とを備える。回路素子は、圧電振動素子に接続され、圧電振動素子の振動に応じた出力信号を生成する発振回路と、複数の出力端子と、複数の出力端子からの出力信号の出力状態を制御する制御回路とを有する。素子搭載部材は、複数の外部接続用端子が形成されると共に、圧電振動素子と回路素子とを電気的に接続する第1の導電路と、出力端子と外部接続用端子とを電気的に接続する第2の導電路とを含む多層の配線領域が形成される。第1の導電路と第2の導電路とは、配線領域の積層方向において交差しない。

【解決手段】実施形態の圧電発振器によれば、圧電振動素子と、回路素子と、素子搭載部材とを備える。回路素子は、圧電振動素子に接続され、圧電振動素子の振動に応じた出力信号を生成する発振回路と、複数の出力端子と、複数の出力端子からの出力信号の出力状態を制御する制御回路とを有する。素子搭載部材は、複数の外部接続用端子が形成されると共に、圧電振動素子と回路素子とを電気的に接続する第1の導電路と、出力端子と外部接続用端子とを電気的に接続する第2の導電路とを含む多層の配線領域が形成される。第1の導電路と第2の導電路とは、配線領域の積層方向において交差しない。

【発明の詳細な説明】

【技術分野】

【0001】

開示の実施形態は、圧電発振器および電子機器に関する。

【背景技術】

【0002】

従来、携帯電話機などの電子機器には、基準信号源やクロック信号源などの信号源が搭載されており、かかる信号源として、圧電振動素子を搭載した圧電発振器が知られている。

【0003】

圧電発振器は、一つの出力端子から信号を出力するものが一般的であったが、近年では、出力端子を複数個備えた多出力型のものが開発されている。例えば、特許文献1に記載の電子機器には、2つの出力端子の一方が高周波回路に接続され、他方がデジタル回路に接続された多出力型の発振器が搭載される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−102323号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

多出力型の圧電発振器では、搭載される電子機器の動作状態に応じて複数の出力端子に対する信号の出力状態を制御した場合であっても所望の出力特性が得られることが望まれる。

【0006】

実施形態の一態様は、上記に鑑みてなされたものであって、複数の出力端子からの信号の出力状態を制御した場合であっても、所望の出力特性を得ることができる圧電発振器および電子機器を提供することを目的とする。

【課題を解決するための手段】

【0007】

実施形態の一態様に係る圧電発振器は、圧電振動素子と、回路素子と、素子搭載部材とを備える。前記回路素子は、前記圧電振動素子に接続され、前記圧電振動素子の振動に応じた出力信号を生成する発振回路と、複数の出力端子と、前記複数の出力端子からの前記出力信号の出力状態を制御する制御回路とを有する。前記素子搭載部材は、複数の外部接続用端子が形成されると共に、前記圧電振動素子と前記回路素子とを電気的に接続する第1の導電路と、前記出力端子と前記外部接続用端子とを電気的に接続する第2の導電路とを含む多層の配線領域が形成される。前記第1の導電路と前記第2の導電路とは、前記配線領域の積層方向において交差しない。

【発明の効果】

【0008】

実施形態の一態様の圧電発振器によれば、複数の出力端子からの信号の出力状態を制御した場合であっても、所望の出力特性を得ることができる。

【図面の簡単な説明】

【0009】

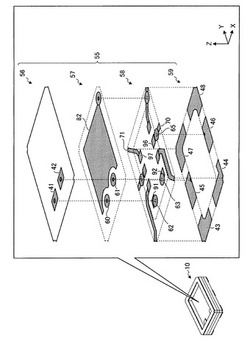

【図1】図1は、第1の実施形態に係る圧電発振器の分解斜視図である。

【図2】図2は、図1に示すA−A線断面図である。

【図3】図3は、第1の実施形態に係る圧電発振器の回路ブロック図である。

【図4】図4は、図1に示す素子搭載部材に形成される配線領域の構成を表す模式図である。

【図5】図5は、配線領域の積層方向から見た場合の第1の導電路および第2の導電路の位置関係を示す図である。

【図6】図6は、第3配線層の配線状態を示す図である。

【図7】図7は、第3配線層に形成されるモニタパッドの位置を示す図である。

【図8】図8は、電子機器のブロック図である。

【図9】図9は、第2の実施形態に係る圧電発振器の素子搭載部材に形成される配線領域の構成を表す模式図である。

【図10】図10は、図9に示す第3配線層の配線状態を示す図である。

【図11】図11は、第3の実施形態に係る圧電発振器の回路ブロック図である。

【図12】図12は、第3の実施形態に係る圧電発振器の他の回路ブロック図である。

【発明を実施するための形態】

【0010】

以下、添付図面を参照して、本願の開示する圧電発振器および電子機器の実施形態を詳細に説明する。なお、以下に示す各実施形態によりこの発明が限定されるものではない。

【0011】

(第1の実施形態)

第1の実施形態に係る圧電発振器について、図1および図2を用いて説明する。図1は、第1の実施形態に係る圧電発振器の分解斜視図であり、図2は、図1に示すA−A線断面図である。なお、以下の説明においては、電子機器の実装ボードへの圧電発振器の搭載面を「下面」と、かかる下面と対向する面を「上面」と、それぞれ記載する。

【0012】

図1および図2に示すように、第1の実施形態に係る圧電発振器1は、素子搭載部材10と、圧電振動素子20と、IC(Integrated Circuit:集積回路)素子30と、蓋部材40とを備える。かかる圧電発振器1は、圧電振動素子20の振動に応じた出力信号を複数の出力端子から出力することができ、また、一部の出力端子のみから出力信号を出力することができる。

【0013】

素子搭載部材10は、圧電振動素子20およびIC素子30を搭載する役割と、各電子部材同士を電気的に接続する役割とを兼用する。かかる素子搭載部材10は、セラミックのシートを所定の形状に切断した絶縁層11〜14を積層して圧着させ、加熱することによって形成される。

【0014】

各絶縁層11〜14には導電ペーストなどが従来周知のスクリーン印刷によって塗布されてビア導体、配線および電極パッドが形成される。なお、以下の説明では、ビア導体、配線および電極パッドを単に配線と記載する場合があり、また、配線が形成される領域を配線領域と記載する場合がある。

【0015】

絶縁層11および絶縁層14は、平面視(Z方向視)した場合に、中央部が開口した略枠状の形状を有しており、絶縁層12,13は、開口がない略矩形平板状の形状を有している。絶縁層11および絶縁層12によって上面側凹部15が形成され、絶縁層13および絶縁層14によって下面側凹部16が形成される。

【0016】

圧電振動素子20は、素子搭載部材10の上面側凹部15内に配置される。圧電振動素子20は、略矩形の圧電片と、圧電片の両主面にそれぞれ形成された一対の励振電極と、一対の励振電極にそれぞれ電気的に接続された一対の引出電極とを含む。圧電片として、例えば、所定の結晶方位角に従ってカットされた略矩形の水晶基板が用いられる。なお、図1および図2では、いわゆる「平板型」の圧電振動素子20を例示したが、例えば、「音叉型」の圧電振動素子20を用いることとしてもよい。

【0017】

圧電振動素子20における一対の引出電極は、素子搭載部材10の上面側凹部15内に形成された一対の電極パッド41,42へ導電性接着剤18によってそれぞれ電気的かつ機械的に接続される。なお、導電性接着剤18は、例えば、シリコーン樹脂等のバインダーの中に導電フィラーとして導電性粉末(例えば銀粉(Ag))を含有している。

【0018】

素子搭載部材10における略枠状の上面には電極17が設けられ、蓋部材40の下面には素子搭載部材10の上面と対向する位置に電極が設けられる。そして、素子搭載部材10の上面側凹部15内に圧電振動素子20が配置された状態で、蓋部材40の電極が、素子搭載部材10の電極17へ、例えば、シーム溶接によって接合される。

【0019】

素子搭載部材10における略枠状の下面には、外部接続用端子43〜48が形成される。これら外部接続用端子43〜48は、電子機器の実装ボード上の電極に接続される。

【0020】

また、素子搭載部材10の下面側凹部16内には、IC素子30が配置される。絶縁層13の下面側には、後述するように複数の電極パッド91〜98(図6参照)が形成されており、かかる電極パッド91〜98にIC素子30の上面側に形成された端子T1〜T8が接続される。電極パッド91〜98と端子T1〜T8との接続は、例えば、GGI接合(GOLD TO GOLD INTERCONNECTION:金―金接合)や半田接合等により金や半田等の導電性接着剤19によって行われる。

【0021】

図3は、圧電発振器1の回路ブロック図である。図3に示すように、圧電発振器1は、圧電振動素子20と、IC素子30と、外部接続用端子43〜48とを備える。かかる圧電発振器1は、外部接続用端子48にグランド電位が印加され、外部接続用端子43に電源電圧VCCが入力されて動作する。

【0022】

IC素子30は、発振回路51と、バッファ回路52,53と、スイッチSW1,SW2と、端子T1〜T8とを備える。かかるIC素子30は、端子T8にグランド(GND)が接続され、端子T3に電源電圧VCCが入力されて動作する。

【0023】

発振回路51は、端子T1,T2を介して圧電振動素子20における一対の引出電極に接続され、圧電振動素子20を所定の周波数で発振させて圧電振動素子20の発振周波数に応じた信号を生成する。

【0024】

発振回路51によって生成された信号はバッファ回路52,53へ入力される。バッファ回路52,53の出力はそれぞれ端子T7,T6(以下、出力端子T7,T6と記載する場合がある)を介して外部接続用端子47,46に接続されており、圧電振動素子20の発振周波数に応じた信号が外部接続用端子47,46から外部へ出力される。なお、発振回路51は、温度補償回路を含んでいてもよい。

【0025】

バッファ回路52には、スイッチSW1を介して電源電圧VCCが入力される。スイッチSW1は、端子T5を介して外部接続用端子45に接続され、外部接続用端子45へ入力される制御信号CONT1によって制御される。同様に、バッファ回路53には、スイッチSW2を介して電源電圧VCCが入力される。スイッチSW2は、端子T4を介して外部接続用端子44に接続され、外部接続用端子44へ入力される制御信号CONT2によって制御される。このように、制御回路の一例であるスイッチSW1,SW2を制御することによって、出力端子T7,T6からの信号の出力状態が制御される。

【0026】

ここで、制御信号CONT1,CONT2の状態と、IC素子30内部の状態および出力端子T7,T6からの出力信号OUT1,OUT2の出力状態との関係を下記表1に示す。表1においては、バッファ回路52を「バッファ1」と記載し、バッファ回路53を「バッファ2」と記載する。なお、ここでは、制御信号CONT1,CONT2は、Highアクティブの信号であるが、これに限定されるものではない。

【0027】

【表1】

【0028】

上記表1に示すように、制御信号CONT1,CONT2の状態に応じて、出力端子T7,T6からの信号の出力状態が変化する。例えば、制御信号CONT1,CONT2が共にHighレベルである場合、スイッチSW1,SW2がON状態となってバッファ回路52,53へ電源電圧VCCが供給され、バッファ回路52,53がアクティブとなる。そのため、出力端子T7,T6から出力信号OUT1,OUT2が同時に出力される。

【0029】

一方、制御信号CONT1がHighレベルであり、制御信号CONT2がLowレベルである場合、スイッチSW2はOFF状態であるため、バッファ回路53へは電源電圧VCCが供給されず、バッファ回路53は非アクティブである。そのため、出力端子T6から出力信号OUT2は出力されず、出力端子T7のみから出力信号OUT1が出力される。

【0030】

また、制御信号CONT1がLowレベルであり、制御信号CONT2がHighレベルである場合、スイッチSW1がOFF状態であるため、バッファ回路52へ電源電圧VCCが供給されず、バッファ回路52は非アクティブである。そのため、出力端子T7から出力信号OUT1は出力されず、出力端子T6のみから出力信号OUT2が出力される。

【0031】

このように圧電発振器1では、バッファ回路52,53の状態をそれぞれアクティブ状態と非アクティブ状態とで切り替えることによって、出力端子T7,T6からの信号の出力状態を切り替える。また、バッファ回路52,53の一方を非アクティブ状態にすることで、出力端子T7,T6のうち一方の出力端子のみから出力信号を出力する場合の消費電力を低減することができる。

【0032】

バッファ回路52,53が非アクティブ状態の場合、バッファ回路52,53の出力ノードは高インピーダンスとなる。したがって、バッファ回路52,53の状態に応じて、バッファ回路52,53の出力ノードのインピーダンスが大きく変化する。

【0033】

バッファ回路52,53の出力ノードには、それぞれ出力端子T7,T6を介して、外部接続用端子47,46が接続される。そのため、バッファ回路52,53の出力ノードから外部接続用端子47,46までの配線に近い他の配線があると、バッファ回路52,53の出力が他の配線に影響を及ぼす場合がある。

【0034】

例えば、圧電振動素子20とIC素子30とを接続する配線(以下、第1の配線と記載する)と、バッファ回路52,53の出力ノードから外部接続用端子47,46までの配線(以下、第2の配線と記載する)とが近接している場合を考える。

【0035】

バッファ回路52,53がアクティブである場合、バッファ回路52,53の出力ノードは低インピーダンスであるが、バッファ回路52,53が非アクティブである場合、バッファ回路52,53の出力ノードは高インピーダンスである。そのため、第1の配線と第2の配線とが近接することによって圧電振動素子20の発振周波数に対して無視できない大きさの寄生容量が第1の配線と第2の配線との間に形成されると、バッファ回路52,53の出力状態が第1の配線へ影響を及ぼす。

【0036】

すなわち、第1の配線は、圧電振動素子20を発振させるための配線であるため、バッファ回路52,53の出力状態によって、圧電振動素子20への負荷状態が変化して圧電振動素子20の発振周波数が変化することになる。そして、このような発振周波数の変化が許容範囲外となる場合には、圧電発振器1において所望の出力特性を得ることが困難になる。

【0037】

以下、本実施形態に係る圧電発振器1の素子搭載部材10に形成される第1の導電路31と第2の導電路32(図3参照)について具体的に説明する。なお、第1の導電路31は、第1の配線のうち、圧電振動素子20とIC素子30とを接続する配線である。また、第2の導電路32は、第2の配線のうち、IC素子30と外部接続用端子46,47とを接続する配線である。

【0038】

図4は、素子搭載部材10内に形成される配線領域の構成を表す模式図である。なお、図4においては、説明の便宜上、各層の間隔を等間隔にしており、また、厚み方向(Z方向)に形成されるビア導体は省略している。

【0039】

図4に示すように、素子搭載部材10内に形成される配線領域55は、第1配線層56と、第2配線層57と、第3配線層58と、第4配線層59とを備える。第1配線層56において圧電振動素子20との接続が行われ、第3配線層58においてIC素子30との接続が行われ、第4配線層59において電子機器の搭載ボードへの接続が行われる。

【0040】

また、第1配線層56は絶縁層12の上面側に形成され、第2配線層57は絶縁層13の上面側に形成され、第3配線層58は絶縁層13の下面側に形成され、第4配線層59は絶縁層14の下面側に形成される。なお、各配線層の形成位置はこれに限定されるものではなく、例えば、第2配線層57が形成される位置は、絶縁層12の下面側としてもよい。

【0041】

まず、第1の導電路31(図3参照)について説明する。第1の導電路31は、第1配線層56と第3配線層58にかけて形成される。第1配線層56には、電極パッド41,42が形成される。かかる電極パッド41,42には、圧電振動素子20における一対の引出電極が接続される。第1配線層56の電極パッド41,42は、ビア導体を介してそれぞれ第2配線層57に形成された円形状の導体パターン60,61に接続される。なお、以下において、円形状の導体パターンをランドと記載する。

【0042】

第2配線層57のランド60,61は、ビア導体を介してそれぞれ第3配線層58に形成されたランド62,63に接続される。かかるランド62,63は、第3配線層58に形成される電極パッド91,92に接続される。電極パッド91,92には、IC素子30の端子T1,T2がそれぞれ接続される。

【0043】

このように、圧電振動素子20とIC素子30とを接続する第1の導電路31は、電極パッド41,42、ランド60〜63、電極パッド91,92、およびビア導体から構成される。

【0044】

電極パッド41,42、ランド60,61およびランド62,63は、積層方向(ここでは、Z方向)から見た場合に、互いに重なる位置関係となり、ビア導体によって積層方向に接続される。また、IC素子30の端子T1,T2が接続される電極パッド91,92はランド62,63に重なって形成される。したがって、第1の導電路31を大幅に短くすることができ、また、積層方向における第1の導電路31の占有面積を大幅に小さくすることができる。

【0045】

なお、第2配線層57では、ランド60,61の周囲を除き全体的にグランドパターン82が形成される。このようにグランドパターンを形成することによって、グランドパターン面積を増加させることができるため、圧電発振器1を安定的に動作させることができる。

【0046】

次に、第2の導電路32(図3参照)について説明する。第2の導電路32は、第3配線層58および素子搭載部材10の側面に形成される。

【0047】

第3配線層58には、IC素子30の出力端子T6,T7が接続される電極パッド96,97と、電極パッド96,97にそれぞれ一端が接続され、外周方向へ向かう配線70,71と、配線70の中途部に配置されるランド65とが形成される。

【0048】

ランド65は、ビア導体を介して外部接続用端子46の一端に接続される。ビア導体が接続される外部接続用端子46の一端は、IC素子30の出力端子T6が接続される電極パッド96とX方向で最も距離が短い位置にある。そのため、IC素子30の出力端子T6と外部接続用端子46とは最短距離で接続される。

【0049】

また、配線71は、素子搭載部材10の側面に形成された不図示の導体によって、外部接続用端子47と接続される。そのため、IC素子30の出力端子T7が接続される電極パッド97と外部接続用端子47とは、ほぼ最短距離で接続される。

【0050】

ここで、第1の導電路31と第2の導電路32の積層方向における位置関係について図5を用いて説明する。図5は、配線領域55を積層方向から見た場合の第1の導電路31および第2の導電路32の位置関係を示す図であり、説明を分かり易くするために、第1の導電路31と第2の導電路32以外の配線を省略している。

【0051】

図5に示すように、第1の導電路31と第2の導電路32とは、積層方向(Z方向)で重なることなく配置される。第1の導電路31と第2の導電路32が積層方向で重なった場合、第1の導電路31と第2の導電路32の間で寄生容量が生じる。この寄生容量は、配線領域の層間距離が短いほど大きくなるが、第1の実施形態に係る圧電発振器1では、このような寄生容量の発生を抑制することができる。そのため、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0052】

また、第3配線層58内においても、導電路31,32間で、出力特性の安定に影響を及ぼす寄生容量が生じない距離となるように、第1の導電路31を構成する電極パッド91,92と、第2の導電路32を構成する電極パッド96,97とを隣接させていない。なお、第3配線層58内において第1の導電路31と第2の導電路32との間の距離は、配線領域55の層間距離よりも長い距離であり、配線領域55の層間距離は、例えば、第2配線層57と第3配線層58との間の距離である。

【0053】

図6は、第3配線層58の配線状態を示す図である。図6に示すように、圧電振動素子20に接続される電極パッド91,92には、電源電圧VCCが入力される電極パッド93と、制御信号CONT2が入力される電極パッド94が隣接しており、電極パッド96,97とは隣接しない。

【0054】

しかも、圧電振動素子20に接続される電極パッド91,92に隣接する電極パッド93,94は、出力信号OUT1,2のような高周波信号ではなく、直流電圧が入力される電極である。そのため、出力信号OUT1,2が出力される電極パッド97,96が電極パッド91,92に隣接する場合に比べ、隣接する電極からの輻射などの影響が低い。そのため、所望の出力特性をさらに安定して得ることができる。

【0055】

なお、電極パッド94に入力される制御信号CONT2は、Highレベルの直流電圧またはLowレベルの直流電圧であるが、その切り替わりで変化する信号でもある。すなわち、出力端子T6からの信号の出力状態が変更される場合、制御信号CONT2は、HighレベルからLowレベルへ、または、LowレベルからHighレベルへ変化する。そのため、圧電振動素子20に接続される電極パッド92に隣接する電極を、より変動がない電極、例えば、グランドが接続される電極パッドとすることで、所望の出力特性をさらに安定して得ることができる。

【0056】

このように、第1の導電路31は、配線領域55の積層方向において、第2の導電路32と交差しない位置に配置され、また、同一配線層内においても、第2の導電路32と層間距離よりも長い間隔を空けて配置される。これにより、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0057】

ここで、第3配線層58に形成されるモニタパッドについて説明する。図4〜図6においては、説明の便宜上、モニタパッドを省略したが、図7に示すように、第3配線層58には、一対のモニタパッドが形成される。図7は、第3配線層58の配線状態を示す図である。

【0058】

図7に示す一対のモニタパッド85,86は、圧電振動素子20に接続される。かかるモニタパッド85,86は、圧電振動素子20の特性を測定するために用いられる。具体的には、素子搭載部材10に圧電振動素子20を搭載した後、IC素子30を素子搭載部材10に搭載する前に、モニタパッド85,86に計測ピンの先端が押しつけられる。そして、モニタパッド85,86に計測ピンを介して計測用回路が接続され、かかる計測用回路によって圧電振動素子20の発振周波数やクリスタルインピーダンス等の特性が測定される。

【0059】

図7に示すように、圧電振動素子20の一端に接続される電極パッド91には、第1のモニタパッド85が接続され、圧電振動素子20の他端に接続される電極パッド92には、第2のモニタパッド86が接続される。これら一対のモニタパッド85,86は、第1の導電路31に接続されるため、第2の導電路32との位置関係を考慮して配置される。

【0060】

電極パッド91〜98間を含む領域99は、図5からも分かるように、積層方向において第2の導電路32とは交差しない領域であり、図7に示すように、一対のモニタパッド85,86が配置される。したがって、モニタパッド85,86と第2の導電路32とは、配線領域55の積層方向において交差しない。このようなモニタパッド85,86の配置によって、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0061】

また、第1のモニタパッド85は、電極パッド93,95寄りに配置され、第2のモニタパッド86は、圧電振動素子20に接続される電極パッド91と電極パッド92との間に配置される。したがって、第2の導電路32である電極パッド96,97とモニタパッド85,86との距離は、出力特性の安定に影響を及ぼす寄生容量が生じない距離となる。

【0062】

しかも、第2のモニタパッド86よりも第2の導電路32に近い第1のモニタパッド85は積層方向において第2配線層57のグランドパターン82と交差する位置となる。そのため、第2のモニタパッド86とグランドとの間に寄生容量が発生し、他の配線からの影響を受けにくくなる。これにより、所望の出力特性をさらに安定させることができる。

【0063】

なお、モニタパッド85,86の配置は、図7に示す位置に限られない。例えば、モニタパッド85,86は、配線領域55の積層方向において、第2の導電路32と交差しない位置に配置され、同一配線層内においても、第2の導電路32との間隔が層間距離よりも長い距離となるように配置されることで、所望の出力特性を安定して得ることができる。

【0064】

次に、圧電発振器1が搭載される電子機器について図8を用いて説明する。図8は、電子機器100のブロック図である。なお、電子機器100は、ここでは、携帯電話機やスマートフォンといったモバイル端末の例を説明するが、これに限定されるものではなく、例えば、パーソナルコンピュータなどであってもよい。

【0065】

図8に示すように、電子機器100は、圧電発振器1と、制御回路101と、信号処理回路102と、無線回路103と、アンテナ104とを備える。なお、その他の電子部材(例えば、ディスプレイ、マイク、スピーカなどのデバイスや回路)については記載を省略している。また、図8には、1つの圧電発振器1を例示したが、2つ以上の圧電発振器1やその他の発振器を設けることとしてもよい。

【0066】

制御回路101は、信号処理回路102や無線回路103を含む電子機器100全体を制御する。圧電発振器1の出力信号OUT1は、信号処理回路102に入力され、圧電発振器1の出力信号OUT2は、無線回路103に入力される。

【0067】

そして、制御回路101は、圧電発振器1に対して制御信号CONT1,CONT2を出力して圧電発振器1の出力状態を制御する。これにより、信号処理回路102および無線回路103への信号入力が制御される。すなわち、信号処理回路102を停止させる場合には、圧電発振器1からの出力信号OUT1の出力を停止させることができる。また、無線回路103を停止させる場合には、圧電発振器1からの出力信号OUT2の出力を停止させることができるため、消費電力を低減させることができる。

【0068】

既に説明したように、圧電発振器1は、複数の出力端子T6,T7に対する出力状態が変化した場合であっても出力特性の変動を抑制することができる。このため、電子機器100を安定して動作させることができる。

【0069】

上述してきたように、第1の実施形態に係る圧電発振器1では、第1の導電路31が配線領域55の積層方向において、第2の導電路32と交差しない位置に配置されることとした。したがって、第1の実施形態に係る圧電発振器1によれば、複数の出力端子T6,T7に対する出力状態が変化した場合であっても出力特性の変動を抑制することができる。

【0070】

また、第1の実施形態に係る圧電発振器1では、第1の導電路31が同一配線層内において、第2の導電路32との間隔が層間距離よりも長くなるように配置されることとした。これにより、複数の出力端子T6,T7に対する出力状態が変化した場合であっても出力特性の変動をさらに抑制することができる。

【0071】

ところで、上述した第1の実施形態では、配線領域55における配置および圧電発振器1の回路構成についての一例を例示した。しかしながら、配線領域における配置および圧電発振器の回路構成には種々のバリエーションが存在する。そこで、以下に示す各実施形態では、その他の例について示すこととする。

【0072】

また、以下に示す各実施形態においては、上述した第1の実施形態の構成要素に対応する構成要素には同一の符号を付し、第1の実施形態と重複する説明については適宜、省略する。

【0073】

(第2の実施形態)

次に、第2の実施形態に係る圧電発振器について、図9および図10を用いて説明する。図9は、第2の実施形態に係る圧電発振器の素子搭載部材に形成される配線領域の構成を表す模式図である。また、図10は、第3配線層の配線状態を示す図である。図9に示すように、第2の実施形態に係る圧電発振器1Aは、配線領域55Aにおける第2および第3配線層57A,58Aの配線パターンが、第1の実施形態に係る圧電発振器1(図4参照)の配線領域55とは異なる。

【0074】

図9に示すように、圧電発振器1Aでは、第3配線層58Aにおいて、圧電振動素子20に接続される電極パッド91,92は、出力信号OUT1,OUT2が出力される電極パッド97,96と隣接する位置に配置される。

【0075】

電極パッド91と電極パッド97との間は、出力端子T7,T6からの出力信号OUT1,OUT2の出力状態を制御した場合であっても、出力特性の安定に影響を及ぼす寄生容量が生じない距離(以下、許容距離と記載する)に設定される。また、電極パッド92と電極パッド96との間も同様に許容距離に設定される。なお、許容距離は、第2配線層57Aと第3配線層58Aとの層間距離よりも長い。

【0076】

また、図10に示すように、第1の導電路31と第2の導電路32とは、第1の実施形態に係る圧電発振器1と同様に、積層方向(Z方向)において、交差しない位置に配置される。

【0077】

このように、第2の実施形態に係る圧電発振器1Aでは、第1の導電路31と第2の導電路32とが、積層方向において交差せず、また、同一配線層においても、許容距離以上に配置される。これにより、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0078】

(第3の実施形態)

次に、第3の実施形態に係る圧電発振器について説明する。図11は、第3の実施形態に係る圧電発振器の回路ブロック図である。なお、図11においては、説明を分かり易くするために、図3に示す圧電発振器1の構成と異なる点を主に記載しており、同様の構成は省略している。また、第1および第2の実施形態に係る圧電発振器1,1Aは、周波数が同一の出力信号を出力端子T6,T7から出力したが、第3の実施形態に係る圧電発振器では周波数が異なる出力信号を出力端子T6,T7から出力する点で異なる。

【0079】

図11に示すように、第3の実施形態に係る圧電発振器1BのIC素子30Aでは、分周回路54を備え、発振回路51の出力に代えて分周回路54の出力がバッファ回路53へ入力される。分周回路54は、圧電振動素子20の発振周波数に応じた信号を発振回路51から取得し、取得した信号を分周してバッファ回路53へ出力する。

【0080】

かかる圧電発振器1Bにおいては、第1の実施形態や第2の実施形態と同様に素子搭載部材の配線領域が構成される。そのため、異なる周波数の信号に対しても所望の出力特性を安定して得ることができる。

【0081】

なお、図11に示す構成では、発振回路51から取得した信号を分周して出力する分周回路54を設けることとしたが、これに限定されるものではない。例えば、分周回路54に代えて、発振回路51から取得した信号を逓倍して出力する逓倍回路を設けるようにしてもよい。この場合においても、異なる周波数の信号に対しても所望の出力特性を安定して得ることができる。

【0082】

また、図11に示す回路ブロックでは、一つの圧電振動素子20によって異なる周波数を出力するようにしたが、これに限定されるものではない。例えば、図12に示す圧電発振器1Cのように、複数の圧電振動素子20,20Aと、これら圧電振動素子20,20Aをそれぞれ発振させる発振回路51,51Aとを設けるようにしてもよい。図12は、第3の実施形態に係る圧電発振器の他の回路ブロック図である。なお、図12においては、説明を分かり易くするために、図11と同様に、図3に示す圧電発振器1の構成と異なる点を主に記載しており、同様の構成は省略している。

【0083】

IC素子30Bの発振回路51Aは、圧電振動素子20Aの発振周波数に応じた信号を生成してバッファ回路53へ出力する。圧電振動素子20Aの発振周波数は、圧電振動素子20の発振周波数とは異なる。そのため、圧電発振器1Cでは、異なる圧電振動素子20,20Aに基づいて生成された異なる周波数の信号が出力端子T6,T7から出力される。

【0084】

かかる圧電発振器1Cにおいては、第1の実施形態や第2の実施形態と同様に素子搭載部材の配線領域が構成される。そのため、異なる周波数の信号に対しても所望の出力特性を安定して得ることができる。

【0085】

なお、圧電発振器1Cにおいては、圧電振動素子20と発振回路51との間の配線が出力端子T7と外部接続用端子47との間の配線に近接した場合であっても、出力端子T7からの出力特性は変動しない。同様に、圧電振動素子20Aと発振回路51Aとの間の配線が出力端子T6と外部接続用端子46との間の配線に近接した場合であっても、出力端子T6からの出力特性は変動しない。

【0086】

したがって、次のような配線状態としてもよい。すなわち、発振回路51と圧電振動素子20との間の第1の導電路31は、出力端子T6と外部接続用端子46との間の第2の導電路32に対して、配線領域の積層方向において交差せず、かつ同一配線層内で層間距離より長い間隔を空ける。また、発振回路51Aと圧電振動素子20Aとの間の第1の導電路31は、出力端子T7と外部接続用端子47との間の第2の導電路32に対して、配線領域の積層方向において交差せず、かつ同一配線層内で層間距離より長い間隔を空けるようにする。このようにすることによっても、異なる周波数の信号に対しても所望の出力特性を安定して得ることができ、また、第1の導電路31および第2の導電路32における配線制限を緩和することができる。

【0087】

さらなる効果や変形例は、当業者によって容易に導き出すことができる。このため、本発明のより広範な態様は、以上のように表しかつ記述した特定の詳細および代表的な実施形態に限定されるものではない。したがって、添付の特許請求の範囲およびその均等物によって定義される総括的な発明の概念の精神または範囲から逸脱することなく、様々な変更が可能である。

【0088】

例えば、上述した圧電発振器1,1A〜1Cでは、IC素子30において2つの出力端子T6,T7から出力する信号の状態を制御するものであるが、出力信号の数や出力端子の数はこれに限定されるものではない。例えば、3つ以上の出力端子から出力する信号の状態を制御するものであってもよい。また、複数の出力端子のいずれについても信号の出力状態を制御することとしたが、一部のみの出力端子からの信号の出力状態を制御するものであってもよい。

【符号の説明】

【0089】

1,1A,1B,1C 圧電発振器

10 素子搭載部材

20,20A 圧電振動素子

30,30A,30B IC素子(回路素子の一例)

31 第1の導電路

32 第2の導電路

46,47 外部接続用端子

51,51A 発振回路

55,55A 配線領域

85,86 モニタパッド

100 電子機器

SW1,SW2 スイッチ(制御回路の一例)

T6,T7 出力端子

【技術分野】

【0001】

開示の実施形態は、圧電発振器および電子機器に関する。

【背景技術】

【0002】

従来、携帯電話機などの電子機器には、基準信号源やクロック信号源などの信号源が搭載されており、かかる信号源として、圧電振動素子を搭載した圧電発振器が知られている。

【0003】

圧電発振器は、一つの出力端子から信号を出力するものが一般的であったが、近年では、出力端子を複数個備えた多出力型のものが開発されている。例えば、特許文献1に記載の電子機器には、2つの出力端子の一方が高周波回路に接続され、他方がデジタル回路に接続された多出力型の発振器が搭載される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−102323号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

多出力型の圧電発振器では、搭載される電子機器の動作状態に応じて複数の出力端子に対する信号の出力状態を制御した場合であっても所望の出力特性が得られることが望まれる。

【0006】

実施形態の一態様は、上記に鑑みてなされたものであって、複数の出力端子からの信号の出力状態を制御した場合であっても、所望の出力特性を得ることができる圧電発振器および電子機器を提供することを目的とする。

【課題を解決するための手段】

【0007】

実施形態の一態様に係る圧電発振器は、圧電振動素子と、回路素子と、素子搭載部材とを備える。前記回路素子は、前記圧電振動素子に接続され、前記圧電振動素子の振動に応じた出力信号を生成する発振回路と、複数の出力端子と、前記複数の出力端子からの前記出力信号の出力状態を制御する制御回路とを有する。前記素子搭載部材は、複数の外部接続用端子が形成されると共に、前記圧電振動素子と前記回路素子とを電気的に接続する第1の導電路と、前記出力端子と前記外部接続用端子とを電気的に接続する第2の導電路とを含む多層の配線領域が形成される。前記第1の導電路と前記第2の導電路とは、前記配線領域の積層方向において交差しない。

【発明の効果】

【0008】

実施形態の一態様の圧電発振器によれば、複数の出力端子からの信号の出力状態を制御した場合であっても、所望の出力特性を得ることができる。

【図面の簡単な説明】

【0009】

【図1】図1は、第1の実施形態に係る圧電発振器の分解斜視図である。

【図2】図2は、図1に示すA−A線断面図である。

【図3】図3は、第1の実施形態に係る圧電発振器の回路ブロック図である。

【図4】図4は、図1に示す素子搭載部材に形成される配線領域の構成を表す模式図である。

【図5】図5は、配線領域の積層方向から見た場合の第1の導電路および第2の導電路の位置関係を示す図である。

【図6】図6は、第3配線層の配線状態を示す図である。

【図7】図7は、第3配線層に形成されるモニタパッドの位置を示す図である。

【図8】図8は、電子機器のブロック図である。

【図9】図9は、第2の実施形態に係る圧電発振器の素子搭載部材に形成される配線領域の構成を表す模式図である。

【図10】図10は、図9に示す第3配線層の配線状態を示す図である。

【図11】図11は、第3の実施形態に係る圧電発振器の回路ブロック図である。

【図12】図12は、第3の実施形態に係る圧電発振器の他の回路ブロック図である。

【発明を実施するための形態】

【0010】

以下、添付図面を参照して、本願の開示する圧電発振器および電子機器の実施形態を詳細に説明する。なお、以下に示す各実施形態によりこの発明が限定されるものではない。

【0011】

(第1の実施形態)

第1の実施形態に係る圧電発振器について、図1および図2を用いて説明する。図1は、第1の実施形態に係る圧電発振器の分解斜視図であり、図2は、図1に示すA−A線断面図である。なお、以下の説明においては、電子機器の実装ボードへの圧電発振器の搭載面を「下面」と、かかる下面と対向する面を「上面」と、それぞれ記載する。

【0012】

図1および図2に示すように、第1の実施形態に係る圧電発振器1は、素子搭載部材10と、圧電振動素子20と、IC(Integrated Circuit:集積回路)素子30と、蓋部材40とを備える。かかる圧電発振器1は、圧電振動素子20の振動に応じた出力信号を複数の出力端子から出力することができ、また、一部の出力端子のみから出力信号を出力することができる。

【0013】

素子搭載部材10は、圧電振動素子20およびIC素子30を搭載する役割と、各電子部材同士を電気的に接続する役割とを兼用する。かかる素子搭載部材10は、セラミックのシートを所定の形状に切断した絶縁層11〜14を積層して圧着させ、加熱することによって形成される。

【0014】

各絶縁層11〜14には導電ペーストなどが従来周知のスクリーン印刷によって塗布されてビア導体、配線および電極パッドが形成される。なお、以下の説明では、ビア導体、配線および電極パッドを単に配線と記載する場合があり、また、配線が形成される領域を配線領域と記載する場合がある。

【0015】

絶縁層11および絶縁層14は、平面視(Z方向視)した場合に、中央部が開口した略枠状の形状を有しており、絶縁層12,13は、開口がない略矩形平板状の形状を有している。絶縁層11および絶縁層12によって上面側凹部15が形成され、絶縁層13および絶縁層14によって下面側凹部16が形成される。

【0016】

圧電振動素子20は、素子搭載部材10の上面側凹部15内に配置される。圧電振動素子20は、略矩形の圧電片と、圧電片の両主面にそれぞれ形成された一対の励振電極と、一対の励振電極にそれぞれ電気的に接続された一対の引出電極とを含む。圧電片として、例えば、所定の結晶方位角に従ってカットされた略矩形の水晶基板が用いられる。なお、図1および図2では、いわゆる「平板型」の圧電振動素子20を例示したが、例えば、「音叉型」の圧電振動素子20を用いることとしてもよい。

【0017】

圧電振動素子20における一対の引出電極は、素子搭載部材10の上面側凹部15内に形成された一対の電極パッド41,42へ導電性接着剤18によってそれぞれ電気的かつ機械的に接続される。なお、導電性接着剤18は、例えば、シリコーン樹脂等のバインダーの中に導電フィラーとして導電性粉末(例えば銀粉(Ag))を含有している。

【0018】

素子搭載部材10における略枠状の上面には電極17が設けられ、蓋部材40の下面には素子搭載部材10の上面と対向する位置に電極が設けられる。そして、素子搭載部材10の上面側凹部15内に圧電振動素子20が配置された状態で、蓋部材40の電極が、素子搭載部材10の電極17へ、例えば、シーム溶接によって接合される。

【0019】

素子搭載部材10における略枠状の下面には、外部接続用端子43〜48が形成される。これら外部接続用端子43〜48は、電子機器の実装ボード上の電極に接続される。

【0020】

また、素子搭載部材10の下面側凹部16内には、IC素子30が配置される。絶縁層13の下面側には、後述するように複数の電極パッド91〜98(図6参照)が形成されており、かかる電極パッド91〜98にIC素子30の上面側に形成された端子T1〜T8が接続される。電極パッド91〜98と端子T1〜T8との接続は、例えば、GGI接合(GOLD TO GOLD INTERCONNECTION:金―金接合)や半田接合等により金や半田等の導電性接着剤19によって行われる。

【0021】

図3は、圧電発振器1の回路ブロック図である。図3に示すように、圧電発振器1は、圧電振動素子20と、IC素子30と、外部接続用端子43〜48とを備える。かかる圧電発振器1は、外部接続用端子48にグランド電位が印加され、外部接続用端子43に電源電圧VCCが入力されて動作する。

【0022】

IC素子30は、発振回路51と、バッファ回路52,53と、スイッチSW1,SW2と、端子T1〜T8とを備える。かかるIC素子30は、端子T8にグランド(GND)が接続され、端子T3に電源電圧VCCが入力されて動作する。

【0023】

発振回路51は、端子T1,T2を介して圧電振動素子20における一対の引出電極に接続され、圧電振動素子20を所定の周波数で発振させて圧電振動素子20の発振周波数に応じた信号を生成する。

【0024】

発振回路51によって生成された信号はバッファ回路52,53へ入力される。バッファ回路52,53の出力はそれぞれ端子T7,T6(以下、出力端子T7,T6と記載する場合がある)を介して外部接続用端子47,46に接続されており、圧電振動素子20の発振周波数に応じた信号が外部接続用端子47,46から外部へ出力される。なお、発振回路51は、温度補償回路を含んでいてもよい。

【0025】

バッファ回路52には、スイッチSW1を介して電源電圧VCCが入力される。スイッチSW1は、端子T5を介して外部接続用端子45に接続され、外部接続用端子45へ入力される制御信号CONT1によって制御される。同様に、バッファ回路53には、スイッチSW2を介して電源電圧VCCが入力される。スイッチSW2は、端子T4を介して外部接続用端子44に接続され、外部接続用端子44へ入力される制御信号CONT2によって制御される。このように、制御回路の一例であるスイッチSW1,SW2を制御することによって、出力端子T7,T6からの信号の出力状態が制御される。

【0026】

ここで、制御信号CONT1,CONT2の状態と、IC素子30内部の状態および出力端子T7,T6からの出力信号OUT1,OUT2の出力状態との関係を下記表1に示す。表1においては、バッファ回路52を「バッファ1」と記載し、バッファ回路53を「バッファ2」と記載する。なお、ここでは、制御信号CONT1,CONT2は、Highアクティブの信号であるが、これに限定されるものではない。

【0027】

【表1】

【0028】

上記表1に示すように、制御信号CONT1,CONT2の状態に応じて、出力端子T7,T6からの信号の出力状態が変化する。例えば、制御信号CONT1,CONT2が共にHighレベルである場合、スイッチSW1,SW2がON状態となってバッファ回路52,53へ電源電圧VCCが供給され、バッファ回路52,53がアクティブとなる。そのため、出力端子T7,T6から出力信号OUT1,OUT2が同時に出力される。

【0029】

一方、制御信号CONT1がHighレベルであり、制御信号CONT2がLowレベルである場合、スイッチSW2はOFF状態であるため、バッファ回路53へは電源電圧VCCが供給されず、バッファ回路53は非アクティブである。そのため、出力端子T6から出力信号OUT2は出力されず、出力端子T7のみから出力信号OUT1が出力される。

【0030】

また、制御信号CONT1がLowレベルであり、制御信号CONT2がHighレベルである場合、スイッチSW1がOFF状態であるため、バッファ回路52へ電源電圧VCCが供給されず、バッファ回路52は非アクティブである。そのため、出力端子T7から出力信号OUT1は出力されず、出力端子T6のみから出力信号OUT2が出力される。

【0031】

このように圧電発振器1では、バッファ回路52,53の状態をそれぞれアクティブ状態と非アクティブ状態とで切り替えることによって、出力端子T7,T6からの信号の出力状態を切り替える。また、バッファ回路52,53の一方を非アクティブ状態にすることで、出力端子T7,T6のうち一方の出力端子のみから出力信号を出力する場合の消費電力を低減することができる。

【0032】

バッファ回路52,53が非アクティブ状態の場合、バッファ回路52,53の出力ノードは高インピーダンスとなる。したがって、バッファ回路52,53の状態に応じて、バッファ回路52,53の出力ノードのインピーダンスが大きく変化する。

【0033】

バッファ回路52,53の出力ノードには、それぞれ出力端子T7,T6を介して、外部接続用端子47,46が接続される。そのため、バッファ回路52,53の出力ノードから外部接続用端子47,46までの配線に近い他の配線があると、バッファ回路52,53の出力が他の配線に影響を及ぼす場合がある。

【0034】

例えば、圧電振動素子20とIC素子30とを接続する配線(以下、第1の配線と記載する)と、バッファ回路52,53の出力ノードから外部接続用端子47,46までの配線(以下、第2の配線と記載する)とが近接している場合を考える。

【0035】

バッファ回路52,53がアクティブである場合、バッファ回路52,53の出力ノードは低インピーダンスであるが、バッファ回路52,53が非アクティブである場合、バッファ回路52,53の出力ノードは高インピーダンスである。そのため、第1の配線と第2の配線とが近接することによって圧電振動素子20の発振周波数に対して無視できない大きさの寄生容量が第1の配線と第2の配線との間に形成されると、バッファ回路52,53の出力状態が第1の配線へ影響を及ぼす。

【0036】

すなわち、第1の配線は、圧電振動素子20を発振させるための配線であるため、バッファ回路52,53の出力状態によって、圧電振動素子20への負荷状態が変化して圧電振動素子20の発振周波数が変化することになる。そして、このような発振周波数の変化が許容範囲外となる場合には、圧電発振器1において所望の出力特性を得ることが困難になる。

【0037】

以下、本実施形態に係る圧電発振器1の素子搭載部材10に形成される第1の導電路31と第2の導電路32(図3参照)について具体的に説明する。なお、第1の導電路31は、第1の配線のうち、圧電振動素子20とIC素子30とを接続する配線である。また、第2の導電路32は、第2の配線のうち、IC素子30と外部接続用端子46,47とを接続する配線である。

【0038】

図4は、素子搭載部材10内に形成される配線領域の構成を表す模式図である。なお、図4においては、説明の便宜上、各層の間隔を等間隔にしており、また、厚み方向(Z方向)に形成されるビア導体は省略している。

【0039】

図4に示すように、素子搭載部材10内に形成される配線領域55は、第1配線層56と、第2配線層57と、第3配線層58と、第4配線層59とを備える。第1配線層56において圧電振動素子20との接続が行われ、第3配線層58においてIC素子30との接続が行われ、第4配線層59において電子機器の搭載ボードへの接続が行われる。

【0040】

また、第1配線層56は絶縁層12の上面側に形成され、第2配線層57は絶縁層13の上面側に形成され、第3配線層58は絶縁層13の下面側に形成され、第4配線層59は絶縁層14の下面側に形成される。なお、各配線層の形成位置はこれに限定されるものではなく、例えば、第2配線層57が形成される位置は、絶縁層12の下面側としてもよい。

【0041】

まず、第1の導電路31(図3参照)について説明する。第1の導電路31は、第1配線層56と第3配線層58にかけて形成される。第1配線層56には、電極パッド41,42が形成される。かかる電極パッド41,42には、圧電振動素子20における一対の引出電極が接続される。第1配線層56の電極パッド41,42は、ビア導体を介してそれぞれ第2配線層57に形成された円形状の導体パターン60,61に接続される。なお、以下において、円形状の導体パターンをランドと記載する。

【0042】

第2配線層57のランド60,61は、ビア導体を介してそれぞれ第3配線層58に形成されたランド62,63に接続される。かかるランド62,63は、第3配線層58に形成される電極パッド91,92に接続される。電極パッド91,92には、IC素子30の端子T1,T2がそれぞれ接続される。

【0043】

このように、圧電振動素子20とIC素子30とを接続する第1の導電路31は、電極パッド41,42、ランド60〜63、電極パッド91,92、およびビア導体から構成される。

【0044】

電極パッド41,42、ランド60,61およびランド62,63は、積層方向(ここでは、Z方向)から見た場合に、互いに重なる位置関係となり、ビア導体によって積層方向に接続される。また、IC素子30の端子T1,T2が接続される電極パッド91,92はランド62,63に重なって形成される。したがって、第1の導電路31を大幅に短くすることができ、また、積層方向における第1の導電路31の占有面積を大幅に小さくすることができる。

【0045】

なお、第2配線層57では、ランド60,61の周囲を除き全体的にグランドパターン82が形成される。このようにグランドパターンを形成することによって、グランドパターン面積を増加させることができるため、圧電発振器1を安定的に動作させることができる。

【0046】

次に、第2の導電路32(図3参照)について説明する。第2の導電路32は、第3配線層58および素子搭載部材10の側面に形成される。

【0047】

第3配線層58には、IC素子30の出力端子T6,T7が接続される電極パッド96,97と、電極パッド96,97にそれぞれ一端が接続され、外周方向へ向かう配線70,71と、配線70の中途部に配置されるランド65とが形成される。

【0048】

ランド65は、ビア導体を介して外部接続用端子46の一端に接続される。ビア導体が接続される外部接続用端子46の一端は、IC素子30の出力端子T6が接続される電極パッド96とX方向で最も距離が短い位置にある。そのため、IC素子30の出力端子T6と外部接続用端子46とは最短距離で接続される。

【0049】

また、配線71は、素子搭載部材10の側面に形成された不図示の導体によって、外部接続用端子47と接続される。そのため、IC素子30の出力端子T7が接続される電極パッド97と外部接続用端子47とは、ほぼ最短距離で接続される。

【0050】

ここで、第1の導電路31と第2の導電路32の積層方向における位置関係について図5を用いて説明する。図5は、配線領域55を積層方向から見た場合の第1の導電路31および第2の導電路32の位置関係を示す図であり、説明を分かり易くするために、第1の導電路31と第2の導電路32以外の配線を省略している。

【0051】

図5に示すように、第1の導電路31と第2の導電路32とは、積層方向(Z方向)で重なることなく配置される。第1の導電路31と第2の導電路32が積層方向で重なった場合、第1の導電路31と第2の導電路32の間で寄生容量が生じる。この寄生容量は、配線領域の層間距離が短いほど大きくなるが、第1の実施形態に係る圧電発振器1では、このような寄生容量の発生を抑制することができる。そのため、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0052】

また、第3配線層58内においても、導電路31,32間で、出力特性の安定に影響を及ぼす寄生容量が生じない距離となるように、第1の導電路31を構成する電極パッド91,92と、第2の導電路32を構成する電極パッド96,97とを隣接させていない。なお、第3配線層58内において第1の導電路31と第2の導電路32との間の距離は、配線領域55の層間距離よりも長い距離であり、配線領域55の層間距離は、例えば、第2配線層57と第3配線層58との間の距離である。

【0053】

図6は、第3配線層58の配線状態を示す図である。図6に示すように、圧電振動素子20に接続される電極パッド91,92には、電源電圧VCCが入力される電極パッド93と、制御信号CONT2が入力される電極パッド94が隣接しており、電極パッド96,97とは隣接しない。

【0054】

しかも、圧電振動素子20に接続される電極パッド91,92に隣接する電極パッド93,94は、出力信号OUT1,2のような高周波信号ではなく、直流電圧が入力される電極である。そのため、出力信号OUT1,2が出力される電極パッド97,96が電極パッド91,92に隣接する場合に比べ、隣接する電極からの輻射などの影響が低い。そのため、所望の出力特性をさらに安定して得ることができる。

【0055】

なお、電極パッド94に入力される制御信号CONT2は、Highレベルの直流電圧またはLowレベルの直流電圧であるが、その切り替わりで変化する信号でもある。すなわち、出力端子T6からの信号の出力状態が変更される場合、制御信号CONT2は、HighレベルからLowレベルへ、または、LowレベルからHighレベルへ変化する。そのため、圧電振動素子20に接続される電極パッド92に隣接する電極を、より変動がない電極、例えば、グランドが接続される電極パッドとすることで、所望の出力特性をさらに安定して得ることができる。

【0056】

このように、第1の導電路31は、配線領域55の積層方向において、第2の導電路32と交差しない位置に配置され、また、同一配線層内においても、第2の導電路32と層間距離よりも長い間隔を空けて配置される。これにより、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0057】

ここで、第3配線層58に形成されるモニタパッドについて説明する。図4〜図6においては、説明の便宜上、モニタパッドを省略したが、図7に示すように、第3配線層58には、一対のモニタパッドが形成される。図7は、第3配線層58の配線状態を示す図である。

【0058】

図7に示す一対のモニタパッド85,86は、圧電振動素子20に接続される。かかるモニタパッド85,86は、圧電振動素子20の特性を測定するために用いられる。具体的には、素子搭載部材10に圧電振動素子20を搭載した後、IC素子30を素子搭載部材10に搭載する前に、モニタパッド85,86に計測ピンの先端が押しつけられる。そして、モニタパッド85,86に計測ピンを介して計測用回路が接続され、かかる計測用回路によって圧電振動素子20の発振周波数やクリスタルインピーダンス等の特性が測定される。

【0059】

図7に示すように、圧電振動素子20の一端に接続される電極パッド91には、第1のモニタパッド85が接続され、圧電振動素子20の他端に接続される電極パッド92には、第2のモニタパッド86が接続される。これら一対のモニタパッド85,86は、第1の導電路31に接続されるため、第2の導電路32との位置関係を考慮して配置される。

【0060】

電極パッド91〜98間を含む領域99は、図5からも分かるように、積層方向において第2の導電路32とは交差しない領域であり、図7に示すように、一対のモニタパッド85,86が配置される。したがって、モニタパッド85,86と第2の導電路32とは、配線領域55の積層方向において交差しない。このようなモニタパッド85,86の配置によって、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0061】

また、第1のモニタパッド85は、電極パッド93,95寄りに配置され、第2のモニタパッド86は、圧電振動素子20に接続される電極パッド91と電極パッド92との間に配置される。したがって、第2の導電路32である電極パッド96,97とモニタパッド85,86との距離は、出力特性の安定に影響を及ぼす寄生容量が生じない距離となる。

【0062】

しかも、第2のモニタパッド86よりも第2の導電路32に近い第1のモニタパッド85は積層方向において第2配線層57のグランドパターン82と交差する位置となる。そのため、第2のモニタパッド86とグランドとの間に寄生容量が発生し、他の配線からの影響を受けにくくなる。これにより、所望の出力特性をさらに安定させることができる。

【0063】

なお、モニタパッド85,86の配置は、図7に示す位置に限られない。例えば、モニタパッド85,86は、配線領域55の積層方向において、第2の導電路32と交差しない位置に配置され、同一配線層内においても、第2の導電路32との間隔が層間距離よりも長い距離となるように配置されることで、所望の出力特性を安定して得ることができる。

【0064】

次に、圧電発振器1が搭載される電子機器について図8を用いて説明する。図8は、電子機器100のブロック図である。なお、電子機器100は、ここでは、携帯電話機やスマートフォンといったモバイル端末の例を説明するが、これに限定されるものではなく、例えば、パーソナルコンピュータなどであってもよい。

【0065】

図8に示すように、電子機器100は、圧電発振器1と、制御回路101と、信号処理回路102と、無線回路103と、アンテナ104とを備える。なお、その他の電子部材(例えば、ディスプレイ、マイク、スピーカなどのデバイスや回路)については記載を省略している。また、図8には、1つの圧電発振器1を例示したが、2つ以上の圧電発振器1やその他の発振器を設けることとしてもよい。

【0066】

制御回路101は、信号処理回路102や無線回路103を含む電子機器100全体を制御する。圧電発振器1の出力信号OUT1は、信号処理回路102に入力され、圧電発振器1の出力信号OUT2は、無線回路103に入力される。

【0067】

そして、制御回路101は、圧電発振器1に対して制御信号CONT1,CONT2を出力して圧電発振器1の出力状態を制御する。これにより、信号処理回路102および無線回路103への信号入力が制御される。すなわち、信号処理回路102を停止させる場合には、圧電発振器1からの出力信号OUT1の出力を停止させることができる。また、無線回路103を停止させる場合には、圧電発振器1からの出力信号OUT2の出力を停止させることができるため、消費電力を低減させることができる。

【0068】

既に説明したように、圧電発振器1は、複数の出力端子T6,T7に対する出力状態が変化した場合であっても出力特性の変動を抑制することができる。このため、電子機器100を安定して動作させることができる。

【0069】

上述してきたように、第1の実施形態に係る圧電発振器1では、第1の導電路31が配線領域55の積層方向において、第2の導電路32と交差しない位置に配置されることとした。したがって、第1の実施形態に係る圧電発振器1によれば、複数の出力端子T6,T7に対する出力状態が変化した場合であっても出力特性の変動を抑制することができる。

【0070】

また、第1の実施形態に係る圧電発振器1では、第1の導電路31が同一配線層内において、第2の導電路32との間隔が層間距離よりも長くなるように配置されることとした。これにより、複数の出力端子T6,T7に対する出力状態が変化した場合であっても出力特性の変動をさらに抑制することができる。

【0071】

ところで、上述した第1の実施形態では、配線領域55における配置および圧電発振器1の回路構成についての一例を例示した。しかしながら、配線領域における配置および圧電発振器の回路構成には種々のバリエーションが存在する。そこで、以下に示す各実施形態では、その他の例について示すこととする。

【0072】

また、以下に示す各実施形態においては、上述した第1の実施形態の構成要素に対応する構成要素には同一の符号を付し、第1の実施形態と重複する説明については適宜、省略する。

【0073】

(第2の実施形態)

次に、第2の実施形態に係る圧電発振器について、図9および図10を用いて説明する。図9は、第2の実施形態に係る圧電発振器の素子搭載部材に形成される配線領域の構成を表す模式図である。また、図10は、第3配線層の配線状態を示す図である。図9に示すように、第2の実施形態に係る圧電発振器1Aは、配線領域55Aにおける第2および第3配線層57A,58Aの配線パターンが、第1の実施形態に係る圧電発振器1(図4参照)の配線領域55とは異なる。

【0074】

図9に示すように、圧電発振器1Aでは、第3配線層58Aにおいて、圧電振動素子20に接続される電極パッド91,92は、出力信号OUT1,OUT2が出力される電極パッド97,96と隣接する位置に配置される。

【0075】

電極パッド91と電極パッド97との間は、出力端子T7,T6からの出力信号OUT1,OUT2の出力状態を制御した場合であっても、出力特性の安定に影響を及ぼす寄生容量が生じない距離(以下、許容距離と記載する)に設定される。また、電極パッド92と電極パッド96との間も同様に許容距離に設定される。なお、許容距離は、第2配線層57Aと第3配線層58Aとの層間距離よりも長い。

【0076】

また、図10に示すように、第1の導電路31と第2の導電路32とは、第1の実施形態に係る圧電発振器1と同様に、積層方向(Z方向)において、交差しない位置に配置される。

【0077】

このように、第2の実施形態に係る圧電発振器1Aでは、第1の導電路31と第2の導電路32とが、積層方向において交差せず、また、同一配線層においても、許容距離以上に配置される。これにより、出力端子T6,T7からの信号の出力状態が変化した場合であっても、所望の出力特性を安定して得ることができる。

【0078】

(第3の実施形態)

次に、第3の実施形態に係る圧電発振器について説明する。図11は、第3の実施形態に係る圧電発振器の回路ブロック図である。なお、図11においては、説明を分かり易くするために、図3に示す圧電発振器1の構成と異なる点を主に記載しており、同様の構成は省略している。また、第1および第2の実施形態に係る圧電発振器1,1Aは、周波数が同一の出力信号を出力端子T6,T7から出力したが、第3の実施形態に係る圧電発振器では周波数が異なる出力信号を出力端子T6,T7から出力する点で異なる。

【0079】

図11に示すように、第3の実施形態に係る圧電発振器1BのIC素子30Aでは、分周回路54を備え、発振回路51の出力に代えて分周回路54の出力がバッファ回路53へ入力される。分周回路54は、圧電振動素子20の発振周波数に応じた信号を発振回路51から取得し、取得した信号を分周してバッファ回路53へ出力する。

【0080】

かかる圧電発振器1Bにおいては、第1の実施形態や第2の実施形態と同様に素子搭載部材の配線領域が構成される。そのため、異なる周波数の信号に対しても所望の出力特性を安定して得ることができる。

【0081】

なお、図11に示す構成では、発振回路51から取得した信号を分周して出力する分周回路54を設けることとしたが、これに限定されるものではない。例えば、分周回路54に代えて、発振回路51から取得した信号を逓倍して出力する逓倍回路を設けるようにしてもよい。この場合においても、異なる周波数の信号に対しても所望の出力特性を安定して得ることができる。

【0082】

また、図11に示す回路ブロックでは、一つの圧電振動素子20によって異なる周波数を出力するようにしたが、これに限定されるものではない。例えば、図12に示す圧電発振器1Cのように、複数の圧電振動素子20,20Aと、これら圧電振動素子20,20Aをそれぞれ発振させる発振回路51,51Aとを設けるようにしてもよい。図12は、第3の実施形態に係る圧電発振器の他の回路ブロック図である。なお、図12においては、説明を分かり易くするために、図11と同様に、図3に示す圧電発振器1の構成と異なる点を主に記載しており、同様の構成は省略している。

【0083】

IC素子30Bの発振回路51Aは、圧電振動素子20Aの発振周波数に応じた信号を生成してバッファ回路53へ出力する。圧電振動素子20Aの発振周波数は、圧電振動素子20の発振周波数とは異なる。そのため、圧電発振器1Cでは、異なる圧電振動素子20,20Aに基づいて生成された異なる周波数の信号が出力端子T6,T7から出力される。

【0084】

かかる圧電発振器1Cにおいては、第1の実施形態や第2の実施形態と同様に素子搭載部材の配線領域が構成される。そのため、異なる周波数の信号に対しても所望の出力特性を安定して得ることができる。

【0085】

なお、圧電発振器1Cにおいては、圧電振動素子20と発振回路51との間の配線が出力端子T7と外部接続用端子47との間の配線に近接した場合であっても、出力端子T7からの出力特性は変動しない。同様に、圧電振動素子20Aと発振回路51Aとの間の配線が出力端子T6と外部接続用端子46との間の配線に近接した場合であっても、出力端子T6からの出力特性は変動しない。

【0086】

したがって、次のような配線状態としてもよい。すなわち、発振回路51と圧電振動素子20との間の第1の導電路31は、出力端子T6と外部接続用端子46との間の第2の導電路32に対して、配線領域の積層方向において交差せず、かつ同一配線層内で層間距離より長い間隔を空ける。また、発振回路51Aと圧電振動素子20Aとの間の第1の導電路31は、出力端子T7と外部接続用端子47との間の第2の導電路32に対して、配線領域の積層方向において交差せず、かつ同一配線層内で層間距離より長い間隔を空けるようにする。このようにすることによっても、異なる周波数の信号に対しても所望の出力特性を安定して得ることができ、また、第1の導電路31および第2の導電路32における配線制限を緩和することができる。

【0087】

さらなる効果や変形例は、当業者によって容易に導き出すことができる。このため、本発明のより広範な態様は、以上のように表しかつ記述した特定の詳細および代表的な実施形態に限定されるものではない。したがって、添付の特許請求の範囲およびその均等物によって定義される総括的な発明の概念の精神または範囲から逸脱することなく、様々な変更が可能である。

【0088】

例えば、上述した圧電発振器1,1A〜1Cでは、IC素子30において2つの出力端子T6,T7から出力する信号の状態を制御するものであるが、出力信号の数や出力端子の数はこれに限定されるものではない。例えば、3つ以上の出力端子から出力する信号の状態を制御するものであってもよい。また、複数の出力端子のいずれについても信号の出力状態を制御することとしたが、一部のみの出力端子からの信号の出力状態を制御するものであってもよい。

【符号の説明】

【0089】

1,1A,1B,1C 圧電発振器

10 素子搭載部材

20,20A 圧電振動素子

30,30A,30B IC素子(回路素子の一例)

31 第1の導電路

32 第2の導電路

46,47 外部接続用端子

51,51A 発振回路

55,55A 配線領域

85,86 モニタパッド

100 電子機器

SW1,SW2 スイッチ(制御回路の一例)

T6,T7 出力端子

【特許請求の範囲】

【請求項1】

圧電振動素子と、

前記圧電振動素子に接続され、前記圧電振動素子の振動に応じた出力信号を生成する発振回路と、複数の出力端子と、前記複数の出力端子からの前記出力信号の出力状態を制御する制御回路とを有する回路素子と、

複数の外部接続用端子が形成されると共に、前記圧電振動素子と前記回路素子とを電気的に接続する第1の導電路と、前記出力端子と前記外部接続用端子とを電気的に接続する第2の導電路とを含む多層の配線領域が形成される素子搭載部材と

を備え、

前記第1の導電路と前記第2の導電路とは、前記配線領域の積層方向において交差しないことを特徴とする圧電発振器。

【請求項2】

前記配線領域には、前記圧電振動素子と電気的に接続されるモニタパッドが形成され、

前記モニタパッドと前記第2の導電路とは、前記配線領域の積層方向において交差しないことを特徴とする請求項1に記載の圧電発振器。

【請求項3】

前記第1の導電路の一部と前記第2の導電路の一部とが前記配線領域の同一層に形成され、当該同一層において前記第1の導電路と前記第2の導電路との間の最短距離が前記配線領域の層間最短距離よりも長いことを特徴とする請求項1又は2に記載の圧電発振器。

【請求項4】

請求項1〜3のいずれか一つに記載の圧電発振器

を備えることを特徴とする電子機器。

【請求項1】

圧電振動素子と、

前記圧電振動素子に接続され、前記圧電振動素子の振動に応じた出力信号を生成する発振回路と、複数の出力端子と、前記複数の出力端子からの前記出力信号の出力状態を制御する制御回路とを有する回路素子と、

複数の外部接続用端子が形成されると共に、前記圧電振動素子と前記回路素子とを電気的に接続する第1の導電路と、前記出力端子と前記外部接続用端子とを電気的に接続する第2の導電路とを含む多層の配線領域が形成される素子搭載部材と

を備え、

前記第1の導電路と前記第2の導電路とは、前記配線領域の積層方向において交差しないことを特徴とする圧電発振器。

【請求項2】

前記配線領域には、前記圧電振動素子と電気的に接続されるモニタパッドが形成され、

前記モニタパッドと前記第2の導電路とは、前記配線領域の積層方向において交差しないことを特徴とする請求項1に記載の圧電発振器。

【請求項3】

前記第1の導電路の一部と前記第2の導電路の一部とが前記配線領域の同一層に形成され、当該同一層において前記第1の導電路と前記第2の導電路との間の最短距離が前記配線領域の層間最短距離よりも長いことを特徴とする請求項1又は2に記載の圧電発振器。

【請求項4】

請求項1〜3のいずれか一つに記載の圧電発振器

を備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−115510(P2013−115510A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−258057(P2011−258057)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000104722)京セラクリスタルデバイス株式会社 (870)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000104722)京セラクリスタルデバイス株式会社 (870)

【Fターム(参考)】

[ Back to top ]