圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ピアース型の圧電発振器に関する。

【背景技術】

【0002】

圧電発振器は周波数安定度、小型軽量、低価格等の利点を有することにより、通信機器や電子機器の多くの分野で用いられ、中でも圧電振動子の周波数温度特性を補償した温度補償型圧電発振器(TCXO)は、携帯電話等に広く用いられている。圧電発振器には、ピアース型の圧電発振器と、コルピッツ型の圧電発振器がある。ピアース型圧電発振器は、低い電源電圧で動作させることができ、回路の集積化に適しているが、低電流で出力できる周波数は、10〜30MHzに留まり、高い周波数の出力ができないという課題がある。

【0003】

図9は、自己バイアス回路を備えた従来のピアースB−C型の圧電発振器8を示す回路図である。図9に示すように、ピアースB−C型の圧電発振器8は、発振回路108とバッファ回路BUFとから構成され、発振回路108は、発振用トランジスタQ1と、発振用トランジスタQ1のベース端子とコレクタ端子との間に接続された圧電振動子10及び帰還抵抗R0と、圧電振動子10の両端と接地電位線GNDとの間に各々接続された容量素子C1,C2と、から構成されている。バッファ回路BUFは、発振回路108の出力となる発振用トランジスタQ1のコレクタ端子に接続されている。また、発振用トランジスタQ1のコレクタ端子には電流源20が接続されている。

【0004】

発振回路108の出力周波数を高めるためには、所望の発振周波数において発振回路108の負性抵抗値を充分大きくする必要がある。発振回路108の負性抵抗値(−Rn)は、発振用トランジスタQ1の相互コンダクタンス値をgmとすると、−Rn=gm/(ωC1C2)となる。従って、負性抵抗値を大きくするには、容量素子C1,C2の容量値を小さくするか、相互コンダクタンス値gmを大きくする必要がある。

【0005】

しかしながら、容量素子C1,C2の容量値を小さくすると、発振回路108の負荷容量も小さくなり、周波数感度が必要以上に大きくなる。このため、発振回路108の出力(発振用トランジスタQ1のコレクタ端子)に接続するバッファ回路BUFによる外部負荷容量の影響が大きくなり、電源変動や経年変化の劣化を引き起こす。また、容量素子C1,C2の容量値を小さくすると、発振回路108の回路損失が増加し、回路Q値が小さくなり、C/N比(Carrier to Noise Ratio)の劣化を引き起こす。

【0006】

この問題を解決するために、例えば特許文献1には、外部負荷容量の影響を軽減するために、発振回路の出力と外部負荷との間にレベルシフト回路を備えたピアース型水晶発振回路が記載されている。しかしながら、このようなピアース型水晶発振回路は、レベルシフト回路の分だけ回路規模が大きくなり消費電流も増えてしまうため、集積化には適さないという課題がある。

【0007】

また、負性抵抗値を大きくするために発振用トランジスタQ1の相互コンダクタンス値gmを大きくする方法では、コレクタ電流Icを大きくする必要があり、発振回路108の消費電流が増えてしまう。

【0008】

この問題を解決するために、例えば特許文献2には、コルピッツ型発振回路において、発振トランジスタのコレクタ−エミッタ間に帰還回路(エミッタフォロワ回路)を備える方法が記載されている。帰還回路を付加したことにより、発振回路の負性抵抗特性が改善され、高い周波数において充分高い負性抵抗値を得ることができる。

【0009】

しかしながら、このような帰還回路をピアース型の発振回路に適用すると、帰還回路を動作させるための電流が必要になり、消費電流が増えてしまう。また、帰還回路の結合容量(特許文献2の図8のC4,C5)が非常に大きな値になり、集積化には向いていない。また、帰還回路を付加することにより、充分な負性抵抗が得られるが、周波数領域が数百MHz(特許文献2の図2参照)となり、水晶のAT振動子などで利用される数十MHzの領域を遥かに超えてしまう。

【0010】

負性抵抗を大きくするための別の方法として、例えば特許文献3には、コルピッツ型の水晶発振回路において、発振用トランジスタをダーリントン接続する方法が記載させている。発振用トランジスタをダーリントン接続することにより、発振トランジスタの電流増幅率Hfeを高め、相互コンダクタンス値gmを大きくできるので、負性抵抗を大きくすることができる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2002−16439号公報(図1)

【特許文献2】特開2005−86378号公報(図8)

【特許文献3】特開2002−237725号公報(図1)

【発明の概要】

【発明が解決しようとする課題】

【0012】

しかしながら、発振用トランジスタをダーリントン接続することにより負性抵抗は大きくなるが、発振周波数が低くなってしまう。図9に、コルピッツ型の水晶発振回路でのシミュレーション結果を示す。図10(A)は、従来のコルピッツ型の水晶発振回路、図10(B)は、発振用トランジスタをダーリントン接続したコルピッツ型の水晶発振回路、図10(C)は、それぞれの負性抵抗値を示すグラフである。

【0013】

この方法は、ピアース型の発振回路で発振用トランジスタをダーリントン接続した場合も同様の結果となる。これは、発振用トランジスタをダーリントン接続することにより発振トランジスタの電流増幅率Hfeは増加するが、発振用トランジスタのコレクタ−エミッタ間のミラー容量も増加するため、高周波において負性抵抗が劣化するためと考えられる。

【課題を解決するための手段】

【0014】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0015】

[適用例1]

圧電振動子と、前記圧電振動子の一方の端子と接地電位線との間に接続された第1の容量素子と、前記圧電振動子の他方の端子と前記接地電位線との間に接続された第2の容量素子と、コレクタ端子が前記圧電振動子の一方の端子に接続され、ベース端子が前記圧電振動子の他方の端子に接続され、エミッタ端子が前記接地電位線に接続された発振用トランジスタと、ベース端子が前記発振用トランジスタのコレクタ端子に第1の抵抗を介して接続され、コレクタ端子が前記発振用トランジスタのコレクタ端子に第2の抵抗を介して接続され、エミッタ端子が前記発振用トランジスタのベース端子に接続された発振補助用トランジスタと、を含む、ことを特徴とする圧電発振器。

【0016】

この構成によれば、発振補助用トランジスタと発振用トランジスタとにより、回路電流を増やすことなく増幅率が上がり従来構成よりも大きい負性抵抗を得ることができるので、高い周波数で発振が可能となり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗とが増えるだけなので、高集積化及び低消費電流を実現できる。

【0017】

[適用例2]

上記に記載の圧電発振器において、前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子をさらに含む、ことを特徴とする圧電発振器。

【0018】

この構成によれば、第3の容量素子により、負性抵抗の谷を周波数の高い側に移動させることができるので、高い周波数で発振することが可能になり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗とが増えるだけなので、高集積化及び低消費電流を実現できる。

【0019】

[適用例3]

上記に記載の圧電発振器において、前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子をさらに含む、ことを特徴とする圧電発振器。

【0020】

この構成によれば、第4の容量素子により、負性抵抗をさらに大きくすることができるので、高い周波数で発振することが可能になり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗とが増えるだけなので、高集積化及び低消費電流を実現できる。

【0021】

[適用例4]

上記に記載の圧電発振器において、前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子と、前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子と、をさらに含む、ことを特徴とする圧電発振器。

【0022】

この構成によれば、第3の容量素子及び第4の容量素子により、負性抵抗の谷が周波数の高い側に移動し、高い周波数で発振することが可能になり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗と第3,第4の容量素子のみが増えるだけなので、高集積化及び低消費電流を実現できる。

【図面の簡単な説明】

【0023】

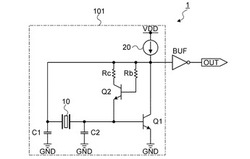

【図1】第1実施形態に係る圧電発振器の構成を示す回路図。

【図2】第1実施形態に係る圧電発振器の動作を示すグラフ。

【図3】変形例1に係る圧電発振器の構成を示す回路図。

【図4】変形例1に係る圧電発振器の動作を示すグラフ。

【図5】変形例2に係る圧電発振器の構成を示す回路図。

【図6】変形例3に係る圧電発振器の構成を示す回路図。

【図7】変形例4に係る圧電発振器の構成を示す回路図。

【図8】変形例5に係る圧電発振器の構成を示す回路図。

【図9】従来の圧電発振器の構成を示す回路図。

【図10】(A)従来のコルピッツ型の水晶発振回路、(B)発振用トランジスタをダーリントン接続したコルピッツ型の水晶発振回路、(C)それぞれの出力周波数を示すグラフ。

【発明を実施するための形態】

【0024】

以下、圧電発振器の実施形態について図面に従って説明する。

【0025】

(第1実施形態)

<圧電発振器の構成>

先ず、第1実施形態に係る圧電発振器の構成について、図1を参照して説明する。図1は、第1実施形態に係る圧電発振器の構成を示す回路図である。

【0026】

図1に示すように、圧電発振器1は、発振回路101とバッファ回路BUFとから構成される。

【0027】

発振回路101は、エミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、発振用トランジスタQ1のベース端子とコレクタ端子との間に接続された圧電振動子10と、圧電振動子10の両端と接地電位線GNDとの間に各々接続された第1の容量素子C1及び第2の容量素子C2と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続され、コレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続され、エミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、発振用トランジスタQ1のコレクタ端子と電源電位線VDDとの間に接続された電流源20と、から構成されている。バッファ回路BUFは、発振回路101の出力となる発振用トランジスタQ1のコレクタ端子に接続されている。

【0028】

図9に示した従来の発振回路108と発振回路101との違いは、帰還抵抗R0を発振補助用トランジスタQ2、第1の抵抗Rb及び第2の抵抗Rcに置き換えたことである。

【0029】

発振補助用トランジスタQ2は、発振用トランジスタQ1による増幅効率の向上をサポートするので、発振補助用トランジスタQ2及び発振用トランジスタQ1の増幅作用により、従来より大きな負性抵抗を得ることができるので、高速な起動特性が得られる。

【0030】

発振補助用トランジスタQ2、第1の抵抗Rb及び第2の抵抗Rcに流れる電流は、発振用トランジスタQ1のベース電流と等しいので、従来の発振回路108の帰還抵抗R0のみで構成した場合と比較しても電流の増加はない。

【0031】

発振用トランジスタQ1の電流増幅率Hfeが小さくなり、負性抵抗が小さくなる状況でも、電流増幅率Hfeの低下によりベース電流が増加し、発振補助用トランジスタQ2に流れる電流は逆に大きくなるので、発振補助用トランジスタQ2は、発振用トランジスタQ1による増幅効率の向上をより大きくサポートすることができる。すなわち、発振周波数を適宜選択することにより、電流増幅率Hfe低下による負性抵抗の劣化を抑制できる。

【0032】

第1実施形態に係る圧電発振器の動作について、図2を参照して説明する。図2は、第1実施形態に係る圧電発振器の動作を示すグラフである。

【0033】

図2に示すように、従来の圧電発振器8の出力OUT8の負性抵抗のピークは、約10MHzであった。本実施形態の圧電発振器1の出力OUTの負性抵抗のピークは、約24MHzとなり、従来に比べ高周波での出力が可能となることがわかる。

【0034】

以上に述べた本実施形態によれば、以下の効果が得られる。

【0035】

本実施形態では、発振補助用トランジスタQ2と発振用トランジスタQ1とにより増幅率が上がるので従来構成よりも、高い周波数において大きい負性抵抗を得ることができるので、高い周波数で発振が可能であり、さらに従来の回路構成より発振補助用トランジスタQ2と第1の抵抗Rbとが増えるだけなので、高集積化及び低消費電流を実現できる。

【0036】

以上、圧電発振器の実施形態を説明したが、こうした実施の形態に何ら限定されるものではなく、趣旨を逸脱しない範囲内において様々な形態で実施し得ることができる。以下、変形例を挙げて説明する。

【0037】

(変形例1)圧電発振器の変形例1について説明する。図3は、変形例1に係る圧電発振器の構成を示す回路図である。図3に示すように、圧電発振器3は、第1実施形態の圧電発振器1に対して発振用トランジスタQ1のコレクタ端子と圧電振動子10の一方の端子(第1の容量素子C1側)との間に接続される第3の容量素子C3をさらに含んで構成されている。図4は、変形例1に係る圧電発振器の動作を示すグラフである。この構成によれば、第3の容量素子C3により発振用トランジスタQ1のコレクタから容量素子C1と圧電振動子10に帰還される信号の位相が変化し、負性抵抗のピークの位置が周波数の高い方へ移動し、より高い周波数で発振することが可能になる。

【0038】

(変形例2)圧電発振器の変形例2について説明する。図5は、変形例2に係る圧電発振器の構成を示す回路図である。図5に示すように、圧電発振器4は、第1実施形態の圧電発振器1に対して発振用トランジスタQ1のベース端子と圧電振動子10の他方の端子(第2の容量素子C2側)との間に接続される第4の容量素子C4をさらに含んで構成されている。この構成によれば、第4の容量素子C4により高い周波数において、負性抵抗をさらに大きくすることができるので、変形例1と同様に高い周波数で発振が可能となる。

【0039】

(変形例3)圧電発振器の変形例3について説明する。図6は、変形例3に係る圧電発振器の構成を示す回路図である。図6に示すように、圧電発振器5は、第1実施形態の圧電発振器1に対して発振用トランジスタQ1のコレクタ端子と圧電振動子10の一方の端子(第1の容量素子C1側)との間に接続される第3の容量素子C3と、圧電発振器1に対して発振用トランジスタQ1のベース端子と圧電振動子10の他方の端子(第2の容量素子C2側)との間に接続される第4の容量素子C4と、をさらに含んで構成されている。この構成によれば、第3の容量素子C3及び第4の容量素子C4により高い周波数において、負性抵抗をさらに大きくすることができるので、変形例1と同様に高い周波数で発振が可能となる。

【0040】

(変形例4)圧電発振器の変形例4について説明する。図7は、変形例4に係る圧電発振器の構成を示す回路図である。図7に示すように、圧電発振器6は、変形例3の圧電発振器5を構成する第1の容量素子C1の換わりに可変容量素子VC1が接続され、第2の容量素子C2の換わりに可変容量素子VC2が接続され、可変容量素子VC1に対し抵抗R1を介して制御電圧Vcが印加され、可変容量素子VC2に対し抵抗R2を介して制御電圧Vcが印加されている。この構成によれば、制御電圧Vcより出力する周波数を制御できる。なお、この例において、容量素子C3,C4が負性抵抗値を大きくすると共に、可変容量素子VC1,VC2に印加した直流電圧の直流カット用コンデンサとして機能する。

【0041】

(変形例5)圧電発振器の変形例5について説明する。図8は、変形例5に係る圧電発振器の構成を示す回路図である。図8に示すように、圧電発振器7は、第1実施形態の圧電発振器1に対して発振補助用トランジスタQ2のエミッタ端子と発振用トランジスタQ1のベース端子との間に接続された抵抗Reをさらに含んで構成される。抵抗Reを含む構成は、圧電発振器3,4,5,6にも同様に適用できる。

【符号の説明】

【0042】

1…圧電発振器、3…圧電発振器、4…圧電発振器、5…圧電発振器、6…圧電発振器、7…圧電発振器、10…圧電振動子、20…電流源、101…発振回路、108…発振回路。

【技術分野】

【0001】

本発明は、ピアース型の圧電発振器に関する。

【背景技術】

【0002】

圧電発振器は周波数安定度、小型軽量、低価格等の利点を有することにより、通信機器や電子機器の多くの分野で用いられ、中でも圧電振動子の周波数温度特性を補償した温度補償型圧電発振器(TCXO)は、携帯電話等に広く用いられている。圧電発振器には、ピアース型の圧電発振器と、コルピッツ型の圧電発振器がある。ピアース型圧電発振器は、低い電源電圧で動作させることができ、回路の集積化に適しているが、低電流で出力できる周波数は、10〜30MHzに留まり、高い周波数の出力ができないという課題がある。

【0003】

図9は、自己バイアス回路を備えた従来のピアースB−C型の圧電発振器8を示す回路図である。図9に示すように、ピアースB−C型の圧電発振器8は、発振回路108とバッファ回路BUFとから構成され、発振回路108は、発振用トランジスタQ1と、発振用トランジスタQ1のベース端子とコレクタ端子との間に接続された圧電振動子10及び帰還抵抗R0と、圧電振動子10の両端と接地電位線GNDとの間に各々接続された容量素子C1,C2と、から構成されている。バッファ回路BUFは、発振回路108の出力となる発振用トランジスタQ1のコレクタ端子に接続されている。また、発振用トランジスタQ1のコレクタ端子には電流源20が接続されている。

【0004】

発振回路108の出力周波数を高めるためには、所望の発振周波数において発振回路108の負性抵抗値を充分大きくする必要がある。発振回路108の負性抵抗値(−Rn)は、発振用トランジスタQ1の相互コンダクタンス値をgmとすると、−Rn=gm/(ωC1C2)となる。従って、負性抵抗値を大きくするには、容量素子C1,C2の容量値を小さくするか、相互コンダクタンス値gmを大きくする必要がある。

【0005】

しかしながら、容量素子C1,C2の容量値を小さくすると、発振回路108の負荷容量も小さくなり、周波数感度が必要以上に大きくなる。このため、発振回路108の出力(発振用トランジスタQ1のコレクタ端子)に接続するバッファ回路BUFによる外部負荷容量の影響が大きくなり、電源変動や経年変化の劣化を引き起こす。また、容量素子C1,C2の容量値を小さくすると、発振回路108の回路損失が増加し、回路Q値が小さくなり、C/N比(Carrier to Noise Ratio)の劣化を引き起こす。

【0006】

この問題を解決するために、例えば特許文献1には、外部負荷容量の影響を軽減するために、発振回路の出力と外部負荷との間にレベルシフト回路を備えたピアース型水晶発振回路が記載されている。しかしながら、このようなピアース型水晶発振回路は、レベルシフト回路の分だけ回路規模が大きくなり消費電流も増えてしまうため、集積化には適さないという課題がある。

【0007】

また、負性抵抗値を大きくするために発振用トランジスタQ1の相互コンダクタンス値gmを大きくする方法では、コレクタ電流Icを大きくする必要があり、発振回路108の消費電流が増えてしまう。

【0008】

この問題を解決するために、例えば特許文献2には、コルピッツ型発振回路において、発振トランジスタのコレクタ−エミッタ間に帰還回路(エミッタフォロワ回路)を備える方法が記載されている。帰還回路を付加したことにより、発振回路の負性抵抗特性が改善され、高い周波数において充分高い負性抵抗値を得ることができる。

【0009】

しかしながら、このような帰還回路をピアース型の発振回路に適用すると、帰還回路を動作させるための電流が必要になり、消費電流が増えてしまう。また、帰還回路の結合容量(特許文献2の図8のC4,C5)が非常に大きな値になり、集積化には向いていない。また、帰還回路を付加することにより、充分な負性抵抗が得られるが、周波数領域が数百MHz(特許文献2の図2参照)となり、水晶のAT振動子などで利用される数十MHzの領域を遥かに超えてしまう。

【0010】

負性抵抗を大きくするための別の方法として、例えば特許文献3には、コルピッツ型の水晶発振回路において、発振用トランジスタをダーリントン接続する方法が記載させている。発振用トランジスタをダーリントン接続することにより、発振トランジスタの電流増幅率Hfeを高め、相互コンダクタンス値gmを大きくできるので、負性抵抗を大きくすることができる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2002−16439号公報(図1)

【特許文献2】特開2005−86378号公報(図8)

【特許文献3】特開2002−237725号公報(図1)

【発明の概要】

【発明が解決しようとする課題】

【0012】

しかしながら、発振用トランジスタをダーリントン接続することにより負性抵抗は大きくなるが、発振周波数が低くなってしまう。図9に、コルピッツ型の水晶発振回路でのシミュレーション結果を示す。図10(A)は、従来のコルピッツ型の水晶発振回路、図10(B)は、発振用トランジスタをダーリントン接続したコルピッツ型の水晶発振回路、図10(C)は、それぞれの負性抵抗値を示すグラフである。

【0013】

この方法は、ピアース型の発振回路で発振用トランジスタをダーリントン接続した場合も同様の結果となる。これは、発振用トランジスタをダーリントン接続することにより発振トランジスタの電流増幅率Hfeは増加するが、発振用トランジスタのコレクタ−エミッタ間のミラー容量も増加するため、高周波において負性抵抗が劣化するためと考えられる。

【課題を解決するための手段】

【0014】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態または適用例として実現することが可能である。

【0015】

[適用例1]

圧電振動子と、前記圧電振動子の一方の端子と接地電位線との間に接続された第1の容量素子と、前記圧電振動子の他方の端子と前記接地電位線との間に接続された第2の容量素子と、コレクタ端子が前記圧電振動子の一方の端子に接続され、ベース端子が前記圧電振動子の他方の端子に接続され、エミッタ端子が前記接地電位線に接続された発振用トランジスタと、ベース端子が前記発振用トランジスタのコレクタ端子に第1の抵抗を介して接続され、コレクタ端子が前記発振用トランジスタのコレクタ端子に第2の抵抗を介して接続され、エミッタ端子が前記発振用トランジスタのベース端子に接続された発振補助用トランジスタと、を含む、ことを特徴とする圧電発振器。

【0016】

この構成によれば、発振補助用トランジスタと発振用トランジスタとにより、回路電流を増やすことなく増幅率が上がり従来構成よりも大きい負性抵抗を得ることができるので、高い周波数で発振が可能となり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗とが増えるだけなので、高集積化及び低消費電流を実現できる。

【0017】

[適用例2]

上記に記載の圧電発振器において、前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子をさらに含む、ことを特徴とする圧電発振器。

【0018】

この構成によれば、第3の容量素子により、負性抵抗の谷を周波数の高い側に移動させることができるので、高い周波数で発振することが可能になり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗とが増えるだけなので、高集積化及び低消費電流を実現できる。

【0019】

[適用例3]

上記に記載の圧電発振器において、前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子をさらに含む、ことを特徴とする圧電発振器。

【0020】

この構成によれば、第4の容量素子により、負性抵抗をさらに大きくすることができるので、高い周波数で発振することが可能になり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗とが増えるだけなので、高集積化及び低消費電流を実現できる。

【0021】

[適用例4]

上記に記載の圧電発振器において、前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子と、前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子と、をさらに含む、ことを特徴とする圧電発振器。

【0022】

この構成によれば、第3の容量素子及び第4の容量素子により、負性抵抗の谷が周波数の高い側に移動し、高い周波数で発振することが可能になり、さらに従来の回路構成より発振補助用トランジスタと第1の抵抗と第3,第4の容量素子のみが増えるだけなので、高集積化及び低消費電流を実現できる。

【図面の簡単な説明】

【0023】

【図1】第1実施形態に係る圧電発振器の構成を示す回路図。

【図2】第1実施形態に係る圧電発振器の動作を示すグラフ。

【図3】変形例1に係る圧電発振器の構成を示す回路図。

【図4】変形例1に係る圧電発振器の動作を示すグラフ。

【図5】変形例2に係る圧電発振器の構成を示す回路図。

【図6】変形例3に係る圧電発振器の構成を示す回路図。

【図7】変形例4に係る圧電発振器の構成を示す回路図。

【図8】変形例5に係る圧電発振器の構成を示す回路図。

【図9】従来の圧電発振器の構成を示す回路図。

【図10】(A)従来のコルピッツ型の水晶発振回路、(B)発振用トランジスタをダーリントン接続したコルピッツ型の水晶発振回路、(C)それぞれの出力周波数を示すグラフ。

【発明を実施するための形態】

【0024】

以下、圧電発振器の実施形態について図面に従って説明する。

【0025】

(第1実施形態)

<圧電発振器の構成>

先ず、第1実施形態に係る圧電発振器の構成について、図1を参照して説明する。図1は、第1実施形態に係る圧電発振器の構成を示す回路図である。

【0026】

図1に示すように、圧電発振器1は、発振回路101とバッファ回路BUFとから構成される。

【0027】

発振回路101は、エミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、発振用トランジスタQ1のベース端子とコレクタ端子との間に接続された圧電振動子10と、圧電振動子10の両端と接地電位線GNDとの間に各々接続された第1の容量素子C1及び第2の容量素子C2と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続され、コレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続され、エミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、発振用トランジスタQ1のコレクタ端子と電源電位線VDDとの間に接続された電流源20と、から構成されている。バッファ回路BUFは、発振回路101の出力となる発振用トランジスタQ1のコレクタ端子に接続されている。

【0028】

図9に示した従来の発振回路108と発振回路101との違いは、帰還抵抗R0を発振補助用トランジスタQ2、第1の抵抗Rb及び第2の抵抗Rcに置き換えたことである。

【0029】

発振補助用トランジスタQ2は、発振用トランジスタQ1による増幅効率の向上をサポートするので、発振補助用トランジスタQ2及び発振用トランジスタQ1の増幅作用により、従来より大きな負性抵抗を得ることができるので、高速な起動特性が得られる。

【0030】

発振補助用トランジスタQ2、第1の抵抗Rb及び第2の抵抗Rcに流れる電流は、発振用トランジスタQ1のベース電流と等しいので、従来の発振回路108の帰還抵抗R0のみで構成した場合と比較しても電流の増加はない。

【0031】

発振用トランジスタQ1の電流増幅率Hfeが小さくなり、負性抵抗が小さくなる状況でも、電流増幅率Hfeの低下によりベース電流が増加し、発振補助用トランジスタQ2に流れる電流は逆に大きくなるので、発振補助用トランジスタQ2は、発振用トランジスタQ1による増幅効率の向上をより大きくサポートすることができる。すなわち、発振周波数を適宜選択することにより、電流増幅率Hfe低下による負性抵抗の劣化を抑制できる。

【0032】

第1実施形態に係る圧電発振器の動作について、図2を参照して説明する。図2は、第1実施形態に係る圧電発振器の動作を示すグラフである。

【0033】

図2に示すように、従来の圧電発振器8の出力OUT8の負性抵抗のピークは、約10MHzであった。本実施形態の圧電発振器1の出力OUTの負性抵抗のピークは、約24MHzとなり、従来に比べ高周波での出力が可能となることがわかる。

【0034】

以上に述べた本実施形態によれば、以下の効果が得られる。

【0035】

本実施形態では、発振補助用トランジスタQ2と発振用トランジスタQ1とにより増幅率が上がるので従来構成よりも、高い周波数において大きい負性抵抗を得ることができるので、高い周波数で発振が可能であり、さらに従来の回路構成より発振補助用トランジスタQ2と第1の抵抗Rbとが増えるだけなので、高集積化及び低消費電流を実現できる。

【0036】

以上、圧電発振器の実施形態を説明したが、こうした実施の形態に何ら限定されるものではなく、趣旨を逸脱しない範囲内において様々な形態で実施し得ることができる。以下、変形例を挙げて説明する。

【0037】

(変形例1)圧電発振器の変形例1について説明する。図3は、変形例1に係る圧電発振器の構成を示す回路図である。図3に示すように、圧電発振器3は、第1実施形態の圧電発振器1に対して発振用トランジスタQ1のコレクタ端子と圧電振動子10の一方の端子(第1の容量素子C1側)との間に接続される第3の容量素子C3をさらに含んで構成されている。図4は、変形例1に係る圧電発振器の動作を示すグラフである。この構成によれば、第3の容量素子C3により発振用トランジスタQ1のコレクタから容量素子C1と圧電振動子10に帰還される信号の位相が変化し、負性抵抗のピークの位置が周波数の高い方へ移動し、より高い周波数で発振することが可能になる。

【0038】

(変形例2)圧電発振器の変形例2について説明する。図5は、変形例2に係る圧電発振器の構成を示す回路図である。図5に示すように、圧電発振器4は、第1実施形態の圧電発振器1に対して発振用トランジスタQ1のベース端子と圧電振動子10の他方の端子(第2の容量素子C2側)との間に接続される第4の容量素子C4をさらに含んで構成されている。この構成によれば、第4の容量素子C4により高い周波数において、負性抵抗をさらに大きくすることができるので、変形例1と同様に高い周波数で発振が可能となる。

【0039】

(変形例3)圧電発振器の変形例3について説明する。図6は、変形例3に係る圧電発振器の構成を示す回路図である。図6に示すように、圧電発振器5は、第1実施形態の圧電発振器1に対して発振用トランジスタQ1のコレクタ端子と圧電振動子10の一方の端子(第1の容量素子C1側)との間に接続される第3の容量素子C3と、圧電発振器1に対して発振用トランジスタQ1のベース端子と圧電振動子10の他方の端子(第2の容量素子C2側)との間に接続される第4の容量素子C4と、をさらに含んで構成されている。この構成によれば、第3の容量素子C3及び第4の容量素子C4により高い周波数において、負性抵抗をさらに大きくすることができるので、変形例1と同様に高い周波数で発振が可能となる。

【0040】

(変形例4)圧電発振器の変形例4について説明する。図7は、変形例4に係る圧電発振器の構成を示す回路図である。図7に示すように、圧電発振器6は、変形例3の圧電発振器5を構成する第1の容量素子C1の換わりに可変容量素子VC1が接続され、第2の容量素子C2の換わりに可変容量素子VC2が接続され、可変容量素子VC1に対し抵抗R1を介して制御電圧Vcが印加され、可変容量素子VC2に対し抵抗R2を介して制御電圧Vcが印加されている。この構成によれば、制御電圧Vcより出力する周波数を制御できる。なお、この例において、容量素子C3,C4が負性抵抗値を大きくすると共に、可変容量素子VC1,VC2に印加した直流電圧の直流カット用コンデンサとして機能する。

【0041】

(変形例5)圧電発振器の変形例5について説明する。図8は、変形例5に係る圧電発振器の構成を示す回路図である。図8に示すように、圧電発振器7は、第1実施形態の圧電発振器1に対して発振補助用トランジスタQ2のエミッタ端子と発振用トランジスタQ1のベース端子との間に接続された抵抗Reをさらに含んで構成される。抵抗Reを含む構成は、圧電発振器3,4,5,6にも同様に適用できる。

【符号の説明】

【0042】

1…圧電発振器、3…圧電発振器、4…圧電発振器、5…圧電発振器、6…圧電発振器、7…圧電発振器、10…圧電振動子、20…電流源、101…発振回路、108…発振回路。

【特許請求の範囲】

【請求項1】

圧電振動子と、

前記圧電振動子の一方の端子と接地電位線との間に接続された第1の容量素子と、

前記圧電振動子の他方の端子と前記接地電位線との間に接続された第2の容量素子と、

コレクタ端子が前記圧電振動子の一方の端子に接続され、ベース端子が前記圧電振動子の他方の端子に接続され、エミッタ端子が前記接地電位線に接続された発振用トランジスタと、

ベース端子が前記発振用トランジスタのコレクタ端子に第1の抵抗を介して接続され、コレクタ端子が前記発振用トランジスタのコレクタ端子に第2の抵抗を介して接続され、エミッタ端子が前記発振用トランジスタのベース端子に接続された発振補助用トランジスタと、

を含むことを特徴とする圧電発振器。

【請求項2】

請求項1に記載の圧電発振器において、

前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子をさらに含む、

ことを特徴とする圧電発振器。

【請求項3】

請求項1に記載の圧電発振器において、

前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子をさらに含む、

ことを特徴とする圧電発振器。

【請求項4】

請求項1に記載の圧電発振器において、

前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子と、

前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子と、

をさらに含む、

ことを特徴とする圧電発振器。

【請求項1】

圧電振動子と、

前記圧電振動子の一方の端子と接地電位線との間に接続された第1の容量素子と、

前記圧電振動子の他方の端子と前記接地電位線との間に接続された第2の容量素子と、

コレクタ端子が前記圧電振動子の一方の端子に接続され、ベース端子が前記圧電振動子の他方の端子に接続され、エミッタ端子が前記接地電位線に接続された発振用トランジスタと、

ベース端子が前記発振用トランジスタのコレクタ端子に第1の抵抗を介して接続され、コレクタ端子が前記発振用トランジスタのコレクタ端子に第2の抵抗を介して接続され、エミッタ端子が前記発振用トランジスタのベース端子に接続された発振補助用トランジスタと、

を含むことを特徴とする圧電発振器。

【請求項2】

請求項1に記載の圧電発振器において、

前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子をさらに含む、

ことを特徴とする圧電発振器。

【請求項3】

請求項1に記載の圧電発振器において、

前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子をさらに含む、

ことを特徴とする圧電発振器。

【請求項4】

請求項1に記載の圧電発振器において、

前記圧電振動子の一方の端子と前記発振用トランジスタのコレクタ端子との間に接続された第3の容量素子と、

前記圧電振動子の他方の端子と前記発振用トランジスタのベース端子との間に接続された第4の容量素子と、

をさらに含む、

ことを特徴とする圧電発振器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−253830(P2012−253830A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2012−211949(P2012−211949)

【出願日】平成24年9月26日(2012.9.26)

【分割の表示】特願2008−307100(P2008−307100)の分割

【原出願日】平成20年12月2日(2008.12.2)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成24年9月26日(2012.9.26)

【分割の表示】特願2008−307100(P2008−307100)の分割

【原出願日】平成20年12月2日(2008.12.2)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]