基板の洗浄方法および半導体装置の製造方法

【課題】基板の表面のフォトレジスト膜などの有機物または金属粒子などを除去する洗浄工程を簡略化し、半導体装置の製造コストを低減する。

【解決手段】SPM洗浄、APM洗浄およびHPM洗浄を行わず、過硫酸生成装置を用いて生成された過硫酸を含む硫酸溶液を用いて半導体ウエハの表面を洗浄し、フォトレジスト膜などの有機物または金属粒子などを除去した後に、半導体ウエハを純水洗浄し、乾燥させる。これにより、過酸化水素水の補充を必要とするSPM洗浄を行う場合に比べて高いレジスト除去性能を維持し、また、少ない工程で洗浄を完了することができる。

【解決手段】SPM洗浄、APM洗浄およびHPM洗浄を行わず、過硫酸生成装置を用いて生成された過硫酸を含む硫酸溶液を用いて半導体ウエハの表面を洗浄し、フォトレジスト膜などの有機物または金属粒子などを除去した後に、半導体ウエハを純水洗浄し、乾燥させる。これにより、過酸化水素水の補充を必要とするSPM洗浄を行う場合に比べて高いレジスト除去性能を維持し、また、少ない工程で洗浄を完了することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基板の洗浄方法および半導体装置の製造方法に関し、特に、基板表面に付着した有機膜または金属粒子などの除去工程を有する半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

半導体装置の製造工程においてパターニングのマスクとして使用するなどの目的により基板上に形成したフォトレジスト膜を除去する工程では、まずアッシング(灰化)することでフォトレジスト膜の大部分を除去した後、例えば硫酸および過酸化水素水を含む薬液を用いて基板表面にSPM(Sulfuric acid/hydrogen peroxide mixture)洗浄法による洗浄を行うことが知られている。

【0003】

特許文献1(特開2008−111184号公報)には、過硫酸を用いた洗浄システムなどに対し、高濃度の過硫酸を安定して供給することが可能な過硫酸供給システムが記載されている。

【0004】

特許文献2(特開2008−019507号公報)には、隔膜を挟むように配置された陽極および陰極を有する硫酸電解部を用いて生成した濃硫酸を用いて対象物の洗浄処理を行うことが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−111184号公報

【特許文献2】特開2008−019507号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

アッシング工程の後に半導体基板(半導体ウエハ)の表面に残ったフォトレジスト膜または金属粒子などを除去することを目的としてSPM洗浄を行っても、半導体基板上には有機物などの微粒子(残渣)が残る可能性が高く、それらを除去するために、アンモニア、過酸化水素水および水を含む薬液を用いたAPM(ammonium hydroxide/hydrogen peroxide/water mixture)洗浄を行う必要がある。また、APM洗浄を行った場合は、その後に半導体基板上に残った金属粒子を除去するために、塩酸、過酸化水素水および水を含む薬液を用いたHPM(hydrochloric acid/hydrogen peroxide/water mixture)洗浄を行う必要がある。

【0007】

また、上記SPM洗浄、APM洗浄およびHPM洗浄のそれぞれを行った際は、次の工程に進む前に、それらの工程で用いた薬液を半導体基板の表面に残さないように除去する工程が必要となる。その場合は、例えばSPM洗浄を行った後に純水を用いた洗浄(純水リンス洗浄)を行い、その後にAPM洗浄を行う。同様に、APM洗浄の後HPM洗浄を行う前にも純水リンス洗浄を行い、HPM洗浄の後にも純水リンス洗浄を行う。

【0008】

このように、半導体基板上のフォトレジスト膜を除去する際にSPM洗浄を行うと、SPM洗浄を行ったことに起因してさらに複数の洗浄工程を行うことになるため、製造工程が煩雑になり、それによって製造工程にかかる時間も長くなるため、半導体装置の製造コストが増加する問題がある。また、フォトレジスト膜除去のための装置の内部または外部にAPM洗浄部(APM洗浄槽)およびHPM洗浄部(HPM洗浄槽)を設ける必要があるため、半導体装置の製造に用いる設備が大きく高価になることによっても半導体装置の製造コストが増加する。また、APM洗浄部およびHPM洗浄部を設けることで、半導体装置の製造を行うクリーンルーム内の空間を洗浄装置が占める割合が大きくなり、床面積に限りがあるクリーンルームを有効に使用することが阻害されるため、半導体装置の製造効率が低下する問題がある。

【0009】

上記のようにSPM洗浄の後にAPM洗浄およびHPM洗浄が必要になる理由として、SPM洗浄用の薬液を循環させて繰り返し洗浄に用いることにより薬液の洗浄力が低下することが挙げられる。SPM洗浄に用いる薬液は装置内で循環させ、フィルタを通すことで何度も洗浄に使用することが考えられるが、その場合、当該薬液中の過硫酸の濃度を低下させないために循環する当該薬液に過酸化水素水(H2O2)を補充し続けなければならない。過酸化水素水が加えられた薬液は過硫酸が生成されるが、それと同時に水(H2O)も生成されるため、結局薬液の過硫酸濃度は徐々に低下し、レジスト除去性能が低下する。したがって、ある程度循環させて何度も洗浄に用いたSPM洗浄用の薬液は一旦全て廃棄し、新たに洗浄装置内に硫酸および過酸化水素水を供給して洗浄用の薬液を用意する必要がある。過酸化水素水を当該薬液に補充し続けること、および定期的に当該薬液を交換する必要があることは半導体装置の製造コストの増加に繋がる。

【0010】

このように水が発生することでSPM洗浄のレジスト除去性能は低下し、フォトレジスト膜の一部や微粒子が残渣となって半導体基板上に残る可能性があるため、リスク回避のためにAPM洗浄が必要となる。また、APM洗浄ではアルミニウム(Al)、鉄(Fe)のような金属不純物が微量でも混入すると金属粒子が半導体基板の表面に多量に付着するため、それを除去するためにHPM洗浄が必要となる。

【0011】

本発明の目的は、半導体装置の製造工程を簡略化する技術を提供することにある。

【0012】

本発明の他の目的は、半導体装置の製造コストを低減することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

すなわち、本願発明の半導体装置の製造方法は、

(a)基板を電解硫酸を用いて洗浄する工程、

(b)前記基板を水を用いて洗浄する工程、

(c)前記基板を乾燥させる工程、

を有する半導体装置の製造方法であって、

前記(a)工程の前に前記基板へのアッシング工程を行わず、

前記(c)工程の前にAPM洗浄工程およびHPM洗浄工程を有していないものである。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

代表的な実施の形態によれば、半導体装置の製造工程を簡略化することができる。

【0018】

半導体装置の製造コストを低減することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1である半導体装置の製造工程中の要部断面図である。

【図2】図1に続く半導体装置の製造工程中の要部断面図である。

【図3】図2に続く半導体装置の製造工程中の要部断面図である。

【図4】図3に続く半導体装置の製造工程中の要部断面図である。

【図5】図4に続く半導体装置の製造工程中の要部断面図である。

【図6】図5に続く半導体装置の製造工程中の要部断面図である。

【図7】図6に続く半導体装置の製造工程中の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の要部断面図である。

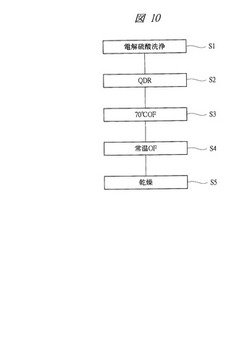

【図10】本発明の実施の形態1である半導体装置の洗浄工程のフローである。

【図11】本発明の実施の形態1である半導体装置の製造工程で用いる洗浄装置の模式図である。

【図12】本発明の実施の形態1で用いる薬液の金属除去性能を説明する表である。

【図13】図9に続く半導体装置の製造工程中の要部断面図である。

【図14】図13に続く半導体装置の製造工程中の要部断面図である。

【図15】図14に続く半導体装置の製造工程中の要部断面図である。

【図16】図15に続く半導体装置の製造工程中の要部断面図である。

【図17】図16に続く半導体装置の製造工程中の要部断面図である。

【図18】図17に続く半導体装置の製造工程中の要部断面図である。

【図19】図18に続く半導体装置の製造工程中の要部断面図である。

【図20】本発明の実施の形態2である半導体装置の洗浄工程のフローである。

【図21】比較例である半導体装置の製造工程中の洗浄工程のフローである。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

(実施の形態1)

まず、本実施の形態の半導体装置の製造工程を図面を参照して説明する。図1〜図9および図13〜図19は、本発明の一実施の形態である半導体装置、例えばCMISFET(Complementary Metal Insulator Semiconductor Field Effect Transistor)を有する半導体装置の製造工程中の要部断面図であり、それぞれの図に示す基板上面の右側の領域にはnチャネル型MISFETが形成され、左側の領域にはpチャネル型MISFETが形成される。

【0022】

まず、図1に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次に、この半導体基板1を熱酸化してその表面に例えば厚さ11nm程度の絶縁膜2を形成した後、その上層にCVD(Chemical Vapor Deposition)法などにより、例えば厚さ90nm程度の絶縁膜3を堆積する。絶縁膜2は酸化シリコンなどからなり、絶縁膜3は窒化シリコン膜などからなる。

【0023】

次に、図2に示すように、フォトリソグラフィ技術を用いてフォトレジスト膜R1を半導体基板1上の形成する。すなわち、半導体基板1上の全面にフォトレジスト膜R1を形成(塗布)した後、フォトレジスト膜R1をフォトマスクを用いて一部露光し、続いて現像することにより、フォトレジスト膜R1を所定の形状のパターンとして絶縁膜3上に残す。

【0024】

次に、図3に示すように、フォトレジスト膜R1をエッチングマスクとして絶縁膜3、絶縁膜2および半導体基板1を順次ドライエッチングすることにより、素子分離形成予定領域の半導体基板1に、例えば深さ300nm程度の溝(素子分離用の溝)4aを形成する。溝4aは、素子分離用の溝であり、すなわち後述する素子分離領域4形成用の溝である。その後、フォトレジスト膜R1を電解硫酸を用いた薬液により除去し、半導体基板の主面を洗浄する。当該洗浄方法の詳細な工程については、後に図10および図11を用いて説明する。なお、フォトレジスト膜R1の除去工程では、アッシング(灰化)は行わないものとする。また、いうまでもなく、本願では水のみを用いた洗浄に用いる液体(水)を薬液とは呼ばない。

【0025】

次に、図4に示すように、溝4aの内部(側壁および底部)を含む半導体基板1の主面上に、例えば厚み10nm程度の絶縁膜4bを形成する。それから、半導体基板1の主面上(すなわち絶縁膜4b上)に、溝4a内を埋めるように、絶縁膜4cをCVD法などにより形成(堆積)する。

【0026】

絶縁膜4bは、酸化シリコン膜または酸窒化シリコン膜からなる。絶縁膜4bが酸窒化シリコン膜の場合には、絶縁膜4b形成工程以降の熱処理によって溝4aの側壁が酸化することによる体積膨張を防止でき、半導体基板1に働く圧縮応力を低減できる効果がある。

【0027】

絶縁膜4cは、HDP−CVD(High Density Plasma CVD:高密度プラズマCVD)法により成膜された酸化シリコン膜、またはO3−TEOS酸化膜などである。なお、O3−TEOS酸化膜とは、O3(オゾン)およびTEOS(Tetraethoxysilane:テトラエトキシシラン、Tetra Ethyl Ortho Silicateともいう)を原料ガス(ソースガス)として用いて熱CVD法により形成した酸化シリコン膜である。

【0028】

それから、半導体基板1を例えば1150℃程度で熱処理することにより、溝4aに埋め込んだ絶縁膜4cを焼き締める。焼き締め前の状態では、O3−TEOS酸化膜よりもHDP−CVD法により成膜された酸化シリコン膜の方が緻密である。このため、絶縁膜4cがO3−TEOS酸化膜の場合、焼き締めによる絶縁膜4cの収縮により、半導体基板1に働く圧縮応力を低減できる効果がある。一方、絶縁膜4cがHDP−CVD法により成膜された酸化シリコン膜の場合には、絶縁膜4cがO3−TEOS酸化膜の場合に比べて、焼き締め時の絶縁膜4cの収縮が少ないため、素子分離領域4によって半導体基板1に働く圧縮応力が大きくなる。

【0029】

次に、図5に示すように、絶縁膜4cをCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨して絶縁膜3を露出させ、熱リン酸などを用いたウエットエッチングにより絶縁膜3を除去した後、HFなどにより溝4aの外部の絶縁膜4cおよび絶縁膜2を除去し、溝4aの内部に絶縁膜4b、4cを残すことにより、素子分離領域(素子分離)4を形成する。

【0030】

このようにして、溝4a内に埋め込まれた絶縁膜4b、4cからなる素子分離領域4が形成される。本実施の形態の素子分離領域4は、半導体基板1に形成された素子分離用の溝4a内に埋め込まれた絶縁体(ここでは絶縁膜4b、4c)からなる。後述するnチャネル型MISFETQn(すなわちnチャネル型MISFETQnを構成するゲート絶縁膜7、ゲート電極8aおよびソース・ドレイン用のn−型半導体領域9aおよびn+型半導体領域9b)は、素子分離領域4で規定された(囲まれた)活性領域に形成される。また、後述するpチャネル型MISFETQp(すなわちpチャネル型MISFETQpを構成するゲート絶縁膜7、ゲート電極8bおよびソース・ドレイン用のp−型半導体領域10aおよびp+型半導体領域10b)も、素子分離領域4で規定された(囲まれた)活性領域に形成される。

【0031】

次に、図6に示すように、半導体基板1上にフォトリソグラフィ技術を用いてフォトレジスト膜R2を形成する。フォトレジスト膜R2は後述するnチャネル型MISFETQnを形成する領域(nチャネル型MISFET形成予定領域)の半導体基板1の主面を露出しており、後述するpチャネル型MISFETQpを形成する領域(pチャネル型MISFET形成予定領域)の半導体基板1の主面を覆っている。

【0032】

続いて、フォトレジスト膜R2をイオン注入阻止マスクとして、図6に矢印で示すようにnチャネル型MISFET形成予定領域の半導体基板1に例えばホウ素(B)などのp型の不純物をイオン注入(ドーズ)することなどによって半導体基板1の主面から所定の深さに渡ってp型ウエル5を形成する。このとき、フォトレジスト膜R2にもp型の不純物が打ち込まれる。

【0033】

次に、図7に示すように、フォトレジスト膜R2を電解硫酸を用いた薬液により除去し、半導体基板の主面を洗浄する。当該洗浄方法の詳細な工程については、後に図10および図11を用いて説明する。なお、フォトレジスト膜R2の除去工程では、アッシング(灰化)は行わないものとする。その後、図6を用いて説明した工程と同様にフォトレジスト膜を半導体基板1上に形成し、半導体基板1のpチャネル型MISFET形成予定領域の主面から所定の深さに渡ってn型ウエル6を形成する。n型ウエル6は、nチャネル型MISFET形成予定領域を覆う他のフォトレジスト膜(図示せず)をイオン注入阻止マスクとして、pチャネル型MISFET形成予定領域の半導体基板1に例えばリン(P)またはヒ素(As)などのn型の不純物をイオン注入することなどによって形成することができる。続いて、図6を用いて説明した工程と同様にフォトレジスト膜を除去する。

【0034】

なお、図6および図7を用いて説明したウエル形成工程ではp型ウエル5を形成した後にn型ウエル6を形成したが、p型ウエル5およびn型ウエル6を形成する順序は逆であってもよい。

【0035】

次に、図8に示すように、半導体基板1の表面(すなわちp型ウエル5およびn型ウエル6の表面)上にゲート絶縁膜7を形成する。ゲート絶縁膜7は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成することができる。

【0036】

その後、半導体基板1上(すなわちp型ウエル5およびn型ウエル6のゲート絶縁膜7上)に、ゲート電極形成用の導体膜として、多結晶シリコン膜のようなシリコン膜8を形成する。シリコン膜8のうちのnチャネル型MISFET形成予定領域(後述するゲート電極8aとなる領域)は、フォトレジスト膜(図示せず)をマスクとして用いてリン(P)またはヒ素(As)などのn型の不純物をイオン注入することなどにより、低抵抗のn型半導体膜(ドープトポリシリコン膜)とされている。また、シリコン膜8のうちのpチャネル型MISFET形成予定領域(後述するゲート電極8bとなる領域)は、他のフォトレジスト膜(図示せず)をマスクとして用いてホウ素(B)などのp型の不純物をイオン注入することなどにより、低抵抗のp型半導体膜(ドープトポリシリコン膜)とされている。また、シリコン膜8は、成膜時にはアモルファスシリコン膜であったものを、成膜後(イオン注入後)の熱処理により多結晶シリコン膜に変えることもできる。

【0037】

続いて、フォトリソグラフィ技術により、nチャネル型MISFET形成予定領域およびpチャネル型MISFET形成予定領域のそれぞれのシリコン膜8上にフォトレジスト膜R3を形成する。

【0038】

次に、図9に示すように、フォトレジスト膜R3をエッチングマスクとして、ドライエッチング法を用いてシリコン膜8およびゲート絶縁膜7をパターニングすることによりゲート電極8a、8bを形成した後、フォトレジスト膜R3を電解硫酸を用いた薬液により除去し、半導体基板の主面を洗浄する。当該洗浄方法の詳細な工程については、後に図10および図11を用いて説明する。なお、フォトレジスト膜R3の除去工程では、アッシング(灰化)は行わないものとする。

【0039】

nチャネル型MISFETのゲート電極となるゲート電極8aは、n型の不純物を導入した多結晶シリコン(n型半導体膜、ドープトポリシリコン膜)からなり、p型ウエル5上にゲート絶縁膜7を介して形成される。すなわち、ゲート電極8aは、p型ウエル5のゲート絶縁膜7上に形成される。また、pチャネル型MISFETのゲート電極となるゲート電極8bは、p型の不純物を導入した多結晶シリコン(p型半導体膜、ドープトポリシリコン膜)からなり、n型ウエル6上にゲート絶縁膜7を介して形成される。すなわち、ゲート電極8bは、n型ウエル6のゲート絶縁膜7上に形成される。ゲート電極8a、8bのゲート長は、必要に応じて変更できるが、例えば50nm程度とすることができる。

【0040】

上述したように、本実施の形態では図3、図7および図9を用いて説明した工程において電解硫酸を用いてフォトレジスト膜の除去を行っているが、フォトレジスト膜を除去・洗浄する別の方法としては、図21のフローのステップSP1およびSP2に示すように、まずアッシングによりフォトレジスト膜の大部分を除去した後にSPM洗浄を用いることが考えられる。図21は、比較例の洗浄工程を示すフロー(工程図)であり、本実施の形態で用いる洗浄工程を示すものではない。以下に、比較例としてSPM洗浄を用いてフォトレジスト膜を除去する方法について説明する。

【0041】

SPM洗浄を行う場合は、図21のステップSP1に示すように、まずアッシングによりフォトレジスト膜を除去する。アッシングとは、エッチングなどの工程の後、不要となったフォトレジスト膜をプラズマなどで反応させ、気相中で分解・除去するレジスト剥離のことである。また、アッシングを行う装置をアッシャー(レジスト剥離装置)と呼ぶ。アッシングは、オゾンやガス等を導入したアッシング室内で、紫外線等の光を照射してガスとフォトレジスト膜の化学反応を使ってレジスト剥離をする光励起アッシングと、ガスを高周波等でプラズマ化し、そのプラズマを利用してレジストを剥離するプラズマアッシングの二つに大別される。

【0042】

アッシングでは半導体基板上のフォトレジスト膜を完全に除去することは困難であり、半導体基板上にはフォトレジスト膜の残渣も残るため、アッシングの次にはSPM洗浄(図21のステップSP2)を行うことで、さらに半導体基板上のフォトレジスト膜または金属粒子を除去する必要がある。SPM洗浄は、例えばSPM洗浄槽内にある硫酸および過酸化水素水を含む薬液内に半導体基板を複数枚同時に浸して半導体基板の表面を洗浄する洗浄方法であり、これによりフォトレジスト膜のような有機物または金属粒子などを除去することができる。ただし、SPM洗浄で用いる薬液は十分なレジスト除去性能を有していない可能性が高いため、レジストの残渣などが半導体基板の表面に残るリスクを回避する必要がある。よって、SPM洗浄により半導体基板上に残った有機物などの微粒子(残渣)を除去するために、アンモニア、過酸化水素水および水を含む薬液を用いたAPM洗浄(図21のステップSP5)を行う。

【0043】

SPM洗浄が十分なレジスト除去性能を保持できない理由は、SPM洗浄に用いる薬液をSPM洗浄槽内からポンプを用いて吸い出し、フィルタを通過させてゴミなどを取り除いた後に前記SPM洗浄槽に戻して循環させることで、薬液を繰り返し洗浄に使用していることに起因する。この場合、洗浄を繰り返し行ううちに薬液内の硫酸濃度が低くなり、レジストなどを除去する過硫酸の濃度が低下する。これを防ぐため、循環する薬液には過酸化水素水(H2O2)を供給し続けなければならない。硫酸を含む薬液に過酸化水素水を加えることで、硫酸および過酸化水素水から過硫酸および水を生成することができ、薬液内の過硫酸濃度の低下を抑えることができる。

【0044】

しかし、硫酸を含む薬液に過酸化水素水を加えると水が生成されるため、薬液に過酸化水素水を加え続けることで薬液内の水の量が増加し、薬液のレジスト除去性能は最終的にSPM洗浄に用いることができなくなるまでに低下する。したがって、SPM洗浄の薬液のレジスト除去性能が限界(許容範囲)より低くなる前に、SPM洗浄槽およびその槽に接続された循環器を含むSPM洗浄装置内の全ての薬液を廃棄し、その後SPM洗浄を行う際には新たに硫酸および過酸化水素水を含む薬液を用意し、それをSPM洗浄装置内で循環させて洗浄を行うこととなる。

【0045】

上述したように、SPM洗浄では薬液に過酸化水素水を追加し続けなければならないため、過酸化水素水が多量に必要となり半導体装置の製造コストが高くなる。また、過酸化水素水を追加し続けても、水が発生して薬液の過硫酸濃度が低下することでレジスト除去性能を高い状態で維持することができないため、除去可能なレジストの量などが制限される。つまり、レジスト除去性能が一定ではなく使用により低下するため、洗浄用の薬液として使用できる範囲で最も低いレジスト除去性能により除去できるフォトレジスト膜の量またはフォトレジスト膜の種類でなければ洗浄対象として扱うことができない。

【0046】

つまり、例えば半導体基板上のフォトレジスト膜の膜厚が厚すぎたり、洗浄槽内で同時に洗浄する半導体ウエハの枚数が多すぎたりすると、半導体基板の表面のフォトレジスト膜を除去しきれない可能性が高くなる。

【0047】

また、フォトレジスト膜はより多くの不純物が導入(ドーズ)されるほど除去されにくくなる性質を有しているため、例えば1×1013個/cm2よりも多く不純物が導入されたフォトレジスト膜はSPM洗浄では除去できない問題が発生する場合がある。

【0048】

次に、SPM洗浄の後であってAPM洗浄を行う前に、SPM洗浄により半導体基板表面に残ったSPM洗浄の薬液(特に硫酸)および残渣の一部を洗い流すために水を用いた洗浄を行う必要がある。水を用いた洗浄では図21のステップSP3に示すQDR(Quick Dump Rinse)を行った後に、ステップSP4に示すOF(Over Flow Rinse)を行う。QDRとは、洗浄する対象である半導体ウエハを入れた槽に水または純水を満たし、洗浄対象に水をシャワーしながら一気に排水する薬液処理後のリンス(濯ぎ)方法である。また、OFは水を供給・排出し続けるリンス槽内の水の中に半導体ウエハを浸して洗浄する洗浄方法である。本願では、QDRおよびOFの工程を行うことを、純水リンス工程と呼ぶ。つまり、純水リンス工程はQDR工程およびOF工程を含んでいる。

【0049】

このように水を用いた洗浄(純水リンス工程)の後に、APM洗浄(図21のステップSP5)を行うことで、半導体基板上に残るフォトレジスト膜の一部などからなる微粒子(残渣)またはその他の有機物を除去する。APM洗浄はAPM洗浄槽内のアンモニア、過酸化水素水および水を含む薬液内に半導体ウエハを浸して洗浄を行う洗浄方法である。しかし、APM洗浄は、アルミニウム(Al)、鉄(Fe)のような金属不純物がAPM洗浄の薬液内に微量でも混入すると金属粒子が半導体基板の表面に多量に付着する問題を有しているため、それらを除去するためにAPM洗浄の後にHPM洗浄(図21のステップSP8)を行わなければならない。

【0050】

HPM洗浄の前にはAPM洗浄の薬液などを半導体基板の表面から除去するために、ステップSP3およびステップSP4と同様にQDR(ステップSP6)およびOF(ステップSP7)を行う。HPM洗浄はHPM洗浄槽内の塩酸、過酸化水素水および水を含む薬液内に半導体ウエハを浸して洗浄を行う洗浄方法であり、これを行うことで半導体基板上に残っていた金属粒子(例えばアルミニウムまたは鉄)を除去する。HPM洗浄を行った後は、半導体基板の表面からHPM洗浄の薬液を除去するためのQDR(ステップSP9)またはOF(ステップSP10)などが必要となる。

【0051】

次に、ステップSP10までの洗浄工程を終えた半導体基板を乾燥させる乾燥(ステップSP11)工程を行う。乾燥工程では、半導体ウエハを例えば機械的に固定し、または真空チャックなどを用いて固定した後、半導体ウエハを回転させることで乾燥させる方法が考えられる。また、他の乾燥方法として、IPA(Iso-Propyl Alcohol)乾燥法を行うことも考えられる。IPA乾燥法は、イソプロピルアルコールの液体に半導体ウエハを浸けた後、アルコールの揮発によって半導体基板の表面を乾燥させる乾燥方法である。

【0052】

以上説明したように、SPM洗浄を行った後にはステップSP3〜ステップSP11に示す洗浄工程および乾燥工程が必要となり、これらの工程を行わなければ、次の成膜工程などに移行することができない。このように多くの工程を要するのはSPM洗浄のレジスト除去性能が薬液内の水の増加により低下するためであり、SPM洗浄を行えば、上記の多くの洗浄工程を行うための時間、薬液、装置およびその装置を半導体装置の製造工場内に配置するスペースが必要となるため、半導体装置の製造コストが増加する問題がある。

【0053】

具体的には、製造工程が増え、半導体装置の製造に要する時間が増加すればスループットが低下し、半導体装置の製造コストも増加する。洗浄装置内にSPM洗浄部、APM洗浄部およびHPM洗浄部を有するような洗浄装置はAPM洗浄部およびHPM洗浄部を有していない洗浄装置に比べて非常に高価になる。また、半導体装置の製造現場において、露光装置、成膜装置または洗浄装置などを設置するクリーンルームはその面積に限りがあるものであり、その面積を有効に活用するためにはそれぞれの装置を集約したり、縮小化することが望ましいのに対し、APM洗浄部およびHPM洗浄部を有するような洗浄装置は大きさが大きくなるため、このような装置を用いればクリーンルーム内の空間を有効に使用することができなくなる。

【0054】

これに対し、本実施の形態の半導体装置の製造工程においては、フォトレジスト膜の除去の際にアッシングを行わず、電解硫酸を用いてフォトレジスト膜を除去し、薬液に過酸化水素水を補充する必要がない基板の洗浄方法を用いる。以下に、図3、図7および図9を用いて説明した工程において行ったフォトレジスト膜の除去工程の詳細を、図10および図11を用いて説明する。図10は、本実施の形態の半導体装置の製造工程における洗浄工程を示すフロー(工程図)である。図11は、図10に示す洗浄工程で用いる洗浄装置を表わした模式図である。

【0055】

図10のステップS1に示すように、半導体基板の上面に形成されたフォトレジスト膜を除去する際には、まず電解硫酸を含む薬液を入れた電解硫酸槽に複数の半導体ウエハを浸す。これにより、半導体基板の表面に付着していたフォトレジスト膜または金属粒子は過硫酸または硫酸により除去される。なお、電解硫酸とは、硫酸を含む薬液(硫酸溶液)に、後述する過硫酸生成装置内の電極に電圧を印可することで生成した過硫酸を含む薬液(溶液)をいう。フォトレジスト膜の除去には過硫酸を用いることが重要であるため、前述した比較例では硫酸を含む薬液に過酸化水素水を加えることで過硫酸を生成していたが、本実施の形態の半導体装置の製造方法においては、電極を用いて硫酸を含む溶液に電圧を印可することで過硫酸を生成している。

【0056】

ここで、図11に本実施の形態の半導体装置の製造工程においてフォトレジスト膜などの除去に用いる洗浄装置の模式図を示す。図11では、薬液および水の循環経路ならびにそれらの流れる方向を矢印で示している。なお、薬液(硫酸溶液)の流れる経路は太い実線の矢印で示し、薬液の冷却に用いる冷却器内に供給される水の流れる経路は細い破線で示し、気体(ガス)の流れる経路は細い一点鎖線で示している。この洗浄装置RDは洗浄機Raおよび電解硫酸生成装置Rbを含んでいる。なお、本実施の形態では一体の洗浄装置RDが洗浄機Raおよび電解硫酸生成装置Rbを有している例を説明するが、洗浄機Raおよび電解硫酸生成装置Rbは別個の装置であってもよい。

【0057】

図11に示すように、洗浄装置RDを構成する洗浄機Raは、内部に電解硫酸槽60を有する。電解硫酸槽60は電解硫酸生成装置Rbから送り込まれる過硫酸などを含む硫酸溶液を用いて半導体ウエハ61を洗浄する洗浄槽であり、一度に複数の半導体ウエハ61を洗浄することができる所謂バッチ式の洗浄槽である。電解硫酸槽60内には前記硫酸溶液を加熱するヒータ62が設けられており、ヒータ62により電解硫酸槽60内の硫酸溶液は110℃〜150℃に加熱される。洗浄工程(レジスト除去工程)では、半導体ウエハ61は例えば50枚程度を並べて電解硫酸槽60内に一度に入れ、それらの表面の洗浄(レジスト除去)を行うことができる。なお、本願では過硫酸を含む硫酸溶液を電解硫酸と呼ぶが、図11に示す洗浄装置RD内を流れる硫酸溶液にも過硫酸は含まれているものとする。

【0058】

また、電解硫酸槽60内の硫酸溶液は主に過硫酸、硫酸および水により構成されており、この場合、電解硫酸槽60内の硫酸溶液内の過硫酸を含む硫酸濃度は80〜90wt%(重量パーセント)の濃度を有しているものとする。

【0059】

また、洗浄機Ra内には、電解硫酸槽60内の硫酸溶液がポンプ63を用いて吸い出され、配管を通じて再び電解硫酸槽60内に戻されるような循環経路が形成されている。前述したヒータ62は電解硫酸槽60内に配置せずに、前記循環経路を通過する硫酸溶液を加熱するように前記循環経路を構成する配管を囲むように配置してもよい。その場合は、例えば前記循環経路の途中に硫酸溶液がガラス管内を通る箇所を設け、そのガラス管の周りにランプによって硫酸溶液を加熱するヒータ62を設けることが考えられる。

【0060】

前記循環経路の途中には硫酸溶液を取出して電解硫酸生成装置Rbに送り込む配管と、電解硫酸生成装置Rbから前記循環経路に硫酸溶液を送り込む配管とが設けられている。電解硫酸生成装置Rbは内部に冷却器64、貯留槽65、過硫酸生成装置66、気液分離器67、ポンプ68〜70およびフィルタ71を有しており、洗浄機Ra内の循環経路から取り込まれた硫酸溶液はまず冷却器64により冷却された後、貯留槽65に送られる。冷却器64は例えば水を用いた水冷装置であり、冷却器64内の水はポンプ68を用いて冷却器64の中と外との間で循環され、その循環経路では冷却水の排出および供給が行われる。

【0061】

貯留槽65内に送られた硫酸溶液の一部はポンプ69により過硫酸生成装置66に送られ、その後気液分離器67に送られた後、再び貯留槽65に戻される。この経路では、硫酸溶液はまず過硫酸生成装置66において電気分解して過硫酸を生成し、硫酸溶液内の過硫酸の濃度を高める。ここで生成される過硫酸は、ペルオキソ二硫酸またはペルオキソ一硫酸の少なくとも一方を含むものである。このとき、過硫酸生成装置66での電気分解工程では硫酸溶液に気泡(ガス)が発生するが、この気泡は気液分離器67において硫酸溶液と分離される。

【0062】

過硫酸生成装置66は、フッ素樹脂などからなる配管内に陰極および陽極からなる電極対を有しており、それらの電極間に電圧印加し、硫酸溶液を介して50Aの電流を流すことにより、硫酸溶液内に過硫酸を生成する。ここでは電極間を流れる電流を50Aの直流電流で固定し、電極間の電圧を約100Vで可変させて電気分解を行う。過硫酸生成装置66内の電極には、不純物が導入されたダイヤモンド電極に銅板を組み合わせたものを使用する。過硫酸生成装置66により電圧を印可された硫酸と水とを含む硫酸溶液内には過硫酸と気泡とが生成される。

【0063】

気液分離器67内には、気泡を硫酸溶液から分離するために不活性ガスが供給されており、前記気泡(ガス)は前記不活性ガスと共に電解硫酸生成装置Rbの外部に排気される。ここでは、不活性ガスとして、図11に示すように例えば窒素(N2)を用いる。

【0064】

過硫酸生成装置66により過硫酸濃度が上昇した硫酸溶液は主に過硫酸、硫酸および水により構成されており、硫酸溶液内の過硫酸を含む硫酸の濃度は85wt%以上の濃度を有しているものとする。硫酸溶液を構成する前記水は、特に純度が高い純水であることが好ましい。ただし、硫酸溶液内には水を混合していなくてもよく、その場合、過硫酸生成装置66を通過した後の硫酸溶液内の過硫酸を含む硫酸の濃度は90wt%以上であるものとする。

【0065】

なお、過硫酸生成装置66はここでは対向する電極対を有するものとするが、この電極間に隔膜を設けて、陰極と陽極とで生成されるそれぞれの物質を分離して利用するような構造を有していても構わない。

【0066】

このように過硫酸生成装置66および気液分離器67を通して過硫酸濃度を高めた硫酸溶液を貯留槽65に戻すことで、電解硫酸槽60におけるレジスト除去および洗浄で消費された過硫酸を補うことができる。

【0067】

貯留槽65内の硫酸溶液の一部はポンプ70により洗浄機Ra内の循環経路にフィルタ71を通じて送られ、再び電解硫酸槽60内でレジストの除去および洗浄に用いられる。フィルタ71では、硫酸溶液内の微粒子などの不純物を取り除く。

【0068】

以上に述べたように、洗浄装置RD内には、洗浄機Ra内で循環し、電解硫酸槽60から硫酸溶液を取り出して再び電解硫酸槽60に戻す第1循環経路と、電解硫酸生成装置Rb内で循環し、貯留槽65内の硫酸溶液を取り出して過硫酸生成装置66および気液分離器67を通して過硫酸濃度を高めた後に貯留槽65に戻す第2循環経路とがある。また、洗浄機Raおよび電解硫酸生成装置Rb間で循環し、第1循環経路から取出した硫酸溶液を貯留槽65に溜めた後に第1循環経路に再び戻す第3循環経路がある。

【0069】

硫酸溶液内の過硫酸は電解硫酸槽60でレジスト除去および洗浄のために消費されるが、上記のように過硫酸生成装置66で連続的に生成された過硫酸を貯留槽65を介して電解硫酸槽60に供給することで補われる。このため、硫酸溶液に過酸化水素水を加えなくても過硫酸濃度の低下を防ぐことができるため、過酸化水素水を加えることに起因して硫酸溶液内に水が生成されることがなく、硫酸溶液内の水が増えることを防ぎ、硫酸溶液のレジスト除去性能が低下することを防ぐことができる。

【0070】

つまり、前述したSPM洗浄とは違い、レジスト除去性能が低下することなく、高いレジスト除去性能を維持することができるため、電解硫酸槽60で行うレジスト除去では有機物などの有機物または金属などからなる微粒子または残渣が半導体基板の表面に残ることを防ぐことができる。したがって、電解硫酸を用いてフォトレジスト膜の除去および半導体基板の洗浄を行う本実施の形態では、SPM洗浄を行った後に必要であったAPM洗浄およびHPM洗浄を行う必要がない。SPM洗浄を行う洗浄機内にはSPM洗浄槽のみならずAPM洗浄部およびHPM洗浄部が設けられていることが考えられるが、本実施の形態の基板の洗浄方法ではAPM洗浄およびHPM洗浄を行わないため、洗浄機Ra内には電解硫酸槽60の他に薬液を用いる洗浄装置(洗浄部)を必要としない。よって、洗浄装置RDを小さくすることが可能であるため、洗浄装置が高価なものになることを防ぎ、洗浄装置RDの大きさを小さくすることができる。これにより、例えば洗浄装置RDをクリーンルーム内などに配置した場合、SPM洗浄部、APM洗浄部およびHPM洗浄部を有する洗浄装置を配置する場合に比べてクリーンルーム内の空間をより有効に利用することができる。

【0071】

また、SPM洗浄、APM洗浄またはHPM洗浄などで洗浄を行う場合、アッシングをせずに薬液および水での洗浄工程のみでフォトレジスト膜を除去することは困難である。したがって、アッシングを行う場合の洗浄工程の手順としては、以下の(1)〜(6)のそれぞれに示す工程順に行う方法が考えられる。

(1)アッシング、SOM洗浄、純水リンス洗浄、APM洗浄、純水リンス洗浄、HPM洗浄、純水リンス洗浄、乾燥。

(2)アッシング、SPM洗浄、純水リンス洗浄、APM洗浄、純水リンス洗浄、HPM洗浄、純水リンス洗浄、乾燥。

(3)アッシング、SPM洗浄、純水リンス洗浄、APM洗浄、純水リンス洗浄、乾燥。

(4)アッシング、SOM洗浄、純水リンス洗浄、乾燥。

(5)アッシング、SPM洗浄、純水リンス洗浄、乾燥。

(6)アッシング、APM洗浄、純水リンス洗浄、HPM洗浄、純水リンス洗浄、乾燥。

【0072】

ここで、例えば上記の手順(1)は、アッシングの後に順にSOM洗浄、純水リンス洗浄(純水リンス工程)、APM洗浄、純水リンス洗浄(純水リンス工程)、HPM洗浄、純水リンス洗浄(純水リンス工程)および乾燥を行うことを示している。なお、SOM(sulfuric-ozone mix)洗浄は、硫酸槽にオゾン(O3)を吹き込んでフォトレジスト膜などを除去し、対象物を洗浄を行う洗浄方法であり、SPM洗浄よりは洗浄能力が劣る洗浄方法である。

【0073】

前述したように、APM洗浄およびHPM洗浄はSPM洗浄で除去できなかった微粒子、または洗浄対象物に付着している金属粒子などを除去するために行うものであるため、SPM洗浄、SOM洗浄を行わない上記手順(6)と、APM洗浄またはHPM洗浄を行わない上記手順(3)〜(5)とは、例えば上記手順(1)、(2)に比べて洗浄性能が低く、使用できる条件が限られる。

【0074】

アッシングを行わず、SPM洗浄によりフォトレジスト膜を除去することも考えられるが、前述したようにSPM洗浄では除去できるフォトレジスト膜の量(膜厚)が大きい場合はレジスト除去が困難になるし、1×1013個/cm2よりも多く不純物が導入されたフォトレジスト膜はSPM洗浄では除去できないという制限がある。

【0075】

これに対し、本実施の形態で用いる洗浄装置RDは高いレジスト除去性能を有していることから、アッシングを行わずに半導体基板表面のフォトレジスト膜を取り除くことができるため、半導体装置の製造工程を図10に示すように簡略化し、スループットを向上させることで、半導体装置の製造コストを低減することができる。本実施の形態のレジスト除去工程では、電解硫酸を用いた洗浄が高いレジスト除去性能を有していることにより、イオン注入工程で打ち込み防止のマスクとして用いられたフォトレジスト膜であって、不純物が5×1014個/cm2注入され、SPM洗浄法では剥離が困難なフォトレジスト膜でも除去することができる。

【0076】

すなわち、不純物が1×1013個/cm2よりも多く注入されたフォトレジスト膜を除去することが困難なSPM洗浄法に比べ、本実施の形態の半導体装置の製造方法における洗浄工程では、より多くの不純物が導入され、除去が困難となったフォトレジスト膜であっても除去することができる。また、このようにレジスト除去性能が向上することで、膜厚が厚いためにSPM洗浄では除去が困難なフォトレジスト膜であっても除去することができる。

【0077】

この場合、アッシング工程を省略することが可能となるため、本実施の形態の基板の洗浄工程では、電解硫酸洗浄、純水リンス洗浄、乾燥という少ない工程で基板の洗浄を行うことができる。つまり、アッシング工程を省くことで、上記手順(1)〜(6)のいずれの洗浄方法よりも洗浄工程を少なくし、かつ洗浄性能を向上させることができる。

【0078】

次に、電解硫酸洗浄(図10のステップS1)を行った後は、半導体基板の表面に残る電解硫酸を取り除くため、QDR工程(ステップS2)、70℃OF工程(ステップS3)および常温OF工程(ステップS4)を順に行い、続いて半導体基板を乾燥させる乾燥工程(ステップS5)を行う。ステップS3の70℃OF工程では、約70℃に温められた純水を用いて半導体基板を洗浄を行い、ステップS4の常温OF工程では、約25℃の純水を用いて半導体基板を洗浄を行う。本実施の形態では、図10に示すステップS2〜S3に示すQDR工程、70℃OF工程および常温OF工程をまとめて純水リンス工程と呼ぶ。

【0079】

図11に示す洗浄機Ra内には半導体基板を洗浄するためのQDR(ステップS2)、70℃OF工程(ステップS3)および常温OF工程(ステップS4)を行う装置が設けられていてもよく、半導体基板を乾燥させるための装置が設けられていてもよい。これは、SPM洗浄を行う洗浄装置であっても同様である。本実施の形態では、図11に示していないが、洗浄機Ra内にはQDR洗浄部、OF洗浄部および乾燥装置が配置されているものとする。したがって、洗浄装置RD内に搬送され、電解硫酸槽60でフォトレジスト膜などの有機物または金属粒子などを除去された半導体ウエハ61は、洗浄機Ra内のQDR洗浄部で純水洗浄された後にOF洗浄部で純水洗浄され、続いて乾燥装置で乾燥工程を経た後に洗浄装置RDから取り出され、次の成膜工程などに用いられる装置に搬送されるものとする。つまり、電解硫酸による洗浄、純水洗浄および乾燥は一台の装置内で処理される。

【0080】

なお、実際に洗浄装置RDを使用する場合には、電解硫酸槽60内に半導体ウエハ61を入れていない状態で硫酸溶液を上記第1〜第3循環経路を循環させ、電解硫酸槽60内の硫酸溶液の温度をヒータ62により例えば140℃程度に加熱し、冷却器64での硫酸溶液の冷却、過硫酸生成装置66での過硫酸の生成、および気液分離器67での気泡分離などを一定時間行う。この洗浄装置RD内のでの一連の動作により硫酸溶液の温度、濃度分布などが定常状態となった後に、レジスト膜が付いた半導体ウエハ61を電解硫酸槽60内に浸し、洗浄を開始する。

【0081】

本実施の形態の基板の洗浄工程は、図10に示すように、比較例として図21に示した洗浄工程に比べて工程数が少ないため、半導体装置の製造工程が簡略化されている。これは、前述したように電解硫酸を用いて半導体基板の洗浄を行っても薬液のレジスト除去性能が低下しないため、薬液のレジスト除去性能が低下するSPM洗浄の後に必要であったAPM洗浄およびHPM洗浄が不要だからである。また本実施の形態の場合はフォトレジスト膜除去のためのアッシングも不要であり、図21に示す比較例の洗浄工程を行った場合に比べ、本実施の形態の洗浄工程を行えば洗浄工程にかかる時間を半分程度に短縮することができる。

【0082】

本発明者らは、電解硫酸を用いた洗浄を繰り返し行った場合、過酸化水素水を補充しなくてもレジスト除去性能が低下しないことを実証するため、洗浄装置の連続稼働によるレジスト除去性能の変化を調べる実験を行った。この実験は、直径6インチの半導体ウエハの主面の全面に、厚さ1.7μmのフォトレジスト膜を塗布し、このフォトレジスト膜の表面にP型の不純物であるホウ素(B)を100keVのエネルギーで5×1014個/cm2導入した半導体ウエハを一度に50枚バッチ処理(洗浄)する事を繰り返し行うものであり、洗浄装置RDを用いたこの洗浄処理を29日間連続稼働させて行った。この期間中に洗浄処理した半導体ウエハは合計1775枚である。また、この期間中に硫酸溶液の補充または交換は行っておらず、硫酸溶液に対する過酸化水素水の供給も行っていない。実験では、最初に洗浄処理を行った半導体ウエハと、29日の連続稼働の最後に洗浄処理した半導体ウエハのそれぞれの表面に残留する直径0.3μm以上の微粒子数を数えることでレジスト除去性能の変化を比較した。

【0083】

実験の結果、実験開始時に洗浄装置RDに硫酸溶液を投入し、装置を稼働させて最初に洗浄を行った半導体ウエハと、29日の連続稼働の最後に洗浄処理した半導体ウエハでは、洗浄処理後に半導体ウエハの表面に残る微粒子の数はほぼ同一といえる程度であり、具体的には一枚の半導体ウエハの主面には10〜30個の微粒子が残存しているのみであった。このことから、電解硫酸を用いた洗浄では、過酸化水素水または硫酸を補充しなくても高いレジスト除去性能を維持することが可能であり、また、過酸化水素水を補充することに起因する水の発生もないため、硫酸溶液が水によって薄まることもなく、レジスト除去性能が低下することを防ぐことが可能であることが分かる。

【0084】

さらに、電解硫酸を用いた洗浄ではフォトレジスト膜のような有機物だけでなく、半導体基板の主面に付着している金属粒子を除去することが可能である。本発明者らが行った実験では、アッシング装置(アッシャー)を用いたアッシングによりレジスト除去を行った場合、半導体基板の表面に金属の残渣が付着しやすいことを利用し、アッシング工程の直後の半導体基板と、アッシング工程の後に電解硫酸を用いた洗浄を行った半導体基板のそれぞれの表面に付着している金属の単位面積当たりの原子数(atoms/cm2)を比べることで、電解硫酸を用いた洗浄による金属除去性能を調べた。

【0085】

図12に示す表は、アッシング工程の後に洗浄を行っていない、つまり電解硫酸による異物の除去工程の前の半導体基板の表面に残存する各金属の原子数を測定した結果を上段に示し、本実施の形態の半導体装置の製造方法で使用する電解硫酸を用いた異物の除去工程(洗浄)をアッシング工程の後に行った場合の半導体基板の表面に残存する各金属の原子数を測定した結果を下段に示すものである。つまり、図12は本実施の形態で用いる電解硫酸の金属除去性能を示している。なお、表の原子数の数値の右側に下向きの矢印が記載されているデータは、実際に半導体基板の表面に残存する原子数がその数値以下であることを示し、計測が困難な程度にまで金属の原子数が少なくなっていることを表わしている。

【0086】

図12に示すように、アッシングを行った半導体基板の表面には特にAlおよびFeが付着しやすく、他の金属に比べて多数の原子が付着していることが分かる。これに対し、電解硫酸による洗浄を行った後の半導体基板の表面におけるAlおよびFeの原子数は大幅に減少している。このように、硫酸が元々有する金属除去性能は電解硫酸も有しているため、電解硫酸を用いた洗浄では半導体基板の主面に形成された金属粒子などを除去することが可能である。

【0087】

次に、図13に示すように、p型ウエル5のゲート電極8aの両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)n−型半導体領域9aを形成し、n型ウエル6のゲート電極8bの両側の領域にホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)p−型半導体領域10aを形成する。n−型半導体領域9aおよびp−型半導体領域10aの深さ(接合深さ)は、例えば30nm程度とすることができる。

【0088】

その後、ゲート電極8a、8bの側壁上に、絶縁膜として、例えば酸化シリコンまたは窒化シリコンあるいはそれら絶縁膜の積層膜などからなる側壁スペーサまたはサイドウォール(側壁絶縁膜)11を形成する。サイドウォール11は、例えば、半導体基板1上に酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜を堆積し、この酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜をRIE(Reactive Ion Etching)法などにより異方性エッチングすることによって形成することができる。

【0089】

サイドウォール11の形成後、(一対の)n+型半導体領域9b(ソース、ドレイン領域)を、例えば、p型ウエル5のゲート電極8aおよびサイドウォール11の両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより形成する。例えば、リン(P)を5×1015/cm2程度、ヒ素(As)を4×1015/cm2程度注入して形成する。また、(一対の)p+型半導体領域10b(ソース、ドレイン領域)を、例えば、n型ウエル6のゲート電極8bおよびサイドウォール11の両側の領域にホウ素(B)などのp型の不純物をイオン注入することにより形成する。例えば、ホウ素(B)を4×1015/cm2程度注入して形成する。n+型半導体領域9bを先に形成しても、あるいはp+型半導体領域10bを先に形成しても良い。イオン注入後、導入した不純物の活性化のためのアニール処理を、例えば1050℃程度で5秒程度の熱処理(スパイクアニール処理)にて行うこともできる。n+型半導体領域9bおよびp+型半導体領域10bの深さ(接合深さ)は、例えば80nm程度とすることができる。

【0090】

n+型半導体領域9bは、n−型半導体領域9aよりも不純物濃度が高く、p+型半導体領域10bは、p−型半導体領域10aよりも不純物濃度が高い。これにより、nチャネル型MISFETのソースまたはドレインとして機能するn型の半導体領域(不純物拡散層)が、n+型半導体領域(不純物拡散層)9bおよびn−型半導体領域9aにより形成され、pチャネル型MISFETのソースまたはドレインとして機能するp型の半導体領域(不純物拡散層)が、p+型半導体領域(不純物拡散層)10bおよびp−型半導体領域10aにより形成される。従って、nチャネル型MISFETおよびpチャネル型MISFETのソース・ドレイン領域は、LDD(Lightly doped Drain)構造を有している。n−型半導体領域9aは、ゲート電極8aに対して自己整合的に形成され、n+型半導体領域9bは、ゲート電極8aの側壁上に形成されたサイドウォール11に対して自己整合的に形成される。p−型半導体領域10aは、ゲート電極8bに対して自己整合的に形成され、p+型半導体領域10bは、ゲート電極8bの側壁上に形成されたサイドウォール11に対して自己整合的に形成される。

【0091】

このようにして、p型ウエル5に、電界効果トランジスタとしてnチャネル型MISFETQnが形成される。また、n型ウエル6に、電界効果トランジスタとしてpチャネル型MISFETQpが形成される。これにより、図13の構造が得られる。nチャネル型MISFETQnは、nチャネル型の電界効果トランジスタとみなすことができ、pチャネル型MISFETQpは、pチャネル型の電界効果トランジスタとみなすことができる。また、n+型半導体領域9bは、nチャネル型MISFETQnのソースまたはドレイン用の半導体領域とみなすことができ、p+型半導体領域10bは、pチャネル型MISFETQpのソースまたはドレイン用の半導体領域とみなすことができる。

【0092】

次に、サリサイド(Salicide:Self Aligned Silicide)技術により、nチャネル型MISFETQnのゲート電極8aおよびソース・ドレイン領域(ここではn+型半導体領域9b)の表面と、pチャネル型MISFETQpのゲート電極8bおよびソース・ドレイン領域(ここではp+型半導体領域10b)の表面とに、低抵抗の金属シリサイド層(後述の金属シリサイド層41に対応)を形成する。本実施の形態におけるサリサイドプロセスは部分反応方式のサリサイドプロセスを用い、以下に、金属シリサイド層の形成工程について説明する。

【0093】

上記のようにして図13の構造が得られた後、図14に示すように、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面を露出した状態で、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10b上を含む半導体基板1の主面(全面)上に金属膜12を、例えばスパッタリング法を用いて形成(堆積)する。すなわち、n+型半導体領域9bおよびp+型半導体領域10b上を含む半導体基板1上に、ゲート電極8a、8bを覆うように、金属膜12が形成される。金属膜12は、例えばNi(ニッケル)−Pt(白金)合金膜(NiとPtの合金膜)からなり、その厚さ(堆積膜厚)は、例えば15〜40nm程度とすることができる。

【0094】

次に、図15に示すように、半導体基板1に第1の熱処理(1stアニール処理)を施す。ここで、第1の熱処理は、250℃〜300℃で行うことが好ましい。第1の熱処理により、ゲート電極8a、8bを構成する多結晶シリコン膜と金属膜12、およびn+型半導体領域9bおよびp+型半導体領域10bを構成する単結晶シリコンと金属膜12を選択的に反応させて、金属・半導体反応層である金属シリサイド層41を形成する。このとき、金属膜12内のNi−Pt合金膜は、半導体基板1(ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部)に接する底面側から反対側の上面方向に向かって5〜7nmの範囲のNi−Pt合金がゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部と反応する。

【0095】

すなわち、図14に示す工程において半導体基板1上に15〜40nmの厚さで形成された金属膜12が、第1の熱処理において、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部において反応して図15に示す金属シリサイド層41となるのは、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部の金属膜12の全膜厚の内の一部である。このため、図15に示すように、金属シリサイド層41が形成された半導体基板1上の金属膜12は、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部において、他の領域の金属膜12の膜厚に比べて膜厚が薄くなっている。このように、金属膜12の膜厚の一部のみを必要量だけ反応させて金属シリサイド層41を形成するサイリサイドプロセスを、ここでは部分反応方式のサリサイドプロセスと呼ぶ。

【0096】

次に、図16に示すように、未反応の金属膜12(すなわちゲート電極8a、8b、n+型半導体領域9bまたはp+型半導体領域10bと反応しなかった金属膜12)とを除去する。この際、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面上に金属シリサイド層41を残存させる。

【0097】

その後、半導体基板1に第2の熱処理(2ndアニール処理)を施す。第2の熱処理は、上記第1の熱処理の熱処理温度とほぼ同程度か、もしくはそれよりも高い熱処理温度で行う。第2の熱処理を行うことで、金属シリサイド層41は低抵抗のNiSiにより構成される領域となる。

【0098】

次に、図17に示すように、半導体基板1の主面上に絶縁膜42を形成する。すなわち、ゲート電極8a、8bを覆うように、金属シリサイド層41上を含む半導体基板1上に絶縁膜42を形成する。絶縁膜42は例えば窒化シリコン膜からなり、成膜温度(基板温度)450℃程度のプラズマCVD法などにより形成することができる。それから、絶縁膜42上に絶縁膜42よりも厚い絶縁膜43を形成する。絶縁膜43は例えば酸化シリコン膜などからなり、TEOSを用いて成膜温度450℃程度のプラズマCVD法などにより形成することができる。これにより、絶縁膜42、43からなる層間絶縁膜が形成される。その後、絶縁膜43の表面をCMP法により研磨するなどして、絶縁膜43の上面を平坦化する。下地段差に起因して絶縁膜42の表面に凹凸形状が形成されていても、絶縁膜43の表面をCMP法により研磨することにより、その表面が平坦化された層間絶縁膜を得ることができる。

【0099】

次に、図18に示すように、絶縁膜43上に形成したフォトレジスト膜(図示せず)をエッチングマスクとして用いて、絶縁膜43、42をドライエッチングすることにより、絶縁膜42、43にコンタクトホール(貫通孔、孔)44を形成する。この際、まず絶縁膜42に比較して絶縁膜43がエッチングされやすい条件で絶縁膜43のドライエッチングを行い、絶縁膜42をエッチングストッパ膜として機能させることで、絶縁膜43にコンタクトホール44を形成してから、絶縁膜43に比較して絶縁膜42がエッチングされやすい条件でコンタクトホール44の底部の絶縁膜42をドライエッチングして除去する。コンタクトホール44の底部では、半導体基板1の主面の一部、例えばn+型半導体領域9bおよびp+型半導体領域10bの表面上の金属シリサイド層41の一部や、ゲート電極8a、8bの表面上の金属シリサイド層41の一部などが露出される。その後、前記フォトレジスト膜(図示せず)はレジスト除去方法により除去する。

【0100】

続いて、コンタクトホール44内に、タングステン(W)などからなるプラグ(接続用導体部、埋め込みプラグ、埋め込み導体部)45を形成する。プラグ45を形成するには、例えば、コンタクトホール44の内部(底部および側壁上)を含む絶縁膜43上に、成膜温度(基板温度)450℃程度のプラズマCVD法によりバリア導体膜45a(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、タングステン膜などからなる主導体膜45bをCVD法などによってバリア導体膜45a上にコンタクトホール44を埋めるように形成し、絶縁膜43上の不要な主導体膜45bおよびバリア導体膜45aをCMP法またはエッチバック法などによって除去することにより、プラグ45を形成することができる。ゲート電極8a、8b、n+型半導体領域9bまたはp+型半導体領域10b上に形成されたプラグ45は、その底部でゲート電極8a、8b、n+型半導体領域9bまたはp+型半導体領域10bの表面上の金属シリサイド層41と接して、電気的に接続される。

【0101】

次に、図19に示すように、プラグ45が埋め込まれた絶縁膜43上に、ストッパ絶縁膜51および配線形成用の絶縁膜52を順次形成する。ストッパ絶縁膜51は絶縁膜52への溝加工の際にエッチングストッパとなる膜であり、絶縁膜52に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜51は、例えばプラズマCVD法により形成される窒化シリコン膜とし、絶縁膜52は、例えばプラズマCVD法により形成される酸化シリコン膜とすることができる。なお、ストッパ絶縁膜51と絶縁膜52には次に説明する第1層目の配線が形成される。

【0102】

続いて、シングルダマシン法により第1層目の配線を形成する。まず、フォトレジスト膜(図示せず)をマスクとしたドライエッチングによって絶縁膜52およびストッパ絶縁膜51の所定の領域に配線溝53を形成し、前記フォトレジスト膜を除去した後、半導体基板1の主面上(すなわち配線溝の底部および側壁上を含む絶縁膜52上)にバリア導体膜(バリアメタル膜)54を形成する。その後、前記フォトレジスト膜はレジスト除去方法により除去する。バリア導体膜54は、例えば窒化チタン膜、タンタル膜または窒化タンタル膜などを用いることができる。

【0103】

続いて、CVD法またはスパッタリング法などによりバリア導体膜54上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成する。銅めっき膜により配線溝53の内部を埋め込む。それから、配線溝53以外の領域の銅めっき膜、シード層およびバリア導体膜54をCMP法により除去して、銅を主導電材料とする第1層目の配線55を形成する。配線55は、プラグ45を介してnチャネル型MISFETQnおよびpチャネル型MISFETQpのソースまたはドレイン用のn+型半導体領域9bおよびp+型半導体領域10bやゲート電極8a、8bなどと電気的に接続されている。その後、デュアルダマシン法により第2層目の配線を形成するが、ここでは図示およびその説明は省略する。以上により、本実施の形態のCMISFETを有する半導体装置が完成する。

【0104】

本実施の形態の半導体装置の製造方法では、基板の洗浄方法として電解硫酸を用いることで半導体基板の表面のフォトレジスト膜などの有機物からなる微粒子または残渣を除去し、さらに金属粒子を除去することができる。この場合、SPM洗浄法のように、薬液(硫酸溶液)に過酸化水素水を補充し続ける必要もなく、また、硫酸溶液のレジスト除去性能も低下しないため、アッシング工程を省略することも可能である。よって、半導体装置の製造工程を簡略化し、スループットを向上させて半導体装置の製造コストを低減することが可能である。

【0105】

本実施の形態の半導体装置の製造工程では、例えば図3、図7および図9において説明したフォトレジスト膜の除去において、電解硫酸を用いた上記除去・洗浄方法を用いることで、比較例として図21を用いて説明したSPM洗浄法を用いる除去・洗浄方法に比べて半導体装置の製造工程を簡略化することを可能としている。

【0106】

また、電解硫酸を用いる洗浄装置内にはAPM洗浄部およびHPM洗浄部が不要であるため、SPM洗浄を行う洗浄装置に比べ、本実施の形態では洗浄装置を小さくすることが可能である。これにより、APM洗浄部およびHPM洗浄部を有する洗浄装置よりも価格が低い洗浄装置を用いることができ、また、小さい洗浄装置を用いることでクリーンルーム内の空間を有効に使用することができるため、設備投資を低減することで半導体装置の製造コストを低減することができる。

【0107】

(実施の形態2)

前記実施の形態では、図10に示すステップS2〜S4において純水リンス工程を行っているが、本実施の形態では、図20に示すように、ステップS3aの70℃OF工程において洗浄用の水(例えば純水)に超音波を印加する洗浄方法、または、ステップS4aの常温OF工程において洗浄用の水に電解イオン水を供給する方法を用いる。

【0108】

具体的には、図20に示すステップS3aの70℃OF洗浄工程では、純水リンス槽内の洗浄用水に1MHz程度の周波数の超音波を印加することにより、電解硫酸洗浄(ステップS1)およびQDR工程(ステップS2)で除去できなかった半導体基板の表面の微粒子を物理的に分離し、取り除くことができる。これにより、70℃OF洗浄の洗浄性能を向上させることができる。

【0109】

また、図20に示すステップS4aの常温OF洗浄工程では、洗浄用水に電気分解により生成したイオン水(還元水)を供給した混合液を洗浄に用いる。この洗浄工程では、半導体基板とその表面の微粒子が共にマイナスに帯電するため、互いの反発力により微粒子を基板表面から分離させて除去することができる。これにより、常温OF洗浄の洗浄性能を向上させることができる。

【0110】

上記の超音波印加および電解イオン水供給はいずれか一方のみを純水リンス工程に適用してもよいし、両方を適用してもよい。これにより、純水洗浄性能を高め、より信頼性の高い半導体装置を製造することができる。

【0111】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0112】

例えば、前記実施の形態1、2では、半導体基板上に半導体素子を形成する場合の洗浄方法について説明したが、本発明を適用する技術はこれに限らず、例えば半導体基板ではないガラス基板、サファイア基板などを用いた基板の表面に残存または付着した有機物の除去などに適用することもできる。

【0113】

また、過硫酸および硫酸を含む硫酸溶液はフォトレジスト膜以外の有機物または金属粒子なども除去することが可能であるため、除去・洗浄する対象はフォトレジスト膜に限られない。

【産業上の利用可能性】

【0114】

本発明は、基板上の有機膜または金属粒子などを除去する工程を有する装置の製造技術に適用して有効である。

【符号の説明】

【0115】

1 半導体基板

2 絶縁膜

3 絶縁膜

4 素子分離領域

4a 溝

4b 絶縁膜

4c 絶縁膜

5 p型ウエル

6 n型ウエル

7 ゲート絶縁膜

8 シリコン膜

8a、8b ゲート電極

9a n−型半導体領域

9b n+型半導体領域

10a p−型半導体領域

10b p+型半導体領域

10p p型半導体層

11 サイドウォール

12 金属膜

41 金属シリサイド層

42、43、52 絶縁膜

44 コンタクトホール

45 プラグ

45a バリア導体膜

45b 主導体膜

51 ストッパ絶縁膜

53 配線溝

54 バリア導体膜

55 配線

60 電解硫酸槽

61 半導体ウエハ

62 ヒータ

63、68〜70 ポンプ

64 冷却器

65 貯留槽

66 過硫酸生成装置

67 気液分離器

71 フィルタ

Qn nチャネル型MISFET

Qp pチャネル型MISFET

R1〜R3 フォトレジスト膜

Ra 洗浄機

Rb 電解硫酸生成装置

RD 洗浄装置

S1〜S5 ステップ

S3a、S4a ステップ

SP1〜SP11 ステップ

【技術分野】

【0001】

本発明は、基板の洗浄方法および半導体装置の製造方法に関し、特に、基板表面に付着した有機膜または金属粒子などの除去工程を有する半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

半導体装置の製造工程においてパターニングのマスクとして使用するなどの目的により基板上に形成したフォトレジスト膜を除去する工程では、まずアッシング(灰化)することでフォトレジスト膜の大部分を除去した後、例えば硫酸および過酸化水素水を含む薬液を用いて基板表面にSPM(Sulfuric acid/hydrogen peroxide mixture)洗浄法による洗浄を行うことが知られている。

【0003】

特許文献1(特開2008−111184号公報)には、過硫酸を用いた洗浄システムなどに対し、高濃度の過硫酸を安定して供給することが可能な過硫酸供給システムが記載されている。

【0004】

特許文献2(特開2008−019507号公報)には、隔膜を挟むように配置された陽極および陰極を有する硫酸電解部を用いて生成した濃硫酸を用いて対象物の洗浄処理を行うことが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−111184号公報

【特許文献2】特開2008−019507号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

アッシング工程の後に半導体基板(半導体ウエハ)の表面に残ったフォトレジスト膜または金属粒子などを除去することを目的としてSPM洗浄を行っても、半導体基板上には有機物などの微粒子(残渣)が残る可能性が高く、それらを除去するために、アンモニア、過酸化水素水および水を含む薬液を用いたAPM(ammonium hydroxide/hydrogen peroxide/water mixture)洗浄を行う必要がある。また、APM洗浄を行った場合は、その後に半導体基板上に残った金属粒子を除去するために、塩酸、過酸化水素水および水を含む薬液を用いたHPM(hydrochloric acid/hydrogen peroxide/water mixture)洗浄を行う必要がある。

【0007】

また、上記SPM洗浄、APM洗浄およびHPM洗浄のそれぞれを行った際は、次の工程に進む前に、それらの工程で用いた薬液を半導体基板の表面に残さないように除去する工程が必要となる。その場合は、例えばSPM洗浄を行った後に純水を用いた洗浄(純水リンス洗浄)を行い、その後にAPM洗浄を行う。同様に、APM洗浄の後HPM洗浄を行う前にも純水リンス洗浄を行い、HPM洗浄の後にも純水リンス洗浄を行う。

【0008】

このように、半導体基板上のフォトレジスト膜を除去する際にSPM洗浄を行うと、SPM洗浄を行ったことに起因してさらに複数の洗浄工程を行うことになるため、製造工程が煩雑になり、それによって製造工程にかかる時間も長くなるため、半導体装置の製造コストが増加する問題がある。また、フォトレジスト膜除去のための装置の内部または外部にAPM洗浄部(APM洗浄槽)およびHPM洗浄部(HPM洗浄槽)を設ける必要があるため、半導体装置の製造に用いる設備が大きく高価になることによっても半導体装置の製造コストが増加する。また、APM洗浄部およびHPM洗浄部を設けることで、半導体装置の製造を行うクリーンルーム内の空間を洗浄装置が占める割合が大きくなり、床面積に限りがあるクリーンルームを有効に使用することが阻害されるため、半導体装置の製造効率が低下する問題がある。

【0009】

上記のようにSPM洗浄の後にAPM洗浄およびHPM洗浄が必要になる理由として、SPM洗浄用の薬液を循環させて繰り返し洗浄に用いることにより薬液の洗浄力が低下することが挙げられる。SPM洗浄に用いる薬液は装置内で循環させ、フィルタを通すことで何度も洗浄に使用することが考えられるが、その場合、当該薬液中の過硫酸の濃度を低下させないために循環する当該薬液に過酸化水素水(H2O2)を補充し続けなければならない。過酸化水素水が加えられた薬液は過硫酸が生成されるが、それと同時に水(H2O)も生成されるため、結局薬液の過硫酸濃度は徐々に低下し、レジスト除去性能が低下する。したがって、ある程度循環させて何度も洗浄に用いたSPM洗浄用の薬液は一旦全て廃棄し、新たに洗浄装置内に硫酸および過酸化水素水を供給して洗浄用の薬液を用意する必要がある。過酸化水素水を当該薬液に補充し続けること、および定期的に当該薬液を交換する必要があることは半導体装置の製造コストの増加に繋がる。

【0010】

このように水が発生することでSPM洗浄のレジスト除去性能は低下し、フォトレジスト膜の一部や微粒子が残渣となって半導体基板上に残る可能性があるため、リスク回避のためにAPM洗浄が必要となる。また、APM洗浄ではアルミニウム(Al)、鉄(Fe)のような金属不純物が微量でも混入すると金属粒子が半導体基板の表面に多量に付着するため、それを除去するためにHPM洗浄が必要となる。

【0011】

本発明の目的は、半導体装置の製造工程を簡略化する技術を提供することにある。

【0012】

本発明の他の目的は、半導体装置の製造コストを低減することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

すなわち、本願発明の半導体装置の製造方法は、

(a)基板を電解硫酸を用いて洗浄する工程、

(b)前記基板を水を用いて洗浄する工程、

(c)前記基板を乾燥させる工程、

を有する半導体装置の製造方法であって、

前記(a)工程の前に前記基板へのアッシング工程を行わず、

前記(c)工程の前にAPM洗浄工程およびHPM洗浄工程を有していないものである。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

代表的な実施の形態によれば、半導体装置の製造工程を簡略化することができる。

【0018】

半導体装置の製造コストを低減することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1である半導体装置の製造工程中の要部断面図である。

【図2】図1に続く半導体装置の製造工程中の要部断面図である。

【図3】図2に続く半導体装置の製造工程中の要部断面図である。

【図4】図3に続く半導体装置の製造工程中の要部断面図である。

【図5】図4に続く半導体装置の製造工程中の要部断面図である。

【図6】図5に続く半導体装置の製造工程中の要部断面図である。

【図7】図6に続く半導体装置の製造工程中の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の要部断面図である。

【図10】本発明の実施の形態1である半導体装置の洗浄工程のフローである。

【図11】本発明の実施の形態1である半導体装置の製造工程で用いる洗浄装置の模式図である。

【図12】本発明の実施の形態1で用いる薬液の金属除去性能を説明する表である。

【図13】図9に続く半導体装置の製造工程中の要部断面図である。

【図14】図13に続く半導体装置の製造工程中の要部断面図である。

【図15】図14に続く半導体装置の製造工程中の要部断面図である。

【図16】図15に続く半導体装置の製造工程中の要部断面図である。

【図17】図16に続く半導体装置の製造工程中の要部断面図である。

【図18】図17に続く半導体装置の製造工程中の要部断面図である。

【図19】図18に続く半導体装置の製造工程中の要部断面図である。

【図20】本発明の実施の形態2である半導体装置の洗浄工程のフローである。

【図21】比較例である半導体装置の製造工程中の洗浄工程のフローである。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

(実施の形態1)

まず、本実施の形態の半導体装置の製造工程を図面を参照して説明する。図1〜図9および図13〜図19は、本発明の一実施の形態である半導体装置、例えばCMISFET(Complementary Metal Insulator Semiconductor Field Effect Transistor)を有する半導体装置の製造工程中の要部断面図であり、それぞれの図に示す基板上面の右側の領域にはnチャネル型MISFETが形成され、左側の領域にはpチャネル型MISFETが形成される。

【0022】

まず、図1に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次に、この半導体基板1を熱酸化してその表面に例えば厚さ11nm程度の絶縁膜2を形成した後、その上層にCVD(Chemical Vapor Deposition)法などにより、例えば厚さ90nm程度の絶縁膜3を堆積する。絶縁膜2は酸化シリコンなどからなり、絶縁膜3は窒化シリコン膜などからなる。

【0023】

次に、図2に示すように、フォトリソグラフィ技術を用いてフォトレジスト膜R1を半導体基板1上の形成する。すなわち、半導体基板1上の全面にフォトレジスト膜R1を形成(塗布)した後、フォトレジスト膜R1をフォトマスクを用いて一部露光し、続いて現像することにより、フォトレジスト膜R1を所定の形状のパターンとして絶縁膜3上に残す。

【0024】

次に、図3に示すように、フォトレジスト膜R1をエッチングマスクとして絶縁膜3、絶縁膜2および半導体基板1を順次ドライエッチングすることにより、素子分離形成予定領域の半導体基板1に、例えば深さ300nm程度の溝(素子分離用の溝)4aを形成する。溝4aは、素子分離用の溝であり、すなわち後述する素子分離領域4形成用の溝である。その後、フォトレジスト膜R1を電解硫酸を用いた薬液により除去し、半導体基板の主面を洗浄する。当該洗浄方法の詳細な工程については、後に図10および図11を用いて説明する。なお、フォトレジスト膜R1の除去工程では、アッシング(灰化)は行わないものとする。また、いうまでもなく、本願では水のみを用いた洗浄に用いる液体(水)を薬液とは呼ばない。

【0025】

次に、図4に示すように、溝4aの内部(側壁および底部)を含む半導体基板1の主面上に、例えば厚み10nm程度の絶縁膜4bを形成する。それから、半導体基板1の主面上(すなわち絶縁膜4b上)に、溝4a内を埋めるように、絶縁膜4cをCVD法などにより形成(堆積)する。

【0026】

絶縁膜4bは、酸化シリコン膜または酸窒化シリコン膜からなる。絶縁膜4bが酸窒化シリコン膜の場合には、絶縁膜4b形成工程以降の熱処理によって溝4aの側壁が酸化することによる体積膨張を防止でき、半導体基板1に働く圧縮応力を低減できる効果がある。

【0027】

絶縁膜4cは、HDP−CVD(High Density Plasma CVD:高密度プラズマCVD)法により成膜された酸化シリコン膜、またはO3−TEOS酸化膜などである。なお、O3−TEOS酸化膜とは、O3(オゾン)およびTEOS(Tetraethoxysilane:テトラエトキシシラン、Tetra Ethyl Ortho Silicateともいう)を原料ガス(ソースガス)として用いて熱CVD法により形成した酸化シリコン膜である。

【0028】

それから、半導体基板1を例えば1150℃程度で熱処理することにより、溝4aに埋め込んだ絶縁膜4cを焼き締める。焼き締め前の状態では、O3−TEOS酸化膜よりもHDP−CVD法により成膜された酸化シリコン膜の方が緻密である。このため、絶縁膜4cがO3−TEOS酸化膜の場合、焼き締めによる絶縁膜4cの収縮により、半導体基板1に働く圧縮応力を低減できる効果がある。一方、絶縁膜4cがHDP−CVD法により成膜された酸化シリコン膜の場合には、絶縁膜4cがO3−TEOS酸化膜の場合に比べて、焼き締め時の絶縁膜4cの収縮が少ないため、素子分離領域4によって半導体基板1に働く圧縮応力が大きくなる。

【0029】

次に、図5に示すように、絶縁膜4cをCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨して絶縁膜3を露出させ、熱リン酸などを用いたウエットエッチングにより絶縁膜3を除去した後、HFなどにより溝4aの外部の絶縁膜4cおよび絶縁膜2を除去し、溝4aの内部に絶縁膜4b、4cを残すことにより、素子分離領域(素子分離)4を形成する。

【0030】

このようにして、溝4a内に埋め込まれた絶縁膜4b、4cからなる素子分離領域4が形成される。本実施の形態の素子分離領域4は、半導体基板1に形成された素子分離用の溝4a内に埋め込まれた絶縁体(ここでは絶縁膜4b、4c)からなる。後述するnチャネル型MISFETQn(すなわちnチャネル型MISFETQnを構成するゲート絶縁膜7、ゲート電極8aおよびソース・ドレイン用のn−型半導体領域9aおよびn+型半導体領域9b)は、素子分離領域4で規定された(囲まれた)活性領域に形成される。また、後述するpチャネル型MISFETQp(すなわちpチャネル型MISFETQpを構成するゲート絶縁膜7、ゲート電極8bおよびソース・ドレイン用のp−型半導体領域10aおよびp+型半導体領域10b)も、素子分離領域4で規定された(囲まれた)活性領域に形成される。

【0031】

次に、図6に示すように、半導体基板1上にフォトリソグラフィ技術を用いてフォトレジスト膜R2を形成する。フォトレジスト膜R2は後述するnチャネル型MISFETQnを形成する領域(nチャネル型MISFET形成予定領域)の半導体基板1の主面を露出しており、後述するpチャネル型MISFETQpを形成する領域(pチャネル型MISFET形成予定領域)の半導体基板1の主面を覆っている。

【0032】

続いて、フォトレジスト膜R2をイオン注入阻止マスクとして、図6に矢印で示すようにnチャネル型MISFET形成予定領域の半導体基板1に例えばホウ素(B)などのp型の不純物をイオン注入(ドーズ)することなどによって半導体基板1の主面から所定の深さに渡ってp型ウエル5を形成する。このとき、フォトレジスト膜R2にもp型の不純物が打ち込まれる。

【0033】

次に、図7に示すように、フォトレジスト膜R2を電解硫酸を用いた薬液により除去し、半導体基板の主面を洗浄する。当該洗浄方法の詳細な工程については、後に図10および図11を用いて説明する。なお、フォトレジスト膜R2の除去工程では、アッシング(灰化)は行わないものとする。その後、図6を用いて説明した工程と同様にフォトレジスト膜を半導体基板1上に形成し、半導体基板1のpチャネル型MISFET形成予定領域の主面から所定の深さに渡ってn型ウエル6を形成する。n型ウエル6は、nチャネル型MISFET形成予定領域を覆う他のフォトレジスト膜(図示せず)をイオン注入阻止マスクとして、pチャネル型MISFET形成予定領域の半導体基板1に例えばリン(P)またはヒ素(As)などのn型の不純物をイオン注入することなどによって形成することができる。続いて、図6を用いて説明した工程と同様にフォトレジスト膜を除去する。

【0034】

なお、図6および図7を用いて説明したウエル形成工程ではp型ウエル5を形成した後にn型ウエル6を形成したが、p型ウエル5およびn型ウエル6を形成する順序は逆であってもよい。

【0035】

次に、図8に示すように、半導体基板1の表面(すなわちp型ウエル5およびn型ウエル6の表面)上にゲート絶縁膜7を形成する。ゲート絶縁膜7は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成することができる。

【0036】

その後、半導体基板1上(すなわちp型ウエル5およびn型ウエル6のゲート絶縁膜7上)に、ゲート電極形成用の導体膜として、多結晶シリコン膜のようなシリコン膜8を形成する。シリコン膜8のうちのnチャネル型MISFET形成予定領域(後述するゲート電極8aとなる領域)は、フォトレジスト膜(図示せず)をマスクとして用いてリン(P)またはヒ素(As)などのn型の不純物をイオン注入することなどにより、低抵抗のn型半導体膜(ドープトポリシリコン膜)とされている。また、シリコン膜8のうちのpチャネル型MISFET形成予定領域(後述するゲート電極8bとなる領域)は、他のフォトレジスト膜(図示せず)をマスクとして用いてホウ素(B)などのp型の不純物をイオン注入することなどにより、低抵抗のp型半導体膜(ドープトポリシリコン膜)とされている。また、シリコン膜8は、成膜時にはアモルファスシリコン膜であったものを、成膜後(イオン注入後)の熱処理により多結晶シリコン膜に変えることもできる。

【0037】

続いて、フォトリソグラフィ技術により、nチャネル型MISFET形成予定領域およびpチャネル型MISFET形成予定領域のそれぞれのシリコン膜8上にフォトレジスト膜R3を形成する。

【0038】

次に、図9に示すように、フォトレジスト膜R3をエッチングマスクとして、ドライエッチング法を用いてシリコン膜8およびゲート絶縁膜7をパターニングすることによりゲート電極8a、8bを形成した後、フォトレジスト膜R3を電解硫酸を用いた薬液により除去し、半導体基板の主面を洗浄する。当該洗浄方法の詳細な工程については、後に図10および図11を用いて説明する。なお、フォトレジスト膜R3の除去工程では、アッシング(灰化)は行わないものとする。

【0039】

nチャネル型MISFETのゲート電極となるゲート電極8aは、n型の不純物を導入した多結晶シリコン(n型半導体膜、ドープトポリシリコン膜)からなり、p型ウエル5上にゲート絶縁膜7を介して形成される。すなわち、ゲート電極8aは、p型ウエル5のゲート絶縁膜7上に形成される。また、pチャネル型MISFETのゲート電極となるゲート電極8bは、p型の不純物を導入した多結晶シリコン(p型半導体膜、ドープトポリシリコン膜)からなり、n型ウエル6上にゲート絶縁膜7を介して形成される。すなわち、ゲート電極8bは、n型ウエル6のゲート絶縁膜7上に形成される。ゲート電極8a、8bのゲート長は、必要に応じて変更できるが、例えば50nm程度とすることができる。

【0040】

上述したように、本実施の形態では図3、図7および図9を用いて説明した工程において電解硫酸を用いてフォトレジスト膜の除去を行っているが、フォトレジスト膜を除去・洗浄する別の方法としては、図21のフローのステップSP1およびSP2に示すように、まずアッシングによりフォトレジスト膜の大部分を除去した後にSPM洗浄を用いることが考えられる。図21は、比較例の洗浄工程を示すフロー(工程図)であり、本実施の形態で用いる洗浄工程を示すものではない。以下に、比較例としてSPM洗浄を用いてフォトレジスト膜を除去する方法について説明する。

【0041】

SPM洗浄を行う場合は、図21のステップSP1に示すように、まずアッシングによりフォトレジスト膜を除去する。アッシングとは、エッチングなどの工程の後、不要となったフォトレジスト膜をプラズマなどで反応させ、気相中で分解・除去するレジスト剥離のことである。また、アッシングを行う装置をアッシャー(レジスト剥離装置)と呼ぶ。アッシングは、オゾンやガス等を導入したアッシング室内で、紫外線等の光を照射してガスとフォトレジスト膜の化学反応を使ってレジスト剥離をする光励起アッシングと、ガスを高周波等でプラズマ化し、そのプラズマを利用してレジストを剥離するプラズマアッシングの二つに大別される。

【0042】

アッシングでは半導体基板上のフォトレジスト膜を完全に除去することは困難であり、半導体基板上にはフォトレジスト膜の残渣も残るため、アッシングの次にはSPM洗浄(図21のステップSP2)を行うことで、さらに半導体基板上のフォトレジスト膜または金属粒子を除去する必要がある。SPM洗浄は、例えばSPM洗浄槽内にある硫酸および過酸化水素水を含む薬液内に半導体基板を複数枚同時に浸して半導体基板の表面を洗浄する洗浄方法であり、これによりフォトレジスト膜のような有機物または金属粒子などを除去することができる。ただし、SPM洗浄で用いる薬液は十分なレジスト除去性能を有していない可能性が高いため、レジストの残渣などが半導体基板の表面に残るリスクを回避する必要がある。よって、SPM洗浄により半導体基板上に残った有機物などの微粒子(残渣)を除去するために、アンモニア、過酸化水素水および水を含む薬液を用いたAPM洗浄(図21のステップSP5)を行う。

【0043】

SPM洗浄が十分なレジスト除去性能を保持できない理由は、SPM洗浄に用いる薬液をSPM洗浄槽内からポンプを用いて吸い出し、フィルタを通過させてゴミなどを取り除いた後に前記SPM洗浄槽に戻して循環させることで、薬液を繰り返し洗浄に使用していることに起因する。この場合、洗浄を繰り返し行ううちに薬液内の硫酸濃度が低くなり、レジストなどを除去する過硫酸の濃度が低下する。これを防ぐため、循環する薬液には過酸化水素水(H2O2)を供給し続けなければならない。硫酸を含む薬液に過酸化水素水を加えることで、硫酸および過酸化水素水から過硫酸および水を生成することができ、薬液内の過硫酸濃度の低下を抑えることができる。

【0044】

しかし、硫酸を含む薬液に過酸化水素水を加えると水が生成されるため、薬液に過酸化水素水を加え続けることで薬液内の水の量が増加し、薬液のレジスト除去性能は最終的にSPM洗浄に用いることができなくなるまでに低下する。したがって、SPM洗浄の薬液のレジスト除去性能が限界(許容範囲)より低くなる前に、SPM洗浄槽およびその槽に接続された循環器を含むSPM洗浄装置内の全ての薬液を廃棄し、その後SPM洗浄を行う際には新たに硫酸および過酸化水素水を含む薬液を用意し、それをSPM洗浄装置内で循環させて洗浄を行うこととなる。

【0045】

上述したように、SPM洗浄では薬液に過酸化水素水を追加し続けなければならないため、過酸化水素水が多量に必要となり半導体装置の製造コストが高くなる。また、過酸化水素水を追加し続けても、水が発生して薬液の過硫酸濃度が低下することでレジスト除去性能を高い状態で維持することができないため、除去可能なレジストの量などが制限される。つまり、レジスト除去性能が一定ではなく使用により低下するため、洗浄用の薬液として使用できる範囲で最も低いレジスト除去性能により除去できるフォトレジスト膜の量またはフォトレジスト膜の種類でなければ洗浄対象として扱うことができない。

【0046】

つまり、例えば半導体基板上のフォトレジスト膜の膜厚が厚すぎたり、洗浄槽内で同時に洗浄する半導体ウエハの枚数が多すぎたりすると、半導体基板の表面のフォトレジスト膜を除去しきれない可能性が高くなる。

【0047】

また、フォトレジスト膜はより多くの不純物が導入(ドーズ)されるほど除去されにくくなる性質を有しているため、例えば1×1013個/cm2よりも多く不純物が導入されたフォトレジスト膜はSPM洗浄では除去できない問題が発生する場合がある。

【0048】

次に、SPM洗浄の後であってAPM洗浄を行う前に、SPM洗浄により半導体基板表面に残ったSPM洗浄の薬液(特に硫酸)および残渣の一部を洗い流すために水を用いた洗浄を行う必要がある。水を用いた洗浄では図21のステップSP3に示すQDR(Quick Dump Rinse)を行った後に、ステップSP4に示すOF(Over Flow Rinse)を行う。QDRとは、洗浄する対象である半導体ウエハを入れた槽に水または純水を満たし、洗浄対象に水をシャワーしながら一気に排水する薬液処理後のリンス(濯ぎ)方法である。また、OFは水を供給・排出し続けるリンス槽内の水の中に半導体ウエハを浸して洗浄する洗浄方法である。本願では、QDRおよびOFの工程を行うことを、純水リンス工程と呼ぶ。つまり、純水リンス工程はQDR工程およびOF工程を含んでいる。

【0049】

このように水を用いた洗浄(純水リンス工程)の後に、APM洗浄(図21のステップSP5)を行うことで、半導体基板上に残るフォトレジスト膜の一部などからなる微粒子(残渣)またはその他の有機物を除去する。APM洗浄はAPM洗浄槽内のアンモニア、過酸化水素水および水を含む薬液内に半導体ウエハを浸して洗浄を行う洗浄方法である。しかし、APM洗浄は、アルミニウム(Al)、鉄(Fe)のような金属不純物がAPM洗浄の薬液内に微量でも混入すると金属粒子が半導体基板の表面に多量に付着する問題を有しているため、それらを除去するためにAPM洗浄の後にHPM洗浄(図21のステップSP8)を行わなければならない。

【0050】

HPM洗浄の前にはAPM洗浄の薬液などを半導体基板の表面から除去するために、ステップSP3およびステップSP4と同様にQDR(ステップSP6)およびOF(ステップSP7)を行う。HPM洗浄はHPM洗浄槽内の塩酸、過酸化水素水および水を含む薬液内に半導体ウエハを浸して洗浄を行う洗浄方法であり、これを行うことで半導体基板上に残っていた金属粒子(例えばアルミニウムまたは鉄)を除去する。HPM洗浄を行った後は、半導体基板の表面からHPM洗浄の薬液を除去するためのQDR(ステップSP9)またはOF(ステップSP10)などが必要となる。

【0051】

次に、ステップSP10までの洗浄工程を終えた半導体基板を乾燥させる乾燥(ステップSP11)工程を行う。乾燥工程では、半導体ウエハを例えば機械的に固定し、または真空チャックなどを用いて固定した後、半導体ウエハを回転させることで乾燥させる方法が考えられる。また、他の乾燥方法として、IPA(Iso-Propyl Alcohol)乾燥法を行うことも考えられる。IPA乾燥法は、イソプロピルアルコールの液体に半導体ウエハを浸けた後、アルコールの揮発によって半導体基板の表面を乾燥させる乾燥方法である。

【0052】

以上説明したように、SPM洗浄を行った後にはステップSP3〜ステップSP11に示す洗浄工程および乾燥工程が必要となり、これらの工程を行わなければ、次の成膜工程などに移行することができない。このように多くの工程を要するのはSPM洗浄のレジスト除去性能が薬液内の水の増加により低下するためであり、SPM洗浄を行えば、上記の多くの洗浄工程を行うための時間、薬液、装置およびその装置を半導体装置の製造工場内に配置するスペースが必要となるため、半導体装置の製造コストが増加する問題がある。

【0053】

具体的には、製造工程が増え、半導体装置の製造に要する時間が増加すればスループットが低下し、半導体装置の製造コストも増加する。洗浄装置内にSPM洗浄部、APM洗浄部およびHPM洗浄部を有するような洗浄装置はAPM洗浄部およびHPM洗浄部を有していない洗浄装置に比べて非常に高価になる。また、半導体装置の製造現場において、露光装置、成膜装置または洗浄装置などを設置するクリーンルームはその面積に限りがあるものであり、その面積を有効に活用するためにはそれぞれの装置を集約したり、縮小化することが望ましいのに対し、APM洗浄部およびHPM洗浄部を有するような洗浄装置は大きさが大きくなるため、このような装置を用いればクリーンルーム内の空間を有効に使用することができなくなる。

【0054】

これに対し、本実施の形態の半導体装置の製造工程においては、フォトレジスト膜の除去の際にアッシングを行わず、電解硫酸を用いてフォトレジスト膜を除去し、薬液に過酸化水素水を補充する必要がない基板の洗浄方法を用いる。以下に、図3、図7および図9を用いて説明した工程において行ったフォトレジスト膜の除去工程の詳細を、図10および図11を用いて説明する。図10は、本実施の形態の半導体装置の製造工程における洗浄工程を示すフロー(工程図)である。図11は、図10に示す洗浄工程で用いる洗浄装置を表わした模式図である。

【0055】

図10のステップS1に示すように、半導体基板の上面に形成されたフォトレジスト膜を除去する際には、まず電解硫酸を含む薬液を入れた電解硫酸槽に複数の半導体ウエハを浸す。これにより、半導体基板の表面に付着していたフォトレジスト膜または金属粒子は過硫酸または硫酸により除去される。なお、電解硫酸とは、硫酸を含む薬液(硫酸溶液)に、後述する過硫酸生成装置内の電極に電圧を印可することで生成した過硫酸を含む薬液(溶液)をいう。フォトレジスト膜の除去には過硫酸を用いることが重要であるため、前述した比較例では硫酸を含む薬液に過酸化水素水を加えることで過硫酸を生成していたが、本実施の形態の半導体装置の製造方法においては、電極を用いて硫酸を含む溶液に電圧を印可することで過硫酸を生成している。

【0056】

ここで、図11に本実施の形態の半導体装置の製造工程においてフォトレジスト膜などの除去に用いる洗浄装置の模式図を示す。図11では、薬液および水の循環経路ならびにそれらの流れる方向を矢印で示している。なお、薬液(硫酸溶液)の流れる経路は太い実線の矢印で示し、薬液の冷却に用いる冷却器内に供給される水の流れる経路は細い破線で示し、気体(ガス)の流れる経路は細い一点鎖線で示している。この洗浄装置RDは洗浄機Raおよび電解硫酸生成装置Rbを含んでいる。なお、本実施の形態では一体の洗浄装置RDが洗浄機Raおよび電解硫酸生成装置Rbを有している例を説明するが、洗浄機Raおよび電解硫酸生成装置Rbは別個の装置であってもよい。

【0057】

図11に示すように、洗浄装置RDを構成する洗浄機Raは、内部に電解硫酸槽60を有する。電解硫酸槽60は電解硫酸生成装置Rbから送り込まれる過硫酸などを含む硫酸溶液を用いて半導体ウエハ61を洗浄する洗浄槽であり、一度に複数の半導体ウエハ61を洗浄することができる所謂バッチ式の洗浄槽である。電解硫酸槽60内には前記硫酸溶液を加熱するヒータ62が設けられており、ヒータ62により電解硫酸槽60内の硫酸溶液は110℃〜150℃に加熱される。洗浄工程(レジスト除去工程)では、半導体ウエハ61は例えば50枚程度を並べて電解硫酸槽60内に一度に入れ、それらの表面の洗浄(レジスト除去)を行うことができる。なお、本願では過硫酸を含む硫酸溶液を電解硫酸と呼ぶが、図11に示す洗浄装置RD内を流れる硫酸溶液にも過硫酸は含まれているものとする。

【0058】

また、電解硫酸槽60内の硫酸溶液は主に過硫酸、硫酸および水により構成されており、この場合、電解硫酸槽60内の硫酸溶液内の過硫酸を含む硫酸濃度は80〜90wt%(重量パーセント)の濃度を有しているものとする。

【0059】

また、洗浄機Ra内には、電解硫酸槽60内の硫酸溶液がポンプ63を用いて吸い出され、配管を通じて再び電解硫酸槽60内に戻されるような循環経路が形成されている。前述したヒータ62は電解硫酸槽60内に配置せずに、前記循環経路を通過する硫酸溶液を加熱するように前記循環経路を構成する配管を囲むように配置してもよい。その場合は、例えば前記循環経路の途中に硫酸溶液がガラス管内を通る箇所を設け、そのガラス管の周りにランプによって硫酸溶液を加熱するヒータ62を設けることが考えられる。

【0060】

前記循環経路の途中には硫酸溶液を取出して電解硫酸生成装置Rbに送り込む配管と、電解硫酸生成装置Rbから前記循環経路に硫酸溶液を送り込む配管とが設けられている。電解硫酸生成装置Rbは内部に冷却器64、貯留槽65、過硫酸生成装置66、気液分離器67、ポンプ68〜70およびフィルタ71を有しており、洗浄機Ra内の循環経路から取り込まれた硫酸溶液はまず冷却器64により冷却された後、貯留槽65に送られる。冷却器64は例えば水を用いた水冷装置であり、冷却器64内の水はポンプ68を用いて冷却器64の中と外との間で循環され、その循環経路では冷却水の排出および供給が行われる。

【0061】

貯留槽65内に送られた硫酸溶液の一部はポンプ69により過硫酸生成装置66に送られ、その後気液分離器67に送られた後、再び貯留槽65に戻される。この経路では、硫酸溶液はまず過硫酸生成装置66において電気分解して過硫酸を生成し、硫酸溶液内の過硫酸の濃度を高める。ここで生成される過硫酸は、ペルオキソ二硫酸またはペルオキソ一硫酸の少なくとも一方を含むものである。このとき、過硫酸生成装置66での電気分解工程では硫酸溶液に気泡(ガス)が発生するが、この気泡は気液分離器67において硫酸溶液と分離される。

【0062】

過硫酸生成装置66は、フッ素樹脂などからなる配管内に陰極および陽極からなる電極対を有しており、それらの電極間に電圧印加し、硫酸溶液を介して50Aの電流を流すことにより、硫酸溶液内に過硫酸を生成する。ここでは電極間を流れる電流を50Aの直流電流で固定し、電極間の電圧を約100Vで可変させて電気分解を行う。過硫酸生成装置66内の電極には、不純物が導入されたダイヤモンド電極に銅板を組み合わせたものを使用する。過硫酸生成装置66により電圧を印可された硫酸と水とを含む硫酸溶液内には過硫酸と気泡とが生成される。

【0063】

気液分離器67内には、気泡を硫酸溶液から分離するために不活性ガスが供給されており、前記気泡(ガス)は前記不活性ガスと共に電解硫酸生成装置Rbの外部に排気される。ここでは、不活性ガスとして、図11に示すように例えば窒素(N2)を用いる。

【0064】

過硫酸生成装置66により過硫酸濃度が上昇した硫酸溶液は主に過硫酸、硫酸および水により構成されており、硫酸溶液内の過硫酸を含む硫酸の濃度は85wt%以上の濃度を有しているものとする。硫酸溶液を構成する前記水は、特に純度が高い純水であることが好ましい。ただし、硫酸溶液内には水を混合していなくてもよく、その場合、過硫酸生成装置66を通過した後の硫酸溶液内の過硫酸を含む硫酸の濃度は90wt%以上であるものとする。

【0065】

なお、過硫酸生成装置66はここでは対向する電極対を有するものとするが、この電極間に隔膜を設けて、陰極と陽極とで生成されるそれぞれの物質を分離して利用するような構造を有していても構わない。

【0066】

このように過硫酸生成装置66および気液分離器67を通して過硫酸濃度を高めた硫酸溶液を貯留槽65に戻すことで、電解硫酸槽60におけるレジスト除去および洗浄で消費された過硫酸を補うことができる。

【0067】

貯留槽65内の硫酸溶液の一部はポンプ70により洗浄機Ra内の循環経路にフィルタ71を通じて送られ、再び電解硫酸槽60内でレジストの除去および洗浄に用いられる。フィルタ71では、硫酸溶液内の微粒子などの不純物を取り除く。

【0068】

以上に述べたように、洗浄装置RD内には、洗浄機Ra内で循環し、電解硫酸槽60から硫酸溶液を取り出して再び電解硫酸槽60に戻す第1循環経路と、電解硫酸生成装置Rb内で循環し、貯留槽65内の硫酸溶液を取り出して過硫酸生成装置66および気液分離器67を通して過硫酸濃度を高めた後に貯留槽65に戻す第2循環経路とがある。また、洗浄機Raおよび電解硫酸生成装置Rb間で循環し、第1循環経路から取出した硫酸溶液を貯留槽65に溜めた後に第1循環経路に再び戻す第3循環経路がある。

【0069】

硫酸溶液内の過硫酸は電解硫酸槽60でレジスト除去および洗浄のために消費されるが、上記のように過硫酸生成装置66で連続的に生成された過硫酸を貯留槽65を介して電解硫酸槽60に供給することで補われる。このため、硫酸溶液に過酸化水素水を加えなくても過硫酸濃度の低下を防ぐことができるため、過酸化水素水を加えることに起因して硫酸溶液内に水が生成されることがなく、硫酸溶液内の水が増えることを防ぎ、硫酸溶液のレジスト除去性能が低下することを防ぐことができる。

【0070】

つまり、前述したSPM洗浄とは違い、レジスト除去性能が低下することなく、高いレジスト除去性能を維持することができるため、電解硫酸槽60で行うレジスト除去では有機物などの有機物または金属などからなる微粒子または残渣が半導体基板の表面に残ることを防ぐことができる。したがって、電解硫酸を用いてフォトレジスト膜の除去および半導体基板の洗浄を行う本実施の形態では、SPM洗浄を行った後に必要であったAPM洗浄およびHPM洗浄を行う必要がない。SPM洗浄を行う洗浄機内にはSPM洗浄槽のみならずAPM洗浄部およびHPM洗浄部が設けられていることが考えられるが、本実施の形態の基板の洗浄方法ではAPM洗浄およびHPM洗浄を行わないため、洗浄機Ra内には電解硫酸槽60の他に薬液を用いる洗浄装置(洗浄部)を必要としない。よって、洗浄装置RDを小さくすることが可能であるため、洗浄装置が高価なものになることを防ぎ、洗浄装置RDの大きさを小さくすることができる。これにより、例えば洗浄装置RDをクリーンルーム内などに配置した場合、SPM洗浄部、APM洗浄部およびHPM洗浄部を有する洗浄装置を配置する場合に比べてクリーンルーム内の空間をより有効に利用することができる。

【0071】

また、SPM洗浄、APM洗浄またはHPM洗浄などで洗浄を行う場合、アッシングをせずに薬液および水での洗浄工程のみでフォトレジスト膜を除去することは困難である。したがって、アッシングを行う場合の洗浄工程の手順としては、以下の(1)〜(6)のそれぞれに示す工程順に行う方法が考えられる。

(1)アッシング、SOM洗浄、純水リンス洗浄、APM洗浄、純水リンス洗浄、HPM洗浄、純水リンス洗浄、乾燥。

(2)アッシング、SPM洗浄、純水リンス洗浄、APM洗浄、純水リンス洗浄、HPM洗浄、純水リンス洗浄、乾燥。

(3)アッシング、SPM洗浄、純水リンス洗浄、APM洗浄、純水リンス洗浄、乾燥。

(4)アッシング、SOM洗浄、純水リンス洗浄、乾燥。

(5)アッシング、SPM洗浄、純水リンス洗浄、乾燥。

(6)アッシング、APM洗浄、純水リンス洗浄、HPM洗浄、純水リンス洗浄、乾燥。

【0072】

ここで、例えば上記の手順(1)は、アッシングの後に順にSOM洗浄、純水リンス洗浄(純水リンス工程)、APM洗浄、純水リンス洗浄(純水リンス工程)、HPM洗浄、純水リンス洗浄(純水リンス工程)および乾燥を行うことを示している。なお、SOM(sulfuric-ozone mix)洗浄は、硫酸槽にオゾン(O3)を吹き込んでフォトレジスト膜などを除去し、対象物を洗浄を行う洗浄方法であり、SPM洗浄よりは洗浄能力が劣る洗浄方法である。

【0073】

前述したように、APM洗浄およびHPM洗浄はSPM洗浄で除去できなかった微粒子、または洗浄対象物に付着している金属粒子などを除去するために行うものであるため、SPM洗浄、SOM洗浄を行わない上記手順(6)と、APM洗浄またはHPM洗浄を行わない上記手順(3)〜(5)とは、例えば上記手順(1)、(2)に比べて洗浄性能が低く、使用できる条件が限られる。

【0074】

アッシングを行わず、SPM洗浄によりフォトレジスト膜を除去することも考えられるが、前述したようにSPM洗浄では除去できるフォトレジスト膜の量(膜厚)が大きい場合はレジスト除去が困難になるし、1×1013個/cm2よりも多く不純物が導入されたフォトレジスト膜はSPM洗浄では除去できないという制限がある。

【0075】

これに対し、本実施の形態で用いる洗浄装置RDは高いレジスト除去性能を有していることから、アッシングを行わずに半導体基板表面のフォトレジスト膜を取り除くことができるため、半導体装置の製造工程を図10に示すように簡略化し、スループットを向上させることで、半導体装置の製造コストを低減することができる。本実施の形態のレジスト除去工程では、電解硫酸を用いた洗浄が高いレジスト除去性能を有していることにより、イオン注入工程で打ち込み防止のマスクとして用いられたフォトレジスト膜であって、不純物が5×1014個/cm2注入され、SPM洗浄法では剥離が困難なフォトレジスト膜でも除去することができる。

【0076】

すなわち、不純物が1×1013個/cm2よりも多く注入されたフォトレジスト膜を除去することが困難なSPM洗浄法に比べ、本実施の形態の半導体装置の製造方法における洗浄工程では、より多くの不純物が導入され、除去が困難となったフォトレジスト膜であっても除去することができる。また、このようにレジスト除去性能が向上することで、膜厚が厚いためにSPM洗浄では除去が困難なフォトレジスト膜であっても除去することができる。

【0077】

この場合、アッシング工程を省略することが可能となるため、本実施の形態の基板の洗浄工程では、電解硫酸洗浄、純水リンス洗浄、乾燥という少ない工程で基板の洗浄を行うことができる。つまり、アッシング工程を省くことで、上記手順(1)〜(6)のいずれの洗浄方法よりも洗浄工程を少なくし、かつ洗浄性能を向上させることができる。

【0078】

次に、電解硫酸洗浄(図10のステップS1)を行った後は、半導体基板の表面に残る電解硫酸を取り除くため、QDR工程(ステップS2)、70℃OF工程(ステップS3)および常温OF工程(ステップS4)を順に行い、続いて半導体基板を乾燥させる乾燥工程(ステップS5)を行う。ステップS3の70℃OF工程では、約70℃に温められた純水を用いて半導体基板を洗浄を行い、ステップS4の常温OF工程では、約25℃の純水を用いて半導体基板を洗浄を行う。本実施の形態では、図10に示すステップS2〜S3に示すQDR工程、70℃OF工程および常温OF工程をまとめて純水リンス工程と呼ぶ。

【0079】

図11に示す洗浄機Ra内には半導体基板を洗浄するためのQDR(ステップS2)、70℃OF工程(ステップS3)および常温OF工程(ステップS4)を行う装置が設けられていてもよく、半導体基板を乾燥させるための装置が設けられていてもよい。これは、SPM洗浄を行う洗浄装置であっても同様である。本実施の形態では、図11に示していないが、洗浄機Ra内にはQDR洗浄部、OF洗浄部および乾燥装置が配置されているものとする。したがって、洗浄装置RD内に搬送され、電解硫酸槽60でフォトレジスト膜などの有機物または金属粒子などを除去された半導体ウエハ61は、洗浄機Ra内のQDR洗浄部で純水洗浄された後にOF洗浄部で純水洗浄され、続いて乾燥装置で乾燥工程を経た後に洗浄装置RDから取り出され、次の成膜工程などに用いられる装置に搬送されるものとする。つまり、電解硫酸による洗浄、純水洗浄および乾燥は一台の装置内で処理される。

【0080】

なお、実際に洗浄装置RDを使用する場合には、電解硫酸槽60内に半導体ウエハ61を入れていない状態で硫酸溶液を上記第1〜第3循環経路を循環させ、電解硫酸槽60内の硫酸溶液の温度をヒータ62により例えば140℃程度に加熱し、冷却器64での硫酸溶液の冷却、過硫酸生成装置66での過硫酸の生成、および気液分離器67での気泡分離などを一定時間行う。この洗浄装置RD内のでの一連の動作により硫酸溶液の温度、濃度分布などが定常状態となった後に、レジスト膜が付いた半導体ウエハ61を電解硫酸槽60内に浸し、洗浄を開始する。

【0081】

本実施の形態の基板の洗浄工程は、図10に示すように、比較例として図21に示した洗浄工程に比べて工程数が少ないため、半導体装置の製造工程が簡略化されている。これは、前述したように電解硫酸を用いて半導体基板の洗浄を行っても薬液のレジスト除去性能が低下しないため、薬液のレジスト除去性能が低下するSPM洗浄の後に必要であったAPM洗浄およびHPM洗浄が不要だからである。また本実施の形態の場合はフォトレジスト膜除去のためのアッシングも不要であり、図21に示す比較例の洗浄工程を行った場合に比べ、本実施の形態の洗浄工程を行えば洗浄工程にかかる時間を半分程度に短縮することができる。

【0082】

本発明者らは、電解硫酸を用いた洗浄を繰り返し行った場合、過酸化水素水を補充しなくてもレジスト除去性能が低下しないことを実証するため、洗浄装置の連続稼働によるレジスト除去性能の変化を調べる実験を行った。この実験は、直径6インチの半導体ウエハの主面の全面に、厚さ1.7μmのフォトレジスト膜を塗布し、このフォトレジスト膜の表面にP型の不純物であるホウ素(B)を100keVのエネルギーで5×1014個/cm2導入した半導体ウエハを一度に50枚バッチ処理(洗浄)する事を繰り返し行うものであり、洗浄装置RDを用いたこの洗浄処理を29日間連続稼働させて行った。この期間中に洗浄処理した半導体ウエハは合計1775枚である。また、この期間中に硫酸溶液の補充または交換は行っておらず、硫酸溶液に対する過酸化水素水の供給も行っていない。実験では、最初に洗浄処理を行った半導体ウエハと、29日の連続稼働の最後に洗浄処理した半導体ウエハのそれぞれの表面に残留する直径0.3μm以上の微粒子数を数えることでレジスト除去性能の変化を比較した。

【0083】

実験の結果、実験開始時に洗浄装置RDに硫酸溶液を投入し、装置を稼働させて最初に洗浄を行った半導体ウエハと、29日の連続稼働の最後に洗浄処理した半導体ウエハでは、洗浄処理後に半導体ウエハの表面に残る微粒子の数はほぼ同一といえる程度であり、具体的には一枚の半導体ウエハの主面には10〜30個の微粒子が残存しているのみであった。このことから、電解硫酸を用いた洗浄では、過酸化水素水または硫酸を補充しなくても高いレジスト除去性能を維持することが可能であり、また、過酸化水素水を補充することに起因する水の発生もないため、硫酸溶液が水によって薄まることもなく、レジスト除去性能が低下することを防ぐことが可能であることが分かる。

【0084】

さらに、電解硫酸を用いた洗浄ではフォトレジスト膜のような有機物だけでなく、半導体基板の主面に付着している金属粒子を除去することが可能である。本発明者らが行った実験では、アッシング装置(アッシャー)を用いたアッシングによりレジスト除去を行った場合、半導体基板の表面に金属の残渣が付着しやすいことを利用し、アッシング工程の直後の半導体基板と、アッシング工程の後に電解硫酸を用いた洗浄を行った半導体基板のそれぞれの表面に付着している金属の単位面積当たりの原子数(atoms/cm2)を比べることで、電解硫酸を用いた洗浄による金属除去性能を調べた。

【0085】

図12に示す表は、アッシング工程の後に洗浄を行っていない、つまり電解硫酸による異物の除去工程の前の半導体基板の表面に残存する各金属の原子数を測定した結果を上段に示し、本実施の形態の半導体装置の製造方法で使用する電解硫酸を用いた異物の除去工程(洗浄)をアッシング工程の後に行った場合の半導体基板の表面に残存する各金属の原子数を測定した結果を下段に示すものである。つまり、図12は本実施の形態で用いる電解硫酸の金属除去性能を示している。なお、表の原子数の数値の右側に下向きの矢印が記載されているデータは、実際に半導体基板の表面に残存する原子数がその数値以下であることを示し、計測が困難な程度にまで金属の原子数が少なくなっていることを表わしている。

【0086】

図12に示すように、アッシングを行った半導体基板の表面には特にAlおよびFeが付着しやすく、他の金属に比べて多数の原子が付着していることが分かる。これに対し、電解硫酸による洗浄を行った後の半導体基板の表面におけるAlおよびFeの原子数は大幅に減少している。このように、硫酸が元々有する金属除去性能は電解硫酸も有しているため、電解硫酸を用いた洗浄では半導体基板の主面に形成された金属粒子などを除去することが可能である。

【0087】

次に、図13に示すように、p型ウエル5のゲート電極8aの両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)n−型半導体領域9aを形成し、n型ウエル6のゲート電極8bの両側の領域にホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)p−型半導体領域10aを形成する。n−型半導体領域9aおよびp−型半導体領域10aの深さ(接合深さ)は、例えば30nm程度とすることができる。

【0088】

その後、ゲート電極8a、8bの側壁上に、絶縁膜として、例えば酸化シリコンまたは窒化シリコンあるいはそれら絶縁膜の積層膜などからなる側壁スペーサまたはサイドウォール(側壁絶縁膜)11を形成する。サイドウォール11は、例えば、半導体基板1上に酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜を堆積し、この酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜をRIE(Reactive Ion Etching)法などにより異方性エッチングすることによって形成することができる。

【0089】

サイドウォール11の形成後、(一対の)n+型半導体領域9b(ソース、ドレイン領域)を、例えば、p型ウエル5のゲート電極8aおよびサイドウォール11の両側の領域にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより形成する。例えば、リン(P)を5×1015/cm2程度、ヒ素(As)を4×1015/cm2程度注入して形成する。また、(一対の)p+型半導体領域10b(ソース、ドレイン領域)を、例えば、n型ウエル6のゲート電極8bおよびサイドウォール11の両側の領域にホウ素(B)などのp型の不純物をイオン注入することにより形成する。例えば、ホウ素(B)を4×1015/cm2程度注入して形成する。n+型半導体領域9bを先に形成しても、あるいはp+型半導体領域10bを先に形成しても良い。イオン注入後、導入した不純物の活性化のためのアニール処理を、例えば1050℃程度で5秒程度の熱処理(スパイクアニール処理)にて行うこともできる。n+型半導体領域9bおよびp+型半導体領域10bの深さ(接合深さ)は、例えば80nm程度とすることができる。

【0090】

n+型半導体領域9bは、n−型半導体領域9aよりも不純物濃度が高く、p+型半導体領域10bは、p−型半導体領域10aよりも不純物濃度が高い。これにより、nチャネル型MISFETのソースまたはドレインとして機能するn型の半導体領域(不純物拡散層)が、n+型半導体領域(不純物拡散層)9bおよびn−型半導体領域9aにより形成され、pチャネル型MISFETのソースまたはドレインとして機能するp型の半導体領域(不純物拡散層)が、p+型半導体領域(不純物拡散層)10bおよびp−型半導体領域10aにより形成される。従って、nチャネル型MISFETおよびpチャネル型MISFETのソース・ドレイン領域は、LDD(Lightly doped Drain)構造を有している。n−型半導体領域9aは、ゲート電極8aに対して自己整合的に形成され、n+型半導体領域9bは、ゲート電極8aの側壁上に形成されたサイドウォール11に対して自己整合的に形成される。p−型半導体領域10aは、ゲート電極8bに対して自己整合的に形成され、p+型半導体領域10bは、ゲート電極8bの側壁上に形成されたサイドウォール11に対して自己整合的に形成される。

【0091】

このようにして、p型ウエル5に、電界効果トランジスタとしてnチャネル型MISFETQnが形成される。また、n型ウエル6に、電界効果トランジスタとしてpチャネル型MISFETQpが形成される。これにより、図13の構造が得られる。nチャネル型MISFETQnは、nチャネル型の電界効果トランジスタとみなすことができ、pチャネル型MISFETQpは、pチャネル型の電界効果トランジスタとみなすことができる。また、n+型半導体領域9bは、nチャネル型MISFETQnのソースまたはドレイン用の半導体領域とみなすことができ、p+型半導体領域10bは、pチャネル型MISFETQpのソースまたはドレイン用の半導体領域とみなすことができる。

【0092】

次に、サリサイド(Salicide:Self Aligned Silicide)技術により、nチャネル型MISFETQnのゲート電極8aおよびソース・ドレイン領域(ここではn+型半導体領域9b)の表面と、pチャネル型MISFETQpのゲート電極8bおよびソース・ドレイン領域(ここではp+型半導体領域10b)の表面とに、低抵抗の金属シリサイド層(後述の金属シリサイド層41に対応)を形成する。本実施の形態におけるサリサイドプロセスは部分反応方式のサリサイドプロセスを用い、以下に、金属シリサイド層の形成工程について説明する。

【0093】

上記のようにして図13の構造が得られた後、図14に示すように、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面を露出した状態で、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10b上を含む半導体基板1の主面(全面)上に金属膜12を、例えばスパッタリング法を用いて形成(堆積)する。すなわち、n+型半導体領域9bおよびp+型半導体領域10b上を含む半導体基板1上に、ゲート電極8a、8bを覆うように、金属膜12が形成される。金属膜12は、例えばNi(ニッケル)−Pt(白金)合金膜(NiとPtの合金膜)からなり、その厚さ(堆積膜厚)は、例えば15〜40nm程度とすることができる。

【0094】

次に、図15に示すように、半導体基板1に第1の熱処理(1stアニール処理)を施す。ここで、第1の熱処理は、250℃〜300℃で行うことが好ましい。第1の熱処理により、ゲート電極8a、8bを構成する多結晶シリコン膜と金属膜12、およびn+型半導体領域9bおよびp+型半導体領域10bを構成する単結晶シリコンと金属膜12を選択的に反応させて、金属・半導体反応層である金属シリサイド層41を形成する。このとき、金属膜12内のNi−Pt合金膜は、半導体基板1(ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部)に接する底面側から反対側の上面方向に向かって5〜7nmの範囲のNi−Pt合金がゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部と反応する。

【0095】

すなわち、図14に示す工程において半導体基板1上に15〜40nmの厚さで形成された金属膜12が、第1の熱処理において、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部において反応して図15に示す金属シリサイド層41となるのは、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部の金属膜12の全膜厚の内の一部である。このため、図15に示すように、金属シリサイド層41が形成された半導体基板1上の金属膜12は、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの各上部において、他の領域の金属膜12の膜厚に比べて膜厚が薄くなっている。このように、金属膜12の膜厚の一部のみを必要量だけ反応させて金属シリサイド層41を形成するサイリサイドプロセスを、ここでは部分反応方式のサリサイドプロセスと呼ぶ。

【0096】

次に、図16に示すように、未反応の金属膜12(すなわちゲート電極8a、8b、n+型半導体領域9bまたはp+型半導体領域10bと反応しなかった金属膜12)とを除去する。この際、ゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面上に金属シリサイド層41を残存させる。

【0097】

その後、半導体基板1に第2の熱処理(2ndアニール処理)を施す。第2の熱処理は、上記第1の熱処理の熱処理温度とほぼ同程度か、もしくはそれよりも高い熱処理温度で行う。第2の熱処理を行うことで、金属シリサイド層41は低抵抗のNiSiにより構成される領域となる。

【0098】

次に、図17に示すように、半導体基板1の主面上に絶縁膜42を形成する。すなわち、ゲート電極8a、8bを覆うように、金属シリサイド層41上を含む半導体基板1上に絶縁膜42を形成する。絶縁膜42は例えば窒化シリコン膜からなり、成膜温度(基板温度)450℃程度のプラズマCVD法などにより形成することができる。それから、絶縁膜42上に絶縁膜42よりも厚い絶縁膜43を形成する。絶縁膜43は例えば酸化シリコン膜などからなり、TEOSを用いて成膜温度450℃程度のプラズマCVD法などにより形成することができる。これにより、絶縁膜42、43からなる層間絶縁膜が形成される。その後、絶縁膜43の表面をCMP法により研磨するなどして、絶縁膜43の上面を平坦化する。下地段差に起因して絶縁膜42の表面に凹凸形状が形成されていても、絶縁膜43の表面をCMP法により研磨することにより、その表面が平坦化された層間絶縁膜を得ることができる。

【0099】

次に、図18に示すように、絶縁膜43上に形成したフォトレジスト膜(図示せず)をエッチングマスクとして用いて、絶縁膜43、42をドライエッチングすることにより、絶縁膜42、43にコンタクトホール(貫通孔、孔)44を形成する。この際、まず絶縁膜42に比較して絶縁膜43がエッチングされやすい条件で絶縁膜43のドライエッチングを行い、絶縁膜42をエッチングストッパ膜として機能させることで、絶縁膜43にコンタクトホール44を形成してから、絶縁膜43に比較して絶縁膜42がエッチングされやすい条件でコンタクトホール44の底部の絶縁膜42をドライエッチングして除去する。コンタクトホール44の底部では、半導体基板1の主面の一部、例えばn+型半導体領域9bおよびp+型半導体領域10bの表面上の金属シリサイド層41の一部や、ゲート電極8a、8bの表面上の金属シリサイド層41の一部などが露出される。その後、前記フォトレジスト膜(図示せず)はレジスト除去方法により除去する。

【0100】

続いて、コンタクトホール44内に、タングステン(W)などからなるプラグ(接続用導体部、埋め込みプラグ、埋め込み導体部)45を形成する。プラグ45を形成するには、例えば、コンタクトホール44の内部(底部および側壁上)を含む絶縁膜43上に、成膜温度(基板温度)450℃程度のプラズマCVD法によりバリア導体膜45a(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、タングステン膜などからなる主導体膜45bをCVD法などによってバリア導体膜45a上にコンタクトホール44を埋めるように形成し、絶縁膜43上の不要な主導体膜45bおよびバリア導体膜45aをCMP法またはエッチバック法などによって除去することにより、プラグ45を形成することができる。ゲート電極8a、8b、n+型半導体領域9bまたはp+型半導体領域10b上に形成されたプラグ45は、その底部でゲート電極8a、8b、n+型半導体領域9bまたはp+型半導体領域10bの表面上の金属シリサイド層41と接して、電気的に接続される。

【0101】

次に、図19に示すように、プラグ45が埋め込まれた絶縁膜43上に、ストッパ絶縁膜51および配線形成用の絶縁膜52を順次形成する。ストッパ絶縁膜51は絶縁膜52への溝加工の際にエッチングストッパとなる膜であり、絶縁膜52に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜51は、例えばプラズマCVD法により形成される窒化シリコン膜とし、絶縁膜52は、例えばプラズマCVD法により形成される酸化シリコン膜とすることができる。なお、ストッパ絶縁膜51と絶縁膜52には次に説明する第1層目の配線が形成される。

【0102】

続いて、シングルダマシン法により第1層目の配線を形成する。まず、フォトレジスト膜(図示せず)をマスクとしたドライエッチングによって絶縁膜52およびストッパ絶縁膜51の所定の領域に配線溝53を形成し、前記フォトレジスト膜を除去した後、半導体基板1の主面上(すなわち配線溝の底部および側壁上を含む絶縁膜52上)にバリア導体膜(バリアメタル膜)54を形成する。その後、前記フォトレジスト膜はレジスト除去方法により除去する。バリア導体膜54は、例えば窒化チタン膜、タンタル膜または窒化タンタル膜などを用いることができる。

【0103】

続いて、CVD法またはスパッタリング法などによりバリア導体膜54上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成する。銅めっき膜により配線溝53の内部を埋め込む。それから、配線溝53以外の領域の銅めっき膜、シード層およびバリア導体膜54をCMP法により除去して、銅を主導電材料とする第1層目の配線55を形成する。配線55は、プラグ45を介してnチャネル型MISFETQnおよびpチャネル型MISFETQpのソースまたはドレイン用のn+型半導体領域9bおよびp+型半導体領域10bやゲート電極8a、8bなどと電気的に接続されている。その後、デュアルダマシン法により第2層目の配線を形成するが、ここでは図示およびその説明は省略する。以上により、本実施の形態のCMISFETを有する半導体装置が完成する。

【0104】

本実施の形態の半導体装置の製造方法では、基板の洗浄方法として電解硫酸を用いることで半導体基板の表面のフォトレジスト膜などの有機物からなる微粒子または残渣を除去し、さらに金属粒子を除去することができる。この場合、SPM洗浄法のように、薬液(硫酸溶液)に過酸化水素水を補充し続ける必要もなく、また、硫酸溶液のレジスト除去性能も低下しないため、アッシング工程を省略することも可能である。よって、半導体装置の製造工程を簡略化し、スループットを向上させて半導体装置の製造コストを低減することが可能である。

【0105】

本実施の形態の半導体装置の製造工程では、例えば図3、図7および図9において説明したフォトレジスト膜の除去において、電解硫酸を用いた上記除去・洗浄方法を用いることで、比較例として図21を用いて説明したSPM洗浄法を用いる除去・洗浄方法に比べて半導体装置の製造工程を簡略化することを可能としている。

【0106】

また、電解硫酸を用いる洗浄装置内にはAPM洗浄部およびHPM洗浄部が不要であるため、SPM洗浄を行う洗浄装置に比べ、本実施の形態では洗浄装置を小さくすることが可能である。これにより、APM洗浄部およびHPM洗浄部を有する洗浄装置よりも価格が低い洗浄装置を用いることができ、また、小さい洗浄装置を用いることでクリーンルーム内の空間を有効に使用することができるため、設備投資を低減することで半導体装置の製造コストを低減することができる。

【0107】

(実施の形態2)

前記実施の形態では、図10に示すステップS2〜S4において純水リンス工程を行っているが、本実施の形態では、図20に示すように、ステップS3aの70℃OF工程において洗浄用の水(例えば純水)に超音波を印加する洗浄方法、または、ステップS4aの常温OF工程において洗浄用の水に電解イオン水を供給する方法を用いる。

【0108】

具体的には、図20に示すステップS3aの70℃OF洗浄工程では、純水リンス槽内の洗浄用水に1MHz程度の周波数の超音波を印加することにより、電解硫酸洗浄(ステップS1)およびQDR工程(ステップS2)で除去できなかった半導体基板の表面の微粒子を物理的に分離し、取り除くことができる。これにより、70℃OF洗浄の洗浄性能を向上させることができる。

【0109】

また、図20に示すステップS4aの常温OF洗浄工程では、洗浄用水に電気分解により生成したイオン水(還元水)を供給した混合液を洗浄に用いる。この洗浄工程では、半導体基板とその表面の微粒子が共にマイナスに帯電するため、互いの反発力により微粒子を基板表面から分離させて除去することができる。これにより、常温OF洗浄の洗浄性能を向上させることができる。

【0110】

上記の超音波印加および電解イオン水供給はいずれか一方のみを純水リンス工程に適用してもよいし、両方を適用してもよい。これにより、純水洗浄性能を高め、より信頼性の高い半導体装置を製造することができる。

【0111】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0112】

例えば、前記実施の形態1、2では、半導体基板上に半導体素子を形成する場合の洗浄方法について説明したが、本発明を適用する技術はこれに限らず、例えば半導体基板ではないガラス基板、サファイア基板などを用いた基板の表面に残存または付着した有機物の除去などに適用することもできる。

【0113】

また、過硫酸および硫酸を含む硫酸溶液はフォトレジスト膜以外の有機物または金属粒子なども除去することが可能であるため、除去・洗浄する対象はフォトレジスト膜に限られない。

【産業上の利用可能性】

【0114】

本発明は、基板上の有機膜または金属粒子などを除去する工程を有する装置の製造技術に適用して有効である。

【符号の説明】

【0115】

1 半導体基板

2 絶縁膜

3 絶縁膜

4 素子分離領域

4a 溝

4b 絶縁膜

4c 絶縁膜

5 p型ウエル

6 n型ウエル

7 ゲート絶縁膜

8 シリコン膜

8a、8b ゲート電極

9a n−型半導体領域

9b n+型半導体領域

10a p−型半導体領域

10b p+型半導体領域

10p p型半導体層

11 サイドウォール

12 金属膜

41 金属シリサイド層

42、43、52 絶縁膜

44 コンタクトホール

45 プラグ

45a バリア導体膜

45b 主導体膜

51 ストッパ絶縁膜

53 配線溝

54 バリア導体膜

55 配線

60 電解硫酸槽

61 半導体ウエハ

62 ヒータ

63、68〜70 ポンプ

64 冷却器

65 貯留槽

66 過硫酸生成装置

67 気液分離器

71 フィルタ

Qn nチャネル型MISFET

Qp pチャネル型MISFET

R1〜R3 フォトレジスト膜

Ra 洗浄機

Rb 電解硫酸生成装置

RD 洗浄装置

S1〜S5 ステップ

S3a、S4a ステップ

SP1〜SP11 ステップ

【特許請求の範囲】

【請求項1】

(a)基板を電解硫酸を用いて洗浄する工程、

(b)前記基板を水を用いて洗浄する工程、

(c)前記基板を乾燥させる工程、

を有する半導体装置の製造方法であって、

前記(a)工程の前に前記基板へのアッシング工程を行わず、

前記(c)工程の前にAPM洗浄工程およびHPM洗浄工程を有していないことを特徴とする半導体装置の製造方法。

【請求項2】

前記電解硫酸を生成する装置は隔膜を有していないことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記(a)工程で用いられる電解硫酸の硫酸の濃度は80〜90wt%であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項4】

前記(a)工程で用いられる電解硫酸の温度は110℃〜150℃であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項5】

前記(a)〜(c)工程は一台の装置内で処理することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項6】

前記(b)工程では、前記水に超音波を印加することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項7】

前記(b)工程で用いる前記水は、純水と電解イオン水との混合液であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項8】

(a)基板を電解硫酸を用いて洗浄する工程、

(b)前記基板を水を用いて洗浄する工程、

(c)前記基板を乾燥させる工程、

を有する半導体装置の製造方法であって、

前記(a)工程の前に前記基板へのアッシング工程を行わず、

前記(c)工程の前にAPM洗浄工程およびHPM洗浄工程を有していないことを特徴とする基板の洗浄方法。

【請求項9】

前記電解硫酸を生成する装置は隔膜を有していないことを特徴とする請求項8記載の基板の洗浄方法。

【請求項10】

前記(a)工程で用いられる電解硫酸の硫酸の濃度は80〜90wt%であることを特徴とする請求項8記載の基板の洗浄方法。

【請求項11】

前記(a)工程で用いられる電解硫酸の温度は110℃〜150℃であることを特徴とする請求項8記載の基板の洗浄方法。

【請求項12】

前記(a)〜(c)工程は一台の装置内で処理することを特徴とする請求項8記載の基板の洗浄方法。

【請求項13】

前記(b)工程では、前記水に超音波を印加することを特徴とする請求項8記載の基板の洗浄方法。

【請求項14】

前記(b)工程で用いる前記水は、純水と電解イオン水との混合液であることを特徴とする請求項8記載の基板の洗浄方法。

【請求項1】

(a)基板を電解硫酸を用いて洗浄する工程、

(b)前記基板を水を用いて洗浄する工程、

(c)前記基板を乾燥させる工程、

を有する半導体装置の製造方法であって、

前記(a)工程の前に前記基板へのアッシング工程を行わず、

前記(c)工程の前にAPM洗浄工程およびHPM洗浄工程を有していないことを特徴とする半導体装置の製造方法。

【請求項2】

前記電解硫酸を生成する装置は隔膜を有していないことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記(a)工程で用いられる電解硫酸の硫酸の濃度は80〜90wt%であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項4】

前記(a)工程で用いられる電解硫酸の温度は110℃〜150℃であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項5】

前記(a)〜(c)工程は一台の装置内で処理することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項6】

前記(b)工程では、前記水に超音波を印加することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項7】

前記(b)工程で用いる前記水は、純水と電解イオン水との混合液であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項8】

(a)基板を電解硫酸を用いて洗浄する工程、

(b)前記基板を水を用いて洗浄する工程、

(c)前記基板を乾燥させる工程、

を有する半導体装置の製造方法であって、

前記(a)工程の前に前記基板へのアッシング工程を行わず、

前記(c)工程の前にAPM洗浄工程およびHPM洗浄工程を有していないことを特徴とする基板の洗浄方法。

【請求項9】

前記電解硫酸を生成する装置は隔膜を有していないことを特徴とする請求項8記載の基板の洗浄方法。

【請求項10】

前記(a)工程で用いられる電解硫酸の硫酸の濃度は80〜90wt%であることを特徴とする請求項8記載の基板の洗浄方法。

【請求項11】

前記(a)工程で用いられる電解硫酸の温度は110℃〜150℃であることを特徴とする請求項8記載の基板の洗浄方法。

【請求項12】

前記(a)〜(c)工程は一台の装置内で処理することを特徴とする請求項8記載の基板の洗浄方法。

【請求項13】

前記(b)工程では、前記水に超音波を印加することを特徴とする請求項8記載の基板の洗浄方法。

【請求項14】

前記(b)工程で用いる前記水は、純水と電解イオン水との混合液であることを特徴とする請求項8記載の基板の洗浄方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−191059(P2012−191059A)

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願番号】特願2011−54463(P2011−54463)

【出願日】平成23年3月11日(2011.3.11)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成22年9月14日 社団法人応用物理学会発行の「2010年(平成22年)秋季 第71回応用物理学会学術講演会 公式ガイドブック」に発表

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願日】平成23年3月11日(2011.3.11)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成22年9月14日 社団法人応用物理学会発行の「2010年(平成22年)秋季 第71回応用物理学会学術講演会 公式ガイドブック」に発表

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]