基板導通を利用した積重ねダイ式の構成をもつ集積回路

【課題】積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供すること。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概して集積回路に関し、より具体的には基板導通の仕組みを介して集積回路内で電源を接続するための技術に関する。

【背景技術】

【0002】

一般的な基板導通の仕組みでは、電流は集積回路ダイ上に設けられた電界効果装置から集積回路のダイの基板を経由してVSS電源に流れる。これが、ダイの表側に必要なVSSのボンド・パッドの数を削減し、ある場合には、このようなボンド・パッドが完全に不必要になり、有利である。基板導通は、電源線インダクタンスの減少並びにリンギングおよびグラウンド・バウンスの軽減を含むその他の利点も提供する。単一ダイの基板導通の仕組みが、1990年8月7日に発明者T.J.Gabara名で発行され、「集積回路電源コンタクト(Integrated Circuit Power Supply Contact)」と題され、その開示内容が参照として本明細書に組み込まれている米国特許第4,947,228号に非常に詳しく説明されている。

【0003】

図1に図示されているのは、上述の米国特許に説明されているタイプの従来形単一ダイ基板導通の仕組みの一例である。この図面および本明細書中のこの他の図面は、説明を明確にするためにかなり簡素化されていることを理解されたい。図示のように、集積回路100は、その上にp型エピタキシャル層104が形成されるP+基板102を含む。エピタキシャル層は基板に関して軽度にドープされており、したがって高抵抗層を提供している。本例ではp型導通性のタブ領域106が、エピタキシャル層104内に形成され、P+の高度にドープされた、タブ・タイ108が、タブ領域106に形成される。タブ・タイ108は、集積回路のVSSバス110に接続されており、そのバスはこの簡素化された図面では明示的に示されていない電界効果装置の端子に結合されている。集積回路100は、VDDボンド・パッド112および信号ボンド・パッド114をさらに含みそれらは、VDDボンディング・ワイヤ116および信号ボンディング・ワイヤ118にそれぞれ結合されている。VDDボンディング・ワイヤ116、VDDボンド・パッド112、信号ボンディング・ワイヤ118、信号ボンド・パッド114および、VSSバス110と、P+のタブ・タイ108とp−のタブ106とによって形成されている基板導通パスは、ダイの上で何度も反復される。

【0004】

図1には示されていないが、基板102の裏側に、つまり基板のエピタキシャル層に対向する側に金属層を形成してもよい。このような金属層は、これも図示していないが集積回路に外付けされるVSS電源に結合されている。

【0005】

図1の仕組みでは、電流IはVDDボンディング・ワイヤ116を経由して集積回路に外付けされるVDD電源から、VDDボンド・パッド112を通って電界効果装置の端子に流れて集積回路を通過する。説明を簡単にするために、電流は信号ボンディング・ワイヤ118などの信号リード線を経由して、集積回路にあるいは集積回路から流入または流出せず、電流Iは、電界効果装置のその他の端子からVSSバス110に流れるものと仮定する。電流Iは、VSSバスからタブ・タイ108、p型タブ106およびエピタキシャル層104、そして最後に基板102を通過して、図面には示されていないが外付けされるVSS電源に流れる。基板導通の方向は、矢印120によって示されている。したがってこの基板導通の仕組みでは、電界効果装置からのVSS電流は、VSSボンディング・ワイヤを通してよりむしろ基板102を通して流れる。

【0006】

従来の基板導通の問題は、単一ダイの集積回路を念頭に技術が開発されたことである。近年積重ねダイ式の構成を利用する集積回路が多数開発されてきたが、その構成では多数の集積回路のダイが、相互に積み重ねられ、隣接するダイが少なくとも部分的に重なっている。上述した単一ダイの基板導通の利点は積重ねダイの状況でも望ましいはずであるが、基板導通を提供することができるのかあるいはどのようにして提供することができるのか従来から明らかではなかった。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第4,947,228号

【発明の概要】

【発明が解決しようとする課題】

【0008】

したがって積重ねダイ式の構成を有する集積回路で基板導通を設けるための技術に対する必要性が存在する。

【課題を解決するための手段】

【0009】

本発明は、積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供する。

本発明の一態様によれば集積回路は、積重ね状に配置された複数の集積回路のダイを含み、積重ねの頂部のダイを除く任意のダイが、基板導通を介してそれ自体および積重ねへの追加のダイ少なくとも1つのための電流を担持する。

【0010】

第1の例示的実施形態では、集積回路は、第1の基板および第1の基板の一部分を覆って形成されている第1の電源導体を有する第1の集積回路のダイと、第2の基板および第2の基板の一部分を覆って形成されている第2の電源導体を有する第2の集積回路のダイとを有する。第2の集積回路のダイは、第1の集積回路のダイの上に積み重ねられかつ少なくとも部分的に重なり合っている。第1の集積回路のダイの第1の電源導体は、第2の集積回路のダイの第2の基板に導通可能に結合されている。第2の集積回路のダイに関連する電源電流は、第1の集積回路のダイの第1の電源導体を経由して第2の基板を通る基板導通により担持される。第1の集積回路のダイに関連する電源電流は第1の基板を通る基板導通によって担持される。

【0011】

集積回路は、第3の基板および第3の基板の一部を覆って形成される第3の電源導体を有する少なくとも1つの追加の集積回路のダイをさらに含むことがあり、その第3の集積回路のダイは、第2の集積回路のダイの上に積み重ねられかつ少なくとも部分的に重なり合っている。この場合、第2の集積回路のダイの第2の電源導体が第3の集積回路のダイの第3の基板に導通可能に結合されることもあり、第3の集積回路のダイに関連する電源電流は、第2の集積回路のダイの第2の電源導体を経由して第3の基板を通る基板導通により担持されることもある。

【0012】

したがって本実施形態では、第1および第2の集積回路のダイは、N個の積み上げられた集積回路のダイのうちの2つのこともあり、ここでNは2より大きく、積重ねの底部のダイを除く各ダイが、基板導通によりその下側のダイの電源導体に関する電源電流を担持する。

【0013】

第2の例示的実施形態では、ここでも集積回路は、第1の基板および第1の基板の一部分を覆って形成されている第1の電源導体を有する第1の集積回路のダイと、第2の基板および第2の基板の一部分を覆って形成されている第2の電源導体を有する第2の集積回路のダイとを有し、第2の集積回路のダイは、第1の集積回路のダイの上に積み重ねられかつ少なくとも部分的に重なり合っている。しかしこの実施形態では、第2の集積回路のダイに関連する電源電流は、第1の集積回路のダイの第1の電源導体を介して第1および第2の基板を通る基板導通により担持される。これは、第1の集積回路のダイの第1の基板が第2の集積回路のダイの第2の基板に向き合うように第1および第2の集積回路のダイを背中合わせの構成で積み重ねることによって実現できる。第1の集積回路のダイの第1の基板は、銀エポキシ等の導電金属の層を介して第2の集積回路のダイの第2の基板に結合されてもよい。この実施形態では、第1の集積回路内での電源電流の流れは、第1の基板の表面から第1の電源導体に向かう方向にあることもあり、この方向は前述の第1の例示的実施形態における電源電流の流れ方向に対向するものである。

【0014】

本発明は、これら例示的実施形態において、必要とする電源ボンド・パッドの数の削減などの単一ダイの基板導通の利点を積重ねダイ式の構成で得ることを可能にしている。

【図面の簡単な説明】

【0015】

【図1】従来式基板導通をもつ単一ダイの集積回路の簡素化した断面図である。

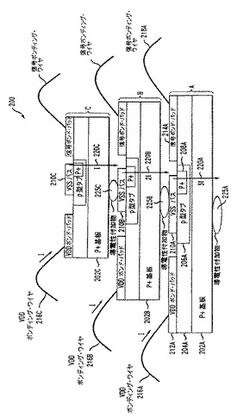

【図2】本発明の第1の例示的実施形態による基板導通をもつ積重ねダイ式の集積回路の簡素化した断面図である。

【図3】本発明の第2の例示的実施形態による基板導通をもつ積重ねダイ式の集積回路の簡素化した断面図である。

【図4】フリップチップ・ボール・グリッド・アレー(BGA)を使用した、図3に示すタイプの積重ねダイ式集積回路の具体的な一実施例を示す図である。

【図5】概して図2の実施形態にそれぞれ対応しているが、対向する導通のタイプを使用して実施される本発明の実施形態を示す図である。

【図6】概して図3の実施形態にそれぞれ対応しているが、対向する導通のタイプを使用して実施される本発明の実施形態を示す図である。

【発明を実施するための形態】

【0016】

本明細書では、いくつかの例示的な積重ねダイ式集積回路およびそのような回路で実施される基板導通の仕組みを念頭に本発明を説明する。ただし、示される具体的な仕組みは説明に役立つ例証としてのみ提供されるものでどんな形であれ本発明の範囲を限定するものではないことを理解されたい。その他積重ねダイ式集積回路の構成において、VSSボンド・パッドの数の削減、または単一ダイの集積回路の基板導通に一般的に伴うその他の利点を得ることが望まれるが、本発明による技法が多種多様な回路構成で利用可能であることが明らかになるであろう。

【0017】

図2は、本発明の第1の例示的実施形態による基板導通を備える積重ねダイ式集積回路200を示している。本実施形態では、集積回路200は一般的に積重ね状に配置された複数の集積回路のダイを含み、積重ねの底部のダイを除く各ダイが基板導通によりその下側のダイの電源導体を介してその電源電流を担持する。より具体的には、積重ねダイ式集積回路200は、A、BおよびCと表示され積重ね状に配置された個別のダイ3つを含み、ダイAは積重ねの第1、つまり底部のダイであり、ダイBは積重ねの第2のダイであり少なくとも部分的にダイAと重なり合い、ダイCは積重ねの第3、つまり頂部のダイであり少なくとも部分的にダイBと重なり合っている。底部のダイAを除く各ダイは、基板導通により下側ダイの電源導体を介してその電源電流を担持する。すなわち、ダイCは、そのVSS電源電流を基板導通によりダイBのVSS電源導体を介して担持し、ダイBは、そのVSS電源電流を基板導通によりダイAのVSS電源導体を介して担持する。

【0018】

底部のダイ、ダイAも基板導通を介してその電源電流を担持するが、下側のダイのVSS電源導体を介してではなく、図示されていないがVSS電源との接続を介してである。

【0019】

周知のように、任意の集積回路のためのVSS電源は、回路グラウンドまたはその他のグラウンド電位を含むこともある。本明細書で使用する「VSS電源」または「電源」という用語は、正または負の電位に加えてグラウンドを含むものとする。

【0020】

本明細書において「積重ね」という用語は、複数の集積回路のダイが、少なくとも一部で互いに重なり合っている方式で構成されている任意の仕組みを含むがこれに限定されないことを理解されたい。したがって、図2に例示的に示すようにダイは、積重ねの底部から頂部に向かってその寸法を減少する必要はない。むしろダイの寸法は、底部から頂部に向かって増加するか実質的に均一である可能性もある。また任意のダイは、その下側または上側のダイと完全に重なり合う必要はなく、したがって多種多様な部分的重なり合い配置が企図されている。

【0021】

本明細書で説明する例示的実施形態では任意の基板は、集積回路のダイの表側と裏側の間に形成された導電性パスの部分を含むとみなされることもある。本発明ではそのような仕組みを必要としないが、この導電性パスは、導電性パスでの電圧降下が減少するように最大のコンダクタンス(最小抵抗)をもって理想的に設計されるものとする。

【0022】

例えば図2で、前述のように、p型ドーパント材料の様々な層およびVSSバス210Aを含むいくつかの構成要素によって形成されるダイA内の導通パスが、基板導通電流220Aを導通させる。p型タブ206Aおよびエピタキシャル層204Aのようなp型ドーパント材料のいくつかの層を、軽度にドープしたp型濃度で形成することがある。これら2つの層(204A、206A)は、残りのp型層(202Aおよび208A)に比べ一般的により低コンダクタンス(高抵抗)を有することになり、その結果導通パス内で好ましくない電圧降下が発生することがある。

【0023】

導通性パスの電圧降下は、例えば層204Aおよび206A内部のp型ドーパント濃度を当技術分野で周知の処理方法を使用して選択的に増加することによって下げることができる。他の例として、P+タブ・タイ208Aを形成するドーパントの注入を、P+タブ・タイ208Aが物理的にP+基板202Aに接するようにダイのさらに奥に達するまで行うことができ、それによって導電性パスが最大コンダクタンス(最小抵抗)を有することを可能になる。さらに他の例は、P+を埋め込んだ層(図示せず)をP+タブ・タイ208Aの下側に配置することである。通常の処理段階で埋め込んだ層内のp型ドーパントが拡散し(排斥され)、P+タブ・タイ208AをP+基板202Aに結合し伝導性パスのコンダクタンスを増加させる。

【0024】

図2の積重ねダイ式集積回路200の底部のダイAは、P+基板202A、軽度にドープされたp型エピタキシャル層204A、p型タブ206A、P+タブ・タイ208A、VSSバス210A、VDDボンド・パッド212A、信号ボンド・パッド214A、VDDボンディング・ワイヤ216A、および信号ボンディング・ワイヤ218Aを含む。これらの構成要素は、図1の従来型単一ダイ式集積回路100の対応する構成要素と同様の方式で構成されている。導電性の付加物225Aが、基板202Aと上記外付けのVSS電源を接続する。図示されてはいないが、基板202Aの裏に、つまり基板のエピタキシャル層204Aと対向する側に金属層が形成されることもある。このような金属層は、外付けのVSS電源に結合されることもある。導電性付加物225Aが、このような金属層、または基板202AをVSS電源に結合するのに適切なその他いかなるタイプの導電性構成要素を含んでもよいことを理解されたい。

【0025】

さらに各ダイBおよびCは、ダイAのものと同様の構成要素を含む。例えばダイBおよびCは、それぞれの基板202Bおよび202Cと、それぞれのVSSバス210Bおよび210Cを含む。VSSバス210A、210Bおよび210Cは、本明細書ではより一般的に「電源導体」と呼ばれているものを示す例証であるとみなすことができる。この用語は、集積回路のダイの1つまたは複数の電界効果装置またはその他の構成要素に供給電圧を与えるのに使用できるあらゆるタイプの導電性構成要素を含むがこれらに限定されず、ここで言うその他の構成要素とは、バイポーラ・トランジスタ、抵抗性部品、またはその他の能動または受動部品を含むがこれに限定されない。例えば、電源導体は、特定のダイの表面上に設けられ、ダイの基板に接続されている金属の相互接続であってもよい。このような金属の相互接続は、個々のダイのための特定の技術で利用可能な1つまたは複数の金属層を使用して形成されるのが一般的である。

【0026】

したがって第1つまり底部の集積回路のダイAは、基板202Aおよび基板202Aの一部を覆って形成された電源導体210Aを含む。第2の集積回路のダイBは、基板202Bおよび基板202Bの一部を覆って形成された電源導体210Bを含む。ダイAの電源導体210Aは、ダイBのためのVSS電源電流が、導電性付加物225Bを使用して、ダイAのVSS電源導体210Aを介して基板202Bを通る基板導通により担持されるようにダイBの基板202Bに導通可能に結合される。第3の、つまり頂部の集積回路のダイCは、基板202Cおよび基板202Cの一部を覆って形成された電源導体210Cを含む。ダイBの電源導体210Bは、ダイCのためのVSS電源電流が、導電性付加物225Cを使用して、ダイBの電源導体210Bを介して基板202Bを通る基板導通により担持されるようにダイCの基板202Cに導通可能に結合される。

【0027】

この例示的実施形態では、各ダイA、BおよびCがIで与えられる電源電流を引き出すものと仮定する。この電流は、外付けのVDD電源(図示せず)から、それぞれVDDボンディング・ワイヤ216A、216Bおよび216Cを介してダイA、BおよびCに向かって対応する矢印で示される方向に流れる。再度説明を簡単にするために電流は、信号リード線を介して集積回路にあるいは集積回路から流入または流出せず、電流値Iが各ダイA、BおよびCとVSS電源の間を流れると仮定する。したがって基板202Aを通る基板導通により担持される合計電流値は、矢印220Aで示されるように3Iで与えられる。同様に矢印220Bおよび220Cで示されるように、基板202Bおよび202Cを通る基板導通により担持される電流量はそれぞれ2IおよびIで与えられる。したがって底部のダイAは、ダイA、BおよびCの3つ全てのための電流を基板導通により担持する。より一般的には、積重ねダイ式集積回路では頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。P+基板の代わりにN+基板を利用する一代替実施形態では、基板電流の流れ方向が、図2の電流矢印で示される方向と対向する方向になることに注意されたい。

【0028】

図2では実装されていない(unpackaged)構成で示されているが、積重ねダイ式集積回路200を、当技術分野で周知の技術を使用して実装してもよい。例えば回路200を、図4と共に説明するタイプのフリップ・チップBGAパッケージ、あるいは積重ねダイ式集積回路に使用するのに適切なその他の任意の実装構成を使用して実装してもよい。

【0029】

図2の実施形態では、p型導通の仕組みを利用しており、その構成要素例えば基板202A、エピタキシャル層204A、p型タブ206A、およびタブ・タイ208Aはp型半導体材料から成っている。その他のタイプの導通の仕組みを使用できることを理解されたい。そのような代替導通の仕組みの例を、図5および図6と共に示し、説明する。

【0030】

図3は、積重ねダイ式集積回路300を示し、その回路は本発明の第2の例示的実施形態による基板導通を伴う。この実施形態は、集積回路のダイAおよびBを含み、各々のダイは前述の実施形態と実質上同じ構成要素のセットを含む。しかしこの実施形態では、背中合わせの構成で第2の集積回路のダイBが、第1の集積回路のダイAに積み重ねられかつ少なくとも部分的に重なり合っており、ダイAの基板202AがダイBの基板202Bに向き合っている。この実施形態では、ダイBのためのVSS電源電流は、ダイAの電源導体210Aを介して基板202Aおよび202Bを通る基板導通により担持され、その方向は電源導体210Bおよび210Aの間で垂直な矢印によって示される方向である。したがってダイAを通るVSS電源電流の流れ方向は基板202Aの表面から電源導体210Aに向かう。この方向は、図1および図2の基板導通の仕組みにおける電流の流れ方向に対向していることに注意されたい。したがってこのタイプの基板導通の仕組みを本明細書では「逆方向」基板導通と呼ぶこともある。

【0031】

この実施形態では、基板202Aと202Bは、導電性材料例えば銀エポキシの層302で互いから引き離されている。向き合っている基板間でその他の導電性材料の層または導電性の結合の仕組みを使用してもよい。半田バンプ304、306および308は、VDDボンド・パッド212A、VSS電源導体210Aおよび信号ボンド・パッド214Aとそれぞれ関連しており、例えば、このようにしなければ従来式であるBGAパッケージを使用して積重ねダイ式集積回路300を実装する際に利用される。

【0032】

この例示的実施形態では、各ダイAおよびBは、Iで与えられる電源電流を引き出すものと仮定する。この電流は、外付けのVDD電源(図示せず)から、VDDボンド・パッド212AおよびVDDボンディング・ワイヤ216Bを介してダイA、Bに向かって対応する矢印で示される方向に流れる。再度説明を簡単にするために電流は、信号リード線を介して集積回路にあるいは集積回路から流入または流出せず電流値Iが、各ダイAおよびBとVSS電源の間を流れると仮定する。基板202Aを通る基板導通により担持される合計電流値は、矢印310で示されるようにIで与えられる。より具体的には、底部のダイAは、逆方向基板導通によりダイBからの第1の電流Iを流す。VDDボンド・パッド212Aに流れ込む第2の電流Iは、ダイAの表面に形成される装置または構成要素に与えられる。これら装置または構成要素が第2の電流IをVSS電源に返す。矢印312で表される電流2Iが、第1の電流Iと第2の電流Iとの合計である。

【0033】

図3に示す基板の背中合わせ配置は、1つまたは複数の集積回路のダイを追加して、例えば図2に示すタイプの仕組みで構成された追加のダイと組み合わせて使用してもよい。したがって本発明による任意の積重ねダイ式集積回路は、図2および図3で説明した技術の組合せを使用してもよい。

【0034】

図4に示すのは、図3に示すタイプの積重ねダイ式集積回路のフリップ・チップBGAパッケージを使用した具体的な実装形態である。この実施形態では、積重ねダイ式集積回路400は、第1つまり底部の集積回路のダイ402および第2つまり頂部の集積回路のダイ404を含み、それらは図示のように積み重ねられている。底部および頂部のダイ402および404の背後はそれぞれ矢印412および414で表示されている。明らかなように、底部および頂部のダイ402および404は、図3と共に説明したタイプの構成で背中合わせに配置されている。銀エポキシまたはその他の導電性材料の層405が、底部および頂部のダイ402および404の基板を結合している。底部ダイ402は、フリップ・チップBGAパッケージの装着用構造(mounting structure)406に取り付けられ、ボンド・ワイヤ408が頂部ダイ404の上側表面に接続される。装着用構造406内の導電性トレースが、底部ダイ402の表側の導体をフリップ・チップBGAパッケージの半田ボール410に接続する。この実施形態では、VSS電流の流れ方向は、図3の実施形態のように矢印420で示されている。

【0035】

図5および図6に示す実施形態は、概して図2および図3の実施形態にそれぞれ対応する本発明の実施形態であるが、対向するタイプの導通性をもつ基板、エピタキシャル層、タブおよびタブ・タイの各要素を使用して実施されている。より具体的には、図5および図6それぞれに示す積重ねダイ式集積回路500および600の構成要素、基板202A’、エピタキシャル層204A’、タブ206A’、タブ・タイ208A’などはn型半導体材料で成り、図2および図3に示すp型半導体材料で成る構成要素に対応している。VDDおよびVSS電源への接続も逆になっており、図5および図6のボンド・パッドがVSSボンド・パッドに対応し、図5および図6の電源導体がVDDバスに対応する。その結果、例えば図5で矢印220A’、図6で矢印310’によって示される電流の流れ方向は、図2および図3に示される対応する方向に対して逆になっている。その他の点ではこれら代替実施形態の構成および動作は、前述の実施形態のものと実質的に同じである。さらに別のタイプの導通性によるこの他の仕組みを使用でき、この点に関して本発明は制約を受けない。

【0036】

図2から図6に示す具体的な積重ねダイ式の構成は、例示的の例証としてのみ提示されており、本発明の範囲をいかなる形であれ制限するとは理解すべきではないことに注意されたい。また、ある従来形の構成要素を図から削除して説明を明確かつ簡素にした。このように削除された構成要素は、当業者ならば理解するであろうが本発明の任意の実施形態に含むことができる。

【0037】

上述のように、本発明の任意の実施形態を1つまたは複数の集積回路として実施することができる。このような仕組みでは複数の同一のダイが、繰返しパターンでウェーハ表面上に形成されるのが一般的である。各ダイは、本明細書で説明したように装置を含むこともあり、その他の構造または回路を含むこともある。個々のダイは、ウェーハから刻みあるいは切り取られ、次いで集積回路として実装される。当業者ならばどのようにしてウェーハを刻み、ダイを実装して集積回路を生産するか理解しているはずである。そのようにして製造された集積回路はこの発明の部分であるものとする。

【0038】

本発明の上述の実施形態は説明のためだけのものである。当業者ならば、以下の特許請求の範囲の視野から逸脱することなく多数の代替実施形態を派生することができる。例えば、基板またはその他の半導体層あるいは領域、ボンド・パッド、ボンド・ワイヤ、積重ね配置、導電性付加物またはパッケージ・タイプなどの集積回路の構成要素に対する数多くの代替構成を使用することができる。当業者にとってこれらおよびその他の代替実施形態は、直ちに明白になるであろう。

【技術分野】

【0001】

本発明は、概して集積回路に関し、より具体的には基板導通の仕組みを介して集積回路内で電源を接続するための技術に関する。

【背景技術】

【0002】

一般的な基板導通の仕組みでは、電流は集積回路ダイ上に設けられた電界効果装置から集積回路のダイの基板を経由してVSS電源に流れる。これが、ダイの表側に必要なVSSのボンド・パッドの数を削減し、ある場合には、このようなボンド・パッドが完全に不必要になり、有利である。基板導通は、電源線インダクタンスの減少並びにリンギングおよびグラウンド・バウンスの軽減を含むその他の利点も提供する。単一ダイの基板導通の仕組みが、1990年8月7日に発明者T.J.Gabara名で発行され、「集積回路電源コンタクト(Integrated Circuit Power Supply Contact)」と題され、その開示内容が参照として本明細書に組み込まれている米国特許第4,947,228号に非常に詳しく説明されている。

【0003】

図1に図示されているのは、上述の米国特許に説明されているタイプの従来形単一ダイ基板導通の仕組みの一例である。この図面および本明細書中のこの他の図面は、説明を明確にするためにかなり簡素化されていることを理解されたい。図示のように、集積回路100は、その上にp型エピタキシャル層104が形成されるP+基板102を含む。エピタキシャル層は基板に関して軽度にドープされており、したがって高抵抗層を提供している。本例ではp型導通性のタブ領域106が、エピタキシャル層104内に形成され、P+の高度にドープされた、タブ・タイ108が、タブ領域106に形成される。タブ・タイ108は、集積回路のVSSバス110に接続されており、そのバスはこの簡素化された図面では明示的に示されていない電界効果装置の端子に結合されている。集積回路100は、VDDボンド・パッド112および信号ボンド・パッド114をさらに含みそれらは、VDDボンディング・ワイヤ116および信号ボンディング・ワイヤ118にそれぞれ結合されている。VDDボンディング・ワイヤ116、VDDボンド・パッド112、信号ボンディング・ワイヤ118、信号ボンド・パッド114および、VSSバス110と、P+のタブ・タイ108とp−のタブ106とによって形成されている基板導通パスは、ダイの上で何度も反復される。

【0004】

図1には示されていないが、基板102の裏側に、つまり基板のエピタキシャル層に対向する側に金属層を形成してもよい。このような金属層は、これも図示していないが集積回路に外付けされるVSS電源に結合されている。

【0005】

図1の仕組みでは、電流IはVDDボンディング・ワイヤ116を経由して集積回路に外付けされるVDD電源から、VDDボンド・パッド112を通って電界効果装置の端子に流れて集積回路を通過する。説明を簡単にするために、電流は信号ボンディング・ワイヤ118などの信号リード線を経由して、集積回路にあるいは集積回路から流入または流出せず、電流Iは、電界効果装置のその他の端子からVSSバス110に流れるものと仮定する。電流Iは、VSSバスからタブ・タイ108、p型タブ106およびエピタキシャル層104、そして最後に基板102を通過して、図面には示されていないが外付けされるVSS電源に流れる。基板導通の方向は、矢印120によって示されている。したがってこの基板導通の仕組みでは、電界効果装置からのVSS電流は、VSSボンディング・ワイヤを通してよりむしろ基板102を通して流れる。

【0006】

従来の基板導通の問題は、単一ダイの集積回路を念頭に技術が開発されたことである。近年積重ねダイ式の構成を利用する集積回路が多数開発されてきたが、その構成では多数の集積回路のダイが、相互に積み重ねられ、隣接するダイが少なくとも部分的に重なっている。上述した単一ダイの基板導通の利点は積重ねダイの状況でも望ましいはずであるが、基板導通を提供することができるのかあるいはどのようにして提供することができるのか従来から明らかではなかった。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第4,947,228号

【発明の概要】

【発明が解決しようとする課題】

【0008】

したがって積重ねダイ式の構成を有する集積回路で基板導通を設けるための技術に対する必要性が存在する。

【課題を解決するための手段】

【0009】

本発明は、積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供する。

本発明の一態様によれば集積回路は、積重ね状に配置された複数の集積回路のダイを含み、積重ねの頂部のダイを除く任意のダイが、基板導通を介してそれ自体および積重ねへの追加のダイ少なくとも1つのための電流を担持する。

【0010】

第1の例示的実施形態では、集積回路は、第1の基板および第1の基板の一部分を覆って形成されている第1の電源導体を有する第1の集積回路のダイと、第2の基板および第2の基板の一部分を覆って形成されている第2の電源導体を有する第2の集積回路のダイとを有する。第2の集積回路のダイは、第1の集積回路のダイの上に積み重ねられかつ少なくとも部分的に重なり合っている。第1の集積回路のダイの第1の電源導体は、第2の集積回路のダイの第2の基板に導通可能に結合されている。第2の集積回路のダイに関連する電源電流は、第1の集積回路のダイの第1の電源導体を経由して第2の基板を通る基板導通により担持される。第1の集積回路のダイに関連する電源電流は第1の基板を通る基板導通によって担持される。

【0011】

集積回路は、第3の基板および第3の基板の一部を覆って形成される第3の電源導体を有する少なくとも1つの追加の集積回路のダイをさらに含むことがあり、その第3の集積回路のダイは、第2の集積回路のダイの上に積み重ねられかつ少なくとも部分的に重なり合っている。この場合、第2の集積回路のダイの第2の電源導体が第3の集積回路のダイの第3の基板に導通可能に結合されることもあり、第3の集積回路のダイに関連する電源電流は、第2の集積回路のダイの第2の電源導体を経由して第3の基板を通る基板導通により担持されることもある。

【0012】

したがって本実施形態では、第1および第2の集積回路のダイは、N個の積み上げられた集積回路のダイのうちの2つのこともあり、ここでNは2より大きく、積重ねの底部のダイを除く各ダイが、基板導通によりその下側のダイの電源導体に関する電源電流を担持する。

【0013】

第2の例示的実施形態では、ここでも集積回路は、第1の基板および第1の基板の一部分を覆って形成されている第1の電源導体を有する第1の集積回路のダイと、第2の基板および第2の基板の一部分を覆って形成されている第2の電源導体を有する第2の集積回路のダイとを有し、第2の集積回路のダイは、第1の集積回路のダイの上に積み重ねられかつ少なくとも部分的に重なり合っている。しかしこの実施形態では、第2の集積回路のダイに関連する電源電流は、第1の集積回路のダイの第1の電源導体を介して第1および第2の基板を通る基板導通により担持される。これは、第1の集積回路のダイの第1の基板が第2の集積回路のダイの第2の基板に向き合うように第1および第2の集積回路のダイを背中合わせの構成で積み重ねることによって実現できる。第1の集積回路のダイの第1の基板は、銀エポキシ等の導電金属の層を介して第2の集積回路のダイの第2の基板に結合されてもよい。この実施形態では、第1の集積回路内での電源電流の流れは、第1の基板の表面から第1の電源導体に向かう方向にあることもあり、この方向は前述の第1の例示的実施形態における電源電流の流れ方向に対向するものである。

【0014】

本発明は、これら例示的実施形態において、必要とする電源ボンド・パッドの数の削減などの単一ダイの基板導通の利点を積重ねダイ式の構成で得ることを可能にしている。

【図面の簡単な説明】

【0015】

【図1】従来式基板導通をもつ単一ダイの集積回路の簡素化した断面図である。

【図2】本発明の第1の例示的実施形態による基板導通をもつ積重ねダイ式の集積回路の簡素化した断面図である。

【図3】本発明の第2の例示的実施形態による基板導通をもつ積重ねダイ式の集積回路の簡素化した断面図である。

【図4】フリップチップ・ボール・グリッド・アレー(BGA)を使用した、図3に示すタイプの積重ねダイ式集積回路の具体的な一実施例を示す図である。

【図5】概して図2の実施形態にそれぞれ対応しているが、対向する導通のタイプを使用して実施される本発明の実施形態を示す図である。

【図6】概して図3の実施形態にそれぞれ対応しているが、対向する導通のタイプを使用して実施される本発明の実施形態を示す図である。

【発明を実施するための形態】

【0016】

本明細書では、いくつかの例示的な積重ねダイ式集積回路およびそのような回路で実施される基板導通の仕組みを念頭に本発明を説明する。ただし、示される具体的な仕組みは説明に役立つ例証としてのみ提供されるものでどんな形であれ本発明の範囲を限定するものではないことを理解されたい。その他積重ねダイ式集積回路の構成において、VSSボンド・パッドの数の削減、または単一ダイの集積回路の基板導通に一般的に伴うその他の利点を得ることが望まれるが、本発明による技法が多種多様な回路構成で利用可能であることが明らかになるであろう。

【0017】

図2は、本発明の第1の例示的実施形態による基板導通を備える積重ねダイ式集積回路200を示している。本実施形態では、集積回路200は一般的に積重ね状に配置された複数の集積回路のダイを含み、積重ねの底部のダイを除く各ダイが基板導通によりその下側のダイの電源導体を介してその電源電流を担持する。より具体的には、積重ねダイ式集積回路200は、A、BおよびCと表示され積重ね状に配置された個別のダイ3つを含み、ダイAは積重ねの第1、つまり底部のダイであり、ダイBは積重ねの第2のダイであり少なくとも部分的にダイAと重なり合い、ダイCは積重ねの第3、つまり頂部のダイであり少なくとも部分的にダイBと重なり合っている。底部のダイAを除く各ダイは、基板導通により下側ダイの電源導体を介してその電源電流を担持する。すなわち、ダイCは、そのVSS電源電流を基板導通によりダイBのVSS電源導体を介して担持し、ダイBは、そのVSS電源電流を基板導通によりダイAのVSS電源導体を介して担持する。

【0018】

底部のダイ、ダイAも基板導通を介してその電源電流を担持するが、下側のダイのVSS電源導体を介してではなく、図示されていないがVSS電源との接続を介してである。

【0019】

周知のように、任意の集積回路のためのVSS電源は、回路グラウンドまたはその他のグラウンド電位を含むこともある。本明細書で使用する「VSS電源」または「電源」という用語は、正または負の電位に加えてグラウンドを含むものとする。

【0020】

本明細書において「積重ね」という用語は、複数の集積回路のダイが、少なくとも一部で互いに重なり合っている方式で構成されている任意の仕組みを含むがこれに限定されないことを理解されたい。したがって、図2に例示的に示すようにダイは、積重ねの底部から頂部に向かってその寸法を減少する必要はない。むしろダイの寸法は、底部から頂部に向かって増加するか実質的に均一である可能性もある。また任意のダイは、その下側または上側のダイと完全に重なり合う必要はなく、したがって多種多様な部分的重なり合い配置が企図されている。

【0021】

本明細書で説明する例示的実施形態では任意の基板は、集積回路のダイの表側と裏側の間に形成された導電性パスの部分を含むとみなされることもある。本発明ではそのような仕組みを必要としないが、この導電性パスは、導電性パスでの電圧降下が減少するように最大のコンダクタンス(最小抵抗)をもって理想的に設計されるものとする。

【0022】

例えば図2で、前述のように、p型ドーパント材料の様々な層およびVSSバス210Aを含むいくつかの構成要素によって形成されるダイA内の導通パスが、基板導通電流220Aを導通させる。p型タブ206Aおよびエピタキシャル層204Aのようなp型ドーパント材料のいくつかの層を、軽度にドープしたp型濃度で形成することがある。これら2つの層(204A、206A)は、残りのp型層(202Aおよび208A)に比べ一般的により低コンダクタンス(高抵抗)を有することになり、その結果導通パス内で好ましくない電圧降下が発生することがある。

【0023】

導通性パスの電圧降下は、例えば層204Aおよび206A内部のp型ドーパント濃度を当技術分野で周知の処理方法を使用して選択的に増加することによって下げることができる。他の例として、P+タブ・タイ208Aを形成するドーパントの注入を、P+タブ・タイ208Aが物理的にP+基板202Aに接するようにダイのさらに奥に達するまで行うことができ、それによって導電性パスが最大コンダクタンス(最小抵抗)を有することを可能になる。さらに他の例は、P+を埋め込んだ層(図示せず)をP+タブ・タイ208Aの下側に配置することである。通常の処理段階で埋め込んだ層内のp型ドーパントが拡散し(排斥され)、P+タブ・タイ208AをP+基板202Aに結合し伝導性パスのコンダクタンスを増加させる。

【0024】

図2の積重ねダイ式集積回路200の底部のダイAは、P+基板202A、軽度にドープされたp型エピタキシャル層204A、p型タブ206A、P+タブ・タイ208A、VSSバス210A、VDDボンド・パッド212A、信号ボンド・パッド214A、VDDボンディング・ワイヤ216A、および信号ボンディング・ワイヤ218Aを含む。これらの構成要素は、図1の従来型単一ダイ式集積回路100の対応する構成要素と同様の方式で構成されている。導電性の付加物225Aが、基板202Aと上記外付けのVSS電源を接続する。図示されてはいないが、基板202Aの裏に、つまり基板のエピタキシャル層204Aと対向する側に金属層が形成されることもある。このような金属層は、外付けのVSS電源に結合されることもある。導電性付加物225Aが、このような金属層、または基板202AをVSS電源に結合するのに適切なその他いかなるタイプの導電性構成要素を含んでもよいことを理解されたい。

【0025】

さらに各ダイBおよびCは、ダイAのものと同様の構成要素を含む。例えばダイBおよびCは、それぞれの基板202Bおよび202Cと、それぞれのVSSバス210Bおよび210Cを含む。VSSバス210A、210Bおよび210Cは、本明細書ではより一般的に「電源導体」と呼ばれているものを示す例証であるとみなすことができる。この用語は、集積回路のダイの1つまたは複数の電界効果装置またはその他の構成要素に供給電圧を与えるのに使用できるあらゆるタイプの導電性構成要素を含むがこれらに限定されず、ここで言うその他の構成要素とは、バイポーラ・トランジスタ、抵抗性部品、またはその他の能動または受動部品を含むがこれに限定されない。例えば、電源導体は、特定のダイの表面上に設けられ、ダイの基板に接続されている金属の相互接続であってもよい。このような金属の相互接続は、個々のダイのための特定の技術で利用可能な1つまたは複数の金属層を使用して形成されるのが一般的である。

【0026】

したがって第1つまり底部の集積回路のダイAは、基板202Aおよび基板202Aの一部を覆って形成された電源導体210Aを含む。第2の集積回路のダイBは、基板202Bおよび基板202Bの一部を覆って形成された電源導体210Bを含む。ダイAの電源導体210Aは、ダイBのためのVSS電源電流が、導電性付加物225Bを使用して、ダイAのVSS電源導体210Aを介して基板202Bを通る基板導通により担持されるようにダイBの基板202Bに導通可能に結合される。第3の、つまり頂部の集積回路のダイCは、基板202Cおよび基板202Cの一部を覆って形成された電源導体210Cを含む。ダイBの電源導体210Bは、ダイCのためのVSS電源電流が、導電性付加物225Cを使用して、ダイBの電源導体210Bを介して基板202Bを通る基板導通により担持されるようにダイCの基板202Cに導通可能に結合される。

【0027】

この例示的実施形態では、各ダイA、BおよびCがIで与えられる電源電流を引き出すものと仮定する。この電流は、外付けのVDD電源(図示せず)から、それぞれVDDボンディング・ワイヤ216A、216Bおよび216Cを介してダイA、BおよびCに向かって対応する矢印で示される方向に流れる。再度説明を簡単にするために電流は、信号リード線を介して集積回路にあるいは集積回路から流入または流出せず、電流値Iが各ダイA、BおよびCとVSS電源の間を流れると仮定する。したがって基板202Aを通る基板導通により担持される合計電流値は、矢印220Aで示されるように3Iで与えられる。同様に矢印220Bおよび220Cで示されるように、基板202Bおよび202Cを通る基板導通により担持される電流量はそれぞれ2IおよびIで与えられる。したがって底部のダイAは、ダイA、BおよびCの3つ全てのための電流を基板導通により担持する。より一般的には、積重ねダイ式集積回路では頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。P+基板の代わりにN+基板を利用する一代替実施形態では、基板電流の流れ方向が、図2の電流矢印で示される方向と対向する方向になることに注意されたい。

【0028】

図2では実装されていない(unpackaged)構成で示されているが、積重ねダイ式集積回路200を、当技術分野で周知の技術を使用して実装してもよい。例えば回路200を、図4と共に説明するタイプのフリップ・チップBGAパッケージ、あるいは積重ねダイ式集積回路に使用するのに適切なその他の任意の実装構成を使用して実装してもよい。

【0029】

図2の実施形態では、p型導通の仕組みを利用しており、その構成要素例えば基板202A、エピタキシャル層204A、p型タブ206A、およびタブ・タイ208Aはp型半導体材料から成っている。その他のタイプの導通の仕組みを使用できることを理解されたい。そのような代替導通の仕組みの例を、図5および図6と共に示し、説明する。

【0030】

図3は、積重ねダイ式集積回路300を示し、その回路は本発明の第2の例示的実施形態による基板導通を伴う。この実施形態は、集積回路のダイAおよびBを含み、各々のダイは前述の実施形態と実質上同じ構成要素のセットを含む。しかしこの実施形態では、背中合わせの構成で第2の集積回路のダイBが、第1の集積回路のダイAに積み重ねられかつ少なくとも部分的に重なり合っており、ダイAの基板202AがダイBの基板202Bに向き合っている。この実施形態では、ダイBのためのVSS電源電流は、ダイAの電源導体210Aを介して基板202Aおよび202Bを通る基板導通により担持され、その方向は電源導体210Bおよび210Aの間で垂直な矢印によって示される方向である。したがってダイAを通るVSS電源電流の流れ方向は基板202Aの表面から電源導体210Aに向かう。この方向は、図1および図2の基板導通の仕組みにおける電流の流れ方向に対向していることに注意されたい。したがってこのタイプの基板導通の仕組みを本明細書では「逆方向」基板導通と呼ぶこともある。

【0031】

この実施形態では、基板202Aと202Bは、導電性材料例えば銀エポキシの層302で互いから引き離されている。向き合っている基板間でその他の導電性材料の層または導電性の結合の仕組みを使用してもよい。半田バンプ304、306および308は、VDDボンド・パッド212A、VSS電源導体210Aおよび信号ボンド・パッド214Aとそれぞれ関連しており、例えば、このようにしなければ従来式であるBGAパッケージを使用して積重ねダイ式集積回路300を実装する際に利用される。

【0032】

この例示的実施形態では、各ダイAおよびBは、Iで与えられる電源電流を引き出すものと仮定する。この電流は、外付けのVDD電源(図示せず)から、VDDボンド・パッド212AおよびVDDボンディング・ワイヤ216Bを介してダイA、Bに向かって対応する矢印で示される方向に流れる。再度説明を簡単にするために電流は、信号リード線を介して集積回路にあるいは集積回路から流入または流出せず電流値Iが、各ダイAおよびBとVSS電源の間を流れると仮定する。基板202Aを通る基板導通により担持される合計電流値は、矢印310で示されるようにIで与えられる。より具体的には、底部のダイAは、逆方向基板導通によりダイBからの第1の電流Iを流す。VDDボンド・パッド212Aに流れ込む第2の電流Iは、ダイAの表面に形成される装置または構成要素に与えられる。これら装置または構成要素が第2の電流IをVSS電源に返す。矢印312で表される電流2Iが、第1の電流Iと第2の電流Iとの合計である。

【0033】

図3に示す基板の背中合わせ配置は、1つまたは複数の集積回路のダイを追加して、例えば図2に示すタイプの仕組みで構成された追加のダイと組み合わせて使用してもよい。したがって本発明による任意の積重ねダイ式集積回路は、図2および図3で説明した技術の組合せを使用してもよい。

【0034】

図4に示すのは、図3に示すタイプの積重ねダイ式集積回路のフリップ・チップBGAパッケージを使用した具体的な実装形態である。この実施形態では、積重ねダイ式集積回路400は、第1つまり底部の集積回路のダイ402および第2つまり頂部の集積回路のダイ404を含み、それらは図示のように積み重ねられている。底部および頂部のダイ402および404の背後はそれぞれ矢印412および414で表示されている。明らかなように、底部および頂部のダイ402および404は、図3と共に説明したタイプの構成で背中合わせに配置されている。銀エポキシまたはその他の導電性材料の層405が、底部および頂部のダイ402および404の基板を結合している。底部ダイ402は、フリップ・チップBGAパッケージの装着用構造(mounting structure)406に取り付けられ、ボンド・ワイヤ408が頂部ダイ404の上側表面に接続される。装着用構造406内の導電性トレースが、底部ダイ402の表側の導体をフリップ・チップBGAパッケージの半田ボール410に接続する。この実施形態では、VSS電流の流れ方向は、図3の実施形態のように矢印420で示されている。

【0035】

図5および図6に示す実施形態は、概して図2および図3の実施形態にそれぞれ対応する本発明の実施形態であるが、対向するタイプの導通性をもつ基板、エピタキシャル層、タブおよびタブ・タイの各要素を使用して実施されている。より具体的には、図5および図6それぞれに示す積重ねダイ式集積回路500および600の構成要素、基板202A’、エピタキシャル層204A’、タブ206A’、タブ・タイ208A’などはn型半導体材料で成り、図2および図3に示すp型半導体材料で成る構成要素に対応している。VDDおよびVSS電源への接続も逆になっており、図5および図6のボンド・パッドがVSSボンド・パッドに対応し、図5および図6の電源導体がVDDバスに対応する。その結果、例えば図5で矢印220A’、図6で矢印310’によって示される電流の流れ方向は、図2および図3に示される対応する方向に対して逆になっている。その他の点ではこれら代替実施形態の構成および動作は、前述の実施形態のものと実質的に同じである。さらに別のタイプの導通性によるこの他の仕組みを使用でき、この点に関して本発明は制約を受けない。

【0036】

図2から図6に示す具体的な積重ねダイ式の構成は、例示的の例証としてのみ提示されており、本発明の範囲をいかなる形であれ制限するとは理解すべきではないことに注意されたい。また、ある従来形の構成要素を図から削除して説明を明確かつ簡素にした。このように削除された構成要素は、当業者ならば理解するであろうが本発明の任意の実施形態に含むことができる。

【0037】

上述のように、本発明の任意の実施形態を1つまたは複数の集積回路として実施することができる。このような仕組みでは複数の同一のダイが、繰返しパターンでウェーハ表面上に形成されるのが一般的である。各ダイは、本明細書で説明したように装置を含むこともあり、その他の構造または回路を含むこともある。個々のダイは、ウェーハから刻みあるいは切り取られ、次いで集積回路として実装される。当業者ならばどのようにしてウェーハを刻み、ダイを実装して集積回路を生産するか理解しているはずである。そのようにして製造された集積回路はこの発明の部分であるものとする。

【0038】

本発明の上述の実施形態は説明のためだけのものである。当業者ならば、以下の特許請求の範囲の視野から逸脱することなく多数の代替実施形態を派生することができる。例えば、基板またはその他の半導体層あるいは領域、ボンド・パッド、ボンド・ワイヤ、積重ね配置、導電性付加物またはパッケージ・タイプなどの集積回路の構成要素に対する数多くの代替構成を使用することができる。当業者にとってこれらおよびその他の代替実施形態は、直ちに明白になるであろう。

【特許請求の範囲】

【請求項1】

第1の基板および前記第1の基板の一部分を覆って形成された第1の電源導体を有する第1の集積回路のダイと、

第2の基板および前記第2の基板の一部分を覆って形成された第2の電源導体を有する第2の集積回路のダイとを備え、

前記第2の集積回路のダイが、前記第1の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っており、

前記第1の集積回路のダイの前記第1の電源導体が、前記第2の集積回路の前記第2の基板に導通可能に結合され、

前記第2の集積回路に関連する電源電流が、前記第1の集積回路のダイの前記第1の電源導体を介して前記第2の基板を通る基板導通によって担持される、

集積回路。

【請求項2】

前記第1の集積回路のダイに関連する電源電流が、前記第1の基板を通る基板導通によって担持される請求項1に記載の集積回路。

【請求項3】

第3の基板および前記第3の基板の一部分を覆って形成された第3の電源導体を有する少なくとも1つの追加の集積回路のダイをさらに備え、前記第3の集積回路のダイが前記第2の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っている請求項1に記載の集積回路。

【請求項4】

前記第1および第2の集積回路のダイが、N個の積み上げられた集積回路のダイのうちの2つであり、ここでNは2より大きく、かつ積重ねの底部のダイを除く各ダイが、下側のダイの電源導体を介して基板導通により電源電流を担持する請求項1に記載の集積回路。

【請求項5】

前記第1の集積回路のダイの前記第1の電源導体が、前記第2の集積回路のダイの前記第2の基板に、前記第1の電源導体と前記第2の基板の間に配置された導電性付加物を介して結合されている請求項1に記載の集積回路。

【請求項6】

前記第2の集積回路のための前記電源電流が、前記第1の集積回路のダイの前記第1の電源導体を介して第2の基板を通る基板導通により担持され、VSS電源電流およびVDD電源電流の1つを含む請求項1に記載の集積回路。

【請求項7】

積み重ねて配置された複数の集積回路のダイを備え、

前記積重ねの底部のダイを除く前記各ダイが、下側のダイの電源導体を介して基板導通によりその電源電流を担持する、

集積回路。

【請求項8】

積み重ねて配置された複数の集積回路のダイを備え、

前記積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する、

集積回路。

【請求項9】

積重ねダイ式集積回路に供給電流を与えるための方法であって、前記集積回路が、少なくとも第1の集積回路のダイと第2の集積回路のダイとを備え、前記第1の集積回路のダイが、第1の基板と前記第1の基板の一部分を覆って形成された第1の電源導体とを有し、前記第2の集積回路のダイが、第2の基板と前記第2の基板の一部分を覆って形成された第2の電源導体とを有し、前記第2の集積回路のダイが前記第1の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っており、

前記第1の集積回路のダイの前記第1の電源導体を前記第2の集積回路のダイの前記第2の基板に導通可能に結合する工程と、

前記第2の集積回路のダイに関連する電源電流を前記第1の集積回路の前記第1の電源導体を介して前記第2の基板を通る基板導通により担持する工程とを備える

方法。

【請求項10】

第1の基板および前記第1の基板の一部分を覆って形成された第1の電源導体を有する第1の集積回路のダイと、

第2の基板および前記第2の基板の一部分を覆って形成された第2の電源導体を有する第2の集積回路のダイとを備え、

前記第2の集積回路のダイが、前記第1の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っており、

前記第2の集積回路のための電源電流が、前記第1の集積回路のダイの前記第1の電源導体を介して前記第1および第2の基板を通る基板導通によって担持される、

集積回路。

【請求項1】

第1の基板および前記第1の基板の一部分を覆って形成された第1の電源導体を有する第1の集積回路のダイと、

第2の基板および前記第2の基板の一部分を覆って形成された第2の電源導体を有する第2の集積回路のダイとを備え、

前記第2の集積回路のダイが、前記第1の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っており、

前記第1の集積回路のダイの前記第1の電源導体が、前記第2の集積回路の前記第2の基板に導通可能に結合され、

前記第2の集積回路に関連する電源電流が、前記第1の集積回路のダイの前記第1の電源導体を介して前記第2の基板を通る基板導通によって担持される、

集積回路。

【請求項2】

前記第1の集積回路のダイに関連する電源電流が、前記第1の基板を通る基板導通によって担持される請求項1に記載の集積回路。

【請求項3】

第3の基板および前記第3の基板の一部分を覆って形成された第3の電源導体を有する少なくとも1つの追加の集積回路のダイをさらに備え、前記第3の集積回路のダイが前記第2の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っている請求項1に記載の集積回路。

【請求項4】

前記第1および第2の集積回路のダイが、N個の積み上げられた集積回路のダイのうちの2つであり、ここでNは2より大きく、かつ積重ねの底部のダイを除く各ダイが、下側のダイの電源導体を介して基板導通により電源電流を担持する請求項1に記載の集積回路。

【請求項5】

前記第1の集積回路のダイの前記第1の電源導体が、前記第2の集積回路のダイの前記第2の基板に、前記第1の電源導体と前記第2の基板の間に配置された導電性付加物を介して結合されている請求項1に記載の集積回路。

【請求項6】

前記第2の集積回路のための前記電源電流が、前記第1の集積回路のダイの前記第1の電源導体を介して第2の基板を通る基板導通により担持され、VSS電源電流およびVDD電源電流の1つを含む請求項1に記載の集積回路。

【請求項7】

積み重ねて配置された複数の集積回路のダイを備え、

前記積重ねの底部のダイを除く前記各ダイが、下側のダイの電源導体を介して基板導通によりその電源電流を担持する、

集積回路。

【請求項8】

積み重ねて配置された複数の集積回路のダイを備え、

前記積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する、

集積回路。

【請求項9】

積重ねダイ式集積回路に供給電流を与えるための方法であって、前記集積回路が、少なくとも第1の集積回路のダイと第2の集積回路のダイとを備え、前記第1の集積回路のダイが、第1の基板と前記第1の基板の一部分を覆って形成された第1の電源導体とを有し、前記第2の集積回路のダイが、第2の基板と前記第2の基板の一部分を覆って形成された第2の電源導体とを有し、前記第2の集積回路のダイが前記第1の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っており、

前記第1の集積回路のダイの前記第1の電源導体を前記第2の集積回路のダイの前記第2の基板に導通可能に結合する工程と、

前記第2の集積回路のダイに関連する電源電流を前記第1の集積回路の前記第1の電源導体を介して前記第2の基板を通る基板導通により担持する工程とを備える

方法。

【請求項10】

第1の基板および前記第1の基板の一部分を覆って形成された第1の電源導体を有する第1の集積回路のダイと、

第2の基板および前記第2の基板の一部分を覆って形成された第2の電源導体を有する第2の集積回路のダイとを備え、

前記第2の集積回路のダイが、前記第1の集積回路のダイに積み重ねられかつ少なくとも部分的に重なり合っており、

前記第2の集積回路のための電源電流が、前記第1の集積回路のダイの前記第1の電源導体を介して前記第1および第2の基板を通る基板導通によって担持される、

集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−33981(P2013−33981A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2012−207994(P2012−207994)

【出願日】平成24年9月21日(2012.9.21)

【分割の表示】特願2005−358376(P2005−358376)の分割

【原出願日】平成17年12月13日(2005.12.13)

【出願人】(500587067)アギア システムズ インコーポレーテッド (302)

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成24年9月21日(2012.9.21)

【分割の表示】特願2005−358376(P2005−358376)の分割

【原出願日】平成17年12月13日(2005.12.13)

【出願人】(500587067)アギア システムズ インコーポレーテッド (302)

【Fターム(参考)】

[ Back to top ]