基板検査装置および基板検査方法

【課題】基板上の積層構造上のパターンの欠陥を、良好な精度で検出する基板検査装置、および基板検査方法を提供する。

【解決手段】基板上の第1の層上に該第1の層と組成の異なる第2の層が積層された積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査装置であって、前記基板上に1次電子を照射する電子放出手段と、前記1次電子の照射により生成される2次電子を検出する電子検出手段と、前記電子検出手段で検出された2次電子のデータを処理するデータ処理手段と、前記1次電子の加速電圧を制御する、電圧制御手段と、を有し、前記電圧制御手段は、前記1次電子が、前記第2の層が露出した部分で前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧を制御することを特徴とする基板検査装置。

【解決手段】基板上の第1の層上に該第1の層と組成の異なる第2の層が積層された積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査装置であって、前記基板上に1次電子を照射する電子放出手段と、前記1次電子の照射により生成される2次電子を検出する電子検出手段と、前記電子検出手段で検出された2次電子のデータを処理するデータ処理手段と、前記1次電子の加速電圧を制御する、電圧制御手段と、を有し、前記電圧制御手段は、前記1次電子が、前記第2の層が露出した部分で前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧を制御することを特徴とする基板検査装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基板上に形成されたパターンを検査する基板検査方法と、該検査方法を実施する基板検査装置に関する。

【背景技術】

【0002】

半導体装置の製造過程において、基板上に形成されたパターンの検査方法については、様々な方法が提案されていた。

【0003】

例えば、基板上に形成されたパターンに電子線を照射し、2次電子を検出することによって該パターンの欠陥を検出する、いわゆる電子線検査が提案されている。電子線検査によれば、光学的な検査にくらべてより微細な欠陥を検出することが可能であるため、近年の微細化された半導体装置のパターニングの欠陥を検出する方法として用いられている。

【特許文献1】特開2002−216698号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、電子線検査においては、実際の欠陥以外のものを欠陥と検出してしまう、いわゆる疑似欠陥検出と呼ばれる現象が起こる場合がある。特に、組成の異なる層が積層されてなる積層構造上に形成されたパターンの欠陥を検出する場合、疑似欠陥検出が発生し、欠陥検出の精度が低下してしまう場合が生じていた。

【0005】

そこで、本発明では、上記の問題を解決した、新規で有用な基板検査装置および基板検査方法を提供することを課題としている。

【0006】

本発明の具体的な課題は、基板上の積層構造上のパターンの欠陥を、良好な精度で検出する基板検査装置、および基板検査方法を提供することである。

【課題を解決するための手段】

【0007】

本発明は、上記の課題を、

請求項1に記載したように、

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査装置であって、

前記基板上に1次電子を照射する電子放出手段と、

前記1次電子の照射により生成される2次電子を検出する電子検出手段と、

前記電子検出手段で検出された2次電子の検出データを処理するデータ処理手段と、

前記1次電子の加速電圧を制御する、電圧制御手段と、を有し、

前記電圧制御手段は、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧を制御することを特徴とする基板検査装置より、また、

請求項2に記載したように、

前記1次電子の加速電圧をシミュレーションにより算出する電圧算出手段をさらに有することを特徴とする請求項1記載の基板検査装置により、また、

請求項3に記載したように、

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項1または2記載の基板検査装置により、また、

請求項4に記載したように、

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項1乃至3のうち、いずれか1項記載の基板検査装置により、また、

請求項5に記載したように、

前記第1の層が多結晶シリコンよりなることを特徴とする請求項4記載の基板検査装置により、また、

請求項6に記載したように、

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項1乃至5のうち、いずれか1項記載の基板検査装置により、また、

請求項7に記載したように、

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査方法であって、

前記基板上に1次電子を照射する電子放出工程と、

前記1次電子の照射により生成される2次電子を検出する電子検出工程と、

前記電子検出手段で検出された2次電子の検出データを処理するデータ処理工程と、を有し、

前記電子放出工程では、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧が制御されることを特徴とする基板検査方法により、また、

請求項8に記載したように、

前記1次電子の加速電圧がシミュレーションにより算出されることを特徴とする請求項7記載の基板検査方法により、また、

請求項9に記載したように、

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項7または8記載の基板検査方法により、また、

請求項10に記載したように、

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項7乃至9のうち、いずれか1項記載の基板検査方法により、また、

請求項11に記載したように、

前記第1の層が多結晶シリコンよりなることを特徴とする請求項10記載の基板検査方法により、また、

請求項12に記載したように、

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項7乃至11のうち、いずれか1項記載の基板検査方法により、解決する。

【発明の効果】

【0008】

本発明によれば、基板上の積層構造上のパターンの欠陥を、良好な精度で検出する基板検査装置、および基板検査方法を提供することが可能となる。

【発明を実施するための最良の形態】

【0009】

本発明に係る基板検査装置(基板検査方法)によれば、基板上の積層構造上に形成されたパターンの欠陥を、電子線検査により、良好な精度で検出することが可能となる。例えば、組成の異なる多層構造上に形成されたパターンは、電子線検査が困難となる場合があることを本発明の発明者は見出した。以下に、本発明の発明者が見出した電子線検査における問題とその解決方法について説明する。

【0010】

このように、電子線検査が困難となる一例として、例えば、エッチングの対象膜上に形成された、レジストパターンの検査を行う場合がある。レジストパターンの露光・現像の直後には、該レジストパターンの下層に反射防止膜(BARC)が残っていることが大半である。すなわち、エッチングの対象膜と反射防止膜との積層構造上にレジストパターンが形成されることになる。このようなレジストパターンが形成される工程を含む、半導体装置の製造の例を以下に示す。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0011】

まず、図1Aに示す工程では、シリコンよりなる基板1上にゲート絶縁膜2を形成し、さらに該ゲート絶縁膜2上に、多結晶シリコン(ポリシリコン)よりなるゲート電極層3(第1の層)を形成する。

【0012】

次に、図1Bに示す工程において、前記ゲート電極層3上に、反射防止膜(第2の層)4を形成し、該反射防止膜4上にフォトレジスト層5を形成する。

【0013】

次に、図1Cに示す工程において、前記フォトレジスト層5を、いわゆるフォトリソグラフィ法により露光・現像してパターニングし、レジストパターン5Aを形成する。ここで、前記レジスト層5が除去された領域Aでは、前記反射防止膜4が露出することになる。

【0014】

次に、図1Dに示す工程において、図1Cにおいて形成された前記レジストパターン5Aをマスクにして前記反射防止膜4のエッチング、さらに前記ゲート電極層3のエッチングを行う。この結果、前記ゲート電極層3のパターニングが実施されて、ゲート電極3Aが形成される。

【0015】

この後の工程において、前記ゲート絶縁膜2のエッチングや、不純物の打ち込み、拡散などの公知の方法を用いた工程を経て、MOSトランジスタを形成することができる。

【0016】

上記のトランジスタを形成する場合、例えば、上記の図1Cの工程の後で、前記レジストパターン5Aのパターニングの欠陥の検出が可能となることが好ましい。しかし従来は、例えばレジストパターン5Aをマスクにしたエッチングの後(図1D以降の工程で)検査が行われることが大半であった。

【0017】

一方で、エッチングの不良はレジストのパターン形成の不良に起因する場合があり、レジストのパターンが形成された時点でパターニングの不良を検出することが可能となれば、より効率よくパターニングの不良を発見することが可能となる。

【0018】

しかし、図1Cに示すように、組成の異なる前記ゲート電極層3と前記反射防止膜4との積層構造上に形成された、前記レジストパターン5Aの電子線検査は、疑似欠陥検出の問題から困難となる場合があることが見出された。また、このような疑似欠陥検出の問題は、電子線検査における1次電子の加速電圧に依存することが本発明者の発明により見出された。次に、これらについて説明する。

【0019】

図2A〜図2Cは、図1Cに示した構造における、レジストパターンの電子線検査による画像(SEM画像)を示したものである。なお、図2A〜図2Cでは、1次電子の加速電圧が異なり、加速電圧はそれぞれ、300eV、1000eV、1500eVである。

【0020】

図2A〜図2Cを参照するに、それぞれの場合において、レジストパターンの欠陥D(レジストパターンが欠落した部分)が認められる。しかし、一方で、図2Bに示した、加速電圧を1000eVとした場合のみ、レジストパターンの間(反射防止膜が露出した部分)に、黒い疑似欠陥deが多数みられる。これらの疑似欠陥deが、電子線検査の検査方法(検査装置)上の問題により発生する疑似欠陥であることは、別途行った電気特性の検査により、確認されている。

【0021】

図3は、上記の疑似欠陥の検出数と、加速電圧の関係を示した図である。図3を参照するに、加速電圧と疑似欠陥検出数には相関関係があり、所定の加速電圧の領域(例えば800〜1000eV程度)において特に疑似欠陥数が著しく増大していることが分かる。すなわち、上記の所定の加速電圧の領域に比べて加速電圧が低い場合や、または加速電圧が高い場合には、疑似欠陥の検出数は少なくなっている。

【0022】

このように、所定の加速電圧において疑似欠陥の検出数が増大することは、検査対象であるパターンの下地の層の影響であることが以下の検証により明らかになった。

【0023】

図4Aは、ポリシリコンの表面モホロジーを示すSEM画像であり、図4Bは、図4Aのポリシリコン上に反射防止膜とレジストパターンを形成した状態(図1Cに示した状態)のSEM画像である。

【0024】

図4Aを参照するに、ポリシリコンの表面モホロジーは、グレイン状の凹凸形状となっていることがわかる。この場合、ポリシリコンのRa表面荒さは、5.7nmである。

【0025】

また、図4Bを参照するに、先に説明したように、レジストパターンの間の反射防止膜には、疑似欠陥deが多数認められる。したがってこのような疑似欠陥は、下地のポリシリコンの表面モホロジーが関連していると考えられた。

【0026】

そこで、ポリシリコンの表面モホロジーが異なる場合について、同様のパターンを形成し、電子線検査を行った。図5Aは、図4Aの場合と異なる表面荒さを有するポリシリコンの表面モホロジーを示すSEM画像であり、図5Bは、図5Aのポリシリコン上に反射防止膜とレジストパターンを形成した状態(図1Cに示した状態)のSEM画像である。

【0027】

図5Aを参照するに、ポリシリコンの表面モホロジーは、図4Aの場合と比べてグレイン状の凹凸形状が小さくなっている。この場合、ポリシリコンのRa表面荒さは、0.9nmである。

【0028】

また、図5Bを参照するに、本図に示す場合、図4Aでみられたような疑似欠陥deは殆ど認められていない。したがって、図4Bにみられた疑似欠陥は、下地のポリシリコンの表面モホロジーが寄与していることが明らかとなった。

【0029】

上記の結果を鑑みると、電子線検査により所定の加速電圧において疑似欠陥の検出数が著しく増大する理由は、以下のモデルによって説明される。

【0030】

図6A、図6Bは、図1Cに示した構造の電子線検査における、露出した前記反射防止膜4(図1Cの領域A)に入射する1次電子の挙動を模式的に示した図である。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する。また、図6Aは、疑似欠陥検出数が多い場合(例えば上記の例で加速電圧800eV〜1000eV程度)を、図6Bは、疑似欠陥検出数が少ない場合(加速電圧が所定の値より小さい場合、または所定の値より大きい場合)を示している。

【0031】

図6Aを参照するに、本図に示す場合、1次電子は、前記ゲート電極層(第1の層)3と、前記反射防止膜(第2の層)4の界面近傍に多く到達する。そのため、当該第1の層で多くの1次電子が反射されると考えられる。

【0032】

すなわち、2次電子を検出することでパターンの欠陥を検出する場合に、上記の、界面で反射した1次電子の影響を受けてしまい、これが疑似欠陥として検出されると考えられる。このような現象は、特に第1の層と第2の層の組成が異なる場合に起こると考えられ、第1の層と第2の層の密度差が大きい場合により生じやすいと考えられれる。

【0033】

例えば、図1Cに示した構造においては、第1の層がポリシリコンよりなる無機物の層(無機層)であり、第2の層が反射防止膜よりなる有機物の層(有機層)である。このため、当該第2の層の密度が第1の層に比べて著しく小さく電子が透過しやすいため、上記の現象が起こりやすいと考えられる。

【0034】

一方で、図6Bに示したように、1次電子の加速電圧を所定の値以下に小さくするか、または所定の値以上に大きくすると、2次電子の検出において、1次電子が第1の層と第2の層の界面近傍で反射する影響を受けることが少なくなる。

【0035】

すなわち、1次電子の到達深さは加速電圧に依存するため、該加速電圧が疑似欠陥検出が少なくなるように制御されることが好ましい。この場合、加速電圧は、露出する第2の層(領域A)に照射される1次電子が、第1の層と第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように制御されることが好ましい。この場合に、疑似欠陥検出数が少なくなり、良好な精度でパターンの欠陥検出を行うことが可能になる。

【0036】

この場合、「界面近傍」とは、1次電子が第1の層の表面モホロジーの影響を受ける領域であり、第1の層のモホロジーの中心線を中心として、少なくとも表面荒さRa程度の厚みを持つものと考えられる。

【0037】

また、この場合加速電圧の下限は、少なくとも1次電子が第1の層に浸透することが可能となる程度の電圧であり、上限は、1次電子が第2の層を透過しない程度であることが好ましい。モンテカルロシミュレーションにより、容易に算出することが可能である。

【0038】

図7は、シミュレーションにより、図1Cの領域Aにおいて、1次電子が到達する深さと、当該深さに存在する電子の割合を求めた結果を示す図である。

【0039】

図7を参照するに、例えば、加速電圧が800eVの場合、1次電子は、第1の層と第2の層の界面近傍に多く存在することがわかる。一方で、加速電圧が300eVの場合には1次電子はその殆どが第2の層(反射防止膜、図中BARCと表記)の界面近傍以外の浅い部分までしか到達していないことがわかる。また、加速電圧を1500eVとした場合には、1次電子の多くは第1の層(ポリシリコン)にまで到達していることがわかる。

【0040】

図7のシミュレーションの結果は、図2A〜2C、図3に示した結果と、図6A、6Bの疑似欠陥検出のモデルとよく一致している。

【0041】

このように、シミュレーションにより1次電子の到達深さが算出されると、1次電子が、第1の層と第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するための加速電圧は容易にもとめられる。

【0042】

次に、上記の原理を用いた基板検査装置、および該基板検査装置を用いた基板検査方法について説明する。

【実施例1】

【0043】

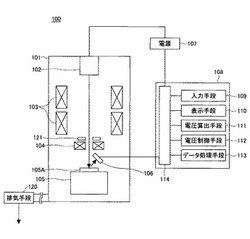

図8は、上記の原理を用いた基板検査装置の一例である、基板検査装置100を模式的に示した図である。

【0044】

図8を参照するに、本実施例による基板検査装置100は、排気手段120によって内部が真空排気されて減圧空間となる真空容器101を有している。前記真空容器101の内部には、検査対象となる基板105A(図1Cの基板1に相当)を保持する基板保持台105が設置され、該基板保持台105に対向するように、当該基板105に1次電子を照射する電子放出部102が設置されている。

【0045】

また、前記電子放出部102と前記基板保持台105の間には、放出された1次電子(電子線)を集束するための集束レンズ103と、1次電子を走査するための走査コイル104、およびアパーチャ121が設置されている。さらに、前記基板保持台105と前記走査コイル104の間には、1次電子の照射によって生成される2次電子を検出する電子検出手段106が設置されている。

【0046】

また、前記電子放出部102には、該電子放出部102に電圧を印加するための電源107が接続されている。前記電源107は、基板検査装置の動作を制御する制御装置(コンピュータ)108のバス114に接続されている。また、当該制御装置108(バス114)には、前記電子検出手段106も接続されている。

【0047】

前記制御装置108は、例えばキーボードや、または通信手段などの入力手段109と、モニタ画面などの表示手段110、前記電源107により印加される加速電圧を算出する電圧算出手段111、前記電源107を制御する電圧制御手段112、および前記電子検出手段106により検出された2次電子のデータを処理するデータ処理手段113が、バス114に接続された構造を有している。

【0048】

前記電子放出手段102には、前記電源107から電圧が印加されるが、この電圧は、前記電圧算出手段111によって、モンテカルロシミュレーションにより算出される。当該電圧算出手段によって算出された電圧に対応して、前記電圧制御手段112が前記電源107を制御し、1次電子の加速電圧を制御する。

【0049】

前記電子放出手段102から放出された電子は、検査対象である基板105に照射される。前記基板105は、例えば、図1Cに示した構造を有している。すなわち、基板105(基板1)上には積層構造が形成されている。該積層構造は、第1の層(前記ゲート電極層3)上に該第1の層と組成の異なる第2の層(前記反射防止膜4)が積層されてなる。さらに、当該積層構造上に、該第2の層が一部露出する(領域A)ようにパターン(レジストパターン5A)が形成されている。照射された1次電子によって生成される2次電子は、前記電子検出手段106によって検出され、前記データ処理手段113によってパターンの欠陥が検出(認識)される。

【0050】

ここで、照射される1次電子の加速電圧は、前記電圧制御手段112によって制御される。この場合、当該加速電圧は、露出する前記第2の層(図1Cの領域A)に照射される1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように制御される(図6Bに図示)。

【0051】

この結果、先に説明したように、1次電子の当該界面近傍での反射による疑似欠陥検出の影響(図6Aに図示)が抑制され、良好な精度でパターン(図1Cのレジストパターン5A)の欠陥を検出することが可能となる。

【0052】

また、この場合、前記加速電圧は、前記電圧算出手段111により、モンテカルロシミュレーションにより算出されるとさらに好適である。

【0053】

図9は、上記のモンテカルロシミュレーションに用いるパラメータを示した図である。当該モンテカルロシミュレーションでは、上記の第1の層(例えばポリシリコン)の、密度M1、質量S1、および膜厚T1と、第2の層(例えば反射防止膜、BARC)の密度M2、質量S2、および膜厚T2から、1次電子が前記界面近傍以外の第1の層または第2の層の中に到達するような加速電圧を算出する。

【0054】

上記のモンテカルロシミュレーションでは、弾性散乱と非弾性散乱を繰り返しながら進行する1次電子の挙動を考慮し、所定の到達深さとなるような加速電圧をもとめることができる。

【0055】

次に、上記の図8の基板検査装置100を用いた基板検査方法の一例について、図1Cに示した構造を検査する場合を例にとって、図10のフローチャートに基づき、説明する。なお、以下の文中では先に説明した部位には同一の参照符号を用い、説明を省略する場合がある。

【0056】

まず、ステップ1(図中S1と表記、以下同様)において、前記入力手段109より、M1、M2、S1、S2、T1、T2が入力される。

【0057】

次に、ステップ2において、前記電圧算出手段111によって、1次電子の加速電圧V1(eV)が算出される。この場合、前記加速電圧V1は、1次電子が、第1の層(前記ゲート電極層3)と第2の層(前記反射防止膜4)の界面近傍以外の、前記第1の層または前記第2の層の中に到達するような値となるようにシミュレーションにより算出される。

【0058】

次に、ステップ3において、前記電子放出手段102から放出される1次電子の加速電圧がV1となるように、前記電圧制御手段112により、前記電源107が制御され、1次電子が放出されて、基板上に照射される。この場合、1次電子は、第1の層と第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達し、2次電子が生成される。

【0059】

次に、ステップ4において、上記の1次電子に起因して生成される2次電子が、前記電子検出手段106によって検出される。該電子検出手段106によって検出された2次電子の検出データは、前記データ処理手段113によって処理され、前記レジストパターン5Aの欠陥が、良好な精度で検出される。これは、先に説明したように、加速電圧が最適化されて疑似欠陥検出の影響が抑制されているためである。

【0060】

また、上記の実施例では、ゲート電極のパターニングの場合を例にとって説明したが、本発明による基板検査装置、および基板検査方法はこれに限定されるものではない。例えば、上記の構造以外でも、組成や密度の異なる積層構造上の微細パターンの欠陥を、効率よく検出することが可能である。また、本実施例による基板検査装置、または基板検査方法では、従来の光学的な検査方法にくらべて微細なパターンの欠陥検出が可能である。例えば、本実施例による基板検査装置では、hp(ハーフピッチ)65nm世代でのレジストパターンの、40nmの微細な欠陥を検出することが可能である。

【0061】

以上、本発明を好ましい実施例について説明したが、本発明は上記の特定の実施例に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【産業上の利用可能性】

【0062】

本発明によれば、基板上の積層構造上のパターンの欠陥を、良好な精度で検出する基板検査装置、および基板検査方法を提供することが可能となる。

【図面の簡単な説明】

【0063】

【図1A】半導体装置の製造方法を示す図(その1)である。

【図1B】半導体装置の製造方法を示す図(その2)である。

【図1C】半導体装置の製造方法を示す図(その3)である。

【図1D】半導体装置の製造方法を示す図(その4)である。

【図2A】パターンの欠陥を可視化した図(その1)である。

【図2B】パターンの欠陥を可視化した図(その2)である。

【図2C】パターンの欠陥を可視化した図(その3)である。

【図3】加速電圧と疑似欠陥検出数の関係を示す図である。

【図4A】ポリシリコンの表面モホロジーを示す図(その1)である。

【図4B】図4Aのポリシリコン上に発生した欠陥を示す図である。

【図5A】ポリシリコンの表面モホロジーを示す図(その2)である。

【図5B】図5Aのポリシリコン上に発生した欠陥を示す図である。

【図6A】欠陥検出の原理を模式的に示した図(その1)である。

【図6B】欠陥検出の原理を模式的に示した図(その2)である。

【図7】シミュレーションにより求めた1次電子到達深さ示す図である。

【図8】実施例1による基板検査装置を模式的に示す図である。

【図9】入力パラメータを示す図である。

【図10】実施例1による基板検査方法を示す図である。

【符号の説明】

【0064】

1 基板

2 ゲート絶縁膜

3 ゲート電極層

3A ゲート電極

4 反射防止膜

5 フォトレジスト層

5A レジストパターン

100 基板検査装置

101 真空容器

102 電子放出部

103 集束レンズ

104 走査コイル

105 基板保持台

105A 基板

106 電子検出部

107 電源

108 コンピュータ

109 入力手段

110 表示手段

111 電圧算出手段

112 電圧制御手段

113 データ処理手段

【技術分野】

【0001】

本発明は、基板上に形成されたパターンを検査する基板検査方法と、該検査方法を実施する基板検査装置に関する。

【背景技術】

【0002】

半導体装置の製造過程において、基板上に形成されたパターンの検査方法については、様々な方法が提案されていた。

【0003】

例えば、基板上に形成されたパターンに電子線を照射し、2次電子を検出することによって該パターンの欠陥を検出する、いわゆる電子線検査が提案されている。電子線検査によれば、光学的な検査にくらべてより微細な欠陥を検出することが可能であるため、近年の微細化された半導体装置のパターニングの欠陥を検出する方法として用いられている。

【特許文献1】特開2002−216698号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、電子線検査においては、実際の欠陥以外のものを欠陥と検出してしまう、いわゆる疑似欠陥検出と呼ばれる現象が起こる場合がある。特に、組成の異なる層が積層されてなる積層構造上に形成されたパターンの欠陥を検出する場合、疑似欠陥検出が発生し、欠陥検出の精度が低下してしまう場合が生じていた。

【0005】

そこで、本発明では、上記の問題を解決した、新規で有用な基板検査装置および基板検査方法を提供することを課題としている。

【0006】

本発明の具体的な課題は、基板上の積層構造上のパターンの欠陥を、良好な精度で検出する基板検査装置、および基板検査方法を提供することである。

【課題を解決するための手段】

【0007】

本発明は、上記の課題を、

請求項1に記載したように、

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査装置であって、

前記基板上に1次電子を照射する電子放出手段と、

前記1次電子の照射により生成される2次電子を検出する電子検出手段と、

前記電子検出手段で検出された2次電子の検出データを処理するデータ処理手段と、

前記1次電子の加速電圧を制御する、電圧制御手段と、を有し、

前記電圧制御手段は、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧を制御することを特徴とする基板検査装置より、また、

請求項2に記載したように、

前記1次電子の加速電圧をシミュレーションにより算出する電圧算出手段をさらに有することを特徴とする請求項1記載の基板検査装置により、また、

請求項3に記載したように、

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項1または2記載の基板検査装置により、また、

請求項4に記載したように、

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項1乃至3のうち、いずれか1項記載の基板検査装置により、また、

請求項5に記載したように、

前記第1の層が多結晶シリコンよりなることを特徴とする請求項4記載の基板検査装置により、また、

請求項6に記載したように、

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項1乃至5のうち、いずれか1項記載の基板検査装置により、また、

請求項7に記載したように、

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査方法であって、

前記基板上に1次電子を照射する電子放出工程と、

前記1次電子の照射により生成される2次電子を検出する電子検出工程と、

前記電子検出手段で検出された2次電子の検出データを処理するデータ処理工程と、を有し、

前記電子放出工程では、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧が制御されることを特徴とする基板検査方法により、また、

請求項8に記載したように、

前記1次電子の加速電圧がシミュレーションにより算出されることを特徴とする請求項7記載の基板検査方法により、また、

請求項9に記載したように、

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項7または8記載の基板検査方法により、また、

請求項10に記載したように、

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項7乃至9のうち、いずれか1項記載の基板検査方法により、また、

請求項11に記載したように、

前記第1の層が多結晶シリコンよりなることを特徴とする請求項10記載の基板検査方法により、また、

請求項12に記載したように、

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項7乃至11のうち、いずれか1項記載の基板検査方法により、解決する。

【発明の効果】

【0008】

本発明によれば、基板上の積層構造上のパターンの欠陥を、良好な精度で検出する基板検査装置、および基板検査方法を提供することが可能となる。

【発明を実施するための最良の形態】

【0009】

本発明に係る基板検査装置(基板検査方法)によれば、基板上の積層構造上に形成されたパターンの欠陥を、電子線検査により、良好な精度で検出することが可能となる。例えば、組成の異なる多層構造上に形成されたパターンは、電子線検査が困難となる場合があることを本発明の発明者は見出した。以下に、本発明の発明者が見出した電子線検査における問題とその解決方法について説明する。

【0010】

このように、電子線検査が困難となる一例として、例えば、エッチングの対象膜上に形成された、レジストパターンの検査を行う場合がある。レジストパターンの露光・現像の直後には、該レジストパターンの下層に反射防止膜(BARC)が残っていることが大半である。すなわち、エッチングの対象膜と反射防止膜との積層構造上にレジストパターンが形成されることになる。このようなレジストパターンが形成される工程を含む、半導体装置の製造の例を以下に示す。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0011】

まず、図1Aに示す工程では、シリコンよりなる基板1上にゲート絶縁膜2を形成し、さらに該ゲート絶縁膜2上に、多結晶シリコン(ポリシリコン)よりなるゲート電極層3(第1の層)を形成する。

【0012】

次に、図1Bに示す工程において、前記ゲート電極層3上に、反射防止膜(第2の層)4を形成し、該反射防止膜4上にフォトレジスト層5を形成する。

【0013】

次に、図1Cに示す工程において、前記フォトレジスト層5を、いわゆるフォトリソグラフィ法により露光・現像してパターニングし、レジストパターン5Aを形成する。ここで、前記レジスト層5が除去された領域Aでは、前記反射防止膜4が露出することになる。

【0014】

次に、図1Dに示す工程において、図1Cにおいて形成された前記レジストパターン5Aをマスクにして前記反射防止膜4のエッチング、さらに前記ゲート電極層3のエッチングを行う。この結果、前記ゲート電極層3のパターニングが実施されて、ゲート電極3Aが形成される。

【0015】

この後の工程において、前記ゲート絶縁膜2のエッチングや、不純物の打ち込み、拡散などの公知の方法を用いた工程を経て、MOSトランジスタを形成することができる。

【0016】

上記のトランジスタを形成する場合、例えば、上記の図1Cの工程の後で、前記レジストパターン5Aのパターニングの欠陥の検出が可能となることが好ましい。しかし従来は、例えばレジストパターン5Aをマスクにしたエッチングの後(図1D以降の工程で)検査が行われることが大半であった。

【0017】

一方で、エッチングの不良はレジストのパターン形成の不良に起因する場合があり、レジストのパターンが形成された時点でパターニングの不良を検出することが可能となれば、より効率よくパターニングの不良を発見することが可能となる。

【0018】

しかし、図1Cに示すように、組成の異なる前記ゲート電極層3と前記反射防止膜4との積層構造上に形成された、前記レジストパターン5Aの電子線検査は、疑似欠陥検出の問題から困難となる場合があることが見出された。また、このような疑似欠陥検出の問題は、電子線検査における1次電子の加速電圧に依存することが本発明者の発明により見出された。次に、これらについて説明する。

【0019】

図2A〜図2Cは、図1Cに示した構造における、レジストパターンの電子線検査による画像(SEM画像)を示したものである。なお、図2A〜図2Cでは、1次電子の加速電圧が異なり、加速電圧はそれぞれ、300eV、1000eV、1500eVである。

【0020】

図2A〜図2Cを参照するに、それぞれの場合において、レジストパターンの欠陥D(レジストパターンが欠落した部分)が認められる。しかし、一方で、図2Bに示した、加速電圧を1000eVとした場合のみ、レジストパターンの間(反射防止膜が露出した部分)に、黒い疑似欠陥deが多数みられる。これらの疑似欠陥deが、電子線検査の検査方法(検査装置)上の問題により発生する疑似欠陥であることは、別途行った電気特性の検査により、確認されている。

【0021】

図3は、上記の疑似欠陥の検出数と、加速電圧の関係を示した図である。図3を参照するに、加速電圧と疑似欠陥検出数には相関関係があり、所定の加速電圧の領域(例えば800〜1000eV程度)において特に疑似欠陥数が著しく増大していることが分かる。すなわち、上記の所定の加速電圧の領域に比べて加速電圧が低い場合や、または加速電圧が高い場合には、疑似欠陥の検出数は少なくなっている。

【0022】

このように、所定の加速電圧において疑似欠陥の検出数が増大することは、検査対象であるパターンの下地の層の影響であることが以下の検証により明らかになった。

【0023】

図4Aは、ポリシリコンの表面モホロジーを示すSEM画像であり、図4Bは、図4Aのポリシリコン上に反射防止膜とレジストパターンを形成した状態(図1Cに示した状態)のSEM画像である。

【0024】

図4Aを参照するに、ポリシリコンの表面モホロジーは、グレイン状の凹凸形状となっていることがわかる。この場合、ポリシリコンのRa表面荒さは、5.7nmである。

【0025】

また、図4Bを参照するに、先に説明したように、レジストパターンの間の反射防止膜には、疑似欠陥deが多数認められる。したがってこのような疑似欠陥は、下地のポリシリコンの表面モホロジーが関連していると考えられた。

【0026】

そこで、ポリシリコンの表面モホロジーが異なる場合について、同様のパターンを形成し、電子線検査を行った。図5Aは、図4Aの場合と異なる表面荒さを有するポリシリコンの表面モホロジーを示すSEM画像であり、図5Bは、図5Aのポリシリコン上に反射防止膜とレジストパターンを形成した状態(図1Cに示した状態)のSEM画像である。

【0027】

図5Aを参照するに、ポリシリコンの表面モホロジーは、図4Aの場合と比べてグレイン状の凹凸形状が小さくなっている。この場合、ポリシリコンのRa表面荒さは、0.9nmである。

【0028】

また、図5Bを参照するに、本図に示す場合、図4Aでみられたような疑似欠陥deは殆ど認められていない。したがって、図4Bにみられた疑似欠陥は、下地のポリシリコンの表面モホロジーが寄与していることが明らかとなった。

【0029】

上記の結果を鑑みると、電子線検査により所定の加速電圧において疑似欠陥の検出数が著しく増大する理由は、以下のモデルによって説明される。

【0030】

図6A、図6Bは、図1Cに示した構造の電子線検査における、露出した前記反射防止膜4(図1Cの領域A)に入射する1次電子の挙動を模式的に示した図である。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する。また、図6Aは、疑似欠陥検出数が多い場合(例えば上記の例で加速電圧800eV〜1000eV程度)を、図6Bは、疑似欠陥検出数が少ない場合(加速電圧が所定の値より小さい場合、または所定の値より大きい場合)を示している。

【0031】

図6Aを参照するに、本図に示す場合、1次電子は、前記ゲート電極層(第1の層)3と、前記反射防止膜(第2の層)4の界面近傍に多く到達する。そのため、当該第1の層で多くの1次電子が反射されると考えられる。

【0032】

すなわち、2次電子を検出することでパターンの欠陥を検出する場合に、上記の、界面で反射した1次電子の影響を受けてしまい、これが疑似欠陥として検出されると考えられる。このような現象は、特に第1の層と第2の層の組成が異なる場合に起こると考えられ、第1の層と第2の層の密度差が大きい場合により生じやすいと考えられれる。

【0033】

例えば、図1Cに示した構造においては、第1の層がポリシリコンよりなる無機物の層(無機層)であり、第2の層が反射防止膜よりなる有機物の層(有機層)である。このため、当該第2の層の密度が第1の層に比べて著しく小さく電子が透過しやすいため、上記の現象が起こりやすいと考えられる。

【0034】

一方で、図6Bに示したように、1次電子の加速電圧を所定の値以下に小さくするか、または所定の値以上に大きくすると、2次電子の検出において、1次電子が第1の層と第2の層の界面近傍で反射する影響を受けることが少なくなる。

【0035】

すなわち、1次電子の到達深さは加速電圧に依存するため、該加速電圧が疑似欠陥検出が少なくなるように制御されることが好ましい。この場合、加速電圧は、露出する第2の層(領域A)に照射される1次電子が、第1の層と第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように制御されることが好ましい。この場合に、疑似欠陥検出数が少なくなり、良好な精度でパターンの欠陥検出を行うことが可能になる。

【0036】

この場合、「界面近傍」とは、1次電子が第1の層の表面モホロジーの影響を受ける領域であり、第1の層のモホロジーの中心線を中心として、少なくとも表面荒さRa程度の厚みを持つものと考えられる。

【0037】

また、この場合加速電圧の下限は、少なくとも1次電子が第1の層に浸透することが可能となる程度の電圧であり、上限は、1次電子が第2の層を透過しない程度であることが好ましい。モンテカルロシミュレーションにより、容易に算出することが可能である。

【0038】

図7は、シミュレーションにより、図1Cの領域Aにおいて、1次電子が到達する深さと、当該深さに存在する電子の割合を求めた結果を示す図である。

【0039】

図7を参照するに、例えば、加速電圧が800eVの場合、1次電子は、第1の層と第2の層の界面近傍に多く存在することがわかる。一方で、加速電圧が300eVの場合には1次電子はその殆どが第2の層(反射防止膜、図中BARCと表記)の界面近傍以外の浅い部分までしか到達していないことがわかる。また、加速電圧を1500eVとした場合には、1次電子の多くは第1の層(ポリシリコン)にまで到達していることがわかる。

【0040】

図7のシミュレーションの結果は、図2A〜2C、図3に示した結果と、図6A、6Bの疑似欠陥検出のモデルとよく一致している。

【0041】

このように、シミュレーションにより1次電子の到達深さが算出されると、1次電子が、第1の層と第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するための加速電圧は容易にもとめられる。

【0042】

次に、上記の原理を用いた基板検査装置、および該基板検査装置を用いた基板検査方法について説明する。

【実施例1】

【0043】

図8は、上記の原理を用いた基板検査装置の一例である、基板検査装置100を模式的に示した図である。

【0044】

図8を参照するに、本実施例による基板検査装置100は、排気手段120によって内部が真空排気されて減圧空間となる真空容器101を有している。前記真空容器101の内部には、検査対象となる基板105A(図1Cの基板1に相当)を保持する基板保持台105が設置され、該基板保持台105に対向するように、当該基板105に1次電子を照射する電子放出部102が設置されている。

【0045】

また、前記電子放出部102と前記基板保持台105の間には、放出された1次電子(電子線)を集束するための集束レンズ103と、1次電子を走査するための走査コイル104、およびアパーチャ121が設置されている。さらに、前記基板保持台105と前記走査コイル104の間には、1次電子の照射によって生成される2次電子を検出する電子検出手段106が設置されている。

【0046】

また、前記電子放出部102には、該電子放出部102に電圧を印加するための電源107が接続されている。前記電源107は、基板検査装置の動作を制御する制御装置(コンピュータ)108のバス114に接続されている。また、当該制御装置108(バス114)には、前記電子検出手段106も接続されている。

【0047】

前記制御装置108は、例えばキーボードや、または通信手段などの入力手段109と、モニタ画面などの表示手段110、前記電源107により印加される加速電圧を算出する電圧算出手段111、前記電源107を制御する電圧制御手段112、および前記電子検出手段106により検出された2次電子のデータを処理するデータ処理手段113が、バス114に接続された構造を有している。

【0048】

前記電子放出手段102には、前記電源107から電圧が印加されるが、この電圧は、前記電圧算出手段111によって、モンテカルロシミュレーションにより算出される。当該電圧算出手段によって算出された電圧に対応して、前記電圧制御手段112が前記電源107を制御し、1次電子の加速電圧を制御する。

【0049】

前記電子放出手段102から放出された電子は、検査対象である基板105に照射される。前記基板105は、例えば、図1Cに示した構造を有している。すなわち、基板105(基板1)上には積層構造が形成されている。該積層構造は、第1の層(前記ゲート電極層3)上に該第1の層と組成の異なる第2の層(前記反射防止膜4)が積層されてなる。さらに、当該積層構造上に、該第2の層が一部露出する(領域A)ようにパターン(レジストパターン5A)が形成されている。照射された1次電子によって生成される2次電子は、前記電子検出手段106によって検出され、前記データ処理手段113によってパターンの欠陥が検出(認識)される。

【0050】

ここで、照射される1次電子の加速電圧は、前記電圧制御手段112によって制御される。この場合、当該加速電圧は、露出する前記第2の層(図1Cの領域A)に照射される1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように制御される(図6Bに図示)。

【0051】

この結果、先に説明したように、1次電子の当該界面近傍での反射による疑似欠陥検出の影響(図6Aに図示)が抑制され、良好な精度でパターン(図1Cのレジストパターン5A)の欠陥を検出することが可能となる。

【0052】

また、この場合、前記加速電圧は、前記電圧算出手段111により、モンテカルロシミュレーションにより算出されるとさらに好適である。

【0053】

図9は、上記のモンテカルロシミュレーションに用いるパラメータを示した図である。当該モンテカルロシミュレーションでは、上記の第1の層(例えばポリシリコン)の、密度M1、質量S1、および膜厚T1と、第2の層(例えば反射防止膜、BARC)の密度M2、質量S2、および膜厚T2から、1次電子が前記界面近傍以外の第1の層または第2の層の中に到達するような加速電圧を算出する。

【0054】

上記のモンテカルロシミュレーションでは、弾性散乱と非弾性散乱を繰り返しながら進行する1次電子の挙動を考慮し、所定の到達深さとなるような加速電圧をもとめることができる。

【0055】

次に、上記の図8の基板検査装置100を用いた基板検査方法の一例について、図1Cに示した構造を検査する場合を例にとって、図10のフローチャートに基づき、説明する。なお、以下の文中では先に説明した部位には同一の参照符号を用い、説明を省略する場合がある。

【0056】

まず、ステップ1(図中S1と表記、以下同様)において、前記入力手段109より、M1、M2、S1、S2、T1、T2が入力される。

【0057】

次に、ステップ2において、前記電圧算出手段111によって、1次電子の加速電圧V1(eV)が算出される。この場合、前記加速電圧V1は、1次電子が、第1の層(前記ゲート電極層3)と第2の層(前記反射防止膜4)の界面近傍以外の、前記第1の層または前記第2の層の中に到達するような値となるようにシミュレーションにより算出される。

【0058】

次に、ステップ3において、前記電子放出手段102から放出される1次電子の加速電圧がV1となるように、前記電圧制御手段112により、前記電源107が制御され、1次電子が放出されて、基板上に照射される。この場合、1次電子は、第1の層と第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達し、2次電子が生成される。

【0059】

次に、ステップ4において、上記の1次電子に起因して生成される2次電子が、前記電子検出手段106によって検出される。該電子検出手段106によって検出された2次電子の検出データは、前記データ処理手段113によって処理され、前記レジストパターン5Aの欠陥が、良好な精度で検出される。これは、先に説明したように、加速電圧が最適化されて疑似欠陥検出の影響が抑制されているためである。

【0060】

また、上記の実施例では、ゲート電極のパターニングの場合を例にとって説明したが、本発明による基板検査装置、および基板検査方法はこれに限定されるものではない。例えば、上記の構造以外でも、組成や密度の異なる積層構造上の微細パターンの欠陥を、効率よく検出することが可能である。また、本実施例による基板検査装置、または基板検査方法では、従来の光学的な検査方法にくらべて微細なパターンの欠陥検出が可能である。例えば、本実施例による基板検査装置では、hp(ハーフピッチ)65nm世代でのレジストパターンの、40nmの微細な欠陥を検出することが可能である。

【0061】

以上、本発明を好ましい実施例について説明したが、本発明は上記の特定の実施例に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【産業上の利用可能性】

【0062】

本発明によれば、基板上の積層構造上のパターンの欠陥を、良好な精度で検出する基板検査装置、および基板検査方法を提供することが可能となる。

【図面の簡単な説明】

【0063】

【図1A】半導体装置の製造方法を示す図(その1)である。

【図1B】半導体装置の製造方法を示す図(その2)である。

【図1C】半導体装置の製造方法を示す図(その3)である。

【図1D】半導体装置の製造方法を示す図(その4)である。

【図2A】パターンの欠陥を可視化した図(その1)である。

【図2B】パターンの欠陥を可視化した図(その2)である。

【図2C】パターンの欠陥を可視化した図(その3)である。

【図3】加速電圧と疑似欠陥検出数の関係を示す図である。

【図4A】ポリシリコンの表面モホロジーを示す図(その1)である。

【図4B】図4Aのポリシリコン上に発生した欠陥を示す図である。

【図5A】ポリシリコンの表面モホロジーを示す図(その2)である。

【図5B】図5Aのポリシリコン上に発生した欠陥を示す図である。

【図6A】欠陥検出の原理を模式的に示した図(その1)である。

【図6B】欠陥検出の原理を模式的に示した図(その2)である。

【図7】シミュレーションにより求めた1次電子到達深さ示す図である。

【図8】実施例1による基板検査装置を模式的に示す図である。

【図9】入力パラメータを示す図である。

【図10】実施例1による基板検査方法を示す図である。

【符号の説明】

【0064】

1 基板

2 ゲート絶縁膜

3 ゲート電極層

3A ゲート電極

4 反射防止膜

5 フォトレジスト層

5A レジストパターン

100 基板検査装置

101 真空容器

102 電子放出部

103 集束レンズ

104 走査コイル

105 基板保持台

105A 基板

106 電子検出部

107 電源

108 コンピュータ

109 入力手段

110 表示手段

111 電圧算出手段

112 電圧制御手段

113 データ処理手段

【特許請求の範囲】

【請求項1】

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査装置であって、

前記基板上に1次電子を照射する電子放出手段と、

前記1次電子の照射により生成される2次電子を検出する電子検出手段と、

前記電子検出手段で検出された2次電子の検出データを処理するデータ処理手段と、

前記1次電子の加速電圧を制御する、電圧制御手段と、を有し、

前記電圧制御手段は、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧を制御することを特徴とする基板検査装置。

【請求項2】

前記1次電子の加速電圧をシミュレーションにより算出する電圧算出手段をさらに有することを特徴とする請求項1記載の基板検査装置。

【請求項3】

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項1または2記載の基板検査装置。

【請求項4】

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項1乃至3のうち、いずれか1項記載の基板検査装置。

【請求項5】

前記第1の層が多結晶シリコンよりなることを特徴とする請求項4記載の基板検査装置。

【請求項6】

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項1乃至5のうち、いずれか1項記載の基板検査装置。

【請求項7】

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査方法であって、

前記基板上に1次電子を照射する電子放出工程と、

前記1次電子の照射により生成される2次電子を検出する電子検出工程と、

前記電子検出工程で検出された2次電子の検出データを処理するデータ処理工程と、を有し、

前記電子放出工程では、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧が制御されることを特徴とする基板検査方法。

【請求項8】

前記1次電子の加速電圧がシミュレーションにより算出されることを特徴とする請求項7記載の基板検査方法。

【請求項9】

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項7または8記載の基板検査方法。

【請求項10】

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項7乃至9のうち、いずれか1項記載の基板検査方法。

【請求項11】

前記第1の層が多結晶シリコンよりなることを特徴とする請求項10記載の基板検査方法。

【請求項12】

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項7乃至11のうち、いずれか1項記載の基板検査方法。

【請求項1】

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査装置であって、

前記基板上に1次電子を照射する電子放出手段と、

前記1次電子の照射により生成される2次電子を検出する電子検出手段と、

前記電子検出手段で検出された2次電子の検出データを処理するデータ処理手段と、

前記1次電子の加速電圧を制御する、電圧制御手段と、を有し、

前記電圧制御手段は、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧を制御することを特徴とする基板検査装置。

【請求項2】

前記1次電子の加速電圧をシミュレーションにより算出する電圧算出手段をさらに有することを特徴とする請求項1記載の基板検査装置。

【請求項3】

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項1または2記載の基板検査装置。

【請求項4】

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項1乃至3のうち、いずれか1項記載の基板検査装置。

【請求項5】

前記第1の層が多結晶シリコンよりなることを特徴とする請求項4記載の基板検査装置。

【請求項6】

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項1乃至5のうち、いずれか1項記載の基板検査装置。

【請求項7】

基板上の、第1の層上に該第1の層と組成の異なる第2の層が積層されてなる積層構造上に、該第2の層が一部露出するように形成されたパターンの欠陥を検査する基板検査方法であって、

前記基板上に1次電子を照射する電子放出工程と、

前記1次電子の照射により生成される2次電子を検出する電子検出工程と、

前記電子検出工程で検出された2次電子の検出データを処理するデータ処理工程と、を有し、

前記電子放出工程では、露出する前記第2の層に照射される前記1次電子が、前記第1の層と前記第2の層の界面近傍以外の、前記第1の層または前記第2の層の中に到達するように加速電圧が制御されることを特徴とする基板検査方法。

【請求項8】

前記1次電子の加速電圧がシミュレーションにより算出されることを特徴とする請求項7記載の基板検査方法。

【請求項9】

前記第1の層が無機層であり、前記第2の層が有機層であることを特徴とする請求項7または8記載の基板検査方法。

【請求項10】

前記第1の層の表面が、グレイン状の凹凸形状を有することを特徴とする請求項7乃至9のうち、いずれか1項記載の基板検査方法。

【請求項11】

前記第1の層が多結晶シリコンよりなることを特徴とする請求項10記載の基板検査方法。

【請求項12】

前記第2の層が反射防止膜よりなり、前記パターンがフォトレジストよりなることを特徴とする請求項7乃至11のうち、いずれか1項記載の基板検査方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図2A】

【図2B】

【図2C】

【図3】

【図4B】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図4A】

【図5A】

【図5B】

【図1B】

【図1C】

【図1D】

【図2A】

【図2B】

【図2C】

【図3】

【図4B】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図4A】

【図5A】

【図5B】

【公開番号】特開2007−218695(P2007−218695A)

【公開日】平成19年8月30日(2007.8.30)

【国際特許分類】

【出願番号】特願2006−38521(P2006−38521)

【出願日】平成18年2月15日(2006.2.15)

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【Fターム(参考)】

【公開日】平成19年8月30日(2007.8.30)

【国際特許分類】

【出願日】平成18年2月15日(2006.2.15)

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【Fターム(参考)】

[ Back to top ]