基板製造方法及び基板

【課題】CMPの処理時間を短縮する。

【解決手段】基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

【解決手段】基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基板や基板上の絶縁層に形成された溝に埋め込まれた金属の平坦化に関する。

【背景技術】

【0002】

半導体装置の製造において、基板上に絶縁層を形成し、絶縁層に形成された溝に金属を埋め込み、絶縁層の溝に埋め込まれた金属の表面と絶縁層の表面とを同一高さに加工(平坦化)する化学的機械研磨(Chemical Mechanical Polishing:CMP)が用いられてい

る。

【0003】

絶縁層の溝に埋め込んだ金属よりも研磨レートが低い材料を絶縁層上に形成し、CMP処理において、研磨レートの差を利用することにより、絶縁層の溝に埋め込んだ金属の表面の高さと、絶縁層の表面の高さとを略同一にすることが行われている。絶縁層の溝に埋め込んだ金属よりも研磨レートが低い材料はストッパ層とも呼ばれている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−274369号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

CMP処理ではスラリー(研磨剤)が用いられているが、スラリーの種類によっては、スラリーを介して絶縁層の溝に埋め込んだ金属とストッパ層とが電気的に接続し、ガルバニック腐食が発生する場合がある。ガルバニック腐食は、材質の異なる金属が電気的に接続した場合、両者間の電位差により電子の移動が起こり、酸化還元電位の小さい金属が腐食することである。

【0006】

ガルバニック腐食が発生すると、ディッシング(絶縁層の溝に埋め込んだ金属の上面中央部分付近の凹み)が発生し、絶縁層の溝に埋め込まれた金属の平坦化が困難となる。CMP処理にディッシングの発生がほとんど見られない中性スラリーを用いた場合、ストッパ層の種類によっては、CMP処理が遅延するという問題がある。本件は、CMPの処理時間を短縮することを目的とする。

【課題を解決するための手段】

【0007】

本件の一観点によれば、基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

【発明の効果】

【0008】

本件によれば、CMPの処理時間を短縮することができる。

【図面の簡単な説明】

【0009】

【図1A】ベタめっきを行った後、CMP処理を行う場合の工程図(その1)である。

【図1B】ベタめっきを行った後、CMP処理を行う場合の工程図(その2)である。

【図1C】ベタめっきを行った後、CMP処理を行う場合の工程図(その3)である。

【図2A】パターンめっきを行った後、CMP処理を行う場合の工程図(その1)である。

【図2B】パターンめっきを行った後、CMP処理を行う場合の工程図(その2)である。

【図2C】パターンめっきを行った後、CMP処理を行う場合の工程図(その3)である。

【図3】本実施形態に係る基板製造方法の工程図(その1)である。

【図4】本実施形態に係る基板製造方法の工程図(その2)である。

【図5】本実施形態に係る基板製造方法の工程図(その3)である。

【図6】本実施形態に係る基板製造方法の工程図(その4)である。

【図7】本実施形態に係る基板製造方法の工程図(その5)である。

【図8】本実施形態に係る基板製造方法の工程図(その6)である。

【図9】本実施形態に係る基板製造方法の工程図(その7)である。

【図10】本実施形態に係る基板製造方法の工程図(その8)である。

【図11】本実施形態に係る基板製造方法の工程図(その9)である。

【図12】本実施形態に係る基板製造方法の工程図(その10)である。

【図13】本実施形態に係る基板製造方法の工程図(その11)である。

【発明を実施するための形態】

【0010】

以下、図面を参照して発明を実施するための形態(以下、実施形態という)を説明する。以下の実施形態の構成は例示であり、本件は、実施形態の構成に限定されない。

【0011】

基板(又は絶縁層)に配線溝(又はビアホール)を形成し、配線溝(又はビアホール)内に金属を埋め込んで配線(又はビア)を形成するダマシンプロセスがある。ダマシンプロセスでは、めっき処理により配線溝(又はビアホール)内に金属を埋め込んでいる。めっき処理には、基板(又は絶縁層)全面を均一にめっきするベタめっきと、金属を埋め込むパターン部分のみをめっきするパターンめっきとの2種類がある。

【0012】

図1は、ダマシンプロセスにおいて、ベタめっきを行った後、CMP(Chemical Mechanical Polishing、化学的機械研磨)処理を行う場合の工程図である。図1Aに示すよう

に、反応性イオンエッチング(RIE)により、基板1上の絶縁層2に溝3が形成され、スパッタリングにより、溝3の内部を含む絶縁層2の表面にストッパ層4が形成される。図1Bに示すように、電界めっき処理により、溝3の内部にめっき層5が埋め込み形成されるとともに、溝3の上方及びストッパ層4の全面にめっき層5が形成される。図1Cに示すように、CMP処理を行うことにより、めっき層5がストッパ層4の表面と同じ高さに平坦化される。

【0013】

図2は、ダマシンプロセスにおいて、パターンめっきを行った後、CMP処理を行う場合の工程図である。図2Aに示すように、反応性イオンエッチングにより、基板1上の絶縁層2に溝3が形成され、スパッタリングにより、溝3の内部を含む絶縁層2の表面にストッパ層4が形成される。ストッパ層4上にレジスト膜を形成した後、フォトリソグラフィにより、図2Aに示すように、溝3の上方が開口されたレジストパターン(マスクパターン)6がストッパ層4上に形成される。図2Bに示すように、電界めっき処理により、

溝3の内部にめっき層5が埋め込み形成されるとともに、溝3の上方にめっき層5が形成される。図2Cに示すように、CMP処理を行うことにより、めっき層5がストッパ層4の表面と同じ高さに平坦化される。

【0014】

パターンめっきは、ベタめっきに比べて、めっき面積が非常に小さいため、めっき速度が速い、めっき液の劣化が少ない等の利点があり、環境面においても有益である。すなわち、パターンめっきは、めっき処理の完了がベタめっきよりも速く、めっき液の劣化がベタめっきよりも少ない。

【0015】

ストッパ層4にRu(ルテニウム)を用いてベタめっきを行った後、CMP平坦化を行う際、CMP処理において仕上げ処理用スラリーを用いる場合がある。仕上げ処理用スラリーは、例えば、中性(pH7)タイプで、γ-アルミナ砥粒を含むスラリーである。ベ

タめっきを行った後、仕上げ処理用スラリーを用いてCMP処理を行った場合、ストッパ層4にRuを用いることでディッシングはほとんど発生しない。

【0016】

また、ストッパ層4にRuを用いてパターンめっきを行った後、CMP平坦化を行う際、CMP処理において仕上げ処理用スラリーを用いる場合がある。パターンめっきを行った後、仕上げ処理用スラリーを用いてCMP処理を行った場合も、ストッパ層4にRuを用いることでディッシングはほとんど発生しない。しかし、同一膜厚のめっき層5にCMP処理を行う場合、ベタめっきを行った場合よりもパターンめっきを行った場合の方が、CMP処理時間が3倍以上になる。

【0017】

ベタめっきを行った後にCMP処理を行う場合、ストッパ層4であるRuが露出すると、研磨速度が極端に低下する現象が起こる。パターンめっきを行った後にCMP処理を行う場合、図2Bに示すように、CMP処理の開始時に既にストッパ層4であるRuが露出している。そのため、パターンめっきを行った後にCMP処理を行う場合、CMP処理の開始時から研磨速度が遅いと考えられ、CMP処理時間が遅延する。

【0018】

ストッパ層4にRuを用いてパターンめっきを行った後、CMP平坦化を行う際、CMP処理において高速処理用スラリーを用いる場合がある。高速処理用スラリーは、CMP処理における研磨速度が速いスラリーであり、例えば、酸性(pH7未満)タイプで、α-アルミナ砥粒を含むスラリーである。パターンめっきを行った後、高速処理用スラリー

を用いてCMP処理を行った場合、平坦化対象のめっき層5とストッパ層4であるRuとの間でガルバニック腐食が発生する。ガルバニック腐食が発生すると、急激なディッシングが発生するため、めっき層5の平坦化が困難となる。

【0019】

めっき処理の種類とめっき処理に用いるスラリーとの組み合わせとして、次の3種類が一般的に用いられている。

(1)ベタめっき+仕上げ処理用スラリー

(2)パターンめっき+仕上げ処理用スラリー

(3)ベタめっき+高速処理用スラリー及び仕上げ処理用スラリーの2ステップ

ベタめっき+高速処理用スラリー及び仕上げ処理用スラリーの2ステップは、ベタめっきを行った後、高速処理用スラリーを用いてCMP処理を開始し、CMP処理が完了する前に仕上げ処理用スラリーに切り替える方法である。

【0020】

ベタめっき+仕上げ処理用スラリーの場合やベタめっき+高速処理用スラリー及び仕上げ処理用スラリーの2ステップの場合、ベタめっきを用いるため、めっき処理の完了の遅延やめっき液の劣化が早い等の問題がある。パターンめっき+仕上げ処理用スラリーの場合、CMP処理の開始時に既にストッパ層4であるRuが露出しているため、CMP処理時間の遅延が問題となる。更に、ベタめっき+高速処理用スラリー及び仕上げ処理用スラ

リーの2ステップの場合、スラリー切り替え時期の見極めが困難になるという問題がある。

【0021】

本実施形態に係る基板製造方法では、めっき処理において、パターンめっきを用いることにより、めっき処理の完了の遅延やめっき液の劣化を回避する。また、本実施形態に係る基板製造方法では、ストッパ層を保護する金属をストッパ層上に形成することで、CMP処理において、スラリーを介してめっき層とストッパ層とが電気的に接続されることを回避する。

【0022】

図3から図13を用いて、本実施形態に係る基板製造方法の一例を説明する。図3から図13は、本実施形態に係る基板製造方法の工程図である。

【0023】

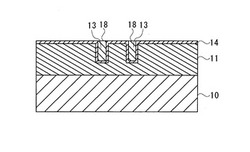

本実施形態に係る基板製造方法の一例においては、まず、図3に示すように、スパッタリングにより、基板10上に絶縁層11を形成する。例えば、基板10は、アルチック基板である。例えば、絶縁層11はアルミナ(Al2O3)であり、絶縁層11の膜厚は1μmである。次に、絶縁層11上にレジスト膜を形成した後、フォトリソグラフィ技術によりレジスト膜を露光・現像して、図3に示すように、絶縁層11上にレジストパターン(マスクパターン)12を形成する。

【0024】

次に、図4に示すように、レジストパターン12をマスクにして、反応性イオンエッチングにより、絶縁層11に溝(埋め込み孔)13を形成した後、レジストパターン12を除去する。例えば、溝13の直径は200nmであり、溝13の高さは400nmである。

【0025】

そして、図5に示すように、スパッタリングにより、絶縁層11上にストッパ層14(第1の金属層に相当)を形成する。この場合、図5に示すように、ストッパ層14は、溝13の内部を含む絶縁層11の全面に形成される。すなわち、ストッパ層14は、絶縁層11上及び溝13の表面に形成される。例えば、ストッパ層14はRuであり、ストッパ層14の膜厚は50nmである。ストッパ層14は、溝13の内部に金属めっきを埋め込むためのめっきシード層の役割を果たす。

【0026】

次いで、ストッパ層14上にレジスト膜を形成した後、フォトリソグラフィ技術によりレジスト膜を露光・現像して、図6に示すように、溝13の内部及び上方にレジストパターン(マスクパターン)15を形成する。図6に示すように、溝13の内部及び上方にレジストパターン15が形成されることにより、溝13の内部以外のストッパ層14が露出した状態になる。

【0027】

次に、図7に示すように、スパッタリングにより、ストッパ層14上にバリア層16(第2の金属層に相当)を形成する。この場合、図7に示すように、溝13の上方に形成されたレジストパターン15の表面にもバリア層16が形成される。例えば、バリア層16はTa(タンタル)であり、バリア層16の膜厚は8nmである。また、バリア層16として、Ti(チタン)、Cr(クロム)、Al(アルミニウム)又はNi(ニッケル)等の金属を用いてもよい。

【0028】

そして、図8に示すように、溝13の内部及び上方に形成されたレジストパターン15を除去するとともに、溝13の上方のレジストパターン15の表面に形成されたバリア層16を除去する(リフトオフ)。

【0029】

次いで、バリア層16上にレジスト膜を形成した後、フォトリソグラフィ技術によりレジスト膜を露光・現像して、図9に示すように、溝13の上方が開口されたレジストパタ

ーン(マスクパターン)17をバリア層16上に形成する。

【0030】

次に、図10に示すように、電界めっき処理により、溝13の内部にめっき層18(第3の金属層に相当)を埋め込み形成するとともに、溝13の上方にめっき層18を形成する。例えば、めっき層18は鉄コバルト(FeCo)であり、めっき層18の膜厚は800nmである。また、めっき層18として、FeNi(鉄ニッケル)等のFe系合金又は銅(Cu)を用いてもよい。

【0031】

そして、図11に示すように、バリア層16上に形成されたレジストパターン17を除去する。

【0032】

次いで、図12に示すように、仕上げ処理用スラリーを用いてCMP処理を行うことにより、めっき層18の平坦化を行う。ここでは、基板10を不図示の研磨パッドに押し付ける圧力を20kPa、回転数100rpmの条件でCMP処理を行う。例えば、仕上げ処理用スラリーは、中性(pH7)タイプで、γ-アルミナ砥粒を含むスラリーである。

仕上げ処理用スラリーとして、バイコウスキー・ジャパン社製のFINAL−3等を用いることができる。

【0033】

図12に示すように、CMP処理により、溝13の上方に形成されためっき層18及びバリア層16を研磨し、バリア層16を除去するとともにめっき層18の表面とストッパ層14の表面とが同じ高さとなるように、めっき層18の平坦化を行う。CMP処理時間を制御することにより、バリア層16を除去し、めっき層18の表面とストッパ層14の表面とが同じ高さとなった時点で、CMPの研磨処理を終了する。

【0034】

仕上げ処理用スラリーとしてバイコウスキー・ジャパン社製のFINAL−3を用いた場合におけるバリア層16に対するめっき層18の研磨選択比は、1:50である。バリア層16に対するめっき層18の研磨選択比に基づいて、バリア層16の膜厚を8nm、めっき層18の膜厚を800nmと決定する。溝13の高さが400nmであるので、CMP処理により、めっき層18の上部を400nm研磨すれば、めっき層18の表面とストッパ層14の表面との高さが同じになる。バリア層16に対するめっき層18の研磨選択比が1:50である場合、めっき層18の上部を400nm研磨した時点で、バリア層16が8nm研磨されることになる。したがって、めっき層18の表面とストッパ層14の表面との高さが同じになった時点でCMPの研磨処理を終了することにより、バリア層16を除去することができる。すなわち、めっき層18の平坦化が完了すると同時にバリア層16を除去することができる。

【0035】

なお、バリア層16を除去する例を説明したが、バリア層16を除去せずにストッパ層14上にバリア層16を残存させた状態で、CMPの研磨処理を終了してもよい。

【0036】

ストッパ層14上にバリア層16を形成することで、CMP処理中にストッパ層14が露出しないため、CMPの処理時間の遅延を抑制することができる。すなわち、ストッパ層14上にバリア層16を形成することにより、ストッパ層14にRuを用いたパターンめっきを行った後のCMPの処理時間を短縮することができる。

【0037】

上記の例では、CMP処理において仕上げ処理用スラリーを用いる場合を説明したが、CMP処理において高速処理用スラリーを用いてもよい。高速処理用スラリーは、CMP処理における研磨速度が速いスラリーである。高速処理用スラリーは、例えば、酸性(pH7未満)タイプで、α-アルミナ砥粒を含むスラリーである。高速処理用スラリーとし

て、バイコウスキー・ジャパン社製のF−200又はFS−200等を用いることができる。

【0038】

ストッパ層14上にバリア層16を形成しない場合、CMP処理において、高速処理用スラリーを介して、ストッパ層14とめっき層18とが電気的に接続し、めっき層18にガルバニック腐食が発生する。

【0039】

FeCo又はFeNi等のFe系合金の酸化還元電位は、−0.44Vである。めっき層18としてFeCo又はFeNi等のFe系合金を用いる場合、Fe系合金の酸化還元電位よりも小さい酸化還元電位の金属をバリア層16として用いることにより、CMP処理におけるめっき層18でのガルバニック腐食を抑制することができる。したがって、CMP処理において高速処理用スラリーを用いる場合、めっき層18がFeCo又はFeNi等のFe系合金であれば、バリア層16としてTa、Ti、Cr、Al等の金属を使用することが可能である。なお、Taの酸化還元電位は、−0.81Vであり、Tiの酸化還元電位は、−1.74Vであり、Crの酸化還元電位は、−0.90Vであり、Alの酸化還元電位は、−1.676Vである。

【0040】

Cuの酸化還元電位は、0.340Vである。めっき層18としてCuを用いる場合、Cuの酸化還元電位よりも小さい酸化還元電位の金属をバリア層16として用いることにより、CMP処理におけるめっき層18でのガルバニック腐食を抑制することができる。したがって、CMP処理において高速処理用スラリーを用いる場合、めっき層18がCuであれば、バリア層16としてTa、Ti、Cr、Al等の金属の他にNiを使用することが可能である。なお、Niの酸化還元電位は、−0.257Vである。

【0041】

ストッパ層14上にバリア層16を形成しない場合には、めっき層18でガルバニック腐食が発生することから、CMP処理において高速処理用スラリーを用いることができなかった。ストッパ層14上にバリア層16を形成することにより、めっき層18でのガルバニック腐食の発生が抑制されるため、CMP処理において高速処理用スラリーを用いることが可能となる。

【0042】

ここで、CMP処理において高速処理用スラリーを用いる場合のCMP処理の完了時点について説明する。CMP処理において高速処理用スラリーを用いる場合、CMP処理の完了時においてストッパ層14上にバリア層16を残存させる。高速処理用スラリーを用いる場合、ストッパ層14上にバリア層16が残存していないと、CMP処理において、高速処理用スラリーを介して、めっき層18とストッパ層14とが電気的に接続し、ガルバニック腐食が発生し、ディッシングが発生する。

【0043】

図13は、高速処理用スラリーを用いてCMP処理を行うことにより、めっき層18の平坦化を行った場合の工程図である。図13に示すように、高速処理用スラリーを用いたCMP処理では、CMP処理の完了時においてストッパ層14上にバリア層16を残存させている。

【0044】

バリア層16とめっき層18とは硬度が異なり、CMPによる研磨処理の速度に差が生じる。CMPによる研磨処理の速度差を検知し、バリア層16の上面が研磨され始めた時点で、CMPの研磨処理を終了することにより、ストッパ層14上にバリア層16を残存させることが可能である。また、CMP処理時間を制御することにより、CMP処理の完了時においてストッパ層14上にバリア層16を残存させてもよい。

【0045】

本実施形態に係る基板製造方法では、シングルダマシンプロセスにおいて、パターンめっきを行った後、CMP処理を行う場合について説明したが、本実施形態に係る基板製造方法をデュアルダマシンプロセスに適用してもよい。

【0046】

また、本実施形態に係る基板製造方法において、パターンめっきを行い、CMP処理において、最初に高速処理用スラリーを用い、後に仕上げ処理用スラリーに切り替えてもよい。CMP処理において、高速処理用スラリーから仕上げ処理用スラリーに切り替える場合、高速処理用スラリーを用いたCMP処理では、ストッパ層14上にバリア層16を残存させた状態でめっき層18の研磨を停止する。そして、仕上げ処理用スラリーを用いたCMP処理では、ストッパ層14上に残存するバリア層16を除去するとともに、めっき層18の表面とストッパ層14の表面とが同じ高さとなるようにめっき層18を平坦化する。

【0047】

本実施形態に係る基板製造方法では、ストッパ層14上にバリア層16を形成するため、高速処理用スラリーを用いたCMP処理において、ストッパ層14が研磨される前にCMP処理を一旦停止することが可能である。そのため、スラリーの切り替えを容易に行うことができる。

【0048】

CMP処理で仕上げ処理用スラリーを用いる場合、ストッパ層14としてTaやTiを使用すると、研磨対象であるめっき層18との研磨選択比がそれほど大きくないため、ストッパ層14が消滅したり、ディッシングが発生したりする。一方、CMP処理で高速処理用スラリーを用いる場合、TaやTiと研磨対象であるめっき層18との研磨選択比は1:100と大きいため、ストッパ層14としてTaやTiを使用することが可能である。また、TaやTiは研磨対象であるめっき層18との酸化還元電位の差がRuほど大きくないため、ガルバニック腐食が発生しにくくなる。しかし、めっきシード層としてはRuが最適であるため、ストッパ層14としてRuを用いることが好ましい。

【符号の説明】

【0049】

1 基板

2 絶縁層

3 溝

4 ストッパ層

5 めっき層

6 レジストパターン

10 基板

11 絶縁層

12 レジストパターン

13 溝

14 ストッパ層

15 レジストパターン

16 バリア層

17 レジストパターン

18 めっき層

【技術分野】

【0001】

本発明は、基板や基板上の絶縁層に形成された溝に埋め込まれた金属の平坦化に関する。

【背景技術】

【0002】

半導体装置の製造において、基板上に絶縁層を形成し、絶縁層に形成された溝に金属を埋め込み、絶縁層の溝に埋め込まれた金属の表面と絶縁層の表面とを同一高さに加工(平坦化)する化学的機械研磨(Chemical Mechanical Polishing:CMP)が用いられてい

る。

【0003】

絶縁層の溝に埋め込んだ金属よりも研磨レートが低い材料を絶縁層上に形成し、CMP処理において、研磨レートの差を利用することにより、絶縁層の溝に埋め込んだ金属の表面の高さと、絶縁層の表面の高さとを略同一にすることが行われている。絶縁層の溝に埋め込んだ金属よりも研磨レートが低い材料はストッパ層とも呼ばれている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−274369号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

CMP処理ではスラリー(研磨剤)が用いられているが、スラリーの種類によっては、スラリーを介して絶縁層の溝に埋め込んだ金属とストッパ層とが電気的に接続し、ガルバニック腐食が発生する場合がある。ガルバニック腐食は、材質の異なる金属が電気的に接続した場合、両者間の電位差により電子の移動が起こり、酸化還元電位の小さい金属が腐食することである。

【0006】

ガルバニック腐食が発生すると、ディッシング(絶縁層の溝に埋め込んだ金属の上面中央部分付近の凹み)が発生し、絶縁層の溝に埋め込まれた金属の平坦化が困難となる。CMP処理にディッシングの発生がほとんど見られない中性スラリーを用いた場合、ストッパ層の種類によっては、CMP処理が遅延するという問題がある。本件は、CMPの処理時間を短縮することを目的とする。

【課題を解決するための手段】

【0007】

本件の一観点によれば、基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

【発明の効果】

【0008】

本件によれば、CMPの処理時間を短縮することができる。

【図面の簡単な説明】

【0009】

【図1A】ベタめっきを行った後、CMP処理を行う場合の工程図(その1)である。

【図1B】ベタめっきを行った後、CMP処理を行う場合の工程図(その2)である。

【図1C】ベタめっきを行った後、CMP処理を行う場合の工程図(その3)である。

【図2A】パターンめっきを行った後、CMP処理を行う場合の工程図(その1)である。

【図2B】パターンめっきを行った後、CMP処理を行う場合の工程図(その2)である。

【図2C】パターンめっきを行った後、CMP処理を行う場合の工程図(その3)である。

【図3】本実施形態に係る基板製造方法の工程図(その1)である。

【図4】本実施形態に係る基板製造方法の工程図(その2)である。

【図5】本実施形態に係る基板製造方法の工程図(その3)である。

【図6】本実施形態に係る基板製造方法の工程図(その4)である。

【図7】本実施形態に係る基板製造方法の工程図(その5)である。

【図8】本実施形態に係る基板製造方法の工程図(その6)である。

【図9】本実施形態に係る基板製造方法の工程図(その7)である。

【図10】本実施形態に係る基板製造方法の工程図(その8)である。

【図11】本実施形態に係る基板製造方法の工程図(その9)である。

【図12】本実施形態に係る基板製造方法の工程図(その10)である。

【図13】本実施形態に係る基板製造方法の工程図(その11)である。

【発明を実施するための形態】

【0010】

以下、図面を参照して発明を実施するための形態(以下、実施形態という)を説明する。以下の実施形態の構成は例示であり、本件は、実施形態の構成に限定されない。

【0011】

基板(又は絶縁層)に配線溝(又はビアホール)を形成し、配線溝(又はビアホール)内に金属を埋め込んで配線(又はビア)を形成するダマシンプロセスがある。ダマシンプロセスでは、めっき処理により配線溝(又はビアホール)内に金属を埋め込んでいる。めっき処理には、基板(又は絶縁層)全面を均一にめっきするベタめっきと、金属を埋め込むパターン部分のみをめっきするパターンめっきとの2種類がある。

【0012】

図1は、ダマシンプロセスにおいて、ベタめっきを行った後、CMP(Chemical Mechanical Polishing、化学的機械研磨)処理を行う場合の工程図である。図1Aに示すよう

に、反応性イオンエッチング(RIE)により、基板1上の絶縁層2に溝3が形成され、スパッタリングにより、溝3の内部を含む絶縁層2の表面にストッパ層4が形成される。図1Bに示すように、電界めっき処理により、溝3の内部にめっき層5が埋め込み形成されるとともに、溝3の上方及びストッパ層4の全面にめっき層5が形成される。図1Cに示すように、CMP処理を行うことにより、めっき層5がストッパ層4の表面と同じ高さに平坦化される。

【0013】

図2は、ダマシンプロセスにおいて、パターンめっきを行った後、CMP処理を行う場合の工程図である。図2Aに示すように、反応性イオンエッチングにより、基板1上の絶縁層2に溝3が形成され、スパッタリングにより、溝3の内部を含む絶縁層2の表面にストッパ層4が形成される。ストッパ層4上にレジスト膜を形成した後、フォトリソグラフィにより、図2Aに示すように、溝3の上方が開口されたレジストパターン(マスクパターン)6がストッパ層4上に形成される。図2Bに示すように、電界めっき処理により、

溝3の内部にめっき層5が埋め込み形成されるとともに、溝3の上方にめっき層5が形成される。図2Cに示すように、CMP処理を行うことにより、めっき層5がストッパ層4の表面と同じ高さに平坦化される。

【0014】

パターンめっきは、ベタめっきに比べて、めっき面積が非常に小さいため、めっき速度が速い、めっき液の劣化が少ない等の利点があり、環境面においても有益である。すなわち、パターンめっきは、めっき処理の完了がベタめっきよりも速く、めっき液の劣化がベタめっきよりも少ない。

【0015】

ストッパ層4にRu(ルテニウム)を用いてベタめっきを行った後、CMP平坦化を行う際、CMP処理において仕上げ処理用スラリーを用いる場合がある。仕上げ処理用スラリーは、例えば、中性(pH7)タイプで、γ-アルミナ砥粒を含むスラリーである。ベ

タめっきを行った後、仕上げ処理用スラリーを用いてCMP処理を行った場合、ストッパ層4にRuを用いることでディッシングはほとんど発生しない。

【0016】

また、ストッパ層4にRuを用いてパターンめっきを行った後、CMP平坦化を行う際、CMP処理において仕上げ処理用スラリーを用いる場合がある。パターンめっきを行った後、仕上げ処理用スラリーを用いてCMP処理を行った場合も、ストッパ層4にRuを用いることでディッシングはほとんど発生しない。しかし、同一膜厚のめっき層5にCMP処理を行う場合、ベタめっきを行った場合よりもパターンめっきを行った場合の方が、CMP処理時間が3倍以上になる。

【0017】

ベタめっきを行った後にCMP処理を行う場合、ストッパ層4であるRuが露出すると、研磨速度が極端に低下する現象が起こる。パターンめっきを行った後にCMP処理を行う場合、図2Bに示すように、CMP処理の開始時に既にストッパ層4であるRuが露出している。そのため、パターンめっきを行った後にCMP処理を行う場合、CMP処理の開始時から研磨速度が遅いと考えられ、CMP処理時間が遅延する。

【0018】

ストッパ層4にRuを用いてパターンめっきを行った後、CMP平坦化を行う際、CMP処理において高速処理用スラリーを用いる場合がある。高速処理用スラリーは、CMP処理における研磨速度が速いスラリーであり、例えば、酸性(pH7未満)タイプで、α-アルミナ砥粒を含むスラリーである。パターンめっきを行った後、高速処理用スラリー

を用いてCMP処理を行った場合、平坦化対象のめっき層5とストッパ層4であるRuとの間でガルバニック腐食が発生する。ガルバニック腐食が発生すると、急激なディッシングが発生するため、めっき層5の平坦化が困難となる。

【0019】

めっき処理の種類とめっき処理に用いるスラリーとの組み合わせとして、次の3種類が一般的に用いられている。

(1)ベタめっき+仕上げ処理用スラリー

(2)パターンめっき+仕上げ処理用スラリー

(3)ベタめっき+高速処理用スラリー及び仕上げ処理用スラリーの2ステップ

ベタめっき+高速処理用スラリー及び仕上げ処理用スラリーの2ステップは、ベタめっきを行った後、高速処理用スラリーを用いてCMP処理を開始し、CMP処理が完了する前に仕上げ処理用スラリーに切り替える方法である。

【0020】

ベタめっき+仕上げ処理用スラリーの場合やベタめっき+高速処理用スラリー及び仕上げ処理用スラリーの2ステップの場合、ベタめっきを用いるため、めっき処理の完了の遅延やめっき液の劣化が早い等の問題がある。パターンめっき+仕上げ処理用スラリーの場合、CMP処理の開始時に既にストッパ層4であるRuが露出しているため、CMP処理時間の遅延が問題となる。更に、ベタめっき+高速処理用スラリー及び仕上げ処理用スラ

リーの2ステップの場合、スラリー切り替え時期の見極めが困難になるという問題がある。

【0021】

本実施形態に係る基板製造方法では、めっき処理において、パターンめっきを用いることにより、めっき処理の完了の遅延やめっき液の劣化を回避する。また、本実施形態に係る基板製造方法では、ストッパ層を保護する金属をストッパ層上に形成することで、CMP処理において、スラリーを介してめっき層とストッパ層とが電気的に接続されることを回避する。

【0022】

図3から図13を用いて、本実施形態に係る基板製造方法の一例を説明する。図3から図13は、本実施形態に係る基板製造方法の工程図である。

【0023】

本実施形態に係る基板製造方法の一例においては、まず、図3に示すように、スパッタリングにより、基板10上に絶縁層11を形成する。例えば、基板10は、アルチック基板である。例えば、絶縁層11はアルミナ(Al2O3)であり、絶縁層11の膜厚は1μmである。次に、絶縁層11上にレジスト膜を形成した後、フォトリソグラフィ技術によりレジスト膜を露光・現像して、図3に示すように、絶縁層11上にレジストパターン(マスクパターン)12を形成する。

【0024】

次に、図4に示すように、レジストパターン12をマスクにして、反応性イオンエッチングにより、絶縁層11に溝(埋め込み孔)13を形成した後、レジストパターン12を除去する。例えば、溝13の直径は200nmであり、溝13の高さは400nmである。

【0025】

そして、図5に示すように、スパッタリングにより、絶縁層11上にストッパ層14(第1の金属層に相当)を形成する。この場合、図5に示すように、ストッパ層14は、溝13の内部を含む絶縁層11の全面に形成される。すなわち、ストッパ層14は、絶縁層11上及び溝13の表面に形成される。例えば、ストッパ層14はRuであり、ストッパ層14の膜厚は50nmである。ストッパ層14は、溝13の内部に金属めっきを埋め込むためのめっきシード層の役割を果たす。

【0026】

次いで、ストッパ層14上にレジスト膜を形成した後、フォトリソグラフィ技術によりレジスト膜を露光・現像して、図6に示すように、溝13の内部及び上方にレジストパターン(マスクパターン)15を形成する。図6に示すように、溝13の内部及び上方にレジストパターン15が形成されることにより、溝13の内部以外のストッパ層14が露出した状態になる。

【0027】

次に、図7に示すように、スパッタリングにより、ストッパ層14上にバリア層16(第2の金属層に相当)を形成する。この場合、図7に示すように、溝13の上方に形成されたレジストパターン15の表面にもバリア層16が形成される。例えば、バリア層16はTa(タンタル)であり、バリア層16の膜厚は8nmである。また、バリア層16として、Ti(チタン)、Cr(クロム)、Al(アルミニウム)又はNi(ニッケル)等の金属を用いてもよい。

【0028】

そして、図8に示すように、溝13の内部及び上方に形成されたレジストパターン15を除去するとともに、溝13の上方のレジストパターン15の表面に形成されたバリア層16を除去する(リフトオフ)。

【0029】

次いで、バリア層16上にレジスト膜を形成した後、フォトリソグラフィ技術によりレジスト膜を露光・現像して、図9に示すように、溝13の上方が開口されたレジストパタ

ーン(マスクパターン)17をバリア層16上に形成する。

【0030】

次に、図10に示すように、電界めっき処理により、溝13の内部にめっき層18(第3の金属層に相当)を埋め込み形成するとともに、溝13の上方にめっき層18を形成する。例えば、めっき層18は鉄コバルト(FeCo)であり、めっき層18の膜厚は800nmである。また、めっき層18として、FeNi(鉄ニッケル)等のFe系合金又は銅(Cu)を用いてもよい。

【0031】

そして、図11に示すように、バリア層16上に形成されたレジストパターン17を除去する。

【0032】

次いで、図12に示すように、仕上げ処理用スラリーを用いてCMP処理を行うことにより、めっき層18の平坦化を行う。ここでは、基板10を不図示の研磨パッドに押し付ける圧力を20kPa、回転数100rpmの条件でCMP処理を行う。例えば、仕上げ処理用スラリーは、中性(pH7)タイプで、γ-アルミナ砥粒を含むスラリーである。

仕上げ処理用スラリーとして、バイコウスキー・ジャパン社製のFINAL−3等を用いることができる。

【0033】

図12に示すように、CMP処理により、溝13の上方に形成されためっき層18及びバリア層16を研磨し、バリア層16を除去するとともにめっき層18の表面とストッパ層14の表面とが同じ高さとなるように、めっき層18の平坦化を行う。CMP処理時間を制御することにより、バリア層16を除去し、めっき層18の表面とストッパ層14の表面とが同じ高さとなった時点で、CMPの研磨処理を終了する。

【0034】

仕上げ処理用スラリーとしてバイコウスキー・ジャパン社製のFINAL−3を用いた場合におけるバリア層16に対するめっき層18の研磨選択比は、1:50である。バリア層16に対するめっき層18の研磨選択比に基づいて、バリア層16の膜厚を8nm、めっき層18の膜厚を800nmと決定する。溝13の高さが400nmであるので、CMP処理により、めっき層18の上部を400nm研磨すれば、めっき層18の表面とストッパ層14の表面との高さが同じになる。バリア層16に対するめっき層18の研磨選択比が1:50である場合、めっき層18の上部を400nm研磨した時点で、バリア層16が8nm研磨されることになる。したがって、めっき層18の表面とストッパ層14の表面との高さが同じになった時点でCMPの研磨処理を終了することにより、バリア層16を除去することができる。すなわち、めっき層18の平坦化が完了すると同時にバリア層16を除去することができる。

【0035】

なお、バリア層16を除去する例を説明したが、バリア層16を除去せずにストッパ層14上にバリア層16を残存させた状態で、CMPの研磨処理を終了してもよい。

【0036】

ストッパ層14上にバリア層16を形成することで、CMP処理中にストッパ層14が露出しないため、CMPの処理時間の遅延を抑制することができる。すなわち、ストッパ層14上にバリア層16を形成することにより、ストッパ層14にRuを用いたパターンめっきを行った後のCMPの処理時間を短縮することができる。

【0037】

上記の例では、CMP処理において仕上げ処理用スラリーを用いる場合を説明したが、CMP処理において高速処理用スラリーを用いてもよい。高速処理用スラリーは、CMP処理における研磨速度が速いスラリーである。高速処理用スラリーは、例えば、酸性(pH7未満)タイプで、α-アルミナ砥粒を含むスラリーである。高速処理用スラリーとし

て、バイコウスキー・ジャパン社製のF−200又はFS−200等を用いることができる。

【0038】

ストッパ層14上にバリア層16を形成しない場合、CMP処理において、高速処理用スラリーを介して、ストッパ層14とめっき層18とが電気的に接続し、めっき層18にガルバニック腐食が発生する。

【0039】

FeCo又はFeNi等のFe系合金の酸化還元電位は、−0.44Vである。めっき層18としてFeCo又はFeNi等のFe系合金を用いる場合、Fe系合金の酸化還元電位よりも小さい酸化還元電位の金属をバリア層16として用いることにより、CMP処理におけるめっき層18でのガルバニック腐食を抑制することができる。したがって、CMP処理において高速処理用スラリーを用いる場合、めっき層18がFeCo又はFeNi等のFe系合金であれば、バリア層16としてTa、Ti、Cr、Al等の金属を使用することが可能である。なお、Taの酸化還元電位は、−0.81Vであり、Tiの酸化還元電位は、−1.74Vであり、Crの酸化還元電位は、−0.90Vであり、Alの酸化還元電位は、−1.676Vである。

【0040】

Cuの酸化還元電位は、0.340Vである。めっき層18としてCuを用いる場合、Cuの酸化還元電位よりも小さい酸化還元電位の金属をバリア層16として用いることにより、CMP処理におけるめっき層18でのガルバニック腐食を抑制することができる。したがって、CMP処理において高速処理用スラリーを用いる場合、めっき層18がCuであれば、バリア層16としてTa、Ti、Cr、Al等の金属の他にNiを使用することが可能である。なお、Niの酸化還元電位は、−0.257Vである。

【0041】

ストッパ層14上にバリア層16を形成しない場合には、めっき層18でガルバニック腐食が発生することから、CMP処理において高速処理用スラリーを用いることができなかった。ストッパ層14上にバリア層16を形成することにより、めっき層18でのガルバニック腐食の発生が抑制されるため、CMP処理において高速処理用スラリーを用いることが可能となる。

【0042】

ここで、CMP処理において高速処理用スラリーを用いる場合のCMP処理の完了時点について説明する。CMP処理において高速処理用スラリーを用いる場合、CMP処理の完了時においてストッパ層14上にバリア層16を残存させる。高速処理用スラリーを用いる場合、ストッパ層14上にバリア層16が残存していないと、CMP処理において、高速処理用スラリーを介して、めっき層18とストッパ層14とが電気的に接続し、ガルバニック腐食が発生し、ディッシングが発生する。

【0043】

図13は、高速処理用スラリーを用いてCMP処理を行うことにより、めっき層18の平坦化を行った場合の工程図である。図13に示すように、高速処理用スラリーを用いたCMP処理では、CMP処理の完了時においてストッパ層14上にバリア層16を残存させている。

【0044】

バリア層16とめっき層18とは硬度が異なり、CMPによる研磨処理の速度に差が生じる。CMPによる研磨処理の速度差を検知し、バリア層16の上面が研磨され始めた時点で、CMPの研磨処理を終了することにより、ストッパ層14上にバリア層16を残存させることが可能である。また、CMP処理時間を制御することにより、CMP処理の完了時においてストッパ層14上にバリア層16を残存させてもよい。

【0045】

本実施形態に係る基板製造方法では、シングルダマシンプロセスにおいて、パターンめっきを行った後、CMP処理を行う場合について説明したが、本実施形態に係る基板製造方法をデュアルダマシンプロセスに適用してもよい。

【0046】

また、本実施形態に係る基板製造方法において、パターンめっきを行い、CMP処理において、最初に高速処理用スラリーを用い、後に仕上げ処理用スラリーに切り替えてもよい。CMP処理において、高速処理用スラリーから仕上げ処理用スラリーに切り替える場合、高速処理用スラリーを用いたCMP処理では、ストッパ層14上にバリア層16を残存させた状態でめっき層18の研磨を停止する。そして、仕上げ処理用スラリーを用いたCMP処理では、ストッパ層14上に残存するバリア層16を除去するとともに、めっき層18の表面とストッパ層14の表面とが同じ高さとなるようにめっき層18を平坦化する。

【0047】

本実施形態に係る基板製造方法では、ストッパ層14上にバリア層16を形成するため、高速処理用スラリーを用いたCMP処理において、ストッパ層14が研磨される前にCMP処理を一旦停止することが可能である。そのため、スラリーの切り替えを容易に行うことができる。

【0048】

CMP処理で仕上げ処理用スラリーを用いる場合、ストッパ層14としてTaやTiを使用すると、研磨対象であるめっき層18との研磨選択比がそれほど大きくないため、ストッパ層14が消滅したり、ディッシングが発生したりする。一方、CMP処理で高速処理用スラリーを用いる場合、TaやTiと研磨対象であるめっき層18との研磨選択比は1:100と大きいため、ストッパ層14としてTaやTiを使用することが可能である。また、TaやTiは研磨対象であるめっき層18との酸化還元電位の差がRuほど大きくないため、ガルバニック腐食が発生しにくくなる。しかし、めっきシード層としてはRuが最適であるため、ストッパ層14としてRuを用いることが好ましい。

【符号の説明】

【0049】

1 基板

2 絶縁層

3 溝

4 ストッパ層

5 めっき層

6 レジストパターン

10 基板

11 絶縁層

12 レジストパターン

13 溝

14 ストッパ層

15 レジストパターン

16 バリア層

17 レジストパターン

18 めっき層

【特許請求の範囲】

【請求項1】

基板上に絶縁層を形成する工程と、

前記絶縁層上に第1のマスクを形成する工程と、

前記第1のマスクを介して前記絶縁層をエッチングすることにより前記絶縁層に溝を形成する工程と、

前記第1のマスクを除去する工程と、

前記絶縁層上及び前記溝の表面に第1の金属層を形成する工程と、

前記溝の内部及び上方に第2のマスクを形成する工程と、

前記第1の金属層上及び前記第2のマスクの表面に第2の金属層を形成する工程と、

前記第2のマスク及び前記第2のマスクの表面に形成された第2の金属層を除去する工程と、

前記溝の上方が開口された第3のマスクを前記第2の金属層上に形成する工程と、

前記溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、

前記第3のマスクを除去する工程と、

前記第3の金属層を化学機械研磨により平坦化する工程と、

を備えることを特徴とする基板製造方法。

【請求項2】

前記第2の金属層の酸化還元電位は、前記第3の金属層の酸化還元電位よりも小さいことを特徴とする請求項1に記載の基板製造方法。

【請求項3】

前記第2の金属層と前記第3の金属層との研磨選択比に基づいて、前記第2の金属層及び前記第3の金属層の膜厚が決定され、前記化学機械研磨を終了した時点で前記第2の金属層の除去が完了することを特徴とする請求項1に記載の基板製造方法。

【請求項4】

溝を有する絶縁層と、

前記絶縁層上及び前記溝の表面に形成された第1の金属層と、

前記溝の内部を除く前記第1の金属層上に形成された第2の金属層と、

前記溝の内部に埋め込み形成された第3の金属層と、を備え、

前記第2の金属層と前記第3の金属層とが同じ高さに平坦化されていることを特徴とする基板。

【請求項5】

前記第2の金属層の酸化還元電位は、前記第3の金属層の酸化還元電位よりも小さいことを特徴とする請求項4に記載の基板。

【請求項1】

基板上に絶縁層を形成する工程と、

前記絶縁層上に第1のマスクを形成する工程と、

前記第1のマスクを介して前記絶縁層をエッチングすることにより前記絶縁層に溝を形成する工程と、

前記第1のマスクを除去する工程と、

前記絶縁層上及び前記溝の表面に第1の金属層を形成する工程と、

前記溝の内部及び上方に第2のマスクを形成する工程と、

前記第1の金属層上及び前記第2のマスクの表面に第2の金属層を形成する工程と、

前記第2のマスク及び前記第2のマスクの表面に形成された第2の金属層を除去する工程と、

前記溝の上方が開口された第3のマスクを前記第2の金属層上に形成する工程と、

前記溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、

前記第3のマスクを除去する工程と、

前記第3の金属層を化学機械研磨により平坦化する工程と、

を備えることを特徴とする基板製造方法。

【請求項2】

前記第2の金属層の酸化還元電位は、前記第3の金属層の酸化還元電位よりも小さいことを特徴とする請求項1に記載の基板製造方法。

【請求項3】

前記第2の金属層と前記第3の金属層との研磨選択比に基づいて、前記第2の金属層及び前記第3の金属層の膜厚が決定され、前記化学機械研磨を終了した時点で前記第2の金属層の除去が完了することを特徴とする請求項1に記載の基板製造方法。

【請求項4】

溝を有する絶縁層と、

前記絶縁層上及び前記溝の表面に形成された第1の金属層と、

前記溝の内部を除く前記第1の金属層上に形成された第2の金属層と、

前記溝の内部に埋め込み形成された第3の金属層と、を備え、

前記第2の金属層と前記第3の金属層とが同じ高さに平坦化されていることを特徴とする基板。

【請求項5】

前記第2の金属層の酸化還元電位は、前記第3の金属層の酸化還元電位よりも小さいことを特徴とする請求項4に記載の基板。

【図1A】

【図1B】

【図1C】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図1B】

【図1C】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2011−96705(P2011−96705A)

【公開日】平成23年5月12日(2011.5.12)

【国際特許分類】

【出願番号】特願2009−246197(P2009−246197)

【出願日】平成21年10月27日(2009.10.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成23年5月12日(2011.5.12)

【国際特許分類】

【出願日】平成21年10月27日(2009.10.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]