基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体製造一般に関する。より詳細には、基板貫通バイア(TSV)を有する半導体構造、およびその製造方法に関する。

【背景技術】

【0002】

現在の半導体技術では、集積回路基板の上面から集積回路基板の裏面までの接続経路を設けるために基板貫通バイアを使用することがある。これによって、集積回路への裏面接続が可能となる。例えば、基板貫通バイアは接地への裏面接続を行うために使用され得る。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許第7633165号明細書

【特許文献2】米国特許第7884016号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は基板貫通バイア(TSV)を有する半導体構造およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

本発明の1つの実施形態では、裏面接地接続などに用いる、基板の上面のデバイスから基板の裏面までの経路を提供するために基板貫通バイアが使用される。このデバイスは、RFまたは電力増幅用途などの高電圧用途のためのLDMOSデバイスであってもよい。LDMOSデバイスは、それらの絶縁破壊電圧が高いためにこのような高電圧用途に使用されることができる。1つの実施形態では、LDOMSデバイスのソースに対する裏面接地接続を提供するために基板貫通バイアが使用される。1つの実施形態では、20ボルト以上の高電圧がLDMOSデバイスのドレインに印加される。しかしながら、デバイスのドレインに高電圧が印加されてソースが接地に接続されることによって、大きなドレイン漏れ電流が観測される場合がある。このドレイン漏れ電流は、印加されるドレイン電圧、およびLDMOSデバイスのドレイン領域のTSVに対する近接性、ならびに不純物濃度に左右される。高密度設計では、このドレイン漏れを低減するために必要とされるLDMOSデバイスと基板貫通バイアとの間の間隔が大きすぎる。それゆえ、1つの実施形態では、基板貫通バイアと基板との間の金属−半導体接触界面の物理的特性を変化させるために、基板貫通バイアの側壁にそって高濃度ドープされた領域が形成され、その結果として、ドレイン漏れ電流が低減され、初期逆バイアスドレイン−ソース接合破壊が妨げられる。このように、現行の基板貫通バイアの間隔要件を変更する必要はない。

【0006】

さらに、(LDMOSデバイスに加えて)他の種類のデバイスが(裏面接地接続のような)裏面接続のためにこれらの基板貫通バイアを使用してもよい。例えば、基板貫通バイアの側壁に沿って形成される高濃度ドープされた領域は、PINダイオードの真性領域(「I」領域)に類似の大きな空乏領域が作成されることを可能にする。このPIN構造は、適切なカソード設計が利用される場合(このカソード設計は、基板貫通バイアの側壁に沿った高濃度ドープ領域の導電型と反対の導電型にドープされた領域を含む)、高周波数受動素子のようなさまざまな種類のデバイスのための低損失基板を形成するために利用されることができる。

【図面の簡単な説明】

【0007】

【図1】本開示の1つの実施形態による、初期処理段階における半導体構造を示す断面図。

【図2】本発明の1つの実施形態による、図1の半導体構造の後の処理工程を示す断面図。

【図3】本発明の1つの実施形態による、図2の半導体構造の後の処理工程を示す断面図。

【図4】本発明の1つの実施形態による、図3の半導体構造の後の処理工程を示す断面図。

【図5】本発明の1つの実施形態による、図4の半導体構造の後の処理工程を示す断面図。

【図6】本発明の1つの実施形態による、図5の半導体構造の後の処理工程を示す断面図。

【図7】本発明の1つの実施形態による、図6の半導体構造の後の処理工程を示す断面図。

【図8】本発明の1つの実施形態による、図7の半導体構造の後の処理工程を示す断面図。

【図9】本発明の1つの実施形態による、図8の半導体構造の後の処理工程を示す断面図。

【図10】本発明の1つの実施形態による、図4の半導体構造の後の処理工程を示す断面図。

【図11】本発明の1つの実施形態による、図10の半導体構造の後の処理工程を示す断面図。

【図12】本発明の1つの実施形態によるPIN構造を三次元形式で示す斜視図。

【図13】本発明の1つの実施形態による、伝送線路を有するPIN構造を三次元形式で示す斜視図。

【図14】本発明の1つの実施形態による、インダクタコイルを有するPIN構造を三次元形式で示す斜視図。

【発明を実施するための形態】

【0008】

本発明は例として示されており、添付の図面によって限定されない。図面において、同様の参照符号は類似の要素を示す。図面内の要素は簡潔かつ明瞭にするために示されており、必ずしも原寸に比例して描かれてはいない。

図1は、基板12と、基板12の上面の中および上に形成されるLDMOSデバイス16とを有する半導体構造10の断面図を示す。なお、LDMOSデバイス16はLDMOSトランジスタとも称される場合がある。LDMOSデバイス16は、基板12の上面上に形成されるゲート14を含み、ゲート14は第1の側壁と、第1の側壁の反対側にある第2の側壁とを有する。LDMOSデバイス16は、基板12の上面の中に、ゲート14の下で、ゲート14の第2の側壁から側方に延在し、続いてゲート14の第1の側壁から第1の方向において側方に延在するドープ領域18を含む。LDMOSデバイス16は、基板12の上面の中に、ゲート14の第2の側壁から第2の方向において側方に延在するドープ領域20も含む。LDMOSデバイス16は、基板12の上面の中に、ゲート14の第1の側壁から第1の方向において側方に延在する(かつ、ゲート14の下には延在しない)ドープ領域24と、基板12の上面の中でドープ領域24に側方に隣接するドープ領域22も含む。ドープ領域22および24はドープ領域18内に位置しており、ドープ領域18はドープ領域24と比較して基板12内により深く延在しており、ドープ領域22はドープ領域18と比較して基板12内により深く延在している。LDMOSデバイス16は、基板12の上面の中で、ドープ領域20内にドープ領域26も含む。ドープ領域20は、ドープ領域26と比較して基板12内により深く延在している。ドープ領域26は、ゲート14の第2の側壁から側方に離間している。1つの実施形態では、当該領域はゲート14から1〜6マイクロメートルの範囲内の距離をおいて位置している。このゲート14からの側方の距離は、LDMOSデバイス16の絶縁破壊電圧を決定する要因の1つである。LDMOSデバイス16のソース領域30はドープ領域18および24を含み、ゲート14の一方の側面に対して整列しており、LDMOSデバイス16のドレイン領域28はドープ領域20および26を含む。ドープ領域22はLDMOSデバイス16の本体接続と称される場合がある。

【0009】

1つの実施形態では、基板12はシリコンである。基板12は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する。1つの実施形態では、基板12はP型ドーパントによって非常に低濃度にドープされ、従ってP−−のバックグラウンドドーピングを有する。1つの実施形態では、LDMOSデバイス16はP型基板内に形成されるN型デバイスである。この実施形態では、ドープ領域24および26はN+の導電性を有することができ、ドープ領域18はPの導電性を有することができ、ドープ領域22はP+の導電性を有することができる。ドープ領域20は、低濃度ドープドレインエクステンションまたはドリフト領域と称される場合がある。ドープ領域18は、側方拡散PウェルまたはPHV領域と称される場合がある。さらに、1つの実施形態では、基板12はP−−の代わりにN−−の導電性を有してもよい。基板12は非常に低濃度にドープされるため、基板12は高い抵抗率を有する。

【0010】

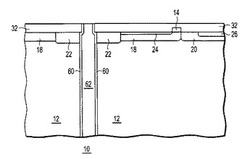

図2は、層間誘電体層(ILD)32およびマスク層34が形成された後の、図1の半導体構造10の断面図を示す。1つの実施形態では、ILD層32は、基板12の上面の上に一面を覆って堆積される誘電体層であり、化学機械研磨(CMP)などによって実質的に平坦化される。マスク層34は窒化物層のようなハードマスク層であることができ、ILD層32の上に一面を覆って堆積されることができる。

【0011】

図3は、マスク層34およびILD層32を貫通して開口36が形成された後の、図2の半導体構造10の断面図を示す。1つの実施形態では、マスク層34の上に、パターニングフォトレジスト層のようなパターニングマスク層が形成され、パターニングマスク層を使用してエッチングが実行されて開口36が形成される。その後、パターニングマスク層が除去される。

【0012】

図4は、開口36が基板12内に延在している図3の半導体構造10の断面図を示す。1つの実施形態では、エッチングは、基板12の大部分を貫通して開口36を延在させるためのマスクとしてのマスク層34内の開口36を使用して実行される。例えば、1つの実施形態では、開口36は基板12内に少なくとも70マイクロメートル延在する。なお、開口36は基板12の裏面まで完全には延在しない。さらに、開口36はTSVの形成に使用されることになる開口である。

【0013】

図5は、結果として開口36の側壁に沿ってドープ領域40をもたらすための傾斜イオン注入38が実行されている、図4の半導体構造10の断面図を示す。イオン注入領域40は、TSV空乏障壁領域と称される場合がある。示されている実施形態では、傾斜イオン注入38は、開口36の側壁内にドーパントを導入するための一連の傾斜イオン注入を含むことができる。開口36内の深さおよびドープ領域40の開口36の側壁に沿った厚さは、ドーパントの種類、ドーパントのドーズ量、およびドーパントのエネルギーのようなイオン注入のパラメータに応じて決まる。1つの実施形態では、ドープ領域40は、基板12の上面から測定して基板12内に少なくとも20マイクロメートル延在する。1つの実施形態では、ドープ領域40は、開口36の側壁に沿った0.1〜0.2マイクロメートルの範囲内の厚さ、および、開口36内により深く延在するテーパを有する。ドープ領域40は、基板12のバックグラウンドドーパント濃度よりも高いドーパント濃度を有する、高濃度ドープされたP型領域(例えば、P+領域)である。例えば、ドープ領域40のドーパント濃度は、基板12のドーパント濃度を、百倍を上回って、または一万倍を上回って超える場合がある。1つの実施形態では、基板12がP−−などである場合、ドープ領域40はP+のドーピングを有する場合がある。例えば、ホウ素のようなP型ドーパントが使用される。この例では、イオン注入領域40を形成するために、80keVのエネルギーにおける1e15のドーズ量が垂直から7度の注入角で使用されることができる。なお、P+ドープ領域40が存在することによって、基板12がN型ドーパントを用いて非常に低濃度にドープされる(例えば、N−−)ことも可能になり得る。

【0014】

1つの実施形態では、傾斜イオン注入は、各ステップにおいて合計のイオン注入の一部が導入される別個のステップに分解される。各ステップの間に、ウェーハはイオン注入を開口36の各側面に向けるように回転される。この実施形態では、ウェーハは0度のウェーハ回転において総量の四半分(1/4)を注入される。その後、ウェーハは90度回転されて、総量のもう四半分を注入される。その後、ウェーハはさらに90度回転されて、総量のもう四半分を注入される。その後、ウェーハはさらに90度回転されて、総量の最後の四半分を注入される。

【0015】

図6は、マスク層34の上および開口36の中に金属層42が形成された後の、図5の半導体構造10の断面図を示す。1つの実施形態では、金属層42は一面を覆って堆積され、基板12内の開口36をマスク層34およびILD層32が覆いかぶさっているため、結果として開口36を閉じる。1つの実施形態では、金属層42はチタン層、チタン層の上の窒化チタン層、および窒化チタン層の上のタングステン層を含む。このように、チタン層が開口36の側壁に沿ってドープ領域40に隣接して形成され、その後チタン層に隣接して窒化チタン層が形成され、その後窒化チタン層に隣接してタングステン層が形成される。代替的には、材料の他の堆積物が使用されてもよく、他の金属が使用されてもよい。

【0016】

図7は、金属エッチバックが実行された後の図6の半導体構造10の断面図を示す。金属エッチバックはマスク層34の大部分を除去し、金属層42によって以前に被覆された開口36を再び開く。

【0017】

図8は、マスク層34の残留部分の上および開口36の中に、金属層42に隣接して金属層44が形成された後の、図7の半導体構造10の断面図を示す。1つの実施形態では、金属層44は一面を覆って堆積され、金属層42と同じである。例えば、金属層44も、チタン、窒化チタン、およびタングステンから成る堆積物である。それゆえ、開口36内で、金属層42および金属層44は、開口36の両側の側壁に沿った金属層間の単一の継ぎ目を含むことができる、結合メタルフィルを形成する。

【0018】

図9は、金属エッチバックが実行された後の図8の半導体構造10の断面図を示す。それゆえ、金属エッチバックの後、開口36内の金属は平坦化され、結果として初期形成のTSV46が生じ、ドープ領域40はTSV46と直接接触する(TSV46の金属と直接接触する)。なお、TSVの形成は後続の処理が実行されるまで完了しない。例えば、ILD32の上に任意の数の相互接続層が形成されることができ、その相互接続層の上に最終的な保護層が形成されることができる。最終的な保護層が形成された後、処理は基板12の裏面において継続し得る。例えば、基板12の裏面においてTSV46を露出させるために裏面研磨が実行される。その後、半導体構造10を完成させるために、基板12の裏面においてさらなる処理が実行され得る。例えば、TSV46は、ソース30が基板12の裏面において接地に結合されることを可能にする。

【0019】

図9において示されているように、ドープ領域40はTSV46を取り囲み、基板12内に十分深く延在してドレイン28に高電圧が印加されることによってドレイン漏れ電流が導入されることを防止する。例えば、ドレイン領域(またはドリフト領域)が基板12内に基板12の上面からどの程度まで延在しているかを表す深さ50は、0.5〜2マイクロメートルの範囲内にあることができ、一方で、ドープ領域40が基板12内でTSV46の側壁に沿って基板12の上面からどの程度まで延在しているかを表す深さ52は、10マイクロメートル以上、20マイクロメートル以上、もしくは25マイクロメートル以上、または30マイクロメートル以上であることができる。1つの実施形態では、深さ52は深さ50の十倍以上である。1つの実施形態では、深さ52は10〜30マイクロメートルである。1つの実施形態では、深さ52は深さ50よりも少なくとも5倍大きい。

【0020】

1つの実施形態では、結果としてTSV46の金属と低抗率の高い基板12との間に高濃度ドープ領域をもたらすドープ領域40は、ドレイン領域に高電圧が印加されてドレイン領域から空乏領域が拡散すると、電荷担体を供給するバッファ領域を形成する。それゆえ、高濃度ドープ領域40が存在することにより、TSV46の抵抗接点がドレイン空乏領域からの突き抜け現象から保護され、ドープ領域40がない場合のドレイン漏れ電流と比較してドレイン漏れ電流が低減される。ドープ領域40の存在によってTSV46の挙動が変化することに起因して、ドレイン漏れはTSV46とドリフト領域20との間の距離48に左右されなくなる。それゆえ、TSVとデバイスとの電流間隔要件を変更する必要はない。

【0021】

図10は、代替の実施形態による図4の半導体構造10の断面図を示し、パターニングマスク層34の上および開口36内にin−situドープ多結晶シリコン層60が形成される。1つの実施形態では、多結晶シリコン層60は基板12の上に一面を覆って堆積され、それによって、開口36の側壁に沿って生じる。多結晶シリコン層60は、同じく開口36の側壁に沿って高濃度ドープ領域を形成する、説明されたドープ領域40に類似の、開口36の側壁に沿った高濃度ドープ領域を形成する。それゆえ、開口36内の多結晶シリコン層60はドープ領域60と称される場合がある。ドープ領域60は、基板12のドーピングと同じ導電型のドーピングを有することができるが、基板12のドーパント濃度よりも高いドーパント濃度による高濃度ドープ領域である。例えば、ドープ領域60のドーパント濃度は、基板12のドーパント濃度を、百倍を上回って、または一万倍を上回って超える場合がある。1つの実施形態では、ドープ領域60は、P+の導電型のin situドーピングによって形成されている場合がある。例えば、ホウ素のようなP型ドーパントが使用されることができる。in−situドープされた多結晶シリコンの場合、ドーパントは注入されず、多結晶シリコンの堆積中に導入される。ドーピングレベルは1e15〜1e20であることができる。さらに、この実施形態では、基板12は代替的にN−−であってもよい。

【0022】

図11は、開口36に金属を充填してTSV62を形成した後の図10の半導体構造10の断面図を示す。なお、TSV46を形成するために使用された同じ処理(上記図6〜図9に記載されたステップなど)が、ここでTSV62を形成するために繰り返されることができる。さらに、なお、ドープ領域40によって提供される効果が、TSV62に沿ってドープ領域60(TSV62を取り囲みTSV62の金属と直接接触する)によっても提供される。すなわち、高濃度ドープ領域60、TSV62の存在は、保護されている抵抗接点の挙動を説明し、ドレイン漏れ電流が低減される。さらに、TSVとデバイスとの電流間隔要件を変更する必要はない。

【0023】

図11に示される処理段階の後、処理はILD32の上に任意の数の相互接続層を形成することに続くことができ、その相互接続層の上に最終的な保護層が形成されることができる。最終的な保護層が形成された後、処理は基板12の裏面において継続し得る。例えば、基板12の裏面においてTSV62を露出させるために裏面研磨が実行される。その後、半導体構造10を完成させるために、基板12の裏面においてさらなる処理が実行され得る。例えば、TSV62は、ソース30が基板12の裏面において接地に結合されることを可能にする。さらに、なお、ドープ領域40とは異なり、ドープ領域62はTSV62の全長にわたって延在する。それゆえ、ドープ領域62は、ドープ領域40と比較して基板12内により深く延在している。

【0024】

図9または図11のいずれかを参照して、周囲に高濃度ドープ領域(P+ドープ領域40または60など)を有するTSVは、PIN構造のアノードを形成し、N型ドリフト領域20がPIN構造のカソードを形成し、カソードとアノードとの間の基板12が「I」領域に対応することに留意されたい。それゆえ、逆バイアス下で、アノードとカソードとの間の基板12は、キャリアを一掃されることになり(従って実質的に空乏する)、それによって導電性が非常に低い領域が確立され、隣接するデバイスとの相互作用を最小限に抑えることが可能となる。このようにして、図1〜図11のLDMOSデバイスのドレイン漏れ電流が低減される。

【0025】

図12は、基板110と、基板110の上面内に形成され、基板110内に深く延在するTSV102とを含むPIN構造100を3次元形式で示す。基板100は、TSV102を完全に取り囲みTSV102と接触するドープ領域104を含む。TSV102およびドープ領域104は、TSV46およびドープ領域40またはTSV62およびドープ領域60に関連して上述したものと同じように形成されることができることに留意されたい。構造100は、TSV102およびドープ領域104から側方に離間される、基板110の上面内に形成されるドープ領域108も含む。ドープ領域108は、既知のパターニングおよびドーピング技法を使用して形成されることができる。構造100は、基板110の上に誘電体層106も含む。1つの実施形態では、基板110は第1の導電型および第1の濃度(P−−など)のバックグラウンドドーピングを有し、ドープ領域104は第1の導電型であるが基板110よりも濃度の高い(P+など)ドーピングを有し、ドープ領域108は第1の導電型と反対の第2の導電型の(N+など)ドーピングを有する。例えば、1つの実施形態において、ドープ領域04のドーパント濃度は、基板110のドーパント濃度を、百倍を上回って、または一万倍を上回って超える。TSV102を取り囲むドープ領域104はPIN構造のアノードを形成し、ドープ領域108はPIN構造のカソードを形成し、カソードとアノードとの間の基板領域はPINの真性領域に対応する。上述のように、逆バイアス下で、アノードとカソードとの間の基板110は完全に空乏することになり、従って誘電体として振る舞う。それゆえ、この完全に空乏した領域は、低損失の高周波数素子を形成するための強化された基板として使用されることができる。

【0026】

例えば、1つの実施形態において、ドープ領域108は、上述の図1〜図11のLDMOSデバイス16のドープ領域20または26に対応することができる。それゆえ、上記で提供された寸法およびドープ領域40とドリフト領域20との間の寸法の比較は、それぞれドープ領域104およびドープ領域108にも当てはまる。例えば、ドープ領域108は基板110内で基板110の上面から0.5〜2マイクロメートル延在することができ、ドープ領域104は基板110内でTSV192の側壁に沿って基板110の上面から10マイクロメートル以上延在することができる。代替的に、ドープ領域104は基板110内に20マイクロメートル以上、25マイクロメートル以上、または30マイクロメートル以上延在することができる。1つの実施形態では、ドープ領域104はドープ領域108よりも十倍以上基板110内に延在する。代替の実施形態では、N型ドープ領域がPIN構造のためのカソードを形成し、結果として完全に空乏した基板をもたらすことができるように、TSV102を接地接続のために使用するN型ドープ領域を有する他の種類のデバイスが形成されてもよい。

【0027】

1つの実施形態では、ドープ領域108は、TSV102を取り囲むかまたは取り巻くように形成されることができ、(PIN構造の完全に空乏した領域内で)ドープ領域104と108との間の基板110内にデバイスが形成されることができる。1つの実施形態では、ドープ領域108はTSV102の周りにリングを形成する。図13および図14は、PIN構造の完全に空乏した領域の上に反応性受動素子が形成される、図12のPIN構造100を示す。図13および図14の例において、ドープ領域108は、TSV102および反応性受動素子を取り巻いている。同様の参照符号は同様の要素を示すのに使用されていることに留意されたい。

【0028】

図13は、ドープ領域104と108の間で基板110の完全に空乏した領域の上および中に伝送線路112が形成されているPIN構造100を示す。図14は、基板100の完全に空乏した領域の上および中にインダクタ114があるPIN構造100を示す。図14において、インダクタ114の第1の端子は接地に接続するためにTSV102に接続されている。さらに、図14において、ドープ領域108はTSV102の周りにリングを形成し、TSV102がそのリングの中心にあることができる。

【0029】

従って、ここまでで、TSVの金属と半導体基板との間に高濃度ドープ領域を有する、改善されたTSVが提供されたことが理解されるべきである。TSVを取り囲む高濃度ドープ領域と共に、反対の導電型のドープ領域がPIN構造を形成することができる。反対の導電型のドープ領域は例えば、LDMOSデバイスのドリフト領域、または、その中にデバイスが形成されることができる、TSVの周りのリングに対応することができる。このようにして、逆バイアス時に完全に空乏した領域が基板内に形成されることができ、従って、高電圧および高周波数用途におけるような、改善した動作が可能になる。

【0030】

本発明は特定の導電型または電位の極性に関して記載されているが、当業者には導電型および電位の極性は逆になってもよいことが理解される。

その上、本明細書および特許請求の範囲における「正面(front)」、「裏(back)」、「上部(top)」、「底(bottom)」、「上(over)」、「下(under)」などの用語は、存在する場合、説明を目的として使用されており、必ずしも永久的な相対位置を記述するために使用されてはいない。このように使用される用語は、本明細書に記載されている本発明の実施形態が例えば、本明細書において例示または他の様態で記載されている以外の方向で動作することが可能であるように、適切な状況下で置き換え可能であることが理解される。

【0031】

本明細書において、具体的な実施形態を参照して本発明を説明したが、添付の特許請求の範囲に明記されているような本発明の範囲から逸脱することなくさまざまな改変および変更を為すことができる。例えば、TSVは任意の種類のデバイスまたはトランジスタに対して裏面接続を提供するために形成されることができる。従って、本明細書および図面は限定的な意味ではなく例示とみなされるべきであり、すべてのこのような改変が本発明の範囲内に含まれることが意図されている。本明細書において具体的な実施形態に関して記載されているいかなる利益、利点、または問題に対する解決策も、任意のまたはすべての請求項の重要な、必要とされる、または基本的な特徴または要素として解釈されるようには意図されていない。

【0032】

本明細書において使用される場合、「結合されている」という用語は、直接結合または機械的結合に限定されるようには意図されていない。

さらに、本明細書において使用される場合、「1つ(“a” or “an”)」という用語は、1つまたは2つ以上として定義される。さらに、特許請求の範囲における「少なくとも1つの」および「1つまたは複数の」のような前置きの語句の使用は、不定冠詞「1つの (狽# or 狽≠飼)」による別の請求項要素の導入が、このように導入された請求項要素を含む任意の特定の請求項を、たとえ同じ請求項が前置きの語句「1つまたは複数の」または「少なくとも1つの」および「1つの (狽# or 狽≠飼)」のような不定冠詞を含む場合であっても、1つだけのこのような要素を含む発明に限定することを暗示するように解釈されるべきではない。同じことが、定冠詞の使用についても当てはまる。

【0033】

別途記載されない限り、「第1の」および「第2の」のような用語は、そのような用語が説明する要素間で適宜区別するように使用される。従って、これらの用語は必ずしも、このような要素の時間的なまたは他の優先順位付けを示すようには意図されていない。

【0034】

以下は本発明のさまざまな実施形態である。

項目1は、半導体デバイス構造であって、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含み、当該基板を貫通する基板貫通バイア(TSV)と、基板の第1の面上のデバイスであって、当該デバイスは、第2の導電型の第1のドープ領域を有する、デバイスと、TSVの周りの第2のドープ領域であって、当該第2のドープ領域は、第1の濃度よりも高い第2の濃度および第1の導電型であるドーピングを有する、第2のドープ領域とを含む、半導体デバイス構造を含む。項目2は、デバイスが、TSVに結合される側方拡散MOS(LDMOS)トランジスタである、項目1の半導体デバイス構造を含む。項目3は、LDMOSトランジスタが、TSVに結合される第1の導電型の本体接続を有する、項目2の半導体デバイス構造を含む。項目4は、第2のドープ領域が、本体接続の深さを下回る、基板内のある深さまで延在する、項目3の半導体デバイス構造を含む。項目5は、第1のドープ領域が、本体接続に隣接するLDMOSトランジスタのソースである、項目3の半導体デバイス構造を含む。項目6は、LDMOSトランジスタがゲートを有し、ソースがゲートの1つの側面に整列する、項目5の半導体デバイス構造を含む。項目7は、第2のドープ領域がTSVと直接接触する、項目1の半導体デバイス構造を含む。項目8は、第1のドープ領域が、基板の第1の面の下で第1の深さまで延在する、LDMOSトランジスタのドリフト領域を含み、第2のドープ領域が基板の第1の面の下で第2の深さまで延在し、第2の深さは第1の深さよりも大きい、項目1の半導体デバイス構造を含む。項目9は、第2の深さが第1の深さの十倍以上大きい、項目8の半導体デバイス構造を含む。項目10は、第1のドープ領域がTSVを取り巻いている、項目1の半導体デバイス構造を含む。項目11は、第2の濃度が第1の濃度の百倍よりも大きい、項目1の半導体デバイス構造を含む。項目12は、第2の濃度が第1の濃度の一万倍よりも大きい、項目11の半導体デバイス構造を含む。項目13は、LDMOSトランジスタが、基板の第1の面の下で第1の深さまで延在するドリフト領域を有し、ドープ領域が基板の第1の面の下で第2の深さまで延在し、第2の深さは第1の深さよりも少なくとも5倍大きい、項目12の半導体デバイス構造を含む。

【0035】

項目14は、半導体デバイス構造であって、半導体基板であって、当該半導体基板を第1の面から第2の面まで貫通するバイアを有する、半導体基板と、第1のドープ領域を有する第1の面上のデバイスと、バイアの周りにあって当該バイアと接触する第2のドープ領域とを含み、基板は第1の濃度のバックグラウンドドーピングレベルを有し、基板は第1の導電型を有し、第1のドープ領域は第2の導電型であるとともに基板の下で第1の深さを有し、第2のドープ領域は基板の下で第2の深さを有し、第2の深さは第1の深さよりも大きく、第2のドープ領域は第2の濃度のドーピングレベルを有し、第2の濃度は第1の濃度よりも大きい、半導体デバイス構造を含む。項目15は、第1のドープ領域がLDMOSデバイスのドリフト領域を含む、項目14の半導体デバイス構造を含む。項目16は、第1のドープ領域が第2のドープ領域を取り巻いている、項目14の半導体デバイス構造を含む。

【0036】

項目17は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する半導体基板を使用して半導体デバイス構造を形成する方法であって、第2の導電型の第1のドープ領域を有する半導体基板の第1の面の中および上にデバイスを形成することであって、第2のドープ領域は第1の面の下で第1の深さを有する、形成することと、基板の第1の面と第2の面との間に延在する、基板を貫通する開口を形成することと、第2のドープ領域を形成することであって、第2のドープ領域は、第1の面から第1の深さより大きい第2の深さまで延在する開口内にあり、第1の濃度よりも大きい第2の濃度を有し、第1の導電型である、形成することと、開口に金属を充填することであって、金属は第2のドープ領域と接触する、充填することを含む、方法を含む。項目18は、第2のドープ領域を形成することが、開口内にin−situドープ多結晶シリコンを堆積することを含む、項目17の方法を含む。項目19は、第2のドープ領域を形成することが、第2の深さまで開口の側壁にドーパントを付加するためのイオン注入を実行することを含む、項目17の方法を含む。項目20は、デバイスを形成することが、第1のドープ領域としてのドリフト領域、および開口の周りの第1の面上のリングを有する側方拡散MOS(LDMOS)トランジスタから成る群のうちの1つを形成することを含み、リングは第1のドープ領域である、項目17の方法を含む。

【符号の説明】

【0037】

10…半導体デバイス構造、12…基板、14…ゲート、16…LDMOSデバイス、36…基板貫通バイア。

【技術分野】

【0001】

本発明は半導体製造一般に関する。より詳細には、基板貫通バイア(TSV)を有する半導体構造、およびその製造方法に関する。

【背景技術】

【0002】

現在の半導体技術では、集積回路基板の上面から集積回路基板の裏面までの接続経路を設けるために基板貫通バイアを使用することがある。これによって、集積回路への裏面接続が可能となる。例えば、基板貫通バイアは接地への裏面接続を行うために使用され得る。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許第7633165号明細書

【特許文献2】米国特許第7884016号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は基板貫通バイア(TSV)を有する半導体構造およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

本発明の1つの実施形態では、裏面接地接続などに用いる、基板の上面のデバイスから基板の裏面までの経路を提供するために基板貫通バイアが使用される。このデバイスは、RFまたは電力増幅用途などの高電圧用途のためのLDMOSデバイスであってもよい。LDMOSデバイスは、それらの絶縁破壊電圧が高いためにこのような高電圧用途に使用されることができる。1つの実施形態では、LDOMSデバイスのソースに対する裏面接地接続を提供するために基板貫通バイアが使用される。1つの実施形態では、20ボルト以上の高電圧がLDMOSデバイスのドレインに印加される。しかしながら、デバイスのドレインに高電圧が印加されてソースが接地に接続されることによって、大きなドレイン漏れ電流が観測される場合がある。このドレイン漏れ電流は、印加されるドレイン電圧、およびLDMOSデバイスのドレイン領域のTSVに対する近接性、ならびに不純物濃度に左右される。高密度設計では、このドレイン漏れを低減するために必要とされるLDMOSデバイスと基板貫通バイアとの間の間隔が大きすぎる。それゆえ、1つの実施形態では、基板貫通バイアと基板との間の金属−半導体接触界面の物理的特性を変化させるために、基板貫通バイアの側壁にそって高濃度ドープされた領域が形成され、その結果として、ドレイン漏れ電流が低減され、初期逆バイアスドレイン−ソース接合破壊が妨げられる。このように、現行の基板貫通バイアの間隔要件を変更する必要はない。

【0006】

さらに、(LDMOSデバイスに加えて)他の種類のデバイスが(裏面接地接続のような)裏面接続のためにこれらの基板貫通バイアを使用してもよい。例えば、基板貫通バイアの側壁に沿って形成される高濃度ドープされた領域は、PINダイオードの真性領域(「I」領域)に類似の大きな空乏領域が作成されることを可能にする。このPIN構造は、適切なカソード設計が利用される場合(このカソード設計は、基板貫通バイアの側壁に沿った高濃度ドープ領域の導電型と反対の導電型にドープされた領域を含む)、高周波数受動素子のようなさまざまな種類のデバイスのための低損失基板を形成するために利用されることができる。

【図面の簡単な説明】

【0007】

【図1】本開示の1つの実施形態による、初期処理段階における半導体構造を示す断面図。

【図2】本発明の1つの実施形態による、図1の半導体構造の後の処理工程を示す断面図。

【図3】本発明の1つの実施形態による、図2の半導体構造の後の処理工程を示す断面図。

【図4】本発明の1つの実施形態による、図3の半導体構造の後の処理工程を示す断面図。

【図5】本発明の1つの実施形態による、図4の半導体構造の後の処理工程を示す断面図。

【図6】本発明の1つの実施形態による、図5の半導体構造の後の処理工程を示す断面図。

【図7】本発明の1つの実施形態による、図6の半導体構造の後の処理工程を示す断面図。

【図8】本発明の1つの実施形態による、図7の半導体構造の後の処理工程を示す断面図。

【図9】本発明の1つの実施形態による、図8の半導体構造の後の処理工程を示す断面図。

【図10】本発明の1つの実施形態による、図4の半導体構造の後の処理工程を示す断面図。

【図11】本発明の1つの実施形態による、図10の半導体構造の後の処理工程を示す断面図。

【図12】本発明の1つの実施形態によるPIN構造を三次元形式で示す斜視図。

【図13】本発明の1つの実施形態による、伝送線路を有するPIN構造を三次元形式で示す斜視図。

【図14】本発明の1つの実施形態による、インダクタコイルを有するPIN構造を三次元形式で示す斜視図。

【発明を実施するための形態】

【0008】

本発明は例として示されており、添付の図面によって限定されない。図面において、同様の参照符号は類似の要素を示す。図面内の要素は簡潔かつ明瞭にするために示されており、必ずしも原寸に比例して描かれてはいない。

図1は、基板12と、基板12の上面の中および上に形成されるLDMOSデバイス16とを有する半導体構造10の断面図を示す。なお、LDMOSデバイス16はLDMOSトランジスタとも称される場合がある。LDMOSデバイス16は、基板12の上面上に形成されるゲート14を含み、ゲート14は第1の側壁と、第1の側壁の反対側にある第2の側壁とを有する。LDMOSデバイス16は、基板12の上面の中に、ゲート14の下で、ゲート14の第2の側壁から側方に延在し、続いてゲート14の第1の側壁から第1の方向において側方に延在するドープ領域18を含む。LDMOSデバイス16は、基板12の上面の中に、ゲート14の第2の側壁から第2の方向において側方に延在するドープ領域20も含む。LDMOSデバイス16は、基板12の上面の中に、ゲート14の第1の側壁から第1の方向において側方に延在する(かつ、ゲート14の下には延在しない)ドープ領域24と、基板12の上面の中でドープ領域24に側方に隣接するドープ領域22も含む。ドープ領域22および24はドープ領域18内に位置しており、ドープ領域18はドープ領域24と比較して基板12内により深く延在しており、ドープ領域22はドープ領域18と比較して基板12内により深く延在している。LDMOSデバイス16は、基板12の上面の中で、ドープ領域20内にドープ領域26も含む。ドープ領域20は、ドープ領域26と比較して基板12内により深く延在している。ドープ領域26は、ゲート14の第2の側壁から側方に離間している。1つの実施形態では、当該領域はゲート14から1〜6マイクロメートルの範囲内の距離をおいて位置している。このゲート14からの側方の距離は、LDMOSデバイス16の絶縁破壊電圧を決定する要因の1つである。LDMOSデバイス16のソース領域30はドープ領域18および24を含み、ゲート14の一方の側面に対して整列しており、LDMOSデバイス16のドレイン領域28はドープ領域20および26を含む。ドープ領域22はLDMOSデバイス16の本体接続と称される場合がある。

【0009】

1つの実施形態では、基板12はシリコンである。基板12は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する。1つの実施形態では、基板12はP型ドーパントによって非常に低濃度にドープされ、従ってP−−のバックグラウンドドーピングを有する。1つの実施形態では、LDMOSデバイス16はP型基板内に形成されるN型デバイスである。この実施形態では、ドープ領域24および26はN+の導電性を有することができ、ドープ領域18はPの導電性を有することができ、ドープ領域22はP+の導電性を有することができる。ドープ領域20は、低濃度ドープドレインエクステンションまたはドリフト領域と称される場合がある。ドープ領域18は、側方拡散PウェルまたはPHV領域と称される場合がある。さらに、1つの実施形態では、基板12はP−−の代わりにN−−の導電性を有してもよい。基板12は非常に低濃度にドープされるため、基板12は高い抵抗率を有する。

【0010】

図2は、層間誘電体層(ILD)32およびマスク層34が形成された後の、図1の半導体構造10の断面図を示す。1つの実施形態では、ILD層32は、基板12の上面の上に一面を覆って堆積される誘電体層であり、化学機械研磨(CMP)などによって実質的に平坦化される。マスク層34は窒化物層のようなハードマスク層であることができ、ILD層32の上に一面を覆って堆積されることができる。

【0011】

図3は、マスク層34およびILD層32を貫通して開口36が形成された後の、図2の半導体構造10の断面図を示す。1つの実施形態では、マスク層34の上に、パターニングフォトレジスト層のようなパターニングマスク層が形成され、パターニングマスク層を使用してエッチングが実行されて開口36が形成される。その後、パターニングマスク層が除去される。

【0012】

図4は、開口36が基板12内に延在している図3の半導体構造10の断面図を示す。1つの実施形態では、エッチングは、基板12の大部分を貫通して開口36を延在させるためのマスクとしてのマスク層34内の開口36を使用して実行される。例えば、1つの実施形態では、開口36は基板12内に少なくとも70マイクロメートル延在する。なお、開口36は基板12の裏面まで完全には延在しない。さらに、開口36はTSVの形成に使用されることになる開口である。

【0013】

図5は、結果として開口36の側壁に沿ってドープ領域40をもたらすための傾斜イオン注入38が実行されている、図4の半導体構造10の断面図を示す。イオン注入領域40は、TSV空乏障壁領域と称される場合がある。示されている実施形態では、傾斜イオン注入38は、開口36の側壁内にドーパントを導入するための一連の傾斜イオン注入を含むことができる。開口36内の深さおよびドープ領域40の開口36の側壁に沿った厚さは、ドーパントの種類、ドーパントのドーズ量、およびドーパントのエネルギーのようなイオン注入のパラメータに応じて決まる。1つの実施形態では、ドープ領域40は、基板12の上面から測定して基板12内に少なくとも20マイクロメートル延在する。1つの実施形態では、ドープ領域40は、開口36の側壁に沿った0.1〜0.2マイクロメートルの範囲内の厚さ、および、開口36内により深く延在するテーパを有する。ドープ領域40は、基板12のバックグラウンドドーパント濃度よりも高いドーパント濃度を有する、高濃度ドープされたP型領域(例えば、P+領域)である。例えば、ドープ領域40のドーパント濃度は、基板12のドーパント濃度を、百倍を上回って、または一万倍を上回って超える場合がある。1つの実施形態では、基板12がP−−などである場合、ドープ領域40はP+のドーピングを有する場合がある。例えば、ホウ素のようなP型ドーパントが使用される。この例では、イオン注入領域40を形成するために、80keVのエネルギーにおける1e15のドーズ量が垂直から7度の注入角で使用されることができる。なお、P+ドープ領域40が存在することによって、基板12がN型ドーパントを用いて非常に低濃度にドープされる(例えば、N−−)ことも可能になり得る。

【0014】

1つの実施形態では、傾斜イオン注入は、各ステップにおいて合計のイオン注入の一部が導入される別個のステップに分解される。各ステップの間に、ウェーハはイオン注入を開口36の各側面に向けるように回転される。この実施形態では、ウェーハは0度のウェーハ回転において総量の四半分(1/4)を注入される。その後、ウェーハは90度回転されて、総量のもう四半分を注入される。その後、ウェーハはさらに90度回転されて、総量のもう四半分を注入される。その後、ウェーハはさらに90度回転されて、総量の最後の四半分を注入される。

【0015】

図6は、マスク層34の上および開口36の中に金属層42が形成された後の、図5の半導体構造10の断面図を示す。1つの実施形態では、金属層42は一面を覆って堆積され、基板12内の開口36をマスク層34およびILD層32が覆いかぶさっているため、結果として開口36を閉じる。1つの実施形態では、金属層42はチタン層、チタン層の上の窒化チタン層、および窒化チタン層の上のタングステン層を含む。このように、チタン層が開口36の側壁に沿ってドープ領域40に隣接して形成され、その後チタン層に隣接して窒化チタン層が形成され、その後窒化チタン層に隣接してタングステン層が形成される。代替的には、材料の他の堆積物が使用されてもよく、他の金属が使用されてもよい。

【0016】

図7は、金属エッチバックが実行された後の図6の半導体構造10の断面図を示す。金属エッチバックはマスク層34の大部分を除去し、金属層42によって以前に被覆された開口36を再び開く。

【0017】

図8は、マスク層34の残留部分の上および開口36の中に、金属層42に隣接して金属層44が形成された後の、図7の半導体構造10の断面図を示す。1つの実施形態では、金属層44は一面を覆って堆積され、金属層42と同じである。例えば、金属層44も、チタン、窒化チタン、およびタングステンから成る堆積物である。それゆえ、開口36内で、金属層42および金属層44は、開口36の両側の側壁に沿った金属層間の単一の継ぎ目を含むことができる、結合メタルフィルを形成する。

【0018】

図9は、金属エッチバックが実行された後の図8の半導体構造10の断面図を示す。それゆえ、金属エッチバックの後、開口36内の金属は平坦化され、結果として初期形成のTSV46が生じ、ドープ領域40はTSV46と直接接触する(TSV46の金属と直接接触する)。なお、TSVの形成は後続の処理が実行されるまで完了しない。例えば、ILD32の上に任意の数の相互接続層が形成されることができ、その相互接続層の上に最終的な保護層が形成されることができる。最終的な保護層が形成された後、処理は基板12の裏面において継続し得る。例えば、基板12の裏面においてTSV46を露出させるために裏面研磨が実行される。その後、半導体構造10を完成させるために、基板12の裏面においてさらなる処理が実行され得る。例えば、TSV46は、ソース30が基板12の裏面において接地に結合されることを可能にする。

【0019】

図9において示されているように、ドープ領域40はTSV46を取り囲み、基板12内に十分深く延在してドレイン28に高電圧が印加されることによってドレイン漏れ電流が導入されることを防止する。例えば、ドレイン領域(またはドリフト領域)が基板12内に基板12の上面からどの程度まで延在しているかを表す深さ50は、0.5〜2マイクロメートルの範囲内にあることができ、一方で、ドープ領域40が基板12内でTSV46の側壁に沿って基板12の上面からどの程度まで延在しているかを表す深さ52は、10マイクロメートル以上、20マイクロメートル以上、もしくは25マイクロメートル以上、または30マイクロメートル以上であることができる。1つの実施形態では、深さ52は深さ50の十倍以上である。1つの実施形態では、深さ52は10〜30マイクロメートルである。1つの実施形態では、深さ52は深さ50よりも少なくとも5倍大きい。

【0020】

1つの実施形態では、結果としてTSV46の金属と低抗率の高い基板12との間に高濃度ドープ領域をもたらすドープ領域40は、ドレイン領域に高電圧が印加されてドレイン領域から空乏領域が拡散すると、電荷担体を供給するバッファ領域を形成する。それゆえ、高濃度ドープ領域40が存在することにより、TSV46の抵抗接点がドレイン空乏領域からの突き抜け現象から保護され、ドープ領域40がない場合のドレイン漏れ電流と比較してドレイン漏れ電流が低減される。ドープ領域40の存在によってTSV46の挙動が変化することに起因して、ドレイン漏れはTSV46とドリフト領域20との間の距離48に左右されなくなる。それゆえ、TSVとデバイスとの電流間隔要件を変更する必要はない。

【0021】

図10は、代替の実施形態による図4の半導体構造10の断面図を示し、パターニングマスク層34の上および開口36内にin−situドープ多結晶シリコン層60が形成される。1つの実施形態では、多結晶シリコン層60は基板12の上に一面を覆って堆積され、それによって、開口36の側壁に沿って生じる。多結晶シリコン層60は、同じく開口36の側壁に沿って高濃度ドープ領域を形成する、説明されたドープ領域40に類似の、開口36の側壁に沿った高濃度ドープ領域を形成する。それゆえ、開口36内の多結晶シリコン層60はドープ領域60と称される場合がある。ドープ領域60は、基板12のドーピングと同じ導電型のドーピングを有することができるが、基板12のドーパント濃度よりも高いドーパント濃度による高濃度ドープ領域である。例えば、ドープ領域60のドーパント濃度は、基板12のドーパント濃度を、百倍を上回って、または一万倍を上回って超える場合がある。1つの実施形態では、ドープ領域60は、P+の導電型のin situドーピングによって形成されている場合がある。例えば、ホウ素のようなP型ドーパントが使用されることができる。in−situドープされた多結晶シリコンの場合、ドーパントは注入されず、多結晶シリコンの堆積中に導入される。ドーピングレベルは1e15〜1e20であることができる。さらに、この実施形態では、基板12は代替的にN−−であってもよい。

【0022】

図11は、開口36に金属を充填してTSV62を形成した後の図10の半導体構造10の断面図を示す。なお、TSV46を形成するために使用された同じ処理(上記図6〜図9に記載されたステップなど)が、ここでTSV62を形成するために繰り返されることができる。さらに、なお、ドープ領域40によって提供される効果が、TSV62に沿ってドープ領域60(TSV62を取り囲みTSV62の金属と直接接触する)によっても提供される。すなわち、高濃度ドープ領域60、TSV62の存在は、保護されている抵抗接点の挙動を説明し、ドレイン漏れ電流が低減される。さらに、TSVとデバイスとの電流間隔要件を変更する必要はない。

【0023】

図11に示される処理段階の後、処理はILD32の上に任意の数の相互接続層を形成することに続くことができ、その相互接続層の上に最終的な保護層が形成されることができる。最終的な保護層が形成された後、処理は基板12の裏面において継続し得る。例えば、基板12の裏面においてTSV62を露出させるために裏面研磨が実行される。その後、半導体構造10を完成させるために、基板12の裏面においてさらなる処理が実行され得る。例えば、TSV62は、ソース30が基板12の裏面において接地に結合されることを可能にする。さらに、なお、ドープ領域40とは異なり、ドープ領域62はTSV62の全長にわたって延在する。それゆえ、ドープ領域62は、ドープ領域40と比較して基板12内により深く延在している。

【0024】

図9または図11のいずれかを参照して、周囲に高濃度ドープ領域(P+ドープ領域40または60など)を有するTSVは、PIN構造のアノードを形成し、N型ドリフト領域20がPIN構造のカソードを形成し、カソードとアノードとの間の基板12が「I」領域に対応することに留意されたい。それゆえ、逆バイアス下で、アノードとカソードとの間の基板12は、キャリアを一掃されることになり(従って実質的に空乏する)、それによって導電性が非常に低い領域が確立され、隣接するデバイスとの相互作用を最小限に抑えることが可能となる。このようにして、図1〜図11のLDMOSデバイスのドレイン漏れ電流が低減される。

【0025】

図12は、基板110と、基板110の上面内に形成され、基板110内に深く延在するTSV102とを含むPIN構造100を3次元形式で示す。基板100は、TSV102を完全に取り囲みTSV102と接触するドープ領域104を含む。TSV102およびドープ領域104は、TSV46およびドープ領域40またはTSV62およびドープ領域60に関連して上述したものと同じように形成されることができることに留意されたい。構造100は、TSV102およびドープ領域104から側方に離間される、基板110の上面内に形成されるドープ領域108も含む。ドープ領域108は、既知のパターニングおよびドーピング技法を使用して形成されることができる。構造100は、基板110の上に誘電体層106も含む。1つの実施形態では、基板110は第1の導電型および第1の濃度(P−−など)のバックグラウンドドーピングを有し、ドープ領域104は第1の導電型であるが基板110よりも濃度の高い(P+など)ドーピングを有し、ドープ領域108は第1の導電型と反対の第2の導電型の(N+など)ドーピングを有する。例えば、1つの実施形態において、ドープ領域04のドーパント濃度は、基板110のドーパント濃度を、百倍を上回って、または一万倍を上回って超える。TSV102を取り囲むドープ領域104はPIN構造のアノードを形成し、ドープ領域108はPIN構造のカソードを形成し、カソードとアノードとの間の基板領域はPINの真性領域に対応する。上述のように、逆バイアス下で、アノードとカソードとの間の基板110は完全に空乏することになり、従って誘電体として振る舞う。それゆえ、この完全に空乏した領域は、低損失の高周波数素子を形成するための強化された基板として使用されることができる。

【0026】

例えば、1つの実施形態において、ドープ領域108は、上述の図1〜図11のLDMOSデバイス16のドープ領域20または26に対応することができる。それゆえ、上記で提供された寸法およびドープ領域40とドリフト領域20との間の寸法の比較は、それぞれドープ領域104およびドープ領域108にも当てはまる。例えば、ドープ領域108は基板110内で基板110の上面から0.5〜2マイクロメートル延在することができ、ドープ領域104は基板110内でTSV192の側壁に沿って基板110の上面から10マイクロメートル以上延在することができる。代替的に、ドープ領域104は基板110内に20マイクロメートル以上、25マイクロメートル以上、または30マイクロメートル以上延在することができる。1つの実施形態では、ドープ領域104はドープ領域108よりも十倍以上基板110内に延在する。代替の実施形態では、N型ドープ領域がPIN構造のためのカソードを形成し、結果として完全に空乏した基板をもたらすことができるように、TSV102を接地接続のために使用するN型ドープ領域を有する他の種類のデバイスが形成されてもよい。

【0027】

1つの実施形態では、ドープ領域108は、TSV102を取り囲むかまたは取り巻くように形成されることができ、(PIN構造の完全に空乏した領域内で)ドープ領域104と108との間の基板110内にデバイスが形成されることができる。1つの実施形態では、ドープ領域108はTSV102の周りにリングを形成する。図13および図14は、PIN構造の完全に空乏した領域の上に反応性受動素子が形成される、図12のPIN構造100を示す。図13および図14の例において、ドープ領域108は、TSV102および反応性受動素子を取り巻いている。同様の参照符号は同様の要素を示すのに使用されていることに留意されたい。

【0028】

図13は、ドープ領域104と108の間で基板110の完全に空乏した領域の上および中に伝送線路112が形成されているPIN構造100を示す。図14は、基板100の完全に空乏した領域の上および中にインダクタ114があるPIN構造100を示す。図14において、インダクタ114の第1の端子は接地に接続するためにTSV102に接続されている。さらに、図14において、ドープ領域108はTSV102の周りにリングを形成し、TSV102がそのリングの中心にあることができる。

【0029】

従って、ここまでで、TSVの金属と半導体基板との間に高濃度ドープ領域を有する、改善されたTSVが提供されたことが理解されるべきである。TSVを取り囲む高濃度ドープ領域と共に、反対の導電型のドープ領域がPIN構造を形成することができる。反対の導電型のドープ領域は例えば、LDMOSデバイスのドリフト領域、または、その中にデバイスが形成されることができる、TSVの周りのリングに対応することができる。このようにして、逆バイアス時に完全に空乏した領域が基板内に形成されることができ、従って、高電圧および高周波数用途におけるような、改善した動作が可能になる。

【0030】

本発明は特定の導電型または電位の極性に関して記載されているが、当業者には導電型および電位の極性は逆になってもよいことが理解される。

その上、本明細書および特許請求の範囲における「正面(front)」、「裏(back)」、「上部(top)」、「底(bottom)」、「上(over)」、「下(under)」などの用語は、存在する場合、説明を目的として使用されており、必ずしも永久的な相対位置を記述するために使用されてはいない。このように使用される用語は、本明細書に記載されている本発明の実施形態が例えば、本明細書において例示または他の様態で記載されている以外の方向で動作することが可能であるように、適切な状況下で置き換え可能であることが理解される。

【0031】

本明細書において、具体的な実施形態を参照して本発明を説明したが、添付の特許請求の範囲に明記されているような本発明の範囲から逸脱することなくさまざまな改変および変更を為すことができる。例えば、TSVは任意の種類のデバイスまたはトランジスタに対して裏面接続を提供するために形成されることができる。従って、本明細書および図面は限定的な意味ではなく例示とみなされるべきであり、すべてのこのような改変が本発明の範囲内に含まれることが意図されている。本明細書において具体的な実施形態に関して記載されているいかなる利益、利点、または問題に対する解決策も、任意のまたはすべての請求項の重要な、必要とされる、または基本的な特徴または要素として解釈されるようには意図されていない。

【0032】

本明細書において使用される場合、「結合されている」という用語は、直接結合または機械的結合に限定されるようには意図されていない。

さらに、本明細書において使用される場合、「1つ(“a” or “an”)」という用語は、1つまたは2つ以上として定義される。さらに、特許請求の範囲における「少なくとも1つの」および「1つまたは複数の」のような前置きの語句の使用は、不定冠詞「1つの (狽# or 狽≠飼)」による別の請求項要素の導入が、このように導入された請求項要素を含む任意の特定の請求項を、たとえ同じ請求項が前置きの語句「1つまたは複数の」または「少なくとも1つの」および「1つの (狽# or 狽≠飼)」のような不定冠詞を含む場合であっても、1つだけのこのような要素を含む発明に限定することを暗示するように解釈されるべきではない。同じことが、定冠詞の使用についても当てはまる。

【0033】

別途記載されない限り、「第1の」および「第2の」のような用語は、そのような用語が説明する要素間で適宜区別するように使用される。従って、これらの用語は必ずしも、このような要素の時間的なまたは他の優先順位付けを示すようには意図されていない。

【0034】

以下は本発明のさまざまな実施形態である。

項目1は、半導体デバイス構造であって、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含み、当該基板を貫通する基板貫通バイア(TSV)と、基板の第1の面上のデバイスであって、当該デバイスは、第2の導電型の第1のドープ領域を有する、デバイスと、TSVの周りの第2のドープ領域であって、当該第2のドープ領域は、第1の濃度よりも高い第2の濃度および第1の導電型であるドーピングを有する、第2のドープ領域とを含む、半導体デバイス構造を含む。項目2は、デバイスが、TSVに結合される側方拡散MOS(LDMOS)トランジスタである、項目1の半導体デバイス構造を含む。項目3は、LDMOSトランジスタが、TSVに結合される第1の導電型の本体接続を有する、項目2の半導体デバイス構造を含む。項目4は、第2のドープ領域が、本体接続の深さを下回る、基板内のある深さまで延在する、項目3の半導体デバイス構造を含む。項目5は、第1のドープ領域が、本体接続に隣接するLDMOSトランジスタのソースである、項目3の半導体デバイス構造を含む。項目6は、LDMOSトランジスタがゲートを有し、ソースがゲートの1つの側面に整列する、項目5の半導体デバイス構造を含む。項目7は、第2のドープ領域がTSVと直接接触する、項目1の半導体デバイス構造を含む。項目8は、第1のドープ領域が、基板の第1の面の下で第1の深さまで延在する、LDMOSトランジスタのドリフト領域を含み、第2のドープ領域が基板の第1の面の下で第2の深さまで延在し、第2の深さは第1の深さよりも大きい、項目1の半導体デバイス構造を含む。項目9は、第2の深さが第1の深さの十倍以上大きい、項目8の半導体デバイス構造を含む。項目10は、第1のドープ領域がTSVを取り巻いている、項目1の半導体デバイス構造を含む。項目11は、第2の濃度が第1の濃度の百倍よりも大きい、項目1の半導体デバイス構造を含む。項目12は、第2の濃度が第1の濃度の一万倍よりも大きい、項目11の半導体デバイス構造を含む。項目13は、LDMOSトランジスタが、基板の第1の面の下で第1の深さまで延在するドリフト領域を有し、ドープ領域が基板の第1の面の下で第2の深さまで延在し、第2の深さは第1の深さよりも少なくとも5倍大きい、項目12の半導体デバイス構造を含む。

【0035】

項目14は、半導体デバイス構造であって、半導体基板であって、当該半導体基板を第1の面から第2の面まで貫通するバイアを有する、半導体基板と、第1のドープ領域を有する第1の面上のデバイスと、バイアの周りにあって当該バイアと接触する第2のドープ領域とを含み、基板は第1の濃度のバックグラウンドドーピングレベルを有し、基板は第1の導電型を有し、第1のドープ領域は第2の導電型であるとともに基板の下で第1の深さを有し、第2のドープ領域は基板の下で第2の深さを有し、第2の深さは第1の深さよりも大きく、第2のドープ領域は第2の濃度のドーピングレベルを有し、第2の濃度は第1の濃度よりも大きい、半導体デバイス構造を含む。項目15は、第1のドープ領域がLDMOSデバイスのドリフト領域を含む、項目14の半導体デバイス構造を含む。項目16は、第1のドープ領域が第2のドープ領域を取り巻いている、項目14の半導体デバイス構造を含む。

【0036】

項目17は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する半導体基板を使用して半導体デバイス構造を形成する方法であって、第2の導電型の第1のドープ領域を有する半導体基板の第1の面の中および上にデバイスを形成することであって、第2のドープ領域は第1の面の下で第1の深さを有する、形成することと、基板の第1の面と第2の面との間に延在する、基板を貫通する開口を形成することと、第2のドープ領域を形成することであって、第2のドープ領域は、第1の面から第1の深さより大きい第2の深さまで延在する開口内にあり、第1の濃度よりも大きい第2の濃度を有し、第1の導電型である、形成することと、開口に金属を充填することであって、金属は第2のドープ領域と接触する、充填することを含む、方法を含む。項目18は、第2のドープ領域を形成することが、開口内にin−situドープ多結晶シリコンを堆積することを含む、項目17の方法を含む。項目19は、第2のドープ領域を形成することが、第2の深さまで開口の側壁にドーパントを付加するためのイオン注入を実行することを含む、項目17の方法を含む。項目20は、デバイスを形成することが、第1のドープ領域としてのドリフト領域、および開口の周りの第1の面上のリングを有する側方拡散MOS(LDMOS)トランジスタから成る群のうちの1つを形成することを含み、リングは第1のドープ領域である、項目17の方法を含む。

【符号の説明】

【0037】

10…半導体デバイス構造、12…基板、14…ゲート、16…LDMOSデバイス、36…基板貫通バイア。

【特許請求の範囲】

【請求項1】

第1の濃度にて第1の導電型のバックグラウンドドーピングがされている基板を含んでなる半導体デバイス構造において、

前記基板を貫通している、基板貫通バイアと、

前記基板の第1の面に設けられ、第2の導電型の第1のドープ領域を有するデバイスと、

前記基板貫通バイアの周りに設けられる第2のドープ領域とを備え、前記第2のドープ領域は前記第1の濃度よりも高い第2の濃度にて前記第1の導電型にドープされている、半導体デバイス構造。

【請求項2】

前記デバイスは前記基板貫通バイアに結合する横方向拡散MOS(LDMOS)トランジスタである、請求項1に記載の半導体デバイス構造。

【請求項3】

前記LDMOSトランジスタは前記基板貫通バイアに結合する前記第1の導電型の本体接続を有している、請求項2に記載の半導体デバイス構造。

【請求項4】

前記第2のドープ領域は前記本体接続よりも深い深さまで延伸している、請求項3に記載の半導体デバイス構造。

【請求項5】

前記第1のドープ領域は前記本体接続に隣接する前記LDMOSトランジスタのソース領域である、請求項3に記載の半導体デバイス構造。

【請求項6】

前記LDMOSトランジスタはゲートを有し、前記ソース領域は前記ゲートの片側に位置合わせされている、請求項5に記載の半導体デバイス構造。

【請求項7】

前記第2のドープ領域は前記基板貫通バイアに直接に接触する、請求項1に記載の半導体デバイス構造。

【請求項8】

前記第1のドープ領域は前記基板の前記第1の面の下方の第1の深さまで延伸する、前記LDMOSトランジスタのドリフト領域を備え、前記第2のドープ領域は前記基板の前記第1の面の下方の第2の深さまで延伸し、前記第2の深さは前記第1の深さよりも大きい、請求項1に記載の半導体デバイス構造。

【請求項9】

前記第2の深さは前記第1の深さの10倍以上である、請求項8に記載の半導体デバイス構造。

【請求項10】

前記第1のドープ領域は前記基板貫通バイアを取り囲む、請求項1に記載の半導体デバイス構造。

【請求項11】

前記第2の濃度は前記第1の濃度の100倍よりも高い、請求項1に記載の半導体デバイス構造。

【請求項12】

前記第2の濃度は前記第1の濃度の10000倍よりも高い、請求項11に記載の半導体デバイス構造。

【請求項13】

前記LDMOSトランジスタは、前記基板の前記第1の面の下方の第1の深さまで延伸するドリフト領域を備え、前記ドープ領域は前記基板の前記第1の面の下方の第2の深さまで延伸し、前記第2の深さは前記第1の深さよりも少なくとも5倍大きい、請求項12に記載の半導体デバイス構造。

【請求項14】

第1の面から第2の面まで貫通するバイアを有した半導体基板と、

第1の面に設けられ、第1のドープ領域を有するデバイスと、

前記バイアの周りに前記バイアに接触するように設けられた第2のドープ領域とを備えた半導体デバイス構造において、

前記基板は第1の濃度のバックグラウンドドーピングレベルを有し、

前記基板は第1の導電型を有し、

前記第1のドープ領域は前記第2の導電型を有して前記基板の表面から第1の深さまで延伸しており、

前記第2のドープ領域は前記基板から第2の深さまで延伸しており、

前記第2の深さは前記第1の深さよりも大きく、

前記第2のドープ領域は第2のドーピングレベルを有し、かつ、

前記第2の濃度は前記第1の濃度よりも高い、半導体デバイス構造。

【請求項15】

前記第1のドープ領域はLDMOSデバイスのドリフト領域を備える、請求項14に記載の半導体デバイス構造。

【請求項16】

前記第1のドープ領域は前記第2のドープ領域を取り囲む、請求項14に記載の半導体デバイス構造。

【請求項17】

第1の濃度にて第1の導電型をバックグラウンドドーピングしてなる半導体基板を用いた半導体デバイス構造の製造方法において、

前記半導体基板の第1の面であって、前記第1の面の下方の第1の深さまで延びる第2の導電型の第1のドープ領域を有している、前記第1の面の上、及び内部にデバイスを形成する工程と、

前記半導体基板の前記第1の面と第2の面の間に延びて前記基板を貫通する開口を形成する工程と、

第2のドープ領域を形成する工程であって、前記第2のドープ領域は前記第1の深さよりも深く前記第1の面から延びる第2の深さまで前記開口の内部に設けられ、前記第1の濃度よりも高い第2の濃度を有し、かつ、前記第1の導電型を有している、前記第2のドープ領域を形成する工程と、

前記開口に金属を充填する工程であって、前記金属は前記第2のドープ領域に接触している、前記開口に金属を充填する工程とを備える、半導体デバイス構造の製造方法。

【請求項18】

前記第2のドープ領域を形成する工程では、前記開口にインサイチューでドープされたポリシリコンを堆積する、請求項17に記載の方法。

【請求項19】

前記第2のドープ領域を形成する工程では、前記開口の側壁に前記第2の深さまでドーパントを与えるためのインプランテーションを行う、請求項17に記載の方法。

【請求項20】

前記デバイスを形成する工程では、前記第1のドープ領域としてドリフト領域を有する横方向拡散MOS(LDMOS)トランジスタ、および前記第1の面にて前記開口の周りに設けられ、前記第1のドープ領域となる環からなる群から選択されるデバイスを形成する、請求項19に記載の方法。

【請求項1】

第1の濃度にて第1の導電型のバックグラウンドドーピングがされている基板を含んでなる半導体デバイス構造において、

前記基板を貫通している、基板貫通バイアと、

前記基板の第1の面に設けられ、第2の導電型の第1のドープ領域を有するデバイスと、

前記基板貫通バイアの周りに設けられる第2のドープ領域とを備え、前記第2のドープ領域は前記第1の濃度よりも高い第2の濃度にて前記第1の導電型にドープされている、半導体デバイス構造。

【請求項2】

前記デバイスは前記基板貫通バイアに結合する横方向拡散MOS(LDMOS)トランジスタである、請求項1に記載の半導体デバイス構造。

【請求項3】

前記LDMOSトランジスタは前記基板貫通バイアに結合する前記第1の導電型の本体接続を有している、請求項2に記載の半導体デバイス構造。

【請求項4】

前記第2のドープ領域は前記本体接続よりも深い深さまで延伸している、請求項3に記載の半導体デバイス構造。

【請求項5】

前記第1のドープ領域は前記本体接続に隣接する前記LDMOSトランジスタのソース領域である、請求項3に記載の半導体デバイス構造。

【請求項6】

前記LDMOSトランジスタはゲートを有し、前記ソース領域は前記ゲートの片側に位置合わせされている、請求項5に記載の半導体デバイス構造。

【請求項7】

前記第2のドープ領域は前記基板貫通バイアに直接に接触する、請求項1に記載の半導体デバイス構造。

【請求項8】

前記第1のドープ領域は前記基板の前記第1の面の下方の第1の深さまで延伸する、前記LDMOSトランジスタのドリフト領域を備え、前記第2のドープ領域は前記基板の前記第1の面の下方の第2の深さまで延伸し、前記第2の深さは前記第1の深さよりも大きい、請求項1に記載の半導体デバイス構造。

【請求項9】

前記第2の深さは前記第1の深さの10倍以上である、請求項8に記載の半導体デバイス構造。

【請求項10】

前記第1のドープ領域は前記基板貫通バイアを取り囲む、請求項1に記載の半導体デバイス構造。

【請求項11】

前記第2の濃度は前記第1の濃度の100倍よりも高い、請求項1に記載の半導体デバイス構造。

【請求項12】

前記第2の濃度は前記第1の濃度の10000倍よりも高い、請求項11に記載の半導体デバイス構造。

【請求項13】

前記LDMOSトランジスタは、前記基板の前記第1の面の下方の第1の深さまで延伸するドリフト領域を備え、前記ドープ領域は前記基板の前記第1の面の下方の第2の深さまで延伸し、前記第2の深さは前記第1の深さよりも少なくとも5倍大きい、請求項12に記載の半導体デバイス構造。

【請求項14】

第1の面から第2の面まで貫通するバイアを有した半導体基板と、

第1の面に設けられ、第1のドープ領域を有するデバイスと、

前記バイアの周りに前記バイアに接触するように設けられた第2のドープ領域とを備えた半導体デバイス構造において、

前記基板は第1の濃度のバックグラウンドドーピングレベルを有し、

前記基板は第1の導電型を有し、

前記第1のドープ領域は前記第2の導電型を有して前記基板の表面から第1の深さまで延伸しており、

前記第2のドープ領域は前記基板から第2の深さまで延伸しており、

前記第2の深さは前記第1の深さよりも大きく、

前記第2のドープ領域は第2のドーピングレベルを有し、かつ、

前記第2の濃度は前記第1の濃度よりも高い、半導体デバイス構造。

【請求項15】

前記第1のドープ領域はLDMOSデバイスのドリフト領域を備える、請求項14に記載の半導体デバイス構造。

【請求項16】

前記第1のドープ領域は前記第2のドープ領域を取り囲む、請求項14に記載の半導体デバイス構造。

【請求項17】

第1の濃度にて第1の導電型をバックグラウンドドーピングしてなる半導体基板を用いた半導体デバイス構造の製造方法において、

前記半導体基板の第1の面であって、前記第1の面の下方の第1の深さまで延びる第2の導電型の第1のドープ領域を有している、前記第1の面の上、及び内部にデバイスを形成する工程と、

前記半導体基板の前記第1の面と第2の面の間に延びて前記基板を貫通する開口を形成する工程と、

第2のドープ領域を形成する工程であって、前記第2のドープ領域は前記第1の深さよりも深く前記第1の面から延びる第2の深さまで前記開口の内部に設けられ、前記第1の濃度よりも高い第2の濃度を有し、かつ、前記第1の導電型を有している、前記第2のドープ領域を形成する工程と、

前記開口に金属を充填する工程であって、前記金属は前記第2のドープ領域に接触している、前記開口に金属を充填する工程とを備える、半導体デバイス構造の製造方法。

【請求項18】

前記第2のドープ領域を形成する工程では、前記開口にインサイチューでドープされたポリシリコンを堆積する、請求項17に記載の方法。

【請求項19】

前記第2のドープ領域を形成する工程では、前記開口の側壁に前記第2の深さまでドーパントを与えるためのインプランテーションを行う、請求項17に記載の方法。

【請求項20】

前記デバイスを形成する工程では、前記第1のドープ領域としてドリフト領域を有する横方向拡散MOS(LDMOS)トランジスタ、および前記第1の面にて前記開口の周りに設けられ、前記第1のドープ領域となる環からなる群から選択されるデバイスを形成する、請求項19に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−93579(P2013−93579A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2012−234265(P2012−234265)

【出願日】平成24年10月24日(2012.10.24)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成24年10月24日(2012.10.24)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

[ Back to top ]