基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、無線通信装置などに用いられる基準周波数信号源に関し、特に、異なる複数の基準信号の周波数に対応可能な改良技術に関するものである。

【背景技術】

【0002】

従来から、無線通信装置などに用いられる基準周波数信号源として、周波数シンセサイザが知られている(たとえば、非特許文献1参照)。

図10は上記非特許文献1に記載された周波数シンセサイザの構成を示すブロック図である。

【0003】

図10において、周波数シンセサイザ(基準周波数信号源)は、周波数fiの基準信号源101と、周波数fdの周波数信号を生成する直接デジタルシンセサイザ(DDS)102と、フィルタ(FLT)103と、周波数fd/Tの分周信号を生成する分周器104と、位相比較器(PD)105と、ループフィルタ(LF)106と、周波数foの出力信号を生成する電圧制御発振器107と、ミクサ108と、フィルタ(FLT)109とを備えている。

【0004】

次に、図10に示した周波数シンセサイザの動作について説明する。

周波数シンセサイザからなる基準周波数信号源は、基準信号源101の出力信号(周波数fi)に位相同期した出力信号(周波数fo)を電圧制御発振器107から外部に出力する。

【0005】

まず、基準信号源101の出力信号をDDS102のクロックとし、DDS102は、正弦波状の連続信号(周波数fd)を出力する。なお、周波数fdは、外部からの周波数制御データに応じて変更可能である。

【0006】

続いて、フィルタ103は、DDS102の出力信号に含まれる不要波成分を抑圧し、分周器104は、フィルタ103で濾波したDDS102の出力信号の周波数分周を行い、分周信号(fd/T)を位相比較器(PD)105に入力する。

【0007】

ミクサ108は、電圧制御発振器107の出力信号と、基準信号源101の出力信号との周波数混合を行い、フィルタ109は、ミクサ108からの周波数混合波に含まれる不要波成分を抑圧し、差周波(周波数|fo−fi|)を所望波として位相比較器105に入力する。

【0008】

位相比較器105は、分周信号(周波数fd/T)と、差周波(周波数|fo−fi|)との位相比較を行い、ループフィルタ106は、位相比較器105からの位相比較信号を濾波し、電圧制御発振器107に対する制御電圧を生成する。

電圧制御発振器107は、制御電圧に応じて周波数foを変化させることにより、基準信号源101の出力信号との位相同期を確立する。

【0009】

図10に示す基準周波数信号源において、位相同期が確立されたときに、分周信号(周波数fd/T)と差周波(周波数|fo−fi|)とは等しくなるが、これらの周波数は、位相比較器105の動作周波数の範囲内である必要があり、一般的に、DC近傍では位相比較器105は動作しない。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】F.J.M.Carrillo他、「Hybrid synthesizers in space:Galileo‘s CMCU」Proc.of 2nd Int.Conf.on RAST2005、pp.361〜368、2005.

【発明の概要】

【発明が解決しようとする課題】

【0011】

従来の基準周波数信号源は、図10の周波数シンセサイザの場合、基準信号源101の周波数fiと電圧制御発振器107の出力周波数foとがほぼ等しい値である場合に、ミクサ108から差周波の周波数|fo−fi|がDC近傍となるので、位相比較器105が動作せず、位相同期を確立することができないという課題があった。

【0012】

また、別の基準信号源に変更した場合に、周波数fiが変化すると、分周信号の周波数fd/Tおよび差周波の周波数|fo−fi|も合わせて変更され、変更後の周波数がフィルタ103、109の通過帯域外に逸脱すると、分周信号または差周波がフィルタ103、109によって抑圧されるので、位相比較器105が動作しなくなり、位相同期を確立することができなくなるという課題があった。

また、フィルタ103、109による抑圧を回避するために、通過帯域が異なる複数のフィルタを用意すると、信号源の構成が複雑となり、全体サイズが大きくなるという課題があった。

【0013】

さらに、周波数fiの変更にともない、DDS102の周波数fdも変更されるが、周波数fdを一定値にするためには、DDS102の制御信号を周波数fiに応じて大幅に変更する必要があるので、DDS制御回路が複雑となり、コストアップを招くという課題があった。

【0014】

この発明は、上記のような課題を解決するためになされたものであり、大幅なハードウエア変更を必要とすることなく、異なる基準信号の周波数に対応可能な基準周波数信号源を得ることを目的とする。

【課題を解決するための手段】

【0015】

この発明に係る基準周波数信号源は、基準信号を生成する基準信号源と、基準信号と基準信号の周波数に応じた制御信号とに基づいてクロック信号および局部発振信号を生成する周波数変換回路と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成する直接デジタルシンセサイザと、直接デジタルシンセサイザからの周波数信号に含まれる不要波成分を抑圧する第1のフィルタと、局部発振信号と電圧制御発振器の出力信号とを周波数混合する第1のミクサと、第1のミクサからの混合信号に含まれる不要波成分を抑圧する第2のフィルタと、第1のフィルタを介した周波数信号と第2のフィルタを介した混合信号との位相差を検出する位相比較器と、位相比較器からの位相差信号を濾波するループフィルタと、ループフィルタを介した位相差信号に応じて出力信号を生成する電圧制御発振器とを備えたものである。

【発明の効果】

【0016】

この発明によれば、大幅なハードウエア変更を必要とすることなく、異なる基準信号の周波数に対応することができる。

【図面の簡単な説明】

【0017】

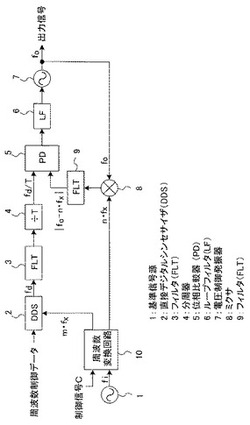

【図1】この発明の実施の形態1に係る基準周波数信号源の第1の構成例を示すブロック図である。

【図2】この発明の実施の形態1に係る基準周波数信号源の第2の構成例を示すブロック図である。

【図3】この発明の実施の形態1に係る基準周波数信号源の第3の構成例を示すブロック図である。

【図4】この発明の実施の形態1に係る基準周波数信号源の第4の構成例を示すブロック図である。

【図5】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第1の構成例を示すブロック図である。

【図6】図5内のミクサからの混合信号(混合波)に含まれる周波数成分を示す説明図である。

【図7】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第2の構成例を示すブロック図である。

【図8】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第3の構成例を示すブロック図である。

【図9】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第4の構成例を示すブロック図である。

【図10】従来の基準周波数信号源の構成を示すブロック図である。

【発明を実施するための形態】

【0018】

実施の形態1.

図1はこの発明の実施の形態1に係る基準周波数信号源を示すブロック図である。

図1において、基準周波数信号源は、周波数fiの基準信号を生成する基準信号源1と、周波数制御データに応じた周波数fdの周波数信号を生成する直接デジタルシンセサイザ(DDS)2と、フィルタ(FLT)3と、周波数fd/Tの分周信号を生成する分周器4と、位相比較器(PD)5と、ループフィルタ(LF)6と、周波数foの出力信号を生成する電圧制御発振器7と、ミクサ8と、フィルタ(FLT)9と、基準信号源1とDDS2およびミクサ8との間に挿入された周波数変換回路10とを備えている。

【0019】

なお、基準信号源1としては、固定周波数を生成する水晶発振器を用いてもよく、周波数を可変設定する周波数シンセサイザを用いてもよい。

【0020】

次に、図1に示したこの発明の実施の形態1による動作について説明する。

まず、周波数変換回路10は、基準信号源1からの基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいて、クロック信号(周波数m・fx)および局部発振信号(周波数n・fx)(m、nは、自然数)を生成する。

【0021】

ここで、周波数n・fxは、基準周波数信号源の出力周波数foと異なる値とし、かつ周波数fiによらず、ほぼ一定値になるものとする。

また、周波数変換回路10からの出力信号は、基準信号源1からの基準信号に同期しているものとする。

【0022】

DDS2は、周波数m・fxの信号をクロックとして、正弦波状の連続信号(周波数fd)を出力する。なお、周波数fdは、外部からの周波数制御データに応じて変更可能である。

【0023】

フィルタ3は、DDS2からの周波数信号(fd)に含まれる不要波成分を抑圧し、分周器4は、フィルタ3を介して濾波されたDDS2からの周波数信号の周波数分周を行い、分周信号(fd/T)を生成する。

【0024】

ミクサ8は、電圧制御発振器7の出力信号(周波数fo)と、周波数変換回路10の出力信号(周波数n・fx)との周波数混合を行う。

フィルタ9は、ミクサ8からの混合波に含まれる不要波成分を抑圧し、差周波(周波数|fo−n・fx|)を所望波として出力する。

【0025】

位相比較器5は、分周信号(周波数fd/T)と、差周波(周波数|fo−n・fx|)との位相比較を行う。

ループフィルタ6は、位相比較器5からの位相比較信号を濾波し、電圧制御発振器7に対する制御電圧を生成する。

【0026】

電圧制御発振器7は、ループフィルタ6からの制御電圧に応じて出力周波数foを変化させ、周波数変換回路10の出力信号との位相同期を確立する。

すなわち、電圧制御発振器7から出力される基準周波数信号源の出力信号(周波数fo)は、基準信号源1からの基準信号(周波数fi)に同期していることになる。

【0027】

図1の基準周波数信号源において、クロック信号の周波数m・fxおよび局部発振信号の周波数n・fxは、基準信号の周波数fiによらず、ほぼ一定値なので、ミクサ8からの混合波成分の周波数も大きく変化しない。

よって、フィルタ9を通過する所望波成分の周波数(|fo−n・fx|)も変化しないので、位相比較器5の動作が常に保証される。

【0028】

また、周波数fiに対して通過帯域が異なる複数のフィルタを用意する必要がないので、基準信号源1のサイズが大きくなることはない。

さらに、DDS2のクロック周波数も大きく変化しないので、DDS制御回路を簡素にすることができる。

【0029】

なお、以上の説明では、ミクサ8からの混合波のうち、周波数|fo−n・fx|の差周波を所望波としているが、周波数|fo+n・fx|の和周波を含めて、他の混合波成分を所望波としても、同様の効果を奏する。

【0030】

また、分周器4の分周数Tの具体的な値について言及しなかったが、一般的には、分周数Tの値は「2以上の整数」である。

仮に、分周数Tが「1」の場合、図1内の分周器4はバイパス(シャント)されることになるので、結果的に、図2に示す回路構成となる。

【0031】

図2の回路構成においては、周波数fdと周波数|fo−n・fx|とが等しくなるように位相同期を確立することにより、図1に示す構成と同様の効果を奏する。

図2においては、フィルタ3と位相比較器5とが直結されており、図1内の分周器4がバイパスされていることを表している。

【0032】

また、図3、図4に示すように、図1、図2内のフィルタ9と位相比較器5との間に、分周数Rの分周器11を挿入してもよい。

図3に示す回路構成においては、周波数fd/Tと周波数|fo−n・fx|/Rとが等しくなるように位相同期を確立することにより、図1に示す構成と同様の効果を奏する。

同様に、図4に示す回路構成においては、周波数fdと周波数|fo−n・fx|/Rとが等しくなるように位相同期を確立することにより、図1に示す構成と同様の効果を奏する。

【0033】

以上のように、この発明の実施の形態1(図1〜図4)に係る基準周波数信号源は、基準信号(周波数fi)を生成する基準信号源1と、基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号(周波数fd)を生成する直接デジタルシンセサイザ(DDS)2と、直接デジタルシンセサイザ2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3(第1のフィルタ)と、局部発振信号(周波数n・fx)と電圧制御発振器7の出力信号(周波数fo)とを周波数混合するミクサ8(第1のミクサ)と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9(第2のフィルタ)と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号(周波数fo)を生成する電圧制御発振器7とを備えている。

【0034】

また、フィルタ3と位相比較器5との間、および、フィルタ9と位相比較器5との間、の少なくとも一方には、周波数分周する分周器4、11(図1、図3、図4)が挿入されている。さらに、基準信号源1は、基準信号の周波数fiを変更可能な可変信号源(周波数シンセサイザ)により構成され得る。

これにより、大幅なハードウエア変更を必要とすることなく、異なる基準信号の周波数fiに対応可能な基準周波数信号源を実現することができる。

【0035】

実施の形態2.

なお、上記実施の形態1(図1〜図4)では、具体的に言及しなかったが、周波数変換回路10を、図5のように構成してもよい。

図5はこの発明の実施の形態2に係る基準周波数信号源の周波数変換回路10の構成を示すブロック図である。

【0036】

図5において、周波数変換回路10は、制御信号Cに応じて基準信号(周波数fi)を周波数分周する可変分周器21と、可変分周器21からの分周信号(周波数fi/A)と基準信号(周波数fi)とを周波数混合するミクサ22と、ミクサ22からの混合信号に含まれる混合波のうち、クロック信号に対応した所望波(周波数m・fx)以外を抑圧するフィルタ23と、ミクサ22からの混合信号に含まれる混合波のうち、局部発振信号に対応した所望波(周波数n・fx)以外を抑圧するフィルタ24とを備えている。

【0037】

次に、図5に示したこの発明の実施の形態2による周波数変換回路10の動作について説明する。

まず、可変分周器21は、基準信号源1からの基準信号(周波数fi)の周波数分周を行い、分周信号(fi/A)を生成する。このとき、可変分周器21の分周数Aは、制御信号Cにより変更することでき、周波数fiに対応した値となる。

続いて、ミクサ22は、基準信号(周波数fi)と可変分周器21からの分周信号(周波数fi/A)との周波数混合を行う。

【0038】

次に、一方のフィルタ23は、ミクサ22からの混合波に含まれる不要波成分(周波数m・fx以外)を抑圧して、DDS22に対するクロック信号として生成する。すなわち、周波数m・fxとなる混合波成分を所望波とする。

また、他方のフィルタ24は、ミクサ22からの混合波に含まれる不要波成分(周波数n・fx以外)を抑圧して、ミクサ8に対する局部発振信号として生成する。すなわち、n・fxとなる混合波成分を所望波とする。

【0039】

このとき、ミクサ22からの混合波の周波数fmは、以下の式(1)で与えられる。

【0040】

fm=|p・fi±q・(fi/A)|

=fi・|p±(q/A)| ・・・(1)

【0041】

ただし、式(1)において、p、qは次数(整数)である。

式(1)より、ミクサ22からの混合波には、図6に示すように、周波数間隔fi/Aで複数の周波数成分が存在する。したがって、図6内の周波数成分のうちの1つの波以外を各フィルタ23、24で抑圧することにより、周波数m・fxまたは周波数n・fxの所望周波数をそれぞれ得ることができる。

【0042】

基準信号の周波数fiを変更する場合には、周波数m・fx、n・fxが得られるように、可変分周器21の分周数Aを変更すればよい。

たとえば、基準信号の周波数fiが10MHzと、10.23MHzとに変更する場合に、第1の所望周波数m・fx(=19.8MHz)と、第2の所望周波数n・fx(=9.9MHz)を得るには、以下のように分周数Aを設定すればよい。

【0043】

まず、基準信号の周波数fiが10MHzの場合には、分周数Aを「100」に設定することにより、所望周波数m・fx、n・fxとして、以下の式(2)、式(3)で示すように、所望値19.8MHz、9.9MHzが得られる。

【0044】

m・fx=fi・|2−(2/A)|

=10MHz・|2−(2/100)|

=19.8MHz ・・・(2)

n・fx=fi・|1−(1/A)|

=10MHz・|1−(1/100)|

=9.9MHz ・・・(3)

【0045】

一方、基準信号の周波数fiが10.23MHzの場合には、分周数Aを「31」に設定することにより、所望周波数m・fx、n・fxとして、以下の式(4)、式(5)で示すように、所望値19.8MHz、9.9MHzが得られる。

【0046】

m・fx=fi・|2−(2/A)|

=10.23MHz・|2−(2/31)|

=19.8MHz ・・・(4)

n・fx=fi・|1−(1/A)|

=10.23MHz・|1−(1/31)|

=9.9MHz ・・・(5)

【0047】

なお、上記式(2)〜式(5)の例では、基準信号の周波数fiを変更しても、所望周波数m・fx、n・fxは変化しなかったが、基準信号の周波数fiの値によっては所望周波数が変化する可能性がある。ただし、そのような場合でも、分周数Aの値を大きく設定することにより、ミクサ22からの混合波成分の配置を密にすることができ、所望周波数をほぼ一定値にすることができる。

【0048】

したがって、図5に示した周波数変換回路10の構成により、基準信号の周波数fiによらず、所望周波数m・fx、n・fxをほぼ一定値にできるので、前述の実施の形態1と同様の効果を奏することができる。

【0049】

なお、図5の回路構成においては、外部(基準信号の入力端子)とミクサ22の一方の入力端子とが直結しており、たとえば、ミクサ22の一方の入力端子側に挿入された分周器(図示せず)がバイパスされた状態を示している。

図7はこの発明の実施の形態2による周波数変換回路10の他の構成例を示すブロック図であり、外部とミクサ22との間に分周数Bの可変分周器25が追加挿入された状態を示している。

【0050】

図7において、前述(図5参照)との相違点は、可変分周器25が追加挿入された点のみであり、前述(図5参照)と同様のものについては、前述と同一符号を付して詳述を省略する。

図7の場合、ミクサ22からの混合波の周波数fmは、以下の式(6)で与えられる。

【0051】

fm=|p・(fi/B)±q・(fi/A)|

=fi・|(p/B)±(q/A)| ・・・(6)

【0052】

式(6)より、ミクサ22からの混合波の周波数間隔は、前述(図6)のfi/Aとは異なり、fi/(A・B)となるので、設定の自由度が高くなる。

この結果、分周数A、Bを適切な値に設定することにより、基準信号の周波数fiによらず、所望周波数m・fx、n・fxをほぼ一定値にすることができる。

【0053】

なお、上記説明では、所望周波数m・fx、n・fxは互いに異なる周波数であることを想定しているが、同一周波数(m・fx=n・fx)であっても同等の作用効果を奏することは言うまでもない。

【0054】

所望周波数m・fx、n・fxが同一周波数の場合には、図5、図7に対応する周波数変換回路10は、それぞれ図8、図9で示す回路構成に削減することができる。

すなわち、図5、図7内の2つのフィルタ23、24のうち、一方を削除して、1つのフィルタ23のみを使用すればよい。

図8,図9の回路構成により、基準周波数信号源の全体サイズを小さくするとともに、コストダウンを実現することができる。

【0055】

以上のように、この発明の実施の形態2(図5)による周波数変換回路10は、制御信号Cに応じて基準信号(fi)を周波数分周する可変分周器21(第1の可変分周器)と、可変分周器21からの分周信号(fi/A)と基準信号(fi)とを周波数混合するミクサ22(第2のミクサ)と、ミクサ22からの混合信号に含まれる混合波のうち、クロック信号に対応した第1の所望波(m・fx)以外を抑圧するフィルタ23(第3のフィルタ)と、ミクサ22からの混合信号に含まれる混合波のうち、局部発振信号に対応した第2の所望波(m・fx)以外を抑圧するフィルタ24(第4のフィルタ)と、を備えている。

【0056】

また、この発明の実施の形態2(図8)による周波数変換回路10は、制御信号Cに応じて基準信号を周波数分周する可変分周器21と、可変分周器21からの分周信号と基準信号とを周波数混合するミクサ22と、ミクサ22からの混合信号に含まれる混合波のうち、クロック信号および局部発振信号に対応した所望波以外を抑圧するフィルタ23(第3のフィルタ)とを備えている。

【0057】

さらに、この発明の実施の形態2(図7、図9)による周波数変換回路10は、図5、図8の構成に加えて、基準信号の入力端子とミクサ22との間に挿入され、制御信号Cに応じて基準信号を周波数分周する可変分周器25(第2の可変分周器)を備えており、ミクサ22は、可変分周器21からの分周信号と可変分周器22からの分周信号とを周波数混合する。

これにより、この発明の実施の形態2によれば、前述の実施の形態1と同様の作用効果を奏することができる。

【符号の説明】

【0058】

1 基準信号源、2 直接デジタルシンセサイザ(DDS)、3 フィルタ(第1のフィルタ)、4 分周器、5 位相比較器、6 ループフィルタ、7 電圧制御発振器、8 ミクサ(第1のミクサ)、9 フィルタ(第2のフィルタ)、10 周波数変換回路、11 分周器、19 所望値、21 可変分周器(第1の可変分周器)、22 ミクサ(第2のミクサ)、23 フィルタ(第3のフィルタ)、24 フィルタ(第4のフィルタ)、25 可変分周器(第2の可変分周器)、C 制御信号。

【技術分野】

【0001】

この発明は、無線通信装置などに用いられる基準周波数信号源に関し、特に、異なる複数の基準信号の周波数に対応可能な改良技術に関するものである。

【背景技術】

【0002】

従来から、無線通信装置などに用いられる基準周波数信号源として、周波数シンセサイザが知られている(たとえば、非特許文献1参照)。

図10は上記非特許文献1に記載された周波数シンセサイザの構成を示すブロック図である。

【0003】

図10において、周波数シンセサイザ(基準周波数信号源)は、周波数fiの基準信号源101と、周波数fdの周波数信号を生成する直接デジタルシンセサイザ(DDS)102と、フィルタ(FLT)103と、周波数fd/Tの分周信号を生成する分周器104と、位相比較器(PD)105と、ループフィルタ(LF)106と、周波数foの出力信号を生成する電圧制御発振器107と、ミクサ108と、フィルタ(FLT)109とを備えている。

【0004】

次に、図10に示した周波数シンセサイザの動作について説明する。

周波数シンセサイザからなる基準周波数信号源は、基準信号源101の出力信号(周波数fi)に位相同期した出力信号(周波数fo)を電圧制御発振器107から外部に出力する。

【0005】

まず、基準信号源101の出力信号をDDS102のクロックとし、DDS102は、正弦波状の連続信号(周波数fd)を出力する。なお、周波数fdは、外部からの周波数制御データに応じて変更可能である。

【0006】

続いて、フィルタ103は、DDS102の出力信号に含まれる不要波成分を抑圧し、分周器104は、フィルタ103で濾波したDDS102の出力信号の周波数分周を行い、分周信号(fd/T)を位相比較器(PD)105に入力する。

【0007】

ミクサ108は、電圧制御発振器107の出力信号と、基準信号源101の出力信号との周波数混合を行い、フィルタ109は、ミクサ108からの周波数混合波に含まれる不要波成分を抑圧し、差周波(周波数|fo−fi|)を所望波として位相比較器105に入力する。

【0008】

位相比較器105は、分周信号(周波数fd/T)と、差周波(周波数|fo−fi|)との位相比較を行い、ループフィルタ106は、位相比較器105からの位相比較信号を濾波し、電圧制御発振器107に対する制御電圧を生成する。

電圧制御発振器107は、制御電圧に応じて周波数foを変化させることにより、基準信号源101の出力信号との位相同期を確立する。

【0009】

図10に示す基準周波数信号源において、位相同期が確立されたときに、分周信号(周波数fd/T)と差周波(周波数|fo−fi|)とは等しくなるが、これらの周波数は、位相比較器105の動作周波数の範囲内である必要があり、一般的に、DC近傍では位相比較器105は動作しない。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】F.J.M.Carrillo他、「Hybrid synthesizers in space:Galileo‘s CMCU」Proc.of 2nd Int.Conf.on RAST2005、pp.361〜368、2005.

【発明の概要】

【発明が解決しようとする課題】

【0011】

従来の基準周波数信号源は、図10の周波数シンセサイザの場合、基準信号源101の周波数fiと電圧制御発振器107の出力周波数foとがほぼ等しい値である場合に、ミクサ108から差周波の周波数|fo−fi|がDC近傍となるので、位相比較器105が動作せず、位相同期を確立することができないという課題があった。

【0012】

また、別の基準信号源に変更した場合に、周波数fiが変化すると、分周信号の周波数fd/Tおよび差周波の周波数|fo−fi|も合わせて変更され、変更後の周波数がフィルタ103、109の通過帯域外に逸脱すると、分周信号または差周波がフィルタ103、109によって抑圧されるので、位相比較器105が動作しなくなり、位相同期を確立することができなくなるという課題があった。

また、フィルタ103、109による抑圧を回避するために、通過帯域が異なる複数のフィルタを用意すると、信号源の構成が複雑となり、全体サイズが大きくなるという課題があった。

【0013】

さらに、周波数fiの変更にともない、DDS102の周波数fdも変更されるが、周波数fdを一定値にするためには、DDS102の制御信号を周波数fiに応じて大幅に変更する必要があるので、DDS制御回路が複雑となり、コストアップを招くという課題があった。

【0014】

この発明は、上記のような課題を解決するためになされたものであり、大幅なハードウエア変更を必要とすることなく、異なる基準信号の周波数に対応可能な基準周波数信号源を得ることを目的とする。

【課題を解決するための手段】

【0015】

この発明に係る基準周波数信号源は、基準信号を生成する基準信号源と、基準信号と基準信号の周波数に応じた制御信号とに基づいてクロック信号および局部発振信号を生成する周波数変換回路と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成する直接デジタルシンセサイザと、直接デジタルシンセサイザからの周波数信号に含まれる不要波成分を抑圧する第1のフィルタと、局部発振信号と電圧制御発振器の出力信号とを周波数混合する第1のミクサと、第1のミクサからの混合信号に含まれる不要波成分を抑圧する第2のフィルタと、第1のフィルタを介した周波数信号と第2のフィルタを介した混合信号との位相差を検出する位相比較器と、位相比較器からの位相差信号を濾波するループフィルタと、ループフィルタを介した位相差信号に応じて出力信号を生成する電圧制御発振器とを備えたものである。

【発明の効果】

【0016】

この発明によれば、大幅なハードウエア変更を必要とすることなく、異なる基準信号の周波数に対応することができる。

【図面の簡単な説明】

【0017】

【図1】この発明の実施の形態1に係る基準周波数信号源の第1の構成例を示すブロック図である。

【図2】この発明の実施の形態1に係る基準周波数信号源の第2の構成例を示すブロック図である。

【図3】この発明の実施の形態1に係る基準周波数信号源の第3の構成例を示すブロック図である。

【図4】この発明の実施の形態1に係る基準周波数信号源の第4の構成例を示すブロック図である。

【図5】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第1の構成例を示すブロック図である。

【図6】図5内のミクサからの混合信号(混合波)に含まれる周波数成分を示す説明図である。

【図7】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第2の構成例を示すブロック図である。

【図8】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第3の構成例を示すブロック図である。

【図9】この発明の実施の形態2に係る基準周波数信号源の周波数変換回路の第4の構成例を示すブロック図である。

【図10】従来の基準周波数信号源の構成を示すブロック図である。

【発明を実施するための形態】

【0018】

実施の形態1.

図1はこの発明の実施の形態1に係る基準周波数信号源を示すブロック図である。

図1において、基準周波数信号源は、周波数fiの基準信号を生成する基準信号源1と、周波数制御データに応じた周波数fdの周波数信号を生成する直接デジタルシンセサイザ(DDS)2と、フィルタ(FLT)3と、周波数fd/Tの分周信号を生成する分周器4と、位相比較器(PD)5と、ループフィルタ(LF)6と、周波数foの出力信号を生成する電圧制御発振器7と、ミクサ8と、フィルタ(FLT)9と、基準信号源1とDDS2およびミクサ8との間に挿入された周波数変換回路10とを備えている。

【0019】

なお、基準信号源1としては、固定周波数を生成する水晶発振器を用いてもよく、周波数を可変設定する周波数シンセサイザを用いてもよい。

【0020】

次に、図1に示したこの発明の実施の形態1による動作について説明する。

まず、周波数変換回路10は、基準信号源1からの基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいて、クロック信号(周波数m・fx)および局部発振信号(周波数n・fx)(m、nは、自然数)を生成する。

【0021】

ここで、周波数n・fxは、基準周波数信号源の出力周波数foと異なる値とし、かつ周波数fiによらず、ほぼ一定値になるものとする。

また、周波数変換回路10からの出力信号は、基準信号源1からの基準信号に同期しているものとする。

【0022】

DDS2は、周波数m・fxの信号をクロックとして、正弦波状の連続信号(周波数fd)を出力する。なお、周波数fdは、外部からの周波数制御データに応じて変更可能である。

【0023】

フィルタ3は、DDS2からの周波数信号(fd)に含まれる不要波成分を抑圧し、分周器4は、フィルタ3を介して濾波されたDDS2からの周波数信号の周波数分周を行い、分周信号(fd/T)を生成する。

【0024】

ミクサ8は、電圧制御発振器7の出力信号(周波数fo)と、周波数変換回路10の出力信号(周波数n・fx)との周波数混合を行う。

フィルタ9は、ミクサ8からの混合波に含まれる不要波成分を抑圧し、差周波(周波数|fo−n・fx|)を所望波として出力する。

【0025】

位相比較器5は、分周信号(周波数fd/T)と、差周波(周波数|fo−n・fx|)との位相比較を行う。

ループフィルタ6は、位相比較器5からの位相比較信号を濾波し、電圧制御発振器7に対する制御電圧を生成する。

【0026】

電圧制御発振器7は、ループフィルタ6からの制御電圧に応じて出力周波数foを変化させ、周波数変換回路10の出力信号との位相同期を確立する。

すなわち、電圧制御発振器7から出力される基準周波数信号源の出力信号(周波数fo)は、基準信号源1からの基準信号(周波数fi)に同期していることになる。

【0027】

図1の基準周波数信号源において、クロック信号の周波数m・fxおよび局部発振信号の周波数n・fxは、基準信号の周波数fiによらず、ほぼ一定値なので、ミクサ8からの混合波成分の周波数も大きく変化しない。

よって、フィルタ9を通過する所望波成分の周波数(|fo−n・fx|)も変化しないので、位相比較器5の動作が常に保証される。

【0028】

また、周波数fiに対して通過帯域が異なる複数のフィルタを用意する必要がないので、基準信号源1のサイズが大きくなることはない。

さらに、DDS2のクロック周波数も大きく変化しないので、DDS制御回路を簡素にすることができる。

【0029】

なお、以上の説明では、ミクサ8からの混合波のうち、周波数|fo−n・fx|の差周波を所望波としているが、周波数|fo+n・fx|の和周波を含めて、他の混合波成分を所望波としても、同様の効果を奏する。

【0030】

また、分周器4の分周数Tの具体的な値について言及しなかったが、一般的には、分周数Tの値は「2以上の整数」である。

仮に、分周数Tが「1」の場合、図1内の分周器4はバイパス(シャント)されることになるので、結果的に、図2に示す回路構成となる。

【0031】

図2の回路構成においては、周波数fdと周波数|fo−n・fx|とが等しくなるように位相同期を確立することにより、図1に示す構成と同様の効果を奏する。

図2においては、フィルタ3と位相比較器5とが直結されており、図1内の分周器4がバイパスされていることを表している。

【0032】

また、図3、図4に示すように、図1、図2内のフィルタ9と位相比較器5との間に、分周数Rの分周器11を挿入してもよい。

図3に示す回路構成においては、周波数fd/Tと周波数|fo−n・fx|/Rとが等しくなるように位相同期を確立することにより、図1に示す構成と同様の効果を奏する。

同様に、図4に示す回路構成においては、周波数fdと周波数|fo−n・fx|/Rとが等しくなるように位相同期を確立することにより、図1に示す構成と同様の効果を奏する。

【0033】

以上のように、この発明の実施の形態1(図1〜図4)に係る基準周波数信号源は、基準信号(周波数fi)を生成する基準信号源1と、基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号(周波数fd)を生成する直接デジタルシンセサイザ(DDS)2と、直接デジタルシンセサイザ2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3(第1のフィルタ)と、局部発振信号(周波数n・fx)と電圧制御発振器7の出力信号(周波数fo)とを周波数混合するミクサ8(第1のミクサ)と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9(第2のフィルタ)と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号(周波数fo)を生成する電圧制御発振器7とを備えている。

【0034】

また、フィルタ3と位相比較器5との間、および、フィルタ9と位相比較器5との間、の少なくとも一方には、周波数分周する分周器4、11(図1、図3、図4)が挿入されている。さらに、基準信号源1は、基準信号の周波数fiを変更可能な可変信号源(周波数シンセサイザ)により構成され得る。

これにより、大幅なハードウエア変更を必要とすることなく、異なる基準信号の周波数fiに対応可能な基準周波数信号源を実現することができる。

【0035】

実施の形態2.

なお、上記実施の形態1(図1〜図4)では、具体的に言及しなかったが、周波数変換回路10を、図5のように構成してもよい。

図5はこの発明の実施の形態2に係る基準周波数信号源の周波数変換回路10の構成を示すブロック図である。

【0036】

図5において、周波数変換回路10は、制御信号Cに応じて基準信号(周波数fi)を周波数分周する可変分周器21と、可変分周器21からの分周信号(周波数fi/A)と基準信号(周波数fi)とを周波数混合するミクサ22と、ミクサ22からの混合信号に含まれる混合波のうち、クロック信号に対応した所望波(周波数m・fx)以外を抑圧するフィルタ23と、ミクサ22からの混合信号に含まれる混合波のうち、局部発振信号に対応した所望波(周波数n・fx)以外を抑圧するフィルタ24とを備えている。

【0037】

次に、図5に示したこの発明の実施の形態2による周波数変換回路10の動作について説明する。

まず、可変分周器21は、基準信号源1からの基準信号(周波数fi)の周波数分周を行い、分周信号(fi/A)を生成する。このとき、可変分周器21の分周数Aは、制御信号Cにより変更することでき、周波数fiに対応した値となる。

続いて、ミクサ22は、基準信号(周波数fi)と可変分周器21からの分周信号(周波数fi/A)との周波数混合を行う。

【0038】

次に、一方のフィルタ23は、ミクサ22からの混合波に含まれる不要波成分(周波数m・fx以外)を抑圧して、DDS22に対するクロック信号として生成する。すなわち、周波数m・fxとなる混合波成分を所望波とする。

また、他方のフィルタ24は、ミクサ22からの混合波に含まれる不要波成分(周波数n・fx以外)を抑圧して、ミクサ8に対する局部発振信号として生成する。すなわち、n・fxとなる混合波成分を所望波とする。

【0039】

このとき、ミクサ22からの混合波の周波数fmは、以下の式(1)で与えられる。

【0040】

fm=|p・fi±q・(fi/A)|

=fi・|p±(q/A)| ・・・(1)

【0041】

ただし、式(1)において、p、qは次数(整数)である。

式(1)より、ミクサ22からの混合波には、図6に示すように、周波数間隔fi/Aで複数の周波数成分が存在する。したがって、図6内の周波数成分のうちの1つの波以外を各フィルタ23、24で抑圧することにより、周波数m・fxまたは周波数n・fxの所望周波数をそれぞれ得ることができる。

【0042】

基準信号の周波数fiを変更する場合には、周波数m・fx、n・fxが得られるように、可変分周器21の分周数Aを変更すればよい。

たとえば、基準信号の周波数fiが10MHzと、10.23MHzとに変更する場合に、第1の所望周波数m・fx(=19.8MHz)と、第2の所望周波数n・fx(=9.9MHz)を得るには、以下のように分周数Aを設定すればよい。

【0043】

まず、基準信号の周波数fiが10MHzの場合には、分周数Aを「100」に設定することにより、所望周波数m・fx、n・fxとして、以下の式(2)、式(3)で示すように、所望値19.8MHz、9.9MHzが得られる。

【0044】

m・fx=fi・|2−(2/A)|

=10MHz・|2−(2/100)|

=19.8MHz ・・・(2)

n・fx=fi・|1−(1/A)|

=10MHz・|1−(1/100)|

=9.9MHz ・・・(3)

【0045】

一方、基準信号の周波数fiが10.23MHzの場合には、分周数Aを「31」に設定することにより、所望周波数m・fx、n・fxとして、以下の式(4)、式(5)で示すように、所望値19.8MHz、9.9MHzが得られる。

【0046】

m・fx=fi・|2−(2/A)|

=10.23MHz・|2−(2/31)|

=19.8MHz ・・・(4)

n・fx=fi・|1−(1/A)|

=10.23MHz・|1−(1/31)|

=9.9MHz ・・・(5)

【0047】

なお、上記式(2)〜式(5)の例では、基準信号の周波数fiを変更しても、所望周波数m・fx、n・fxは変化しなかったが、基準信号の周波数fiの値によっては所望周波数が変化する可能性がある。ただし、そのような場合でも、分周数Aの値を大きく設定することにより、ミクサ22からの混合波成分の配置を密にすることができ、所望周波数をほぼ一定値にすることができる。

【0048】

したがって、図5に示した周波数変換回路10の構成により、基準信号の周波数fiによらず、所望周波数m・fx、n・fxをほぼ一定値にできるので、前述の実施の形態1と同様の効果を奏することができる。

【0049】

なお、図5の回路構成においては、外部(基準信号の入力端子)とミクサ22の一方の入力端子とが直結しており、たとえば、ミクサ22の一方の入力端子側に挿入された分周器(図示せず)がバイパスされた状態を示している。

図7はこの発明の実施の形態2による周波数変換回路10の他の構成例を示すブロック図であり、外部とミクサ22との間に分周数Bの可変分周器25が追加挿入された状態を示している。

【0050】

図7において、前述(図5参照)との相違点は、可変分周器25が追加挿入された点のみであり、前述(図5参照)と同様のものについては、前述と同一符号を付して詳述を省略する。

図7の場合、ミクサ22からの混合波の周波数fmは、以下の式(6)で与えられる。

【0051】

fm=|p・(fi/B)±q・(fi/A)|

=fi・|(p/B)±(q/A)| ・・・(6)

【0052】

式(6)より、ミクサ22からの混合波の周波数間隔は、前述(図6)のfi/Aとは異なり、fi/(A・B)となるので、設定の自由度が高くなる。

この結果、分周数A、Bを適切な値に設定することにより、基準信号の周波数fiによらず、所望周波数m・fx、n・fxをほぼ一定値にすることができる。

【0053】

なお、上記説明では、所望周波数m・fx、n・fxは互いに異なる周波数であることを想定しているが、同一周波数(m・fx=n・fx)であっても同等の作用効果を奏することは言うまでもない。

【0054】

所望周波数m・fx、n・fxが同一周波数の場合には、図5、図7に対応する周波数変換回路10は、それぞれ図8、図9で示す回路構成に削減することができる。

すなわち、図5、図7内の2つのフィルタ23、24のうち、一方を削除して、1つのフィルタ23のみを使用すればよい。

図8,図9の回路構成により、基準周波数信号源の全体サイズを小さくするとともに、コストダウンを実現することができる。

【0055】

以上のように、この発明の実施の形態2(図5)による周波数変換回路10は、制御信号Cに応じて基準信号(fi)を周波数分周する可変分周器21(第1の可変分周器)と、可変分周器21からの分周信号(fi/A)と基準信号(fi)とを周波数混合するミクサ22(第2のミクサ)と、ミクサ22からの混合信号に含まれる混合波のうち、クロック信号に対応した第1の所望波(m・fx)以外を抑圧するフィルタ23(第3のフィルタ)と、ミクサ22からの混合信号に含まれる混合波のうち、局部発振信号に対応した第2の所望波(m・fx)以外を抑圧するフィルタ24(第4のフィルタ)と、を備えている。

【0056】

また、この発明の実施の形態2(図8)による周波数変換回路10は、制御信号Cに応じて基準信号を周波数分周する可変分周器21と、可変分周器21からの分周信号と基準信号とを周波数混合するミクサ22と、ミクサ22からの混合信号に含まれる混合波のうち、クロック信号および局部発振信号に対応した所望波以外を抑圧するフィルタ23(第3のフィルタ)とを備えている。

【0057】

さらに、この発明の実施の形態2(図7、図9)による周波数変換回路10は、図5、図8の構成に加えて、基準信号の入力端子とミクサ22との間に挿入され、制御信号Cに応じて基準信号を周波数分周する可変分周器25(第2の可変分周器)を備えており、ミクサ22は、可変分周器21からの分周信号と可変分周器22からの分周信号とを周波数混合する。

これにより、この発明の実施の形態2によれば、前述の実施の形態1と同様の作用効果を奏することができる。

【符号の説明】

【0058】

1 基準信号源、2 直接デジタルシンセサイザ(DDS)、3 フィルタ(第1のフィルタ)、4 分周器、5 位相比較器、6 ループフィルタ、7 電圧制御発振器、8 ミクサ(第1のミクサ)、9 フィルタ(第2のフィルタ)、10 周波数変換回路、11 分周器、19 所望値、21 可変分周器(第1の可変分周器)、22 ミクサ(第2のミクサ)、23 フィルタ(第3のフィルタ)、24 フィルタ(第4のフィルタ)、25 可変分周器(第2の可変分周器)、C 制御信号。

【特許請求の範囲】

【請求項1】

基準信号を生成する基準信号源と、

前記基準信号と前記基準信号の周波数に応じた制御信号とに基づいてクロック信号および局部発振信号を生成する周波数変換回路と、

前記クロック信号に同期して、周波数制御データに応じた周波数信号を生成する直接デジタルシンセサイザと、

前記直接デジタルシンセサイザからの周波数信号に含まれる不要波成分を抑圧する第1のフィルタと、

前記局部発振信号と後記電圧制御発振器の出力信号とを周波数混合する第1のミクサと、

前記第1のミクサからの混合信号に含まれる不要波成分を抑圧する第2のフィルタと、

前記第1のフィルタを介した周波数信号と前記第2のフィルタを介した混合信号との位相差を検出する位相比較器と、

前記位相比較器からの位相差信号を濾波するループフィルタと、

前記ループフィルタを介した位相差信号に応じて前記出力信号を生成する電圧制御発振器と

を備えたことを特徴とする基準周波数信号源。

【請求項2】

前記第1のフィルタと前記位相比較器との間、および、前記第2のフィルタと前記位相比較器との間、の少なくとも一方に周波数分周する分周器を挿入したことを特徴とする請求項1に記載の基準周波数信号源。

【請求項3】

前記周波数変換回路は、

前記制御信号に応じて前記基準信号を周波数分周する第1の可変分周器と、

前記第1の可変分周器からの分周信号と前記基準信号とを周波数混合する第2のミクサと、

前記第2のミクサからの混合信号に含まれる混合波のうち、前記クロック信号に対応した第1の所望波以外を抑圧する第3のフィルタと、

前記第2のミクサからの混合信号に含まれる混合波のうち、前記局部発振信号に対応した第2の所望波以外を抑圧する第4のフィルタと

を備えたことを特徴とする請求項1または請求項2に記載の基準周波数信号源。

【請求項4】

前記周波数変換回路は、

前記制御信号に応じて前記基準信号を周波数分周する第1の可変分周器と、

前記第1の可変分周器からの分周信号と前記基準信号とを周波数混合する第2のミクサと、

前記第2のミクサからの混合信号に含まれる混合波のうち、前記クロック信号および前記局部発振信号に対応した所望波以外を抑圧する第3のフィルタと

を備えたことを特徴とする請求項1または請求項2に記載の基準周波数信号源。

【請求項5】

前記周波数変換回路は、

前記基準信号の入力端子と前記第2のミクサとの間に挿入され、前記制御信号に応じて前記基準信号を周波数分周する第2の可変分周器を備え、

前記第2のミクサは、前記第1の可変分周器からの分周信号と前記第2の可変分周器からの分周信号とを周波数混合することを特徴とする請求項3または請求項4に記載の基準周波数信号源。

【請求項6】

前記基準信号源は、前記基準信号の周波数を変更可能な可変信号源により構成されたことを特徴とする請求項1から請求項5までのいずれか1項に記載の基準周波数信号源。

【請求項1】

基準信号を生成する基準信号源と、

前記基準信号と前記基準信号の周波数に応じた制御信号とに基づいてクロック信号および局部発振信号を生成する周波数変換回路と、

前記クロック信号に同期して、周波数制御データに応じた周波数信号を生成する直接デジタルシンセサイザと、

前記直接デジタルシンセサイザからの周波数信号に含まれる不要波成分を抑圧する第1のフィルタと、

前記局部発振信号と後記電圧制御発振器の出力信号とを周波数混合する第1のミクサと、

前記第1のミクサからの混合信号に含まれる不要波成分を抑圧する第2のフィルタと、

前記第1のフィルタを介した周波数信号と前記第2のフィルタを介した混合信号との位相差を検出する位相比較器と、

前記位相比較器からの位相差信号を濾波するループフィルタと、

前記ループフィルタを介した位相差信号に応じて前記出力信号を生成する電圧制御発振器と

を備えたことを特徴とする基準周波数信号源。

【請求項2】

前記第1のフィルタと前記位相比較器との間、および、前記第2のフィルタと前記位相比較器との間、の少なくとも一方に周波数分周する分周器を挿入したことを特徴とする請求項1に記載の基準周波数信号源。

【請求項3】

前記周波数変換回路は、

前記制御信号に応じて前記基準信号を周波数分周する第1の可変分周器と、

前記第1の可変分周器からの分周信号と前記基準信号とを周波数混合する第2のミクサと、

前記第2のミクサからの混合信号に含まれる混合波のうち、前記クロック信号に対応した第1の所望波以外を抑圧する第3のフィルタと、

前記第2のミクサからの混合信号に含まれる混合波のうち、前記局部発振信号に対応した第2の所望波以外を抑圧する第4のフィルタと

を備えたことを特徴とする請求項1または請求項2に記載の基準周波数信号源。

【請求項4】

前記周波数変換回路は、

前記制御信号に応じて前記基準信号を周波数分周する第1の可変分周器と、

前記第1の可変分周器からの分周信号と前記基準信号とを周波数混合する第2のミクサと、

前記第2のミクサからの混合信号に含まれる混合波のうち、前記クロック信号および前記局部発振信号に対応した所望波以外を抑圧する第3のフィルタと

を備えたことを特徴とする請求項1または請求項2に記載の基準周波数信号源。

【請求項5】

前記周波数変換回路は、

前記基準信号の入力端子と前記第2のミクサとの間に挿入され、前記制御信号に応じて前記基準信号を周波数分周する第2の可変分周器を備え、

前記第2のミクサは、前記第1の可変分周器からの分周信号と前記第2の可変分周器からの分周信号とを周波数混合することを特徴とする請求項3または請求項4に記載の基準周波数信号源。

【請求項6】

前記基準信号源は、前記基準信号の周波数を変更可能な可変信号源により構成されたことを特徴とする請求項1から請求項5までのいずれか1項に記載の基準周波数信号源。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2011−166684(P2011−166684A)

【公開日】平成23年8月25日(2011.8.25)

【国際特許分類】

【出願番号】特願2010−30405(P2010−30405)

【出願日】平成22年2月15日(2010.2.15)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成23年8月25日(2011.8.25)

【国際特許分類】

【出願日】平成22年2月15日(2010.2.15)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]