基準電圧回路

【課題】 デプレッション型MOSFETとエンハンスメント型MOSFETとを用いた基準電圧回路において、基準電圧を低電圧化する。

【解決手段】 デプレッション型MOSFET(M1)のソースを、主トランジスタがn型であるソースフォロワ11の入力端子に接続し、ソースフォロワ11の出力端子を主トランジスタがp型であるソースフォロワ12の入力端子に接続し、ソースフォロワ12の出力はエンハンスメント型MOSFET(M2)のゲートに接続され、

ソースフォロワ12の出力を抵抗分割して所定の電圧を得ることを特徴とする基準電圧回路とする。

【解決手段】 デプレッション型MOSFET(M1)のソースを、主トランジスタがn型であるソースフォロワ11の入力端子に接続し、ソースフォロワ11の出力端子を主トランジスタがp型であるソースフォロワ12の入力端子に接続し、ソースフォロワ12の出力はエンハンスメント型MOSFET(M2)のゲートに接続され、

ソースフォロワ12の出力を抵抗分割して所定の電圧を得ることを特徴とする基準電圧回路とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の内部の基準電圧回路において出力電圧の低電圧化に係るものである。

【背景技術】

【0002】

図4に従来の基準電圧回路を示す。nチャネルのデプレッション型MOSFETのゲートとソースを共に接続して定電流を作り出す第1のトランジスタM1と、

nチャネルのMOSFETのゲートとドレインを共に接続してダイオード接続された第2のトランジスタM2が、第1のトランジスタM1のソースと第2のトランジスタM2のドレインが共に接続されて、電源電圧VDDとグランドGND間に直列に接続されている。この回路において基準電圧VREFは第2のトランジスタのゲート・ソース間電圧Vgs2である。

【0003】

第1のトランジスタM1のドレイン電流Id1と第2のトランジスタM2のドレイン電流Id2は、Vds>Vgs−Vtにおいて、

Id1=β1/2(Vgs1−Vt1)2 (1)

Id2=β2/2(Vgs2−Vt2)2 (2)

である。

Vdsはドレイン・ソース間電圧、Vgsはゲート・ソース間電圧、Vtは閾値電圧である。Vgs1とVgs2、Vt1とVt2は、それぞれ第1のトランジスタM1と第2のトランジスタM2のゲート・ソース間電圧、閾値電圧である。また、β1、β2は、それぞれ第1のトランジスタM1と第2のトランジスタM2の導電係数であり、

β=(εox/tox)μ(W/L)

の形で表わされる。ここで、μはキャリア移動度、εoxは酸化膜の誘電率、toxは酸化膜厚、Wはゲート幅、Lはゲート長である。

(1)式と(2)式は、Id1=Id2,Vgs1=0,Vgs2=VREFより、

β1(−Vt1)2=β2(VREF−Vt2)2となり、

【数1】

となる。

【0004】

同一半導体内であれば第1のトランジスタM1と第2のトランジスタM2の酸化膜の誘電率εox、酸化膜厚toxは同じである。ここで更に閾値電圧Vt1とVt2の温度特性がほぼ同じとなるゲート長L,ゲート幅Wとすれば、第1のトランジスタM1と第2のトランジスタM2の導電係数は、β1≒β2の関係となる。

第1のトランジスタM1の閾値電圧Vt1は負の値なので、基準電圧VREFは第1のトランジスタM1と第2のトランジスタM2の閾値電圧の絶対値の和の大きさとなる。なお、閾値電圧が温度で変化した場合は第1のトランジスタM1と第2のトランジスタM2の両方の閾値電圧は同じ方向に増減するので、閾値電圧の温度変化による基準電圧VREFの温度変化は極めて小さくなる。

したがって、図4に示す従来の基準電圧回路は、電源電圧に依存しない、温度依存性の小さい基準電圧VREFを得る。

【0005】

近年、携帯端末等の普及に伴いバッテリーによる動作時間を延長するために、機器の動作電圧を下げて低消費電力化を低減するということが行われている。このような動作電圧の低電圧化においては低い電圧を出力する電源回路が必要であり、その電源回路を動作させる上で低い基準電圧が必要である。

【0006】

【特許文献1】特公平4−65546号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

今後の低電圧化には更に低い基準電圧が必要だが、前記従来回路において基準電圧VREFは第1のトランジスタM1と第2のトランジスタM2の閾値電圧の絶対値の和でほぼ決まってしまう。このため、それより更に低い基準電圧VREFを得るためには普通、基準電圧VREFを抵抗で分割するが、Id1=Id2とならないので基準電圧が変わってしまう恐れがある。この問題に対応するために回路を追加した場合は、追加した回路により基準電圧の精度が低下してしまう問題があった。

【0008】

本発明は、温度依存度が小さく、従来の基準電圧回路と比較して低い基準電圧を得る基準電圧回路を提供すること目的とする。

【課題を解決するための手段】

【0009】

デプレッション型MOSFETの第1のトランジスタと、エンハンスメント型MOSFETの第2のトランジスタとが、電源電圧端子間に直列に接続された基準電圧回路において、該基準電圧回路は、

前記第1のトランジスタのドレインを高電圧供給端子に接続し、

前記第2のトランジスタのソースを低電圧供給端子に接続し、

前記第1のトランジスタのソースとゲートを共に接続し、

前記第1のトランジスタのソースを第1のソースフォロワの入力に接続し、

前記第1のソースフォロワの出力を第2のソースフォロワの入力に接続し、

第2のソースフォロワの出力を前記第2のトランジスタのゲートに接続し、

第2のソースフォロワの出力から所定の基準電圧を得ることを特徴とする。

前記第1,2のソースフォロワは、ソース接地増幅であってもよい。

【発明の効果】

【0010】

本発明によれば、電圧が1V以下の任意の基準電圧を容易に得ることができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施の形態を図示例と共に説明する。

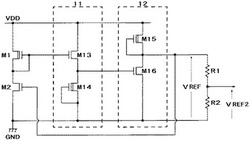

図1は本発明の第1の実施形態を示す回路図である。

図において、ソースフォロワ11は直列に接続された、n型のエンハンスメント型MOSFETからなるトランジスタM13と、n型のデプレッション型MOSFETからなるトランジスタM14で構成され、トランジスタM13のドレインは電源電圧VDDに接続され、トランジスタM14のソースはグランドGNDに接続され、トランジスタM14のゲートとソースは互いに接続されている。

ソースフォロワ12は直列に接続された、n型のデプレッション型MOSFETからなるトランジスタM15と、p型のエンハンスメント型MOSFETからなるトランジスタM16で構成され、トランジスタM15のドレインは電源電圧VDDに接続され、トランジスタM16のドレインはグランドGNDに接続され、トランジスタM15のゲートとソースは互いに接続されている。

n型のデプレッション型MOSFETからなる第1のトランジスタM1と、n型のエンハンスメント型MOSFETからなる第2のトランジスタM2とが、電源電圧VDDとグランドGND間に直列に接続され、第1のトランジスタM1のソースはゲートに接続されている。

第1のトランジスタM1のゲートはソースフォロワ11の入力であるトランジスタM13のゲートに接続され、第2のトランジスタM2のゲートはソースフォロワ12の出力であるトランジスタM16のソースに接続され、ソースフォロワ11の出力であるトランジスタM13のソースは、ソースフォロワ12の入力であるトランジスタM16のゲートに接続されている。

第2のトランジスタM2のゲートとソースフォロワ12の出力の接続点は、分圧回路を構成する抵抗R1とR2に接続されている。そして抵抗R1とR2の共通接続点は、基準電圧VREF2の供給先回路(図示せず)に接続された回路構成となっている。

【0012】

このような構成を持つ図1の回路動作は、概ね以下のようになる。

例えば、基準電圧VREF(第2のトランジスタM2のゲート電圧)が何らかの原因で所定の値より高くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)はそれまでの値から低くなろうとする。

第1のトランジスタM1のゲート電圧(ソースフォロワ11の入力)が低くなろうとすると、ソースフォロワ11の出力(ソースフォロワ12の入力)は低くなろうとする。

ソースフォロワ12の入力が低くなろうとすると、ソースフォロワ12の出力(第2のトランジスタM2のゲート電圧)は低くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

逆に、基準電圧VREF(第2のトランジスタM2のゲート電圧)が所定の値より低くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)が高くなろうとする。

第1のトランジスタM1のゲート電圧(ソースフォロワ11の入力)が高くなろうとすると、ソースフォロワ11の出力(ソースフォロワ12の入力)は高くなろうとする。

ソースフォロワ12の入力が高くなろうとすると、ソースフォロワ12の出力(第2のトランジスタM2のゲート電圧)は高くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

以上に説明したような回路各部に生じる動作作用により、第2のトランジスタM2のゲート電圧は、所定の基準電圧VREFに安定化される。

【0013】

なお第1のトランジスタM1のゲート電圧は、第2のトランジスタM2のゲート電圧に対してソースフォロワ11によりトランジスタM13のゲート・ソース電圧Vgs13だけ低くなるようにレベルシフトされた電圧となり、ソースフォロワ12によってトランジスタM16のゲートソース間電圧Vgs16だけ高くなるようにレベルシフトされた電圧となる。Vgs13≒Vgs16になっていれば、第1のトランジスタM1のゲート電圧と第2のトランジスタM2のゲート電圧はほぼ同じ電圧となり、第1のトランジスタM1と第2のトランジスタM2の動作は従来例と実質的に同じとなる。ここで図1のように基準電圧VREF2を得るために基準電圧VREFを抵抗R1とR2で分割した場合に、抵抗R1とR2に電流が流れて第2のトランジスタM2のゲート電圧が変化しようとしても帰還制御ループにより第2のトランジスタM2のゲート電圧が安定された基準電圧VREFとなることが本発明の特徴である。

したがって、抵抗R1とR2の比を変えることにより、基準電圧VREF2を基準電圧VREFより低い任意の電圧値に設定することが可能である。

なお、抵抗R1とR2の少なくとも一方をあらかじめ複数の抵抗で構成し、それぞれの抵抗に並列にヒューズを設けた上で当該ヒューズを選択的にレーザで切断することで、基準電圧を変更することも可能である。

【0014】

図2は、温度特性を示すグラフであり、横軸は温度であり、縦軸は電圧である。図において、特性Aは図5に示す従来回路の場合であり、特性Bは図1に示す実施例において、抵抗R1とR2を1MΩとした場合である。

図2から判るように本発明の基準電圧回路の特性Bは、従来回路の特性Aと同等の温度依存度であり、基準電圧は特性Aより低くなる。

【0015】

図3は本発明の第2の実施形態を示す回路図である。

図3に示す回路は、図1のソースフォロワ11,12を、ソース接地21,22で置換したものである。

ソース接地21は直列に接続された、n型のデプレッション型MOSFETからなるトランジスタM23と、n型のエンハンスメント型MOSFETからなるトランジスタM24で構成され、トランジスタM23のドレインは電源電圧VDDに接続され、トランジスタM24のソースはグランドGNDに接続され、トランジスタM23のゲート・ソース間は互いに接続されている。

ソース接地22は直列に接続された、n型のデプレッション型MOSFETからなるトランジスタM25と、n型のエンハンスメント型MOSFETからなるトランジスタM26で構成され、トランジスタM25のドレインは電源電圧VDDに接続され、トランジスタM26のソースはグランドGNDに接続され、トランジスタM25のゲート・ソース間は互いに接続されている。

【0016】

このような構成を持つ図3の回路動作は、概ね以下のようになる。

例えば、基準電圧VREF(第2のトランジスタM2のゲート電圧)が何らかの原因で所定のより高くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)はそれまでの値から低くなろうとする。

第1のトランジスタM1のゲート電圧(ソース接地21の入力)が低くなろうとすると、ソース接地21の出力(ソース接地22の入力)は高くなろうとする。

ソース接地22の入力が高くなろうとすると、ソース接地22の出力(第2のトランジスタM2のゲート電圧)は低くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

逆に、基準電圧VREF(第2のトランジスタM2のゲート電圧)が所定の値より低くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)が高くなろうとする。

第1のトランジスタM1のゲート電圧(ソース接地21の入力)が高くなろうとすると、ソース接地21の出力(ソース接地22の入力)は低くなろうとする。

ソース接地22の入力が低くなろうとすると、ソース接地22の出力(第2のトランジスタM2のゲート電圧)は高くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

以上に説明したような回路各部に生じる動作作用により、第2のトランジスタM2のゲート電圧は、所定の基準電圧VREFに安定化される。

【0017】

上述した実施形態において、第1の実施形態におけるトランジスタM14とM15、第2の実施形態におけるトランジスタM23とM25は、MOSFETトランジスタに限定されるものではなく、例えば、抵抗、ダイオードを用いてもよい。

【図面の簡単な説明】

【0018】

【図1】本発明の第1の実施形態の例を示す回路図である。

【図2】本発明の第1の実施形態と従来例における、温度特性を示すグラフである。

【図3】本発明の第2の実施形態の例を示す回路図である。

【図4】従来の基準電圧回路を示す回路図である。

【符号の説明】

【0019】

M2,M13,M24,M26 n型のエンハンスメント型MOSFET

M1,M14,M15,M23,M25 n型のデプレッション型MOSFET

M16 p型のエンハンスメント型MOSFET

R1,R2 抵抗

GND グランド電位

VDD 電源電位

11,12 ソースフォロワ

21,22 ソース接地

【技術分野】

【0001】

本発明は、半導体装置の内部の基準電圧回路において出力電圧の低電圧化に係るものである。

【背景技術】

【0002】

図4に従来の基準電圧回路を示す。nチャネルのデプレッション型MOSFETのゲートとソースを共に接続して定電流を作り出す第1のトランジスタM1と、

nチャネルのMOSFETのゲートとドレインを共に接続してダイオード接続された第2のトランジスタM2が、第1のトランジスタM1のソースと第2のトランジスタM2のドレインが共に接続されて、電源電圧VDDとグランドGND間に直列に接続されている。この回路において基準電圧VREFは第2のトランジスタのゲート・ソース間電圧Vgs2である。

【0003】

第1のトランジスタM1のドレイン電流Id1と第2のトランジスタM2のドレイン電流Id2は、Vds>Vgs−Vtにおいて、

Id1=β1/2(Vgs1−Vt1)2 (1)

Id2=β2/2(Vgs2−Vt2)2 (2)

である。

Vdsはドレイン・ソース間電圧、Vgsはゲート・ソース間電圧、Vtは閾値電圧である。Vgs1とVgs2、Vt1とVt2は、それぞれ第1のトランジスタM1と第2のトランジスタM2のゲート・ソース間電圧、閾値電圧である。また、β1、β2は、それぞれ第1のトランジスタM1と第2のトランジスタM2の導電係数であり、

β=(εox/tox)μ(W/L)

の形で表わされる。ここで、μはキャリア移動度、εoxは酸化膜の誘電率、toxは酸化膜厚、Wはゲート幅、Lはゲート長である。

(1)式と(2)式は、Id1=Id2,Vgs1=0,Vgs2=VREFより、

β1(−Vt1)2=β2(VREF−Vt2)2となり、

【数1】

となる。

【0004】

同一半導体内であれば第1のトランジスタM1と第2のトランジスタM2の酸化膜の誘電率εox、酸化膜厚toxは同じである。ここで更に閾値電圧Vt1とVt2の温度特性がほぼ同じとなるゲート長L,ゲート幅Wとすれば、第1のトランジスタM1と第2のトランジスタM2の導電係数は、β1≒β2の関係となる。

第1のトランジスタM1の閾値電圧Vt1は負の値なので、基準電圧VREFは第1のトランジスタM1と第2のトランジスタM2の閾値電圧の絶対値の和の大きさとなる。なお、閾値電圧が温度で変化した場合は第1のトランジスタM1と第2のトランジスタM2の両方の閾値電圧は同じ方向に増減するので、閾値電圧の温度変化による基準電圧VREFの温度変化は極めて小さくなる。

したがって、図4に示す従来の基準電圧回路は、電源電圧に依存しない、温度依存性の小さい基準電圧VREFを得る。

【0005】

近年、携帯端末等の普及に伴いバッテリーによる動作時間を延長するために、機器の動作電圧を下げて低消費電力化を低減するということが行われている。このような動作電圧の低電圧化においては低い電圧を出力する電源回路が必要であり、その電源回路を動作させる上で低い基準電圧が必要である。

【0006】

【特許文献1】特公平4−65546号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

今後の低電圧化には更に低い基準電圧が必要だが、前記従来回路において基準電圧VREFは第1のトランジスタM1と第2のトランジスタM2の閾値電圧の絶対値の和でほぼ決まってしまう。このため、それより更に低い基準電圧VREFを得るためには普通、基準電圧VREFを抵抗で分割するが、Id1=Id2とならないので基準電圧が変わってしまう恐れがある。この問題に対応するために回路を追加した場合は、追加した回路により基準電圧の精度が低下してしまう問題があった。

【0008】

本発明は、温度依存度が小さく、従来の基準電圧回路と比較して低い基準電圧を得る基準電圧回路を提供すること目的とする。

【課題を解決するための手段】

【0009】

デプレッション型MOSFETの第1のトランジスタと、エンハンスメント型MOSFETの第2のトランジスタとが、電源電圧端子間に直列に接続された基準電圧回路において、該基準電圧回路は、

前記第1のトランジスタのドレインを高電圧供給端子に接続し、

前記第2のトランジスタのソースを低電圧供給端子に接続し、

前記第1のトランジスタのソースとゲートを共に接続し、

前記第1のトランジスタのソースを第1のソースフォロワの入力に接続し、

前記第1のソースフォロワの出力を第2のソースフォロワの入力に接続し、

第2のソースフォロワの出力を前記第2のトランジスタのゲートに接続し、

第2のソースフォロワの出力から所定の基準電圧を得ることを特徴とする。

前記第1,2のソースフォロワは、ソース接地増幅であってもよい。

【発明の効果】

【0010】

本発明によれば、電圧が1V以下の任意の基準電圧を容易に得ることができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施の形態を図示例と共に説明する。

図1は本発明の第1の実施形態を示す回路図である。

図において、ソースフォロワ11は直列に接続された、n型のエンハンスメント型MOSFETからなるトランジスタM13と、n型のデプレッション型MOSFETからなるトランジスタM14で構成され、トランジスタM13のドレインは電源電圧VDDに接続され、トランジスタM14のソースはグランドGNDに接続され、トランジスタM14のゲートとソースは互いに接続されている。

ソースフォロワ12は直列に接続された、n型のデプレッション型MOSFETからなるトランジスタM15と、p型のエンハンスメント型MOSFETからなるトランジスタM16で構成され、トランジスタM15のドレインは電源電圧VDDに接続され、トランジスタM16のドレインはグランドGNDに接続され、トランジスタM15のゲートとソースは互いに接続されている。

n型のデプレッション型MOSFETからなる第1のトランジスタM1と、n型のエンハンスメント型MOSFETからなる第2のトランジスタM2とが、電源電圧VDDとグランドGND間に直列に接続され、第1のトランジスタM1のソースはゲートに接続されている。

第1のトランジスタM1のゲートはソースフォロワ11の入力であるトランジスタM13のゲートに接続され、第2のトランジスタM2のゲートはソースフォロワ12の出力であるトランジスタM16のソースに接続され、ソースフォロワ11の出力であるトランジスタM13のソースは、ソースフォロワ12の入力であるトランジスタM16のゲートに接続されている。

第2のトランジスタM2のゲートとソースフォロワ12の出力の接続点は、分圧回路を構成する抵抗R1とR2に接続されている。そして抵抗R1とR2の共通接続点は、基準電圧VREF2の供給先回路(図示せず)に接続された回路構成となっている。

【0012】

このような構成を持つ図1の回路動作は、概ね以下のようになる。

例えば、基準電圧VREF(第2のトランジスタM2のゲート電圧)が何らかの原因で所定の値より高くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)はそれまでの値から低くなろうとする。

第1のトランジスタM1のゲート電圧(ソースフォロワ11の入力)が低くなろうとすると、ソースフォロワ11の出力(ソースフォロワ12の入力)は低くなろうとする。

ソースフォロワ12の入力が低くなろうとすると、ソースフォロワ12の出力(第2のトランジスタM2のゲート電圧)は低くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

逆に、基準電圧VREF(第2のトランジスタM2のゲート電圧)が所定の値より低くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)が高くなろうとする。

第1のトランジスタM1のゲート電圧(ソースフォロワ11の入力)が高くなろうとすると、ソースフォロワ11の出力(ソースフォロワ12の入力)は高くなろうとする。

ソースフォロワ12の入力が高くなろうとすると、ソースフォロワ12の出力(第2のトランジスタM2のゲート電圧)は高くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

以上に説明したような回路各部に生じる動作作用により、第2のトランジスタM2のゲート電圧は、所定の基準電圧VREFに安定化される。

【0013】

なお第1のトランジスタM1のゲート電圧は、第2のトランジスタM2のゲート電圧に対してソースフォロワ11によりトランジスタM13のゲート・ソース電圧Vgs13だけ低くなるようにレベルシフトされた電圧となり、ソースフォロワ12によってトランジスタM16のゲートソース間電圧Vgs16だけ高くなるようにレベルシフトされた電圧となる。Vgs13≒Vgs16になっていれば、第1のトランジスタM1のゲート電圧と第2のトランジスタM2のゲート電圧はほぼ同じ電圧となり、第1のトランジスタM1と第2のトランジスタM2の動作は従来例と実質的に同じとなる。ここで図1のように基準電圧VREF2を得るために基準電圧VREFを抵抗R1とR2で分割した場合に、抵抗R1とR2に電流が流れて第2のトランジスタM2のゲート電圧が変化しようとしても帰還制御ループにより第2のトランジスタM2のゲート電圧が安定された基準電圧VREFとなることが本発明の特徴である。

したがって、抵抗R1とR2の比を変えることにより、基準電圧VREF2を基準電圧VREFより低い任意の電圧値に設定することが可能である。

なお、抵抗R1とR2の少なくとも一方をあらかじめ複数の抵抗で構成し、それぞれの抵抗に並列にヒューズを設けた上で当該ヒューズを選択的にレーザで切断することで、基準電圧を変更することも可能である。

【0014】

図2は、温度特性を示すグラフであり、横軸は温度であり、縦軸は電圧である。図において、特性Aは図5に示す従来回路の場合であり、特性Bは図1に示す実施例において、抵抗R1とR2を1MΩとした場合である。

図2から判るように本発明の基準電圧回路の特性Bは、従来回路の特性Aと同等の温度依存度であり、基準電圧は特性Aより低くなる。

【0015】

図3は本発明の第2の実施形態を示す回路図である。

図3に示す回路は、図1のソースフォロワ11,12を、ソース接地21,22で置換したものである。

ソース接地21は直列に接続された、n型のデプレッション型MOSFETからなるトランジスタM23と、n型のエンハンスメント型MOSFETからなるトランジスタM24で構成され、トランジスタM23のドレインは電源電圧VDDに接続され、トランジスタM24のソースはグランドGNDに接続され、トランジスタM23のゲート・ソース間は互いに接続されている。

ソース接地22は直列に接続された、n型のデプレッション型MOSFETからなるトランジスタM25と、n型のエンハンスメント型MOSFETからなるトランジスタM26で構成され、トランジスタM25のドレインは電源電圧VDDに接続され、トランジスタM26のソースはグランドGNDに接続され、トランジスタM25のゲート・ソース間は互いに接続されている。

【0016】

このような構成を持つ図3の回路動作は、概ね以下のようになる。

例えば、基準電圧VREF(第2のトランジスタM2のゲート電圧)が何らかの原因で所定のより高くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)はそれまでの値から低くなろうとする。

第1のトランジスタM1のゲート電圧(ソース接地21の入力)が低くなろうとすると、ソース接地21の出力(ソース接地22の入力)は高くなろうとする。

ソース接地22の入力が高くなろうとすると、ソース接地22の出力(第2のトランジスタM2のゲート電圧)は低くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

逆に、基準電圧VREF(第2のトランジスタM2のゲート電圧)が所定の値より低くなろうとすると、第2のトランジスタM2のドレイン電圧(第1のトランジスタM1のゲート電圧)が高くなろうとする。

第1のトランジスタM1のゲート電圧(ソース接地21の入力)が高くなろうとすると、ソース接地21の出力(ソース接地22の入力)は低くなろうとする。

ソース接地22の入力が低くなろうとすると、ソース接地22の出力(第2のトランジスタM2のゲート電圧)は高くなろうとする。

その結果、基準電圧VREFの元の値に戻ろうとする作用が働く。

以上に説明したような回路各部に生じる動作作用により、第2のトランジスタM2のゲート電圧は、所定の基準電圧VREFに安定化される。

【0017】

上述した実施形態において、第1の実施形態におけるトランジスタM14とM15、第2の実施形態におけるトランジスタM23とM25は、MOSFETトランジスタに限定されるものではなく、例えば、抵抗、ダイオードを用いてもよい。

【図面の簡単な説明】

【0018】

【図1】本発明の第1の実施形態の例を示す回路図である。

【図2】本発明の第1の実施形態と従来例における、温度特性を示すグラフである。

【図3】本発明の第2の実施形態の例を示す回路図である。

【図4】従来の基準電圧回路を示す回路図である。

【符号の説明】

【0019】

M2,M13,M24,M26 n型のエンハンスメント型MOSFET

M1,M14,M15,M23,M25 n型のデプレッション型MOSFET

M16 p型のエンハンスメント型MOSFET

R1,R2 抵抗

GND グランド電位

VDD 電源電位

11,12 ソースフォロワ

21,22 ソース接地

【特許請求の範囲】

【請求項1】

デプレッション型MOSFETの第1のトランジスタと、エンハンスメント型MOSFETの第2のトランジスタとが、電源電圧端子間に直列に接続された基準電圧回路において、該基準電圧回路は、

前記第1のトランジスタのドレインを高電圧供給端子に接続し、

前記第2のトランジスタのソースを低電圧供給端子に接続し、

前記第1のトランジスタのソースとゲートを共に接続し、

前記第1のトランジスタのソースを第1のソースフォロワの入力に接続し、

前記第1のソースフォロワの出力を第2のソースフォロワの入力に接続し、

第2のソースフォロワの出力を前記第2のトランジスタのゲートに接続し、

第2のソースフォロワの出力から所定の基準電圧を得ることを特徴とする基準電圧回路。

【請求項2】

前記第1のソースフォロワは主トランジスタにnチャネル型のMOSFETを備え、前記第2のソースフォロワは主トランジスタにpチャネル型のMOSFETを備えた

ことを特徴とする請求項1に記載の基準電圧回路。

【請求項3】

前記第1〜2のソースフォロワが、nチャネル型のMOSFETからなるソース接地増幅器であることを特徴とする請求項1に記載の基準電圧回路。

【請求項4】

前記基準電圧回路は、第2のトランジスタのゲート電圧を複数の抵抗で分割し、該複数の抵抗の接続点から所定の基準電圧を得ることを特徴とする請求項1と3に記載の基準電圧回路。

【請求項5】

前記複数の抵抗は、トリミングにより所望の抵抗値に設定できる抵抗体を含んでいることを特徴とする請求項4に記載の基準電圧回路。

【請求項1】

デプレッション型MOSFETの第1のトランジスタと、エンハンスメント型MOSFETの第2のトランジスタとが、電源電圧端子間に直列に接続された基準電圧回路において、該基準電圧回路は、

前記第1のトランジスタのドレインを高電圧供給端子に接続し、

前記第2のトランジスタのソースを低電圧供給端子に接続し、

前記第1のトランジスタのソースとゲートを共に接続し、

前記第1のトランジスタのソースを第1のソースフォロワの入力に接続し、

前記第1のソースフォロワの出力を第2のソースフォロワの入力に接続し、

第2のソースフォロワの出力を前記第2のトランジスタのゲートに接続し、

第2のソースフォロワの出力から所定の基準電圧を得ることを特徴とする基準電圧回路。

【請求項2】

前記第1のソースフォロワは主トランジスタにnチャネル型のMOSFETを備え、前記第2のソースフォロワは主トランジスタにpチャネル型のMOSFETを備えた

ことを特徴とする請求項1に記載の基準電圧回路。

【請求項3】

前記第1〜2のソースフォロワが、nチャネル型のMOSFETからなるソース接地増幅器であることを特徴とする請求項1に記載の基準電圧回路。

【請求項4】

前記基準電圧回路は、第2のトランジスタのゲート電圧を複数の抵抗で分割し、該複数の抵抗の接続点から所定の基準電圧を得ることを特徴とする請求項1と3に記載の基準電圧回路。

【請求項5】

前記複数の抵抗は、トリミングにより所望の抵抗値に設定できる抵抗体を含んでいることを特徴とする請求項4に記載の基準電圧回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2009−294978(P2009−294978A)

【公開日】平成21年12月17日(2009.12.17)

【国際特許分類】

【出願番号】特願2008−148959(P2008−148959)

【出願日】平成20年6月6日(2008.6.6)

【出願人】(509120894)旭化成東光パワーデバイス株式会社 (20)

【Fターム(参考)】

【公開日】平成21年12月17日(2009.12.17)

【国際特許分類】

【出願日】平成20年6月6日(2008.6.6)

【出願人】(509120894)旭化成東光パワーデバイス株式会社 (20)

【Fターム(参考)】

[ Back to top ]