基準電圧回路

【課題】温度に依存しない基準電圧をより安定に発生できる基準電圧回路を提供する。

【解決手段】NMOSトランジスタ1〜2において、ソースとバックゲートとがショートするので、閾値電圧Vth1〜Vth2はNMOSトランジスタ1〜2のプロセスばらつきだけに依存して他の素子のプロセスばらつきに依存しない。よって、温度に依存しない基準電圧Vrefがより安定に発生する。

【解決手段】NMOSトランジスタ1〜2において、ソースとバックゲートとがショートするので、閾値電圧Vth1〜Vth2はNMOSトランジスタ1〜2のプロセスばらつきだけに依存して他の素子のプロセスばらつきに依存しない。よって、温度に依存しない基準電圧Vrefがより安定に発生する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基準電圧を発生する基準電圧回路に関する。

【背景技術】

【0002】

従来の基準電圧回路について説明する。図7は、従来の基準電圧回路を示す回路図である。

【0003】

ここで、弱反転動作するMOSトランジスタにおいて、Wはゲート幅、Lはゲート長、Vthは閾値電圧、Vgsはゲート・ソース間電圧、qは電子の電荷量、kはボルツマン定数、Tは絶対温度、Id0及びnはプロセスによって定まる定数であるとすると、ドレイン電流Idは

Id=Id0・(W/L)・exp{(Vgs−Vth)・q/nkT}・・・(61)

によって算出される。nkT/qは熱電圧であるとしてUTとすると、

Id=Id0・(W/L)・exp{(Vgs−Vth)/UT}・・・(62)

が成立する。よって、ゲート・ソース間電圧Vgsは

Vgs=UT・ln[Id/{Id0・(W/L)}]+Vth・・・(63)

によって算出される。

【0004】

PMOSトランジスタ43〜45はカレントミラー接続しているので、PMOSトランジスタ43〜45のドレイン電流Id41〜Id42及びドレイン電流Id45は同一である。

【0005】

弱反転動作するNMOSトランジスタ41のゲート・ソース間電圧Vgs41から弱反転動作するNMOSトランジスタ42のゲート・ソース間電圧Vgs42を減算した電圧(Vgs41−Vgs42)が抵抗58に発生する。よって、この電圧(Vgs41−Vgs42)及び抵抗58の抵抗値R58に基づき、ドレイン電流Id42が算出され、ドレイン電流Id45も算出される。すると、

Id45=Id42=(Vgs41−Vgs42)/R58・・・(64)

が成立する。よって、R59は抵抗59の抵抗値であるとすると、抵抗59に発生する出力電圧Vrefは

Vref

=R59・Id45

=(R59/R58)・(Vgs41−Vgs42)・・・(65)

によって算出される。W41はNMOSトランジスタ41のゲート幅、L41はNMOSトランジスタ41のゲート長、Vth41はNMOSトランジスタ41の閾値電圧、W42はNMOSトランジスタ42のゲート幅、L42はNMOSトランジスタ42のゲート長、Vth42はNMOSトランジスタ42の閾値電圧、ΔVthはNMOSトランジスタ41〜42の閾値電圧差(ΔVth=Vth41−Vth42)であるとすると、式(63)より、出力電圧Vrefは

Vref

=(R59/R58)・[UT・ln{(W42/L42)/(W41/L41)}+ΔVth]・・・(66)

によって算出される。

【0006】

ここで、上記のように、第1項の温度特性と第2項の温度特性とが相殺されるようにNMOSトランジスタ41〜42のアスペクト比が調整されることにより、出力電圧Vrefは温度に依存しにくくなる(例えば、特許文献1参照)。

【特許文献1】特許第3024645号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、NMOSトランジスタ42ではソースとバックゲートとの間に抵抗58が存在する。よって、抵抗58のプロセスばらつきにより、閾値電圧Vth42もばらついてしまう。つまり、閾値電圧Vth42は、NMOSトランジスタ42のプロセスばらつきだけでなくて抵抗58のプロセスばらつきにも依存してしまう。よって、温度に依存しない基準電圧は、NMOSトランジスタ41〜42の閾値電圧差(ΔVth=Vth41−Vth42)に基づくので、不安定になってしまうことがある。

【0008】

本発明は、上記課題に鑑みてなされ、温度に依存しない基準電圧をより安定に発生できる基準電圧回路を提供する。

【課題を解決するための手段】

【0009】

本発明は、上記課題を解決するため、基準電圧を発生する基準電圧回路において、第一電源端子と、第二電源端子と、電流を入力される入力端子と、前記入力端子の電流に基づいた電流を出力する第一〜第二出力端子と、を有する電流供給回路と、第一抵抗と、ゲートを前記第一出力端子に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記第一出力端子に前記第一抵抗を介して接続され、弱反転動作する第一導電型の第一MOSトランジスタと、ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第一導電型の第二MOSトランジスタと、前記第二出力端子と前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、を備えることを特徴とする基準電圧回路を提供する。

【0010】

また、本発明は、上記課題を解決するため、基準電圧を発生する基準電圧回路において、第一電源端子と、第二電源端子と、電流を入力される入力端子及び前記入力端子の電流に基づいた電流を出力する出力端子を有する電流供給回路と、第一抵抗と、ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記出力端子に前記第一抵抗を介して接続され、弱反転動作する第二導電型の第一MOSトランジスタと、ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第二導電型の第二MOSトランジスタと、ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続される第二導電型の第三MOSトランジスタと、前記第三MOSトランジスタのドレインと前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、を備えることを特徴とする基準電圧回路を提供する。

【発明の効果】

【0011】

本発明では、第一〜第二MOSトランジスタにおいて、ソースとバックゲートとがショートするので、閾値電圧は第一〜第二MOSトランジスタのプロセスばらつきだけに依存して他の素子のプロセスばらつきに依存しない。よって、温度に依存しない基準電圧がより安定に発生する。

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施形態を、図面を参照して説明する。

【0013】

<第1実施形態>

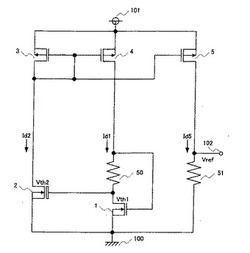

まず、基準電圧回路の構成について説明する。図1は、基準電圧回路を示す図である。

【0014】

基準電圧回路は、PMOSトランジスタ3〜5、NMOSトランジスタ1〜2及び抵抗50〜51を備える。また、基準電圧回路は、電源端子101、接地端子100及び出力端子102を備える。

【0015】

PMOSトランジスタ3は、ゲート及びドレインをNMOSトランジスタ2のドレインに接続され、ソース及びバックゲートを電源端子101に接続される。PMOSトランジスタ4は、ゲートをPMOSトランジスタ3のゲートに接続され、ソース及びバックゲートを電源端子101に接続され、ドレインを抵抗50の一端及びNMOSトランジスタ1のゲートに接続される。PMOSトランジスタ5は、ゲートをPMOSトランジスタ3のゲートに接続され、ソース及びバックゲートを電源端子101に接続され、ドレインを出力端子102に接続される。NMOSトランジスタ2は、ゲートを抵抗50の他端及びNMOSトランジスタ1のドレインに接続され、ソース及びバックゲートを接地端子100に接続される。NMOSトランジスタ1は、ソース及びバックゲートを接地端子100に接続される。抵抗51は、出力端子102と接地端子100との間に設けられる。

【0016】

PMOSトランジスタ3〜5のアスペクト比は同一である。また、PMOSトランジスタ3〜5のゲートは互いに接続される。よって、PMOSトランジスタ3〜5に流れるドレイン電流も同一になる。PMOSトランジスタ3〜5は、電流供給回路として機能し、電流を入力される入力端子(PMOSトランジスタ3のドレイン)と入力端子の電流に基づいた電流を出力する出力端子(PMOSトランジスタ4のドレイン)及び出力端子(PMOSトランジスタ5のドレイン)とを有する。

【0017】

また、NMOSトランジスタ1〜2のゲート幅はドレイン電流に対して十分に大きく設計されるので、NMOSトランジスタ1〜2は弱反転動作する。

【0018】

また、NMOSトランジスタ1の閾値電圧の絶対値はNMOSトランジスタ2の閾値電圧の絶対値よりも高い。

【0019】

抵抗50〜51は同一種類のポリシリコンで形成され、抵抗50〜51の温度係数が最小になるように、抵抗50〜51へのイオン打ち込み量は設定される。

【0020】

NMOSトランジスタ1〜2は同一濃度の基板上に形成され、NMOSトランジスタ1またはNMOSトランジスタ2のみがチャネルドープをされる。すると、NMOSトランジスタ1〜2の閾値電圧差のプロセスばらつきはNMOSトランジスタ1またはNMOSトランジスタ2のチャネルドープのプロセスばらつきにのみ依存するので、デプレッション型NMOSトランジスタと比較してプロセスばらつきの影響が小さくなる。

【0021】

なお、NMOSトランジスタ1〜2は同一濃度の基板上に形成され、NMOSトランジスタ1〜2は1回目のチャネルドープをされ、その後、NMOSトランジスタ1またはNMOSトランジスタ2のみが2回目のチャネルドープをされても良い。

【0022】

次に、基準電圧回路の動作について説明する。

【0023】

ここで、弱反転動作するMOSトランジスタにおいて、Wはゲート幅、Lはゲート長、Vthは閾値電圧、Vgsはゲート・ソース間電圧、qは電子の電荷量、kはボルツマン定数、Tは絶対温度、Id0及びnはプロセスによって定まる定数であるとすると、ドレイン電流Idは

Id=Id0・(W/L)・exp{(Vgs−Vth)・q/nkT}・・・(11)

によって算出される。nkT/qは熱電圧であるとしてUTとすると、

Id=Id0・(W/L)・exp{(Vgs−Vth)/UT}・・・(12)

が成立する。よって、ゲート・ソース間電圧Vgsは

Vgs=UT・ln[Id/{Id0・(W/L)}]+Vth・・・(13)

によって算出される。

【0024】

Vgs1はNMOSトランジスタ1のゲート・ソース間電圧、Vgs2はNMOSトランジスタ2のゲート・ソース間電圧、R50は抵抗50の抵抗値であるとすると、NMOSトランジスタ1のドレイン電流Id1は

Id1=(Vgs1−Vgs2)/R50・・・(14)

によって算出される。また、Id2はNMOSトランジスタ2のドレイン電流、W1はNMOSトランジスタ1のゲート幅、L1はNMOSトランジスタ1のゲート長、Vth1はNMOSトランジスタ1の閾値電圧、W2はNMOSトランジスタ2のゲート幅、L2はNMOSトランジスタ2のゲート長、Vth2はNMOSトランジスタ2の閾値電圧であるとすると、式(14)より、ゲート・ソース間電圧Vgs1〜Vgs2は

Vgs1=UT・ln[Id1/{Id0・(W1/L1)}]+Vth1・・・(15)

Vgs2=UT・ln[Id2/{Id0・(W2/L2)}]+Vth2・・・(16)

によって算出される。ドレイン電流Id1〜Id2は同一であり、ΔVthはNMOSトランジスタ1〜2の閾値電圧差(ΔVth=Vth1−Vth2)であるとすると、式(14)〜(16)より、ドレイン電流Id1は

Id1=(1/R50)・[UT・ln{(Id1/Id2)・(W2/L2)/(W1/L1)}+ΔVth]・・・(17)

Id1=(1/R50)・[UT・ln{(W2/L2)/(W1/L1)}+ΔVth]・・・(18)

によって算出される。

【0025】

ここで、熱電圧UTは、温度に正比例するので、正の温度係数を有する。また、NMOSトランジスタ1〜2の閾値電圧Vth1〜Vth2は、図2に示すように、負の温度係数をそれぞれ有する。閾値電圧の絶対値を高く設定されたNMOSトランジスタ1の温度係数の傾きは、NMOSトランジスタ2の温度係数の傾きよりも急になる。よって、閾値電圧差(ΔVth=Vth1−Vth2)も負の温度係数を有する。よって、式(18)において、第1項は正の温度係数を有し、第2項は負の温度係数を有するので、第1項の温度特性と第2項の温度特性とが相殺されるようにNMOSトランジスタ1〜2のアスペクト比が調整されることにより、ドレイン電流Id1は温度に依存しにくくなる。

【0026】

すると、PMOSトランジスタ4〜5において、ゲートは互いに接続し、ソースは電源端子101にそれぞれ接続しているので、ドレイン電流Id1とドレイン電流Id5とは同一になる。よって、

Id5=Id1・・・(19)

が成立する。R51は抵抗51の抵抗値であるとすると、出力端子102と接地端子100との間に(抵抗51に)発生する出力電圧Vrefは

Vref=R51・Id5=(R51/R50)・[UT・ln{(W2/L2)/(W1/L1)}+ΔVth]・・・(20)

によって算出される。

【0027】

ここで、上記のように、第1項の温度特性と第2項の温度特性とが相殺されるようにNMOSトランジスタ1〜2のアスペクト比が調整されることにより、出力電圧Vrefは温度に依存しにくくなる。また、同一種類のポリシリコンで形成される抵抗50〜51は温度特性を有するが、式(20)の(R51/R50)に示すように、これらの温度特性は相殺される。

【0028】

NMOSトランジスタ1〜2において、ソースとバックゲートとがショートするので、閾値電圧Vth1〜Vth2はNMOSトランジスタ1〜2のプロセスばらつきだけに依存して他の素子のプロセスばらつきに依存しない。よって、温度に依存しない基準電圧Vrefがより安定に発生する。

【0029】

なお、抵抗50〜51が使用されているが、線形領域で動作するMOSトランジスタが使用されても良い。

【0030】

また、抵抗50〜51が図示しない複数個の抵抗によって形成され、配線工程で各抵抗間の接続関係が変更することにより、抵抗50〜51の抵抗値が可変できるようにしても良い。すると、出力電圧Vrefは任意の電圧に調整されることできる。

【0031】

また、抵抗50〜51が図示しない複数個の抵抗及びヒューズによって形成され、ヒューズが切断されて各抵抗間の接続関係が変更することにより、抵抗50〜51の抵抗値が可変できるようにしても良い。すると、出力電圧Vrefは任意の電圧に調整されることできる。

【0032】

また、PMOSトランジスタ3〜5のアスペクト比は異なっても良い。

【0033】

また、図1では、PMOSトランジスタ3のドレインがPMOSトランジスタ3〜5のゲートに接続されている。しかし、図3に示すように、アンプ70が設けられ、非反転入力端子がPMOSトランジスタ3のドレインとNMOSトランジスタ2のドレインとの接続点に接続され、反転入力端子がPMOSトランジスタ4のドレインと抵抗50の一端との接続点に接続され、出力端子がPMOSトランジスタ3〜5のゲートに接続されても良い。すると、PMOSトランジスタ3〜4のドレイン電圧がより同一になるので、ドレイン電流Id1〜Id2がより同一になる。よって、式(17)より、ドレイン電流Id1がより正確に算出される。

【0034】

また、図4に示すように、起動回路80が設けられても良い。電流が全く流れない場合と電流が流れる場合との2つの安定点が基準電圧回路に存在していて、前者の場合から後者の場合に基準電圧回路が移行するように、起動回路80は動作する。具体的には、PMOSトランジスタ3及びNMOSトランジスタ2のドレイン電流が所定電流未満であり、PMOSトランジスタ3のゲート電圧が所定電圧以上であると、起動回路80は電源端子101からNMOSトランジスタ2のゲートに起動電流を流し込んで基準電圧回路を起動する。

【0035】

また、図5に示すように、電源端子101とPMOSトランジスタ3〜5のソースとの間にカスコード回路90が設けられても良い。すると、カスコード回路90を介して電圧端子101からPMOSトランジスタ3〜5のソースに電源電圧が供給されるので、電源電圧が変動しても、PMOSトランジスタ3〜5のソース電圧が変動しにくくなる。よって、電源電圧変動除去比が良くなる。

【0036】

また、図示しないが、PMOSトランジスタ3〜5のドレインとそれらの接続先との間にカスコード回路がそれぞれ設けられても良い。すると、電源電圧が変動しても、その接続先の電圧が変動しにくくなる。よって、電源電圧変動除去比が良くなる。

【0037】

また、図1では、NMOSトランジスタが弱反転動作し、PMOSトランジスタがカレントミラー回路を構成し、出力電圧Vrefが出力端子102と接地端子100との間に発生している。しかし、図示しないが、PMOSトランジスタが弱反転動作し、NMOSトランジスタがカレントミラー回路を構成し、出力電圧Vrefが電源端子101と出力端子102との間に発生しても良い。

【0038】

<第2実施形態>

まず、基準電圧回路の構成について説明する。図6は、基準電圧回路を示す図である。

【0039】

基準電圧回路は、PMOSトランジスタ8〜10、NMOSトランジスタ11〜12及び抵抗52〜53を備える。また、基準電圧回路は、電源端子101、接地端子100及び出力端子102を備える。

【0040】

NMOSトランジスタ11は、ゲート及びドレインをNMOSトランジスタ9のドレインに接続され、ソース及びバックゲートを接地端子100に接続される。NMOSトランジスタ12は、ゲートをNMOSトランジスタ11のゲートに接続され、ソース及びバックゲートを接地端子100に接続され、ドレインを抵抗52の一端に接続される。PMOSトランジスタ9は、ゲートをPMOSトランジスタ8のドレインと抵抗52の他端との接続点に接続され、ソース及びバックゲートを電源端子101に接続される。PMOSトランジスタ8は、ゲートをPMOSトランジスタ10のゲート及び抵抗52の一端に接続され、ソース及びバックゲートを電源端子101に接続される。PMOSトランジスタ8は、ソース及びバックゲートを電源端子101に接続され、ドレインを出力端子102に接続される。抵抗53は、出力端子102と接地端子100との間に設けられる。

【0041】

NMOSトランジスタ11〜12のアスペクト比は同一である。また、NMOSトランジスタ11〜12のゲートは互いに接続される。よって、NMOSトランジスタ11〜12に流れるドレイン電流も同一になる。NMOSトランジスタ11〜12は、電流供給回路として機能し、電流を入力される入力端子(NMOSトランジスタ11のドレイン)及び入力端子の電流に基づいた電流を出力する出力端子(NMOSトランジスタ12のドレイン)を有する。

【0042】

次に、基準電圧回路の動作について説明する。

【0043】

Vgs8はPMOSトランジスタ8のゲート・ソース間電圧、Vgs9はPMOSトランジスタ9のゲート・ソース間電圧、R52は抵抗52の抵抗値であるとすると、PMOSトランジスタ8のドレイン電流Id8は

Id8=(Vgs8−Vgs9)/R52・・・(34)

によって算出される。また、Id9はPMOSトランジスタ9のドレイン電流、W8はPMOSトランジスタ8のゲート幅、L8はPMOSトランジスタ8のゲート長、Vth8はPMOSトランジスタ8の閾値電圧、W9はPMOSトランジスタ9のゲート幅、L9はPMOSトランジスタ9のゲート長、Vth9はPMOSトランジスタ9の閾値電圧であるとすると、式(34)より、ゲート・ソース間電圧Vgs8〜Vgs9は

Vgs8=UT・ln[Id8/{Id0・(W8/L8)}]+Vth8・・・(35)

Vgs9=UT・ln[Id9/{Id0・(W9/L9)}]+Vth9・・・(36)

によって算出される。ドレイン電流Id8〜Id9は同一であり、ΔVthはPMOSトランジスタ8〜9の閾値電圧差(ΔVth=Vth8−Vth9)であるとすると、式(34)〜(36)より、ドレイン電流Id8は

Id8=(1/R52)・[UT・ln{(Id8/Id9)・(W9/L9)/(W8/L8)}+ΔVth]・・・(37)

Id8=(1/R52)・[UT・ln{(W9/L9)/(W8/L8)}+ΔVth]・・・(38)

によって算出される。

【0044】

ここで、第1実施形態のように、ドレイン電流Id8は温度に依存しにくくなる。

【0045】

すると、PMOSトランジスタ8〜9において、ゲートは互いに接続し、ソースは電源端子101にそれぞれ接続しているので、ドレイン電流Id8とドレイン電流Id10とは同一になる。よって、

Id10=Id8・・・(39)

が成立する。R53は抵抗53の抵抗値であるとすると、出力端子102と接地端子100との間に発生する出力電圧Vrefは

Vref=R53・Id10=(R53/R52)・[UT・ln{(W9/L9)/(W8/L8)}+ΔVth]・・・(40)

によって算出される。

【0046】

従って、第1実施形態のように、抵抗52〜53の温度特性は相殺される。

【図面の簡単な説明】

【0047】

【図1】本発明の基準電圧回路を示す回路図である。

【図2】NMOSトランジスタの閾値電圧の絶対値の温度特性を示す図である。

【図3】本発明の基準電圧回路の他の例を示す回路図である。

【図4】本発明の基準電圧回路の他の例を示す回路図である。

【図5】本発明の基準電圧回路の他の例を示す回路図である。

【図6】本発明の第二実施形態の基準電圧回路を示す回路図である。

【図7】従来の基準電圧回路を示す回路図である。

【符号の説明】

【0048】

1、2 NMOSトランジスタ

3〜5 PMOSトランジスタ

70 アンプ

80 起動回路

90 カスコード回路

101 電源端子

102 出力端子

【技術分野】

【0001】

本発明は、基準電圧を発生する基準電圧回路に関する。

【背景技術】

【0002】

従来の基準電圧回路について説明する。図7は、従来の基準電圧回路を示す回路図である。

【0003】

ここで、弱反転動作するMOSトランジスタにおいて、Wはゲート幅、Lはゲート長、Vthは閾値電圧、Vgsはゲート・ソース間電圧、qは電子の電荷量、kはボルツマン定数、Tは絶対温度、Id0及びnはプロセスによって定まる定数であるとすると、ドレイン電流Idは

Id=Id0・(W/L)・exp{(Vgs−Vth)・q/nkT}・・・(61)

によって算出される。nkT/qは熱電圧であるとしてUTとすると、

Id=Id0・(W/L)・exp{(Vgs−Vth)/UT}・・・(62)

が成立する。よって、ゲート・ソース間電圧Vgsは

Vgs=UT・ln[Id/{Id0・(W/L)}]+Vth・・・(63)

によって算出される。

【0004】

PMOSトランジスタ43〜45はカレントミラー接続しているので、PMOSトランジスタ43〜45のドレイン電流Id41〜Id42及びドレイン電流Id45は同一である。

【0005】

弱反転動作するNMOSトランジスタ41のゲート・ソース間電圧Vgs41から弱反転動作するNMOSトランジスタ42のゲート・ソース間電圧Vgs42を減算した電圧(Vgs41−Vgs42)が抵抗58に発生する。よって、この電圧(Vgs41−Vgs42)及び抵抗58の抵抗値R58に基づき、ドレイン電流Id42が算出され、ドレイン電流Id45も算出される。すると、

Id45=Id42=(Vgs41−Vgs42)/R58・・・(64)

が成立する。よって、R59は抵抗59の抵抗値であるとすると、抵抗59に発生する出力電圧Vrefは

Vref

=R59・Id45

=(R59/R58)・(Vgs41−Vgs42)・・・(65)

によって算出される。W41はNMOSトランジスタ41のゲート幅、L41はNMOSトランジスタ41のゲート長、Vth41はNMOSトランジスタ41の閾値電圧、W42はNMOSトランジスタ42のゲート幅、L42はNMOSトランジスタ42のゲート長、Vth42はNMOSトランジスタ42の閾値電圧、ΔVthはNMOSトランジスタ41〜42の閾値電圧差(ΔVth=Vth41−Vth42)であるとすると、式(63)より、出力電圧Vrefは

Vref

=(R59/R58)・[UT・ln{(W42/L42)/(W41/L41)}+ΔVth]・・・(66)

によって算出される。

【0006】

ここで、上記のように、第1項の温度特性と第2項の温度特性とが相殺されるようにNMOSトランジスタ41〜42のアスペクト比が調整されることにより、出力電圧Vrefは温度に依存しにくくなる(例えば、特許文献1参照)。

【特許文献1】特許第3024645号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、NMOSトランジスタ42ではソースとバックゲートとの間に抵抗58が存在する。よって、抵抗58のプロセスばらつきにより、閾値電圧Vth42もばらついてしまう。つまり、閾値電圧Vth42は、NMOSトランジスタ42のプロセスばらつきだけでなくて抵抗58のプロセスばらつきにも依存してしまう。よって、温度に依存しない基準電圧は、NMOSトランジスタ41〜42の閾値電圧差(ΔVth=Vth41−Vth42)に基づくので、不安定になってしまうことがある。

【0008】

本発明は、上記課題に鑑みてなされ、温度に依存しない基準電圧をより安定に発生できる基準電圧回路を提供する。

【課題を解決するための手段】

【0009】

本発明は、上記課題を解決するため、基準電圧を発生する基準電圧回路において、第一電源端子と、第二電源端子と、電流を入力される入力端子と、前記入力端子の電流に基づいた電流を出力する第一〜第二出力端子と、を有する電流供給回路と、第一抵抗と、ゲートを前記第一出力端子に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記第一出力端子に前記第一抵抗を介して接続され、弱反転動作する第一導電型の第一MOSトランジスタと、ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第一導電型の第二MOSトランジスタと、前記第二出力端子と前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、を備えることを特徴とする基準電圧回路を提供する。

【0010】

また、本発明は、上記課題を解決するため、基準電圧を発生する基準電圧回路において、第一電源端子と、第二電源端子と、電流を入力される入力端子及び前記入力端子の電流に基づいた電流を出力する出力端子を有する電流供給回路と、第一抵抗と、ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記出力端子に前記第一抵抗を介して接続され、弱反転動作する第二導電型の第一MOSトランジスタと、ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第二導電型の第二MOSトランジスタと、ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続される第二導電型の第三MOSトランジスタと、前記第三MOSトランジスタのドレインと前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、を備えることを特徴とする基準電圧回路を提供する。

【発明の効果】

【0011】

本発明では、第一〜第二MOSトランジスタにおいて、ソースとバックゲートとがショートするので、閾値電圧は第一〜第二MOSトランジスタのプロセスばらつきだけに依存して他の素子のプロセスばらつきに依存しない。よって、温度に依存しない基準電圧がより安定に発生する。

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施形態を、図面を参照して説明する。

【0013】

<第1実施形態>

まず、基準電圧回路の構成について説明する。図1は、基準電圧回路を示す図である。

【0014】

基準電圧回路は、PMOSトランジスタ3〜5、NMOSトランジスタ1〜2及び抵抗50〜51を備える。また、基準電圧回路は、電源端子101、接地端子100及び出力端子102を備える。

【0015】

PMOSトランジスタ3は、ゲート及びドレインをNMOSトランジスタ2のドレインに接続され、ソース及びバックゲートを電源端子101に接続される。PMOSトランジスタ4は、ゲートをPMOSトランジスタ3のゲートに接続され、ソース及びバックゲートを電源端子101に接続され、ドレインを抵抗50の一端及びNMOSトランジスタ1のゲートに接続される。PMOSトランジスタ5は、ゲートをPMOSトランジスタ3のゲートに接続され、ソース及びバックゲートを電源端子101に接続され、ドレインを出力端子102に接続される。NMOSトランジスタ2は、ゲートを抵抗50の他端及びNMOSトランジスタ1のドレインに接続され、ソース及びバックゲートを接地端子100に接続される。NMOSトランジスタ1は、ソース及びバックゲートを接地端子100に接続される。抵抗51は、出力端子102と接地端子100との間に設けられる。

【0016】

PMOSトランジスタ3〜5のアスペクト比は同一である。また、PMOSトランジスタ3〜5のゲートは互いに接続される。よって、PMOSトランジスタ3〜5に流れるドレイン電流も同一になる。PMOSトランジスタ3〜5は、電流供給回路として機能し、電流を入力される入力端子(PMOSトランジスタ3のドレイン)と入力端子の電流に基づいた電流を出力する出力端子(PMOSトランジスタ4のドレイン)及び出力端子(PMOSトランジスタ5のドレイン)とを有する。

【0017】

また、NMOSトランジスタ1〜2のゲート幅はドレイン電流に対して十分に大きく設計されるので、NMOSトランジスタ1〜2は弱反転動作する。

【0018】

また、NMOSトランジスタ1の閾値電圧の絶対値はNMOSトランジスタ2の閾値電圧の絶対値よりも高い。

【0019】

抵抗50〜51は同一種類のポリシリコンで形成され、抵抗50〜51の温度係数が最小になるように、抵抗50〜51へのイオン打ち込み量は設定される。

【0020】

NMOSトランジスタ1〜2は同一濃度の基板上に形成され、NMOSトランジスタ1またはNMOSトランジスタ2のみがチャネルドープをされる。すると、NMOSトランジスタ1〜2の閾値電圧差のプロセスばらつきはNMOSトランジスタ1またはNMOSトランジスタ2のチャネルドープのプロセスばらつきにのみ依存するので、デプレッション型NMOSトランジスタと比較してプロセスばらつきの影響が小さくなる。

【0021】

なお、NMOSトランジスタ1〜2は同一濃度の基板上に形成され、NMOSトランジスタ1〜2は1回目のチャネルドープをされ、その後、NMOSトランジスタ1またはNMOSトランジスタ2のみが2回目のチャネルドープをされても良い。

【0022】

次に、基準電圧回路の動作について説明する。

【0023】

ここで、弱反転動作するMOSトランジスタにおいて、Wはゲート幅、Lはゲート長、Vthは閾値電圧、Vgsはゲート・ソース間電圧、qは電子の電荷量、kはボルツマン定数、Tは絶対温度、Id0及びnはプロセスによって定まる定数であるとすると、ドレイン電流Idは

Id=Id0・(W/L)・exp{(Vgs−Vth)・q/nkT}・・・(11)

によって算出される。nkT/qは熱電圧であるとしてUTとすると、

Id=Id0・(W/L)・exp{(Vgs−Vth)/UT}・・・(12)

が成立する。よって、ゲート・ソース間電圧Vgsは

Vgs=UT・ln[Id/{Id0・(W/L)}]+Vth・・・(13)

によって算出される。

【0024】

Vgs1はNMOSトランジスタ1のゲート・ソース間電圧、Vgs2はNMOSトランジスタ2のゲート・ソース間電圧、R50は抵抗50の抵抗値であるとすると、NMOSトランジスタ1のドレイン電流Id1は

Id1=(Vgs1−Vgs2)/R50・・・(14)

によって算出される。また、Id2はNMOSトランジスタ2のドレイン電流、W1はNMOSトランジスタ1のゲート幅、L1はNMOSトランジスタ1のゲート長、Vth1はNMOSトランジスタ1の閾値電圧、W2はNMOSトランジスタ2のゲート幅、L2はNMOSトランジスタ2のゲート長、Vth2はNMOSトランジスタ2の閾値電圧であるとすると、式(14)より、ゲート・ソース間電圧Vgs1〜Vgs2は

Vgs1=UT・ln[Id1/{Id0・(W1/L1)}]+Vth1・・・(15)

Vgs2=UT・ln[Id2/{Id0・(W2/L2)}]+Vth2・・・(16)

によって算出される。ドレイン電流Id1〜Id2は同一であり、ΔVthはNMOSトランジスタ1〜2の閾値電圧差(ΔVth=Vth1−Vth2)であるとすると、式(14)〜(16)より、ドレイン電流Id1は

Id1=(1/R50)・[UT・ln{(Id1/Id2)・(W2/L2)/(W1/L1)}+ΔVth]・・・(17)

Id1=(1/R50)・[UT・ln{(W2/L2)/(W1/L1)}+ΔVth]・・・(18)

によって算出される。

【0025】

ここで、熱電圧UTは、温度に正比例するので、正の温度係数を有する。また、NMOSトランジスタ1〜2の閾値電圧Vth1〜Vth2は、図2に示すように、負の温度係数をそれぞれ有する。閾値電圧の絶対値を高く設定されたNMOSトランジスタ1の温度係数の傾きは、NMOSトランジスタ2の温度係数の傾きよりも急になる。よって、閾値電圧差(ΔVth=Vth1−Vth2)も負の温度係数を有する。よって、式(18)において、第1項は正の温度係数を有し、第2項は負の温度係数を有するので、第1項の温度特性と第2項の温度特性とが相殺されるようにNMOSトランジスタ1〜2のアスペクト比が調整されることにより、ドレイン電流Id1は温度に依存しにくくなる。

【0026】

すると、PMOSトランジスタ4〜5において、ゲートは互いに接続し、ソースは電源端子101にそれぞれ接続しているので、ドレイン電流Id1とドレイン電流Id5とは同一になる。よって、

Id5=Id1・・・(19)

が成立する。R51は抵抗51の抵抗値であるとすると、出力端子102と接地端子100との間に(抵抗51に)発生する出力電圧Vrefは

Vref=R51・Id5=(R51/R50)・[UT・ln{(W2/L2)/(W1/L1)}+ΔVth]・・・(20)

によって算出される。

【0027】

ここで、上記のように、第1項の温度特性と第2項の温度特性とが相殺されるようにNMOSトランジスタ1〜2のアスペクト比が調整されることにより、出力電圧Vrefは温度に依存しにくくなる。また、同一種類のポリシリコンで形成される抵抗50〜51は温度特性を有するが、式(20)の(R51/R50)に示すように、これらの温度特性は相殺される。

【0028】

NMOSトランジスタ1〜2において、ソースとバックゲートとがショートするので、閾値電圧Vth1〜Vth2はNMOSトランジスタ1〜2のプロセスばらつきだけに依存して他の素子のプロセスばらつきに依存しない。よって、温度に依存しない基準電圧Vrefがより安定に発生する。

【0029】

なお、抵抗50〜51が使用されているが、線形領域で動作するMOSトランジスタが使用されても良い。

【0030】

また、抵抗50〜51が図示しない複数個の抵抗によって形成され、配線工程で各抵抗間の接続関係が変更することにより、抵抗50〜51の抵抗値が可変できるようにしても良い。すると、出力電圧Vrefは任意の電圧に調整されることできる。

【0031】

また、抵抗50〜51が図示しない複数個の抵抗及びヒューズによって形成され、ヒューズが切断されて各抵抗間の接続関係が変更することにより、抵抗50〜51の抵抗値が可変できるようにしても良い。すると、出力電圧Vrefは任意の電圧に調整されることできる。

【0032】

また、PMOSトランジスタ3〜5のアスペクト比は異なっても良い。

【0033】

また、図1では、PMOSトランジスタ3のドレインがPMOSトランジスタ3〜5のゲートに接続されている。しかし、図3に示すように、アンプ70が設けられ、非反転入力端子がPMOSトランジスタ3のドレインとNMOSトランジスタ2のドレインとの接続点に接続され、反転入力端子がPMOSトランジスタ4のドレインと抵抗50の一端との接続点に接続され、出力端子がPMOSトランジスタ3〜5のゲートに接続されても良い。すると、PMOSトランジスタ3〜4のドレイン電圧がより同一になるので、ドレイン電流Id1〜Id2がより同一になる。よって、式(17)より、ドレイン電流Id1がより正確に算出される。

【0034】

また、図4に示すように、起動回路80が設けられても良い。電流が全く流れない場合と電流が流れる場合との2つの安定点が基準電圧回路に存在していて、前者の場合から後者の場合に基準電圧回路が移行するように、起動回路80は動作する。具体的には、PMOSトランジスタ3及びNMOSトランジスタ2のドレイン電流が所定電流未満であり、PMOSトランジスタ3のゲート電圧が所定電圧以上であると、起動回路80は電源端子101からNMOSトランジスタ2のゲートに起動電流を流し込んで基準電圧回路を起動する。

【0035】

また、図5に示すように、電源端子101とPMOSトランジスタ3〜5のソースとの間にカスコード回路90が設けられても良い。すると、カスコード回路90を介して電圧端子101からPMOSトランジスタ3〜5のソースに電源電圧が供給されるので、電源電圧が変動しても、PMOSトランジスタ3〜5のソース電圧が変動しにくくなる。よって、電源電圧変動除去比が良くなる。

【0036】

また、図示しないが、PMOSトランジスタ3〜5のドレインとそれらの接続先との間にカスコード回路がそれぞれ設けられても良い。すると、電源電圧が変動しても、その接続先の電圧が変動しにくくなる。よって、電源電圧変動除去比が良くなる。

【0037】

また、図1では、NMOSトランジスタが弱反転動作し、PMOSトランジスタがカレントミラー回路を構成し、出力電圧Vrefが出力端子102と接地端子100との間に発生している。しかし、図示しないが、PMOSトランジスタが弱反転動作し、NMOSトランジスタがカレントミラー回路を構成し、出力電圧Vrefが電源端子101と出力端子102との間に発生しても良い。

【0038】

<第2実施形態>

まず、基準電圧回路の構成について説明する。図6は、基準電圧回路を示す図である。

【0039】

基準電圧回路は、PMOSトランジスタ8〜10、NMOSトランジスタ11〜12及び抵抗52〜53を備える。また、基準電圧回路は、電源端子101、接地端子100及び出力端子102を備える。

【0040】

NMOSトランジスタ11は、ゲート及びドレインをNMOSトランジスタ9のドレインに接続され、ソース及びバックゲートを接地端子100に接続される。NMOSトランジスタ12は、ゲートをNMOSトランジスタ11のゲートに接続され、ソース及びバックゲートを接地端子100に接続され、ドレインを抵抗52の一端に接続される。PMOSトランジスタ9は、ゲートをPMOSトランジスタ8のドレインと抵抗52の他端との接続点に接続され、ソース及びバックゲートを電源端子101に接続される。PMOSトランジスタ8は、ゲートをPMOSトランジスタ10のゲート及び抵抗52の一端に接続され、ソース及びバックゲートを電源端子101に接続される。PMOSトランジスタ8は、ソース及びバックゲートを電源端子101に接続され、ドレインを出力端子102に接続される。抵抗53は、出力端子102と接地端子100との間に設けられる。

【0041】

NMOSトランジスタ11〜12のアスペクト比は同一である。また、NMOSトランジスタ11〜12のゲートは互いに接続される。よって、NMOSトランジスタ11〜12に流れるドレイン電流も同一になる。NMOSトランジスタ11〜12は、電流供給回路として機能し、電流を入力される入力端子(NMOSトランジスタ11のドレイン)及び入力端子の電流に基づいた電流を出力する出力端子(NMOSトランジスタ12のドレイン)を有する。

【0042】

次に、基準電圧回路の動作について説明する。

【0043】

Vgs8はPMOSトランジスタ8のゲート・ソース間電圧、Vgs9はPMOSトランジスタ9のゲート・ソース間電圧、R52は抵抗52の抵抗値であるとすると、PMOSトランジスタ8のドレイン電流Id8は

Id8=(Vgs8−Vgs9)/R52・・・(34)

によって算出される。また、Id9はPMOSトランジスタ9のドレイン電流、W8はPMOSトランジスタ8のゲート幅、L8はPMOSトランジスタ8のゲート長、Vth8はPMOSトランジスタ8の閾値電圧、W9はPMOSトランジスタ9のゲート幅、L9はPMOSトランジスタ9のゲート長、Vth9はPMOSトランジスタ9の閾値電圧であるとすると、式(34)より、ゲート・ソース間電圧Vgs8〜Vgs9は

Vgs8=UT・ln[Id8/{Id0・(W8/L8)}]+Vth8・・・(35)

Vgs9=UT・ln[Id9/{Id0・(W9/L9)}]+Vth9・・・(36)

によって算出される。ドレイン電流Id8〜Id9は同一であり、ΔVthはPMOSトランジスタ8〜9の閾値電圧差(ΔVth=Vth8−Vth9)であるとすると、式(34)〜(36)より、ドレイン電流Id8は

Id8=(1/R52)・[UT・ln{(Id8/Id9)・(W9/L9)/(W8/L8)}+ΔVth]・・・(37)

Id8=(1/R52)・[UT・ln{(W9/L9)/(W8/L8)}+ΔVth]・・・(38)

によって算出される。

【0044】

ここで、第1実施形態のように、ドレイン電流Id8は温度に依存しにくくなる。

【0045】

すると、PMOSトランジスタ8〜9において、ゲートは互いに接続し、ソースは電源端子101にそれぞれ接続しているので、ドレイン電流Id8とドレイン電流Id10とは同一になる。よって、

Id10=Id8・・・(39)

が成立する。R53は抵抗53の抵抗値であるとすると、出力端子102と接地端子100との間に発生する出力電圧Vrefは

Vref=R53・Id10=(R53/R52)・[UT・ln{(W9/L9)/(W8/L8)}+ΔVth]・・・(40)

によって算出される。

【0046】

従って、第1実施形態のように、抵抗52〜53の温度特性は相殺される。

【図面の簡単な説明】

【0047】

【図1】本発明の基準電圧回路を示す回路図である。

【図2】NMOSトランジスタの閾値電圧の絶対値の温度特性を示す図である。

【図3】本発明の基準電圧回路の他の例を示す回路図である。

【図4】本発明の基準電圧回路の他の例を示す回路図である。

【図5】本発明の基準電圧回路の他の例を示す回路図である。

【図6】本発明の第二実施形態の基準電圧回路を示す回路図である。

【図7】従来の基準電圧回路を示す回路図である。

【符号の説明】

【0048】

1、2 NMOSトランジスタ

3〜5 PMOSトランジスタ

70 アンプ

80 起動回路

90 カスコード回路

101 電源端子

102 出力端子

【特許請求の範囲】

【請求項1】

基準電圧を発生する基準電圧回路において、

第一電源端子と、

第二電源端子と、

電流を入力される入力端子と、前記入力端子の電流に基づいた電流を出力する第一〜第二出力端子と、を有する電流供給回路と、

第一抵抗と、

ゲートを前記第一出力端子に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記第一出力端子に前記第一抵抗を介して接続され、弱反転動作する第一導電型の第一MOSトランジスタと、

ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第一導電型の第二MOSトランジスタと、

前記第二出力端子と前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、

を備えることを特徴とする基準電圧回路。

【請求項2】

前記電流供給回路は、

ゲート及びドレインを前記入力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続される第二導電型の第三MOSトランジスタと、

ゲートを前記入力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第一出力端子に接続される第二導電型の第四MOSトランジスタと、

ゲートを前記入力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第二出力端子に接続される第二導電型の第五MOSトランジスタと、

を有することを特徴とする請求項1記載の基準電圧回路。

【請求項3】

前記電流供給回路は、

前記第三〜第五MOSトランジスタのドレインとそれらの接続先との間にそれぞれ設けられる複数個のカスコード回路、

をさらに有することを特徴とする請求項2記載の基準電圧回路。

【請求項4】

前記電流供給回路は、

ゲートをアンプの出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記入力端子に接続される第二導電型の第三MOSトランジスタと、

ゲートを前記アンプの出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第一出力端子に接続される第二導電型の第四MOSトランジスタと、

ゲートを前記アンプの出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第二出力端子に接続される第二導電型の第五MOSトランジスタと、

非反転入力端子を前記入力端子に接続され、反転入力端子を前記第一出力端子に接続される前記アンプと、

を有することを特徴とする請求項1記載の基準電圧回路。

【請求項5】

前記第一〜第二MOSトランジスタは同一濃度の基板上に形成され、前記第一MOSトランジスタまたは前記第二MOSトランジスタのみがチャネルドープをされることを特徴とする請求項1記載の基準電圧回路。

【請求項6】

前記第一〜第二MOSトランジスタは同一濃度の基板上に形成され、前記第一〜第二MOSトランジスタは1回目のチャネルドープをされ、その後、前記第一MOSトランジスタまたは前記第二MOSトランジスタのみが2回目のチャネルドープをされることを特徴とする請求項1記載の基準電圧回路。

【請求項7】

前記第一〜第二抵抗は、同一種類の材料で形成されることを特徴とする請求項1記載の基準電圧回路。

【請求項8】

前記材料は、ポリシリコンであることを特徴とする請求項7記載の基準電圧回路。

【請求項9】

前記第一〜第二抵抗は、線形領域で動作するMOSトランジスタであることを特徴とする請求項1記載の基準電圧回路。

【請求項10】

前記第一〜第二抵抗は、複数個の抵抗によって形成され、配線工程で各前記抵抗間の接続関係が変更することにより、抵抗値を可変することを特徴とする請求項1記載の基準電圧回路。

【請求項11】

前記第一〜第二抵抗は、複数個の抵抗及びヒューズによって形成され、前記ヒューズが切断されて各前記抵抗間の接続関係が変更することにより、抵抗値を可変することを特徴とする請求項1記載の基準電圧回路。

【請求項12】

前記第二MOSトランジスタのドレイン電流が所定電流未満であると、前記第二MOSトランジスタのゲートに起動電流を流し込む起動回路、

をさらに備えることを特徴とする請求項1記載の基準電圧回路。

【請求項13】

前記第一電源端子または前記第二電源端子と、前記電流供給回路、前記第一抵抗、前記第一〜第二MOSトランジスタ及び前記第二抵抗を有する回路と、の間に設けられるカスコード回路、

をさらに備えることを特徴とする請求項1記載の基準電圧回路。

【請求項14】

基準電圧を発生する基準電圧回路において、

第一電源端子と、

第二電源端子と、

電流を入力される入力端子及び前記入力端子の電流に基づいた電流を出力する出力端子を有する電流供給回路と、

第一抵抗と、

ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記出力端子に前記第一抵抗を介して接続され、弱反転動作する第二導電型の第一MOSトランジスタと、

ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第二導電型の第二MOSトランジスタと、

ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続される第二導電型の第三MOSトランジスタと、

前記第三MOSトランジスタのドレインと前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、

を備えることを特徴とする基準電圧回路。

【請求項1】

基準電圧を発生する基準電圧回路において、

第一電源端子と、

第二電源端子と、

電流を入力される入力端子と、前記入力端子の電流に基づいた電流を出力する第一〜第二出力端子と、を有する電流供給回路と、

第一抵抗と、

ゲートを前記第一出力端子に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記第一出力端子に前記第一抵抗を介して接続され、弱反転動作する第一導電型の第一MOSトランジスタと、

ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第一電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第一導電型の第二MOSトランジスタと、

前記第二出力端子と前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、

を備えることを特徴とする基準電圧回路。

【請求項2】

前記電流供給回路は、

ゲート及びドレインを前記入力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続される第二導電型の第三MOSトランジスタと、

ゲートを前記入力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第一出力端子に接続される第二導電型の第四MOSトランジスタと、

ゲートを前記入力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第二出力端子に接続される第二導電型の第五MOSトランジスタと、

を有することを特徴とする請求項1記載の基準電圧回路。

【請求項3】

前記電流供給回路は、

前記第三〜第五MOSトランジスタのドレインとそれらの接続先との間にそれぞれ設けられる複数個のカスコード回路、

をさらに有することを特徴とする請求項2記載の基準電圧回路。

【請求項4】

前記電流供給回路は、

ゲートをアンプの出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記入力端子に接続される第二導電型の第三MOSトランジスタと、

ゲートを前記アンプの出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第一出力端子に接続される第二導電型の第四MOSトランジスタと、

ゲートを前記アンプの出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記第二出力端子に接続される第二導電型の第五MOSトランジスタと、

非反転入力端子を前記入力端子に接続され、反転入力端子を前記第一出力端子に接続される前記アンプと、

を有することを特徴とする請求項1記載の基準電圧回路。

【請求項5】

前記第一〜第二MOSトランジスタは同一濃度の基板上に形成され、前記第一MOSトランジスタまたは前記第二MOSトランジスタのみがチャネルドープをされることを特徴とする請求項1記載の基準電圧回路。

【請求項6】

前記第一〜第二MOSトランジスタは同一濃度の基板上に形成され、前記第一〜第二MOSトランジスタは1回目のチャネルドープをされ、その後、前記第一MOSトランジスタまたは前記第二MOSトランジスタのみが2回目のチャネルドープをされることを特徴とする請求項1記載の基準電圧回路。

【請求項7】

前記第一〜第二抵抗は、同一種類の材料で形成されることを特徴とする請求項1記載の基準電圧回路。

【請求項8】

前記材料は、ポリシリコンであることを特徴とする請求項7記載の基準電圧回路。

【請求項9】

前記第一〜第二抵抗は、線形領域で動作するMOSトランジスタであることを特徴とする請求項1記載の基準電圧回路。

【請求項10】

前記第一〜第二抵抗は、複数個の抵抗によって形成され、配線工程で各前記抵抗間の接続関係が変更することにより、抵抗値を可変することを特徴とする請求項1記載の基準電圧回路。

【請求項11】

前記第一〜第二抵抗は、複数個の抵抗及びヒューズによって形成され、前記ヒューズが切断されて各前記抵抗間の接続関係が変更することにより、抵抗値を可変することを特徴とする請求項1記載の基準電圧回路。

【請求項12】

前記第二MOSトランジスタのドレイン電流が所定電流未満であると、前記第二MOSトランジスタのゲートに起動電流を流し込む起動回路、

をさらに備えることを特徴とする請求項1記載の基準電圧回路。

【請求項13】

前記第一電源端子または前記第二電源端子と、前記電流供給回路、前記第一抵抗、前記第一〜第二MOSトランジスタ及び前記第二抵抗を有する回路と、の間に設けられるカスコード回路、

をさらに備えることを特徴とする請求項1記載の基準電圧回路。

【請求項14】

基準電圧を発生する基準電圧回路において、

第一電源端子と、

第二電源端子と、

電流を入力される入力端子及び前記入力端子の電流に基づいた電流を出力する出力端子を有する電流供給回路と、

第一抵抗と、

ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記出力端子に前記第一抵抗を介して接続され、弱反転動作する第二導電型の第一MOSトランジスタと、

ゲートを前記第一抵抗と前記第一MOSトランジスタとの接続点に接続され、ソース及びバックゲートを前記第二電源端子に接続され、ドレインを前記入力端子に接続され、前記第一MOSトランジスタの閾値電圧の絶対値よりも低い閾値電圧の絶対値を持ち、弱反転動作する第二導電型の第二MOSトランジスタと、

ゲートを前記出力端子に接続され、ソース及びバックゲートを前記第二電源端子に接続される第二導電型の第三MOSトランジスタと、

前記第三MOSトランジスタのドレインと前記第一電源端子との間に設けられ、前記基準電圧を発生する第二抵抗と、

を備えることを特徴とする基準電圧回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−152510(P2010−152510A)

【公開日】平成22年7月8日(2010.7.8)

【国際特許分類】

【出願番号】特願2008−327935(P2008−327935)

【出願日】平成20年12月24日(2008.12.24)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

【公開日】平成22年7月8日(2010.7.8)

【国際特許分類】

【出願日】平成20年12月24日(2008.12.24)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

[ Back to top ]