基準電圧回路

【課題】プロセス変動によるバラつき要因が少ない基準電圧回路の提供。

【解決手段】第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

【解決手段】第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基準電圧回路に関する。

【背景技術】

【0002】

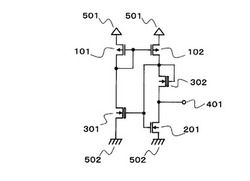

図6は、従来の基準電圧回路を示す回路図である。

従来の基準電圧回路は、PMOSトランジスタ101〜103、NMOSトランジスタ201〜204、301、出力端子401、電源端子501、接地端子502及び抵抗601を備える。NMOSトランジスタ301のしきい値電圧(以後Vtnlとする)は、NMOSトランジスタ201〜204のしきい値電圧(以後Vtnhとする)より低い。PMOSトランジスタ102と103は、PMOSトランジスタ101とカレントミラー回路を構成し、PMOSトランジスタ101のドレイン端子電流の所望比のドレイン端子電流を流す。NMOSトランジスタ204は、NMOSトランジスタ203とカレントミラー回路を構成し、NMOSトランジスタ203のドレイン端子電流の所望比のドレイン端子電流を流す。

【0003】

PMOSトランジスタ101〜103のソース端子は電源端子に接続される。PMOSトランジスタ102及び103のゲート端子は、PMOSトランジスタ101のゲート端子及びドレイン端子、NMOSトランジスタ201のドレイン端子に接続される。NMOSトランジスタ201及び202のゲート端子は、NMOSトランジスタ201のドレイン端子及びPMOSトランジスタ102のドレイン端子に接続される。NMOSトランジスタ202のソース端子は接地端子に接続される。抵抗601の一端はNMOSトランジスタ201のソース端子に接続され、もう一端は接地端子に接続される。NMOSトランジスタ203、204及び301のゲート端子は、NMOSトランジスタ203及びPMOSトランジスタ103のドレイン端子に接続される。NMOSトランジスタ203及び204のソース端子は接地端子に接続される。NMOSトランジスタ301のドレイン端子は電源端子に接続される。出力端子401は、NMOSトランジスタ204のドレイン端子及びNMOSトランジスタ301のソース端子に接続される。

【0004】

NMOSトランジスタ201〜204、301のK値はそれぞれ、K201、K202、K203、K204及びK301、抵抗601の抵抗値はR601である。

【0005】

PMOSトランジスタ101と102、NMOSトランジスタ201と202、及び抵抗601は定電流回路を構成する。例えば、各トランジスタが飽和領域で動作する場合、PMOSトランジスタ101と102のK値が等しければ、PMOSトランジスタ101と102に流れる電流は等しく、この電流値は0Aまたは、ある定電流値(以後IKとする)を取る。電流が0Aにならないように起動回路を設けることで、PMOSトランジスタ101と102、NMOSトランジスタ201と202、及び抵抗601は定電流回路として動作する。定電流IKは次式で表される。

【0006】

【数1】

【0007】

ただし、K201>K202である。

【0008】

PMOSトランジスタ103には定電流IKがミラーされ、NMOSトランジスタ204にはPMOSトランジスタ103のドレイン端子電流がミラーされる。例えば、図6のトランジスタが全て飽和領域で動作する場合、PMOSトランジスタ101と103のK値が等しく、NMOSトランジスタ203と204のK値が等しい場合、NMOSトランジスタ204と301には、定電流IKが流れる。NMOSトランジスタ204と301が定電流IKを流すのに必要なゲートソース間電圧をそれぞれVGS204K、VGS301Kとした時、出力端子401の電圧(以後VrefKとする)は(1)式を用いると次式で表される。

【0009】

【数2】

【0010】

ただし、K201>K202である。

【0011】

上述したように、図6の基準電圧回路は、Vtnl、Vtnh、K201、K202、K204、K301、R601で決まる基準電圧VrefKを出力する回路である。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2007−148530号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかし、図6に示す従来の基準電圧回路では、(2)式からトランジスタのK値及びしきい値に加え抵抗値が基準電圧値を決定するため、プロセス変動に対する影響や温度特性の影響が大きくなるという課題があった。また、基準電圧値の温度特性を小さくするように補正する場合に、プロセス変動によるバラつき要因が増えてしまうという課題もあった。さらに、補正をするためには、温度センサや補正用のロジック回路を内蔵する必要になるため、回路規模が増大してしまうという課題があった。

【0014】

本発明は、上記課題に鑑みてなされ、回路規模を増大させずに、プロセス変動によるバラつき要因を減らし、基準電圧値及び、基準電圧値の温度特性を所望の範囲内に容易に補正することができる基準電圧回路を提供する。

【課題を解決するための手段】

【0015】

本発明の基準電圧回路は、上記課題を解決するため、第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

【発明の効果】

【0016】

本発明の基準電圧回路を用いれば、回路規模を増大させずに、抵抗のプロセス変動による基準電圧値のバラつきや、基準電圧値や温度特性の補正値のバラつきを小さくすることが可能である。

【図面の簡単な説明】

【0017】

【図1】第1の実施形態の基準電圧回路を示す回路図である。

【図2】しきい値及びK値の異なる2つのNMOSトランジスタのゲートソース間電圧対ドレイン端子電流の曲線を示すグラフである。

【図3】第2の実施形態の基準電圧回路を示す回路図である。

【図4】第3の実施形態の基準電圧回路を示す回路図である。

【図5】第4の実施形態の基準電圧回路を示す回路図である。

【図6】従来の基準電圧回路を示す回路図である。

【発明を実施するための形態】

【0018】

以下に、本実施形態について、図面を参照して説明する。

【実施例1】

【0019】

図1は、第1の実施形態の基準電圧回路を示す回路図である。

第1の実施形態の基準電圧回路は、PMOSトランジスタ101、102と、NMOSトランジスタ201、301、302と、出力端子401と、電源端子501と、接地端子502を備える。NMOSトランジスタ301、302のしきい値電圧(以後Vtnlとする)は、NMOSトランジスタ201のしきい値電圧(以後Vtnhとする)より低い。NMOSトランジスタ201、301、302のK値はそれぞれ、K201、K301、K302である。PMOSトランジスタ101とPMOSトランジスタ102は、カレントミラー回路を構成する。

【0020】

次に、第1の実施形態の基準電圧回路の接続について説明する。

PMOSトランジスタ101、102のソース端子は、電源端子501に接続される。PMOSトランジスタ102のゲート端子は、PMOSトランジスタ101のゲート端子及びドレイン端子とNMOSトランジスタ301のドレイン端子に接続される。NMOSトランジスタ201、301のゲート端子は、NMOSトランジスタ302のドレイン端子及びゲート端子とPMOSトランジスタ102のドレイン端子に接続され、ソース端子は接地端子502に接続される。出力端子401は、NMOSトランジスタ201のドレイン端子とNMOSトランジスタ302のソース端子に接続される。

【0021】

次に、第1の実施形態の基準電圧回路の動作について説明する。

PMOSトランジスタ101、102のドレイン端子電流をそれぞれI101、I102とする。出力端子401の電圧をVrefとする。PMOSトランジスタ101、102はカレントミラー回路を構成しているため、それぞれのK値が等しければ電流I101と電流I102は等しい電流が流れる。図2に、NMOSトランジスタ201とNMOSトランジスタ301が飽和領域で動作する場合の、ゲートソース間電圧(以後VGSとする)対ドレイン端子電流(以後IDとする)特性を示す。各々の曲線の立ち上がり位置と傾きは、それぞれしきい値電圧とK値によって決まる。電流I101と電流I102が等しく、NMOSトランジスタ201とNMOSトランジスタ301のゲート端子は接続されているため、この2つのトランジスタが飽和領域で動作すると、電圧VGSはA点となる。起動回路を設けると、電流I101(=I102)はA点の電流値(以後IAとする)となり、この値はVtnl、Vtnh、K201、K301によって次式のように表される。

【0022】

【数3】

【0023】

ただし、K201>K301である。

【0024】

NMOSトランジスタ201、302が電流IAを流すのに必要な電圧VGSをそれぞれVGS201A、VGS302A、接地端子電圧をVSSとすると、出力端子401の基準電圧VrefはVref=VSS+VGS201A−VGS302Aとなる。電圧VGS201A、電圧VGS302Aの値は、IA、Vtnl、Vtnh、K201、K302の値で決まる。(3)式より電流IAはVtnl、Vtnh、K201、K301の値で決まるため、出力端子401の基準電圧Vrefの値は、Vtnh、Vtnl、K201、K301、K302の値のみで決まる。

【0025】

NMOSトランジスタ201とNMOSトランジスタ302が飽和領域で動作する場合は、基準電圧Vrefは次式で表される。

【0026】

【数4】

【0027】

ここで、全てのトランジスタが飽和領域で動作すると、(4)式の電流IAに(3)式を代入することで基準電圧Vrefは次式で表される。

【0028】

【数5】

【0029】

ただし、K201>K301である。

(5)式から、基準電圧Vrefの値はVtnh、Vtnl、K201、K301、K302で決定する電圧であることがわかる。こうして、抵抗のプロセス変動によるばらつきのない基準電圧を得ることができる。また、温度特性を補正するには、K201、K301、K302の値のみを調整することで容易に補正することができる。

【0030】

ここで、NMOSトランジスタ201、301、302が飽和領域で動作した場合を例に取ったが、いずれかまたは全てが弱反転領域で動作したとしても、両トランジスタのVGS対IDカーブが交わるようにK201、K301を設定すれば、前述したVtnl、Vtnh、K201、及びK301の値で決まる電流IAを作ることが出来る。また、基準電圧Vrefも、Vtnl、Vtnh、K201、K301、K302の値で決定することができる。そのため、各トランジスタのK値のみを調整することで、温度特性の補正が可能である。

【0031】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0032】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K201、K301、K302の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【実施例2】

【0033】

図3は、第2の実施形態の基準電圧回路を示す回路図である。

第2の実施形態の基準電圧回路は、PMOSトランジスタ101〜106と、NMOSトランジスタ201〜204、301〜303と、出力端子401と、電源端子501と、接地端子502と、抵抗601〜602とを備える。NMOSトランジスタ301〜302のしきい値電圧(以後Vtnlとする)は、NMOSトランジスタ201〜202のしきい値電圧(以後Vtnhとする)より低い。NMOSトランジスタ201、202、301、302のK値はそれぞれ、K201、K202、K301、K302とする。抵抗601、602の抵抗値はそれぞれ、R601、R602とする。NMOSトランジスタ203、204はカレントミラー回路を構成する。PMOSトランジスタ101とPMOSトランジスタ102、103、104はカレントミラー回路を構成する。

【0034】

次に、第2の実施形態の基準電圧回路の接続について説明する。

PMOSトランジスタ101〜106のソース端子は電源端子501に接続される。PMOSトランジスタ102〜104のゲート端子は、PMOSトランジスタ101のゲート端子及びドレイン端子とNMOSトランジスタ301のドレイン端子に接続される。NMOSトランジスタ201、301のゲート端子は、NMOSトランジスタ201のドレイン端子とPMOSトランジスタ102のドレイン端子に接続され、ソース端子は接地端子502に接続される。抵抗601の一端は、NMOSトランジスタ202のゲート端子とNMOSトランジスタ303のソース端子に接続され、もう一端はNMOSトランジスタ204のドレイン端子とNMOSトランジスタ302のゲート端子に接続される。NMOSトランジスタ202のドレイン端子は、PMOSトランジスタ103とNMOSトランジスタ303のゲート端子に接続され、ソース端子は接地端子に接続される。NMOSトランジスタ303のドレイン端子は電源端子501に接続される。NMOSトランジスタ302のドレイン端子は、PMOSトランジスタ104のドレイン端子とPMOSトランジスタ105、106のゲート端子に接続され、ソース端子は接地端子502に接続される。NMOSトランジスタ203、204のゲート端子は、NMOSトランジスタ203のドレイン端子とPMOSトランジスタ105のドレイン端子に接続され、ソース端子は接地端子502に接続される。抵抗602の一端はPMOSトランジスタ106のドレイン端子と出力端子401に接続され、もう一端は接地端子502に接続される。

【0035】

次に、第2の実施形態の基準電圧回路の動作について説明する。出力端子401の電圧を基準電圧Vrefとする。PMOSトランジスタ101、102に流れる電流は、K値が等しければ、第1の実施形態の(3)式で述べた、Vtnl、Vtnh、K201、K301の値で決まる電流IAである。

【0036】

PMOSトランジスタ103、104に流れる電流は、PMOSトランジスタ101とカレントミラー回路を構成しているため、それぞれK値が同じであれば電流IAが流れる。 NMOSトランジスタ303は、NMOSトランジスタ202のゲートソース間電圧が電流IAを流すのに必要な電圧になるようにNMOSトランジスタ202のゲート端子電圧を制御する。PMOSトランジスタ104、NMOSトランジスタ203、NMOSトランジスタ204は、NMOSトランジスタ302のゲートソース間電圧が電流IAを流すのに必要な電圧になるようにNMOSトランジスタ302のゲート端子電圧を制御する。

【0037】

NMOSトランジスタ202、302が電流IAを流すのに必要なゲートソース間電圧をそれぞれ電圧VGS202A、電圧VGS302Aとすると、抵抗601の両端には、VGS202A−VGS302Aの電圧Vref2が現れる。この電圧Vref2はIA、Vtnl、Vtnh、K202、K302の値で決定される。電流IAはVtnl、Vtnh、K201、K301の値で決まるため、電圧Vref2はすなわち、Vtnl、Vtnh、K201、K202、K301、K302の値で決定される。こうして抵抗のプロセス変動によるばらつきのない基準電圧を得ることができる。また、電圧Vref2の温度特性はK202、K302の値を調整することでIA、VGS202A、VGS302Aの温度特性に対しフラットになるように補正することができる。

各トランジスタが飽和領域で動作した時、電圧Vref2の値は次式で表される。

【0038】

【数6】

【0039】

ただし、K201>K301である。

(6)式から、電圧Vref2の値はVtnh、Vtnl、K201、K202、K301、K302で決定される基準電圧であることがわかる。また、温度特性を補正するには、K201、K202、K301、K302の値のみを調整すれば良い。

【0040】

NMOSトランジスタ203、204はカレントミラー回路を構成し、PMOSトランジスタ105、106はゲート端子ソース端子間電位が同じため、各トランジスタには同じ電流が流れる。このため、抵抗601、602にも同じ電流が流れ、出力端子401の基準電圧Vrefは、Vref=VSS+Vref2×(R602/R601)となり、電圧Vref2を抵抗比R602/R601倍した任意の基準電圧値を出力することができる。一般に、同一チップ内の抵抗比のずれは無視できるほど小さくできるため、抵抗によるプロセス変動の影響がない任意の基準電圧を得ることが可能である。

【0041】

P型基板の場合、第1の実施形態では、NMOSトランジスタ302にバックゲートバイアスがかかってしまうため、基準電圧値を決定する要因にNMOSトランジスタ302のバックゲートバイアス効果が入って、プロセスの変動によるばらつき要因が増えてしまう。しかし、第2の実施形態では、P型基板を用いた場合でも基準電圧値を決定するトランジスタにバックゲートバイアスがかからないため、基準電圧値がVtnl、Vtnh、K201、K202、K301、K302の値のみで決まる。そのため、本発明の第2の実施形態の構成を取れば、P型基板を用いた場合でも基準電圧のプロセス変動によるばらつき要因が少なく、また基準電圧値やその温度特性の補正値を小さくすることが可能である。

【0042】

ここで、NMOSトランジスタ201〜204は同じしきい値電圧Vtnhを持つトランジスタを使用しているが、NMOSトランジスタ203、204で一対のカレントミラー回路を構成できれば、NMOSトランジスタ201、202としきい値が異なっても良い。また、NMOSトランジスタ301〜303は同じしきい値電圧Vtnlを持つトランジスタを使用しているが、NMOSトランジスタ303は動作電源電圧に対して適切な他と異なるしきい値電圧を持つトランジスタを使用しても良い。

【0043】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0044】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K201、K202、K301、K302の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【実施例3】

【0045】

図4は、第3の実施形態の基準電圧回路を示す回路図である。

第3の実施形態の基準電圧回路は、PMOSトランジスタ101、701、702と、NMOSトランジスタ201、202と、出力端子401と、電源端子501と、接地端子502を備える。PMOSトランジスタ701、702のしきい値電圧(以後Vtplとする)の絶対値|Vtpl|は、PMOSトランジスタ101のしきい値電圧(以後Vtphとする)の絶対値|Vtph|より低い。PMOSトランジスタ101、701、702のK値はそれぞれ、K101、K701、K702とする。NMOSトランジスタ201、202はカレントミラー回路を構成する。

【0046】

次に、第3の実施形態の基準電圧回路の接続について説明する。NMOSトランジスタ201、202のソース端子は接地端子502に接続される。NMOSトランジスタ202のゲート端子は、NMOSトランジスタ201のゲート端子及びドレイン端子とPMOSトランジスタ701のドレイン端子に接続される。PMOSトランジスタ101、701のゲート端子は、PMOSトランジスタ702のドレイン端子及びゲート端子とNMOSトランジスタ202のドレイン端子に接続され、ソース端子は電源端子501に接続される。出力端子401は、PMOSトランジスタ101のドレイン端子とPMOSトランジスタ702のソース端子に接続される。

【0047】

次に、第3の実施形態の基準電圧回路の動作について説明する。第3の実施形態の基準電圧回路は、電源端子電圧(VDD)を基準とした基準電圧を作る回路である。回路動作は、第1の実施形態のPMOSトランジスタとNMOSトランジスタの役割を逆転させたものになる。NMOSトランジスタ201、202に流れる電流(以後IBとする)は、PMOSトランジスタ101、701のVGS−IDカーブの交点で、0Aで安定しないように起動回路を設けると、Vtph、Vtpl、K101、K701で決まる一定電流となる。PMOSトランジスタ101、702が電流IBを流すのに必要なゲートソース間電圧をそれぞれVGS101B、VGS702Bとすると、出力端子401に現れる基準電圧Vrefは、Vref=VDD−(|VGS101B|−|VGS702B|)となり、その値は、IB、Vtph、Vtpl、K101、K702で決まる。ここで電流IBは、Vtph、Vtpl、K101、K701で決定されるため、基準電圧値Vref4はVtph、Vtpl、K101、K701、K702のみで決定される。こうして、抵抗のプロセス変動によるばらつきのない基準電圧を得ることができる。

【0048】

また、K101、K702の値を設定することで、IB、VGS101B、VGS702Bの温度特性に対し、基準電圧値Vrefの温度特性がフラットになるように補正することが可能である。

全てのトランジスタが飽和領域で動作する場合、定電流IB、基準電圧Vrefは次式で表される。

【0049】

【数7】

【0050】

ただし、K101>K701である。

【0051】

【数8】

【0052】

ただし、K101>K701である。

(8)式から、基準電圧Vrefの値はVtph、Vtpl、K101、K701、K702で決定する基準電圧であることがわかる。また、温度特性を補正するには、K101、K701、K702の値のみを調整すれば良い。

【0053】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0054】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K101、K701、K702の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【実施例4】

【0055】

図5は、第4の実施形態の基準電圧回路を示す回路図である。

第4の実施形態の基準電圧回路は、PMOSトランジスタ101〜104、701〜703と、NMOSトランジスタ201〜206と、出力端子401、電源端子501と、接地端子502と、抵抗601、602とを備える。PMOSトランジスタ701、702のしきい値電圧の絶対値|Vtpl|は、PMOSトランジスタ101、102のしきい値電圧の絶対値|Vtph|より低い。PMOSトランジスタ101、102、701、702のK値はそれぞれ、K101、K102、K701、K702とする。抵抗601、602の抵抗値はそれぞれ、R601、R602とする。PMOSトランジスタ103、104は、カレントミラー回路を構成し、NMOSトランジスタ201とNMOSトランジスタ202、203、204はカレントミラー回路を構成する。

【0056】

次に、第4の実施形態の基準電圧回路の接続について説明する。NMOSトランジスタ201〜206のソース端子は接地端子502に接続される。NMOSトランジスタ202〜204のゲート端子は、NMOSトランジスタ201のゲート端子及びドレイン端子とPMOSトランジスタ701のドレイン端子に接続される。PMOSトランジスタ101、701のゲート端子は、PMOSトランジスタ101のドレイン端子とNMOSトランジスタ202のドレイン端子に接続され、ソース端子は電源端子501に接続される。抵抗601の一端は、PMOSトランジスタ102のゲート端子とPMOSトランジスタ703のソース端子に接続され、もう一端はPMOSトランジスタ104のドレイン端子とPMOSトランジスタ702のゲート端子に接続される。PMOSトランジスタ102のドレイン端子は、NMOSトランジスタ203のドレイン端子とPMOSトランジスタ703のゲート端子に接続され、ソース端子は電源端子501に接続される。PMOSトランジスタ703のドレイン端子は接地端子502に接続される。PMOSトランジスタ702のドレイン端子は、NMOSトランジスタ204のドレイン端子とNMOSトランジスタ205、206のゲート端子に接続され、ソース端子は電源端子501に接続される。PMOSトランジスタ103、104のゲート端子は、PMOSトランジスタ103のドレイン端子とNMOSトランジスタ205のドレイン端子に接続され、ソース端子は電源端子501に接続される。抵抗602の一端はNMOSトランジスタ206のドレイン端子と出力端子401に接続され、もう一端は電源端子501に接続される。

【0057】

次に、第4の実施形態の基準電圧回路の動作について説明する。第4の実施形態の基準電圧回路は、第2の実施形態のPMOSトランジスタとNMOSトランジスタの役割を逆転させたものになる。NMOSトランジスタ201〜204に流れる電流は、第3の実施形態にて前述したVtph、Vtpl、K101、K701で決まる一定電流(IB)である。PMOSトランジスタ102、702に電流IBを流すのに必要な電圧VGSをそれぞれVGS102B、VGS702Bとすると、抵抗601の両端に現れる電圧Vref5は、Vref5=|VGS102B|−|VGS702B|となり、その値は、IB、Vtpl、Vtph、K102、K702で決まる。電流IBはVtph、Vtpl、K101、K701で決まるため、電圧Vref5を取り出すことで、Vtph、Vtpl、K101、K102、K701、K702の値で決まる抵抗によるプロセス変動によるバラつきのない基準電圧を得ることができる。また、K102、K702の値を調整することでIB、VGS102B、VGS702Bの温度特性に対し電圧Vref5の温度特性がフラットになるように補正することができる。

全てのトランジスタが飽和領域で動作する場合、電圧Vref5は次式で表される。

【0058】

【数9】

【0059】

ただし、K101>K701である。

(9)式から、電圧Vref5の値はVtph、Vtpl、K101、K102、K701、K702で決定する基準電圧であることがわかる。また、温度特性を補正するには、K101、K102、K701、K702の値のみを調整すれば良い。

【0060】

PMOSトランジスタ104とNMOSトランジスタ206には同じ電流が流れるため、出力端子401の基準電圧Vrefは、Vref=VDD−Vref5×(R602/R601)となり、電圧Vref5をR602/R601倍した電源端子電圧基準の任意の基準電圧値を出力することができる。一般に、同一チップ内の抵抗比のずれは無視できるほど小さくできるため抵抗によるプロセス変動の影響がない任意の基準電圧を得ることが可能である。

【0061】

第4の実施形態の基準電圧回路は、電源端子電圧(VDD)を基準とした基準電圧を作る回路で、N型基板を使用する場合に、基準電圧値がバックゲートバイアス効果の影響を受けない回路である。第3の実施形態の回路では、図4のPMOSトランジスタ702にバックゲートバイアスがかかってしまうため、基準電圧値を決定する要因にPMOSトランジスタ702のバックゲートバイアス効果が入って、プロセスの変動によるばらつき要因が増えてしまう。しかし、第4の実施形態では、N型基板を用いた場合でも基準電圧値を決定するトランジスタにバックゲートバイアスがかからないため、基準電圧値がVtpl、Vtph、K101、K102、K701、K702の値のみで決まる。そのため、本発明の第4の実施形態の構成を取れば、N型基板を用いた場合でもプロセス変動によるばらつき要因が少なく、また基準電圧値やその温度特性の補正値を小さくすることが可能である。

【0062】

ここで、PMOSトランジスタ101〜104は同じしきい値電圧Vtphを持つトランジスタを使用しているが、PMOSトランジスタ103、104でカレントミラー回路を構成すれば、PMOSトランジスタ101、102としきい値が異なっても良い。また、PMOSトランジスタ701〜703は同じしきい値電圧Vtplを持つトランジスタを使用しているが、PMOSトランジスタ703は、動作電源電圧に応じて適切な他と異なるしきい値電圧を持つトランジスタを使用しても良い。

【0063】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0064】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K101、K102、K701、K702の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【0065】

以上説明したように、本発明の基準電圧回路は、第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力するように構成されればよい。

【0066】

従って、実施例で示した基準電圧回路の定電圧を発生する回路やその定電圧を基準電圧として出力する回路は、一例であり、これらの回路に限定されるものではない。

【符号の説明】

【0067】

101〜106 PMOSトランジスタ

201〜206 NMOSトランジスタ

301〜303 しきい値の低いNMOSトランジスタ

401 出力端子

701〜703 しきい値の絶対値が低いPMOSトランジスタ

【技術分野】

【0001】

本発明は、基準電圧回路に関する。

【背景技術】

【0002】

図6は、従来の基準電圧回路を示す回路図である。

従来の基準電圧回路は、PMOSトランジスタ101〜103、NMOSトランジスタ201〜204、301、出力端子401、電源端子501、接地端子502及び抵抗601を備える。NMOSトランジスタ301のしきい値電圧(以後Vtnlとする)は、NMOSトランジスタ201〜204のしきい値電圧(以後Vtnhとする)より低い。PMOSトランジスタ102と103は、PMOSトランジスタ101とカレントミラー回路を構成し、PMOSトランジスタ101のドレイン端子電流の所望比のドレイン端子電流を流す。NMOSトランジスタ204は、NMOSトランジスタ203とカレントミラー回路を構成し、NMOSトランジスタ203のドレイン端子電流の所望比のドレイン端子電流を流す。

【0003】

PMOSトランジスタ101〜103のソース端子は電源端子に接続される。PMOSトランジスタ102及び103のゲート端子は、PMOSトランジスタ101のゲート端子及びドレイン端子、NMOSトランジスタ201のドレイン端子に接続される。NMOSトランジスタ201及び202のゲート端子は、NMOSトランジスタ201のドレイン端子及びPMOSトランジスタ102のドレイン端子に接続される。NMOSトランジスタ202のソース端子は接地端子に接続される。抵抗601の一端はNMOSトランジスタ201のソース端子に接続され、もう一端は接地端子に接続される。NMOSトランジスタ203、204及び301のゲート端子は、NMOSトランジスタ203及びPMOSトランジスタ103のドレイン端子に接続される。NMOSトランジスタ203及び204のソース端子は接地端子に接続される。NMOSトランジスタ301のドレイン端子は電源端子に接続される。出力端子401は、NMOSトランジスタ204のドレイン端子及びNMOSトランジスタ301のソース端子に接続される。

【0004】

NMOSトランジスタ201〜204、301のK値はそれぞれ、K201、K202、K203、K204及びK301、抵抗601の抵抗値はR601である。

【0005】

PMOSトランジスタ101と102、NMOSトランジスタ201と202、及び抵抗601は定電流回路を構成する。例えば、各トランジスタが飽和領域で動作する場合、PMOSトランジスタ101と102のK値が等しければ、PMOSトランジスタ101と102に流れる電流は等しく、この電流値は0Aまたは、ある定電流値(以後IKとする)を取る。電流が0Aにならないように起動回路を設けることで、PMOSトランジスタ101と102、NMOSトランジスタ201と202、及び抵抗601は定電流回路として動作する。定電流IKは次式で表される。

【0006】

【数1】

【0007】

ただし、K201>K202である。

【0008】

PMOSトランジスタ103には定電流IKがミラーされ、NMOSトランジスタ204にはPMOSトランジスタ103のドレイン端子電流がミラーされる。例えば、図6のトランジスタが全て飽和領域で動作する場合、PMOSトランジスタ101と103のK値が等しく、NMOSトランジスタ203と204のK値が等しい場合、NMOSトランジスタ204と301には、定電流IKが流れる。NMOSトランジスタ204と301が定電流IKを流すのに必要なゲートソース間電圧をそれぞれVGS204K、VGS301Kとした時、出力端子401の電圧(以後VrefKとする)は(1)式を用いると次式で表される。

【0009】

【数2】

【0010】

ただし、K201>K202である。

【0011】

上述したように、図6の基準電圧回路は、Vtnl、Vtnh、K201、K202、K204、K301、R601で決まる基準電圧VrefKを出力する回路である。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2007−148530号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかし、図6に示す従来の基準電圧回路では、(2)式からトランジスタのK値及びしきい値に加え抵抗値が基準電圧値を決定するため、プロセス変動に対する影響や温度特性の影響が大きくなるという課題があった。また、基準電圧値の温度特性を小さくするように補正する場合に、プロセス変動によるバラつき要因が増えてしまうという課題もあった。さらに、補正をするためには、温度センサや補正用のロジック回路を内蔵する必要になるため、回路規模が増大してしまうという課題があった。

【0014】

本発明は、上記課題に鑑みてなされ、回路規模を増大させずに、プロセス変動によるバラつき要因を減らし、基準電圧値及び、基準電圧値の温度特性を所望の範囲内に容易に補正することができる基準電圧回路を提供する。

【課題を解決するための手段】

【0015】

本発明の基準電圧回路は、上記課題を解決するため、第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

【発明の効果】

【0016】

本発明の基準電圧回路を用いれば、回路規模を増大させずに、抵抗のプロセス変動による基準電圧値のバラつきや、基準電圧値や温度特性の補正値のバラつきを小さくすることが可能である。

【図面の簡単な説明】

【0017】

【図1】第1の実施形態の基準電圧回路を示す回路図である。

【図2】しきい値及びK値の異なる2つのNMOSトランジスタのゲートソース間電圧対ドレイン端子電流の曲線を示すグラフである。

【図3】第2の実施形態の基準電圧回路を示す回路図である。

【図4】第3の実施形態の基準電圧回路を示す回路図である。

【図5】第4の実施形態の基準電圧回路を示す回路図である。

【図6】従来の基準電圧回路を示す回路図である。

【発明を実施するための形態】

【0018】

以下に、本実施形態について、図面を参照して説明する。

【実施例1】

【0019】

図1は、第1の実施形態の基準電圧回路を示す回路図である。

第1の実施形態の基準電圧回路は、PMOSトランジスタ101、102と、NMOSトランジスタ201、301、302と、出力端子401と、電源端子501と、接地端子502を備える。NMOSトランジスタ301、302のしきい値電圧(以後Vtnlとする)は、NMOSトランジスタ201のしきい値電圧(以後Vtnhとする)より低い。NMOSトランジスタ201、301、302のK値はそれぞれ、K201、K301、K302である。PMOSトランジスタ101とPMOSトランジスタ102は、カレントミラー回路を構成する。

【0020】

次に、第1の実施形態の基準電圧回路の接続について説明する。

PMOSトランジスタ101、102のソース端子は、電源端子501に接続される。PMOSトランジスタ102のゲート端子は、PMOSトランジスタ101のゲート端子及びドレイン端子とNMOSトランジスタ301のドレイン端子に接続される。NMOSトランジスタ201、301のゲート端子は、NMOSトランジスタ302のドレイン端子及びゲート端子とPMOSトランジスタ102のドレイン端子に接続され、ソース端子は接地端子502に接続される。出力端子401は、NMOSトランジスタ201のドレイン端子とNMOSトランジスタ302のソース端子に接続される。

【0021】

次に、第1の実施形態の基準電圧回路の動作について説明する。

PMOSトランジスタ101、102のドレイン端子電流をそれぞれI101、I102とする。出力端子401の電圧をVrefとする。PMOSトランジスタ101、102はカレントミラー回路を構成しているため、それぞれのK値が等しければ電流I101と電流I102は等しい電流が流れる。図2に、NMOSトランジスタ201とNMOSトランジスタ301が飽和領域で動作する場合の、ゲートソース間電圧(以後VGSとする)対ドレイン端子電流(以後IDとする)特性を示す。各々の曲線の立ち上がり位置と傾きは、それぞれしきい値電圧とK値によって決まる。電流I101と電流I102が等しく、NMOSトランジスタ201とNMOSトランジスタ301のゲート端子は接続されているため、この2つのトランジスタが飽和領域で動作すると、電圧VGSはA点となる。起動回路を設けると、電流I101(=I102)はA点の電流値(以後IAとする)となり、この値はVtnl、Vtnh、K201、K301によって次式のように表される。

【0022】

【数3】

【0023】

ただし、K201>K301である。

【0024】

NMOSトランジスタ201、302が電流IAを流すのに必要な電圧VGSをそれぞれVGS201A、VGS302A、接地端子電圧をVSSとすると、出力端子401の基準電圧VrefはVref=VSS+VGS201A−VGS302Aとなる。電圧VGS201A、電圧VGS302Aの値は、IA、Vtnl、Vtnh、K201、K302の値で決まる。(3)式より電流IAはVtnl、Vtnh、K201、K301の値で決まるため、出力端子401の基準電圧Vrefの値は、Vtnh、Vtnl、K201、K301、K302の値のみで決まる。

【0025】

NMOSトランジスタ201とNMOSトランジスタ302が飽和領域で動作する場合は、基準電圧Vrefは次式で表される。

【0026】

【数4】

【0027】

ここで、全てのトランジスタが飽和領域で動作すると、(4)式の電流IAに(3)式を代入することで基準電圧Vrefは次式で表される。

【0028】

【数5】

【0029】

ただし、K201>K301である。

(5)式から、基準電圧Vrefの値はVtnh、Vtnl、K201、K301、K302で決定する電圧であることがわかる。こうして、抵抗のプロセス変動によるばらつきのない基準電圧を得ることができる。また、温度特性を補正するには、K201、K301、K302の値のみを調整することで容易に補正することができる。

【0030】

ここで、NMOSトランジスタ201、301、302が飽和領域で動作した場合を例に取ったが、いずれかまたは全てが弱反転領域で動作したとしても、両トランジスタのVGS対IDカーブが交わるようにK201、K301を設定すれば、前述したVtnl、Vtnh、K201、及びK301の値で決まる電流IAを作ることが出来る。また、基準電圧Vrefも、Vtnl、Vtnh、K201、K301、K302の値で決定することができる。そのため、各トランジスタのK値のみを調整することで、温度特性の補正が可能である。

【0031】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0032】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K201、K301、K302の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【実施例2】

【0033】

図3は、第2の実施形態の基準電圧回路を示す回路図である。

第2の実施形態の基準電圧回路は、PMOSトランジスタ101〜106と、NMOSトランジスタ201〜204、301〜303と、出力端子401と、電源端子501と、接地端子502と、抵抗601〜602とを備える。NMOSトランジスタ301〜302のしきい値電圧(以後Vtnlとする)は、NMOSトランジスタ201〜202のしきい値電圧(以後Vtnhとする)より低い。NMOSトランジスタ201、202、301、302のK値はそれぞれ、K201、K202、K301、K302とする。抵抗601、602の抵抗値はそれぞれ、R601、R602とする。NMOSトランジスタ203、204はカレントミラー回路を構成する。PMOSトランジスタ101とPMOSトランジスタ102、103、104はカレントミラー回路を構成する。

【0034】

次に、第2の実施形態の基準電圧回路の接続について説明する。

PMOSトランジスタ101〜106のソース端子は電源端子501に接続される。PMOSトランジスタ102〜104のゲート端子は、PMOSトランジスタ101のゲート端子及びドレイン端子とNMOSトランジスタ301のドレイン端子に接続される。NMOSトランジスタ201、301のゲート端子は、NMOSトランジスタ201のドレイン端子とPMOSトランジスタ102のドレイン端子に接続され、ソース端子は接地端子502に接続される。抵抗601の一端は、NMOSトランジスタ202のゲート端子とNMOSトランジスタ303のソース端子に接続され、もう一端はNMOSトランジスタ204のドレイン端子とNMOSトランジスタ302のゲート端子に接続される。NMOSトランジスタ202のドレイン端子は、PMOSトランジスタ103とNMOSトランジスタ303のゲート端子に接続され、ソース端子は接地端子に接続される。NMOSトランジスタ303のドレイン端子は電源端子501に接続される。NMOSトランジスタ302のドレイン端子は、PMOSトランジスタ104のドレイン端子とPMOSトランジスタ105、106のゲート端子に接続され、ソース端子は接地端子502に接続される。NMOSトランジスタ203、204のゲート端子は、NMOSトランジスタ203のドレイン端子とPMOSトランジスタ105のドレイン端子に接続され、ソース端子は接地端子502に接続される。抵抗602の一端はPMOSトランジスタ106のドレイン端子と出力端子401に接続され、もう一端は接地端子502に接続される。

【0035】

次に、第2の実施形態の基準電圧回路の動作について説明する。出力端子401の電圧を基準電圧Vrefとする。PMOSトランジスタ101、102に流れる電流は、K値が等しければ、第1の実施形態の(3)式で述べた、Vtnl、Vtnh、K201、K301の値で決まる電流IAである。

【0036】

PMOSトランジスタ103、104に流れる電流は、PMOSトランジスタ101とカレントミラー回路を構成しているため、それぞれK値が同じであれば電流IAが流れる。 NMOSトランジスタ303は、NMOSトランジスタ202のゲートソース間電圧が電流IAを流すのに必要な電圧になるようにNMOSトランジスタ202のゲート端子電圧を制御する。PMOSトランジスタ104、NMOSトランジスタ203、NMOSトランジスタ204は、NMOSトランジスタ302のゲートソース間電圧が電流IAを流すのに必要な電圧になるようにNMOSトランジスタ302のゲート端子電圧を制御する。

【0037】

NMOSトランジスタ202、302が電流IAを流すのに必要なゲートソース間電圧をそれぞれ電圧VGS202A、電圧VGS302Aとすると、抵抗601の両端には、VGS202A−VGS302Aの電圧Vref2が現れる。この電圧Vref2はIA、Vtnl、Vtnh、K202、K302の値で決定される。電流IAはVtnl、Vtnh、K201、K301の値で決まるため、電圧Vref2はすなわち、Vtnl、Vtnh、K201、K202、K301、K302の値で決定される。こうして抵抗のプロセス変動によるばらつきのない基準電圧を得ることができる。また、電圧Vref2の温度特性はK202、K302の値を調整することでIA、VGS202A、VGS302Aの温度特性に対しフラットになるように補正することができる。

各トランジスタが飽和領域で動作した時、電圧Vref2の値は次式で表される。

【0038】

【数6】

【0039】

ただし、K201>K301である。

(6)式から、電圧Vref2の値はVtnh、Vtnl、K201、K202、K301、K302で決定される基準電圧であることがわかる。また、温度特性を補正するには、K201、K202、K301、K302の値のみを調整すれば良い。

【0040】

NMOSトランジスタ203、204はカレントミラー回路を構成し、PMOSトランジスタ105、106はゲート端子ソース端子間電位が同じため、各トランジスタには同じ電流が流れる。このため、抵抗601、602にも同じ電流が流れ、出力端子401の基準電圧Vrefは、Vref=VSS+Vref2×(R602/R601)となり、電圧Vref2を抵抗比R602/R601倍した任意の基準電圧値を出力することができる。一般に、同一チップ内の抵抗比のずれは無視できるほど小さくできるため、抵抗によるプロセス変動の影響がない任意の基準電圧を得ることが可能である。

【0041】

P型基板の場合、第1の実施形態では、NMOSトランジスタ302にバックゲートバイアスがかかってしまうため、基準電圧値を決定する要因にNMOSトランジスタ302のバックゲートバイアス効果が入って、プロセスの変動によるばらつき要因が増えてしまう。しかし、第2の実施形態では、P型基板を用いた場合でも基準電圧値を決定するトランジスタにバックゲートバイアスがかからないため、基準電圧値がVtnl、Vtnh、K201、K202、K301、K302の値のみで決まる。そのため、本発明の第2の実施形態の構成を取れば、P型基板を用いた場合でも基準電圧のプロセス変動によるばらつき要因が少なく、また基準電圧値やその温度特性の補正値を小さくすることが可能である。

【0042】

ここで、NMOSトランジスタ201〜204は同じしきい値電圧Vtnhを持つトランジスタを使用しているが、NMOSトランジスタ203、204で一対のカレントミラー回路を構成できれば、NMOSトランジスタ201、202としきい値が異なっても良い。また、NMOSトランジスタ301〜303は同じしきい値電圧Vtnlを持つトランジスタを使用しているが、NMOSトランジスタ303は動作電源電圧に対して適切な他と異なるしきい値電圧を持つトランジスタを使用しても良い。

【0043】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0044】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K201、K202、K301、K302の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【実施例3】

【0045】

図4は、第3の実施形態の基準電圧回路を示す回路図である。

第3の実施形態の基準電圧回路は、PMOSトランジスタ101、701、702と、NMOSトランジスタ201、202と、出力端子401と、電源端子501と、接地端子502を備える。PMOSトランジスタ701、702のしきい値電圧(以後Vtplとする)の絶対値|Vtpl|は、PMOSトランジスタ101のしきい値電圧(以後Vtphとする)の絶対値|Vtph|より低い。PMOSトランジスタ101、701、702のK値はそれぞれ、K101、K701、K702とする。NMOSトランジスタ201、202はカレントミラー回路を構成する。

【0046】

次に、第3の実施形態の基準電圧回路の接続について説明する。NMOSトランジスタ201、202のソース端子は接地端子502に接続される。NMOSトランジスタ202のゲート端子は、NMOSトランジスタ201のゲート端子及びドレイン端子とPMOSトランジスタ701のドレイン端子に接続される。PMOSトランジスタ101、701のゲート端子は、PMOSトランジスタ702のドレイン端子及びゲート端子とNMOSトランジスタ202のドレイン端子に接続され、ソース端子は電源端子501に接続される。出力端子401は、PMOSトランジスタ101のドレイン端子とPMOSトランジスタ702のソース端子に接続される。

【0047】

次に、第3の実施形態の基準電圧回路の動作について説明する。第3の実施形態の基準電圧回路は、電源端子電圧(VDD)を基準とした基準電圧を作る回路である。回路動作は、第1の実施形態のPMOSトランジスタとNMOSトランジスタの役割を逆転させたものになる。NMOSトランジスタ201、202に流れる電流(以後IBとする)は、PMOSトランジスタ101、701のVGS−IDカーブの交点で、0Aで安定しないように起動回路を設けると、Vtph、Vtpl、K101、K701で決まる一定電流となる。PMOSトランジスタ101、702が電流IBを流すのに必要なゲートソース間電圧をそれぞれVGS101B、VGS702Bとすると、出力端子401に現れる基準電圧Vrefは、Vref=VDD−(|VGS101B|−|VGS702B|)となり、その値は、IB、Vtph、Vtpl、K101、K702で決まる。ここで電流IBは、Vtph、Vtpl、K101、K701で決定されるため、基準電圧値Vref4はVtph、Vtpl、K101、K701、K702のみで決定される。こうして、抵抗のプロセス変動によるばらつきのない基準電圧を得ることができる。

【0048】

また、K101、K702の値を設定することで、IB、VGS101B、VGS702Bの温度特性に対し、基準電圧値Vrefの温度特性がフラットになるように補正することが可能である。

全てのトランジスタが飽和領域で動作する場合、定電流IB、基準電圧Vrefは次式で表される。

【0049】

【数7】

【0050】

ただし、K101>K701である。

【0051】

【数8】

【0052】

ただし、K101>K701である。

(8)式から、基準電圧Vrefの値はVtph、Vtpl、K101、K701、K702で決定する基準電圧であることがわかる。また、温度特性を補正するには、K101、K701、K702の値のみを調整すれば良い。

【0053】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0054】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K101、K701、K702の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【実施例4】

【0055】

図5は、第4の実施形態の基準電圧回路を示す回路図である。

第4の実施形態の基準電圧回路は、PMOSトランジスタ101〜104、701〜703と、NMOSトランジスタ201〜206と、出力端子401、電源端子501と、接地端子502と、抵抗601、602とを備える。PMOSトランジスタ701、702のしきい値電圧の絶対値|Vtpl|は、PMOSトランジスタ101、102のしきい値電圧の絶対値|Vtph|より低い。PMOSトランジスタ101、102、701、702のK値はそれぞれ、K101、K102、K701、K702とする。抵抗601、602の抵抗値はそれぞれ、R601、R602とする。PMOSトランジスタ103、104は、カレントミラー回路を構成し、NMOSトランジスタ201とNMOSトランジスタ202、203、204はカレントミラー回路を構成する。

【0056】

次に、第4の実施形態の基準電圧回路の接続について説明する。NMOSトランジスタ201〜206のソース端子は接地端子502に接続される。NMOSトランジスタ202〜204のゲート端子は、NMOSトランジスタ201のゲート端子及びドレイン端子とPMOSトランジスタ701のドレイン端子に接続される。PMOSトランジスタ101、701のゲート端子は、PMOSトランジスタ101のドレイン端子とNMOSトランジスタ202のドレイン端子に接続され、ソース端子は電源端子501に接続される。抵抗601の一端は、PMOSトランジスタ102のゲート端子とPMOSトランジスタ703のソース端子に接続され、もう一端はPMOSトランジスタ104のドレイン端子とPMOSトランジスタ702のゲート端子に接続される。PMOSトランジスタ102のドレイン端子は、NMOSトランジスタ203のドレイン端子とPMOSトランジスタ703のゲート端子に接続され、ソース端子は電源端子501に接続される。PMOSトランジスタ703のドレイン端子は接地端子502に接続される。PMOSトランジスタ702のドレイン端子は、NMOSトランジスタ204のドレイン端子とNMOSトランジスタ205、206のゲート端子に接続され、ソース端子は電源端子501に接続される。PMOSトランジスタ103、104のゲート端子は、PMOSトランジスタ103のドレイン端子とNMOSトランジスタ205のドレイン端子に接続され、ソース端子は電源端子501に接続される。抵抗602の一端はNMOSトランジスタ206のドレイン端子と出力端子401に接続され、もう一端は電源端子501に接続される。

【0057】

次に、第4の実施形態の基準電圧回路の動作について説明する。第4の実施形態の基準電圧回路は、第2の実施形態のPMOSトランジスタとNMOSトランジスタの役割を逆転させたものになる。NMOSトランジスタ201〜204に流れる電流は、第3の実施形態にて前述したVtph、Vtpl、K101、K701で決まる一定電流(IB)である。PMOSトランジスタ102、702に電流IBを流すのに必要な電圧VGSをそれぞれVGS102B、VGS702Bとすると、抵抗601の両端に現れる電圧Vref5は、Vref5=|VGS102B|−|VGS702B|となり、その値は、IB、Vtpl、Vtph、K102、K702で決まる。電流IBはVtph、Vtpl、K101、K701で決まるため、電圧Vref5を取り出すことで、Vtph、Vtpl、K101、K102、K701、K702の値で決まる抵抗によるプロセス変動によるバラつきのない基準電圧を得ることができる。また、K102、K702の値を調整することでIB、VGS102B、VGS702Bの温度特性に対し電圧Vref5の温度特性がフラットになるように補正することができる。

全てのトランジスタが飽和領域で動作する場合、電圧Vref5は次式で表される。

【0058】

【数9】

【0059】

ただし、K101>K701である。

(9)式から、電圧Vref5の値はVtph、Vtpl、K101、K102、K701、K702で決定する基準電圧であることがわかる。また、温度特性を補正するには、K101、K102、K701、K702の値のみを調整すれば良い。

【0060】

PMOSトランジスタ104とNMOSトランジスタ206には同じ電流が流れるため、出力端子401の基準電圧Vrefは、Vref=VDD−Vref5×(R602/R601)となり、電圧Vref5をR602/R601倍した電源端子電圧基準の任意の基準電圧値を出力することができる。一般に、同一チップ内の抵抗比のずれは無視できるほど小さくできるため抵抗によるプロセス変動の影響がない任意の基準電圧を得ることが可能である。

【0061】

第4の実施形態の基準電圧回路は、電源端子電圧(VDD)を基準とした基準電圧を作る回路で、N型基板を使用する場合に、基準電圧値がバックゲートバイアス効果の影響を受けない回路である。第3の実施形態の回路では、図4のPMOSトランジスタ702にバックゲートバイアスがかかってしまうため、基準電圧値を決定する要因にPMOSトランジスタ702のバックゲートバイアス効果が入って、プロセスの変動によるばらつき要因が増えてしまう。しかし、第4の実施形態では、N型基板を用いた場合でも基準電圧値を決定するトランジスタにバックゲートバイアスがかからないため、基準電圧値がVtpl、Vtph、K101、K102、K701、K702の値のみで決まる。そのため、本発明の第4の実施形態の構成を取れば、N型基板を用いた場合でもプロセス変動によるばらつき要因が少なく、また基準電圧値やその温度特性の補正値を小さくすることが可能である。

【0062】

ここで、PMOSトランジスタ101〜104は同じしきい値電圧Vtphを持つトランジスタを使用しているが、PMOSトランジスタ103、104でカレントミラー回路を構成すれば、PMOSトランジスタ101、102としきい値が異なっても良い。また、PMOSトランジスタ701〜703は同じしきい値電圧Vtplを持つトランジスタを使用しているが、PMOSトランジスタ703は、動作電源電圧に応じて適切な他と異なるしきい値電圧を持つトランジスタを使用しても良い。

【0063】

なお、カレントミラー回路のK値が等しいとして、各トランジスタのK値を調整することで基準電圧を補正する方式を例に挙げたが、カレントミラー回路のミラー対のK値を変えて各トランジスタのドレイン端子電流比を調節することで基準電圧値を補正することも可能である。

【0064】

以上により、抵抗のプロセス変動によるばらつきがなく、温度特性を補正するには、K101、K102、K701、K702の値のみを調整することで容易に補正することができる基準電圧を得る事ができる。

【0065】

以上説明したように、本発明の基準電圧回路は、第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力するように構成されればよい。

【0066】

従って、実施例で示した基準電圧回路の定電圧を発生する回路やその定電圧を基準電圧として出力する回路は、一例であり、これらの回路に限定されるものではない。

【符号の説明】

【0067】

101〜106 PMOSトランジスタ

201〜206 NMOSトランジスタ

301〜303 しきい値の低いNMOSトランジスタ

401 出力端子

701〜703 しきい値の絶対値が低いPMOSトランジスタ

【特許請求の範囲】

【請求項1】

ソース端子が第1の電源端子に接続された第1のMOSトランジスタと、

ソース端子が第1の電源端子に接続され、ゲート端子が前記第1のMOSトランジスタのゲート端子に接続された、前記第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、

前記第1のMOSトランジスタと前記第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、

前記カレントミラー回路の電流を流す第3のMOSトランジスタと、

前記第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、前記カレントミラー回路の電流を流す第4のMOSトランジスタと、を備え、

前記第3のMOSトランジスタと前記第4のMOSトランジスタのしきい値の絶対値とK値に基づく定電圧を基準電圧として出力する、

ことを特徴とするとする基準電圧回路。

【請求項2】

前記カレントミラー回路は、

ドレイン端子及びゲート端子が前記第1のMOSトランジスタのドレイン端子に接続された第5のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第2のMOSトランジスタのゲート端子とドレイン端子に接続された第6のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第3のMOSトランジスタのドレイン端子に接続された第7のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第4のMOSトランジスタのドレイン端子に接続された第8のMOSトランジスタと、

一方の端子が前記第3のMOSトランジスタのゲート端子に接続され、他方の端子が前記第4のMOSトランジスタのゲート端子に接続された抵抗と、を備え

前記抵抗の両端の電圧に基づく定電圧を基準電圧として出力する、

ことを特徴とする請求項1に記載の基準電圧回路。

【請求項3】

前記カレントミラー回路は、

ドレイン端子及びゲート端子が前記第1のMOSトランジスタのドレイン端子に接続された第5のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第3のMOSトランジスタのゲート端子とドレイン端子に接続された第6のMOSトランジスタと、を備え、

前記第3のMOSトランジスタを、ゲート端子を前記第2のMOSトランジスタのゲート端子に接続され、ソース端子を前記第2のMOSトランジスタのドレイン端子に接続される構成として、前記第4のMOSトランジスタと前記第2のMOSトランジスタを共通にすることによって、

前記第3のMOSトランジスタのソース端子と前記第2のMOSトランジスタのドレイン端子の接続点から前記基準電圧を出力する、

ことを特徴とする請求項1に記載の基準電圧回路。

【請求項1】

ソース端子が第1の電源端子に接続された第1のMOSトランジスタと、

ソース端子が第1の電源端子に接続され、ゲート端子が前記第1のMOSトランジスタのゲート端子に接続された、前記第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、

前記第1のMOSトランジスタと前記第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、

前記カレントミラー回路の電流を流す第3のMOSトランジスタと、

前記第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、前記カレントミラー回路の電流を流す第4のMOSトランジスタと、を備え、

前記第3のMOSトランジスタと前記第4のMOSトランジスタのしきい値の絶対値とK値に基づく定電圧を基準電圧として出力する、

ことを特徴とするとする基準電圧回路。

【請求項2】

前記カレントミラー回路は、

ドレイン端子及びゲート端子が前記第1のMOSトランジスタのドレイン端子に接続された第5のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第2のMOSトランジスタのゲート端子とドレイン端子に接続された第6のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第3のMOSトランジスタのドレイン端子に接続された第7のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第4のMOSトランジスタのドレイン端子に接続された第8のMOSトランジスタと、

一方の端子が前記第3のMOSトランジスタのゲート端子に接続され、他方の端子が前記第4のMOSトランジスタのゲート端子に接続された抵抗と、を備え

前記抵抗の両端の電圧に基づく定電圧を基準電圧として出力する、

ことを特徴とする請求項1に記載の基準電圧回路。

【請求項3】

前記カレントミラー回路は、

ドレイン端子及びゲート端子が前記第1のMOSトランジスタのドレイン端子に接続された第5のMOSトランジスタと、

ゲート端子が前記第5のMOSトランジスタのゲート端子に接続され、ドレイン端子が前記第3のMOSトランジスタのゲート端子とドレイン端子に接続された第6のMOSトランジスタと、を備え、

前記第3のMOSトランジスタを、ゲート端子を前記第2のMOSトランジスタのゲート端子に接続され、ソース端子を前記第2のMOSトランジスタのドレイン端子に接続される構成として、前記第4のMOSトランジスタと前記第2のMOSトランジスタを共通にすることによって、

前記第3のMOSトランジスタのソース端子と前記第2のMOSトランジスタのドレイン端子の接続点から前記基準電圧を出力する、

ことを特徴とする請求項1に記載の基準電圧回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−73375(P2013−73375A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−211220(P2011−211220)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

[ Back to top ]