基準電圧発生回路及びそれを備えた半導体素子

【課題】バンドギャップ電圧よりも低い電源電圧で動作し、低消費電力かつ高精度の基準電圧発生回路を提供すること。

【解決手段】第1のダイオードDaの両端と、直列に接続した第2のダイオードDbと第1抵抗R1との間に同じ電圧が掛かるように差動増幅回路A1でフィードバックをかけ、正の温度依存性を持つ差分電圧VSを第2電流I2に変換する。また、第2ダイオードDbに第3の抵抗素子R3Aを接続し、第1のダイオードDaに第4の抵抗素子R3Bを接続して、負の温度依存性を持つ順方向電圧を第3電流I3に変換する。そして、この第2電流I2と第3電流I3とを合成することで、温度依存性のない第1電流I1を生成する。さらに、第3の抵抗素子R3Aと第4の抵抗素子R3Bを出力ノードN3に接続して、第2の抵抗素子R2にI1+I3×2となる電流を流して出力電圧Voutを生成する。

【解決手段】第1のダイオードDaの両端と、直列に接続した第2のダイオードDbと第1抵抗R1との間に同じ電圧が掛かるように差動増幅回路A1でフィードバックをかけ、正の温度依存性を持つ差分電圧VSを第2電流I2に変換する。また、第2ダイオードDbに第3の抵抗素子R3Aを接続し、第1のダイオードDaに第4の抵抗素子R3Bを接続して、負の温度依存性を持つ順方向電圧を第3電流I3に変換する。そして、この第2電流I2と第3電流I3とを合成することで、温度依存性のない第1電流I1を生成する。さらに、第3の抵抗素子R3Aと第4の抵抗素子R3Bを出力ノードN3に接続して、第2の抵抗素子R2にI1+I3×2となる電流を流して出力電圧Voutを生成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、所望の基準電圧を発生する基準電圧発生回路及びそれを備えた半導体素子に関し、特に、シリコンのバンドギャップ電圧以下の電源電圧で動作する基準電圧発生回路及びそれを備えた半導体素子に関するものである。

【背景技術】

【0002】

半導体チップなどの半導体素子においては、内部回路を適切に動作させるために、その回路内のノードが所望の電圧になるように調整する必要があり、特にアナログ回路においては、その電圧の精度が重要となる。

【0003】

そのため、通常、半導体素子内には、所望の基準電圧を発生する基準電圧発生回路が形成されている。

【0004】

この基準電圧発生回路として、電流密度の異なる2つのダイオードDa,Dbを用いて正の温度依存性を持つ電圧を取り出し、この電圧と負の温度依存性を持つPN接合の順方向電圧とを適切な比率で加算することで、温度に依存しない基準電圧を生成する回路がある。

【0005】

すなわち、電流密度の異なる2つのダイオードDa,Dbの差分電圧VSが正の温度依存性を持ち、ダイオードDa,Dbの順方向電圧VBEが負の温度依存性を持つことから、これらの電圧を適切な比率で加算して温度に依存しない基準電圧を生成するのである。

【0006】

例えば、温度が上がったとき、負の温度依存性を持つ順方向電圧VBEの降下分の電圧をΔVBEとし、正の温度依存性を持つ差分電圧VSの上昇分の電圧ΔVSとすると、適切に比率αを調整することで、ΔVBE+αΔVS=0となる。これにより、温度依存性を持たない高精度の基準電圧を生成することができる。

【0007】

しかしながら、90nm以降の先端プロセスの半導体素子では、電源電圧がバンドギャップ電圧以下の電圧(例えば、1.2V)であるため、上記従来の構成では動作させることができない。

【0008】

そこで、下記特許文献1には、電源電圧がバンドギャップ電圧以下の電圧であっても、高精度の基準電圧を生成することができる基準電圧発生回路が開示されている。

【0009】

特許文献1の基準電圧発生回路は、正の温度依存性を持つ差分電圧VSを電流に変換すると共に、負の温度依存性を持つ順方向電圧VBEを電流に変換し、これらの電流を加算した後に、電圧に変換することで、基準電圧Voutを生成するものである。

【0010】

図4に特許文献1に記載された基準電圧発生回路100の構成を示す。

【0011】

ダイオードDbはダイオードDaよりもエミッター面積がN倍(N>1)となっており、これらに同じ電流I11Aを流したときの順方向電圧の差分電圧VS1は、以下の式(10)のように表すことができる。ここで、kはボルツマン定数、Tは絶対温度、qは電子の電荷量、logは自然対数である。

VS1=kT/qlogN ・・・(10)

【0012】

ダイオードDbには直列に抵抗素子R11が接続されており、2つのノードN10,N11の電圧V10a,V10bの電圧が等しくなるように差動増幅回路A10とPMOSトランジスタM11,M12を用いたフィードバックが掛かっている。

【0013】

このようにノードN10,N11の電圧V10a,V10bが等しくなることから、ダイオードDa,Dbの差分電圧VS1は、抵抗素子R11の両端電圧と同じ電圧となり、ダイオードDa,Dbに流れる電流I11Aは、下記の式(11)のように表すことができる。

I11A=kT/(R11q)logN ・・・(11)

【0014】

従って、ダイオードDa,Dbに流れる電流I11Aは、温度上昇に応じて電流が増加する正の温度依存性を持つ電流であることがわかる。

【0015】

一方、ノードN10,N11と接地ノードとの間には、同じ抵抗値R13を持つ抵抗素子R13A,R13Bがそれぞれ接続されている。これらの抵抗素子R13A,R13Bには、それぞれダイオードDaの順方向電圧VBEと同じ電圧が掛かることから、これら抵抗素子R13A,R13Bに流れる電流I11Bは、以下の式(12)のように表すことができる。

I11B=VBE/R13 ・・・(12)

【0016】

上記式(12)において順方向電圧VBEは、温度上昇に応じて電圧が低下する負の温度依存性を持つ電圧であることから、抵抗素子R13A,R13Bに流れる電流I11Bは負の温度依存性を持つ電流であることがわかる。

【0017】

PMOSトランジスタM11,M12にはこれらの電流の和I10(=I11A+I11B)が流れることになるため、抵抗素子R11,R13A,R13Bの抵抗値を適切に選ぶことによって、これら正と負の温度依存性を持つ電流I11A, I11Bの比率を調整することが出来る。従って、最適な比率で設計すると、温度依存性を持たない電流I10を生成することが出来ることになる。

【0018】

そして、これと同じ電流I10をPMOSトランジスタM13から抵抗素子R12へ流すことで、温度依存性を持たない出力電圧Voutを生成して、出力ノードN12から出力することができる。

【0019】

【特許文献1】特許第3586073号公報

【発明の開示】

【発明が解決しようとする課題】

【0020】

しかしながら、上記特許文献1の技術では、正の温度依存性を持つ電流I11Aを生成するために、抵抗素子R13A,R13Bで余分な電流が消費されることになる。

【0021】

一方、携帯機器などでは、シビアな低消費電力が求められており、できるだけ消費電流を削減することが望まれている。

【0022】

そこで、本発明は、バンドギャップ電圧よりも低い電源電圧で動作し、かつ従来よりも低消費電力である高精度の基準電圧発生回路を提供することを目的とする。

【課題を解決するための手段】

【0023】

上記目的を達成するために、請求項1に記載の発明は、電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、さらに、前記第1のPMOSトランジスタのドレインと前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えたものである。

【0024】

また、請求項2に記載の発明は、請求項1に記載の発明において、前記第1の電圧は、前記第1のPMOSトランジスタと前記第1のPN接合との接続点に発生する電圧とし、前記第2の電圧は、前記第2のPMOSトランジスタと前記第1の抵抗素子との接続点に発生する電圧とした。

【0025】

また、請求項3に記載の発明は、請求項1又は請求項2に記載の発明において、前記第2のPN接合を、並列に接続された複数個のPN接合から構成した。

【0026】

また、請求項4に記載の発明は、請求項1又は請求項2に記載の発明において、前記第2のPMOSトランジスタを、並列に接続された複数個のPMOSトランジスタから構成し、前記第4の抵抗素子の抵抗値を前記第3の抵抗素子の抵抗値のN倍にし、前記第1のPN接合を前記第1のPN接合と同一サイズで形成した。

【0027】

また、請求項5に記載の発明は、所定の基準電圧を発生する基準電圧発生回路を内部に備え、前記基準電圧発生回路は、電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、さらに、前記第1のPMOSトランジスタのドレインと前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えたものである。

【発明の効果】

【0028】

本発明によれば、バンドギャップ電圧よりも低い電源電圧で動作し、かつ従来よりも低消費電力である高精度の基準電圧発生回路を提供することができる。

【発明を実施するための最良の形態】

【0029】

本発明の一実施形態に係る半導体素子は、バンドギャップ電圧よりも低い電源電圧で動作し、低消費電力かつ高精度の基準電圧発生回路を備えている。

【0030】

この基準電圧発生回路は、電流密度の異なる第1のダイオードと第2のダイオードの差分電圧が正の温度依存性を持ち、第1及び第2のダイオードの順方向電圧VBEが負の温度依存性を持つことから、これらを利用して高精度の基準電圧を生成するものである。

【0031】

そして、バンドギャップ電圧よりも低い電源電圧で動作させるために、正の温度依存性を持つ差分電圧と負の温度依存性を持つ順方向電圧との加算を直接行わずに、一旦電流に変換し、電流で加算を行った後に電圧に変換して基準電圧を生成している。

【0032】

すなわち、第1のダイオードと、直列に接続した第2のダイオード及び第1の抵抗素子とに同じ電圧が掛かるように差動増幅回路でフィードバックをかけ、正の温度依存性を持つ差分電圧を第1のダイオード又は第2のダイオードに流れる第1電流に変換する。

【0033】

また、第1のダイオードに第3の抵抗素子を接続し、第2のダイオードに第4抵抗素子を接続して、正の温度依存性を持つ順方向電圧を第3及び第4の抵抗素子に流れる第2電流に変換する。

【0034】

第1の電流は正の温度依存性を持つ電流となり、第2の電流は負の温度依存性を持つ電流となるため、これらを加算することにより温度依存性を持たない第3の電流を得ることができる。そして、この第3の電流を第2の抵抗素子に流すことにより温度依存性を持たない電圧を生成している。

【0035】

さらに、本実施形態に係る基準電圧発生回路では、基準電圧を出力する出力ノードに第3及び第4の抵抗素子を接続するようにしている。

【0036】

上記特許文献1の技術では、第3及び第4抵抗素子である抵抗素子R13B,R13Aを接地ノードに接続するようにしていたため、消費電力が無駄になっていたが、本実施形態に係る基準電圧発生回路では、第3及び第4抵抗素子に流れる電流を第2の抵抗素子に流して基準電圧を生成するために用いている。

【0037】

従って、消費電力を抑制することができ、携帯機器などのようにシビアな低消費電力が求められる機器に適用して低消費電力を図ることができる。

【0038】

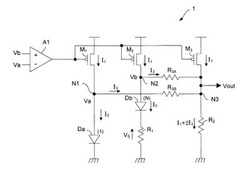

以下、本発明の一実施形態に係る半導体素子内に形成された基準電圧発生回路について図面を参照して具体的に説明する。図1及び図2は本発明の一実施形態に係る基準電圧発生回路の構成図である。

【0039】

基準電圧発生回路1は、第1〜第3のPMOSトランジスタM1〜M3、第1及び第2のダイオードDa,Db(第1のPN接合及び第2のPN接合の一例)、第1〜第4の抵抗素子R1,R2,R3B,R3A、差動増幅回路A1とから構成される。

【0040】

図1に示すように、第1のPMOSトランジスタM1と第1のダイオードDaは直列に電源ノードと接地ノードに接続され、第2のPMOSトランジスタM2、第2のダイオードDb及び第1の抵抗素子R1は電源ノードと接地ノードとの間に直列に接続されている。なお、第2のダイオードDb及び第1の抵抗素子R1の配置は第1の抵抗素子R1を接地するのに限られず、図2に示すように第2のダイオードDbを接地するように配置してもよい。

【0041】

また、第1及び第2のPMOSトランジスタM1,M2は、同一サイズで形成され、共に差動増幅回路A1の出力電圧が入力されている。そのため、第1及び第2のPMOSトランジスタM1,M2は電流源として、第1のダイオードDa及び第2のダイオードDbに等しい電流I2を供給することになる。

【0042】

また、第1のPMOSトランジスタM1のドレインと第1のダイオードDaとが接続されるノードN1と、第2のPMOSトランジスタM2のドレインと第2のダイオードDbとが接続されるノードN2とが差動増幅回路A1の入力ノードに接続されて、フィードバックループが形成される。そのため、ノードN1の電圧Va(第1の電圧)とノードN2の電圧Vbは等しい電圧になるようにフィードバックがかかることになる。より具体的には、差動増幅回路A1には、第1のダイオードDaの特性に依存する電圧Va(第1の電圧)と第2のダイオードDbの特性に依存する電圧Vb(第2の電圧)が入力される。そして、差動増幅回路A1は、電圧Va及び電圧Vbの差分に応じた出力電圧を第1及び第2のPMOSトランジスタM1,M2の各ゲートに供給している。なお、差動増幅回路A1は、電圧Va及び電圧Vbの差分に応じた出力電圧を第3のPMOSトランジスタM3にも供給しており、この第3のPMOSトランジスタM3は第1のPMOSトランジスタM1と同じサイズで形成している。従って、第3のPMOSトランジスタM3から供給する電流は、第1及び第2のPMOSトランジスタM1,M2から供給する電流I1と同じである。

【0043】

また、第2のダイオードDbは、第1のダイオードDaと同じサイズのダイオードをN個並列接続しているため、第2のダイオードDbの順方向電圧は、第1のダイオードDaの順方向電圧に対して、kT/qlogNだけ電圧が小さくなる。

【0044】

この第2のダイオードDbには抵抗素子R1が接続されているので、2つのダイオードDa,Dbの順方向電圧の差分電圧VSは、抵抗素子R1の両端の電圧に等しくなる。すなわち、ノードN1の電圧VaとノードN2の電圧Vbとは上述のように等しい電圧になるため、抵抗素子R1の両端電圧は第1のダイオードDaの順方向電圧から第2のダイオードDbの順方向電圧を減じた電圧VSとなる。

【0045】

さらに、本実施形態の基準電圧発生回路1には、ノードN1と出力ノードN3との間に接続された第4の抵抗素子R3Bと、ノードN2と出力ノードN3との間に接続された第3の抵抗素子R3Aとを備えている。この2つの抵抗素子R3AとR3Bとは同じ抵抗値R3である。

【0046】

上述のように、ノードN1の電圧VaとノードN2の電圧Vbとは等しい電圧であることから、これらの抵抗素子R3A,R3Bにかかる電圧は等しく、等しい電流I3が流れることになる。

【0047】

第1及び第2のダイオードDa,Dbに流れる電流I2は、共に、I1−I3となることから、以下の式(1)で表される関係が導き出せる。但し、熱電圧VT=kT/qである。

R1×(I1−I3)=VTlog(N)・・・(1)

【0048】

電源ノードと接地ノードとの間には、直列に第3のPMOSトランジスタM3と第2の抵抗素子R2とが接続されており、第3のPMOSトランジスタM3から第2の抵抗素子R2へ供給する電流はI1となる。また、第3の抵抗素子R3A,R3Bから第2の抵抗素子R2へ供給する電流はそれぞれ電流I3となる。従って、第2の抵抗素子R2に流れる電流はI1+2I3となり、出力ノードN3の電圧Voutは、以下の式(2)で表すことができる。

Vout=R2×(I1+2I3) ・・・(2)

【0049】

さらに、第3の抵抗素子R3A,R3Bに流れる電流は電流I3であることから、VBEをダイオードDaの順方向電圧とすると、次の関係式が導き出せる。

VBE−Vout=R3×I3 ・・・(3)

【0050】

上記式(1),(2),(3)から、電流I1,I3を消去すると、出力電圧Voutは、以下の式(4)で表すことができる。

Vout=3R2/(R3+3R2){R3/(3R1)*VTlog(N)+VBE} ・・・(4)

【0051】

ここで、式(4)における波括弧{ }中では熱電圧VTとダイオードの順方向電圧VBEとの和を取っている。そして、この和がシリコンのバンドギャップ電圧と等しい電圧になるとき出力電圧Voutが温度依存性を持たなくなる。

【0052】

ここでは、波括弧の外に、3R2/(R3+3R2)が掛かっているので、実際の出力電圧Voutは、シリコンのバンドギャップ電圧よりも低くすることが出来る。

【0053】

しかも、上記特許文献1の技術では、ノードN10,N11に接続する抵抗素子R13A,R13Bを介して無駄な電流をグランドに流していたが、基準電圧発生回路1では、ノードN1,N2に接続する第3及び第4の抵抗素子R3A,R3Bを介して電流をグランドに流さない。すなわち、第3及び第4の抵抗素子R3A,R3Bに流れる電流I3は第2の抵抗素子R2に流れて基準電圧を生成するため用いられる。従って、本実施形態に係る基準電圧発生回路1では、上記特許文献1の技術に比べ消費電力を低減することができる。

【0054】

ここで、基準電圧発生回路1について、実際の設計の際の留意点について説明する。

【0055】

実際の設計においては、PMOSトランジスタM1〜M3が定電流源として動作させることが重要となる。従って、PMOSトランジスタM1〜M3のソース・ドレイン電圧は出来るだけ等しくなるような回路定数を選定する。

【0056】

また、第1のダイオードDaの順方向電圧は、−40℃において、0.82V程度であり、125℃において0.55V程度となる。従って、温度が変化したとき、PMOSトランジスタM1,M2のソース・ドレイン電圧はこの分だけ変化することになる。

【0057】

一方、出力電圧Voutは温度依存性が無い。従って、出力電圧Voutは、0.82Vと0.55Vの中間電圧として 0.7V付近に設定することが望ましい。このとき、3R2/(R3+3R2)を適切に選ぶことで、0.7V付近に設定することが可能である。

【0058】

また、PMOSトランジスタM1〜M3は、飽和状態で動作するよう設計することで、若干のソース・ドレイン電圧の違いがあっても、流れる電流は殆ど変化しないようにできる。

【0059】

このように出力電圧Voutを0.7V付近に設定した場合の最低動作電圧は、低温において第1のダイオードDaの順方向電圧が0.82Vと高くなったとき、PMOSトランジスタM1,M2が電流源として飽和状態で動作できる限界の電圧によって決まる。従って、最悪のケースでも電源電圧が1.0V以上であればこの基準電圧発生回路1は動作することが出来る。

【0060】

次に、図3を参照して、基準電圧発生回路1の変形例について説明する。図3は本発明の一実施形態に係る別の基準電圧発生回路1’の構成を示す図である。

【0061】

図3に示す基準電圧発生回路1’は、第1及び第2のダイオードDa,Dbのサイズを同一サイズとし、第2のPMOSトランジスタM2に流れる電流を第1のPMOSトランジスタM1に流れる電流の1/Nにしたものである。

【0062】

第2のPMOSトランジスタM2に流れる電流を第1のPMOSトランジスタM1に流れる電流の1/Nにするためには、第2のMOSトランジスタM2と同じサイズを持つPMOSトランジスタをN個並列接続したものを第1及び第3のPMOSトランジスタM1,M3とすることで実現できる。

【0063】

基準電圧発生回路1’においても、第2のダイオードDbの順方向電圧は、第1のダイオードDaの順方向電圧よりもkT/qlog(N)だけ小さいことは、基準電圧発生回路1の場合と同じである。これは、第2のPMOSトランジスタM2に流れる電流が第1のPMOSトランジスタM1に流れる電流の1/Nであるからである。

【0064】

また、第4の抵抗素子R3Bの値は抵抗値R3のN倍に設定する。これにより第4の抵抗素子R3Bに流れる電流を第3の抵抗素子R3Aに流れる電流の1/N倍にすることができる。

【0065】

そして、この基準電圧発生回路1’の出力電圧Voutは、以下の式(5)のように表すことができる。

Vout=

{(2N+1)R2}/{NR3+(2N+1)R2}[{N2/(2N+1)R3/R1VTlog (N)+VBE}]

・・・(5)

【0066】

従って、この基準電圧発生回路1’であっても基準電圧発生回路1と同様に高精度の基準電圧を発生させることが出来る。

【0067】

以上、本発明の好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【図面の簡単な説明】

【0068】

【図1】本発明の一実施形態に係る基準電圧発生回路の構成図である。

【図2】本発明の一実施形態に係る基準電圧発生回路の構成図である。

【図3】本発明の一実施形態に係る別の基準電圧発生回路の構成図である。

【図4】従来の基準電圧発生回路の構成を示す図である。

【符号の説明】

【0069】

1,1‘ 基準電圧発生回路

M1 第1のPMOSトランジスタ

M2 第2のPMOSトランジスタ

M3 第3のPMOSトランジスタ

Da 第1のダイオード(第1のPN接合)

Db 第2のダイオード(第2のPN接合)

R1 第1の抵抗素子

R2 第2の抵抗素子

R3A,R3B 第3の抵抗素子

A1 差動増幅回路

【技術分野】

【0001】

本発明は、所望の基準電圧を発生する基準電圧発生回路及びそれを備えた半導体素子に関し、特に、シリコンのバンドギャップ電圧以下の電源電圧で動作する基準電圧発生回路及びそれを備えた半導体素子に関するものである。

【背景技術】

【0002】

半導体チップなどの半導体素子においては、内部回路を適切に動作させるために、その回路内のノードが所望の電圧になるように調整する必要があり、特にアナログ回路においては、その電圧の精度が重要となる。

【0003】

そのため、通常、半導体素子内には、所望の基準電圧を発生する基準電圧発生回路が形成されている。

【0004】

この基準電圧発生回路として、電流密度の異なる2つのダイオードDa,Dbを用いて正の温度依存性を持つ電圧を取り出し、この電圧と負の温度依存性を持つPN接合の順方向電圧とを適切な比率で加算することで、温度に依存しない基準電圧を生成する回路がある。

【0005】

すなわち、電流密度の異なる2つのダイオードDa,Dbの差分電圧VSが正の温度依存性を持ち、ダイオードDa,Dbの順方向電圧VBEが負の温度依存性を持つことから、これらの電圧を適切な比率で加算して温度に依存しない基準電圧を生成するのである。

【0006】

例えば、温度が上がったとき、負の温度依存性を持つ順方向電圧VBEの降下分の電圧をΔVBEとし、正の温度依存性を持つ差分電圧VSの上昇分の電圧ΔVSとすると、適切に比率αを調整することで、ΔVBE+αΔVS=0となる。これにより、温度依存性を持たない高精度の基準電圧を生成することができる。

【0007】

しかしながら、90nm以降の先端プロセスの半導体素子では、電源電圧がバンドギャップ電圧以下の電圧(例えば、1.2V)であるため、上記従来の構成では動作させることができない。

【0008】

そこで、下記特許文献1には、電源電圧がバンドギャップ電圧以下の電圧であっても、高精度の基準電圧を生成することができる基準電圧発生回路が開示されている。

【0009】

特許文献1の基準電圧発生回路は、正の温度依存性を持つ差分電圧VSを電流に変換すると共に、負の温度依存性を持つ順方向電圧VBEを電流に変換し、これらの電流を加算した後に、電圧に変換することで、基準電圧Voutを生成するものである。

【0010】

図4に特許文献1に記載された基準電圧発生回路100の構成を示す。

【0011】

ダイオードDbはダイオードDaよりもエミッター面積がN倍(N>1)となっており、これらに同じ電流I11Aを流したときの順方向電圧の差分電圧VS1は、以下の式(10)のように表すことができる。ここで、kはボルツマン定数、Tは絶対温度、qは電子の電荷量、logは自然対数である。

VS1=kT/qlogN ・・・(10)

【0012】

ダイオードDbには直列に抵抗素子R11が接続されており、2つのノードN10,N11の電圧V10a,V10bの電圧が等しくなるように差動増幅回路A10とPMOSトランジスタM11,M12を用いたフィードバックが掛かっている。

【0013】

このようにノードN10,N11の電圧V10a,V10bが等しくなることから、ダイオードDa,Dbの差分電圧VS1は、抵抗素子R11の両端電圧と同じ電圧となり、ダイオードDa,Dbに流れる電流I11Aは、下記の式(11)のように表すことができる。

I11A=kT/(R11q)logN ・・・(11)

【0014】

従って、ダイオードDa,Dbに流れる電流I11Aは、温度上昇に応じて電流が増加する正の温度依存性を持つ電流であることがわかる。

【0015】

一方、ノードN10,N11と接地ノードとの間には、同じ抵抗値R13を持つ抵抗素子R13A,R13Bがそれぞれ接続されている。これらの抵抗素子R13A,R13Bには、それぞれダイオードDaの順方向電圧VBEと同じ電圧が掛かることから、これら抵抗素子R13A,R13Bに流れる電流I11Bは、以下の式(12)のように表すことができる。

I11B=VBE/R13 ・・・(12)

【0016】

上記式(12)において順方向電圧VBEは、温度上昇に応じて電圧が低下する負の温度依存性を持つ電圧であることから、抵抗素子R13A,R13Bに流れる電流I11Bは負の温度依存性を持つ電流であることがわかる。

【0017】

PMOSトランジスタM11,M12にはこれらの電流の和I10(=I11A+I11B)が流れることになるため、抵抗素子R11,R13A,R13Bの抵抗値を適切に選ぶことによって、これら正と負の温度依存性を持つ電流I11A, I11Bの比率を調整することが出来る。従って、最適な比率で設計すると、温度依存性を持たない電流I10を生成することが出来ることになる。

【0018】

そして、これと同じ電流I10をPMOSトランジスタM13から抵抗素子R12へ流すことで、温度依存性を持たない出力電圧Voutを生成して、出力ノードN12から出力することができる。

【0019】

【特許文献1】特許第3586073号公報

【発明の開示】

【発明が解決しようとする課題】

【0020】

しかしながら、上記特許文献1の技術では、正の温度依存性を持つ電流I11Aを生成するために、抵抗素子R13A,R13Bで余分な電流が消費されることになる。

【0021】

一方、携帯機器などでは、シビアな低消費電力が求められており、できるだけ消費電流を削減することが望まれている。

【0022】

そこで、本発明は、バンドギャップ電圧よりも低い電源電圧で動作し、かつ従来よりも低消費電力である高精度の基準電圧発生回路を提供することを目的とする。

【課題を解決するための手段】

【0023】

上記目的を達成するために、請求項1に記載の発明は、電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、さらに、前記第1のPMOSトランジスタのドレインと前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えたものである。

【0024】

また、請求項2に記載の発明は、請求項1に記載の発明において、前記第1の電圧は、前記第1のPMOSトランジスタと前記第1のPN接合との接続点に発生する電圧とし、前記第2の電圧は、前記第2のPMOSトランジスタと前記第1の抵抗素子との接続点に発生する電圧とした。

【0025】

また、請求項3に記載の発明は、請求項1又は請求項2に記載の発明において、前記第2のPN接合を、並列に接続された複数個のPN接合から構成した。

【0026】

また、請求項4に記載の発明は、請求項1又は請求項2に記載の発明において、前記第2のPMOSトランジスタを、並列に接続された複数個のPMOSトランジスタから構成し、前記第4の抵抗素子の抵抗値を前記第3の抵抗素子の抵抗値のN倍にし、前記第1のPN接合を前記第1のPN接合と同一サイズで形成した。

【0027】

また、請求項5に記載の発明は、所定の基準電圧を発生する基準電圧発生回路を内部に備え、前記基準電圧発生回路は、電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、さらに、前記第1のPMOSトランジスタのドレインと前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えたものである。

【発明の効果】

【0028】

本発明によれば、バンドギャップ電圧よりも低い電源電圧で動作し、かつ従来よりも低消費電力である高精度の基準電圧発生回路を提供することができる。

【発明を実施するための最良の形態】

【0029】

本発明の一実施形態に係る半導体素子は、バンドギャップ電圧よりも低い電源電圧で動作し、低消費電力かつ高精度の基準電圧発生回路を備えている。

【0030】

この基準電圧発生回路は、電流密度の異なる第1のダイオードと第2のダイオードの差分電圧が正の温度依存性を持ち、第1及び第2のダイオードの順方向電圧VBEが負の温度依存性を持つことから、これらを利用して高精度の基準電圧を生成するものである。

【0031】

そして、バンドギャップ電圧よりも低い電源電圧で動作させるために、正の温度依存性を持つ差分電圧と負の温度依存性を持つ順方向電圧との加算を直接行わずに、一旦電流に変換し、電流で加算を行った後に電圧に変換して基準電圧を生成している。

【0032】

すなわち、第1のダイオードと、直列に接続した第2のダイオード及び第1の抵抗素子とに同じ電圧が掛かるように差動増幅回路でフィードバックをかけ、正の温度依存性を持つ差分電圧を第1のダイオード又は第2のダイオードに流れる第1電流に変換する。

【0033】

また、第1のダイオードに第3の抵抗素子を接続し、第2のダイオードに第4抵抗素子を接続して、正の温度依存性を持つ順方向電圧を第3及び第4の抵抗素子に流れる第2電流に変換する。

【0034】

第1の電流は正の温度依存性を持つ電流となり、第2の電流は負の温度依存性を持つ電流となるため、これらを加算することにより温度依存性を持たない第3の電流を得ることができる。そして、この第3の電流を第2の抵抗素子に流すことにより温度依存性を持たない電圧を生成している。

【0035】

さらに、本実施形態に係る基準電圧発生回路では、基準電圧を出力する出力ノードに第3及び第4の抵抗素子を接続するようにしている。

【0036】

上記特許文献1の技術では、第3及び第4抵抗素子である抵抗素子R13B,R13Aを接地ノードに接続するようにしていたため、消費電力が無駄になっていたが、本実施形態に係る基準電圧発生回路では、第3及び第4抵抗素子に流れる電流を第2の抵抗素子に流して基準電圧を生成するために用いている。

【0037】

従って、消費電力を抑制することができ、携帯機器などのようにシビアな低消費電力が求められる機器に適用して低消費電力を図ることができる。

【0038】

以下、本発明の一実施形態に係る半導体素子内に形成された基準電圧発生回路について図面を参照して具体的に説明する。図1及び図2は本発明の一実施形態に係る基準電圧発生回路の構成図である。

【0039】

基準電圧発生回路1は、第1〜第3のPMOSトランジスタM1〜M3、第1及び第2のダイオードDa,Db(第1のPN接合及び第2のPN接合の一例)、第1〜第4の抵抗素子R1,R2,R3B,R3A、差動増幅回路A1とから構成される。

【0040】

図1に示すように、第1のPMOSトランジスタM1と第1のダイオードDaは直列に電源ノードと接地ノードに接続され、第2のPMOSトランジスタM2、第2のダイオードDb及び第1の抵抗素子R1は電源ノードと接地ノードとの間に直列に接続されている。なお、第2のダイオードDb及び第1の抵抗素子R1の配置は第1の抵抗素子R1を接地するのに限られず、図2に示すように第2のダイオードDbを接地するように配置してもよい。

【0041】

また、第1及び第2のPMOSトランジスタM1,M2は、同一サイズで形成され、共に差動増幅回路A1の出力電圧が入力されている。そのため、第1及び第2のPMOSトランジスタM1,M2は電流源として、第1のダイオードDa及び第2のダイオードDbに等しい電流I2を供給することになる。

【0042】

また、第1のPMOSトランジスタM1のドレインと第1のダイオードDaとが接続されるノードN1と、第2のPMOSトランジスタM2のドレインと第2のダイオードDbとが接続されるノードN2とが差動増幅回路A1の入力ノードに接続されて、フィードバックループが形成される。そのため、ノードN1の電圧Va(第1の電圧)とノードN2の電圧Vbは等しい電圧になるようにフィードバックがかかることになる。より具体的には、差動増幅回路A1には、第1のダイオードDaの特性に依存する電圧Va(第1の電圧)と第2のダイオードDbの特性に依存する電圧Vb(第2の電圧)が入力される。そして、差動増幅回路A1は、電圧Va及び電圧Vbの差分に応じた出力電圧を第1及び第2のPMOSトランジスタM1,M2の各ゲートに供給している。なお、差動増幅回路A1は、電圧Va及び電圧Vbの差分に応じた出力電圧を第3のPMOSトランジスタM3にも供給しており、この第3のPMOSトランジスタM3は第1のPMOSトランジスタM1と同じサイズで形成している。従って、第3のPMOSトランジスタM3から供給する電流は、第1及び第2のPMOSトランジスタM1,M2から供給する電流I1と同じである。

【0043】

また、第2のダイオードDbは、第1のダイオードDaと同じサイズのダイオードをN個並列接続しているため、第2のダイオードDbの順方向電圧は、第1のダイオードDaの順方向電圧に対して、kT/qlogNだけ電圧が小さくなる。

【0044】

この第2のダイオードDbには抵抗素子R1が接続されているので、2つのダイオードDa,Dbの順方向電圧の差分電圧VSは、抵抗素子R1の両端の電圧に等しくなる。すなわち、ノードN1の電圧VaとノードN2の電圧Vbとは上述のように等しい電圧になるため、抵抗素子R1の両端電圧は第1のダイオードDaの順方向電圧から第2のダイオードDbの順方向電圧を減じた電圧VSとなる。

【0045】

さらに、本実施形態の基準電圧発生回路1には、ノードN1と出力ノードN3との間に接続された第4の抵抗素子R3Bと、ノードN2と出力ノードN3との間に接続された第3の抵抗素子R3Aとを備えている。この2つの抵抗素子R3AとR3Bとは同じ抵抗値R3である。

【0046】

上述のように、ノードN1の電圧VaとノードN2の電圧Vbとは等しい電圧であることから、これらの抵抗素子R3A,R3Bにかかる電圧は等しく、等しい電流I3が流れることになる。

【0047】

第1及び第2のダイオードDa,Dbに流れる電流I2は、共に、I1−I3となることから、以下の式(1)で表される関係が導き出せる。但し、熱電圧VT=kT/qである。

R1×(I1−I3)=VTlog(N)・・・(1)

【0048】

電源ノードと接地ノードとの間には、直列に第3のPMOSトランジスタM3と第2の抵抗素子R2とが接続されており、第3のPMOSトランジスタM3から第2の抵抗素子R2へ供給する電流はI1となる。また、第3の抵抗素子R3A,R3Bから第2の抵抗素子R2へ供給する電流はそれぞれ電流I3となる。従って、第2の抵抗素子R2に流れる電流はI1+2I3となり、出力ノードN3の電圧Voutは、以下の式(2)で表すことができる。

Vout=R2×(I1+2I3) ・・・(2)

【0049】

さらに、第3の抵抗素子R3A,R3Bに流れる電流は電流I3であることから、VBEをダイオードDaの順方向電圧とすると、次の関係式が導き出せる。

VBE−Vout=R3×I3 ・・・(3)

【0050】

上記式(1),(2),(3)から、電流I1,I3を消去すると、出力電圧Voutは、以下の式(4)で表すことができる。

Vout=3R2/(R3+3R2){R3/(3R1)*VTlog(N)+VBE} ・・・(4)

【0051】

ここで、式(4)における波括弧{ }中では熱電圧VTとダイオードの順方向電圧VBEとの和を取っている。そして、この和がシリコンのバンドギャップ電圧と等しい電圧になるとき出力電圧Voutが温度依存性を持たなくなる。

【0052】

ここでは、波括弧の外に、3R2/(R3+3R2)が掛かっているので、実際の出力電圧Voutは、シリコンのバンドギャップ電圧よりも低くすることが出来る。

【0053】

しかも、上記特許文献1の技術では、ノードN10,N11に接続する抵抗素子R13A,R13Bを介して無駄な電流をグランドに流していたが、基準電圧発生回路1では、ノードN1,N2に接続する第3及び第4の抵抗素子R3A,R3Bを介して電流をグランドに流さない。すなわち、第3及び第4の抵抗素子R3A,R3Bに流れる電流I3は第2の抵抗素子R2に流れて基準電圧を生成するため用いられる。従って、本実施形態に係る基準電圧発生回路1では、上記特許文献1の技術に比べ消費電力を低減することができる。

【0054】

ここで、基準電圧発生回路1について、実際の設計の際の留意点について説明する。

【0055】

実際の設計においては、PMOSトランジスタM1〜M3が定電流源として動作させることが重要となる。従って、PMOSトランジスタM1〜M3のソース・ドレイン電圧は出来るだけ等しくなるような回路定数を選定する。

【0056】

また、第1のダイオードDaの順方向電圧は、−40℃において、0.82V程度であり、125℃において0.55V程度となる。従って、温度が変化したとき、PMOSトランジスタM1,M2のソース・ドレイン電圧はこの分だけ変化することになる。

【0057】

一方、出力電圧Voutは温度依存性が無い。従って、出力電圧Voutは、0.82Vと0.55Vの中間電圧として 0.7V付近に設定することが望ましい。このとき、3R2/(R3+3R2)を適切に選ぶことで、0.7V付近に設定することが可能である。

【0058】

また、PMOSトランジスタM1〜M3は、飽和状態で動作するよう設計することで、若干のソース・ドレイン電圧の違いがあっても、流れる電流は殆ど変化しないようにできる。

【0059】

このように出力電圧Voutを0.7V付近に設定した場合の最低動作電圧は、低温において第1のダイオードDaの順方向電圧が0.82Vと高くなったとき、PMOSトランジスタM1,M2が電流源として飽和状態で動作できる限界の電圧によって決まる。従って、最悪のケースでも電源電圧が1.0V以上であればこの基準電圧発生回路1は動作することが出来る。

【0060】

次に、図3を参照して、基準電圧発生回路1の変形例について説明する。図3は本発明の一実施形態に係る別の基準電圧発生回路1’の構成を示す図である。

【0061】

図3に示す基準電圧発生回路1’は、第1及び第2のダイオードDa,Dbのサイズを同一サイズとし、第2のPMOSトランジスタM2に流れる電流を第1のPMOSトランジスタM1に流れる電流の1/Nにしたものである。

【0062】

第2のPMOSトランジスタM2に流れる電流を第1のPMOSトランジスタM1に流れる電流の1/Nにするためには、第2のMOSトランジスタM2と同じサイズを持つPMOSトランジスタをN個並列接続したものを第1及び第3のPMOSトランジスタM1,M3とすることで実現できる。

【0063】

基準電圧発生回路1’においても、第2のダイオードDbの順方向電圧は、第1のダイオードDaの順方向電圧よりもkT/qlog(N)だけ小さいことは、基準電圧発生回路1の場合と同じである。これは、第2のPMOSトランジスタM2に流れる電流が第1のPMOSトランジスタM1に流れる電流の1/Nであるからである。

【0064】

また、第4の抵抗素子R3Bの値は抵抗値R3のN倍に設定する。これにより第4の抵抗素子R3Bに流れる電流を第3の抵抗素子R3Aに流れる電流の1/N倍にすることができる。

【0065】

そして、この基準電圧発生回路1’の出力電圧Voutは、以下の式(5)のように表すことができる。

Vout=

{(2N+1)R2}/{NR3+(2N+1)R2}[{N2/(2N+1)R3/R1VTlog (N)+VBE}]

・・・(5)

【0066】

従って、この基準電圧発生回路1’であっても基準電圧発生回路1と同様に高精度の基準電圧を発生させることが出来る。

【0067】

以上、本発明の好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【図面の簡単な説明】

【0068】

【図1】本発明の一実施形態に係る基準電圧発生回路の構成図である。

【図2】本発明の一実施形態に係る基準電圧発生回路の構成図である。

【図3】本発明の一実施形態に係る別の基準電圧発生回路の構成図である。

【図4】従来の基準電圧発生回路の構成を示す図である。

【符号の説明】

【0069】

1,1‘ 基準電圧発生回路

M1 第1のPMOSトランジスタ

M2 第2のPMOSトランジスタ

M3 第3のPMOSトランジスタ

Da 第1のダイオード(第1のPN接合)

Db 第2のダイオード(第2のPN接合)

R1 第1の抵抗素子

R2 第2の抵抗素子

R3A,R3B 第3の抵抗素子

A1 差動増幅回路

【特許請求の範囲】

【請求項1】

電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、

前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、

さらに、前記第1のPMOSトランジスタのドレインと、前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、

前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えた基準電圧発生回路。

【請求項2】

前記第1の電圧は、前記第1のPMOSトランジスタと前記第1のPN接合との接続点に発生する電圧であり、前記第2の電圧は、前記第2のPMOSトランジスタと前記第1の抵抗素子との接続点に発生する電圧であることを特徴とする請求項1記載の基準電圧発生回路。

【請求項3】

前記第2のPN接合を、並列に接続された複数個のPN接合から構成した請求項1又は請求項2に記載の基準電圧発生回路。

【請求項4】

前記第2のPMOSトランジスタを、並列に接続された複数個のPMOSトランジスタから構成し、

前記第4の抵抗素子の抵抗値を前記第3の抵抗素子の抵抗値のN倍にし、

前記第1のPN接合を前記第1のPN接合と同一サイズで形成した請求項1又は請求項2に記載の基準電圧発生回路。

【請求項5】

所定の基準電圧を発生する基準電圧発生回路を内部に備え、

前記基準電圧発生回路は、

電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、

前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、

さらに、前記第1のPMOSトランジスタのドレインと、前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、

前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えた半導体素子。

【請求項1】

電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、

前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、

さらに、前記第1のPMOSトランジスタのドレインと、前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、

前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えた基準電圧発生回路。

【請求項2】

前記第1の電圧は、前記第1のPMOSトランジスタと前記第1のPN接合との接続点に発生する電圧であり、前記第2の電圧は、前記第2のPMOSトランジスタと前記第1の抵抗素子との接続点に発生する電圧であることを特徴とする請求項1記載の基準電圧発生回路。

【請求項3】

前記第2のPN接合を、並列に接続された複数個のPN接合から構成した請求項1又は請求項2に記載の基準電圧発生回路。

【請求項4】

前記第2のPMOSトランジスタを、並列に接続された複数個のPMOSトランジスタから構成し、

前記第4の抵抗素子の抵抗値を前記第3の抵抗素子の抵抗値のN倍にし、

前記第1のPN接合を前記第1のPN接合と同一サイズで形成した請求項1又は請求項2に記載の基準電圧発生回路。

【請求項5】

所定の基準電圧を発生する基準電圧発生回路を内部に備え、

前記基準電圧発生回路は、

電源ノードと接地ノードとの間に直列に接続された第1のPMOSトランジスタ及び第1のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第2のPMOSトランジスタ、第1の抵抗素子及び第2のPN接合と、

電源ノードと接地ノードとの間に直列に接続された第3のPMOSトランジスタ及び第2の抵抗素子と、

前記第1のPN接合の特性に依存する第1の電圧及び前記第2のPN接合の特性に依存する第2の電圧が入力され、前記第1の電圧及び前記第2の電圧の差分に応じた出力電圧を前記第1、第2及び第3のPMOSトランジスタの各ゲートに供給する差動増幅回路と、を備え、

さらに、前記第1のPMOSトランジスタのドレインと、前記第3のPMOSトランジスタと前記第2の抵抗素子との間の出力ノードとの間に接続された第3の抵抗素子と、

前記第2のPMOSトランジスタのドレインと前記出力ノードとの間に接続された第4の抵抗素子とを備えた半導体素子。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−39648(P2010−39648A)

【公開日】平成22年2月18日(2010.2.18)

【国際特許分類】

【出願番号】特願2008−200228(P2008−200228)

【出願日】平成20年8月1日(2008.8.1)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成22年2月18日(2010.2.18)

【国際特許分類】

【出願日】平成20年8月1日(2008.8.1)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]