基準電圧発生回路

【課題】雑音を低減するローパスフィルタの容量を高速で充電して、高速に出力電圧を整定することが可能な基準電圧発生回路を提供する。

【解決手段】基準となる直流電圧を発生する基準電圧源1と、基準電圧源の出力に接続されたローパスフィルタ2と、基準電圧源の出力が入力端子に接続されローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路10と、基準電圧源の出力が一方の入力端子に接続されローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータ11とを備える。起動時に基準電圧源の出力とローパスフィルタの出力の電圧差が所定値を超えている期間は、ヒステリシスコンパレータの出力信号により第1電圧バッファ回路の出力インピーダンスが制御される。起動時にローパスフィルタを低インピーダンスで急速に充電することにより、整定の時間を早めることができる。

【解決手段】基準となる直流電圧を発生する基準電圧源1と、基準電圧源の出力に接続されたローパスフィルタ2と、基準電圧源の出力が入力端子に接続されローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路10と、基準電圧源の出力が一方の入力端子に接続されローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータ11とを備える。起動時に基準電圧源の出力とローパスフィルタの出力の電圧差が所定値を超えている期間は、ヒステリシスコンパレータの出力信号により第1電圧バッファ回路の出力インピーダンスが制御される。起動時にローパスフィルタを低インピーダンスで急速に充電することにより、整定の時間を早めることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基準電圧の雑音を低減させるローパスフィルタの容量を高速で充電して、出力電圧を高速に整定する基準電圧発生回路に関するものである。

【背景技術】

【0002】

基準電圧源の雑音を低減させるために基準電圧源の後段にローパスフィルタを追加する構成が、例えば特許文献1に開示されている(第1従来例)。この第1従来例の回路を図7に示す。図7の構成は、基準電圧源1の電圧が出力されるA点に、抵抗Rと容量Cからなるローパスフィルタ2を接続して、B点に出力される電圧の雑音を低減するものである。なお、一般的な構成として、B点の電圧は、オペアンプ3を用いた非反転増幅器で増幅され、出力トランジスタ4により出力端子5から出力電圧Voutとして出力される。

【0003】

この構成では、ローパスフィルタ2の時定数RCが一般的に、基準電圧源1やオペアンプ3を構成するトランジスタなどの時定数よりも大きい。そのため、電源を投入してから出力電圧Voutが定常状態に整定するまでには、時定数RCで対数的に立ち上がるための相当な時間を要する。図9に、出力電圧Voutが整定するまでの波形を示す。横軸が時間、縦軸が出力電圧Voutである。第1従来例の出力波形P1の場合、出力電圧Voutが整定するまでに相当な時間を要することが判る。

【0004】

この問題を解決するため、電圧をモニタしてローパスフィルタを高速に充電する構成が、例えば特許文献2に開示されている(第2従来例)。この第2従来例の回路を図8に示す。図8の構成では、抵抗Rと容量Cからなるローパスフィルタの出力点であるB点が、ステリシスコンパレータ6の一方の入力端子に接続されている。ステリシスコンパレータ6の他方の入力端子は、基準電圧源1の電圧が出力されるA点に接続されている。B点は、スイッチSW1を介して電源Vddに接続され、また、容量CのB点側の端子は、スイッチSW2を介して接地側の端子と接続される。

【0005】

この回路の動作は、次のとおりである。まず、電源投入直後に基準電圧源1からA点に出力される電圧は、直ちに一定電圧まで立ち上がる。一方、B点の電圧は、ローパスフィルタの容量Cのために時定数RCでゆっくり対数的に立ち上がろうとする。このとき、A点の電圧とB点の電圧とをヒステリシスコンパレータ6で比較して、設定した一定電圧以上の電圧差が発生しているときに、B点と電源VddとをスイッチSW1で短絡する。それにより、B点に接続されているローパスフィルタの容量Cが高速に充電される。

【0006】

この結果、図9に示す第2従来例の出力波形P2のように、スイッチSW1の短絡時等価抵抗と容量Cの乗算した値を時定数として、急速に出力電圧Voutが立ち上がる。ローパスフィルタのRに比較してスイッチSW1の短絡時等価抵抗は非常に小さいため、定常状態になるまでの整定時間が短縮される。なお、A点とB点の電位差が設定電圧未満になった時点でスイッチSW1が開放され、以後B点の電圧はローパスフィルタの時定数RCで上昇してA点の電圧に漸近する。

【0007】

なお、スイッチSW2は、出力電圧Voutの立下り時に、容量Cに蓄積された電荷を強制的に放電させるために用いられる。これにより、出力電圧Voutを急速に降下させて、消費電流を削減する。

【0008】

上記構成以外にも、特許文献3に開示された、基準電圧源の内部電圧の非平衡をコンパレータで検出して容量を充電する構成や、特許文献4に開示された、ローパスフィルタの時定数を小から大へ切り替える構成により、出力電圧Voutが整定するまでの時間を短縮することが知られている。

【特許文献1】特開平8-272461号公報

【特許文献2】特開2002-23870号公報

【特許文献3】特開2005-346522号公報

【特許文献4】特開平6-301429号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら上記第2従来例では、A点とB点の電圧差がヒステリシスコンパレータ6の設定値に達すると、スイッチSW1による急速充電が停止するため、定常状態の電圧に達するまでは、ローパスフィルタの時定数RCを介して充電が行われる。従って、設定値に達してから定常状態に達するまでさらに時間がかかる。

【0010】

第2従来例の方法によれば、時定数が十分小さくなくとも、ヒステリシスコンパレータ6の設定値を小さくすることにより、整定時間をいくらでも短くできるように見えるが、実際にはそうではない。すなわち、ヒステリシスコンパレータ6のオフセット電圧を0にするのが困難であるため、設定値の前後に入力電圧差がずれてしまう。

【0011】

またそのオフセット電圧を校正や補正により0にできても、ヒステリシスコンパレータ6の応答性が有限であるため、結果としてスイッチのオフが遅れてしまい、電源電圧側に過剰に電圧印加されて出力電圧Voutがオーバーシュートしてしまう。

【0012】

さらに、スイッチSW1がMOSなどの半導体素子であれば、オフ時にチャネルに蓄積された電荷が放電するチャージ・インジェクション効果があることにより、オフ後にも短時間ではあるが電流がローパスフィルタの容量に流れ込み、さらに電圧が過剰になる。出力電圧Voutが、定常状態の電圧に対して不足であっても過剰であっても、時定数RCで漸近する動作が発生するため、整定が遅くなる。

【0013】

近年の携帯通信機器などバッテリ駆動の装置は、高出力駆動とバッテリの長時間寿命を同時に達成するために、電力を細かに制御する。それにともない、電源投入後直ちに所定の基準電圧を発生しなければならないが、従来の方法では十分に対応することが困難であった。

【0014】

本発明は上記問題を解決するものであり、雑音を低減するローパスフィルタの容量を高速で充電して、高速に出力電圧を整定することが可能な基準電圧発生回路を提供することを目的とする。

【発明の効果】

【0015】

上記構成の基準電圧発生回路によれば、電源の投入直後の所定期間は、第1電圧バッファ回路あるいはスイッチ素子を介してローパスフィルタの容量Cが急速に充電される。そのため、基準電圧源の雑音および外乱を低減でき、かつ、電源起動時に短時間で正確な基準電圧に到達することができる。

【課題を解決するための手段】

【0016】

上記課題を解決するために、本発明の第1の構成の基準電圧発生回路は、基準となる直流電圧を発生する基準電圧源と、前記基準電圧源の出力に接続されたローパスフィルタと、前記基準電圧源の出力が入力端子に接続され前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路と、前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記ヒステリシスコンパレータの出力信号により前記第1電圧バッファ回路の出力インピーダンスが制御されることを特徴とする。

【0017】

本発明の第2の構成の基準電圧発生回路は、基準となる直流電圧を発生する基準電圧源と、前記基準電圧源の出力に接続されたローパスフィルタと、前記ローパスフィルタの出力をインピーダンス変換して出力する電圧バッファ回路と、前記ローパスフィルタの出力と前記電圧バッファ回路の入力端子の間に挿入された第1スイッチ素子と、前記ローパスフィルタの出力と前記電圧バッファ回路の出力端子との間に挿入された第2スイッチ素子と、前記基準電圧源の出力と前記電圧バッファ回路の入力端子の間に挿入された第3スイッチ素子と、前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタ出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、前記ヒステリシスコンパレータの出力信号により前記第1〜第3スイッチ素子が制御されて、前記第1スイッチ素子がオンで前記第2および第3スイッチ素子がオフの状態と、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態とが切替えられることを特徴とする。

【0018】

本発明の第3の構成の基準電圧発生回路は、基準となる直流電圧を発生する基準電圧源と、前記基準電圧源の出力に接続されたローパスフィルタと、前記基準電圧源の出力が入力端子に接続され、前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路とを備え、外部信号により前記第1電圧バッファ回路の出力インピーダンスが制御されることを特徴とする。

【発明を実施するための最良の形態】

【0019】

本発明は、上記構成を基本として、以下のような態様をとることができる。

【0020】

すなわち、第1の構成において、前記ヒステリシスコンパレータの出力信号を一定期間遅延させた信号で前記第1電圧バッファ回路の出力インピーダンスが制御されることが好ましい。

【0021】

また、前記ローパスフィルタの出力が第2電圧バッファを介して出力されることが好ましい。

【0022】

第2の構成において、起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態に制御される構成とすることができる。

【0023】

以下、本発明の実施形態における基準電圧発生回路について、図面を参照しながら説明する。

【0024】

(第1の実施形態)

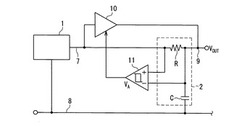

図1は、本発明の第1の実施形態に係る基準電圧発生回路の構成図である。基準となる直流電圧を発生する基準電圧源1からの出力ノード7には、ローパスフィルタ2が接続されている。ローパスフィルタ2は、出力ノード7と基準電圧源1の接地端子8との間に直列接続された抵抗Rと容量Cから構成された、ローパスフィルタの最も単純な形態であるRC一次フィルタである。抵抗Rと容量Cの接続点は、ローパスフィルタ2からの出力ノード9であって、基準電圧源1の出力電圧を平滑した電圧が発生する。それにより、基準電圧源1が発生する雑音や基準電圧源1への外乱の影響が低減される。

【0025】

基準電圧源1の出力ノード7にはさらに、第1電圧バッファ回路10の入力端子が接続されている。第1電圧バッファ回路10の出力端子は、ローパスフィルタ2の出力ノード9に接続されている。第1電圧バッファ回路10は、出力インピーダンスが高出力インピーダンスの状態と低出力インピーダンスの状態の2状態に切り替えられる。低出力インピーダンス状態のときには、出力電圧と入力電圧の比、すなわち電圧ゲインが1倍である。

【0026】

第1電圧バッファ回路10の制御端子には、ヒステリシスコンパレータ11の出力VAが入力される。ヒステリシスコンパレータ11の一方の入力端子には、基準電圧源1の出力である出力ノード7の電圧が入力され、他方の入力端子には、ローパスフィルタ2の出力である出力ノード9の電圧Voutが入力される。

【0027】

なお、基準電圧源1は定常状態で一定の電圧を発生し、代表的な基準電圧源としては、半導体素子のバンドギャップ電圧を利用したものを用いることができる。また、ローパスフィルタは用途により様々なものがあり、本実施形態の構成に限定されることはない。機能としては、ローパスフィルタ2の入力と出力ノード9との間で、電圧の交流成分が平滑化されて出力されればよい。出力ノード9には、通常、さらに誤差増幅器や電圧バッファや電圧コンパレータなどの高出力インピーダンス回路が接続され使用されるが、本発明の本質とは関係ないので、図示は省略する。

【0028】

次に、上記構成の回路の動作について説明する。第1電圧バッファ回路10の高出力インピーダンス状態においては、ローパスフィルタ2の出力ノード9には、基準電圧源1の出力ノード7の電圧が平滑されて出力される。

【0029】

一方、第1電圧バッファ回路10の低出力インピーダンス状態においては、基準電圧源1の出力ノード7の電圧が第1電圧バッファ回路10を介して出力ノード9に供給される。第1電圧バッファ回路10の出力インピーダンスを、出力ノード9から見たローパスフィルタ2の入力インピーダンスに対して十分に小さく設定することにより、このとき、ローパスフィルタ2の容量Cが急速に充電される。それにより、ローパスフィルタ2の出力ノード9の電圧は、高速に基準電圧源1の出力ノード7の電圧に漸近させられる。

【0030】

第1電圧バッファ回路10の出力インピーダンスは、基準電圧源1の出力ノード7とローパスフィルタ2の出力ノード9の電圧に基づき、ヒステリシスコンパレータ11の出力VAで次のように制御される。

【0031】

基準電圧源1の電源が投入されたときの動作は、次のとおりである。まず、図1において、基準電圧源1の電源を遮断している状態、あるいは外部よりバイアス電流を遮断している状態では、基準電圧源1の出力ノード7の電圧は、定常状態の電圧と接地端子8の電位との間の初期電圧、通常は接地端子8と同電位になっている。この状態より、基準電圧源1の遮断を解除する。この動作は、基準電圧源の起動と呼ばれる。起動により、基準電圧源1の応答性が十分に早いときは、出力ノード7は直ちに定常状態になると考えて良い。一方、ローパスフィルタ2は、構成するパラメータと構造により固有の時定数を持ち、出力ノード9の電圧は直ちには上昇できない。その結果、出力ノード9と出力ノード7の間に電圧差が発生する。

【0032】

この電圧差がヒステリシスコンパレータ11の第1設定値よりも大きければ、第1電圧バッファ回路10の出力インピーダンスは、低インピーダンス状態に制御される。それにより、出力ノード7の定常状態の電圧を目標値としてローパスフィルタ2を低インピーダンスで充電するように動作する。その結果、図9の出力波形Eに示すように、高速に出力ノード9の電圧が立ち上がる。

【0033】

出力ノード9と出力ノード7との間の電圧差がヒステリシスコンパレータ11の第2設定値に達すると、第1電圧バッファ回路10の出力インピーダンスは、高インピーダンス状態に制御される。それにより、第1電圧バッファ回路10の出力からローパスフィルタ2への充電電流が遮断される。この時点より、ローパスフィルタ2の出力ノード9の電圧は、ローパスフィルタ2の固有の時定数で基準電圧源1の出力ノード7の定常状態の電圧値に漸近する。図1に示すRC一次フィルタにより構成されたローパスフィルタ2の時定数は、抵抗Rと容量Cの抵抗値と容量値の積である。

【0034】

ローパスフィルタ2の出力ノード9の電圧が、ローパスフィルタ2の固有の時定数で基準電圧源1の出力ノード7の定常状態の電圧値に漸近している間、および定常状態では、出力ノード9と出力ノード7との間の電圧差は、ヒステリシスコンパレータ11の第2設定値よりも小さくなる。そのため、その間中、ヒステリシスコンパレータ11の出力VAは、第1電圧バッファ回路10の出力インピーダンスを高インピーダンス状態に維持する値となる。このとき、ローパスフィルタ2は基準電圧源1の出力ノード7の電圧を平滑し、基準電圧源1が発生する雑音や基準電圧源1への外乱の影響を低減して出力ノード9に出力する。

【0035】

本実施形態の構成を採ることにより、ヒステリシスコンパレータ11の第2設定値を十分に小さくすれば、ヒステリシスコンパレータ11のオフセット電圧や応答の遅れ、あるいは第1電圧バッファ回路10の応答の遅れがあっても、従来例と異なり電源電圧側への過剰な電圧印加を十分に抑制できるため、高速に定常状態に達することができる。

【0036】

なお、ローパスフィルタ2の出力ノード9の電圧がヒステリシスコンパレータ11の第2設定値を横切るとき、第1電圧バッファ回路10の発生する雑音あるいは第1電圧バッファ回路10への外乱により、出力ノード9の電圧がチャタリングを起こし、第1電圧バッファ回路10の動作が不安定になる場合がある。これを防止してチャタリングを発生させないように、ヒステリシスコンパレータ11の第1設定値を第2設定値よりも十分大きな値に設定する。しかし、第1電圧バッファ回路10の応答性がチャタリングの周期より十分遅い場合や、雑音と外乱が十分小さくチャタリングが発生しないのであれば、ヒステリシスコンパレータ11の第1設定値を第2設定値と同一にすることができるため、ヒステリシスのないコンパレータで代用しても良い。

【0037】

(第2の実施形態)

図2は、本発明の第2の実施形態に係る基準電圧発生回路の構成図である。この基準電圧発生回路は、図1に示した第1の実施形態の基準電圧発生回路におけるヒステリシスコンパレータ11の出力VAを、遅延回路12を介して第1電圧バッファ回路10に入力する構成となっている。遅延回路12により一定期間遅延された制御信号VBにより、第1電圧バッファ回路10が制御される。

【0038】

第1の実施形態では、第1電圧バッファ回路10の出力インピーダンスを高インピーダンス状態に切り替えてから、出力ノード9の電圧が定常状態に達するまでの時間は、ローパスフィルタ2の時定数によって決まる。定常状態に達する時間は、ヒステリシスコンパレータ11の第2設定値を小さくすればするほど短縮される。ところが、第2設定値をヒステリシスコンパレータ11のオフセット電圧値よりも小さくすると、出力ノード9の電圧が定常状態の値に達してもヒステリシスコンパレータ11が切り替わらず、第1電圧バッファ回路10の出力インピーダンスを低インピーダンス状態に維持する。このため、基準電圧源1と第1電圧バッファ回路10の雑音と外乱が加算されて、出力ノード9に現れてしまう。

【0039】

これに対し、第2の実施形態においては遅延回路12の挿入により、第1電圧バッファ回路10への制御信号VBの入力が、ヒステリシスコンパレータ11の出力VAより一定期間遅延される。これにより、出力ノード9の電圧値が、ヒステリシスコンパレータ11のオフセット電圧値以上に設定された第2設定値に達しても、遅延回路12により設定された一定期間後までは、第1電圧バッファ回路10の出力インピーダンスは低インピーダンス状態に保たれる。

【0040】

この遅延期間を、定常状態に達する予想時間の近傍あるいはそれ以上の時間で、かつ、遅延回路12を挿入しない場合に定常状態に達する時間よりも短い時間に設定すればよい。通常、遅延回路12を挿入しない場合に定常状態に達する時間よりも比較的短く遅延期間を設定できる。

【0041】

なお、第1電圧バッファ回路10の応答の遅れによりたとえ電圧がオーバーシュートしても、減衰を見込んだ期間を設定することにより、影響を受けないようにできる。

【0042】

なお、遅延回路12の代わりに、ヒステリシスコンパレータ11に容量を内蔵するなどして、ヒステリシスコンパレータ11自体に遅延作用を持たせても良い。

【0043】

(第3の実施形態)

図3は、第3の実施形態に係る基準電圧発生回路の構成図である。本実施形態では、図2の基準電圧発生回路のローパスフィルタ2の出力ノード9に、第2電圧バッファ回路13の入力端子に接続し、第2電圧バッファ回路13の出力を基準電圧発生回路の出力端子14としたものである。

【0044】

このような構成とすることにより、本実施形態に係る基準電圧発生回路によれば、出力端子14に低出力インピーダンスで出力することができる。多くの負荷は抵抗性または容量性であり、ローパスフィルタ2の出力インピーダンスでは十分に駆動できない場合がある。これに対して、第2電圧バッファ回路13でインピーダンス変換を行うことにより、そのような問題を解消することができる。

【0045】

なお、出力電圧値の変換が必要な場合には、出力電圧を抵抗分割してから演算増幅器に帰還して使う反転増幅回路あるいは非反転増幅回路を、第2電圧バッファ回路13の代わりに用いても良い。

【0046】

(第4の実施形態)

図4は、第4の実施形態に係る基準電圧発生回路の構成図である。本実施形態は、図3に示した第3の実施形態に係る基準電圧発生回路の構成において、第2電圧バッファ回路13で第1電圧バッファ回路10(本実施の形態では電圧バッファ回路15)を兼用した構成を特徴とする。

【0047】

そのために、接続切り替え用の第1〜第3スイッチ素子16〜18を設ける。同時に、図3の第1電圧バッファ回路10の出力インピーダンスを切り替えることに代えて、第1〜第3スイッチ素子16〜18の導通と遮断でローパスフィルタ2の高速充電と遮断を行う。

【0048】

基準電圧源1の出力ノード7にはローパスフィルタ2が接続される。ローパスフィルタ2の出力ノード9には、基準電圧源1の出力ノード7の電圧を平滑した電圧が発生し、基準電圧源1が発生する雑音や基準電圧源1への外乱の影響を低減する。

【0049】

ローパスフィルタ2の出力ノード9は、第1スイッチ素子16を介して、電圧ゲインが1倍である電圧バッファ回路15の入力端子に接続される。さらに、出力ノード9は、第2スイッチ素子17を介して電圧バッファ回路15の出力端子19に接続される。さらに、第1スイッチ素子16と電圧バッファ回路15との接続点は、第3スイッチ素子18を介して基準電圧源1の出力ノード7に接続される。

【0050】

図4の回路の動作について、具体的に説明する。第1〜第3スイッチ素子16〜18の制御は、基準電圧源1の出力ノード7とローパスフィルタ2の出力ノード9の出力が入力されるヒステリシスコンパレータ11によって、遅延回路12を介して次のように制御される。

【0051】

図4において、基準電圧源1の電源を遮断あるいは外部よりバイアス電流を遮断している状態より、基準電圧源1の遮断を解除し基準電圧源1を起動する。第1の実施形態の説明と同様に、ローパスフィルタ2の固有の時定数により、出力ノード9の電圧は直ちには上昇できない結果、出力ノード9と出力ノード7の間に電圧差が発生する。

【0052】

この電圧差がヒステリシスコンパレータ11の第1設定値よりも大きければ、図4に示す状態のように、第1スイッチ素子16を遮断し、第2スイッチ素子17と第3スイッチ素子18を導通させる。それにより、電圧バッファ回路15の出力端子19には、出力ノード7の電圧に電圧バッファ回路15のオフセット電圧が印加された電圧が、低インピーダンスで出力される。同時に、電圧バッファ回路15により、出力ノード7の定常状態の電圧を目標値としてローパスフィルタ2が低インピーダンスで充電されることにより、出力ノード9の電圧が高速に立ち上がる。

【0053】

出力ノード9の電圧上昇により、出力ノード9と出力ノード7との間の電圧差がヒステリシスコンパレータ11の第2設定値に達すると、第1スイッチ素子16を導通させ、第2スイッチ素子17と第3スイッチ素子18を遮断する。それにより、電圧バッファ回路15からローパスフィルタ2への充電が停止されるため、ローパスフィルタ2の出力ノード9の電圧は、ローパスフィルタ2の固有の時定数で基準電圧源1の出力ノード7の定常状態の電圧値に漸近する。電圧バッファ回路15の出力端子19には、ローパスフィルタ2で雑音が低減された出力ノード9の電圧に電圧バッファ回路15のオフセット電圧が印加された電圧が、低インピーダンスで出力される。

【0054】

以上のような構成により、より少ない素子数で、図3に示した第3の実施形態の基準電圧発生回路と同等の機能を得ることができる。

【0055】

なお、第1〜第3スイッチ素子16〜18の切り替わり時のスイッチング雑音が電圧バッファ回路15の入力端子に混入すること防ぐために、電圧バッファ回路15の入力端子と接地端子8の間に、雑音除去用容量20を接続しても良い。この雑音除去用容量20の静電容量は通常小さなものでよく、電圧バッファ回路15の入力端子の浮遊容量や入力容量で代用しても良い。また、スイッチング雑音を緩和するために第1〜第3スイッチ素子16〜18の導通と遮断とを切り替えるときに、必ず3つのスイッチ素子が一旦すべて遮断する短時間の期間を設けるとよい。

【0056】

(第5の実施形態)

図5は、第5の実施形態に係る基準電圧発生回路の構成図である。本実施形態は、図1に示した第1の実施形態に係る基準電圧発生回路の第1電圧バッファ回路10の出力インピーダンスの状態の切り替えを、ヒステリシスコンパレータ11ではなく外部端子21の信号で制御するものである。

【0057】

起動開始より、図5の第1電圧バッファ回路10の出力インピーダンスを低インピーダンスに切り替え、外部端子21から与える信号により制御される期間で、第1電圧バッファ回路10の出力インピーダンスを高インピーダンスに切り替える。外部端子21から与える信号で設定する期間は、定常状態に達する予想時間の近傍あるいはそれ以上の時間に設定する。ヒステリシスコンパレータを用いないため、上述の実施形態ほど短時間で整定できないが、第1電圧バッファ回路10の出力インピーダンスを自由に切り替えることが可能である。

【0058】

なお、以上の実施形態における第1電圧バッファ回路10は、例えば、図6に示す回路のように構成することができる。この回路は、トランジスタ22、23により構成された差動入力段の一方をソース接地で出力端子に出力し、その出力端子を差動負入力端子に直結して負帰還をかけることにより、電圧ゲイン1倍の増幅回路を構成したものである。ソース接地のトランジスタ24のゲートを接地端子に対しMOSスイッチ25で導通させることにより、出力を遮断すなわち出力インピーダンスを高インピーダンスにする。またMOSスイッチ25を遮断してソース接地を動作させることにより、出力インピーダンスを低インピーダンスにする。

【0059】

なお、この実施形態では電流を引き込む能力がないため、出力電圧のオーバーシュートが予想される場合には、出力段をAB級出力段などとして引き込み能力を持たせればよい。

【産業上の利用可能性】

【0060】

本発明は、短時間で起動かつ整定した低雑音の基準電圧の供給を可能とするものであり、携帯電話を含む携帯通信端末などのバッテリ駆動機器の基準電圧発生回路として有用である。

【図面の簡単な説明】

【0061】

【図1】本発明の第1の実施形態における基準電圧発生回路の回路図

【図2】本発明の第2の実施形態における基準電圧発生回路の回路図

【図3】本発明の第3の実施形態における基準電圧発生回路の回路図

【図4】本発明の第4の実施形態における基準電圧発生回路の回路図

【図5】本発明の第5の実施形態における基準電圧発生回路の回路図

【図6】本発明の実施形態における電圧バッファ回路の構成例を示す回路図

【図7】第1従来例の基準電圧発生回路の回路図

【図8】第2従来例の基準電圧発生回路の回路図

【図9】本発明の実施形態と従来例における基準電圧発生回路の電圧波形を比較して示すグラフ

【符号の説明】

【0062】

1 基準電圧源

2 ローパスフィルタ

3 オペアンプ

4 出力トランジスタ

5、14、19 出力端子

6、11 ヒステリシスコンパレータ

7 出力ノード

8 接地端子

9 出力ノード

10 第1電圧バッファ回路

12 遅延回路

13 第2電圧バッファ回路

15 電圧バッファ回路

16 第1スイッチ素子

17 第2スイッチ素子

18 第3スイッチ素子

20 雑音除去用容量

21 外部端子

22〜24 トランジスタ

25 MOSスイッチ

C 容量

R 抵抗

【技術分野】

【0001】

本発明は、基準電圧の雑音を低減させるローパスフィルタの容量を高速で充電して、出力電圧を高速に整定する基準電圧発生回路に関するものである。

【背景技術】

【0002】

基準電圧源の雑音を低減させるために基準電圧源の後段にローパスフィルタを追加する構成が、例えば特許文献1に開示されている(第1従来例)。この第1従来例の回路を図7に示す。図7の構成は、基準電圧源1の電圧が出力されるA点に、抵抗Rと容量Cからなるローパスフィルタ2を接続して、B点に出力される電圧の雑音を低減するものである。なお、一般的な構成として、B点の電圧は、オペアンプ3を用いた非反転増幅器で増幅され、出力トランジスタ4により出力端子5から出力電圧Voutとして出力される。

【0003】

この構成では、ローパスフィルタ2の時定数RCが一般的に、基準電圧源1やオペアンプ3を構成するトランジスタなどの時定数よりも大きい。そのため、電源を投入してから出力電圧Voutが定常状態に整定するまでには、時定数RCで対数的に立ち上がるための相当な時間を要する。図9に、出力電圧Voutが整定するまでの波形を示す。横軸が時間、縦軸が出力電圧Voutである。第1従来例の出力波形P1の場合、出力電圧Voutが整定するまでに相当な時間を要することが判る。

【0004】

この問題を解決するため、電圧をモニタしてローパスフィルタを高速に充電する構成が、例えば特許文献2に開示されている(第2従来例)。この第2従来例の回路を図8に示す。図8の構成では、抵抗Rと容量Cからなるローパスフィルタの出力点であるB点が、ステリシスコンパレータ6の一方の入力端子に接続されている。ステリシスコンパレータ6の他方の入力端子は、基準電圧源1の電圧が出力されるA点に接続されている。B点は、スイッチSW1を介して電源Vddに接続され、また、容量CのB点側の端子は、スイッチSW2を介して接地側の端子と接続される。

【0005】

この回路の動作は、次のとおりである。まず、電源投入直後に基準電圧源1からA点に出力される電圧は、直ちに一定電圧まで立ち上がる。一方、B点の電圧は、ローパスフィルタの容量Cのために時定数RCでゆっくり対数的に立ち上がろうとする。このとき、A点の電圧とB点の電圧とをヒステリシスコンパレータ6で比較して、設定した一定電圧以上の電圧差が発生しているときに、B点と電源VddとをスイッチSW1で短絡する。それにより、B点に接続されているローパスフィルタの容量Cが高速に充電される。

【0006】

この結果、図9に示す第2従来例の出力波形P2のように、スイッチSW1の短絡時等価抵抗と容量Cの乗算した値を時定数として、急速に出力電圧Voutが立ち上がる。ローパスフィルタのRに比較してスイッチSW1の短絡時等価抵抗は非常に小さいため、定常状態になるまでの整定時間が短縮される。なお、A点とB点の電位差が設定電圧未満になった時点でスイッチSW1が開放され、以後B点の電圧はローパスフィルタの時定数RCで上昇してA点の電圧に漸近する。

【0007】

なお、スイッチSW2は、出力電圧Voutの立下り時に、容量Cに蓄積された電荷を強制的に放電させるために用いられる。これにより、出力電圧Voutを急速に降下させて、消費電流を削減する。

【0008】

上記構成以外にも、特許文献3に開示された、基準電圧源の内部電圧の非平衡をコンパレータで検出して容量を充電する構成や、特許文献4に開示された、ローパスフィルタの時定数を小から大へ切り替える構成により、出力電圧Voutが整定するまでの時間を短縮することが知られている。

【特許文献1】特開平8-272461号公報

【特許文献2】特開2002-23870号公報

【特許文献3】特開2005-346522号公報

【特許文献4】特開平6-301429号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら上記第2従来例では、A点とB点の電圧差がヒステリシスコンパレータ6の設定値に達すると、スイッチSW1による急速充電が停止するため、定常状態の電圧に達するまでは、ローパスフィルタの時定数RCを介して充電が行われる。従って、設定値に達してから定常状態に達するまでさらに時間がかかる。

【0010】

第2従来例の方法によれば、時定数が十分小さくなくとも、ヒステリシスコンパレータ6の設定値を小さくすることにより、整定時間をいくらでも短くできるように見えるが、実際にはそうではない。すなわち、ヒステリシスコンパレータ6のオフセット電圧を0にするのが困難であるため、設定値の前後に入力電圧差がずれてしまう。

【0011】

またそのオフセット電圧を校正や補正により0にできても、ヒステリシスコンパレータ6の応答性が有限であるため、結果としてスイッチのオフが遅れてしまい、電源電圧側に過剰に電圧印加されて出力電圧Voutがオーバーシュートしてしまう。

【0012】

さらに、スイッチSW1がMOSなどの半導体素子であれば、オフ時にチャネルに蓄積された電荷が放電するチャージ・インジェクション効果があることにより、オフ後にも短時間ではあるが電流がローパスフィルタの容量に流れ込み、さらに電圧が過剰になる。出力電圧Voutが、定常状態の電圧に対して不足であっても過剰であっても、時定数RCで漸近する動作が発生するため、整定が遅くなる。

【0013】

近年の携帯通信機器などバッテリ駆動の装置は、高出力駆動とバッテリの長時間寿命を同時に達成するために、電力を細かに制御する。それにともない、電源投入後直ちに所定の基準電圧を発生しなければならないが、従来の方法では十分に対応することが困難であった。

【0014】

本発明は上記問題を解決するものであり、雑音を低減するローパスフィルタの容量を高速で充電して、高速に出力電圧を整定することが可能な基準電圧発生回路を提供することを目的とする。

【発明の効果】

【0015】

上記構成の基準電圧発生回路によれば、電源の投入直後の所定期間は、第1電圧バッファ回路あるいはスイッチ素子を介してローパスフィルタの容量Cが急速に充電される。そのため、基準電圧源の雑音および外乱を低減でき、かつ、電源起動時に短時間で正確な基準電圧に到達することができる。

【課題を解決するための手段】

【0016】

上記課題を解決するために、本発明の第1の構成の基準電圧発生回路は、基準となる直流電圧を発生する基準電圧源と、前記基準電圧源の出力に接続されたローパスフィルタと、前記基準電圧源の出力が入力端子に接続され前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路と、前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記ヒステリシスコンパレータの出力信号により前記第1電圧バッファ回路の出力インピーダンスが制御されることを特徴とする。

【0017】

本発明の第2の構成の基準電圧発生回路は、基準となる直流電圧を発生する基準電圧源と、前記基準電圧源の出力に接続されたローパスフィルタと、前記ローパスフィルタの出力をインピーダンス変換して出力する電圧バッファ回路と、前記ローパスフィルタの出力と前記電圧バッファ回路の入力端子の間に挿入された第1スイッチ素子と、前記ローパスフィルタの出力と前記電圧バッファ回路の出力端子との間に挿入された第2スイッチ素子と、前記基準電圧源の出力と前記電圧バッファ回路の入力端子の間に挿入された第3スイッチ素子と、前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタ出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、前記ヒステリシスコンパレータの出力信号により前記第1〜第3スイッチ素子が制御されて、前記第1スイッチ素子がオンで前記第2および第3スイッチ素子がオフの状態と、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態とが切替えられることを特徴とする。

【0018】

本発明の第3の構成の基準電圧発生回路は、基準となる直流電圧を発生する基準電圧源と、前記基準電圧源の出力に接続されたローパスフィルタと、前記基準電圧源の出力が入力端子に接続され、前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路とを備え、外部信号により前記第1電圧バッファ回路の出力インピーダンスが制御されることを特徴とする。

【発明を実施するための最良の形態】

【0019】

本発明は、上記構成を基本として、以下のような態様をとることができる。

【0020】

すなわち、第1の構成において、前記ヒステリシスコンパレータの出力信号を一定期間遅延させた信号で前記第1電圧バッファ回路の出力インピーダンスが制御されることが好ましい。

【0021】

また、前記ローパスフィルタの出力が第2電圧バッファを介して出力されることが好ましい。

【0022】

第2の構成において、起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態に制御される構成とすることができる。

【0023】

以下、本発明の実施形態における基準電圧発生回路について、図面を参照しながら説明する。

【0024】

(第1の実施形態)

図1は、本発明の第1の実施形態に係る基準電圧発生回路の構成図である。基準となる直流電圧を発生する基準電圧源1からの出力ノード7には、ローパスフィルタ2が接続されている。ローパスフィルタ2は、出力ノード7と基準電圧源1の接地端子8との間に直列接続された抵抗Rと容量Cから構成された、ローパスフィルタの最も単純な形態であるRC一次フィルタである。抵抗Rと容量Cの接続点は、ローパスフィルタ2からの出力ノード9であって、基準電圧源1の出力電圧を平滑した電圧が発生する。それにより、基準電圧源1が発生する雑音や基準電圧源1への外乱の影響が低減される。

【0025】

基準電圧源1の出力ノード7にはさらに、第1電圧バッファ回路10の入力端子が接続されている。第1電圧バッファ回路10の出力端子は、ローパスフィルタ2の出力ノード9に接続されている。第1電圧バッファ回路10は、出力インピーダンスが高出力インピーダンスの状態と低出力インピーダンスの状態の2状態に切り替えられる。低出力インピーダンス状態のときには、出力電圧と入力電圧の比、すなわち電圧ゲインが1倍である。

【0026】

第1電圧バッファ回路10の制御端子には、ヒステリシスコンパレータ11の出力VAが入力される。ヒステリシスコンパレータ11の一方の入力端子には、基準電圧源1の出力である出力ノード7の電圧が入力され、他方の入力端子には、ローパスフィルタ2の出力である出力ノード9の電圧Voutが入力される。

【0027】

なお、基準電圧源1は定常状態で一定の電圧を発生し、代表的な基準電圧源としては、半導体素子のバンドギャップ電圧を利用したものを用いることができる。また、ローパスフィルタは用途により様々なものがあり、本実施形態の構成に限定されることはない。機能としては、ローパスフィルタ2の入力と出力ノード9との間で、電圧の交流成分が平滑化されて出力されればよい。出力ノード9には、通常、さらに誤差増幅器や電圧バッファや電圧コンパレータなどの高出力インピーダンス回路が接続され使用されるが、本発明の本質とは関係ないので、図示は省略する。

【0028】

次に、上記構成の回路の動作について説明する。第1電圧バッファ回路10の高出力インピーダンス状態においては、ローパスフィルタ2の出力ノード9には、基準電圧源1の出力ノード7の電圧が平滑されて出力される。

【0029】

一方、第1電圧バッファ回路10の低出力インピーダンス状態においては、基準電圧源1の出力ノード7の電圧が第1電圧バッファ回路10を介して出力ノード9に供給される。第1電圧バッファ回路10の出力インピーダンスを、出力ノード9から見たローパスフィルタ2の入力インピーダンスに対して十分に小さく設定することにより、このとき、ローパスフィルタ2の容量Cが急速に充電される。それにより、ローパスフィルタ2の出力ノード9の電圧は、高速に基準電圧源1の出力ノード7の電圧に漸近させられる。

【0030】

第1電圧バッファ回路10の出力インピーダンスは、基準電圧源1の出力ノード7とローパスフィルタ2の出力ノード9の電圧に基づき、ヒステリシスコンパレータ11の出力VAで次のように制御される。

【0031】

基準電圧源1の電源が投入されたときの動作は、次のとおりである。まず、図1において、基準電圧源1の電源を遮断している状態、あるいは外部よりバイアス電流を遮断している状態では、基準電圧源1の出力ノード7の電圧は、定常状態の電圧と接地端子8の電位との間の初期電圧、通常は接地端子8と同電位になっている。この状態より、基準電圧源1の遮断を解除する。この動作は、基準電圧源の起動と呼ばれる。起動により、基準電圧源1の応答性が十分に早いときは、出力ノード7は直ちに定常状態になると考えて良い。一方、ローパスフィルタ2は、構成するパラメータと構造により固有の時定数を持ち、出力ノード9の電圧は直ちには上昇できない。その結果、出力ノード9と出力ノード7の間に電圧差が発生する。

【0032】

この電圧差がヒステリシスコンパレータ11の第1設定値よりも大きければ、第1電圧バッファ回路10の出力インピーダンスは、低インピーダンス状態に制御される。それにより、出力ノード7の定常状態の電圧を目標値としてローパスフィルタ2を低インピーダンスで充電するように動作する。その結果、図9の出力波形Eに示すように、高速に出力ノード9の電圧が立ち上がる。

【0033】

出力ノード9と出力ノード7との間の電圧差がヒステリシスコンパレータ11の第2設定値に達すると、第1電圧バッファ回路10の出力インピーダンスは、高インピーダンス状態に制御される。それにより、第1電圧バッファ回路10の出力からローパスフィルタ2への充電電流が遮断される。この時点より、ローパスフィルタ2の出力ノード9の電圧は、ローパスフィルタ2の固有の時定数で基準電圧源1の出力ノード7の定常状態の電圧値に漸近する。図1に示すRC一次フィルタにより構成されたローパスフィルタ2の時定数は、抵抗Rと容量Cの抵抗値と容量値の積である。

【0034】

ローパスフィルタ2の出力ノード9の電圧が、ローパスフィルタ2の固有の時定数で基準電圧源1の出力ノード7の定常状態の電圧値に漸近している間、および定常状態では、出力ノード9と出力ノード7との間の電圧差は、ヒステリシスコンパレータ11の第2設定値よりも小さくなる。そのため、その間中、ヒステリシスコンパレータ11の出力VAは、第1電圧バッファ回路10の出力インピーダンスを高インピーダンス状態に維持する値となる。このとき、ローパスフィルタ2は基準電圧源1の出力ノード7の電圧を平滑し、基準電圧源1が発生する雑音や基準電圧源1への外乱の影響を低減して出力ノード9に出力する。

【0035】

本実施形態の構成を採ることにより、ヒステリシスコンパレータ11の第2設定値を十分に小さくすれば、ヒステリシスコンパレータ11のオフセット電圧や応答の遅れ、あるいは第1電圧バッファ回路10の応答の遅れがあっても、従来例と異なり電源電圧側への過剰な電圧印加を十分に抑制できるため、高速に定常状態に達することができる。

【0036】

なお、ローパスフィルタ2の出力ノード9の電圧がヒステリシスコンパレータ11の第2設定値を横切るとき、第1電圧バッファ回路10の発生する雑音あるいは第1電圧バッファ回路10への外乱により、出力ノード9の電圧がチャタリングを起こし、第1電圧バッファ回路10の動作が不安定になる場合がある。これを防止してチャタリングを発生させないように、ヒステリシスコンパレータ11の第1設定値を第2設定値よりも十分大きな値に設定する。しかし、第1電圧バッファ回路10の応答性がチャタリングの周期より十分遅い場合や、雑音と外乱が十分小さくチャタリングが発生しないのであれば、ヒステリシスコンパレータ11の第1設定値を第2設定値と同一にすることができるため、ヒステリシスのないコンパレータで代用しても良い。

【0037】

(第2の実施形態)

図2は、本発明の第2の実施形態に係る基準電圧発生回路の構成図である。この基準電圧発生回路は、図1に示した第1の実施形態の基準電圧発生回路におけるヒステリシスコンパレータ11の出力VAを、遅延回路12を介して第1電圧バッファ回路10に入力する構成となっている。遅延回路12により一定期間遅延された制御信号VBにより、第1電圧バッファ回路10が制御される。

【0038】

第1の実施形態では、第1電圧バッファ回路10の出力インピーダンスを高インピーダンス状態に切り替えてから、出力ノード9の電圧が定常状態に達するまでの時間は、ローパスフィルタ2の時定数によって決まる。定常状態に達する時間は、ヒステリシスコンパレータ11の第2設定値を小さくすればするほど短縮される。ところが、第2設定値をヒステリシスコンパレータ11のオフセット電圧値よりも小さくすると、出力ノード9の電圧が定常状態の値に達してもヒステリシスコンパレータ11が切り替わらず、第1電圧バッファ回路10の出力インピーダンスを低インピーダンス状態に維持する。このため、基準電圧源1と第1電圧バッファ回路10の雑音と外乱が加算されて、出力ノード9に現れてしまう。

【0039】

これに対し、第2の実施形態においては遅延回路12の挿入により、第1電圧バッファ回路10への制御信号VBの入力が、ヒステリシスコンパレータ11の出力VAより一定期間遅延される。これにより、出力ノード9の電圧値が、ヒステリシスコンパレータ11のオフセット電圧値以上に設定された第2設定値に達しても、遅延回路12により設定された一定期間後までは、第1電圧バッファ回路10の出力インピーダンスは低インピーダンス状態に保たれる。

【0040】

この遅延期間を、定常状態に達する予想時間の近傍あるいはそれ以上の時間で、かつ、遅延回路12を挿入しない場合に定常状態に達する時間よりも短い時間に設定すればよい。通常、遅延回路12を挿入しない場合に定常状態に達する時間よりも比較的短く遅延期間を設定できる。

【0041】

なお、第1電圧バッファ回路10の応答の遅れによりたとえ電圧がオーバーシュートしても、減衰を見込んだ期間を設定することにより、影響を受けないようにできる。

【0042】

なお、遅延回路12の代わりに、ヒステリシスコンパレータ11に容量を内蔵するなどして、ヒステリシスコンパレータ11自体に遅延作用を持たせても良い。

【0043】

(第3の実施形態)

図3は、第3の実施形態に係る基準電圧発生回路の構成図である。本実施形態では、図2の基準電圧発生回路のローパスフィルタ2の出力ノード9に、第2電圧バッファ回路13の入力端子に接続し、第2電圧バッファ回路13の出力を基準電圧発生回路の出力端子14としたものである。

【0044】

このような構成とすることにより、本実施形態に係る基準電圧発生回路によれば、出力端子14に低出力インピーダンスで出力することができる。多くの負荷は抵抗性または容量性であり、ローパスフィルタ2の出力インピーダンスでは十分に駆動できない場合がある。これに対して、第2電圧バッファ回路13でインピーダンス変換を行うことにより、そのような問題を解消することができる。

【0045】

なお、出力電圧値の変換が必要な場合には、出力電圧を抵抗分割してから演算増幅器に帰還して使う反転増幅回路あるいは非反転増幅回路を、第2電圧バッファ回路13の代わりに用いても良い。

【0046】

(第4の実施形態)

図4は、第4の実施形態に係る基準電圧発生回路の構成図である。本実施形態は、図3に示した第3の実施形態に係る基準電圧発生回路の構成において、第2電圧バッファ回路13で第1電圧バッファ回路10(本実施の形態では電圧バッファ回路15)を兼用した構成を特徴とする。

【0047】

そのために、接続切り替え用の第1〜第3スイッチ素子16〜18を設ける。同時に、図3の第1電圧バッファ回路10の出力インピーダンスを切り替えることに代えて、第1〜第3スイッチ素子16〜18の導通と遮断でローパスフィルタ2の高速充電と遮断を行う。

【0048】

基準電圧源1の出力ノード7にはローパスフィルタ2が接続される。ローパスフィルタ2の出力ノード9には、基準電圧源1の出力ノード7の電圧を平滑した電圧が発生し、基準電圧源1が発生する雑音や基準電圧源1への外乱の影響を低減する。

【0049】

ローパスフィルタ2の出力ノード9は、第1スイッチ素子16を介して、電圧ゲインが1倍である電圧バッファ回路15の入力端子に接続される。さらに、出力ノード9は、第2スイッチ素子17を介して電圧バッファ回路15の出力端子19に接続される。さらに、第1スイッチ素子16と電圧バッファ回路15との接続点は、第3スイッチ素子18を介して基準電圧源1の出力ノード7に接続される。

【0050】

図4の回路の動作について、具体的に説明する。第1〜第3スイッチ素子16〜18の制御は、基準電圧源1の出力ノード7とローパスフィルタ2の出力ノード9の出力が入力されるヒステリシスコンパレータ11によって、遅延回路12を介して次のように制御される。

【0051】

図4において、基準電圧源1の電源を遮断あるいは外部よりバイアス電流を遮断している状態より、基準電圧源1の遮断を解除し基準電圧源1を起動する。第1の実施形態の説明と同様に、ローパスフィルタ2の固有の時定数により、出力ノード9の電圧は直ちには上昇できない結果、出力ノード9と出力ノード7の間に電圧差が発生する。

【0052】

この電圧差がヒステリシスコンパレータ11の第1設定値よりも大きければ、図4に示す状態のように、第1スイッチ素子16を遮断し、第2スイッチ素子17と第3スイッチ素子18を導通させる。それにより、電圧バッファ回路15の出力端子19には、出力ノード7の電圧に電圧バッファ回路15のオフセット電圧が印加された電圧が、低インピーダンスで出力される。同時に、電圧バッファ回路15により、出力ノード7の定常状態の電圧を目標値としてローパスフィルタ2が低インピーダンスで充電されることにより、出力ノード9の電圧が高速に立ち上がる。

【0053】

出力ノード9の電圧上昇により、出力ノード9と出力ノード7との間の電圧差がヒステリシスコンパレータ11の第2設定値に達すると、第1スイッチ素子16を導通させ、第2スイッチ素子17と第3スイッチ素子18を遮断する。それにより、電圧バッファ回路15からローパスフィルタ2への充電が停止されるため、ローパスフィルタ2の出力ノード9の電圧は、ローパスフィルタ2の固有の時定数で基準電圧源1の出力ノード7の定常状態の電圧値に漸近する。電圧バッファ回路15の出力端子19には、ローパスフィルタ2で雑音が低減された出力ノード9の電圧に電圧バッファ回路15のオフセット電圧が印加された電圧が、低インピーダンスで出力される。

【0054】

以上のような構成により、より少ない素子数で、図3に示した第3の実施形態の基準電圧発生回路と同等の機能を得ることができる。

【0055】

なお、第1〜第3スイッチ素子16〜18の切り替わり時のスイッチング雑音が電圧バッファ回路15の入力端子に混入すること防ぐために、電圧バッファ回路15の入力端子と接地端子8の間に、雑音除去用容量20を接続しても良い。この雑音除去用容量20の静電容量は通常小さなものでよく、電圧バッファ回路15の入力端子の浮遊容量や入力容量で代用しても良い。また、スイッチング雑音を緩和するために第1〜第3スイッチ素子16〜18の導通と遮断とを切り替えるときに、必ず3つのスイッチ素子が一旦すべて遮断する短時間の期間を設けるとよい。

【0056】

(第5の実施形態)

図5は、第5の実施形態に係る基準電圧発生回路の構成図である。本実施形態は、図1に示した第1の実施形態に係る基準電圧発生回路の第1電圧バッファ回路10の出力インピーダンスの状態の切り替えを、ヒステリシスコンパレータ11ではなく外部端子21の信号で制御するものである。

【0057】

起動開始より、図5の第1電圧バッファ回路10の出力インピーダンスを低インピーダンスに切り替え、外部端子21から与える信号により制御される期間で、第1電圧バッファ回路10の出力インピーダンスを高インピーダンスに切り替える。外部端子21から与える信号で設定する期間は、定常状態に達する予想時間の近傍あるいはそれ以上の時間に設定する。ヒステリシスコンパレータを用いないため、上述の実施形態ほど短時間で整定できないが、第1電圧バッファ回路10の出力インピーダンスを自由に切り替えることが可能である。

【0058】

なお、以上の実施形態における第1電圧バッファ回路10は、例えば、図6に示す回路のように構成することができる。この回路は、トランジスタ22、23により構成された差動入力段の一方をソース接地で出力端子に出力し、その出力端子を差動負入力端子に直結して負帰還をかけることにより、電圧ゲイン1倍の増幅回路を構成したものである。ソース接地のトランジスタ24のゲートを接地端子に対しMOSスイッチ25で導通させることにより、出力を遮断すなわち出力インピーダンスを高インピーダンスにする。またMOSスイッチ25を遮断してソース接地を動作させることにより、出力インピーダンスを低インピーダンスにする。

【0059】

なお、この実施形態では電流を引き込む能力がないため、出力電圧のオーバーシュートが予想される場合には、出力段をAB級出力段などとして引き込み能力を持たせればよい。

【産業上の利用可能性】

【0060】

本発明は、短時間で起動かつ整定した低雑音の基準電圧の供給を可能とするものであり、携帯電話を含む携帯通信端末などのバッテリ駆動機器の基準電圧発生回路として有用である。

【図面の簡単な説明】

【0061】

【図1】本発明の第1の実施形態における基準電圧発生回路の回路図

【図2】本発明の第2の実施形態における基準電圧発生回路の回路図

【図3】本発明の第3の実施形態における基準電圧発生回路の回路図

【図4】本発明の第4の実施形態における基準電圧発生回路の回路図

【図5】本発明の第5の実施形態における基準電圧発生回路の回路図

【図6】本発明の実施形態における電圧バッファ回路の構成例を示す回路図

【図7】第1従来例の基準電圧発生回路の回路図

【図8】第2従来例の基準電圧発生回路の回路図

【図9】本発明の実施形態と従来例における基準電圧発生回路の電圧波形を比較して示すグラフ

【符号の説明】

【0062】

1 基準電圧源

2 ローパスフィルタ

3 オペアンプ

4 出力トランジスタ

5、14、19 出力端子

6、11 ヒステリシスコンパレータ

7 出力ノード

8 接地端子

9 出力ノード

10 第1電圧バッファ回路

12 遅延回路

13 第2電圧バッファ回路

15 電圧バッファ回路

16 第1スイッチ素子

17 第2スイッチ素子

18 第3スイッチ素子

20 雑音除去用容量

21 外部端子

22〜24 トランジスタ

25 MOSスイッチ

C 容量

R 抵抗

【特許請求の範囲】

【請求項1】

基準となる直流電圧を発生する基準電圧源と、

前記基準電圧源の出力に接続されたローパスフィルタと、

前記基準電圧源の出力が入力端子に接続され前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路と、

前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、

起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記ヒステリシスコンパレータの出力信号により前記第1電圧バッファ回路が低出力インピーダンス状態に制御される基準電圧発生回路。

【請求項2】

前記ヒステリシスコンパレータの出力信号を一定期間遅延させた信号で前記第1電圧バッファ回路の出力インピーダンスが制御される請求項1記載の基準電圧発生回路。

【請求項3】

前記ローパスフィルタの出力が第2電圧バッファを介して出力される請求項1または2記載の基準電圧発生回路。

【請求項4】

基準となる直流電圧を発生する基準電圧源と、

前記基準電圧源の出力に接続されたローパスフィルタと、

前記ローパスフィルタの出力をインピーダンス変換して出力する電圧バッファ回路と、

前記ローパスフィルタの出力と前記電圧バッファ回路の入力端子の間に挿入された第1スイッチ素子と、

前記ローパスフィルタの出力と前記電圧バッファ回路の出力端子との間に挿入された第2スイッチ素子と、

前記基準電圧源の出力と前記電圧バッファ回路の入力端子の間に挿入された第3スイッチ素子と、

前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタ出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、

前記ヒステリシスコンパレータの出力信号により前記第1〜第3スイッチ素子が制御されて、前記第1スイッチ素子がオンで前記第2および第3スイッチ素子がオフの状態と、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態とが切替えられることを特徴とする基準電圧発生回路。

【請求項5】

起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態に制御される請求項4記載の基準電圧発生回路。

【請求項6】

基準となる直流電圧を発生する基準電圧源と、

前記基準電圧源の出力に接続されたローパスフィルタと、

前記基準電圧源の出力が入力端子に接続され、前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路とを備え、

外部信号により前記第1電圧バッファ回路の出力インピーダンスが制御されることを特徴とする基準電圧発生回路。

【請求項1】

基準となる直流電圧を発生する基準電圧源と、

前記基準電圧源の出力に接続されたローパスフィルタと、

前記基準電圧源の出力が入力端子に接続され前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路と、

前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、

起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記ヒステリシスコンパレータの出力信号により前記第1電圧バッファ回路が低出力インピーダンス状態に制御される基準電圧発生回路。

【請求項2】

前記ヒステリシスコンパレータの出力信号を一定期間遅延させた信号で前記第1電圧バッファ回路の出力インピーダンスが制御される請求項1記載の基準電圧発生回路。

【請求項3】

前記ローパスフィルタの出力が第2電圧バッファを介して出力される請求項1または2記載の基準電圧発生回路。

【請求項4】

基準となる直流電圧を発生する基準電圧源と、

前記基準電圧源の出力に接続されたローパスフィルタと、

前記ローパスフィルタの出力をインピーダンス変換して出力する電圧バッファ回路と、

前記ローパスフィルタの出力と前記電圧バッファ回路の入力端子の間に挿入された第1スイッチ素子と、

前記ローパスフィルタの出力と前記電圧バッファ回路の出力端子との間に挿入された第2スイッチ素子と、

前記基準電圧源の出力と前記電圧バッファ回路の入力端子の間に挿入された第3スイッチ素子と、

前記基準電圧源の出力が一方の入力端子に接続され前記ローパスフィルタ出力が他方の入力端子に接続されたヒステリシスコンパレータとを備え、

前記ヒステリシスコンパレータの出力信号により前記第1〜第3スイッチ素子が制御されて、前記第1スイッチ素子がオンで前記第2および第3スイッチ素子がオフの状態と、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態とが切替えられることを特徴とする基準電圧発生回路。

【請求項5】

起動時に前記基準電圧源の出力と前記ローパスフィルタの出力の電圧差が所定値を超えている期間は、前記第1スイッチ素子がオフで前記第2および第3スイッチ素子がオンの状態に制御される請求項4記載の基準電圧発生回路。

【請求項6】

基準となる直流電圧を発生する基準電圧源と、

前記基準電圧源の出力に接続されたローパスフィルタと、

前記基準電圧源の出力が入力端子に接続され、前記ローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路とを備え、

外部信号により前記第1電圧バッファ回路の出力インピーダンスが制御されることを特徴とする基準電圧発生回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2010−146526(P2010−146526A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−326442(P2008−326442)

【出願日】平成20年12月22日(2008.12.22)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月22日(2008.12.22)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]