増幅回路

【課題】追加プロセスなしに、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる高耐圧の入力段とすることが可能な増幅回路を提供する。

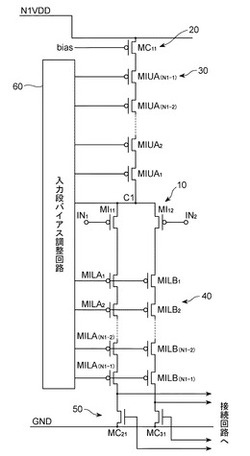

【解決手段】増幅回路の入力段は、入力端子IN1,IN2が接続された第1の差動対トランジスタ10と、N1VDDに接続された第1の入力段電流バイアス手段20と、第1の差動対トランジスタ10と第1の入力段電流バイアス手段20に接続された第1の入力段カスコードトランジスタ群30と、第1の差動対トランジスタ10に接続された第2の入力段カスコードトランジスタ群40と、0VからN1VDDまで変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のVGSとVGDの絶対値がVDD以内となるバイアス電圧に調整する入力段バイアス調整回路60を備えている。

【解決手段】増幅回路の入力段は、入力端子IN1,IN2が接続された第1の差動対トランジスタ10と、N1VDDに接続された第1の入力段電流バイアス手段20と、第1の差動対トランジスタ10と第1の入力段電流バイアス手段20に接続された第1の入力段カスコードトランジスタ群30と、第1の差動対トランジスタ10に接続された第2の入力段カスコードトランジスタ群40と、0VからN1VDDまで変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のVGSとVGDの絶対値がVDD以内となるバイアス電圧に調整する入力段バイアス調整回路60を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積化可能な差動入力型の増幅回路に関するものである。

【背景技術】

【0002】

集積回路の微細化技術の発展により、デバイスの耐圧は低下の一方である。集積回路に用いられる電源電圧の値はデバイス耐圧によって制限される。一般に微細化集積回路では電源電圧はデバイス耐圧以下の値に設定されるが、近年では、電源電圧の低下が著しい。特に、CMOS LSIでは、電源電圧であるVDDが、例えば1.8Vから更に低下する傾向にある。従来のアナログ・デジタル混載のLSIでは、スケーリング則に沿ってゲート酸化膜の厚みを薄くした通常の低耐圧MOSトランジスタ以外に、追加プロセスにより同一チップ上にゲート酸化膜の厚みを厚くした中耐圧や高耐圧のアナログ専用MOSトランジスタを形成するようにして、高耐圧化を図ってきたが、プロセスが複雑化するため製造コストが増大する。従って、追加プロセス無しに高耐圧が実現できるのが望ましい。

【0003】

ここで、追加プロセスを必要としない従来の増幅回路の一例を図面に基づいて説明する。まず入力段であるが、非特許文献1に記載されたものが知られている。この非特許文献1に記載された増幅回路を図25に基づいて説明する。

図25に示す増幅回路の入力段は、バイポーラトランジスタのLSIに使用される回路であるが、以下の説明は、npnトランジスタをnMOSトランジスタに、pnpトランジスタをpMOSトランジスタに読みかえれば、MOSトランジスタについても成り立つ。この回路では2電源V+とV-を使用しており、電源電圧は合わせて2Vとなっている。この電源電圧2Vは通常のデバイスの耐圧から決まる定格電源電圧(以内)に設定されている。npnトランジスタQ1とnpnトランジスタQ2とは入力端子がベースに接続された差動対トランジスタである。このnpnトランジスタQ1,Q2は、電流増幅率βの値が大きいスーパβデバイス(super beta transistor)と称される特殊トランジスタである。このnpnトランジスタQ1,Q2は通常のnpnトランジスタQ3,Q4と比較して耐圧が低いため、npnトランジスタQ1,Q2のそれぞれには、直列接続されたダイオードD1,D2と電流源I1,I2によりバイアスされたnpnトランジスタQ3,Q4がカスコード接続されている。

【0004】

次に、従来の出力段であるが、非特許文献2に記載されたものが知られている。この非特許文献2に記載された増幅回路を図26に基づいて説明する。なお、本明細書の以下の記述では、表記の簡略化のために、特にことわらない限り、pMOSトランジスタをpトランジスタと表記し、nMOSトランジスタをnトランジスタと表記することとする。

図26に示す増幅回路の出力段は、高耐圧化を実現するために、デジタル回路のI/Oバッファ用として知られているダブルカスコード型バッファをプッシュプル構成としたpトランジスタおよびnトランジスタM13〜M22に、AB級動作用のレベルシフタとしてpトランジスタおよびnトランジスタM9〜M12と抵抗R1,R2とを組み合わせたものである。

【0005】

図26に示す非特許文献2に記載の増幅回路の出力段では、電源電圧がMOSトランジスタの定格電源電圧VDD(本発明の請求項1で定義したVDDに相当)の2倍の2×VDDに設定されている。この電源電圧はVSSを基準としたものである。プッシュプル構成とした出力回路においては、出力端子と2×VDDの電圧を与える電源との間と、出力端子とVSSとの間に、それぞれ3つのトランジスタが設けられ、増幅用のトランジスタM13,M22を除くと2個ずつ設けられている。集積回路ではトランジスタの数が増えると駆動能力が低下し、それを補うためにトランジスタサイズを大きくして面積を占有してしまうため小型化を阻害する要因となる。

この点については、出力端子とMOSトランジスタの定格電源電圧Vdd(本発明の請求項1で定義したVDDに相当)の3倍電圧(3×Vdd)との間と、出力端子とグランドとの間に、それぞれ2つのトランジスタが積み上げたスタック数が2個の出力段が、非特許文献3に記載されている(図27参照)。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】PAUL R.GRAY,PAUL J.HURST,STEPHEN H.LEWIS,ROBERT G. MEYER,「ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUIT」,(米国),第4版,John Wiley & Sons Inc,2001年,p.479−480

【非特許文献2】石田光一,アティットタムタカーン,桜井貴康,「1.8VCOMSプロセスによる高耐圧オペアンプ」,電子情報通信学会総合大会講演論文集2005年,社団法人電子情報通信学会,2005年3月7日,p.13

【非特許文献3】Prem Swaroop, Anand J. Vasani,Maysam Ghovanloo、「A High-Voltage Output Driver for Implantable Biomedical Stimulators and I/O Applications」、「Circuits and Systems, 2006.MWSCAS'06. 49th IEEE International Midwest Symposium on」、(米国)、IEEE、2006年8月6日、p.566−569

【非特許文献4】Anne-Johan Annema, Govert J. G. M. Geelen, and Peter C. de Jong,「5.5-V I/O in a 2.5-V 0.25μm CMOS Technology」,「IEEE Journal of Solid-State Circuits VOL.36, NO.3, MARCH 2001」、(米国)、IEEE,2001年3月、p.528−538

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、図25に示す非特許文献1に記載の増幅回路の入力段では、追加プロセスを必要としないものの、任意の電圧に耐えられるようにしたものではないため、定格電源電圧の任意の倍数電圧でも耐えることが可能なものが望まれている。

アナログ増幅器として幅広く用いられる増幅回路は、一対の入力端子、つまりプラス入力端子とマイナス入力端子との一対の入力端子を有する差動対入力段、一つの出力端子を有する出力段とから構成される増幅回路で、一対の入力端子に印加された信号成分のうちの差分、つまり差動モード入力電圧を増幅して出力端子に出力する。その際に、増幅回路の性能は一対の入力端子に印加された共通成分、つまりコモンモード入力電圧の影響を受ける。差動モード入力に対する性能を維持できるコモンモード入力電圧の範囲をコモンモード入力電圧範囲という。一般にコモンモード入力電圧が電源電圧に近くなったり、グランド電圧に近くなったりすると、性能が極度に悪化する。コモンモード入力電圧範囲は、グランドから電源電圧の任意の倍数の電圧まで広い範囲であることが望ましい。

【0008】

また、図27に示す非特許文献3に記載の出力段では、デジタル回路であるため、デジタル信号が入力されるpトランジスタP1とnトランジスタN1のゲートソース間電圧の絶対値は、0VからVdd(=VDD)まで振幅する。従って、デジタル入力信号が0VからVdd(=VDD)まで急峻に変化する過渡状態では、出力段トランジスタがONしてもドレイン−ソース間電圧が直ちに0Vとはならず、ドレイン−ソース間電圧がVDD以上の電圧となることがあり、ホットキャリアの問題が生じる。

【0009】

例えば、非特許文献4では、ホットキャリアの問題についての記載があり、以下に説明する。

MOSトランジスタのプロセスは、ある寿命を境界条件としてデジタル回路で用いられるトランジスタの性能を最大化するように最適化される。目標となる寿命は最悪動作条件下で典型的に5〜10年の連続動作である。寿命はトランジスタの動作条件に依存する。一つはゲート−ソース間電圧Vgs(本明細書の表記では、VGS)、ゲート−ドレイン間電圧Vgd(本明細書の表記では、VGD)(縦方向の電界)にかかわるゲート酸化膜耐圧(BVgs/BVGS,BVgd/BVGD)であり、他の一つは、ドレイン−ソース間電圧Vds(本明細書の表記では、VDS)(横方向の電界)にかかわるホットキャリア劣化である。Vgsが大きく、かつ、Vdsが大きい条件下では(例えば、Vgs=Vds=Vdd)(Vddは本発明の表記では、VDDに相当)、トランジスタの寿命時間は極端に短くなる(図28参照)。

【0010】

つまり、ゲート−ソース間電圧VGSが大きな電圧(VDD)で駆動されて、トランジスタがONになっていて、なおかつ、VDSに大きな電圧(VDD)が印加されている条件下で、寿命は最短となる。このような条件は、デジタル論理回路のトランジスタが急峻にOFFからONに切り替わった状態(VGSが0からVDDに切り替わった状態)で過渡的に生じる。寿命を長くするには、MOSトランジスタがこのような条件下で動作するのを可能な限り避けることが望ましい。

【0011】

従って、非特許文献3に記載の出力段においては、過渡的な状態でも出力トランジスタ(pトランジスタP2,P3,nトランジスタN2,N3)とそれをドライブするトランジスタ(pトランジスタP1,nトランジスタN1)のゲート−ソース間電圧とドレイン−ソース間電圧が同時にVDDに近い電圧またはVDD以上の高い電圧が印加されないようにするには、更にスタック数を増やす必要がある。

【0012】

また、増幅回路では一般に出力端子から入力端子にある種の帰還をかけて用いられる。よく用いられる応用例として、非反転型負帰還増幅回路、反転型負帰還増幅回路が知られている。反転型負帰還増幅回路では、入力信号はマイナス入力端子に印加され、入力信号に対してコモンモード入力電圧は変化せず、プラス入力端子の電圧に保持される。一方、非反転型負帰還増幅回路では、入力信号はプラス入力端子に印加され、コモンモード入力電圧は入力信号に応じて変化する。

【0013】

非特許文献2には、マイナス入力端子In−とプラス入力端子In+を一対の入力端子とする入力段の電源も定格電源電圧の2倍の2×VDD(VDDは本発明の請求項1で定義したVDDに相当)に設定されて、それに対応した入力段回路が示されている。しかし、非特許文献2に記載の回路においては、コモンモード入力電圧がVSS(本発明における他方の電源線の電圧に相当)近くになったり、2倍のVDD近くになったりすると、耐圧の問題が生じる。非特許文献2に記載の回路を反転型負帰還増幅回路として用いる場合、プラス入力端子の電圧を適当に設定すれば、つまり反転型負帰還増幅回路でコモンモード入力電圧を適当に設定すれば(例えば、2×VDDとVSSの中点電圧など)入力段の回路に耐圧の問題は生じないが、それ以外の応用に対しては、耐圧の問題が解決できない。

【0014】

このように、上記理由で非特許文献1に記載の入力段回路,非特許文献2に記載の出力段回路、入力段回路を採用することができない。また、出力段では、デジタル信号を出力する非特許文献3の回路においては、非特許文献2の回路より少ないトランジスタ数で実現されているものの、上記問題があるため、非特許文献3の回路を採用することができない。

従って、アナログ信号をドライブする高耐圧の出力段を、少ないトランジスタ数で実現することができる回路が望まれている。

【0015】

このように様々な課題を有する増幅回路ではあるが、本発明では、入力段の課題を解決するものとする。

【0016】

そこで本発明は、追加プロセスなしに実現できる汎用性の高い高耐圧アナログ信号増幅回路、特にコモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる増幅回路を提供することを目的とする。

【課題を解決するための手段】

【0017】

本発明に係る増幅回路の入力段は、MOSトランジスタにより形成された入力段、出力段および前記入力段と前記出力段とを接続する接続回路を備えた増幅回路であって、前記入力段は、2つのMOSトランジスタより成り、2つのゲート端子を一対の入力端子とした第1の差動対トランジスタと、電位差の絶対値が前記MOSトランジスタの定格電源電圧(以下、この電圧をVDDと称す。)のN1倍(但し、N1は2以上の整数である。以下、この電圧をN1VDDと称す。)以上の電源電圧を供給する一方の電源線と他方の電源線とのうち、前記一方の電源線に接続された第1の入力段電流バイアス手段と、前記第1の差動対トランジスタの接続点に一端が接続され、前記第1の入力段電流バイアス手段から他端にバイアス電流が供給される前記第1の差動対トランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタがカスコード接続された第1の入力段カスコードトランジスタ群と、前記第1の差動対トランジスタのそれぞれのMOSトランジスタに前記第1の差動対トランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタがカスコード接続された一対の第2の入力段カスコードトランジスタ群と、前記一対の第2の入力段カスコードトランジスタ群のそれぞれに接続された前記第1の差動対トランジスタと異なる伝導極性を有する一対の出力用MOSトランジスタと、前記一対の入力端子に前記他方の電源線を基準として電圧の絶対値が0VからN1VDDまでの間で変化するコモンモード入力電圧が入力されたときに、前記第1の差動対トランジスタの接続点の電圧に基づいて、前記第1の差動対トランジスタ、前記第1の入力段カスコードトランジスタ群、前記第2の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値がVDD以内となるように調整する入力段バイアス調整回路とを備えたことを特徴とする。

【0018】

この増幅回路の入力段によれば、一対の入力端子に前記他方の電源線を基準として0VからN1VDDまでの間で変化するコモンモード入力電圧が入力されたときに、入力段バイアス調整回路が第1の差動対トランジスタ、第1の入力段カスコードトランジスタ群、第2の入力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内、すなわちデバイス耐圧以下、となるようにバイアス電圧を調整するので、第1の差動対トランジスタに流れる信号電流を一対の第2の入力段カスコードトランジスタ群を介して後段への出力信号として出力することができる。

【0019】

ここで、伝導極性とは、MOSトランジスタのチャンネルを流れる電流を運ぶ担体(キャリア)の極性の意味で用いており、キャリアが電子であればnMOSトランジスタ、正孔であればpMOSトランジスタを指す。つまり、伝導極性が同じとは、一方がpMOSトランジスタであれば他方もpMOSトランジスタ、一方がnMOSトランジスタであれば他方もnMOSトランジスタということを意味し、タイプが同じであることを意味する。また、伝導極性が異なるとは、一方がpMOSトランジスタであれば他方はnMOSトランジスタ、一方がnMOSトランジスタであれば他方はpMOSトランジスタということを意味し、タイプが違うことを意味する。

【0020】

前記入力段バイアス調整回路は、前記一対の入力端子に入力されたコモンモード入力電圧の絶対値が前記他方の電源線を基準としてN1VDDであれば、前記第1の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート電圧の絶対値を(N1−1)×VDDとすると共に、前記一対の第2の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート電圧の絶対値を前記第1の差動対トランジスタ側から順に(N1−M1)×VDD(但し、M1は前記第2の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタに付与した番号であり、前記第1の差動対トランジスタ側から前記一対の出力用MOSトランジスタ側までのMOSトランジスタに対応する1からN1−1までの整数である。)とし、前記一対の入力端子に入力されたコモンモード入力電圧が前記他方の電源線を基準として0Vであれば、前記第1の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート電圧の絶対値をN1VDD側から順に(N1−M2)×VDD(但し、M2は前記第1の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタに付与した番号であり、第1のバイアス電流手段側から第1の差動対トランジスタ側までのMOSトランジスタに対応する1からN1−1までの整数である。)とすると共に、前記第2の入力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を0Vとするのが望ましい。

【0021】

入力端子に入力されたコモンモード入力電圧の絶対値が他方の電源線を基準としてN1VDDである場合に、または0Vのときに、入力段バイアス調整回路を、上記バイアス電圧とするような調整回路とすることで、第1の差動対トランジスタ、第1の入力段カスコードトランジスタ群、第2の入力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内とすることができる。

【0022】

前記入力段バイアス調整回路は、前記第1の差動対トランジスタのゲート−ソース間電圧に相当する電圧分またはそれ以上の電圧をレベルシフトするレベルシフト手段と、前記他方の電源線を基準とした前記一方の電源線の電圧の正負に応じて、それぞれ(N1−1)×VDDあるいは−(N1−1)×VDDの電圧を供給する電源に一端が接続されたN1−2個の直列接続された抵抗手段より成る第1の入力段カスコードバイアス用抵抗手段であって、前記第1の入力段カスコードバイアス用抵抗手段の両端と前記第1の入力段カスコードバイアス用抵抗手段の隣り合う各抵抗手段の接続点とが、それぞれ前記第1の入力段カスコードトランジスタ群の隣り合う各MOSトランジスタのゲートに接続された前記第1の入力段カスコードバイアス用抵抗手段と、前記レベルシフト手段と共に、前記他方の電源線に接続されたN1個の抵抗手段であって、前記他方の電源線側から少なくとも(N1−1)個の抵抗が直列接続された抵抗手段より成り、前記一対の第2の入力カスコードトランジスタ群の各MOSトランジスタのゲート端子に、前記N1個の隣り合う抵抗手段の接続点がそれぞれ接続された第2の入力段カスコードバイアス用抵抗手段と、前記第1の入力段カスコードバイアス用抵抗手段の他端に接続されていると共に、前記他方の電源線を基準とした前記一方の電源線の電圧の正負に応じて、VDDあるいは−VDDの電圧を供給する電源に接続された第1の抵抗手段と、前記第1の入力段カスコードバイアス用抵抗手段と、前記第1の抵抗手段との接続点に一端が接続され、前記第1の差動対トランジスタの接続点に他端が接続された第2の抵抗手段とを備えるのが望ましい。

【0023】

入力段バイアス調整回路を、前記ダイオード接続のMOSトランジスタと、前記第1の入力段カスコードバイアス用抵抗手段と、前記第2の入力段カスコードバイアス用抵抗手段と、前記第1の抵抗手段と、前記第2の抵抗手段とにより構成することで、入力端子に入力されたコモンモードの電圧範囲が他方の電源線を基準として0VからN1VDD(または−N1VDD)まで変化しても、前記第1入力段カスコードトランジスタ群と前記第2の入力段カスコードトランジスタ群のゲートへのバイアス電圧を前記のように調整した電圧に制御することができる。

【0024】

当該入力段バイアス調整回路に対し、前記他方の電源線を基準とした電位差の絶対値がN1VDDである前記一方の電源線に接続された第2の入力段電流バイアス手段と、前記一対の入力端子が接続され、前記第1の差動対トランジスタのMOSトランジスタと同じ伝導極性を有する一対のMOSトランジスタより成り、当該一対のMOSトランジスタのそれぞれのドレイン端子およびソース端子を接続した第2の差動対トランジスタと、前記第2の差動対トランジスタの一方の接続点に一端が接続され、前記第2の入力段電流バイアス手段から他端にバイアス電流が供給される前記第1の差動対トランジスタのMOSトランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタより成り、さらに当該N1−1個の各MOSトランジスタの各ゲート端子が、前記第1の入力段カスコードトランジスタ群のN1−1個の各MOSトランジスタの対応するゲート端子と接続された第3の入力段カスコードトランジスタ群と、前記第2の差動対トランジスタの他方の接続点と前記他方の電源線に接続され、前記第1の差動対トランジスタのMOSトランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタより成り、さらに当該N1−1個の各MOSトランジスタの各ゲート端子が、前記第2の一対入力段カスコードトランジスタ群のそれぞれN1−1個の各MOSトランジスタの対応するゲート端子と接続された第4の入力段カスコードトランジスタ群と、を追加し、バイアス電圧の調整を前記第2の差動対トランジスタの接続点の電圧に基づいて行うのが望ましい。そうすることで、出力段へ伝達される信号電流が流れる第1の差動対トランジスタへの影響を排除することができる。

【0025】

本発明に係る増幅回路の出力段は、MOSトランジスタにより形成された前記入力段、前記出力段および前記入力段と前記出力段とを接続する接続回路を備えた増幅回路であって、前記出力段は、電位差の絶対値がMOSトランジスタの定格電源電圧VDDのN2倍(但し、N2は2以上の整数である。以下、この電圧をN2VDDと称す。)の電圧を供給する一方の出力段電源線と他方の出力段電源線とのうち、前記一方の出力段電源線に接続された、1個のMOSトランジスタより成り、前記接続回路により駆動される第1の出力電流源と、出力端子に一端が接続され、他端が前記第1の出力電流源に接続され、カスコード接続された、前記第1の出力電流源のMOSトランジスタと同じ伝導極性を有するN2−1個(但し、N2は2以上の整数である。)のMOSトランジスタより成る第1の出力段カスコードトランジスタ群と、前記出力端子に一端が接続され、カスコード接続された、前記第1の出力段カスコードトランジスタ群のMOSトランジスタとは異なる伝導極性を有するN2−1個のMOSトランジスタより成る第2の出力段カスコードトランジスタ群と、前記第2の出力段カスコードトランジスタ群の他端と前記他方の出力段電源線とに接続された、第2の出力段カスコードトランジスタ群のMOSトランジスタと同じ伝導極性を有するMOSトランジスタより成り、前記接続回路により駆動される第2の出力電流源と、により構成され、前記他方の出力段電源線を基準とした前記出力端子の電圧の絶対値が0VからN2VDDまでの間で変化したときに、前記第1の出力段カスコードトランジスタ群と前記第2の出力段カスコードトランジスタ群を構成するMOSトランジスタのそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値がVDD以内となるバイアス電圧に調整する出力段バイアス調整回路とを備え、前記接続回路は、前記入力段からの信号に応じて、前記第1の出力電流源および前記第2の出力電流源を構成する各MOSトランジスタのゲート−ソース間電圧の絶対値がVDDより小さくなるように駆動することを特徴とする。

【0026】

この増幅回路の出力段によれば、他方の出力段電源線を基準として、出力端子から出力される出力電圧の絶対値が0VからN2VDDまでの間で変化しても、出力段バイアス調整回路が第1の出力段カスコードトランジスタ群、第2の出力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値がVDD以内となるようにバイアス電圧を調整し、また接続回路が第1の出力電流源および第2の出力電流源を構成する各MOSトランジスタのゲート−ソース間電圧の絶対値がVDDより小さくなるように調整するので、出力電圧に対する耐圧を任意倍数の電圧とすることができる。また、第1の出力電流源と第2の出力電流源とは、第1の差動対トランジスタに流れる入力信号の電流に応じて変化する電流を流す電流制御によるものであり、非特許文献3の出力段の回路のように、ゲート−ソース間電圧が0からVDDのまでの電圧制御によるものでないため、ドライブする電流の制御にVDDより十分低いゲート−ソース間電圧で行うことができる。ここで、VDDより低いゲート−ソース間電圧とは、例えば0.5VDD程度またはそれ以下の電圧のことである。従って、ホットキャリアの問題を軽減することができる。

【0027】

前記出力段バイアス調整回路は、前記他方の出力段電源線を基準とした前記出力端子の電圧の絶対値がN2VDDであれば、前記第1の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値を(N2−1)×VDDとすると共に、前記第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値を出力端子側から順に(N2−M3)×VDD(但し、M3は出力端子側から第2の出力段電流源側までのMOSトランジスタに対応する1からN2−1までの整数)とし、前記他方の出力段電源線を基準とした前記出力端子の電圧が0Vであれば、前記第1の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値を(N2−M4)×VDD(但し、M4は第1の出力電流源側から出力端子側までの各MOSトランジスタに対応する1からN2−1までの整数)とすると共に、前記第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値をVDDとするのが望ましい。

【0028】

このようにして、他方の出力段電源線を基準として、出力端子から出力される出力電圧の絶対値が0VからN2VDDまでの間で変化しても、出力段バイアス調整回路を、上記バイアス電圧とするような調整回路とすることで、第1の出力段カスコードトランジスタ群、第2の出力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内とすることができる。

【0029】

前記出力段バイアス調整回路は、前記他方の出力段電源線を基準とした前記一方の出力段電源線の電圧の正負に応じて、それぞれ(N2−1)×VDDあるいは−(N2−1)×VDDの電圧を供給する電源に一端が接続されたN2−1個の直列接続された抵抗手段より成る第1の出力段カスコードバイアス用抵抗手段であって、前記第1の出力段カスコードバイアス用抵抗手段の隣り合う各抵抗手段の接続点が前記第1の出力段カスコードトランジスタ群の各MOSトランジスタのゲート端子に接続された前記第1の出力段カスコードバイアス用抵抗手段と、前記他方の電源線を基準とした前記一方の出力段電源線の電圧の正負に応じて、それぞれVDDあるいは−VDDの電圧を供給する電源に接続されたN2−1個の直列接続された抵抗手段より成る第2の出力段カスコードバイアス用抵抗手段であって、前記第2の出力段カスコードバイアス用抵抗手段の隣り合う各抵抗手段の接続点が前記第2の出力段カスコードトランジスタ群の隣り合う各MOSトランジスタのゲート端子に接続された前記第2の出力段カスコードバイアス用抵抗手段と、前記第1の出力段カスコードバイアス用抵抗手段の他端および前記第2の出力段カスコードバイアス用抵抗手段の他端の接続点と前記出力端子との間に接続された出力抵抗手段とを備えているのが望ましい。

【0030】

出力段バイアス調整回路を、第1の出力段カスコードバイアス用抵抗手段と、第2の出力段カスコードバイアス用抵抗手段と、出力抵抗手段とにより構成することで、他方の出力段電源線を基準として、出力端子から出力される出力電圧の絶対値が0VからN2VDDまでの間で変化しても、第1の出力段カスコードトランジスタ群と第2の出力段カスコードトランジスタ群へのバイアス電圧を調整した電圧に制御することができる。

【0031】

前記第1の出力電流源には、前記第1の差動対トランジスタの一方のMOSトランジスタの信号電流に略比例して変化する電流を流す機能を持たせ、前記第2の出力電流源には、前記第1の差動対トランジスタの他方のトランジスタの信号電流に略比例して変化する電流を流す機能を持たせるように、前記接続回路を構成することができる。

【0032】

また、前記第1の出力電流源または前記第2の出力電流源の少なくとも一方の電流源には、前記第1の差動対トランジスタの一方のトランジスタと他方のトランジスタの信号電流の差に応じてあるいは当該信号電流の差に略比例して変化する電流を流す機能を持たせるように、前記接続回路を構成することができる。

【0033】

上記入力段と上記出力段とを備えた増幅回路は、MOSトランジスタのドレイン、ゲートおよびソースをそれぞれバイポーラトランジスタのコレクタ、ベースおよびエミッタに置換して、回路接続関係を変更することなくMOSトランジスタをバイポーラトランジスタに置換することができる。

【0034】

なお、伝導極性について、バイポーラトランジスタの場合では、ベース領域をコレクタに向けて流れる電流を運ぶキャリアの極性を意味しており、それが電子であればnpnトランジスタ、正孔であればpnpトランジスタを意味する。つまり、伝導極性が同じとは、一方がnpnトランジスタであれば他方もnpnトランジスタ、一方がpnpトランジスタであれば他方もpnpトランジスタであり、タイプが同じであることを意味する。また、伝導極性が異なるとは、一方がnpnトランジスタであれば他方はpnpトランジスタ、一方がpnpトランジスタであれば他方はnpnトランジスタということを意味し、タイプが違うことを意味する。

【発明の効果】

【0035】

本発明は、コモンモード入力電圧が他方の入力段電源線を基準としてその絶対値が0VからN1VDDまで変化しても、入力段バイアス調整回路が第1の差動対トランジスタ、第1の入力段カスコードトランジスタ、第2の入力段カスコードトランジスタのそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内とすることにより、任意倍数の入力電圧でも耐えることができる高耐圧の入力段とすることが可能である。

【図面の簡単な説明】

【0036】

【図1】本発明の実施の形態に係る増幅回路の入力段を示す図である。

【図2】図1に示す増幅回路の入力段の入力段バイアス調整回路の基本的な構成を説明するための図である。

【図3】図2に示す入力段の第1の入力段カスコードトランジスタ群・第1の差動対トランジスタ・第2の入力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は他方の入力段電源線を基準として一対の入力端子へのコモンモード入力電圧が0Vの場合を示す図、(B)は同じくN1VDDの場合を示す図である。

【図4】図2に示す入力段のpトランジスタとnトランジスタとを置換し、一方の電源線の極性を、他方の電源線を基準として負に反転させた図である。

【図5】図4に示す入力段の第1の入力段カスコードトランジスタ群・第1の差動対トランジスタ・第2の入力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は他方の出力段電源線を基準として入力端子に入力されるコモンモード入力電圧が0Vの場合を示す図、(B)は同じくコモンモード入力電圧が−N1VDDの場合を示す図である。

【図6】図2に示す入力段の第1変形例を説明するための図である。

【図7】図6の入力段において、他方の入力段電源線を基準として一対の入力端子へのコモンモード入力電圧が0Vから2VDDの場合(N1=2)を示す図である。

【図8】図6の入力段において、他方の入力段電源線を基準として一対の入力端子へのコモンモード入力電圧が0Vから3VDDの場合(N1=3)を示す図である。

【図9】図6に示す入力段の第2変形例を説明するための図である。

【図10】図6に示す入力段の第3変形例を説明するための図である。

【図11】本発明の実施の形態に係る増幅回路の出力段を示す図である。

【図12】図11に示す増幅回路の出力段の出力段バイアス調整回路の基本的な構成を説明するための図である。

【図13】図12に示す出力段の第1の出力段カスコードトランジスタ群・第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は他方の出力段電源線を基準として出力電圧が0Vの場合を示す図、(B)は同じく、出力電圧がN2VDDの場合を示す図である。

【図14】図12に示す出力段のpトランジスタとnトランジスタとを置換し、一方の電源線の極性を、他方の電源線を基準として負に反転させた図である。

【図15】図14に示す出力段の第1の出力段カスコードトランジスタ群・第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は、他方の出力段電源線を基準として出力電圧が0Vの場合を示す図、(B)は同じく出力電圧が−N2VDDの場合を示す図である。

【図16】図12に示す出力段のN2=4の場合の第1変形例を説明するための図である。

【図17】図12に示す出力段のN2=3の場合の第2変形例を説明するための図である。

【図18】図12に示す出力段のN2=3の場合の第3変形例を説明するための図である。

【図19】本発明の実施の形態に係る増幅回路を示す図である。

【図20】接続回路として折り返しカスコード回路を用いた増幅回路を示す図である。

【図21】他の接続回路を用いた増幅回路を示す図である。

【図22】図9に示す入力段と、図18に示す出力段と、図19に示す接続回路とにより構成したシミュレーションのための増幅回路を示す図である。

【図23】図22に示す増幅回路を非反転型負帰還増幅回路として動作させたシミュレーションのための各条件を示す一覧表である。

【図24】シミュレーション結果の直流伝達特性曲線を示すグラフである。

【図25】従来の増幅回路の入力段を示す図である。

【図26】従来の増幅回路の入力段と出力段とを説明するため図である。

【図27】他の従来の増幅回路(デジタルバッファ回路)の出力段(出力回路)を示す図である。

【図28】ホットキャリア問題を説明するためのグラフである。

【発明を実施するための形態】

【0037】

本発明の実施の形態に係る増幅回路を図面に基づいて説明する。なお、以下の表記において、pトランジスタはpMOSトランジスタ、nトランジスタはnMOSトランジスタを示している。また、図中、「bias」は電圧バイアスまたは電流バイアスを示す。

【0038】

(増幅回路の入力段)

まず、増幅回路の入力段(入力回路)について、図1から図10に基づいて説明する。入力段の説明においては、定格電源電圧に対して1倍の電圧をVDD、2倍の電圧を2VDD、3倍の電圧を3VDD、N1倍(N1は2以上の整数)の電圧をN1VDDと称す。

図1に示す増幅回路の入力段は、一方の電源線と他方の電源線とにより供給される電圧と同じ値の電圧N1VDDのコモンモード入力電圧を入力できるものであり、一方の電源線を電圧がN1VDDの電源線、他方の電源線をグランド(電圧の基準節点)としたものである。増幅回路の入力段は、VDDより高い電源電圧を使用しているが、この電圧は外部から供給したり、LSI内部に設けたチャージポンプにより昇圧したりすることができる。

【0039】

この増幅回路の入力段は、一対の入力端子IN1,IN2を介して入力電圧(差動モード入力電圧およびコモンモード入力電圧)が入力される第1の差動対トランジスタ10と、第1の入力段電流バイアス手段20と、第1の入力段カスコードトランジスタ群30と、一対の第2の入力段カスコードトランジスタ群40と、一対の出力用トランジスタ対50と、入力段バイアス調整回路60とを備えている。

【0040】

第1の差動対トランジスタ10は、pトランジスタMI11とpトランジスタMI12とにより形成され、ソース同士が接続点C1で接続され、それぞれのゲートに入力端子IN1,IN2が接続されている。

第1の入力段電流バイアス手段20は、ソースが一方の電源線のN1VDDに接続されている。第1の入力段電流バイアス手段20は、第1の差動対トランジスタ10に第1の入力段カスコードトランジスタ群30を介して所定のバイアス電流を供給するもので、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMC11により形成されている。この第1の入力段電流バイアス手段20は、pトランジスタMC11と対となるトランジスタを設けることでカレントミラー回路構成とすることができる。

【0041】

第1の入力段カスコードトランジスタ群30は、N1−1個がカスコード接続された第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMIUA1〜MIUA(N1-1)により構成され、一端が第1の差動対トランジスタ10のそれぞれのpトランジスタMI11,MI12の2つのソース端子の接続点C1に接続され、他端が第1の入力段電流バイアス手段20のpトランジスタMC11のドレインに接続されている。

第2の入力段カスコードトランジスタ群40は、N1−1個がカスコード接続された第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMILA1〜MILA(N1-1)と、pトランジスタMILB1〜MILB(N1-1)により構成され、一端が第1の差動対トランジスタ10のそれぞれのpトランジスタMI11,MI12のドレインに接続され、他端が出力用トランジスタ対50に接続されている。

【0042】

出力用トランジスタ対50は、第1の差動対トランジスタ10と異なる伝導極性を有するnトランジスタMC21とnトランジスタMC31とから構成され、ゲートおよびドレインが出力段への接続回路へ接続され、ソースが他方の電源線であるグランドに接続されている。

【0043】

入力段バイアス調整回路60は、入力段におけるバイアスを調整する回路である。入力段バイアス調整回路60は、第1の入力段カスコードトランジスタ群30のそれぞれのゲートと、第2の入力段カスコードトランジスタ群40のそれぞれのゲートに接続されて、コモンモード入力電圧に応じて調整されたバイアス電圧を与えることで、一対の入力端子IN1,IN2に0VからN1VDDまでの間で変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のそれぞれのゲート−ソース間電圧(VGS)およびゲート−ドレイン間電圧(VGD)の絶対値がVDD以内となるように、第1の入力段カスコードトランジスタ群30および第2の入力段カスコードトランジスタ群40のバイアス電圧を調整する機能を備えている。

図1は、一方の電源線の電圧がN1VDD以上の場合を示しているが、この電圧を−N1VDD以下(絶対値がN1VDD以上)にして、MOSトランジスタの伝導極性をpトランジスタとnトランジスタとで相互に反転させれば、回路の接続関係を変更することなく同様の動作をさせることができる。

【0044】

ここで、入力段バイアス調整回路60は、図2に示すような構成とすることができる。なお、図2において、図1と同じ構成のものは同符号を付して説明を省略する。

入力段バイアス調整回路60は、レベルシフト手段を構成するpトランジスタMD1と、第1の入力段カスコードバイアス用抵抗手段61と、第2の入力段カスコードバイアス用抵抗手段62と、第1の抵抗手段63と、第2の抵抗手段64と、第1の入力段電流バイアス手段20のpトランジスタMC11と対となるpトランジスタMC12とを備えている。

【0045】

pトランジスタMD1は、第1の差動対トランジスタ10(pトランジスタMI11,MI12)の接続点C1に接続されたダイオード接続されたトランジスタであり、pトランジスタMI11,MI12のVGSに相当する電圧分またはそれ以上の電圧をレベルシフトするレベルシフト手段としての働きを担うものである。

第1の入力段カスコードバイアス用抵抗手段61は、第1の入力段カスコードトランジスタ群30のバイアス電圧として接続された(N1−1)×VDDに一端が接続されていると共に、第1の入力段カスコードトランジスタ群30の各ゲート間に接続されたN1−2個のほぼ同値の直列抵抗(抵抗RIU1〜RIU(N1-2))が接続されている。

第2の入力段カスコードバイアス用抵抗手段62は、pトランジスタMD1とグランドとの間にN1個のほぼ同値の直列抵抗(抵抗RIL1〜RILN1)が接続されていると共に、第2の入力段カスコードトランジスタ群40の各ゲートに直列抵抗の各接続点C21〜C2(N1-1)が接続されている。

【0046】

第1の抵抗手段63(抵抗RX)は、第1の入力段カスコードバイアス用抵抗手段61の他端に接続されている共に、VDDに接続されている。この抵抗RXの抵抗値は、第1の入力段カスコードバイアス用抵抗手段61の合計の抵抗値とほぼ同値(抵抗RX=抵抗RIU1+抵抗RIU2+・・・+抵抗RIU(N1-3)+抵抗RIU(N1-2))である。

【0047】

第2の抵抗手段64(抵抗R0)は、第1の入力段カスコードバイアス用抵抗手段61と、第1の抵抗手段63との接続点C3に一端が接続され、第1の差動対トランジスタ10(pトランジスタMI11,MI12)の接続点C1に他端が接続されている。この抵抗R0の抵抗値は、第1の入力段カスコードバイアス用抵抗手段61の各抵抗値とほぼ同値(抵抗R0=抵抗RIU1=抵抗RIU2=・・・=抵抗RIU(N1-3)=抵抗RIU(N1-2))である。第2の抵抗手段64は、第1の入力段カスコードバイアス用抵抗手段61と第1の抵抗手段63と共に、コモンモード入力電圧に応じて調整されたバイアス電圧を発生させる制御手段とも考えることができる。従って、後述するように他の制御手段に置き換えることもできる。また、コモンモード入力電圧に応じて制御されていればそれが必ずしも接続点C1に接続されている必要はない。

【0048】

以上のように構成された本発明の実施の形態に係る増幅回路の入力段の動作を図面に基づいて説明する。

入力端子IN1,IN2に0Vとなるコモンモード入力電圧が入力されたときには、説明を簡単にするために第1の差動対トランジスタ10のゲートソース間電圧を|pトランジスタMI11,MI12のVGS|≪VDDとしてVGSを無視すれば、接続点C1が略0Vとなるため、第1の入力段カスコードバイアス用抵抗手段61の各抵抗(抵抗RIU1〜RIU(N1-2))と第2の抵抗手段64(抵抗R0)とは、(N1−1)×VDDの電圧が印加された分割抵抗となる。また、そのとき接続点C3がVDDとなるため、抵抗RXからは電流が流れ込まない。従って、各抵抗の電圧降下はそれぞれVDDとなるため、第1の入力段カスコードトランジスタ群30のpトランジスタMIUA(N1-1)のゲート電圧として(N1−1)×VDD、pトランジスタMIUA(N1-2)のゲート電圧として(N1−2)×VDD、・・・pトランジスタMIUA2のゲート電圧として2VDD、pトランジスタMIUA1のゲート電圧としてVDDがバイアスされる(図3(A)参照)。従って、各pトランジスタMIUA1〜MIUA(N1-1)のVGSおよびVGDの絶対値がVDD以内となる。

【0049】

また、接続点C1が0Vであり、pトランジスタMD1を介した接続点C4はほぼ0Vとなるため、0Vとなった接続点C4とグランドとの間の第2の入力段カスコードバイアス用抵抗手段62の端子電圧はそれぞれが0Vとなる。従って、第2の入力段カスコードトランジスタ群40のpトランジスタMILA1〜MILA(N1-1)のゲート電圧およびpトランジスタMILB1〜MILB(N1-1)のゲート電圧は0Vとなる(図3(A)参照)。

【0050】

次に、入力端子IN1,IN2にN1VDDとなるコモンモード入力電圧が入力されたときには、接続点C1が略N1VDDとなるため、接続点C3の電圧は抵抗R0と抵抗Rxによる電圧分割により(N1−1)×VDDとなる。従って、第1の入力段カスコードバイアス用抵抗手段61の各抵抗(抵抗RIU1〜RIU(N1-2))には、全ての端子に同一の(N1−1)×VDDの電圧が印加された状態となるため、第1の入力段カスコードトランジスタ群30のpトランジスタMIUA1〜MIUA(N1-1)の各ゲートには、(N1−1)×VDDがバイアスされる(図3(B)参照)。

【0051】

また、N1VDDとなった接続点C1から、pトランジスタMD1と第2の入力段カスコードバイアス用抵抗手段62とを介してグランドに電流が流れるが、簡単とするためにpトランジスタMD1のゲートソース間電圧を|pトランジスタMD1のVGS|≪VDDとしてVGSを無視すれば、第2の入力段カスコードバイアス用抵抗手段62の各抵抗(抵抗RIL1〜RIL(N1-2))は、N1VDDの電圧が印加された分割抵抗となる。従って、各抵抗の電圧降下はVDDとなるため、第2の入力段カスコードトランジスタ群40のpトランジスタMILA1,MILB1のゲート電圧として(N1−1)×VDD、pトランジスタMILA2,MILB2のゲート電圧として(N1−2)×VDD、・・・pトランジスタMILA(N1-2),MILB(N1-2)のゲート電圧として2VDD、pトランジスタMILA(N1-1),MILB(N1-1)のゲート電圧としてVDDがバイアスされる(図3(B)参照)。従って、各pトランジスタMILA1〜MILA(N1-1),MILB1〜MILB(N1-1)のVGSおよびVGDの絶対値がVDD以内となる。

以上の動作説明では、説明を簡単とするために第1の差動対トランジスタ10のゲート−ソース間電圧VGSとpトランジスタMD1のゲート−ソース間電圧VGSを無視したが、この影響によるバイアス調整電圧の差は実質的には本発明の効果を損ねるものではない。

また、第1の差動対トランジスタ10のゲート−ソース間電圧VGSとpトランジスタMD1のゲート−ソース間電圧VGSの影響も考慮して抵抗Ro,Rx,抵抗RIL1の値を上記バイアス電圧により近くなるように調整することもできる。

【0052】

そして、それぞれの第2の入力段カスコードトランジスタ群40を流れる信号電流は、nトランジスタMC21とnトランジスタMC31とのそれぞれのドレインからソースに流れる。そのうちの少なくとも信号電流成分を次段である出力段に接続される接続回路への出力信号として出力することができる。

【0053】

このように、入力端子IN1,IN2に入力されたコモンモード入力電圧が0VからN1VDDまで変化しても、第1の入力段カスコードトランジスタ群30と第2の入力段カスコードトランジスタ群40へのバイアス電圧を調整した電圧に制御することができるので、本実施の形態に係る増幅回路の入力段は、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる。

【0054】

なお、ダイオード接続されたpトランジスタMD1と、第2の入力段カスコードバイアス用抵抗手段62の抵抗RIL1との接続関係は、必ずしも上記に限定されるものではない。pトランジスタMD1と第2の入力段カスコードバイアス用抵抗手段62の抵抗RIL1を入れ替えても回路動作は等価であることは自明である。すなわち、第2の入力段カスコードバイアス用抵抗手段62は、接続点C1とグランドの間にpトランジスタMD1を介して直列接続されたN1個の抵抗手段とすることもできる。

【0055】

図2に示す入力段は、pトランジスタとnトランジスタとを置換すると共に、一方の電源線を−N1VDDとし、他方の電源線をグランド(基準節点)として電位(極性)を反転させた図4に示す入力段とすることができる。なお、図4においては、pトランジスタとnトランジスタとの違いはあるが、理解がしやすいように、図2に対応させて符号を記載している。

図4に示す入力段では、入力端子IN1,IN2に0Vとなるコモンモード入力電圧が入力されたときには、nトランジスタMIUA(N1-1)のゲート電圧として−(N1−1)×VDD、nトランジスタMIUA(N1-2)のゲート電圧として−(N1−2)×VDD、・・・nトランジスタMIUA2のゲート電圧として−2VDD、nトランジスタMIUA1のゲート電圧として−VDDがバイアスされる。また、nトランジスタMILA1〜MILA(N1-1)のゲート電圧およびnトランジスタMILB1〜MILB(N1-1)のゲート電圧は0Vとなる(図5(A)参照)。従って、各nトランジスタMIUA1〜MIUA(N1-1)のVGSおよびVGDの絶対値をVDD以内とすることができる。

入力端子IN1,IN2に−N1VDDとなるコモンモード入力電圧が入力されたときには、nトランジスタMIUA1〜MIUA(N1-1)の各ゲートには、−(N1−1)×VDDがバイアスされる。また、nトランジスタMILA1,MILB1のゲート電圧として−(N1−1)×VDD、nトランジスタMILA2,MILB2のゲート電圧として−(N1−2)×VDD、・・・nトランジスタMILA(N1-2),MILB(N1-2)のゲート電圧として−2VDD、nトランジスタMILA(N1-1),MILB(N1-1)のゲート電圧として−VDDがバイアスされる(図5(B)参照)。従って、各nトランジスタMILA1〜MILA(N1-1),MILB1〜MILB(N1-1)のVGSおよびVGDの絶対値をVDD以内とすることができる。

【0056】

(入力段の第1変形例)

図2に示す増幅回路の入力段では、抵抗R0を第1の差動対トランジスタ10の接続点C1に接続していたが、図6に示すように分離することも可能である。

図6に示す増幅回路の入力段には、入力段バイアス調整回路60aとして、第1の差動対トランジスタ10に対応する第2の差動対トランジスタ11と、第1の入力段電流バイアス手段20に対応する第2の入力段電流バイアス手段21と、第1の入力段カスコードトランジスタ群30に対応する第3の入力段カスコードトランジスタ群31と、第2の入力段カスコードトランジスタ群40に対応する第4の入力段カスコードトランジスタ群41とが含まれている。

【0057】

第2の差動対トランジスタ11は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMI21とpトランジスタMI22とにより形成され、ソース同士が接続点C5で接続され、ドレイン同士が接続点C6で接続され、それぞれのゲートに入力端子IN1,IN2とが接続されている。

第2の入力段電流バイアス手段21は、第1の入力段電流バイアス手段20のpトランジスタMC11と共に、pトランジスタMC12とカレントミラー回路を構成し、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMC13により形成されている。

【0058】

第3の入力段カスコードトランジスタ群31は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMIUB1〜MIUB(N1-1)により形成され、第2の差動対トランジスタ11のソース同士を接続する接続点C5に一端が接続されている。

第4の入力段カスコードトランジスタ群41は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMILC1〜MILC(N1-1)により形成され、第2の差動対トランジスタ11のドレイン同士を接続する接続点C6とグランドとの間に接続されている。

pトランジスタMC13は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMC11と同様にソースがN1VDDに接続され、ドレインが第3の入力段カスコードトランジスタ群31に接続され、pトランジスタMC12とカレントミラー回路を構成する。

【0059】

このように第2の差動対トランジスタ11を新たに設け、第2の入力段電流バイアス手段21と、第3の入力段カスコードトランジスタ群31と、第4の入力段カスコードトランジスタ群41とを設けることで、図2と同様の動作をさせることができると同時に、出力段に伝送するための信号電流が流れる第1の差動対トランジスタ10と、第2の入力段カスコードバイアス用抵抗手段62および第1の入力段カスコードバイアス用抵抗手段61に流れる電流とを分離することができるので、第1の差動対トランジスタ10への悪影響を排除することができる。

【0060】

図6に示す増幅回路の入力段は、一般化した場合を示し、電源電圧をN1VDDとした例であるが、例えば、コモンモード入力電圧を2VDD(N1=2)とした場合には、図7に示すような回路とすることができる。また、コモンモード入力電圧を3VDD(N1=3)とした場合には、図8に示すような回路とすることができる。

【0061】

図7(N1=2の入力段)および図8(N1=3の入力段)を比較して判るように、コモンモード入力電圧の耐圧を2VDDとした場合には、第1の入力段カスコードトランジスタ群30,第3の入力段カスコードトランジスタ群31がpトランジスタMIUA1,MIUB1が1個ずつとなるため、pトランジスタMIUA1,MIUB1にはゲート電圧としてVDDをバイアスすればよい。従って、図6に示した第1の入力段カスコードバイアス用抵抗手段61と第1の抵抗手段63と、第2の抵抗手段64とが省略される。

このようにして、コモンモード電圧が定格電源電圧の任意の倍数電圧でも耐える増幅回路の入力段を設計することができる。

【0062】

(入力段の第2変形例)

図2,図4,図6における一般化した入力段バイアス調整回路60,60aの各抵抗手段(第1の入力段カスコードバイアス用抵抗手段61,第1の抵抗手段63,第2の抵抗手段64)は、以下で説明するように、コモンモード入力電圧により制御されるMOSトランジスタ回路に置換することができる。すなわち、抵抗手段の代わりに、MOSトランジスタによる可変抵抗手段、スイッチ手段、レベルシフト手段を使用することができる。そのことを図9に基づいて説明する。

図7に示す入力段は、図9に示すような入力段とすることもできる。図9に示す増幅回路の入力段は、定格電源電圧の2倍(VDDのN1倍の電圧をN1VDDと表記したときのN1=2の場合である。)のコモンモード入力電圧を入力可能とするものである。図9においては、一方の電源線の電圧はN1(=2)以上の3VDDが使用されている。なお、図9においては、図7と同じ構成のものは同符号を付して説明を省略する。

【0063】

図9に示す入力段の入力段バイアス調整回路60bは、ダイオード接続されたpトランジスタMD1のゲートとドレインとの接続点C10とグランドとの間に、カレントミラー回路構成のnトランジスタMC61,MC62のうちの一方のnトランジスタMC61が接続されてpトランジスタMD1に電流バイアスを与えている。この接続点C10には、第2の入力段カスコードトランジスタ群40,第4の入力段カスコードトランジスタ群41のpトランジスタMILA1,MILB1,MILC1のゲートが接続されている。

ダイオード接続されたpトランジスタMD1のソースは、接続点C11を介してpトランジスタMB1のソースに接続されている。pトランジスタMB1のゲートはVDDにバイアスされ、ドレインはグランドに接続されている。

【0064】

第1の入力段カスコードトランジスタ群30のpトランジスタMIUA1と、第3の入力段カスコードトランジスタ群31のpトランジスタMIUB1とは、VDDに固定バイアスされている。このpトランジスタMIUA1は、pトランジスタMIUA1と同じ伝導極性のpトランジスタMUX1を介在して第1の入力段電流バイアス手段20のpトランジスタMC11に接続されている。従って、第1の入力段カスコードトランジスタ群30のpトランジスタMIUA1には、バイアス電流が第1の入力段電流バイアス手段20から供給される。

また、このpトランジスタMIUB1はpトランジスタMIUB1と同じ伝導極性のpトランジスタMUY1を介在して第2の入力段電流バイアス手段21のpトランジスタMC13に接続されている。従って、第3の入力段カスコードトランジスタ群31のpトランジスタMIUB1には、バイアス電流が第2の入力段電流バイアス手段21から供給される。

【0065】

また、第2の差動対トランジスタ11にダイオード接続のpトランジスタMD2,MD3をそれぞれのゲートに接続している。これは、増幅回路をボルテージフォロワ等の非反転型帰還増幅回路に応用した際に、立ち上がりが急峻な矩形波を入力信号として入力したときにレスポンスが遅くなり、出力段から入力段への帰還信号が遅れて到達することによる不具合を解消するためのものである。

【0066】

次に、図9に示す入力段の動作について図面に基づいて説明する。

図9のpトランジスタMB1,nトランジスタMC61は図7の抵抗RIL1,RIL2に代わるもので、可変抵抗手段として機能するものである。入力端子IN1,IN2に入力されたコモンモード入力電圧が変化すると、第2の差動対トランジスタ11のpトランジスタMI21,MI22のゲートが制御され、コモンモード入力電圧に応じてpトランジスタMB1のソース(接続点C11)、pトランジスタMD1を介して、nトランジスタMC61のドレインが制御される。

【0067】

まず、入力端子IN1,IN2に、2VDDを超えないVDDを中心として増減するコモンモード入力電圧が入力されると、第1の差動対トランジスタ10のpトランジスタMI11,MI12のゲートが制御され、接続点C6,C10,C11の電圧が増減する。

【0068】

例えば、コモンモード入力電圧がVDDを超えた場合には、pトランジスタMB1のゲートがVDDによりバイアスされているため、第2の差動対トランジスタ11のpトランジスタMI21,MI22はカットオフ状態となり、接続点C11の電圧は一定値に保持される。従って、接続点C11とダイオード接続されたpトランジスタMD1を介した接続点C10の電圧は、接続点C11からpトランジスタMD1のVGS分降下した電圧となり、接続点C11の電圧は、pトランジスタMB1のゲート電圧VDDからVGS分高い電圧となる。つまり、接続点C10の電圧は、VDD+|pトランジスタMB1のVGS|−|pトランジスタMD1のVGS|≒VDDとなる。

【0069】

接続点C10がVDDとなることにより、第1の差動対トランジスタ10のpトランジスタMI11,MI12にカスケード接続されたpトランジスタMILA1,MILB1がVDDにバイアスされる。

従って、コモンモード入力電圧がVDDを超えて2VDDに到達しても、pトランジスタMI11,MI12のVGS,VGDと、pトランジスタMI21,MI22のVGS,VGDとは、その絶対値をVDD以内とすることができる。

図9に示す入力段で一方の電源線にN1VDD(=2)以上の3VDDを使用しているのはこの効果のためである。

【0070】

コモンモード入力電圧がVDDのとき、pトランジスタMIUA1,MIUB1は線形領域で動作している。更に、コモンモード入力電圧が増加して2VDDとなると、pトランジスタMUX1も線形領域で動作し始める。しかし、pトランジスタMC11,MC13はソースが3VDDに接続されているため活性領域での作動状態であるので、第1の差動対トランジスタ10への増幅動作に与える影響はほとんど無視できる。

【0071】

次に、コモンモード入力電圧がVDDより低くなると、接続点C11の電圧が下がり、pトランジスタMB1はカットオフとなる。接続点C11の電圧が下がると、pトランジスタMD1を介してnトランジスタMC61のドレイン(接続点C10)の電圧も下がる。このとき、接続点C10の電圧は、(コモンモード入力電圧)+|pトランジスタMI21のVGS|−|pトランジスタMD1のVGS|≒(コモンモード入力電圧)となる。従って、コモンモード入力電圧が0Vのとき、接続点C10の電圧も0Vとなり、この電圧が第2の入力段カスコードトランジスタ群40のゲートにバイアスされる。このとき、pトランジスタMIUA1とpトランジスタMIUB1のゲートはVDDにバイアスされている。従って、コモンモード入力電圧が0Vに到達しても、pトランジスタMI11,MI12のVGS,VGDと、pトランジスタMI21,MI22のVGS,VGDとは、その絶対値をVDD以内とすることができる。

【0072】

このように、pトランジスタMC11,MC13をN1=2VDDより高い電圧である3VDDに接続し、pトランジスタMUX1,MUY1を、第1の入力段カスコードトランジスタ群30と第3の入力段カスコードトランジスタ群31とにカスコード接続することで、コモンモード入力電圧が2VDDのときでもpトランジスタMC11とpトランジスタMC13を活性領域に維持できるので、第1の差動対トランジスタ10への増幅動作に与える影響を排除することができる。従って、入力段X1の性能を向上させることができる。

コモンモード入力電圧がVDDより小さいときに、差動対トランジスタMI11,MI12を活性領域で動作させるために、pトランジスタMD1のアスペクト比を小さくして|VGS|を大きく設定し、差動対トランジスタMI11,MI12の|VDS|が大きくなるようにするのが望ましい。

【0073】

以上の説明から明らかなように、図9に示す入力段バイアス調整回路60bのpトランジスタMB1,nトランジスタMC61は、図7に示す入力段バイアス調整回路60aの第2の入力段カスコードバイアス用抵抗手段62に代わるもので、コモンモード入力電圧によって制御される。pトランジスタMB1はレベルシフト手段を備えたスイッチ手段またはレベルシフト手段を備えた可変抵抗手段として動作し、また、nトランジスタMC61は可変抵抗手段として動作して入力段のバイアスを調整する。

【0074】

図9に示す入力段では、定格電源電圧の2倍となる2VDD(N1=2)よりVDD分ほど高い3VDDを一方の電源線としているため、第1の入力段カスコードトランジスタ群30と第1の入力段電流バイアス手段(pトランジスタMC11のドレイン)との間、および第3の入力段カスコードトランジスタ群31と第2の入力段電流バイアス手段(pトランジスタMC13のドレイン)との間に、それぞれ同じ伝導極性を有するpトランジスタMUX1,MUY1を1個ずつカスコード接続している。

そして、入力段の電源電圧が2VDDより2VDDだけ高い4VDDの場合では、同様に、第1の入力段カスコードトランジスタ群30と第1の入力段電流バイアス手段(pトランジスタMC11のドレイン)との間、および第3の入力段カスコードトランジスタ群31と第2の入力段電流バイアス手段(pトランジスタMC13のドレイン)との間に、それぞれ2個のpトランジスタを接続すればよいし、入力段の電源電圧が2VDDより3VDDだけ高い5VDDの場合ではそれぞれ3個のpトランジスタを接続すればよいというように、4VDD以上でも第1の入力段カスコードトランジスタ群30および第3の入力段カスコードトランジスタ群31と伝導極性が同じpトランジスタをカスコード接続して積み上げて、pトランジスタMC11またはMC13に接続すればよい。

つまり、一方の電源線の電源電圧と入力可能とするコモンモード入力電圧との差分からVDDの何倍であるかを算出して、VDDの倍数分のMOSトランジスタを第1の入力段カスコードトランジスタ群30と第3の入力段カスコードトランジスタ群31とのそれぞれにカスコード接続することで、入力可能とするコモンモード入力電圧以上の電源電圧を一方の電源線とすることができる。

【0075】

図9においては、N1=2の場合であるが、更に、N1が3以上の場合にも同様である。すなわち、例えば、コモンモード入力電圧の最大値がMOSトランジスタの定格電源電圧の3倍となる3VDD(N1=3)の場合、それよりVDD分ほど高い4VDDを一方の電源線として使用し、第1の入力段カスコードトランジスタ群30と第3の入力段カスコードトランジスタ群31とに、同じ伝導極性を有するpトランジスタを1つカスコード接続すればよいし、2VDD高い5VDDの場合は前記pトランジスタをそれぞれ2個カスコード接続すればよい。このように、一方の電源線の電源電圧の絶対値を他方の電源線を基準としてN1VDDより大きくするこの手法は、図7、図9の回路に限定されず、本発明に係るすべての入力段に適用することができる。

【0076】

(入力段の第3変形例)

図8に示す入力段は、図10に示すような入力段とすることもできる。図10に示す増幅回路の入力段は、定格電源電圧の3倍(VDDのN1倍の電圧をN1VDDと表記したときのN1=3の場合である。)のコモンモード入力電圧を入力可能とするものである。なお、図10においては、図8と同じ構成のものは同符号を付して説明を省略する。また、図10においては、第2の差動対トランジスタ11に付加された図9に示すダイオード接続のpトランジスタMD2,MD3は省略されている。

【0077】

図10に示す入力段バイアス調整回路60cは、カレントミラー回路構成のpトランジスタMC71,MC72のソースが2VDDに接続されている。pトランジスタMC71のドレインには、VDDによりゲートがバイアスされたnトランジスタMB2のドレインが接続されている。pトランジスタMC72のドレインには、VDDにドレインが接続されたpトランジスタMB3のソースが接続されている。

【0078】

pトランジスタMC72とpトランジスタMB3との接続点C12には、第3の入力段カスコードトランジスタ群31のpトランジスタMIUB1のゲートと、pトランジスタMB4のゲートとが接続されている。また、pトランジスタMB4のソースは、pトランジスタMIUB1のドレインと接続点C13で接続されている。

pトランジスタMB3のゲートには、ダイオード接続されたpトランジスタMD1のゲートおよびドレインが接続されていると共に、第2,第4の入力段カスコードトランジスタ群40,41のpトランジスタMILA1〜MILC1のゲートが、接続点C14により接続されている。

【0079】

pトランジスタMB4のドレインには、ゲートがVDDでバイアスされ、ドレインがグランドに接続されたpトランジスタMB5のソースが接続されている。

接続点C14に、ゲートがVDDによりバイアスされたnトランジスタMB6のドレインが接続されている。nトランジスタMB6のソースは、接続点C15によりnトランジスタMC61と共に、nトランジスタMC62とカレントミラー回路を構成するnトランジスタMC63のドレインが接続されている。また、接続点C15には、第2,第4の入力段カスコードトランジスタ群40,41のpトランジスタMILA2〜MILC2のゲートが接続されている。

【0080】

以上のように構成された入力段の第3変形例の動作を説明する。

図10のpトランジスタMB3,MC72は、図8の第1の抵抗手段(抵抗Rx)、第1の出力段カスコードバイアス用抵抗手段111の抵抗手段RIU1に代わるものである。また、図10のpトランジスタMB4は図8の抵抗RIL1に代わり、nトランジスタMB6,MC63は抵抗RIL2,RIL3に代わるものである。入力端子IN1,IN2に入力されたコモンモード入力電圧が変化すると、第2の差動対トランジスタ11のpトランジスタMI21,MI22のゲートが制御され、コモンモード入力電圧に応じてpトランジスタMB4のソース(接続点C13)、pトランジスタMD1を介して、pトランジスタMB3のゲート、nトランジスタMB6のドレイン、nトランジスタMC63ソースが制御される。

コモンモード入力電圧が1.5VDDの値を中心に増減すると、コモンモード入力電圧に応じてpトランジスタMB4のソース電圧(接続点C13)・ドレイン電圧(接続点C16)、nトランジスタMB6のドレイン電圧(接続点C14)・ソース電圧(接続点C15)、pトランジスタMILC1のソース電圧(接続点C6)・ドレイン電圧(接続点C17)が増減する。

【0081】

(1)コモンモード入力電圧≧2VDD−|Vthp|(但し、Vthpは、pトランジスタの閾値電圧を示す。)

まず、コモンモード入力電圧が2VDD−|Vthp|以上である場合を説明する。

pトランジスタMB3がオフであり、pトランジスタMC72はオンであるから接続点12の電圧は2VDD、接続点C15の電圧は(VDD−nトランジスタMB6のVGS)である。

コモンモード入力電圧が2VDDを少し超えると、pトランジスタMB4のゲートが2VDDで固定であるので、第2の差動対トランジスタ11のpトランジスタMI21,MI22はオフとなり、接続点C13は一定値に保持される。従って、接続点C14は、2VDD+|pトランジスタMB4のVGS|−|pトランジスタMD1のVGS|であることから、ほぼ2VDDに保持される。

【0082】

pトランジスタMILA1,MILB1のゲートは、2VDDに保持されるので、コモンモード入力電圧が2VDDを超えて3VDDになっても、第1の差動対トランジスタ10のpトランジスタMI11,MI12のVGDはVDD以内に保持される。また、第2の差動対トランジスタ11のpトランジスタMI21,MI22のVGDも同様にVDD以内に保持される。

【0083】

このとき、pトランジスタMIUA1,MIUB1,MIUA2,MIUB2は線形領域で動作している。しかし、pトランジスタMC11が活性領域である限り、第1の差動対トランジスタ10に与える影響はほとんど無視できる。

更に、コモンモード入力電圧が増大して3VDD−|Vthp|に近づくと、pトランジスタMC11,MC13も線形領域に入る。また、pトランジスタMI11,MI12はオフとなり、増幅作用がなくなる。これが増幅作用を保持できるコモンモード入力電圧の上限となる。但し、このコモンモード入力電圧の上限は、本発明の技術を用いたnMOS差動対トランジスタを備えた入力段を併用することで、あるいは図10で説明した手法で、拡大することが可能である。

【0084】

(2)VDD−|Vthp|<コモンモード入力電圧<2VDD−|Vthp|

コモンモード入力電圧が2VDD−|Vthp|から減少すると、pトランジスタMB4がオフであるため、接続点C13、接続点C14の電圧が低下する。更に、pトランジスタMB3がオンとなるため接続点C12がコモンモード入力電圧に応じて制御される。

ここで、接続点C13の電圧は、(コモンモード入力電圧)+|pトランジスタMI21のVGS|となるから、接続点C14の電圧は、(コモンモード入力電圧)+|pトランジスタMI21のVGS|−|pトランジスタMD1のVGS|となる。従って、接続点C12の電圧は、(コモンモード入力電圧)+|pトランジスタMI21のVGS|−|pトランジスタMD1のVGS|+|pトランジスタMB3のVGS|となるため、コモンモード入力電圧の電圧低下に伴って、pトランジスタMIUA1,MIUB1,MB4,MILA1〜MILC1のゲート電圧が制御される。また、図9の回路動作で説明したように、pトランジスタMD1のアスペクト比を小さくして|VGS|を大きく設定し、第1の差動対トランジスタ10のpトランジスタMI11,MI12の|VDS|が大きくなるようにpトランジスタMILA1,MILB1のゲート電圧が制御されることで、第1の差動対トランジスタ10のpトランジスタMI11,MI12が線形領域に入ることを防止する。

【0085】

(3)コモンモード入力電圧≦VDD−|Vthp|

コモンモード入力電圧がVDD−|Vthp|以下であると、pトランジスタMB3のゲート電圧である接続点C14の電圧が下がってもpトランジスタMB3のソース電圧となる接続点C12の電圧はVDD以下に下がることができないため、接続点C12の電圧はほぼVDDに固定される。一方、接続点C14の電圧は、(コモンモード入力電圧)+|pトランジスタMI21のVGS|−|pトランジスタMD1のVGS|となるため、コモンモード入力電圧に応じて更に電圧が低下する。コモンモード入力電圧が更に低下すると、nトランジスタMB6が線形領域に入り、接続点C15も低下し始める。

【0086】

これにより、pトランジスタMILA1,MILB1,MILA2,MILB2のゲート電圧が減少することで、pトランジスタMI11,MI12の|VDS|が小さくなることによるpトランジスタMI11,MI12の線形領域への移行を防止する。

コモンモード入力電圧が減少するにつれて、接続点C1の電圧が低下するが、pトランジスタMIUA1のゲート電圧はVDDに固定され、pトランジスタMIUA2のゲート電圧は2VDDに固定されるので、pトランジスタMIUA1,MIUA2,MC11のVGDをVDD以内に保持することができる。また、同様に、pトランジスタMIUB1,MIUB2,MC13のVGDもVDD以内に保持することができる。

【0087】

従って、コモンモード入力電圧が0Vから3VDDまで変動しても、入力段の全てのトランジスタのVGS,VGDの絶対値をVDD以内に保持することができる。

以上の説明から明らかなように、図10に示す入力段バイアス調整回路60cのpトランジスタMB4とpトランジスタMB5、更にnトランジスタMB6,MC63は、図2に示す入力段バイアス調整回路60の第2の入力段カスコードバイアス用抵抗手段62に代わるものである。

また、pトランジスタMB4,MB5およびnトランジスタMB6,MC63は、コモンモード入力電圧によって制御され、レベルシフト手段を備えたスイッチ手段またはレベルシフト手段を備えた可変抵抗手段または可変抵抗手段として動作し、入力段のバイアスを調整する。また、図10に示すpトランジスタMC72は、図2に示す入力段バイアス調整回路60の第1の入力段カスコードバイアス用抵抗手段61に代わるものである。更に、図10に示すpトランジスタMB3は、図2に示す第1の抵抗手段63と第2の抵抗手段64とに代わるものである。

そして、図2の回路では第1の入力段カスコードバイアス用抵抗手段61と第1の抵抗手段63からなる回路のバイアス電圧が第2の抵抗手段64を介してコモンモード入力電圧により制御されるが、図10の回路では、pトランジスタMB3のゲート−ソースを介してコモンモード入力電圧によりpトランジスタMC72が制御されることになる。このとき、pトランジスタMC72は可変抵抗手段またはスイッチ手段として、pトランジスタMB3はレベルシフト手段を備えたスイッチ手段またはレベルシフト手段を備えた可変抵抗手段として動作し、入力段のバイアスを調整する。

【0088】

(増幅回路の出力段)

次に、増幅回路の出力段(出力回路)について、図11から図18に基づいて説明する。なお、出力段の説明においては、定格電源電圧VDDに対して1倍の電圧をVDD、2倍の電圧を2VDD、3倍の電圧を3VDD、N2倍(N2は2以上の整数)の電圧をN2VDDと称す。

図11に示す増幅回路の出力段は、コモンモード入力電圧に応じて定格電源電圧のN2倍の信号が出力できるものである。増幅回路の出力段は、入力段と同様に、VDDより高い電源電圧を使用しているが、この電圧は外部から供給したり、LSI内部に設けたチャージポンプにより昇圧したりすることができる。

【0089】

この増幅回路の出力段は、第1の出力電流源70と、第2の出力電流源80と、第1の出力段カスコードトランジスタ群90と、第2の出力段カスコードトランジスタ群100と、出力段バイアス調整回路110とを備えている。

【0090】

第1の出力段電流源70は、pトランジスタMC41により形成されている。pトランジスタMC41は、ソースが一方の出力段電源線であるN2VDDに接続され、図1に示す第1の差動対トランジスタ10の一方のトランジスタであるpトランジスタMI11に流れる電流に応じて変化する電流を流す機能を有するものである。

第2の出力段電流源80は、第2の出力段カスコードトランジスタ群100のMOSトランジスタと同じ伝導極性を有するnトランジスタMC51により形成されている。nトランジスタMC51は、ソースが他方の出力段電源線であるグランドに接続され、図1に示す、第1の差動対トランジスタ10の他方のトランジスタであるpトランジスタMI12に流れる電流に応じて変化する電流を流す機能を有するものである。

【0091】

第1の出力段カスコードトランジスタ群90は、出力端子OUTに一端が接続され、他端が第1の出力段電流源70(pトランジスタMC41)に接続された、第1の出力段電流源70と同じ伝導極性を有するN2−1個のpトランジスタMOU1〜MOU(N2-1)がカスコード接続されたものである。

第2の出力段カスコードトランジスタ群100は、出力端子OUTに一端が接続され、他端が第1の出力段電流源70に接続された、第1の出力段カスコードトランジスタ群90と異なる伝導極性を有するN2−1個のnトランジスタMOL1〜MOL(N2-1)がカスコード接続されたものである。

【0092】

出力段バイアス調整回路110は、出力端子OUTの電圧が0VからN2VDDまでの間で変化したときに、第1の出力段カスコードトランジスタ群90と第2の出力段カスコードトランジスタ群100とのそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値がVDD以内となるようにバイアス電圧を調整するものである。

【0093】

ここで、出力段バイアス調整回路110は、図12に示すような構成とすることができる。なお、図12において、図11と同じ構成のものは同符号を付して説明を省略する。

出力段バイアス調整回路110は、第1の出力段カスコードバイアス用抵抗手段111と、第2の出力段カスコードバイアス用抵抗手段112と、出力抵抗手段113とを備えている。

【0094】

第1の出力段カスコードバイアス用抵抗手段111は、(N2−1)×VDDの電圧を有する電源に一端が接続されていると共に、第1の出力段カスコードトランジスタ群90の各ゲートに接続されたN2−2個の抵抗ROU1〜ROU(N2-2)が直列接続されたものである。この各抵抗ROU1〜ROU(N2-2)は略同じ抵抗値(同値)である。

【0095】

第2の出力段カスコードバイアス用抵抗手段112は、一端がVDDの電圧を有する電源に接続されていると共に、第2の出力段カスコードトランジスタ群100の各ゲートに接続されたN2−2個の抵抗ROL1〜ROL(N2-2)が直列接続されたものである。この各抵抗ROL1〜ROL(N2-2)は略同じ抵抗値で、かつ抵抗ROU1〜ROU(N2-2)とも同じ抵抗値である。

【0096】

出力抵抗手段113(ROUT)は、第1の出力段カスコードバイアス用抵抗手段111の他端および第2の出力段カスコードバイアス用抵抗手段112の他端の接続点C7と、出力端子OUTとの間に接続されている。この出力抵抗手段113は、第1の出力段カスコードバイアス用抵抗手段111および第2の出力段カスコードバイアス用抵抗手段112の各抵抗と略同じ抵抗値である。

【0097】

以上のように構成された本発明の実施の形態に係る増幅回路の出力段の動作を図12に基づいて説明する。

出力端子OUTの電圧が0Vとなった場合には、第1の出力段カスコードバイアス用抵抗手段111の各抵抗ROU1〜ROU(N2-2)と出力抵抗手段113(ROUT)とは、(N2−1)×VDDの電圧が印加された分割抵抗となる。また、接続点C7がVDDとなることから、第2の出力段カスコードバイアス用抵抗手段112側からは電流が流れ込まない。従って、第1の出力段カスコードバイアス用抵抗手段111の各抵抗の電圧降下はVDDとなるため、第1の出力段カスコードトランジスタ群90のpトランジスタMOU(N2-1)のゲート電圧として(N2−1)×VDD、pトランジスタMOU(N2-2)のゲート電圧として(N2−2)×VDD、・・・pトランジスタMOU2のゲート電圧として2VDD、pトランジスタMOU1のゲート電圧としてVDDがバイアスされる。従って、各pトランジスタMOU1〜MOU(N2-1)のVGSおよびVGDの絶対値がVDD以内となる(図13(A)参照)。

【0098】

また、接続点C7がVDDとなることから、第2の出力段カスコードバイアス用抵抗手段112の全ての抵抗の端子電圧はVDDとなるため、第2の出力段カスコードトランジスタ群100のnトランジスタMOL1〜MOL(N2-1)のゲート電圧はVDDとなる(図13(A)参照)。

【0099】

出力端子OUTの電圧がN2VDDとなった場合には、接続点C7の電圧は出力抵抗手段113による電圧降下により(N2−1)×VDDとなる。従って、第1の出力段カスコードバイアス用抵抗手段111の全ての抵抗ROU1〜ROU(N2-2)の端子電圧は(N2−1)×VDDとなるため、第1の出力段カスコードトランジスタ群90のpトランジスタMOU1〜MOU(N2-1)の各ゲートには、(N2−1)×VDDがバイアスされる。

【0100】

また、接続点C7の電圧が(N2−1)×VDDであることから、第2の出力段カスコードバイアス用抵抗手段112の各抵抗ROL1〜ROL(N2-2)は、一端に(N2−1)×VDDが、他端にVDDが印加された分割抵抗となる。従って、各抵抗の電圧降下はVDDとなるため、第2の出力段カスコードトランジスタ群100のnトランジスタMOL1のゲート電圧として(N2−1)×VDD、nトランジスタMOL2のゲート電圧として(N2−2)×VDD、・・・nトランジスタMOL(N2-2)のゲート電圧として2VDD、nトランジスタMOL(N2-1)のゲート電圧としてVDDがバイアスされる。従って、各nトランジスタMOL1〜MOL(N2-1)のVGSおよびVGDの絶対値がVDD以内となる(図13(B)参照)。

【0101】

このように、出力端子OUTの出力電圧が他方の出力段電源線であるグランドを基準として、その絶対値が0VからN2VDDまで変化しても、出力段バイアス調整回路110が、第1の出力段カスコードトランジスタ群90と第2の出力段カスコードトランジスタ群100へのバイアス電圧を調整した電圧に制御することができるので、本実施の形態に係る増幅回路の出力段は、出力電圧が定格電源電圧VDDの任意倍数の電圧でも耐えることができる。

【0102】

第1の出力段カスコードトランジスタ群90と、第2の出力段カスコードトランジスタ群100とを、いずれもN2−1個で実現できるため、特許文献2に記載の出力段より、トランジスタを一方の出力段電源線側と他方の出力段電源線(グランド線)側とで2個少なく構成することができる。従って、高耐圧の出力段を少ないトランジスタ数で実現することができるので、トランジスタによる占有面積を小さいものとすることができるため、回路の小型化に寄与する。

【0103】

図12に示す出力段は、pトランジスタとnトランジスタとを置換すると共に、一方の出力段電源線を−N2VDDとし、他方の出力段電源線をグランド(基準節点)として電位(極性)を反転させた図14に示す出力段とすることができる。なお、図14においては、pトランジスタとnトランジスタとの違いはあるが、理解がしやすいように、図12に対応させて符号を記載している。

図14に示す出力段では、出力端子OUTの電圧が0Vとなった場合には、nトランジスタMOU(N2-1)のゲート電圧として−(N2−1)×VDD、nトランジスタMOU(N2-2)のゲート電圧として−(N2−2)×VDD、・・・nトランジスタMOU2のゲート電圧として−2VDD、nトランジスタMOU1のゲート電圧として−VDDがバイアスされる。従って、各nトランジスタMOU1〜MOU(N2-1)のVGSおよびVGDの絶対値がVDD以内となる。また、pトランジスタMOL1〜MOL(N2-1)のゲート電圧は−VDDとなる(図15(A)参照)。

出力端子OUTの電圧が−N2VDDとなった場合には、nトランジスタMOU1〜MOU(N2-1)の各ゲートには、−(N2−1)×VDDがバイアスされる。また、pトランジスタMOL1のゲート電圧として−(N2−1)×VDD、pトランジスタMOL2のゲート電圧として−(N2−2)×VDD、・・・pトランジスタMOL(N2-2)のゲート電圧として−2VDD、pトランジスタMOL(N2-1)のゲート電圧として−VDDがバイアスされる。従って、各pトランジスタMOL1〜MOL(N2-1)のVGSおよびVGDの絶対値がVDD以内となる(図15(B)参照)。

【0104】

(出力段の第1変形例)

図12に示す出力段バイアス調整回路110は、図16に示すような出力段バイアス調整回路110aとすることもできる。図16に示す増幅回路の出力段は、出力電圧範囲を4VDDとした出力段の一例である(N2=4)。なお、図16においては、図12と同じ構成のものは同符号を付して説明を省略する。

【0105】

図16に示すように、出力段バイアス調整回路110aは、3VDDと接続点C7との間に、第1の出力段カスコードバイアス用抵抗手段111(図12参照)として、直列接続した抵抗ROUA1と抵抗ROUA2と、抵抗ROUB1とが並列接続されている。第1の出力段カスコードトランジスタ群90のpトランジスタMOU1のゲートは接続点C7に接続されている。pトランジスタMOU2のゲートは、抵抗ROUA1と抵抗ROUA2との接続点C8に接続されている。pトランジスタMOU3のゲートは、抵抗ROUA2の他の端子、すなわち3VDDに接続されている。

【0106】

また、VDDと接続点C7との間に、第2の出力段カスコードバイアス用抵抗手段として、直列接続した抵抗ROLA1および抵抗ROLA2と、抵抗ROLB1とが並列接続されている。第2の出力段カスコードトランジスタ群100のnトランジスタMOL1のゲートは接続点C7に接続されている。nトランジスタMOL2のゲートは、抵抗ROLA1と抵抗ROLA2との接続点C9に接続されている。nトランジスタMOL3のゲートは、抵抗ROLA2の他の端子、すなわちVDDに接続されている。

【0107】

なお、抵抗値であるが、抵抗ROUT=1/2としたときに、抵抗ROUA1=抵抗ROUA2=抵抗ROLA1=抵抗ROLA2=1、抵抗ROUB1=抵抗ROLB1=2となる比率とする。

抵抗ROUA1,ROUA2,ROUB1の3つの抵抗は、接続点C8の電圧に注目した等価変換により図12に示す抵抗ROU1〜ROU(N2-2)においてN2=4にした場合に容易に変換できる。すなわち、ROUB1を2分割して、その分割点を接続点C8に接続しても接続点C8の電圧は不変である。また、同様に、抵抗ROLA1,ROLA2,ROLB1の3つの抵抗は、接続点C9の電圧に注目した等価変換により図12に示す抵抗ROL1〜ROL(N2-2)においてN2=4にした場合に容易に変換できる。従って、図16に示す出力段バイアス調整回路110aは、図12に示す出力段バイアス調整回路110と実質的に等価であると言える。

【0108】

このように、出力段バイアス調整回路110aが構成されているので、出力電圧が4VDDとなった場合には、接続点C7,C8が3VDDとなることにより、pトランジスタMOU1,MOU2,nトランジスタMOL1のゲート電圧として3VDDがバイアスされる。また、接続点C9が2VDDとなることにより、nトランジスタMOL2のゲート電圧として2VDDがバイアスされる。

【0109】

また、出力電圧が0Vとなった場合には、接続点C8が2VDDとなることで、pトランジスタMOU2のゲート電圧として2VDDがバイアスされる。また、接続点C7,C9がVDDとなることで、pトランジスタMOU1,nトランジスタMOL1,MOL2のゲート電圧としてVDDがバイアスされる。従って、出力電圧が0Vから4VDDの間で変動したとしても、各pトランジスタMOU1〜MOU3とnトランジスタMOL1〜MOL3とのVGSおよびVGDの絶対値がVDD以内となる。

【0110】

(出力段の第2変形例)

また、図12に示す出力段バイアス調整回路110は、図17に示すような出力段バイアス調整回路110bとすることもできる。図17に示す増幅回路の出力段は、出力電圧範囲を3VDDとした出力段の一例である(N2=3)。なお、図17においては、図12と同じ構成のものは同符号を付して説明を省略する。

【0111】

図17に示す増幅回路の出力段は、第1の出力段カスコードバイアス用抵抗手段111、第2の出力段カスコードバイアス用抵抗手段112(図12参照)の代わりに、第1の出力段カスコードバイアス用トランジスタ群114と、第2の出力段カスコードバイアス用トランジスタ群115とを備えたものである。一般的には、第1の出力段カスコードバイアス用トランジスタ群114は、第1の出力段カスコードトランジスタ群を構成するMOSトランジスタと異なる伝導極性を有する(N2−2)個のMOSトランジスタより構成され、第2の出力段カスコードバイアス用トランジスタ群115は、第2の出力段カスコードトランジスタ群を構成するMOSトランジスタと異なる伝導極性を有する(N2−2)個のMOSトランジスタより構成される。従って、図17の場合は、N2=3の場合に相当するので、第1の出力段カスコードバイアス用トランジスタ群114は、1個のnトランジスタMUにより構成され、第2の出力段カスコードバイアス用トランジスタ群115は、1個のpトランジスタMLにより形成されている。

【0112】

pトランジスタMOU2のゲート電圧は2VDDに固定バイアスされている。また、nトランジスタMOL2のゲート電圧はVDDに固定バイアスされている。

出力電圧が2VDDより高くなり3VDDとなった場合、つまり、出力電圧の電圧が、(2VDD+nトランジスタMUのVthn−|pトランジスタMOU1のVGS|)より大きくなった場合に、nトランジスタMUがオンとなり、pトランジスタMOU1,nトランジスタMOL1のゲート電圧が2VDDとなる(但し、Vthnはnトランジスタの閾値電圧)。

【0113】

また、出力電圧がVDDより低くなり0Vとなった場合、つまり、出力電圧が、(VDD−|pトランジスタMLのVthp|+nトランジスタMOL1のVGS)より小さくなった場合に、pトランジスタMLがオンとなり、pトランジスタMOU1,nトランジスタMOL1のゲート電圧がVDDとなる。つまり、この2つのMOSトランジスタ(nトランジスタMU,pトランジスタML)は、ゲートバイアスが変動することにより電流が大きく変動するものであるため、等価的に可変抵抗と同じような機能と考えられる。従って、nトランジスタMUが第1の出力段カスコードバイアス用抵抗手段として機能し、pトランジスタMLが第2の出力段カスコードバイアス用抵抗手段として機能する。

これは、出力電圧範囲を3VDDとしたN2=3のみならず、N2≧4でも、第1の出力段カスコードトランジスタ群90のそれぞれのpトランジスタMOU1〜MOU(N2-1)に対応させてnトランジスタMUと同等のnトランジスタを設け、また第2の出力段カスコードトランジスタ群100のそれぞれのnトランジスタMOL1〜MOL(N2-1)に対応させてpトランジスタMLと同等のnトランジスタを設けることで成立させることができる。

【0114】

従って、出力電圧が0Vから3VDDの間で変動したとしても、各pトランジスタMOU1,MOU2とnトランジスタMOL1,MOL2とのVGSおよびVGDの絶対値がVDD以内となる。

【0115】

(出力段の第3変形例)

また、図12に示す出力段バイアス調整回路110は、図18に示すような出力段バイアス調整回路110cとすることもできる。図18に示す増幅回路の出力段は、出力電圧範囲を3VDDとした出力段の一例である(N2=3)。

なお、図18においては、図12と同じ構成のものは同符号を付して説明を省略する。また、図18に示す出力段は、図12に示す出力段と基本的に動作は同じであるため説明を省略する。

【0116】

第1の出力段カスコードバイアス用抵抗手段111の抵抗ROU1と第2の出力段カスコードバイアス用抵抗手段112の抵抗ROL1とには、コンデンサCU,CLが並列接続されている。出力段バイアス調整回路110cにコンデンサCU,CLを設けることで、接続点C7の電圧の過渡レスポンスを改良することができる。

なお、図18に示す出力段バイアス調整回路110cは、出力電圧範囲を3VDD(N2=3)としたものであるが、N2≧4の場合でも第1の出力段カスコードバイアス用抵抗手段111と第2の出力段カスコードバイアス用抵抗手段112とにコンデンサCU,CLを並列接続することで過渡レスポンスを改良することができる。

【0117】

(増幅回路)

次に、本実施の形態に係る増幅回路について、図19に基づいて説明する。なお、図19においては、図1および図11と同じ構成のものは同符号を付して説明を省略する。

図19に示す増幅回路は、CMOSによる集積回路としてLSI内に内蔵することが可能な増幅回路である。

入力段については定格電源電圧のN1倍のコモンモード入力電圧を入力可能とし、出力段については定格電源電圧のN2倍の出力電圧が出力可能とするものであるが、図19に示す増幅回路は、N1=N2の回路例であるため、N1およびN2を単にNと称す。図20および図21においても、同様にN1=N2=Nとする。

【0118】

図19に示す増幅回路は、図1に示す入力段を入力段X1とすると共に、図11に示す出力段を出力段X2とし、この入力段X1と出力段X2とを接続回路X3とにより接続したものである。

この増幅回路例における接続回路X3には、nトランジスタMC22と、入力段のnトランジスタMC21のドレインとゲートとを接続しその接続点とMC22のゲートとを接続する回路と、ドレインとゲートとを接続したpトランジスタMC42と、pトランジスタMC42のゲートと出力段のpトランジスタMC41とを接続する接続線と、接続用カスコードトランジスタ群120と、入力段の出力用トランジスタ対50のnトランジスタMC31のドレインとゲートと接続し、さらにnトランジスタMC31および出力段のnトランジスタMC51のゲート同士を接続する接続線と、絶対値がNVDDの電圧を供給する電源線と、グランド線と、が設けられている。

【0119】

nトランジスタMC22は、入力段X1の出力用トランジスタ対50の一方のトランジスタであるnトランジスタMC21と共に、第1のカレントミラー回路51を構成するトランジスタである。

pトランジスタMC42は、第1の出力電流源70であるpトランジスタMC41と共に、カレントミラー回路を構成するトランジスタである。

接続用カスコードトランジスタ群120は、pトランジスタMC42とnトランジスタMC22とを結ぶ経路に、N−1個がカスコード接続されたnトランジスタMC22と同じ伝導極性を有するnトランジスタMO1〜MO(N-1)により形成されている。

【0120】

以上のように構成された増幅回路の動作を説明する。

nトランジスタMC22は、入力段X1のnトランジスタMC21とカレントミラー回路を構成するため、入力端子IN1,IN2に入力される差動モード入力電圧に応じた電流が、nトランジスタMC22から、接続用カスコードトランジスタ群120を介してpトランジスタMC42に流れる。pトランジスタMC42はpトランジスタMC41とカレントミラー回路を構成するため、nトランジスタMC22に流れる電流に応じた電流がpトランジスタMC41から出力段X2の第1の出力段カスコードトランジスタ群90へ流れる。

【0121】

また、入力端子IN1,IN2に入力される差動モード入力電圧に応じた電流が、nトランジスタMC31に流れると、nトランジスタMC31に流れる電流に応じた電流がnトランジスタMC31とカレントミラー回路を構成するnトランジスタMC51に流れる。従って、出力段X2の第2の出力段カスコードトランジスタ群100へ、nトランジスタMC31に流れる電流に応じた電流が流れる。従って、入力端子IN1,IN2に入力される差動モード入力電圧に応じた出力を、出力端子OUTから得ることができる。

【0122】

ここで、出力段X2の第1の出力電流源70であるpトランジスタMC41と、接続回路X3のpトランジスタMC42とをカレントミラー回路構成としている。従って、第1の出力段カスコードトランジスタ群90をドライブするpトランジスタMC41のゲート−ソース間電圧は、入力段の第1の差動対トランジスタ10に流れる入力信号の電流に応じて比例する電流を流すpトランジスタMC42のゲート−ソース間電圧により決まる。また、第2の出力電流源80であるnトランジスタMC51のゲート−ソース間電圧は、入力段の第1の差動対トランジスタ10に流れる入力信号の電流に応じて比例する電流を流すnトランジスタMC31のゲート−ソース間電圧により決まる。よって、第1の出力電流源70のpトランジスタMC41,第2の出力電流源80のnトランジスタMC51の信号電流を制御するゲート−ソース間電圧の絶対値をVDDより十分小さい電圧に抑制することができる。

本実施の形態では、pトランジスタMC41およびnトランジスタMC51のゲート−ソース間電圧の絶対値がVDDより小さい値、例えば、1/2VDD程度かそれ以下となるように設定されている。従って、pトランジスタMC41およびnトランジスタMC51のホットキャリアの問題を軽減することができる。

【0123】

(増幅回路の第1変形例)

図19に示す増幅回路では、第2の入力段カスコードトランジスタ群40に流れる電流をカレントミラー回路により接続回路X3を介して出力側X2へと伝達しているが、折り返しカスコード回路により入力段X1の信号を出力段X2へ伝達することも可能である。

その一例を図20に示す。なお、図20においては、図19と同じ構成のものは同符号を付して説明を省略する。

【0124】

図20に示す回路例では、入力段X1の出力用MOSトランジスタとして設けられ、第2の入力段カスコードトランジスタ群40とグランドとの間に接続され、固定バイアスされた一対のnトランジスタMC21,MC31と、nトランジスタMC21,MC31のそれぞれのドレインに、ソースが接続されたnトランジスタMR01,MR02とが折り返しカスコード回路として設けられている。

そして、nトランジスタMR01のドレインとNVDDの電圧を有する電源に接続されたpトランジスタMC42との間には、VDDによりバイアスされたnトランジスタMO1と、・・・(N−2)×VDDの電圧によりバイアスされたnトランジスタMO(N-2)と、(N−1)×VDDの電圧によりバイアスされたnトランジスタMO(N-1)とが接続用カスコードトランジスタ群120として接続されている。

また、nトランジスタMR02のドレインには、VDDに接続されたカレントミラー回路を構成する一方のトランジスタであるpトランジスタMC81のドレインが接続されている。そして、カレントミラー回路を構成する他方のトランジスタであるpトランジスタMC82のドレインは、nトランジスタMC52のドレインに接続されている。

この回路例における接続回路X3は、出力段X2のpトランジスタMC41とカレントミラー回路を構成するpトランジスタMC42と、nトランジスタMO1〜MO(N-1)により構成される接続用カスコードトランジスタ群120と、nトランジスタMR01,MR02と、カレントミラー回路を構成するnトランジスタMC81,MC82と、出力段X2のnトランジスタMC51とカレントミラー回路を構成するnトランジスタMC52と、nトランジスタMC21およびnトランジスタMC31のゲートを接続しその接続点に適切なバイアス電圧を与える回路と、絶対値がNVDDの電圧を供給する電源線と、グランド線と、により構成されている。

【0125】

このような回路構成としても、第1の差動対トランジスタ10(pトランジスタMI11,MI12)に流れる信号電流を、出力段へ伝達することもできる。

【0126】

また、本実施の形態では、第1の出力段電流源70であるpトランジスタMC41がpトランジスタMC42とカレントミラー回路を構成し、第2の出力段電流源80であるnトランジスタMC51がnトランジスタMC52とカレントミラー回路を構成しており、両方の出力段電流源が第1の差動対トランジスタ10に流れる入力信号電流に応じて比例する電流を流すように構成しているが、一方または他方のいずれかの電流源を一定のバイアス電流を流すように構成してもよい。

【0127】

(増幅回路の第2変形例)

また、第1の出力段電流源70と第2の出力段電流源80とをカレントミラー回路構成とした接続回路X3は、図21に示すように構成することもできる。なお、図21においては、図20と同じ構成のものは同符号を付して説明を省略する。

【0128】

図21に示す入力段X1は、第2の入力段カスコードトランジスタ群40のpトランジスタMILA1〜MILA(N-1),MILB1〜MILB(N-1)に接続された一対の出力用トランジスタ対50であるnトランジスタMC21,MC31をカレントミラー回路構成としている。

接続回路X3は、第1の出力段電流源70であるpトランジスタMC41とカレントミラー回路を構成して一定のバイアス電流を流すpトランジスタMC42と、nトランジスタMC31のドレインおよび第2の出力段電流源80であるnトランジスタMC51のゲートを接続する接続線Lと、nトランジスタMC51のゲート電圧を制限するダイオード接続のnトランジスタMR03,MR04と、nトランジスタMC21のドレインとゲートを接続し、その接続点とnトランジスタMC31のゲートとを接続する回路と、絶対値がNVDDの電圧を供給する電源線と、グランド線と、から構成されている。

【0129】

この増幅回路の動作であるが、まず、第1の差動対トランジスタ10の出力に接続回路を通じてカレントミラー回路構成とした能動負荷(nトランジスタMC21,MC31)が接続されていることで、その出力には、第1の差動対トランジスタ10の信号電流の差に比例した電流が現れ、信号電流の差に応じて変化する出力電圧が生じる。この出力電圧を接続線LによりnトランジスタMC51のゲートに印加することで信号電流が発生する。この信号電流(ドレイン電流)はnトランジスタMC51のゲート電圧の2乗に比例する電流となる。

nトランジスタMC51のゲート−ソース間に印加させる出力電圧は、ダイオード接続され、接続線Lとグランドとの間で直列接続されたダイオード接続されたnトランジスタMR03,MR04により決定することができるため、その最大値はVDDより小さい値(例えば、0.5VDD以下)に制限することができる。従って、出力段トランジスタのホットキャリアの問題を軽減することができる。

【0130】

図21に示す増幅回路では、第1の出力段電流源70を一定バイアスを流す電流源、第2の出力段電流源80を第1の差動対トランジスタ10のpトランジスタMI11とpトランジスタMI12の信号電流の差に応じて変化する電流を流す電流源としたが、反対に第1の出力段電流源70を第1の差動対トランジスタ10に流れる信号電流の差に応じて変化する電流を流す電流源、第2の出力段電流源80を、一定バイアスを流す電流源としてもよい。

【0131】

また、これまでの説明では、一方の電源線の電圧を他方の電源線に対してNVDD(あるいはN1VDD、N2VDD)のように正の値とし、他方の電源線をグランド線としてきたが、一方の電源線の電圧を他方の電源線に対して−NVDD(あるいは−N1VDD、−N2VDD)のように負の値として、MOSトランジスタの伝導極性を全て反転させれば、すなわち、pトランジスタをnトランジスタに、nトランジスタをpトランジスタと反転させれば、本発明技術による回路を構成することが可能である。

【0132】

更に、pトランジスタとnトランジスタとは、MOSトランジスタに限らず、バイポーラトランジスタ(pnpトランジスタ、npnトランジスタ)とすることが可能である。その場合には、ゲートをベースに、ソースをエミッタに、ドレインをコレクタに置き換えて、回路接続関係を変更せずに接続することで実現できる。また、入力段のバイアス電流手段(第1,2の入力電流バイアス手段)はカレントミラー回路でなく、他の抵抗手段に置き換えることもできる。更に、出力段の第1,第2の出力段電流源は入力段差動対トランジスタに流れる信号電流に対して増幅比が1以上のカレントミラー回路としたり、入力段の差動対トランジスタに流れる電流に概ね比例する電流を発生するトランジスタ回路に置き換えたりすることも可能である。更に、入力段バイアス調整回路における各抵抗手段である第1の入力段カスコードバイアス用抵抗手段61、第2の入力段カスコードバイアス用抵抗手段62、第1の抵抗手段63、第2の抵抗手段64と、出力段バイアス調整回路における各抵抗手段である第1の出力段カスコードバイアス用抵抗手段111、第2の出力段カスコードバイアス用抵抗手段112と、および出力抵抗手段113とは、実質的に抵抗として動作するトランジスタなどの抵抗手段、コモンモード入力電圧あるいは出力電圧により制御されたトランジスタ回路による可変抵抗手段、スイッチ手段、レベルシフトを備えた可変抵抗手段、レベルシフトを備えたスイッチ手段に置き換えたりすることも可能である。

【実施例】

【0133】

本発明の実施の形態に係る増幅回路について、入力段X1として図9に示す回路と、出力段X2として図18に示す回路と、接続回路X3として図19に示す回路を採用して増幅回路を構成した。そして、この増幅回路の動作を確認するためにシミュレーションを行った。この増幅回路を図22に示す。

なお、図22の増幅回路では、N1=2(コモンモード入力電圧の範囲が2VDD)、N2=3(出力振幅が3VDD)であるが、出力段で使用している3VDDの電源を入力段にも効果的に使用することができ、入力段の一方の電源線にもN1VDD以上の電圧である3VDDが使用されている。この効果は既に図9に示す入力段の第2変形例で説明した通りである。

【0134】

本実施例では、図22に示す増幅回路を、電圧利得が1.5となるように出力から入力に負帰還を施した非反転型負帰還増幅回路として動作させた。

【0135】

シミュレーションの各条件を示す。

(1)プロセス:標準CMOSプロセス 0.18μm

MOSトランジスタのゲート長1μm(pトランジスタMD1の4μmを除く)

(2)各部の条件は図23参照(なお、L:ゲート長、W:ゲート幅、M:並列数)。

(3)VDD=1.8V,2VDD=3.6V,3VDD=5.4V

(4)抵抗負荷=無限大、容量負荷=5pF

(5)回路シミュレーター:HSPICE(登録商標)

なお、pトランジスタMC12とnトランジスタMC62との電流バイアスは直流5μAである。

【0136】

シミュレーションの結果を図24に示す。図24では、非反転型負帰還増幅回路の入力電圧と出力端子OUTおよび各接続点における電圧との間の直流伝達特性曲線が示されている。

ここで、非反転型負帰還増幅回路ではその入力電圧は増幅回路のコモンモード入力電圧となることに注意する。これよりコモンモード入力電圧の範囲が2VDD、出力振幅が3VDD、更に、出力端子OUTおよび各接続点における電圧から、コモンモード入力電圧が0から2VDDの間で変動しても(利得が1.5倍であるため、入力電圧が2VDDのとき出力電圧は3VDDとなる)、常にすべてのトランジスタの|VGS|、|VGD|はVDD以内であることが確認できる。

【産業上の利用可能性】

【0137】

本発明は、増幅回路が使用できるものであれば適用が可能である。特に、本発明は、集積化した増幅回路LSIに好適である。

【符号の説明】

【0138】

10 第1の差動対トランジスタ

11 第2の差動対トランジスタ

20 第1の入力段電流バイアス手段

21 第2の入力段電流バイアス手段

30 第1の入力段カスコードトランジスタ群

31 第3の入力段カスコードトランジスタ群

40 第2の入力段カスコードトランジスタ群

41 第4の入力段カスコードトランジスタ群

50 出力用トランジスタ対

51 第1のカレントミラー回路

52 第2のカレントミラー回路

60,60a,60b,60c 入力段バイアス調整回路

61 第1の入力段カスコードバイアス用抵抗手段

62 第2の入力段カスコードバイアス用抵抗手段

63 第1の抵抗手段

64 第2の抵抗手段

70 第1の出力段電流源

80 第2の出力段電流源

90 第1の出力段カスコードトランジスタ群

100 第2の出力段カスコードトランジスタ群

110,110a,110b,110c 出力段バイアス調整回路

111 第1の出力段カスコードバイアス用抵抗手段

112 第2の出力段カスコードバイアス用抵抗手段

113 出力抵抗手段

114 第1の出力段カスコードバイアス用トランジスタ群

115 第2の出力段カスコードバイアス用トランジスタ群

120 接続用カスコードトランジスタ群

C1〜C17 接続点

IN1,IN2 入力端子

MB1,MB3,MB4,MB5 pトランジスタ(極性を反転した回路では、nトランジスタ、以下同様)

MB2,MB6 nトランジスタ(極性を反転した回路では、pトランジスタ、以下同様)

MI11,MI12 pトランジスタ

MI21,MI22 pトランジスタ

MIUA1〜MIUA(N1-1) pトランジスタ

MIUB1〜MIUB(N1-1) pトランジスタ

MILA1〜MILA(N1-1) pトランジスタ

MILB1〜MILB(N1-1) pトランジスタ

MILC1〜MILC(N1-1) pトランジスタ

MD1,MD2,MD3 pトランジスタ

MC11,MC12,MC13 pトランジスタ

MC21,MC22 nトランジスタ

MC31 nトランジスタ

MC41,MC42 pトランジスタ

MC51,MC52 nトランジスタ

MC61,MC62,MC63 nトランジスタ

MC71,MC72 pトランジスタ

MC81,MC82 nトランジスタ

ML pトランジスタ

MU nトランジスタ

MOU1〜MOU(N2-1) pトランジスタ

MOL1〜MOL(N2-1) nトランジスタ

MO1〜MO(N2-1) nトランジスタ

MR01,MR02 nトランジスタ

MUX1 pトランジスタ

MUY1 pトランジスタ

OUT 出力端子

RIU1〜RIU(N1-2) 抵抗手段

RIL1〜RILN1 抵抗手段

ROU1〜ROU(N2-2) 抵抗手段

ROL1〜ROL(N2-2) 抵抗手段

ROUA1,ROUA2 抵抗手段

ROUB1,ROUB2 抵抗手段

RX 抵抗

R0 抵抗

ROUT 抵抗

CU,CL コンデンサ

X1 入力段

X2 出力段

X3 接続回路

L 接続線

【技術分野】

【0001】

本発明は、集積化可能な差動入力型の増幅回路に関するものである。

【背景技術】

【0002】

集積回路の微細化技術の発展により、デバイスの耐圧は低下の一方である。集積回路に用いられる電源電圧の値はデバイス耐圧によって制限される。一般に微細化集積回路では電源電圧はデバイス耐圧以下の値に設定されるが、近年では、電源電圧の低下が著しい。特に、CMOS LSIでは、電源電圧であるVDDが、例えば1.8Vから更に低下する傾向にある。従来のアナログ・デジタル混載のLSIでは、スケーリング則に沿ってゲート酸化膜の厚みを薄くした通常の低耐圧MOSトランジスタ以外に、追加プロセスにより同一チップ上にゲート酸化膜の厚みを厚くした中耐圧や高耐圧のアナログ専用MOSトランジスタを形成するようにして、高耐圧化を図ってきたが、プロセスが複雑化するため製造コストが増大する。従って、追加プロセス無しに高耐圧が実現できるのが望ましい。

【0003】

ここで、追加プロセスを必要としない従来の増幅回路の一例を図面に基づいて説明する。まず入力段であるが、非特許文献1に記載されたものが知られている。この非特許文献1に記載された増幅回路を図25に基づいて説明する。

図25に示す増幅回路の入力段は、バイポーラトランジスタのLSIに使用される回路であるが、以下の説明は、npnトランジスタをnMOSトランジスタに、pnpトランジスタをpMOSトランジスタに読みかえれば、MOSトランジスタについても成り立つ。この回路では2電源V+とV-を使用しており、電源電圧は合わせて2Vとなっている。この電源電圧2Vは通常のデバイスの耐圧から決まる定格電源電圧(以内)に設定されている。npnトランジスタQ1とnpnトランジスタQ2とは入力端子がベースに接続された差動対トランジスタである。このnpnトランジスタQ1,Q2は、電流増幅率βの値が大きいスーパβデバイス(super beta transistor)と称される特殊トランジスタである。このnpnトランジスタQ1,Q2は通常のnpnトランジスタQ3,Q4と比較して耐圧が低いため、npnトランジスタQ1,Q2のそれぞれには、直列接続されたダイオードD1,D2と電流源I1,I2によりバイアスされたnpnトランジスタQ3,Q4がカスコード接続されている。

【0004】

次に、従来の出力段であるが、非特許文献2に記載されたものが知られている。この非特許文献2に記載された増幅回路を図26に基づいて説明する。なお、本明細書の以下の記述では、表記の簡略化のために、特にことわらない限り、pMOSトランジスタをpトランジスタと表記し、nMOSトランジスタをnトランジスタと表記することとする。

図26に示す増幅回路の出力段は、高耐圧化を実現するために、デジタル回路のI/Oバッファ用として知られているダブルカスコード型バッファをプッシュプル構成としたpトランジスタおよびnトランジスタM13〜M22に、AB級動作用のレベルシフタとしてpトランジスタおよびnトランジスタM9〜M12と抵抗R1,R2とを組み合わせたものである。

【0005】

図26に示す非特許文献2に記載の増幅回路の出力段では、電源電圧がMOSトランジスタの定格電源電圧VDD(本発明の請求項1で定義したVDDに相当)の2倍の2×VDDに設定されている。この電源電圧はVSSを基準としたものである。プッシュプル構成とした出力回路においては、出力端子と2×VDDの電圧を与える電源との間と、出力端子とVSSとの間に、それぞれ3つのトランジスタが設けられ、増幅用のトランジスタM13,M22を除くと2個ずつ設けられている。集積回路ではトランジスタの数が増えると駆動能力が低下し、それを補うためにトランジスタサイズを大きくして面積を占有してしまうため小型化を阻害する要因となる。

この点については、出力端子とMOSトランジスタの定格電源電圧Vdd(本発明の請求項1で定義したVDDに相当)の3倍電圧(3×Vdd)との間と、出力端子とグランドとの間に、それぞれ2つのトランジスタが積み上げたスタック数が2個の出力段が、非特許文献3に記載されている(図27参照)。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】PAUL R.GRAY,PAUL J.HURST,STEPHEN H.LEWIS,ROBERT G. MEYER,「ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUIT」,(米国),第4版,John Wiley & Sons Inc,2001年,p.479−480

【非特許文献2】石田光一,アティットタムタカーン,桜井貴康,「1.8VCOMSプロセスによる高耐圧オペアンプ」,電子情報通信学会総合大会講演論文集2005年,社団法人電子情報通信学会,2005年3月7日,p.13

【非特許文献3】Prem Swaroop, Anand J. Vasani,Maysam Ghovanloo、「A High-Voltage Output Driver for Implantable Biomedical Stimulators and I/O Applications」、「Circuits and Systems, 2006.MWSCAS'06. 49th IEEE International Midwest Symposium on」、(米国)、IEEE、2006年8月6日、p.566−569

【非特許文献4】Anne-Johan Annema, Govert J. G. M. Geelen, and Peter C. de Jong,「5.5-V I/O in a 2.5-V 0.25μm CMOS Technology」,「IEEE Journal of Solid-State Circuits VOL.36, NO.3, MARCH 2001」、(米国)、IEEE,2001年3月、p.528−538

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、図25に示す非特許文献1に記載の増幅回路の入力段では、追加プロセスを必要としないものの、任意の電圧に耐えられるようにしたものではないため、定格電源電圧の任意の倍数電圧でも耐えることが可能なものが望まれている。

アナログ増幅器として幅広く用いられる増幅回路は、一対の入力端子、つまりプラス入力端子とマイナス入力端子との一対の入力端子を有する差動対入力段、一つの出力端子を有する出力段とから構成される増幅回路で、一対の入力端子に印加された信号成分のうちの差分、つまり差動モード入力電圧を増幅して出力端子に出力する。その際に、増幅回路の性能は一対の入力端子に印加された共通成分、つまりコモンモード入力電圧の影響を受ける。差動モード入力に対する性能を維持できるコモンモード入力電圧の範囲をコモンモード入力電圧範囲という。一般にコモンモード入力電圧が電源電圧に近くなったり、グランド電圧に近くなったりすると、性能が極度に悪化する。コモンモード入力電圧範囲は、グランドから電源電圧の任意の倍数の電圧まで広い範囲であることが望ましい。

【0008】

また、図27に示す非特許文献3に記載の出力段では、デジタル回路であるため、デジタル信号が入力されるpトランジスタP1とnトランジスタN1のゲートソース間電圧の絶対値は、0VからVdd(=VDD)まで振幅する。従って、デジタル入力信号が0VからVdd(=VDD)まで急峻に変化する過渡状態では、出力段トランジスタがONしてもドレイン−ソース間電圧が直ちに0Vとはならず、ドレイン−ソース間電圧がVDD以上の電圧となることがあり、ホットキャリアの問題が生じる。

【0009】

例えば、非特許文献4では、ホットキャリアの問題についての記載があり、以下に説明する。

MOSトランジスタのプロセスは、ある寿命を境界条件としてデジタル回路で用いられるトランジスタの性能を最大化するように最適化される。目標となる寿命は最悪動作条件下で典型的に5〜10年の連続動作である。寿命はトランジスタの動作条件に依存する。一つはゲート−ソース間電圧Vgs(本明細書の表記では、VGS)、ゲート−ドレイン間電圧Vgd(本明細書の表記では、VGD)(縦方向の電界)にかかわるゲート酸化膜耐圧(BVgs/BVGS,BVgd/BVGD)であり、他の一つは、ドレイン−ソース間電圧Vds(本明細書の表記では、VDS)(横方向の電界)にかかわるホットキャリア劣化である。Vgsが大きく、かつ、Vdsが大きい条件下では(例えば、Vgs=Vds=Vdd)(Vddは本発明の表記では、VDDに相当)、トランジスタの寿命時間は極端に短くなる(図28参照)。

【0010】

つまり、ゲート−ソース間電圧VGSが大きな電圧(VDD)で駆動されて、トランジスタがONになっていて、なおかつ、VDSに大きな電圧(VDD)が印加されている条件下で、寿命は最短となる。このような条件は、デジタル論理回路のトランジスタが急峻にOFFからONに切り替わった状態(VGSが0からVDDに切り替わった状態)で過渡的に生じる。寿命を長くするには、MOSトランジスタがこのような条件下で動作するのを可能な限り避けることが望ましい。

【0011】

従って、非特許文献3に記載の出力段においては、過渡的な状態でも出力トランジスタ(pトランジスタP2,P3,nトランジスタN2,N3)とそれをドライブするトランジスタ(pトランジスタP1,nトランジスタN1)のゲート−ソース間電圧とドレイン−ソース間電圧が同時にVDDに近い電圧またはVDD以上の高い電圧が印加されないようにするには、更にスタック数を増やす必要がある。

【0012】

また、増幅回路では一般に出力端子から入力端子にある種の帰還をかけて用いられる。よく用いられる応用例として、非反転型負帰還増幅回路、反転型負帰還増幅回路が知られている。反転型負帰還増幅回路では、入力信号はマイナス入力端子に印加され、入力信号に対してコモンモード入力電圧は変化せず、プラス入力端子の電圧に保持される。一方、非反転型負帰還増幅回路では、入力信号はプラス入力端子に印加され、コモンモード入力電圧は入力信号に応じて変化する。

【0013】

非特許文献2には、マイナス入力端子In−とプラス入力端子In+を一対の入力端子とする入力段の電源も定格電源電圧の2倍の2×VDD(VDDは本発明の請求項1で定義したVDDに相当)に設定されて、それに対応した入力段回路が示されている。しかし、非特許文献2に記載の回路においては、コモンモード入力電圧がVSS(本発明における他方の電源線の電圧に相当)近くになったり、2倍のVDD近くになったりすると、耐圧の問題が生じる。非特許文献2に記載の回路を反転型負帰還増幅回路として用いる場合、プラス入力端子の電圧を適当に設定すれば、つまり反転型負帰還増幅回路でコモンモード入力電圧を適当に設定すれば(例えば、2×VDDとVSSの中点電圧など)入力段の回路に耐圧の問題は生じないが、それ以外の応用に対しては、耐圧の問題が解決できない。

【0014】

このように、上記理由で非特許文献1に記載の入力段回路,非特許文献2に記載の出力段回路、入力段回路を採用することができない。また、出力段では、デジタル信号を出力する非特許文献3の回路においては、非特許文献2の回路より少ないトランジスタ数で実現されているものの、上記問題があるため、非特許文献3の回路を採用することができない。

従って、アナログ信号をドライブする高耐圧の出力段を、少ないトランジスタ数で実現することができる回路が望まれている。

【0015】

このように様々な課題を有する増幅回路ではあるが、本発明では、入力段の課題を解決するものとする。

【0016】

そこで本発明は、追加プロセスなしに実現できる汎用性の高い高耐圧アナログ信号増幅回路、特にコモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる増幅回路を提供することを目的とする。

【課題を解決するための手段】

【0017】

本発明に係る増幅回路の入力段は、MOSトランジスタにより形成された入力段、出力段および前記入力段と前記出力段とを接続する接続回路を備えた増幅回路であって、前記入力段は、2つのMOSトランジスタより成り、2つのゲート端子を一対の入力端子とした第1の差動対トランジスタと、電位差の絶対値が前記MOSトランジスタの定格電源電圧(以下、この電圧をVDDと称す。)のN1倍(但し、N1は2以上の整数である。以下、この電圧をN1VDDと称す。)以上の電源電圧を供給する一方の電源線と他方の電源線とのうち、前記一方の電源線に接続された第1の入力段電流バイアス手段と、前記第1の差動対トランジスタの接続点に一端が接続され、前記第1の入力段電流バイアス手段から他端にバイアス電流が供給される前記第1の差動対トランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタがカスコード接続された第1の入力段カスコードトランジスタ群と、前記第1の差動対トランジスタのそれぞれのMOSトランジスタに前記第1の差動対トランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタがカスコード接続された一対の第2の入力段カスコードトランジスタ群と、前記一対の第2の入力段カスコードトランジスタ群のそれぞれに接続された前記第1の差動対トランジスタと異なる伝導極性を有する一対の出力用MOSトランジスタと、前記一対の入力端子に前記他方の電源線を基準として電圧の絶対値が0VからN1VDDまでの間で変化するコモンモード入力電圧が入力されたときに、前記第1の差動対トランジスタの接続点の電圧に基づいて、前記第1の差動対トランジスタ、前記第1の入力段カスコードトランジスタ群、前記第2の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値がVDD以内となるように調整する入力段バイアス調整回路とを備えたことを特徴とする。

【0018】

この増幅回路の入力段によれば、一対の入力端子に前記他方の電源線を基準として0VからN1VDDまでの間で変化するコモンモード入力電圧が入力されたときに、入力段バイアス調整回路が第1の差動対トランジスタ、第1の入力段カスコードトランジスタ群、第2の入力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内、すなわちデバイス耐圧以下、となるようにバイアス電圧を調整するので、第1の差動対トランジスタに流れる信号電流を一対の第2の入力段カスコードトランジスタ群を介して後段への出力信号として出力することができる。

【0019】

ここで、伝導極性とは、MOSトランジスタのチャンネルを流れる電流を運ぶ担体(キャリア)の極性の意味で用いており、キャリアが電子であればnMOSトランジスタ、正孔であればpMOSトランジスタを指す。つまり、伝導極性が同じとは、一方がpMOSトランジスタであれば他方もpMOSトランジスタ、一方がnMOSトランジスタであれば他方もnMOSトランジスタということを意味し、タイプが同じであることを意味する。また、伝導極性が異なるとは、一方がpMOSトランジスタであれば他方はnMOSトランジスタ、一方がnMOSトランジスタであれば他方はpMOSトランジスタということを意味し、タイプが違うことを意味する。

【0020】

前記入力段バイアス調整回路は、前記一対の入力端子に入力されたコモンモード入力電圧の絶対値が前記他方の電源線を基準としてN1VDDであれば、前記第1の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート電圧の絶対値を(N1−1)×VDDとすると共に、前記一対の第2の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート電圧の絶対値を前記第1の差動対トランジスタ側から順に(N1−M1)×VDD(但し、M1は前記第2の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタに付与した番号であり、前記第1の差動対トランジスタ側から前記一対の出力用MOSトランジスタ側までのMOSトランジスタに対応する1からN1−1までの整数である。)とし、前記一対の入力端子に入力されたコモンモード入力電圧が前記他方の電源線を基準として0Vであれば、前記第1の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタのゲート電圧の絶対値をN1VDD側から順に(N1−M2)×VDD(但し、M2は前記第1の入力段カスコードトランジスタ群のそれぞれのMOSトランジスタに付与した番号であり、第1のバイアス電流手段側から第1の差動対トランジスタ側までのMOSトランジスタに対応する1からN1−1までの整数である。)とすると共に、前記第2の入力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を0Vとするのが望ましい。

【0021】

入力端子に入力されたコモンモード入力電圧の絶対値が他方の電源線を基準としてN1VDDである場合に、または0Vのときに、入力段バイアス調整回路を、上記バイアス電圧とするような調整回路とすることで、第1の差動対トランジスタ、第1の入力段カスコードトランジスタ群、第2の入力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内とすることができる。

【0022】

前記入力段バイアス調整回路は、前記第1の差動対トランジスタのゲート−ソース間電圧に相当する電圧分またはそれ以上の電圧をレベルシフトするレベルシフト手段と、前記他方の電源線を基準とした前記一方の電源線の電圧の正負に応じて、それぞれ(N1−1)×VDDあるいは−(N1−1)×VDDの電圧を供給する電源に一端が接続されたN1−2個の直列接続された抵抗手段より成る第1の入力段カスコードバイアス用抵抗手段であって、前記第1の入力段カスコードバイアス用抵抗手段の両端と前記第1の入力段カスコードバイアス用抵抗手段の隣り合う各抵抗手段の接続点とが、それぞれ前記第1の入力段カスコードトランジスタ群の隣り合う各MOSトランジスタのゲートに接続された前記第1の入力段カスコードバイアス用抵抗手段と、前記レベルシフト手段と共に、前記他方の電源線に接続されたN1個の抵抗手段であって、前記他方の電源線側から少なくとも(N1−1)個の抵抗が直列接続された抵抗手段より成り、前記一対の第2の入力カスコードトランジスタ群の各MOSトランジスタのゲート端子に、前記N1個の隣り合う抵抗手段の接続点がそれぞれ接続された第2の入力段カスコードバイアス用抵抗手段と、前記第1の入力段カスコードバイアス用抵抗手段の他端に接続されていると共に、前記他方の電源線を基準とした前記一方の電源線の電圧の正負に応じて、VDDあるいは−VDDの電圧を供給する電源に接続された第1の抵抗手段と、前記第1の入力段カスコードバイアス用抵抗手段と、前記第1の抵抗手段との接続点に一端が接続され、前記第1の差動対トランジスタの接続点に他端が接続された第2の抵抗手段とを備えるのが望ましい。

【0023】

入力段バイアス調整回路を、前記ダイオード接続のMOSトランジスタと、前記第1の入力段カスコードバイアス用抵抗手段と、前記第2の入力段カスコードバイアス用抵抗手段と、前記第1の抵抗手段と、前記第2の抵抗手段とにより構成することで、入力端子に入力されたコモンモードの電圧範囲が他方の電源線を基準として0VからN1VDD(または−N1VDD)まで変化しても、前記第1入力段カスコードトランジスタ群と前記第2の入力段カスコードトランジスタ群のゲートへのバイアス電圧を前記のように調整した電圧に制御することができる。

【0024】

当該入力段バイアス調整回路に対し、前記他方の電源線を基準とした電位差の絶対値がN1VDDである前記一方の電源線に接続された第2の入力段電流バイアス手段と、前記一対の入力端子が接続され、前記第1の差動対トランジスタのMOSトランジスタと同じ伝導極性を有する一対のMOSトランジスタより成り、当該一対のMOSトランジスタのそれぞれのドレイン端子およびソース端子を接続した第2の差動対トランジスタと、前記第2の差動対トランジスタの一方の接続点に一端が接続され、前記第2の入力段電流バイアス手段から他端にバイアス電流が供給される前記第1の差動対トランジスタのMOSトランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタより成り、さらに当該N1−1個の各MOSトランジスタの各ゲート端子が、前記第1の入力段カスコードトランジスタ群のN1−1個の各MOSトランジスタの対応するゲート端子と接続された第3の入力段カスコードトランジスタ群と、前記第2の差動対トランジスタの他方の接続点と前記他方の電源線に接続され、前記第1の差動対トランジスタのMOSトランジスタと同じ伝導極性を有するN1−1個のMOSトランジスタより成り、さらに当該N1−1個の各MOSトランジスタの各ゲート端子が、前記第2の一対入力段カスコードトランジスタ群のそれぞれN1−1個の各MOSトランジスタの対応するゲート端子と接続された第4の入力段カスコードトランジスタ群と、を追加し、バイアス電圧の調整を前記第2の差動対トランジスタの接続点の電圧に基づいて行うのが望ましい。そうすることで、出力段へ伝達される信号電流が流れる第1の差動対トランジスタへの影響を排除することができる。

【0025】

本発明に係る増幅回路の出力段は、MOSトランジスタにより形成された前記入力段、前記出力段および前記入力段と前記出力段とを接続する接続回路を備えた増幅回路であって、前記出力段は、電位差の絶対値がMOSトランジスタの定格電源電圧VDDのN2倍(但し、N2は2以上の整数である。以下、この電圧をN2VDDと称す。)の電圧を供給する一方の出力段電源線と他方の出力段電源線とのうち、前記一方の出力段電源線に接続された、1個のMOSトランジスタより成り、前記接続回路により駆動される第1の出力電流源と、出力端子に一端が接続され、他端が前記第1の出力電流源に接続され、カスコード接続された、前記第1の出力電流源のMOSトランジスタと同じ伝導極性を有するN2−1個(但し、N2は2以上の整数である。)のMOSトランジスタより成る第1の出力段カスコードトランジスタ群と、前記出力端子に一端が接続され、カスコード接続された、前記第1の出力段カスコードトランジスタ群のMOSトランジスタとは異なる伝導極性を有するN2−1個のMOSトランジスタより成る第2の出力段カスコードトランジスタ群と、前記第2の出力段カスコードトランジスタ群の他端と前記他方の出力段電源線とに接続された、第2の出力段カスコードトランジスタ群のMOSトランジスタと同じ伝導極性を有するMOSトランジスタより成り、前記接続回路により駆動される第2の出力電流源と、により構成され、前記他方の出力段電源線を基準とした前記出力端子の電圧の絶対値が0VからN2VDDまでの間で変化したときに、前記第1の出力段カスコードトランジスタ群と前記第2の出力段カスコードトランジスタ群を構成するMOSトランジスタのそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値がVDD以内となるバイアス電圧に調整する出力段バイアス調整回路とを備え、前記接続回路は、前記入力段からの信号に応じて、前記第1の出力電流源および前記第2の出力電流源を構成する各MOSトランジスタのゲート−ソース間電圧の絶対値がVDDより小さくなるように駆動することを特徴とする。

【0026】

この増幅回路の出力段によれば、他方の出力段電源線を基準として、出力端子から出力される出力電圧の絶対値が0VからN2VDDまでの間で変化しても、出力段バイアス調整回路が第1の出力段カスコードトランジスタ群、第2の出力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値がVDD以内となるようにバイアス電圧を調整し、また接続回路が第1の出力電流源および第2の出力電流源を構成する各MOSトランジスタのゲート−ソース間電圧の絶対値がVDDより小さくなるように調整するので、出力電圧に対する耐圧を任意倍数の電圧とすることができる。また、第1の出力電流源と第2の出力電流源とは、第1の差動対トランジスタに流れる入力信号の電流に応じて変化する電流を流す電流制御によるものであり、非特許文献3の出力段の回路のように、ゲート−ソース間電圧が0からVDDのまでの電圧制御によるものでないため、ドライブする電流の制御にVDDより十分低いゲート−ソース間電圧で行うことができる。ここで、VDDより低いゲート−ソース間電圧とは、例えば0.5VDD程度またはそれ以下の電圧のことである。従って、ホットキャリアの問題を軽減することができる。

【0027】

前記出力段バイアス調整回路は、前記他方の出力段電源線を基準とした前記出力端子の電圧の絶対値がN2VDDであれば、前記第1の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値を(N2−1)×VDDとすると共に、前記第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値を出力端子側から順に(N2−M3)×VDD(但し、M3は出力端子側から第2の出力段電流源側までのMOSトランジスタに対応する1からN2−1までの整数)とし、前記他方の出力段電源線を基準とした前記出力端子の電圧が0Vであれば、前記第1の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値を(N2−M4)×VDD(但し、M4は第1の出力電流源側から出力端子側までの各MOSトランジスタに対応する1からN2−1までの整数)とすると共に、前記第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧の絶対値をVDDとするのが望ましい。

【0028】

このようにして、他方の出力段電源線を基準として、出力端子から出力される出力電圧の絶対値が0VからN2VDDまでの間で変化しても、出力段バイアス調整回路を、上記バイアス電圧とするような調整回路とすることで、第1の出力段カスコードトランジスタ群、第2の出力段カスコードトランジスタ群のそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内とすることができる。

【0029】

前記出力段バイアス調整回路は、前記他方の出力段電源線を基準とした前記一方の出力段電源線の電圧の正負に応じて、それぞれ(N2−1)×VDDあるいは−(N2−1)×VDDの電圧を供給する電源に一端が接続されたN2−1個の直列接続された抵抗手段より成る第1の出力段カスコードバイアス用抵抗手段であって、前記第1の出力段カスコードバイアス用抵抗手段の隣り合う各抵抗手段の接続点が前記第1の出力段カスコードトランジスタ群の各MOSトランジスタのゲート端子に接続された前記第1の出力段カスコードバイアス用抵抗手段と、前記他方の電源線を基準とした前記一方の出力段電源線の電圧の正負に応じて、それぞれVDDあるいは−VDDの電圧を供給する電源に接続されたN2−1個の直列接続された抵抗手段より成る第2の出力段カスコードバイアス用抵抗手段であって、前記第2の出力段カスコードバイアス用抵抗手段の隣り合う各抵抗手段の接続点が前記第2の出力段カスコードトランジスタ群の隣り合う各MOSトランジスタのゲート端子に接続された前記第2の出力段カスコードバイアス用抵抗手段と、前記第1の出力段カスコードバイアス用抵抗手段の他端および前記第2の出力段カスコードバイアス用抵抗手段の他端の接続点と前記出力端子との間に接続された出力抵抗手段とを備えているのが望ましい。

【0030】

出力段バイアス調整回路を、第1の出力段カスコードバイアス用抵抗手段と、第2の出力段カスコードバイアス用抵抗手段と、出力抵抗手段とにより構成することで、他方の出力段電源線を基準として、出力端子から出力される出力電圧の絶対値が0VからN2VDDまでの間で変化しても、第1の出力段カスコードトランジスタ群と第2の出力段カスコードトランジスタ群へのバイアス電圧を調整した電圧に制御することができる。

【0031】

前記第1の出力電流源には、前記第1の差動対トランジスタの一方のMOSトランジスタの信号電流に略比例して変化する電流を流す機能を持たせ、前記第2の出力電流源には、前記第1の差動対トランジスタの他方のトランジスタの信号電流に略比例して変化する電流を流す機能を持たせるように、前記接続回路を構成することができる。

【0032】

また、前記第1の出力電流源または前記第2の出力電流源の少なくとも一方の電流源には、前記第1の差動対トランジスタの一方のトランジスタと他方のトランジスタの信号電流の差に応じてあるいは当該信号電流の差に略比例して変化する電流を流す機能を持たせるように、前記接続回路を構成することができる。

【0033】

上記入力段と上記出力段とを備えた増幅回路は、MOSトランジスタのドレイン、ゲートおよびソースをそれぞれバイポーラトランジスタのコレクタ、ベースおよびエミッタに置換して、回路接続関係を変更することなくMOSトランジスタをバイポーラトランジスタに置換することができる。

【0034】

なお、伝導極性について、バイポーラトランジスタの場合では、ベース領域をコレクタに向けて流れる電流を運ぶキャリアの極性を意味しており、それが電子であればnpnトランジスタ、正孔であればpnpトランジスタを意味する。つまり、伝導極性が同じとは、一方がnpnトランジスタであれば他方もnpnトランジスタ、一方がpnpトランジスタであれば他方もpnpトランジスタであり、タイプが同じであることを意味する。また、伝導極性が異なるとは、一方がnpnトランジスタであれば他方はpnpトランジスタ、一方がpnpトランジスタであれば他方はnpnトランジスタということを意味し、タイプが違うことを意味する。

【発明の効果】

【0035】

本発明は、コモンモード入力電圧が他方の入力段電源線を基準としてその絶対値が0VからN1VDDまで変化しても、入力段バイアス調整回路が第1の差動対トランジスタ、第1の入力段カスコードトランジスタ、第2の入力段カスコードトランジスタのそれぞれのゲート−ソース間電圧およびゲート−ドレイン間電圧の絶対値をVDD以内とすることにより、任意倍数の入力電圧でも耐えることができる高耐圧の入力段とすることが可能である。

【図面の簡単な説明】

【0036】

【図1】本発明の実施の形態に係る増幅回路の入力段を示す図である。

【図2】図1に示す増幅回路の入力段の入力段バイアス調整回路の基本的な構成を説明するための図である。

【図3】図2に示す入力段の第1の入力段カスコードトランジスタ群・第1の差動対トランジスタ・第2の入力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は他方の入力段電源線を基準として一対の入力端子へのコモンモード入力電圧が0Vの場合を示す図、(B)は同じくN1VDDの場合を示す図である。

【図4】図2に示す入力段のpトランジスタとnトランジスタとを置換し、一方の電源線の極性を、他方の電源線を基準として負に反転させた図である。

【図5】図4に示す入力段の第1の入力段カスコードトランジスタ群・第1の差動対トランジスタ・第2の入力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は他方の出力段電源線を基準として入力端子に入力されるコモンモード入力電圧が0Vの場合を示す図、(B)は同じくコモンモード入力電圧が−N1VDDの場合を示す図である。

【図6】図2に示す入力段の第1変形例を説明するための図である。

【図7】図6の入力段において、他方の入力段電源線を基準として一対の入力端子へのコモンモード入力電圧が0Vから2VDDの場合(N1=2)を示す図である。

【図8】図6の入力段において、他方の入力段電源線を基準として一対の入力端子へのコモンモード入力電圧が0Vから3VDDの場合(N1=3)を示す図である。

【図9】図6に示す入力段の第2変形例を説明するための図である。

【図10】図6に示す入力段の第3変形例を説明するための図である。

【図11】本発明の実施の形態に係る増幅回路の出力段を示す図である。

【図12】図11に示す増幅回路の出力段の出力段バイアス調整回路の基本的な構成を説明するための図である。

【図13】図12に示す出力段の第1の出力段カスコードトランジスタ群・第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は他方の出力段電源線を基準として出力電圧が0Vの場合を示す図、(B)は同じく、出力電圧がN2VDDの場合を示す図である。

【図14】図12に示す出力段のpトランジスタとnトランジスタとを置換し、一方の電源線の極性を、他方の電源線を基準として負に反転させた図である。

【図15】図14に示す出力段の第1の出力段カスコードトランジスタ群・第2の出力段カスコードトランジスタ群の各MOSトランジスタのゲート電圧を示す図であり、(A)は、他方の出力段電源線を基準として出力電圧が0Vの場合を示す図、(B)は同じく出力電圧が−N2VDDの場合を示す図である。

【図16】図12に示す出力段のN2=4の場合の第1変形例を説明するための図である。

【図17】図12に示す出力段のN2=3の場合の第2変形例を説明するための図である。

【図18】図12に示す出力段のN2=3の場合の第3変形例を説明するための図である。

【図19】本発明の実施の形態に係る増幅回路を示す図である。

【図20】接続回路として折り返しカスコード回路を用いた増幅回路を示す図である。

【図21】他の接続回路を用いた増幅回路を示す図である。

【図22】図9に示す入力段と、図18に示す出力段と、図19に示す接続回路とにより構成したシミュレーションのための増幅回路を示す図である。

【図23】図22に示す増幅回路を非反転型負帰還増幅回路として動作させたシミュレーションのための各条件を示す一覧表である。

【図24】シミュレーション結果の直流伝達特性曲線を示すグラフである。

【図25】従来の増幅回路の入力段を示す図である。

【図26】従来の増幅回路の入力段と出力段とを説明するため図である。

【図27】他の従来の増幅回路(デジタルバッファ回路)の出力段(出力回路)を示す図である。

【図28】ホットキャリア問題を説明するためのグラフである。

【発明を実施するための形態】

【0037】

本発明の実施の形態に係る増幅回路を図面に基づいて説明する。なお、以下の表記において、pトランジスタはpMOSトランジスタ、nトランジスタはnMOSトランジスタを示している。また、図中、「bias」は電圧バイアスまたは電流バイアスを示す。

【0038】

(増幅回路の入力段)

まず、増幅回路の入力段(入力回路)について、図1から図10に基づいて説明する。入力段の説明においては、定格電源電圧に対して1倍の電圧をVDD、2倍の電圧を2VDD、3倍の電圧を3VDD、N1倍(N1は2以上の整数)の電圧をN1VDDと称す。

図1に示す増幅回路の入力段は、一方の電源線と他方の電源線とにより供給される電圧と同じ値の電圧N1VDDのコモンモード入力電圧を入力できるものであり、一方の電源線を電圧がN1VDDの電源線、他方の電源線をグランド(電圧の基準節点)としたものである。増幅回路の入力段は、VDDより高い電源電圧を使用しているが、この電圧は外部から供給したり、LSI内部に設けたチャージポンプにより昇圧したりすることができる。

【0039】

この増幅回路の入力段は、一対の入力端子IN1,IN2を介して入力電圧(差動モード入力電圧およびコモンモード入力電圧)が入力される第1の差動対トランジスタ10と、第1の入力段電流バイアス手段20と、第1の入力段カスコードトランジスタ群30と、一対の第2の入力段カスコードトランジスタ群40と、一対の出力用トランジスタ対50と、入力段バイアス調整回路60とを備えている。

【0040】

第1の差動対トランジスタ10は、pトランジスタMI11とpトランジスタMI12とにより形成され、ソース同士が接続点C1で接続され、それぞれのゲートに入力端子IN1,IN2が接続されている。

第1の入力段電流バイアス手段20は、ソースが一方の電源線のN1VDDに接続されている。第1の入力段電流バイアス手段20は、第1の差動対トランジスタ10に第1の入力段カスコードトランジスタ群30を介して所定のバイアス電流を供給するもので、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMC11により形成されている。この第1の入力段電流バイアス手段20は、pトランジスタMC11と対となるトランジスタを設けることでカレントミラー回路構成とすることができる。

【0041】

第1の入力段カスコードトランジスタ群30は、N1−1個がカスコード接続された第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMIUA1〜MIUA(N1-1)により構成され、一端が第1の差動対トランジスタ10のそれぞれのpトランジスタMI11,MI12の2つのソース端子の接続点C1に接続され、他端が第1の入力段電流バイアス手段20のpトランジスタMC11のドレインに接続されている。

第2の入力段カスコードトランジスタ群40は、N1−1個がカスコード接続された第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMILA1〜MILA(N1-1)と、pトランジスタMILB1〜MILB(N1-1)により構成され、一端が第1の差動対トランジスタ10のそれぞれのpトランジスタMI11,MI12のドレインに接続され、他端が出力用トランジスタ対50に接続されている。

【0042】

出力用トランジスタ対50は、第1の差動対トランジスタ10と異なる伝導極性を有するnトランジスタMC21とnトランジスタMC31とから構成され、ゲートおよびドレインが出力段への接続回路へ接続され、ソースが他方の電源線であるグランドに接続されている。

【0043】

入力段バイアス調整回路60は、入力段におけるバイアスを調整する回路である。入力段バイアス調整回路60は、第1の入力段カスコードトランジスタ群30のそれぞれのゲートと、第2の入力段カスコードトランジスタ群40のそれぞれのゲートに接続されて、コモンモード入力電圧に応じて調整されたバイアス電圧を与えることで、一対の入力端子IN1,IN2に0VからN1VDDまでの間で変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のそれぞれのゲート−ソース間電圧(VGS)およびゲート−ドレイン間電圧(VGD)の絶対値がVDD以内となるように、第1の入力段カスコードトランジスタ群30および第2の入力段カスコードトランジスタ群40のバイアス電圧を調整する機能を備えている。

図1は、一方の電源線の電圧がN1VDD以上の場合を示しているが、この電圧を−N1VDD以下(絶対値がN1VDD以上)にして、MOSトランジスタの伝導極性をpトランジスタとnトランジスタとで相互に反転させれば、回路の接続関係を変更することなく同様の動作をさせることができる。

【0044】

ここで、入力段バイアス調整回路60は、図2に示すような構成とすることができる。なお、図2において、図1と同じ構成のものは同符号を付して説明を省略する。

入力段バイアス調整回路60は、レベルシフト手段を構成するpトランジスタMD1と、第1の入力段カスコードバイアス用抵抗手段61と、第2の入力段カスコードバイアス用抵抗手段62と、第1の抵抗手段63と、第2の抵抗手段64と、第1の入力段電流バイアス手段20のpトランジスタMC11と対となるpトランジスタMC12とを備えている。

【0045】

pトランジスタMD1は、第1の差動対トランジスタ10(pトランジスタMI11,MI12)の接続点C1に接続されたダイオード接続されたトランジスタであり、pトランジスタMI11,MI12のVGSに相当する電圧分またはそれ以上の電圧をレベルシフトするレベルシフト手段としての働きを担うものである。

第1の入力段カスコードバイアス用抵抗手段61は、第1の入力段カスコードトランジスタ群30のバイアス電圧として接続された(N1−1)×VDDに一端が接続されていると共に、第1の入力段カスコードトランジスタ群30の各ゲート間に接続されたN1−2個のほぼ同値の直列抵抗(抵抗RIU1〜RIU(N1-2))が接続されている。

第2の入力段カスコードバイアス用抵抗手段62は、pトランジスタMD1とグランドとの間にN1個のほぼ同値の直列抵抗(抵抗RIL1〜RILN1)が接続されていると共に、第2の入力段カスコードトランジスタ群40の各ゲートに直列抵抗の各接続点C21〜C2(N1-1)が接続されている。

【0046】

第1の抵抗手段63(抵抗RX)は、第1の入力段カスコードバイアス用抵抗手段61の他端に接続されている共に、VDDに接続されている。この抵抗RXの抵抗値は、第1の入力段カスコードバイアス用抵抗手段61の合計の抵抗値とほぼ同値(抵抗RX=抵抗RIU1+抵抗RIU2+・・・+抵抗RIU(N1-3)+抵抗RIU(N1-2))である。

【0047】

第2の抵抗手段64(抵抗R0)は、第1の入力段カスコードバイアス用抵抗手段61と、第1の抵抗手段63との接続点C3に一端が接続され、第1の差動対トランジスタ10(pトランジスタMI11,MI12)の接続点C1に他端が接続されている。この抵抗R0の抵抗値は、第1の入力段カスコードバイアス用抵抗手段61の各抵抗値とほぼ同値(抵抗R0=抵抗RIU1=抵抗RIU2=・・・=抵抗RIU(N1-3)=抵抗RIU(N1-2))である。第2の抵抗手段64は、第1の入力段カスコードバイアス用抵抗手段61と第1の抵抗手段63と共に、コモンモード入力電圧に応じて調整されたバイアス電圧を発生させる制御手段とも考えることができる。従って、後述するように他の制御手段に置き換えることもできる。また、コモンモード入力電圧に応じて制御されていればそれが必ずしも接続点C1に接続されている必要はない。

【0048】

以上のように構成された本発明の実施の形態に係る増幅回路の入力段の動作を図面に基づいて説明する。

入力端子IN1,IN2に0Vとなるコモンモード入力電圧が入力されたときには、説明を簡単にするために第1の差動対トランジスタ10のゲートソース間電圧を|pトランジスタMI11,MI12のVGS|≪VDDとしてVGSを無視すれば、接続点C1が略0Vとなるため、第1の入力段カスコードバイアス用抵抗手段61の各抵抗(抵抗RIU1〜RIU(N1-2))と第2の抵抗手段64(抵抗R0)とは、(N1−1)×VDDの電圧が印加された分割抵抗となる。また、そのとき接続点C3がVDDとなるため、抵抗RXからは電流が流れ込まない。従って、各抵抗の電圧降下はそれぞれVDDとなるため、第1の入力段カスコードトランジスタ群30のpトランジスタMIUA(N1-1)のゲート電圧として(N1−1)×VDD、pトランジスタMIUA(N1-2)のゲート電圧として(N1−2)×VDD、・・・pトランジスタMIUA2のゲート電圧として2VDD、pトランジスタMIUA1のゲート電圧としてVDDがバイアスされる(図3(A)参照)。従って、各pトランジスタMIUA1〜MIUA(N1-1)のVGSおよびVGDの絶対値がVDD以内となる。

【0049】

また、接続点C1が0Vであり、pトランジスタMD1を介した接続点C4はほぼ0Vとなるため、0Vとなった接続点C4とグランドとの間の第2の入力段カスコードバイアス用抵抗手段62の端子電圧はそれぞれが0Vとなる。従って、第2の入力段カスコードトランジスタ群40のpトランジスタMILA1〜MILA(N1-1)のゲート電圧およびpトランジスタMILB1〜MILB(N1-1)のゲート電圧は0Vとなる(図3(A)参照)。

【0050】

次に、入力端子IN1,IN2にN1VDDとなるコモンモード入力電圧が入力されたときには、接続点C1が略N1VDDとなるため、接続点C3の電圧は抵抗R0と抵抗Rxによる電圧分割により(N1−1)×VDDとなる。従って、第1の入力段カスコードバイアス用抵抗手段61の各抵抗(抵抗RIU1〜RIU(N1-2))には、全ての端子に同一の(N1−1)×VDDの電圧が印加された状態となるため、第1の入力段カスコードトランジスタ群30のpトランジスタMIUA1〜MIUA(N1-1)の各ゲートには、(N1−1)×VDDがバイアスされる(図3(B)参照)。

【0051】

また、N1VDDとなった接続点C1から、pトランジスタMD1と第2の入力段カスコードバイアス用抵抗手段62とを介してグランドに電流が流れるが、簡単とするためにpトランジスタMD1のゲートソース間電圧を|pトランジスタMD1のVGS|≪VDDとしてVGSを無視すれば、第2の入力段カスコードバイアス用抵抗手段62の各抵抗(抵抗RIL1〜RIL(N1-2))は、N1VDDの電圧が印加された分割抵抗となる。従って、各抵抗の電圧降下はVDDとなるため、第2の入力段カスコードトランジスタ群40のpトランジスタMILA1,MILB1のゲート電圧として(N1−1)×VDD、pトランジスタMILA2,MILB2のゲート電圧として(N1−2)×VDD、・・・pトランジスタMILA(N1-2),MILB(N1-2)のゲート電圧として2VDD、pトランジスタMILA(N1-1),MILB(N1-1)のゲート電圧としてVDDがバイアスされる(図3(B)参照)。従って、各pトランジスタMILA1〜MILA(N1-1),MILB1〜MILB(N1-1)のVGSおよびVGDの絶対値がVDD以内となる。

以上の動作説明では、説明を簡単とするために第1の差動対トランジスタ10のゲート−ソース間電圧VGSとpトランジスタMD1のゲート−ソース間電圧VGSを無視したが、この影響によるバイアス調整電圧の差は実質的には本発明の効果を損ねるものではない。

また、第1の差動対トランジスタ10のゲート−ソース間電圧VGSとpトランジスタMD1のゲート−ソース間電圧VGSの影響も考慮して抵抗Ro,Rx,抵抗RIL1の値を上記バイアス電圧により近くなるように調整することもできる。

【0052】

そして、それぞれの第2の入力段カスコードトランジスタ群40を流れる信号電流は、nトランジスタMC21とnトランジスタMC31とのそれぞれのドレインからソースに流れる。そのうちの少なくとも信号電流成分を次段である出力段に接続される接続回路への出力信号として出力することができる。

【0053】

このように、入力端子IN1,IN2に入力されたコモンモード入力電圧が0VからN1VDDまで変化しても、第1の入力段カスコードトランジスタ群30と第2の入力段カスコードトランジスタ群40へのバイアス電圧を調整した電圧に制御することができるので、本実施の形態に係る増幅回路の入力段は、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる。

【0054】

なお、ダイオード接続されたpトランジスタMD1と、第2の入力段カスコードバイアス用抵抗手段62の抵抗RIL1との接続関係は、必ずしも上記に限定されるものではない。pトランジスタMD1と第2の入力段カスコードバイアス用抵抗手段62の抵抗RIL1を入れ替えても回路動作は等価であることは自明である。すなわち、第2の入力段カスコードバイアス用抵抗手段62は、接続点C1とグランドの間にpトランジスタMD1を介して直列接続されたN1個の抵抗手段とすることもできる。

【0055】

図2に示す入力段は、pトランジスタとnトランジスタとを置換すると共に、一方の電源線を−N1VDDとし、他方の電源線をグランド(基準節点)として電位(極性)を反転させた図4に示す入力段とすることができる。なお、図4においては、pトランジスタとnトランジスタとの違いはあるが、理解がしやすいように、図2に対応させて符号を記載している。

図4に示す入力段では、入力端子IN1,IN2に0Vとなるコモンモード入力電圧が入力されたときには、nトランジスタMIUA(N1-1)のゲート電圧として−(N1−1)×VDD、nトランジスタMIUA(N1-2)のゲート電圧として−(N1−2)×VDD、・・・nトランジスタMIUA2のゲート電圧として−2VDD、nトランジスタMIUA1のゲート電圧として−VDDがバイアスされる。また、nトランジスタMILA1〜MILA(N1-1)のゲート電圧およびnトランジスタMILB1〜MILB(N1-1)のゲート電圧は0Vとなる(図5(A)参照)。従って、各nトランジスタMIUA1〜MIUA(N1-1)のVGSおよびVGDの絶対値をVDD以内とすることができる。

入力端子IN1,IN2に−N1VDDとなるコモンモード入力電圧が入力されたときには、nトランジスタMIUA1〜MIUA(N1-1)の各ゲートには、−(N1−1)×VDDがバイアスされる。また、nトランジスタMILA1,MILB1のゲート電圧として−(N1−1)×VDD、nトランジスタMILA2,MILB2のゲート電圧として−(N1−2)×VDD、・・・nトランジスタMILA(N1-2),MILB(N1-2)のゲート電圧として−2VDD、nトランジスタMILA(N1-1),MILB(N1-1)のゲート電圧として−VDDがバイアスされる(図5(B)参照)。従って、各nトランジスタMILA1〜MILA(N1-1),MILB1〜MILB(N1-1)のVGSおよびVGDの絶対値をVDD以内とすることができる。

【0056】

(入力段の第1変形例)

図2に示す増幅回路の入力段では、抵抗R0を第1の差動対トランジスタ10の接続点C1に接続していたが、図6に示すように分離することも可能である。

図6に示す増幅回路の入力段には、入力段バイアス調整回路60aとして、第1の差動対トランジスタ10に対応する第2の差動対トランジスタ11と、第1の入力段電流バイアス手段20に対応する第2の入力段電流バイアス手段21と、第1の入力段カスコードトランジスタ群30に対応する第3の入力段カスコードトランジスタ群31と、第2の入力段カスコードトランジスタ群40に対応する第4の入力段カスコードトランジスタ群41とが含まれている。

【0057】

第2の差動対トランジスタ11は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMI21とpトランジスタMI22とにより形成され、ソース同士が接続点C5で接続され、ドレイン同士が接続点C6で接続され、それぞれのゲートに入力端子IN1,IN2とが接続されている。

第2の入力段電流バイアス手段21は、第1の入力段電流バイアス手段20のpトランジスタMC11と共に、pトランジスタMC12とカレントミラー回路を構成し、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMC13により形成されている。

【0058】

第3の入力段カスコードトランジスタ群31は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMIUB1〜MIUB(N1-1)により形成され、第2の差動対トランジスタ11のソース同士を接続する接続点C5に一端が接続されている。

第4の入力段カスコードトランジスタ群41は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMILC1〜MILC(N1-1)により形成され、第2の差動対トランジスタ11のドレイン同士を接続する接続点C6とグランドとの間に接続されている。

pトランジスタMC13は、第1の差動対トランジスタ10と同じ伝導極性を有するpトランジスタMC11と同様にソースがN1VDDに接続され、ドレインが第3の入力段カスコードトランジスタ群31に接続され、pトランジスタMC12とカレントミラー回路を構成する。

【0059】

このように第2の差動対トランジスタ11を新たに設け、第2の入力段電流バイアス手段21と、第3の入力段カスコードトランジスタ群31と、第4の入力段カスコードトランジスタ群41とを設けることで、図2と同様の動作をさせることができると同時に、出力段に伝送するための信号電流が流れる第1の差動対トランジスタ10と、第2の入力段カスコードバイアス用抵抗手段62および第1の入力段カスコードバイアス用抵抗手段61に流れる電流とを分離することができるので、第1の差動対トランジスタ10への悪影響を排除することができる。

【0060】

図6に示す増幅回路の入力段は、一般化した場合を示し、電源電圧をN1VDDとした例であるが、例えば、コモンモード入力電圧を2VDD(N1=2)とした場合には、図7に示すような回路とすることができる。また、コモンモード入力電圧を3VDD(N1=3)とした場合には、図8に示すような回路とすることができる。

【0061】

図7(N1=2の入力段)および図8(N1=3の入力段)を比較して判るように、コモンモード入力電圧の耐圧を2VDDとした場合には、第1の入力段カスコードトランジスタ群30,第3の入力段カスコードトランジスタ群31がpトランジスタMIUA1,MIUB1が1個ずつとなるため、pトランジスタMIUA1,MIUB1にはゲート電圧としてVDDをバイアスすればよい。従って、図6に示した第1の入力段カスコードバイアス用抵抗手段61と第1の抵抗手段63と、第2の抵抗手段64とが省略される。

このようにして、コモンモード電圧が定格電源電圧の任意の倍数電圧でも耐える増幅回路の入力段を設計することができる。

【0062】

(入力段の第2変形例)

図2,図4,図6における一般化した入力段バイアス調整回路60,60aの各抵抗手段(第1の入力段カスコードバイアス用抵抗手段61,第1の抵抗手段63,第2の抵抗手段64)は、以下で説明するように、コモンモード入力電圧により制御されるMOSトランジスタ回路に置換することができる。すなわち、抵抗手段の代わりに、MOSトランジスタによる可変抵抗手段、スイッチ手段、レベルシフト手段を使用することができる。そのことを図9に基づいて説明する。

図7に示す入力段は、図9に示すような入力段とすることもできる。図9に示す増幅回路の入力段は、定格電源電圧の2倍(VDDのN1倍の電圧をN1VDDと表記したときのN1=2の場合である。)のコモンモード入力電圧を入力可能とするものである。図9においては、一方の電源線の電圧はN1(=2)以上の3VDDが使用されている。なお、図9においては、図7と同じ構成のものは同符号を付して説明を省略する。

【0063】

図9に示す入力段の入力段バイアス調整回路60bは、ダイオード接続されたpトランジスタMD1のゲートとドレインとの接続点C10とグランドとの間に、カレントミラー回路構成のnトランジスタMC61,MC62のうちの一方のnトランジスタMC61が接続されてpトランジスタMD1に電流バイアスを与えている。この接続点C10には、第2の入力段カスコードトランジスタ群40,第4の入力段カスコードトランジスタ群41のpトランジスタMILA1,MILB1,MILC1のゲートが接続されている。

ダイオード接続されたpトランジスタMD1のソースは、接続点C11を介してpトランジスタMB1のソースに接続されている。pトランジスタMB1のゲートはVDDにバイアスされ、ドレインはグランドに接続されている。

【0064】

第1の入力段カスコードトランジスタ群30のpトランジスタMIUA1と、第3の入力段カスコードトランジスタ群31のpトランジスタMIUB1とは、VDDに固定バイアスされている。このpトランジスタMIUA1は、pトランジスタMIUA1と同じ伝導極性のpトランジスタMUX1を介在して第1の入力段電流バイアス手段20のpトランジスタMC11に接続されている。従って、第1の入力段カスコードトランジスタ群30のpトランジスタMIUA1には、バイアス電流が第1の入力段電流バイアス手段20から供給される。

また、このpトランジスタMIUB1はpトランジスタMIUB1と同じ伝導極性のpトランジスタMUY1を介在して第2の入力段電流バイアス手段21のpトランジスタMC13に接続されている。従って、第3の入力段カスコードトランジスタ群31のpトランジスタMIUB1には、バイアス電流が第2の入力段電流バイアス手段21から供給される。

【0065】

また、第2の差動対トランジスタ11にダイオード接続のpトランジスタMD2,MD3をそれぞれのゲートに接続している。これは、増幅回路をボルテージフォロワ等の非反転型帰還増幅回路に応用した際に、立ち上がりが急峻な矩形波を入力信号として入力したときにレスポンスが遅くなり、出力段から入力段への帰還信号が遅れて到達することによる不具合を解消するためのものである。

【0066】

次に、図9に示す入力段の動作について図面に基づいて説明する。

図9のpトランジスタMB1,nトランジスタMC61は図7の抵抗RIL1,RIL2に代わるもので、可変抵抗手段として機能するものである。入力端子IN1,IN2に入力されたコモンモード入力電圧が変化すると、第2の差動対トランジスタ11のpトランジスタMI21,MI22のゲートが制御され、コモンモード入力電圧に応じてpトランジスタMB1のソース(接続点C11)、pトランジスタMD1を介して、nトランジスタMC61のドレインが制御される。

【0067】

まず、入力端子IN1,IN2に、2VDDを超えないVDDを中心として増減するコモンモード入力電圧が入力されると、第1の差動対トランジスタ10のpトランジスタMI11,MI12のゲートが制御され、接続点C6,C10,C11の電圧が増減する。

【0068】

例えば、コモンモード入力電圧がVDDを超えた場合には、pトランジスタMB1のゲートがVDDによりバイアスされているため、第2の差動対トランジスタ11のpトランジスタMI21,MI22はカットオフ状態となり、接続点C11の電圧は一定値に保持される。従って、接続点C11とダイオード接続されたpトランジスタMD1を介した接続点C10の電圧は、接続点C11からpトランジスタMD1のVGS分降下した電圧となり、接続点C11の電圧は、pトランジスタMB1のゲート電圧VDDからVGS分高い電圧となる。つまり、接続点C10の電圧は、VDD+|pトランジスタMB1のVGS|−|pトランジスタMD1のVGS|≒VDDとなる。

【0069】

接続点C10がVDDとなることにより、第1の差動対トランジスタ10のpトランジスタMI11,MI12にカスケード接続されたpトランジスタMILA1,MILB1がVDDにバイアスされる。

従って、コモンモード入力電圧がVDDを超えて2VDDに到達しても、pトランジスタMI11,MI12のVGS,VGDと、pトランジスタMI21,MI22のVGS,VGDとは、その絶対値をVDD以内とすることができる。

図9に示す入力段で一方の電源線にN1VDD(=2)以上の3VDDを使用しているのはこの効果のためである。

【0070】

コモンモード入力電圧がVDDのとき、pトランジスタMIUA1,MIUB1は線形領域で動作している。更に、コモンモード入力電圧が増加して2VDDとなると、pトランジスタMUX1も線形領域で動作し始める。しかし、pトランジスタMC11,MC13はソースが3VDDに接続されているため活性領域での作動状態であるので、第1の差動対トランジスタ10への増幅動作に与える影響はほとんど無視できる。

【0071】

次に、コモンモード入力電圧がVDDより低くなると、接続点C11の電圧が下がり、pトランジスタMB1はカットオフとなる。接続点C11の電圧が下がると、pトランジスタMD1を介してnトランジスタMC61のドレイン(接続点C10)の電圧も下がる。このとき、接続点C10の電圧は、(コモンモード入力電圧)+|pトランジスタMI21のVGS|−|pトランジスタMD1のVGS|≒(コモンモード入力電圧)となる。従って、コモンモード入力電圧が0Vのとき、接続点C10の電圧も0Vとなり、この電圧が第2の入力段カスコードトランジスタ群40のゲートにバイアスされる。このとき、pトランジスタMIUA1とpトランジスタMIUB1のゲートはVDDにバイアスされている。従って、コモンモード入力電圧が0Vに到達しても、pトランジスタMI11,MI12のVGS,VGDと、pトランジスタMI21,MI22のVGS,VGDとは、その絶対値をVDD以内とすることができる。

【0072】

このように、pトランジスタMC11,MC13をN1=2VDDより高い電圧である3VDDに接続し、pトランジスタMUX1,MUY1を、第1の入力段カスコードトランジスタ群30と第3の入力段カスコードトランジスタ群31とにカスコード接続することで、コモンモード入力電圧が2VDDのときでもpトランジスタMC11とpトランジスタMC13を活性領域に維持できるので、第1の差動対トランジスタ10への増幅動作に与える影響を排除することができる。従って、入力段X1の性能を向上させることができる。

コモンモード入力電圧がVDDより小さいときに、差動対トランジスタMI11,MI12を活性領域で動作させるために、pトランジスタMD1のアスペクト比を小さくして|VGS|を大きく設定し、差動対トランジスタMI11,MI12の|VDS|が大きくなるようにするのが望ましい。

【0073】

以上の説明から明らかなように、図9に示す入力段バイアス調整回路60bのpトランジスタMB1,nトランジスタMC61は、図7に示す入力段バイアス調整回路60aの第2の入力段カスコードバイアス用抵抗手段62に代わるもので、コモンモード入力電圧によって制御される。pトランジスタMB1はレベルシフト手段を備えたスイッチ手段またはレベルシフト手段を備えた可変抵抗手段として動作し、また、nトランジスタMC61は可変抵抗手段として動作して入力段のバイアスを調整する。

【0074】

図9に示す入力段では、定格電源電圧の2倍となる2VDD(N1=2)よりVDD分ほど高い3VDDを一方の電源線としているため、第1の入力段カスコードトランジスタ群30と第1の入力段電流バイアス手段(pトランジスタMC11のドレイン)との間、および第3の入力段カスコードトランジスタ群31と第2の入力段電流バイアス手段(pトランジスタMC13のドレイン)との間に、それぞれ同じ伝導極性を有するpトランジスタMUX1,MUY1を1個ずつカスコード接続している。

そして、入力段の電源電圧が2VDDより2VDDだけ高い4VDDの場合では、同様に、第1の入力段カスコードトランジスタ群30と第1の入力段電流バイアス手段(pトランジスタMC11のドレイン)との間、および第3の入力段カスコードトランジスタ群31と第2の入力段電流バイアス手段(pトランジスタMC13のドレイン)との間に、それぞれ2個のpトランジスタを接続すればよいし、入力段の電源電圧が2VDDより3VDDだけ高い5VDDの場合ではそれぞれ3個のpトランジスタを接続すればよいというように、4VDD以上でも第1の入力段カスコードトランジスタ群30および第3の入力段カスコードトランジスタ群31と伝導極性が同じpトランジスタをカスコード接続して積み上げて、pトランジスタMC11またはMC13に接続すればよい。

つまり、一方の電源線の電源電圧と入力可能とするコモンモード入力電圧との差分からVDDの何倍であるかを算出して、VDDの倍数分のMOSトランジスタを第1の入力段カスコードトランジスタ群30と第3の入力段カスコードトランジスタ群31とのそれぞれにカスコード接続することで、入力可能とするコモンモード入力電圧以上の電源電圧を一方の電源線とすることができる。

【0075】

図9においては、N1=2の場合であるが、更に、N1が3以上の場合にも同様である。すなわち、例えば、コモンモード入力電圧の最大値がMOSトランジスタの定格電源電圧の3倍となる3VDD(N1=3)の場合、それよりVDD分ほど高い4VDDを一方の電源線として使用し、第1の入力段カスコードトランジスタ群30と第3の入力段カスコードトランジスタ群31とに、同じ伝導極性を有するpトランジスタを1つカスコード接続すればよいし、2VDD高い5VDDの場合は前記pトランジスタをそれぞれ2個カスコード接続すればよい。このように、一方の電源線の電源電圧の絶対値を他方の電源線を基準としてN1VDDより大きくするこの手法は、図7、図9の回路に限定されず、本発明に係るすべての入力段に適用することができる。

【0076】

(入力段の第3変形例)