変換器及び変換方法

【課題】メモリアクセスを削減する変換器及び変換方法を提供する。

【解決手段】本発明の変換器は、メモリからフェッチしたレジスタ形式のバイトコードを保持する保持部と、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部と、保持部からバイトコードを取り出し、第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成する命令作成部と、物理レジスタと、命令作成部が作成したネイティブコードにより当該物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタとの対応関係を示すデータを格納する第2記憶部と、を備え、命令作成部は、作成するネイティブコードが、第2記憶部に格納されたデータに含まれるメモリ上のレジスタに関するロード命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする。

【解決手段】本発明の変換器は、メモリからフェッチしたレジスタ形式のバイトコードを保持する保持部と、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部と、保持部からバイトコードを取り出し、第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成する命令作成部と、物理レジスタと、命令作成部が作成したネイティブコードにより当該物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタとの対応関係を示すデータを格納する第2記憶部と、を備え、命令作成部は、作成するネイティブコードが、第2記憶部に格納されたデータに含まれるメモリ上のレジスタに関するロード命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、レジスタ形式のバイトコードをネイティブコードに変換する変換器及び変換方法の技術に関する。

【背景技術】

【0002】

近年、Google(登録商標)社の携帯情報端末向けプラットフォームAndroid(登録商標

)を搭載した携帯電話が急速に普及している。このような携帯電話で実行されるアプリケーションは、ポータビリティを高めるため、通常は、Java(登録商標)などの特定のコンピュータ及びオペレーティングシステムに依存しないプログラム言語により作成される。当該プログラム言語では、すべてのプログラムは一度、中間言語であるバイトコードにコンパイルされる。Androidで採用されているバイトコードは、Javaバイトコードなどとは

異なり、メモリ上に存在するレジスタ(領域)を直接指定して演算を行う、という特徴をもつ。このようなバイトコードは、レジスタ形式のバイトコードと呼ばれている。

【0003】

バイトコードは、特定のコンピュータ及びオペレーティングシステムに依存しないため、それを解釈及び実行できる環境があれば、任意のプロセッサ上で実行される。通常、VM(Virtual Machine)が、バイトコードを逐次解釈し、実行する。

【0004】

このようなバイトコードの実行は、VMを介して行われるため、機械語で表されたネイティブコード(オブジェクトプログラムまたはオブジェクトコードとも呼ばれる)の実行と比べて遅い。そのため、バイトコードの実行を高速化する様々な手法がこれまでに提案されてきた。当該手法を開示する文献として、以下の非特許文献1が挙げられる。

【0005】

非特許文献1には、例えば、プロセッサの一部に、Javaバイトコードをネイティブコードに変換できるハードウェア(アクセラレータ)を追加することにより、バイトコードの実行を高速化する手法が開示されている。このようなアクセラレータが追加されることにより、バイトコードはネイティブコードに変換されるため、プロセッサは、VM等のソフトウェアを介さず、直接バイトコードを解釈及び実行することができるようになる。これによって、VM等のソフトウェアを介することによるオーバヘッドが削減される。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】“ARMアーキテクチャリファレンスマニュアル”、[online]、アーム株式会社、[平成22年10月15日検索]、インターネット〈URL:https://www.jp.arm.com/document/manual/files/051020DDI0100HJ_v6_1.pdf〉

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記非特許文献1において開示される技術により単純に実装されたアクセラレータは、レジスタ形式のバイトコードの場合、バイトコードの各オペランドがメモリ上に存在するため、多数のストア命令及びロード命令に関するネイティブコードを発行してしまう。そのため、メモリアクセスの効率が悪い。

【0008】

本発明は、このような点を考慮してなされたものであり、メモリアクセスを削減する変換器及び変換方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明は、上述した課題を解決するために、以下の構成を採用する。

【0010】

すなわち、本発明の変換器は、メモリからフェッチしたレジスタ形式のバイトコードを保持する保持部と、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部と、保持部に保持されているバイトコードを取り出し、第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成する命令作成部と、物理レジスタの番号と、命令作成部が作成したネイティブコードにより当該番号の物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタの番号との対応関係を示すデータを格納する第2記憶部と、を備え、命令作成部は、作成するネイティブコードが、第2記憶部に格納されたメモリ上のレジスタの番号によって特定されるアドレスに関するロード命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする。

【0011】

上記構成によれば、命令作成部は、第2記憶部に格納されたメモリ上のレジスタの番号によって特定されるアドレスに関するロード命令に関するネイティブコードの作成を省略する。したがって、上記構成によれば、一部のロード命令に関するネイティブコードの発行が省かれるため、メモリアクセスを削減することができる。

【0012】

また、上記命令作成部は、ネイティブコードを作成する際に必要な物理レジスタの番号を、第2記憶部に格納されたデータに含まれる物理レジスタの番号を用いて特定してもよい。

【0013】

また、上記命令作成部は、作成するネイティブコードがメモリ上のレジスタに関するストア命令であると判定した場合、当該ネイティブコードの作成を省略してもよい。

【0014】

上記構成によれば、命令作成部は、メモリ上のレジスタに関するストア命令に関するネイティブコードの作成を省略する。したがって、上記構成によれば、一部のストア命令に関するネイティブコードの発行が省かれるため、メモリアクセスを削減することができる。

【0015】

また、上記命令作成部は、物理レジスタを割り当てるネイティブコードのひな形を第1記憶部から取得した時、バイトコードに含まれるメモリ上のレジスタの番号と、当該アドレスに割り当てる物理レジスタの番号との対応関係を示すデータを作成し、当該データを第2記憶部に格納してもよい。

【0016】

上記構成によれば、命令作成部により作成されるネイティブコードにより対応付けられる物理レジスタとメモリ上のレジスタの番号との対応関係が第2記憶部に格納される。つまり、第2記憶部は、ネイティブコードの実行状態に対応した、メモリ上のレジスタの番号と物理レジスタの番号との対応関係を示すデータが格納される。これにより、命令作成部は、ネイティブコードの実行状態に対応して、ロード命令に関するネイティブコードの作成を省略することができる。

【0017】

また、上記命令作成部は、所定の時点において、第2記憶部に格納されているデータを削除し、当該削除するデータに含まれる番号の物理レジスタに格納されたデータを、当該削除するデータに含まれるメモリ上のレジスタの番号によって特定されるアドレスに書き込むストア命令のネイティブコードを作成してもよい。

【0018】

上記構成によれば、メモリ上のレジスタの番号と物理レジスタの番号との対応関係を示すデータが削除される時に、物理レジスタに格納されたデータを、対応するメモリ上のレジスタの番号によって特定されるアドレスにストアすることができる。

【0019】

また、本発明の変換方法は、メモリからフェッチしたレジスタ形式のバイトコードを保持するステップと、保持したバイトコードを取り出し、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成するネイティブコード作成ステップと、物理レジスタの番号と、ネイティブコード作成ステップにより作成されたネイティブコードにより当該番号の物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタの番号との対応関係を示すデータを第2記憶部に格納する記憶ステップと、を含み、ネイティブコード作成ステップでは、作成するネイティブコードが、第2記憶部に格納されたメモリ上のレジスタの番号に関するロード命令であると判定される場合、当該ネイティブコードの作成が省略されることを特徴とする。

【0020】

なお、本発明の別態様として、FPGA(Field-Programmable Gate Array)に読み込ませ

ることにより以上の各構成を実現するプログラムであってもよい。

【発明の効果】

【0021】

本発明によれば、メモリアクセスを削減する変換器及び変換方法を提供することができる。

【図面の簡単な説明】

【0022】

【図1】実施の形態に係る変換器を含むプロセッサの構成を例示する図

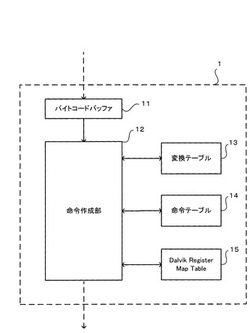

【図2】実施の形態に係る変換器の構成を例示する図

【図3】変換テーブルと命令テーブルの一例を示す図

【図4】DRMTの一例を示す図

【図5】1つ目の加算命令に関するバイトコードの変換例を示す図

【図6】2つ目の加算命令に関するバイトコードの変換例を示す図

【発明を実施するための形態】

【0023】

以下、本発明の一側面に係る変換器及び変換方法を、実施の形態(以下、「本実施形態」とも表記する)として説明する。ただし、以下に挙げる実施形態は例示であり、本発明は以下の実施形態の構成に限定されない。

【0024】

本実施形態の変換器を含むプロセッサは、その一例としてMIPSプロセッサである。そして、本実施形態の変換器は、レジスタ形式のバイトコードの一例としてDalvikバイトコードを、MIPS命令セットに対応したネイティブコードに変換する。Dalvikバイトコードとは、Androidにおいて用いられているJavaの実行モデルで採用されている命令セットである

。

【0025】

なお、MIPS命令セットに対応したネイティブコードの命令長は32ビットである。これに対して、Dalvikバイトコードの命令長は、可変長であり、最長80ビットである。また、Dalvikバイトコードでは、各命令は、Dalvikレジスタに対して演算処理を行う。ここで、Dalvikレジスタは、物理レジスタを指すものではなく、メモリ上に割り当てられた領域を指す。そして、当該領域のアドレスは、ベースアドレスと当該Dalvikレジスタの番号とによって特定される。Dalvikバイトコードにおける各命令では、0〜3個のDalvikレジスタをオペランドとして、これらの値を用いた演算が実施される。

【0026】

§1 プロセッサの構成例

まず、本実施形態に係る変換器を含むプロセッサの構成例について説明する。図1は、本実施形態に係る変換器を含むプロセッサを例示する。図1に示されるとおり、本実施形

態に係る変換器1を含むプロセッサ100は、変換器1、フェッチャ2、ステータスレジスタ3、ネイティブデコーダ4、演算装置5、及び物理レジスタ6を備える。

【0027】

フェッチャ2は、メモリ7に格納されたDalvikバイトコードまたはネイティブコードをフェッチする(読み出す)。フェッチしたDalvikバイトコードは、変換器1によってネイティブコードに変換される。そして、変換器1によって変換された又はフェッチャ2が出力したネイティブコードは、ネイティブデコーダ4に入力される。

【0028】

変換器1は、フェッチャ2がフェッチしたDalvikバイトコードをネイティブコードに変換する。詳細は「§2 変換器の構成例」に後述する。

【0029】

ステータスレジスタ3は、Dalvikバイトコードによる命令実行モードか、ネイティブコードによる命令実行モードかを特定する識別子を格納する。このステータスレジスタ3により、上述したネイティブデコーダ4に入力されるネイティブコードの入力元が特定される。ステータスレジスタ3は、例えば、ネイティブコードによる命令実行モードにおいて、演算装置5が行う所定の演算処理により、その格納する識別子をDalvikバイトコードによる命令実行モードを示す識別子に書き換えられる。また、ステータスレジスタ3は、例えば、Dalvikバイトコードによる命令実行モードにおいて、変換器1が、フェッチャ2がフェッチしたバイトコードをネイティブコードに変換できなかった時、その格納する識別子をネイティブコードによる命令実行モードを示す識別子に所定の方法によって書き換えられる。このようにステータスレジスタ3の格納する値が書き換えられることにより、ネイティブデコーダ4にネイティブコードを入力する入力元が切り替えられる。

【0030】

ネイティブデコーダ4は、フェッチャ2または変換器1により入力されるネイティブコードをデコードする。

【0031】

演算装置5及び物理レジスタ6は、ネイティブデコーダ4のデコード結果に基づいて、所定の演算処理を行う。

【0032】

なお、これらの構成は、例えば、不図示の制御装置によって制御される。

【0033】

§2 変換器の構成例

次に、本実施形態に係る変換器1の構成例について説明する。図2は、本実施形態に係る変換器1の構成例を示す。

【0034】

変換器1は、図2に示されるとおり、そのハードウェア構成として、バイトコードバッファ11、命令作成部12、変換テーブル13、命令テーブル14、Dalvik Register Map Table(以下、「DRMT」と表記する)15、を有している。

【0035】

<バイトコードバッファ11>

バイトコードバッファ11は、フェッチャ2がフェッチして出力するDalvikバイトコードを保持する。これにより、後述する命令作成部12は、Dalvikバイトコードを1つ取り出すことが可能となる。

【0036】

具体的に説明すると、MIPS命令セットに対応したネイティブコードの命令長は32ビットであるため、フェッチャ2がメモリ7からフェッチするデータ長は32ビットである。これに対して、Dalvikバイトコードの命令長は、可変長であり、最長80ビットである。したがって、フェッチャ2は、1回のフェッチでDalvikバイトコードを1つ取り出すことができない場合がある。このため、1つのDalvikバイトコードをメモリ7から取り出すためには、フェッチャ2は複数回にわたりデータをフェッチする必要がある。バイトコード

バッファ11は、主に、このようなデータを保持するために用いられる。つまり、バイトコードバッファ11は、フェッチャ2が複数回にわたりメモリ7からフェッチしたデータを保持する。これにより、後述する命令作成部12は、当該バイトコードバッファ11に保持されたデータからDalvikバイトコードを1つ取り出すことが可能となる。

【0037】

なお、このような命令作成部12の処理を可能にするため、バイトコードバッファ11は、少なくともDalvikバイトコードの最長の命令長である80ビットのデータを保持する。

【0038】

<命令作成部12>

命令作成部12は、1つのDalvikバイトコードを、対応する1又は複数のネイティブコード(本実施形態では、MIPS命令列)へと変換する。

【0039】

具体的には、命令作成部12は、変換テーブル13、及び命令テーブル14から読み出された1または複数のネイティブコードのひな形(MIPS命令列のひな形)と、Dalvikバイトコードから得られたオペランドにより、ネイティブコードを作成し、後続するユニット(本実施形態では、ネイティブデコーダ4)へ出力する。ネイティブコードのひな形は、ネイティブコードのオペコード(命令コード)と、仮のオペランドとを有する。命令作成部12は、このネイティブコードのひな形に含まれる仮のオペランドを、バイトコードから得られたオペランド等を用いて所定のオペランドに置き換えることにより、ネイティブコードを作成する。これにより、命令作成部12は、1つのDalvikバイトコードを、対応する1又は複数のネイティブコード(本実施形態では、MIPS命令列)へと変換する。

【0040】

また、命令作成部12は、当該ネイティブコードの作成の際、DRMT15を参照することにより、一部のロード命令に関するネイティブコードの発行を停止する。言い換えると、命令作成部12は、DRMT15を参照することにより、一部のロード命令に関するネイティブコードの作成を省略する。具体的な処理については後述する。

【0041】

また、命令作成部12は、作成したネイティブコードが物理レジスタをDalvikレジスタに割り当てる命令である場合、当該Dalvikレジスタと物理レジスタの対応関係を示すデータ、具体的にはDalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)をDRMT15に登録する。具体的な処理については後述する。

【0042】

なお、物理レジスタをDalvikレジスタに割り当てる命令として、本実施形態では2つの命令が考えられる。

【0043】

1つ目の命令は、Dalvikレジスタをロードする命令である。当該命令が実行されると、メモリ上のあるアドレスに格納されているデータ(本実施形態では、Dalvikレジスタに格納されているデータ)が、物理レジスタにロードされる。つまり、物理レジスタがDalvikレジスタに割り当てられる。命令作成部12は、このような命令のネイティブコードのひな形を取得した時、Dalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)をDRMT15に登録する。

【0044】

2つ目の命令は、Dalvikバイトコードのデスティネーションオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令である。デスティネーションオペランドとは、そのバイトコードによる演算結果を格納するオペランドであり、Dalvikバイトコードの場合は先頭のオペランドがこれに該当する。このような命令も、上記ロード命令と同様に、物理レジスタがDalvikレジスタに割り当てられる。命令作成部12は、このような命令のネイティブコードのひな形を取得した時、Dalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)をDRMT15に登録する。なお、このような命令であることは、

変換テーブル13及び命令テーブル14のネイティブコードのひな形を格納するフィールド(後述する、Instフィールド)のデータフラグにより示される。命令作成部12は、このデータフラグにより、変換テーブル13又は命令テーブル14から取得したネイティブコードのひな形が、Dalvikバイトコードの先頭のオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令であることを認識する。

【0045】

また、命令作成部12は、変換テーブル13又は命令テーブル14から取得したネイティブコードのひな形がストア命令に関するひな形であって、Dalvikレジスタに対するストア命令のひな形である場合、当該ストア命令のネイティブコードの作成を省略する。つまり、命令作成部12は、Dalvikレジスタに対するストア命令に関するネイティブコードのひな形に対して、オペランドの置き換えを行わず、ネイティブコードの作成をしない。これにより、メモリアクセスが削減される。

【0046】

なお、本実施形態では、命令作成部12は、特定の時にDalvikレジスタに対するストア命令に関するネイティブコードを作成する。特定の時とは、後述するDRMT15がDalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)を削除する時である。命令作成部12は、後述するDRMT15がDalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)を削除する時、当該物理レジスタに格納されるデータを当該Dalvikレジスタにストアする命令に関するネイティブコードを作成する。

【0047】

<変換テーブル13>

変換テーブル13は、例えば、SRAM(Static Random Access Memory)により構成され

る。変換テーブル13は、Dalvikバイトコードのオペコードに対応付けられたネイティブコードのひな形を格納する命令テーブル14へのポインタを格納する。また、変換テーブル13は、Dalvikバイトコードのオペコードに対応づけられた1又は複数のネイティブコードのひな形が変換テーブル13又は命令テーブル14に存在するかどうかを示すフラグを格納する。言い換えると、変換テーブル13は、Dalvikバイトコードをネイティブコードに変換可能かどうかを示すフラグを格納する。

【0048】

ここで、変換テーブル13は、命令作成部12が命令テーブル14を参照してネイティブコードを作成する際のレイテンシの増加を抑えるため、命令テーブル14上の上記対応する1又は複数のネイティブコードのひな形の一部(例えば、数命令分のネイティブコードのひな形)を格納していてもよい。本実施形態では、1命令分のネイティブコードを格納している。

【0049】

図3は、変換テーブル13及び後述する命令テーブル14の一例を示す。図3に示されるとおり、一例としての変換テーブル13の各エントリは、Opフィールドと、Eフィールドと、Instフィールドと、NEXTフィールドと、を含む。

【0050】

Opフィールドには、当該エントリに対応付けられたDalvikバイトコードのオペコードが格納される。

【0051】

Eフィールドには、Dalvikバイトコードのオペコードに対応づけられた1又は複数のネイティブコードのひな形が変換テーブル13又は命令テーブル14に存在するかどうかを示すフラグが格納される。本実施形態では、Eフィールドには、オペコードに対応付けられた1又は複数のネイティブコードのひな形が変換テーブル13又は命令テーブル14に存在する場合に「1」が格納され、存在しない場合に「0」が格納される。

【0052】

Instフィールドには、1命令分のネイティブコードのひな形が格納される。なお、図3では、説明をわかり易くするため自然言語を用いてネイティブコードを表現している

(図5及び図6、以下の説明においても同様)。

【0053】

NEXTフィールドには、当該ネイティブコードのひな形の次に続く命令(ネイティブコード)のひな形を格納する命令テーブルに含まれる所定のエントリへのポインタが格納される。なお、次に続く命令のひな形が存在しない場合、NEXTフィールドには、このようなポインタは格納されていない。つまり、次に続く命令のひな形が存在しない場合、当該NEXTフィールドには何も格納されていない。

【0054】

<命令テーブル14>

命令テーブル14は、例えば、SRAMにより構成される。命令テーブル14は、Dalvikバイトコードのオペコードに対応づけられた1又は複数のネイティブコードのひな形を格納する。例えば、命令テーブル14は、Dalvikバイトコードのオペコードに対応づけられた複数のネイティブコードのひな形を1つ1つのネイティブコードのひな形毎に実行される順にポインタでつないで格納する。

【0055】

図3に示されるとおり、一例としての命令テーブル14の各エントリは、1命令分のネイティブコードのひな形(図中のInstフィールド)と、当該ネイティブコードのひな形の次に続く命令のひな形を格納する命令テーブルの所定のデータへのポインタ(図中のNEXTフィールド)と、を格納する。上述の変換テーブル13と同様に、次に続く命令のひな形が存在しない場合、当該NEXTフィールドには、このようなポインタは格納されていない。

【0056】

<DRMT15>

DRMT15は、Dalvikレジスタと物理レジスタ(本実施形態では、物理レジスタ6)との対応関係を管理する。

【0057】

Dalvikバイトコードでは、すべてのDalvikレジスタのデータがメモリ上の所定の領域に存在するため、同一のDalvikレジスタに対するロード命令が頻繁に生じうる。このDRMT15は、主に、このような頻発するロード命令を削減するために用いられる。つまり、後述するように、このDRMT15により、命令作成部12は、一部のロード命令の作成を省略する。これにより、メモリアクセスが削減される。

【0058】

言い換えると、DRMT15は、不要なネイティブコードの作成を防止するため、既に行われたメモリアクセスを管理する。具体的には、DRMT15は、既に行われたメモリアクセスの管理するため、Dalvikレジスタがどの物理レジスタに対応づけられているかを示す情報を格納する。

【0059】

図4は、DRMT15の一例を示す。DRMT15は、Dalvikレジスタがどの物理レジスタに対応づけられているかを示す情報として、図4に示される各情報を格納する。DRMT15は、図4に示されるとおり、DMフィールド、Validフィールド、Dirtyフィールド、Timeフィールドを含む。

【0060】

DMフィールドには、エントリに対応するDalvikレジスタの番号が格納される。命令作成部12は、Dalvikレジスタがどの物理レジスタに対応づけられているかを示す情報をDRMT15から検索するため、当該DMフィールドに格納されたDalvikレジスタの番号を用いる。

【0061】

Validフィールドには、エントリが有効であるか否かを示すValidビットが格納される。Validビットは、当該エントリが有効であることを「1」で示し、当該エントリが無効で

あることを「0」で示す。

【0062】

Dirtyフィールドには、物理レジスタに格納されている値が、対応するDalvikレジスタ

に格納されている値よりも新しいか否かを示すDirtyビットが格納される。Dirtyビットは、物理レジスタに格納されているデータが、対応するDalvikレジスタに格納されているデータよりも新しいことを「1」で示す。また、Dirtyビットは、物理レジスタに格納され

ているデータが対応するDalvikレジスタに格納されているデータよりも新しくない(例えば、同一である)ことを「0」で示す。なお、物理レジスタに格納されているデータが、対応するDalvikレジスタに格納されているデータよりも新しいとは、Dalvikレジスタに格納されているデータが物理レジスタにロードされた後に、所定の演算処理が行われることで、物理レジスタに格納されているデータがDalvikレジスタに格納されているデータと異なった状態を指す。本実施形態では、命令作成部12が、ストア命令に関するネイティブコードの作成を省略した時に、当該ストア命令に関するDalvikレジスタと同一の番号をDMフィールドに格納するエントリの当該Dirtyフィールドに格納される値を「1」に置き換

える。

【0063】

Timeフィールドには、DMフィールドに格納された番号のDalvikレジスタに関する処理を命令作成部12が行った時刻を記録するタイムスタンプを格納する。なお、本実施形態では、当該Timeフィールドに格納される値は、その値が大きいほど新しい時間を表す。

【0064】

DRフィールドには、DMフィールドに格納された番号のDalvikレジスタに対応する物理レジスタの番号が格納される。

【0065】

命令作成部12は、このDRMT15を用いて、Dalvikレジスタと物理レジスタの対応関係を認識する。つまり、命令作成部12は、DRMT15により、物理レジスタが割り当てられているDalvikレジスタの番号を、割り当てられている物理レジスタの番号と共に認識する。

【0066】

なお、Dalvikレジスタに割り当てる物理レジスタは、例えば、オペレーティングシステムや所定のアプリケーションのために保持されておらず、自由に用いることができる物理レジスタから選ばれてもよい。

【0067】

また、Dalvikレジスタに割り当てる物理レジスタの数は任意でよい。本実施形態では、Dalvikレジスタに割り当てることができる物理レジスタの数は12個であるとする。そして、物理レジスタの番号は、0番から11番までであるとする。このため、DRMT15は12のエントリを格納する記憶部である。

【0068】

<まとめ>

変換器1は、Dalvikバイトコードから1又は複数のネイティブコードを作成する。この時、変換器1は、一部のロード命令に関するネイティブコードについては、その作成を実行しない。

【0069】

なお、バイトコードバッファ11は、本発明に係る「保持部」に相当する。また、変換テーブル13及び命令テーブル14は、本発明に係る「第1記憶部」に相当する。さらに、DRMT15は、本発明に係る「第2記憶部」に相当する。

【0070】

§3 動作例

以下、図5及び図6を用いて、本実施形態に係る変換器1の動作例を説明する。図5及び図6は、本実施形態に係る変換器1の動作例を示す。以下、Dalvikレジスタを「Mx(x

は自然数であり、Dalvikレジスタの番号を示す)」で表す。物理レジスタを「Rx(xは自

然数であり、物理レジスタの番号を示す)」で表す。仮の物理レジスタを「DRx(xは自然数であり、仮の物理レジスタの番号を示す)」で表す。仮のDalvikレジスタを「DMy(yは

自然数、但し、yは、Dalvikバイトコードのオペランドの番号)」で表す。加算命令を「add」で表す。ロード命令を「load」で表す。ストア命令を「store」で表す。ただし、こ

れらは、より具体的には、それぞれのコードにおける所定の方法で指定される。

【0071】

なお、簡単に説明するため、本動作例では、2つの連続する加算命令のDalvikバイトコードを、変換器1がネイティブコードに変換する例を示す。2つの連続する加算命令とは、1つ目が「M0, add, M1, M2」(M0 = M1 + M2)であり、2つ目が「M3, add, M2, M0」(M3 = M2 + M0)である。

【0072】

また、本動作例では、当初DRMT15には何も格納されていないものとして、当該2つの加算命令のネイティブコードが作成される処理手順の一例を説明する。図5は、命令作成部12が1つ目の加算命令「M0, add, M1, M2」のネイティブコードを作成する時の処理

手順の一例を示す。また、図6は、命令作成部12が2つ目の加算命令「M3, add, M2, M0」のネイティブコードを作成する時の処理手順の一例を示す。なお、以下ではネイティ

ブコードを1サイクルに1命令ずつ作成および出力することを想定して説明しているが、同一サイクルに複数の命令を作成および出力してもよい。

【0073】

<1つ目の加算命令>

図5に示されるとおり、まず、命令作成部12は、バイトコードバッファ11からDalvikバイトコードを1つ分取得する(S100)。当該取得したDalvikバイトコードは、加算命令「M0, add, M1, M2」である。

【0074】

次に、命令作成部12は、取得したDalvikバイトコードのオペコード(add)を参照し

て、Opフィールドに当該オペコードを格納するエントリが変換テーブル13に存在するかどうかを検索する(S101)。本実施形態では、図5に示されるとおり、エントリが検索される。なお、命令作成部12は、取得したDalvikバイトコードのオペコードに対応するエントリが変換テーブル13から検索できなかった場合、上記ステータスレジスタ3の格納する識別子をネイティブコードによる命令実行モードを示す識別子に所定の方法によって書き換えてもよい。

【0075】

次に、命令作成部12は、変換テーブル13から検索したエントリのEフィールドに格納される値を参照し、当該オペコード(add)に対応する1又は複数のネイティブコード

のひな形が変換テーブル13又は命令テーブル14に存在するかを判定する(S102)。本実施形態では、図5に示されるとおり、Eフィールドには「1」が格納されているので、オペコード(add)に対応する1又は複数のネイティブコードのひな形が変換テーブ

ル13又は命令テーブル14に存在すると判定される。

【0076】

次に、命令作成部12は、変換テーブル13から検索したエントリのInstフィールドに格納されている1命令分のネイティブコードのひな形「load DR0, DM2」(ロード命

令)を取得する(S103)。

【0077】

次に、命令作成部12は、取得したひな形である「load DR0, DM2」の仮のオペランド

の置き換えを行う(S104、S105)。ここで、「load DR0, DM2」の仮のオペラン

ドは、「DR0」と「DM2」である。

【0078】

まず、命令作成部12は、「DM2」に置き換えるオペランドを1つ目の加算命令であるDalvikバイトコード(M0, add, M1, M2)より取得する。「DM2」は、Dalvikバイトコード

の2番目のオペランドを指すため、命令作成部12は、「DM2」を、Dalvikバイトコード

の2番目のオペランドである「M1」(Dalvikレジスタの1番)に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「1」(置き換えたオペラ

ンドのDalvikレジスタの番号)を格納したエントリを検索する(S104)。

【0079】

この時点では、DRMT15には何も格納されていないので、命令作成部12は、DMフィールドに「1」(Dalvikレジスタの1番)を格納したエントリを検索することはできない。この場合、命令作成部12は、Dalvikレジスタの割り当てに用いられていない物理レジスタを所定の方法で割り当てる。例えば、本実施形態のように、命令作成部12は、Dalvikレジスタに割り当てられていない物理レジスタの中から番号の一番小さい物理レジスタを割り当てる。具体的には、命令作成部12は、「DR0」を「R0」に置き換える。これによ

り、命令作成部12は、ネイティブコード「load R0, M1」の作成を完了し、当該作成し

たネイティブコードをネイティブデコーダ4へ出力する(S105)。

【0080】

次に、命令作成部12は、作成したネイティブコード「load R0, M1」に基づいて、DRMT15にエントリを登録する(S106)。これは、当該ネイティブコード「load R0, M1」が実行されることにより、メモリアクセスが行われ、Dalvikレジスタの1番が物理レジスタの0番に割り当てられることによる。命令作成部12は、例えば、DMフィールドに「1」、Validフィールドに「1」、Dirtyフィールドに「0」、Timeフィールドに「1」、DRフィールドに「0」を格納したエントリをDRMT15に登録する。

【0081】

S104〜S106の処理により変換テーブル13から取得したひな形である「load DR0, DM2」に関する処理が完了する。

【0082】

次に、命令作成部12は、変換テーブル13から検索したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S107)。

【0083】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「load DR1, DM3」(ロード命令)の仮のオペラ

ンドの置き換えを行う(S108、S109)。ここで、「load DR1, DM3」の仮のオペ

ランドは、「DR1」と「DM3」である。

【0084】

まず、命令作成部12は、「DM3」に置き換えるオペランドを1つ目の加算命令であるDalvikバイトコード(M0 add, M1, M2)より取得する。「DM3」は、Dalvikバイトコードの3番目のオペランドを指すため、命令作成部12は、「DM3」を、Dalvikバイトコードの

3番目のオペランドである「M2」に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「2」を格納したエントリを検索する(S108)。

【0085】

この時点では、DRMT15には、DMフィールドに「1」を格納したエントリしか登録されていないので、上記と同様、命令作成部12は、DMフィールドに「2」を格納したエントリを検索することはできない。この場合、命令作成部12は、「DR1」を「R1」に置き換

える。これにより、命令作成部12は、ネイティブコード「load R1, M2」の作成を完了

し、当該作成したネイティブコードをネイティブデコーダ4へ出力する(S109)。

【0086】

次に、命令作成部12は、作成したネイティブコード「load R1, M2」に基づいて、DRMT15にエントリ登録をする(S110)。これは、当該ネイティブコード「load R1, M2」が実行されることにより、メモリアクセスが行われ、Dalvikレジスタの2番が物理レジスタの1番に割り当てられることによる。命令作成部12は、例えば、DMフィールドに「2」、Validフィールドに「1」、Dirtyフィールドに「0」、Timeフィールドに「2」、DRフィールドに「1」を格納したエントリをDRMT15に登録する。

【0087】

S108〜S110の処理により命令テーブル14から取得したひな形である「load D

R1, DM3」に関する処理が完了する。

【0088】

次に、命令作成部12は、S107で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S111)。

【0089】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「add DR2, DR0, DR1」(加算命令)の仮のオペ

ランドの置き換えを行う(S112、S113)。ここで、「add DR2, DR0, DR1」の仮

のオペランドは、「DR2」、「DR0」、「DR1」である。また、当該エントリのInstフ

ィールドには、Dalvikバイトコードの先頭のオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令であることを示すデータフラグが存在する(不図示)。

【0090】

命令作成部12は、当該データフラグの存在により、まずはDalvikバイトコードの先頭のオペランド「M0」を取得する。そして、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「0」を格納したエントリを検索する(S112)。これは、当該命令が、Dalvikバイトコードの先頭のオペランド(M0)に物理レジスタ(「DR2」に置き換

えられる物理レジスタ)を割り当てる命令であることによる。したがって、命令作成部12は、DRMT15のDMフィールドに「0」を格納したエントリを検索することにより、Dalvikレジスタ「M0」にすでに割り当てられた物理レジスタが存在するか否かを判定する。

【0091】

この時点では、DRMT15には、DMフィールドに「0」を格納したエントリは登録されていないので、上記と同様、命令作成部12は、DMフィールドに「0」を格納したエントリを検索することはできない。この場合、Dalvikレジスタ「M0」にすでに割り当てられた物理レジスタが存在しないので、仮のオペランド「DR2」を適当な物理レジスタの番号に置

き換える。この場合、命令作成部12は、「DR2」を「R2」に置き換える。なお、DRMT1

5からエントリが検索された場合、命令作成部12は、「DR2」を、検索されたエントリ

のDRフィールドに格納された物理レジスタの番号に置き換える。

【0092】

また、命令作成部12は、例えば、同一バイトコード内の別のネイティブコードと共通の番号が割り当てられている仮の物理レジスタを、当該別のネイティブコードにおいて割り当てた物理レジスタにより置き換える。つまり、命令作成部12は、「DR0」を「R0」

(1番目のネイティブコードのひな形を参照)と置き換え、「DR1」を「R1」(2番目の

ネイティブコードのひな形を参照)と置き換える。これにより、命令作成部12は、ネイティブコード「add R2, R0, R1」の作成を完了し、当該完成したネイティブコードをネイティブデコーダ4へ出力する(S113)。なお、これらの仮の物理レジスタと物理レジスタとの対応関係(上記の「DR0」と「R0」との対応関係、および、「DR1」と「R1」との対応関係)は命令作成部12内のテーブル(不図示)によって管理される。

【0093】

次に、命令作成部12は、作成したネイティブコード「add R2, R0, R1」に基づいて、DRMT15にエントリ登録をする(S114)。当該命令は、上述のとおり、Dalvikバイトコードの先頭のオペランド(M0)に物理レジスタ(R2)を割り当てる命令であることによる。命令作成部12は、例えば、DMフィールドに「0」、Validフィールドに「1」、Dirtyフィールドに「1」、Timeフィールドに「3」、DRフィールドに「2」を格納したエントリをDRMT15に登録する。なお、上述までのエントリと異なりDirtyフィールドに「1

」を格納する理由は、この時点において、当該add命令によりR2(物理レジスタ)に格納

されるデータがDalvikレジスタ(M0)にストアされていないからである。つまり、Dalvikレジスタ(M0)よりも、当該Dalvikレジスタ(M0)に割り当てられた物理レジスタ(R2)の方が新しいデータを格納しているからである。

【0094】

S112〜S114の処理により命令テーブル14から取得したひな形である「add DR2, DR0, DR1」に関する処理が完了する。

【0095】

次に、命令作成部12は、S111で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S115)。

【0096】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「store DR2, DM1」(ストア命令)の仮のオペランドの置き換えを行う。ここで、「store DR2, DM1」の仮のオペランドは、「DR2」と「DM1」である。ただし、当該ネイティブコードのひな形は、Dalvikレジスタに対するストア命令に関するネイティブコードのひな形であるため、ネイティブコードの作成は省略される。

【0097】

この時、命令作成部12は、ネイティブコードの作成については実行しないが、「DM1

」に置き換えるはずであったオペランドを1つ目の加算命令であるDalvikバイトコード(M0 add, M1, M2)より取得する。「DM1」は、Dalvikバイトコードの1番目のオペランド

を指すため、命令作成部12は、「DM1」に置き換えるはずであったオペランドとして、

「M0」(Dalvikレジスタの0番)を取得する。そして、命令作成部12は、当該Dalvikレジスタの番号「0」をDMフィールドに格納したエントリを検索する(S116)。図5に示されるとおり、DMフィールドに「0」を格納したエントリが検索される。命令作成部12は、検索したエントリのDirtyフィールドに格納された値を「1」に置き換える。なお

、この時点においてすでに当該エントリのDirtyフィールドに格納された値は「1」であ

るため、命令作成部12は、当該処理を省略してもよい。

【0098】

以上までのS100〜S116の処理により、命令作成部12は、1つ目の加算命令「M0, add, M1, M2」のネイティブコードの作成を完了する。具体的に、命令作成部12は

、1つ目の加算命令「M0, add, M1, M2」に対して、「load R0, M1」、「load R1, M2」

、「add R2, R0, R1」の3つのネイティブコードを作成する。

【0099】

<2つ目の加算命令>

次に、図6を用いて、2つ目の加算命令「M3, add, M2, M0」(M3 = M2 + M0)のネイ

ティブコードを作成するときの処理手順について説明する。

【0100】

図6に示されるとおり、まず、命令作成部12は、バイトコードバッファ11からDalvikバイトコードを1つ分取得する(S200)。当該取得したDalvikバイトコードは、加算命令「M3, add, M2, M0」である。

【0101】

次に、命令作成部12は、取得したDalvikバイトコードのオペコード(add)を参照し

て、変換テーブル3のOpフィールドに当該オペコードを格納するエントリが変換テーブル13に存在するかどうかを検索する(S201)。本実施形態では、図6に示されるとおり、エントリが検索される。

【0102】

次に、命令作成部12は、変換テーブル13から検索したエントリのEフィールドに格納される値を参照し、当該オペコード(add)に対応する1又は複数のネイティブコード

のひな形が変換テーブル13又は命令テーブル14に存在するかを判定する(S202)。本実施形態では、図6に示されるとおり、Eフィールドには「1」が格納されているので、オペコード(add)に対応する1又は複数のネイティブコードのひな形が変換テーブ

ル13又は命令テーブル14に存在すると判定される。

【0103】

次に、命令作成部12は、変換テーブル13から検索したエントリのInstフィールドに格納されている1命令分のネイティブコードのひな形「load DR0, DM2」(ロード命

令)を取得する(S203)。

【0104】

次に、命令作成部12は、取得したひな形である「load DR0, DM2」の仮のオペランド

の置き換えを行う。ここで、「load DR0, DM2」の仮のオペランドは、「DR0」と「DM2」

である。

【0105】

まず、命令作成部12は、「DM2」に置き換えるオペランドを2つ目の加算命令であるDalvikバイトコード(M3, add, M2, M0)より取得する。「DM2」は、Dalvikバイトコード

の2番目のオペランドを指すため、命令作成部12は、「DM2」を、Dalvikバイトコード

の2番目のオペランドである「M2」(Dalvikレジスタの2番)に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「2」(置き換えたオペランドのDalvikレジスタの番号)を格納したエントリを検索する(S204)。

【0106】

この時点において、DRMT15にはDMフィールドに「2」(Dalvikレジスタの2番)を格納したエントリが検索される。したがって、この時、命令作成部12は、当該ロード命令のネイティブコードの作成は省略される。つまり、命令作成部12は、仮のオペランドの置き換えを実行せず、ネイティブコードの作成を実行しない。この時点で、「load DR0, DM2」に関する処理が完了する。

【0107】

次に、命令作成部12は、変換テーブル13から検索したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S205)。

【0108】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「load DR1, DM3」(ロード命令)の仮のオペラ

ンドの置き換えを行う。ここで、「load DR1, DM3」の仮のオペランドは、「DR1」と「DM3」である。

【0109】

まず、命令作成部12は、「DM3」に置き換えるオペランドを2つ目の加算命令であるDalvikバイトコード「M3, add, M2, M0」より取得する。「DM3」は、Dalvikバイトコード

の3番目のオペランドを指すため、命令作成部12は、「DM3」を、Dalvikバイトコード

の3番目のオペランドである「M0」に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「0」を格納したエントリを検索する(S206)。

【0110】

この時点において、DRMT15にはDMフィールドに「0」(Dalvikレジスタの0番)を格納したエントリが検索される。したがって、この時、命令作成部12は、当該ロード命令のネイティブコードの作成は省略される。つまり、命令作成部12は、仮のオペランドの置き換えを実行せず、ネイティブコードの作成を実行しない。この時点で、「load DR1, DM3」に関する処理が完了する。

【0111】

次に、命令作成部12は、S205で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S207)。

【0112】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「add DR2, DR0, DR1」(加算命令)の仮のオペ

ランドの置き換えを行う。ここで、「add DR2, DR0, DR1」の仮のオペランドは、「DR2」、「DR0」、「DR1」である。また、当該エントリのInstフィールドには、Dalvikバイ

トコードの先頭のオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令であることを示すデータフラグが存在する(不図示)。

【0113】

命令作成部12は、当該データフラグの存在により、まずはDalvikバイトコードの先頭のオペランド「M3」を取得する。そして、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「3」を格納したエントリを検索する(S208)。以上のS112と同様の処理である。

【0114】

この時点では、DRMT15には、DMフィールドに「3」を格納したエントリは登録されていないので、上記と同様、命令作成部12は、DMフィールドに「3」を格納したエントリを検索することはできない。この場合、Dalvikレジスタ「M3」にすでに割り当てられた物理レジスタが存在しないので、仮のオペランド「DR2」を適当な物理レジスタの番号に置

き換える。この場合、命令作成部12は、「DR2」を「R3」に置き換える。

【0115】

また、命令作成部12は、例えば、同一バイトコード内の別のネイティブコードと共通の番号が割り当てられている仮の物理レジスタを、当該別のネイティブコードにおいて割り当てた物理レジスタにより置き換える。つまり、命令作成部12は、「DR0」を「R1」

(1番目のネイティブコードのひな形を参照)と置き換え、「DR1」を「R2」(2番目の

ネイティブコードのひな形を参照)と置き換える。なお、1番目及び2番目のネイティブコードは作成されていない。命令作成部12は、これらをDRMT15から取得する。命令作成部12は、1番目のネイティブコードのひな形「load DR0, DM2」に対する処理(S2

04)の際、検索されたエントリ(DMフィールドに「2」を格納したエントリ)のDRフィールドから「1」を取得する。これにより、命令作成部12は、「DR0」と置き換える物

理レジスタの番号を取得する。また、命令作成部12は、2番目のネイティブコードのひな形「load DR1, DM3」に対する処理(S206)の際、検索されたエントリ(DMフィー

ルドに「0」を格納したエントリ)のDRフィールドから「2」を取得する。これにより、命令作成部12は、「DR1」と置き換える物理レジスタの番号を取得する。なお、これら

の仮の物理レジスタ「DRx」と物理レジスタ「Rx」との対応関係は、命令作成部12内に

存在するテーブル(不図示)によって管理されている。

【0116】

これにより、命令作成部12は、ネイティブコード「add R3, R1, R2」の作成を完了し、当該完成したネイティブコードをネイティブデコーダ4へ出力する(S209)。

【0117】

次に、命令作成部12は、作成したネイティブコード「add R3, R1, R2」に基づいて、DRMT15にエントリを登録する(S210)。当該命令は、上述のとおり、Dalvikバイトコードの先頭のオペランド(M3)に物理レジスタ(R3)を割り当てる命令であることによる。命令作成部12は、例えば、DMフィールドに「3」、Validフィールドに「1」、Dirtyフィールドに「1」、Timeフィールドに「4」、DRフィールドに「3」を格納したエントリをDRMT15に登録する。この時点で「add DR2, DR0, DR1」に関する処理が完了する

。

【0118】

次に、命令作成部12は、S207で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S211)。

【0119】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「store DR2, DM1」の仮のオペランドの置き換えを行う。ここで、「store DR2, DM1」の仮のオペランドは、「DR2」と「DM1」である。ただし、当該ネイティブコードのひな形は、Dalvikレジスタに関するストア命令に関するネイティブコードのひな形であるため、ネイティブコードの作成は省略される。

【0120】

この時、命令作成部12は、ネイティブコードの作成については実行しないが、「DM1

」に置き換えるはずであったオペランドを2つ目の加算命令であるDalvikバイトコード「M3, add, M2, M0」より取得する。「DM1」は、Dalvikバイトコードの1番目のオペランドを指すため、命令作成部12は、「DM1」に置き換えるはずであったオペランドとして、

「M3」(Dalvikレジスタの3番)を取得する。そして、命令作成部12は、当該Dalvikレジスタの番号「3」をDMフィールドに格納したエントリを検索する(S212)。図6に示されるとおり、DMフィールドに「3」を格納したエントリが検索される。命令作成部12は、検索したエントリのDirtyフィールドに格納された値を「1」に置き換える。なお

、この時点においてすでに当該エントリのDirtyフィールドに格納された値は「1」であ

るため、命令作成部12は、当該処理を省略してもよい。

【0121】

以上までのS200〜S212の処理により、命令作成部12は、2つ目の加算命令「M3, add, M2, M0」のネイティブコードの作成を完了する。具体的に、命令作成部12は

、2つ目の加算命令「M3, add, M2, M0」に対して、「add DR2, DR0, DR1」の1つのネイティブコードを作成する。

【0122】

<その他>

以上のようにして、命令作成部12は、Dalvikバイトコードからネイティブコードを作成する。また、以上のようにして、DRMT15にエントリが追加されていく。このように追加されるエントリについて、命令作成部12は、所定のタイミングでエントリの削除を行う。所定のタイミングとは、例えば、DRMT15のエントリが一杯で命令作成部12によるエントリの追加が出来ない時である。この時、命令作成部12は、DRMT15から所定のエントリを削除し、当該エントリの追加を実行する。また、所定のタイミングの他の例として、バイトコードによる命令実行モードからネイティブコードによる命令実行モードに遷移する時が挙げられる。この時、命令作成部12はDRMT15の全エントリを削除する。

【0123】

なお、所定のエントリとは、例えば、登録されてから一番時間が経っているエントリである。命令作成部12は、このようなエントリをTimeフィールドに格納されている時刻から判断する。またその他の例として、所定のエントリとは、例えば、命令作成部12がランダムに選択したエントリである。

【0124】

また、命令作成部12が削除するエントリの数は任意でよい。例えば、命令作成部12は、DRMT15のエントリを削除する時、一度に3つのエントリを削除してもよい。

【0125】

なお、このようなDRMT15のエントリを削除する時、命令作成部12は、削除する対象のエントリのDirtyフィールドの値(Dirtyビット)を確認する。

【0126】

削除する対象のエントリのDirtyフィールドに「0」が格納されている場合、当該エン

トリに含まれた番号の物理レジスタに格納されているデータは、当該エントリに含まれた番号のDalvikレジスタに格納されているデータと同一である。すなわち、対応関係にあるDalvikレジスタと物理レジスタとは同一のデータを格納しているため、物理レジスタに格納されているデータをDalvikレジスタにストアする必要はない。したがって、この時、命令作成部12は、何らネイティブコードを作成しない。

【0127】

他方、削除するエントリのDirtyフィールドに「1」が格納されている場合、当該エン

トリに含まれた番号の物理レジスタに格納されているデータは、更新されているため、当該エントリに含まれた番号のDalvikレジスタに格納されているデータと異なる。すなわち、対応関係にあるDalvikレジスタと物理レジスタとは異なるデータを格納しているため、物理レジスタに格納されているデータをDalvikレジスタにストアする必要がある。命令作

成部12は、当該物理レジスタに格納されるデータを当該Dalvikレジスタにストアする命令に関するネイティブコードを作成する。例えば、命令作成部12は、命令テーブル14等に格納されたストア命令に関するネイティブコードのひな形を取得する。そして、命令作成部12は、当該取得したネイティブコードのひな形に含まれた仮のオペランドを、当該削除する対象のエントリに含まれたDMフィールド及びDRフィールドに格納されている値で置き換える。このようにして、命令作成部12は、削除する対象のエントリに含まれた番号の物理レジスタとDalvikレジスタとに関するストア命令のネイティブコードを作成する。これにより、物理レジスタに格納されている新しいデータがDalvikレジスタ(メモリ)に格納される前に、当該新しいデータを格納する物理レジスタに別のDalvikレジスタが割り当てられることを防ぐことができる。

【0128】

§4 実施の形態に係る作用及び効果

以上によれば、本実施形態に係る変換器は、Dalvikバイトコードに対応するネイティブコードを作成する。この時、命令作成部12は、DRMT15を参照して、一部のロード命令のネイティブコードの作成を省略する。また、命令作成部12は、DRMT15からエントリを削除する時にのみDalvikレジスタに対するストア命令のネイティブコードの作成を行い、それ以外の時はDalvikレジスタに対するストア命令のネイティブコードの作成を省略する。これにより、本実施形態に係る変換器によれば、ロード命令及びストア命令の発行を抑えることができ、メモリアクセスを削減することができる。

【0129】

§5 補足

以上、本発明の実施の形態を詳細に説明してきたが、前述までの説明はあらゆる点において本発明の例示に過ぎず、その範囲を限定しようとするものではない。本発明の範囲を逸脱することなく種々の改良や変形を行うことができることは言うまでもない。本発明は、特許請求の範囲によってのみその範囲が解釈される。また、当業者は、上記本実施形態の記載から、特許請求の範囲の記載および技術常識に基づいて等価な範囲を実施することができる。また、本明細書において使用される用語は、特に言及しない限り、当該分野で通常用いられる意味で用いられる。したがって、他に定義されない限り、本明細書中で使用される全ての専門用語および技術用語は、本発明の属する分野の当業者によって一般的に理解される意味と同じ意味を有する。両者が矛盾する場合、本明細書において使用される用語は、本明細書(定義を含めて)に記載された意味において理解される。

【符号の説明】

【0130】

1 変換器

2 フェッチャ

3 ステータスレジスタ

4 ネイティブデコーダ

5 演算装置

6 物理レジスタ

7 メモリ

11 バイトコードバッファ

12 命令作成部

13 変換テーブル

14 命令テーブル

15 DRMT(Dalvik Register Map Table)

100 プロセッサ

【技術分野】

【0001】

本発明は、レジスタ形式のバイトコードをネイティブコードに変換する変換器及び変換方法の技術に関する。

【背景技術】

【0002】

近年、Google(登録商標)社の携帯情報端末向けプラットフォームAndroid(登録商標

)を搭載した携帯電話が急速に普及している。このような携帯電話で実行されるアプリケーションは、ポータビリティを高めるため、通常は、Java(登録商標)などの特定のコンピュータ及びオペレーティングシステムに依存しないプログラム言語により作成される。当該プログラム言語では、すべてのプログラムは一度、中間言語であるバイトコードにコンパイルされる。Androidで採用されているバイトコードは、Javaバイトコードなどとは

異なり、メモリ上に存在するレジスタ(領域)を直接指定して演算を行う、という特徴をもつ。このようなバイトコードは、レジスタ形式のバイトコードと呼ばれている。

【0003】

バイトコードは、特定のコンピュータ及びオペレーティングシステムに依存しないため、それを解釈及び実行できる環境があれば、任意のプロセッサ上で実行される。通常、VM(Virtual Machine)が、バイトコードを逐次解釈し、実行する。

【0004】

このようなバイトコードの実行は、VMを介して行われるため、機械語で表されたネイティブコード(オブジェクトプログラムまたはオブジェクトコードとも呼ばれる)の実行と比べて遅い。そのため、バイトコードの実行を高速化する様々な手法がこれまでに提案されてきた。当該手法を開示する文献として、以下の非特許文献1が挙げられる。

【0005】

非特許文献1には、例えば、プロセッサの一部に、Javaバイトコードをネイティブコードに変換できるハードウェア(アクセラレータ)を追加することにより、バイトコードの実行を高速化する手法が開示されている。このようなアクセラレータが追加されることにより、バイトコードはネイティブコードに変換されるため、プロセッサは、VM等のソフトウェアを介さず、直接バイトコードを解釈及び実行することができるようになる。これによって、VM等のソフトウェアを介することによるオーバヘッドが削減される。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】“ARMアーキテクチャリファレンスマニュアル”、[online]、アーム株式会社、[平成22年10月15日検索]、インターネット〈URL:https://www.jp.arm.com/document/manual/files/051020DDI0100HJ_v6_1.pdf〉

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記非特許文献1において開示される技術により単純に実装されたアクセラレータは、レジスタ形式のバイトコードの場合、バイトコードの各オペランドがメモリ上に存在するため、多数のストア命令及びロード命令に関するネイティブコードを発行してしまう。そのため、メモリアクセスの効率が悪い。

【0008】

本発明は、このような点を考慮してなされたものであり、メモリアクセスを削減する変換器及び変換方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明は、上述した課題を解決するために、以下の構成を採用する。

【0010】

すなわち、本発明の変換器は、メモリからフェッチしたレジスタ形式のバイトコードを保持する保持部と、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部と、保持部に保持されているバイトコードを取り出し、第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成する命令作成部と、物理レジスタの番号と、命令作成部が作成したネイティブコードにより当該番号の物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタの番号との対応関係を示すデータを格納する第2記憶部と、を備え、命令作成部は、作成するネイティブコードが、第2記憶部に格納されたメモリ上のレジスタの番号によって特定されるアドレスに関するロード命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする。

【0011】

上記構成によれば、命令作成部は、第2記憶部に格納されたメモリ上のレジスタの番号によって特定されるアドレスに関するロード命令に関するネイティブコードの作成を省略する。したがって、上記構成によれば、一部のロード命令に関するネイティブコードの発行が省かれるため、メモリアクセスを削減することができる。

【0012】

また、上記命令作成部は、ネイティブコードを作成する際に必要な物理レジスタの番号を、第2記憶部に格納されたデータに含まれる物理レジスタの番号を用いて特定してもよい。

【0013】

また、上記命令作成部は、作成するネイティブコードがメモリ上のレジスタに関するストア命令であると判定した場合、当該ネイティブコードの作成を省略してもよい。

【0014】

上記構成によれば、命令作成部は、メモリ上のレジスタに関するストア命令に関するネイティブコードの作成を省略する。したがって、上記構成によれば、一部のストア命令に関するネイティブコードの発行が省かれるため、メモリアクセスを削減することができる。

【0015】

また、上記命令作成部は、物理レジスタを割り当てるネイティブコードのひな形を第1記憶部から取得した時、バイトコードに含まれるメモリ上のレジスタの番号と、当該アドレスに割り当てる物理レジスタの番号との対応関係を示すデータを作成し、当該データを第2記憶部に格納してもよい。

【0016】

上記構成によれば、命令作成部により作成されるネイティブコードにより対応付けられる物理レジスタとメモリ上のレジスタの番号との対応関係が第2記憶部に格納される。つまり、第2記憶部は、ネイティブコードの実行状態に対応した、メモリ上のレジスタの番号と物理レジスタの番号との対応関係を示すデータが格納される。これにより、命令作成部は、ネイティブコードの実行状態に対応して、ロード命令に関するネイティブコードの作成を省略することができる。

【0017】

また、上記命令作成部は、所定の時点において、第2記憶部に格納されているデータを削除し、当該削除するデータに含まれる番号の物理レジスタに格納されたデータを、当該削除するデータに含まれるメモリ上のレジスタの番号によって特定されるアドレスに書き込むストア命令のネイティブコードを作成してもよい。

【0018】

上記構成によれば、メモリ上のレジスタの番号と物理レジスタの番号との対応関係を示すデータが削除される時に、物理レジスタに格納されたデータを、対応するメモリ上のレジスタの番号によって特定されるアドレスにストアすることができる。

【0019】

また、本発明の変換方法は、メモリからフェッチしたレジスタ形式のバイトコードを保持するステップと、保持したバイトコードを取り出し、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成するネイティブコード作成ステップと、物理レジスタの番号と、ネイティブコード作成ステップにより作成されたネイティブコードにより当該番号の物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタの番号との対応関係を示すデータを第2記憶部に格納する記憶ステップと、を含み、ネイティブコード作成ステップでは、作成するネイティブコードが、第2記憶部に格納されたメモリ上のレジスタの番号に関するロード命令であると判定される場合、当該ネイティブコードの作成が省略されることを特徴とする。

【0020】

なお、本発明の別態様として、FPGA(Field-Programmable Gate Array)に読み込ませ

ることにより以上の各構成を実現するプログラムであってもよい。

【発明の効果】

【0021】

本発明によれば、メモリアクセスを削減する変換器及び変換方法を提供することができる。

【図面の簡単な説明】

【0022】

【図1】実施の形態に係る変換器を含むプロセッサの構成を例示する図

【図2】実施の形態に係る変換器の構成を例示する図

【図3】変換テーブルと命令テーブルの一例を示す図

【図4】DRMTの一例を示す図

【図5】1つ目の加算命令に関するバイトコードの変換例を示す図

【図6】2つ目の加算命令に関するバイトコードの変換例を示す図

【発明を実施するための形態】

【0023】

以下、本発明の一側面に係る変換器及び変換方法を、実施の形態(以下、「本実施形態」とも表記する)として説明する。ただし、以下に挙げる実施形態は例示であり、本発明は以下の実施形態の構成に限定されない。

【0024】

本実施形態の変換器を含むプロセッサは、その一例としてMIPSプロセッサである。そして、本実施形態の変換器は、レジスタ形式のバイトコードの一例としてDalvikバイトコードを、MIPS命令セットに対応したネイティブコードに変換する。Dalvikバイトコードとは、Androidにおいて用いられているJavaの実行モデルで採用されている命令セットである

。

【0025】

なお、MIPS命令セットに対応したネイティブコードの命令長は32ビットである。これに対して、Dalvikバイトコードの命令長は、可変長であり、最長80ビットである。また、Dalvikバイトコードでは、各命令は、Dalvikレジスタに対して演算処理を行う。ここで、Dalvikレジスタは、物理レジスタを指すものではなく、メモリ上に割り当てられた領域を指す。そして、当該領域のアドレスは、ベースアドレスと当該Dalvikレジスタの番号とによって特定される。Dalvikバイトコードにおける各命令では、0〜3個のDalvikレジスタをオペランドとして、これらの値を用いた演算が実施される。

【0026】

§1 プロセッサの構成例

まず、本実施形態に係る変換器を含むプロセッサの構成例について説明する。図1は、本実施形態に係る変換器を含むプロセッサを例示する。図1に示されるとおり、本実施形

態に係る変換器1を含むプロセッサ100は、変換器1、フェッチャ2、ステータスレジスタ3、ネイティブデコーダ4、演算装置5、及び物理レジスタ6を備える。

【0027】

フェッチャ2は、メモリ7に格納されたDalvikバイトコードまたはネイティブコードをフェッチする(読み出す)。フェッチしたDalvikバイトコードは、変換器1によってネイティブコードに変換される。そして、変換器1によって変換された又はフェッチャ2が出力したネイティブコードは、ネイティブデコーダ4に入力される。

【0028】

変換器1は、フェッチャ2がフェッチしたDalvikバイトコードをネイティブコードに変換する。詳細は「§2 変換器の構成例」に後述する。

【0029】

ステータスレジスタ3は、Dalvikバイトコードによる命令実行モードか、ネイティブコードによる命令実行モードかを特定する識別子を格納する。このステータスレジスタ3により、上述したネイティブデコーダ4に入力されるネイティブコードの入力元が特定される。ステータスレジスタ3は、例えば、ネイティブコードによる命令実行モードにおいて、演算装置5が行う所定の演算処理により、その格納する識別子をDalvikバイトコードによる命令実行モードを示す識別子に書き換えられる。また、ステータスレジスタ3は、例えば、Dalvikバイトコードによる命令実行モードにおいて、変換器1が、フェッチャ2がフェッチしたバイトコードをネイティブコードに変換できなかった時、その格納する識別子をネイティブコードによる命令実行モードを示す識別子に所定の方法によって書き換えられる。このようにステータスレジスタ3の格納する値が書き換えられることにより、ネイティブデコーダ4にネイティブコードを入力する入力元が切り替えられる。

【0030】

ネイティブデコーダ4は、フェッチャ2または変換器1により入力されるネイティブコードをデコードする。

【0031】

演算装置5及び物理レジスタ6は、ネイティブデコーダ4のデコード結果に基づいて、所定の演算処理を行う。

【0032】

なお、これらの構成は、例えば、不図示の制御装置によって制御される。

【0033】

§2 変換器の構成例

次に、本実施形態に係る変換器1の構成例について説明する。図2は、本実施形態に係る変換器1の構成例を示す。

【0034】

変換器1は、図2に示されるとおり、そのハードウェア構成として、バイトコードバッファ11、命令作成部12、変換テーブル13、命令テーブル14、Dalvik Register Map Table(以下、「DRMT」と表記する)15、を有している。

【0035】

<バイトコードバッファ11>

バイトコードバッファ11は、フェッチャ2がフェッチして出力するDalvikバイトコードを保持する。これにより、後述する命令作成部12は、Dalvikバイトコードを1つ取り出すことが可能となる。

【0036】

具体的に説明すると、MIPS命令セットに対応したネイティブコードの命令長は32ビットであるため、フェッチャ2がメモリ7からフェッチするデータ長は32ビットである。これに対して、Dalvikバイトコードの命令長は、可変長であり、最長80ビットである。したがって、フェッチャ2は、1回のフェッチでDalvikバイトコードを1つ取り出すことができない場合がある。このため、1つのDalvikバイトコードをメモリ7から取り出すためには、フェッチャ2は複数回にわたりデータをフェッチする必要がある。バイトコード

バッファ11は、主に、このようなデータを保持するために用いられる。つまり、バイトコードバッファ11は、フェッチャ2が複数回にわたりメモリ7からフェッチしたデータを保持する。これにより、後述する命令作成部12は、当該バイトコードバッファ11に保持されたデータからDalvikバイトコードを1つ取り出すことが可能となる。

【0037】

なお、このような命令作成部12の処理を可能にするため、バイトコードバッファ11は、少なくともDalvikバイトコードの最長の命令長である80ビットのデータを保持する。

【0038】

<命令作成部12>

命令作成部12は、1つのDalvikバイトコードを、対応する1又は複数のネイティブコード(本実施形態では、MIPS命令列)へと変換する。

【0039】

具体的には、命令作成部12は、変換テーブル13、及び命令テーブル14から読み出された1または複数のネイティブコードのひな形(MIPS命令列のひな形)と、Dalvikバイトコードから得られたオペランドにより、ネイティブコードを作成し、後続するユニット(本実施形態では、ネイティブデコーダ4)へ出力する。ネイティブコードのひな形は、ネイティブコードのオペコード(命令コード)と、仮のオペランドとを有する。命令作成部12は、このネイティブコードのひな形に含まれる仮のオペランドを、バイトコードから得られたオペランド等を用いて所定のオペランドに置き換えることにより、ネイティブコードを作成する。これにより、命令作成部12は、1つのDalvikバイトコードを、対応する1又は複数のネイティブコード(本実施形態では、MIPS命令列)へと変換する。

【0040】

また、命令作成部12は、当該ネイティブコードの作成の際、DRMT15を参照することにより、一部のロード命令に関するネイティブコードの発行を停止する。言い換えると、命令作成部12は、DRMT15を参照することにより、一部のロード命令に関するネイティブコードの作成を省略する。具体的な処理については後述する。

【0041】

また、命令作成部12は、作成したネイティブコードが物理レジスタをDalvikレジスタに割り当てる命令である場合、当該Dalvikレジスタと物理レジスタの対応関係を示すデータ、具体的にはDalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)をDRMT15に登録する。具体的な処理については後述する。

【0042】

なお、物理レジスタをDalvikレジスタに割り当てる命令として、本実施形態では2つの命令が考えられる。

【0043】

1つ目の命令は、Dalvikレジスタをロードする命令である。当該命令が実行されると、メモリ上のあるアドレスに格納されているデータ(本実施形態では、Dalvikレジスタに格納されているデータ)が、物理レジスタにロードされる。つまり、物理レジスタがDalvikレジスタに割り当てられる。命令作成部12は、このような命令のネイティブコードのひな形を取得した時、Dalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)をDRMT15に登録する。

【0044】

2つ目の命令は、Dalvikバイトコードのデスティネーションオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令である。デスティネーションオペランドとは、そのバイトコードによる演算結果を格納するオペランドであり、Dalvikバイトコードの場合は先頭のオペランドがこれに該当する。このような命令も、上記ロード命令と同様に、物理レジスタがDalvikレジスタに割り当てられる。命令作成部12は、このような命令のネイティブコードのひな形を取得した時、Dalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)をDRMT15に登録する。なお、このような命令であることは、

変換テーブル13及び命令テーブル14のネイティブコードのひな形を格納するフィールド(後述する、Instフィールド)のデータフラグにより示される。命令作成部12は、このデータフラグにより、変換テーブル13又は命令テーブル14から取得したネイティブコードのひな形が、Dalvikバイトコードの先頭のオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令であることを認識する。

【0045】

また、命令作成部12は、変換テーブル13又は命令テーブル14から取得したネイティブコードのひな形がストア命令に関するひな形であって、Dalvikレジスタに対するストア命令のひな形である場合、当該ストア命令のネイティブコードの作成を省略する。つまり、命令作成部12は、Dalvikレジスタに対するストア命令に関するネイティブコードのひな形に対して、オペランドの置き換えを行わず、ネイティブコードの作成をしない。これにより、メモリアクセスが削減される。

【0046】

なお、本実施形態では、命令作成部12は、特定の時にDalvikレジスタに対するストア命令に関するネイティブコードを作成する。特定の時とは、後述するDRMT15がDalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)を削除する時である。命令作成部12は、後述するDRMT15がDalvikレジスタの番号と物理レジスタの番号とを保持するデータ(エントリ)を削除する時、当該物理レジスタに格納されるデータを当該Dalvikレジスタにストアする命令に関するネイティブコードを作成する。

【0047】

<変換テーブル13>

変換テーブル13は、例えば、SRAM(Static Random Access Memory)により構成され

る。変換テーブル13は、Dalvikバイトコードのオペコードに対応付けられたネイティブコードのひな形を格納する命令テーブル14へのポインタを格納する。また、変換テーブル13は、Dalvikバイトコードのオペコードに対応づけられた1又は複数のネイティブコードのひな形が変換テーブル13又は命令テーブル14に存在するかどうかを示すフラグを格納する。言い換えると、変換テーブル13は、Dalvikバイトコードをネイティブコードに変換可能かどうかを示すフラグを格納する。

【0048】

ここで、変換テーブル13は、命令作成部12が命令テーブル14を参照してネイティブコードを作成する際のレイテンシの増加を抑えるため、命令テーブル14上の上記対応する1又は複数のネイティブコードのひな形の一部(例えば、数命令分のネイティブコードのひな形)を格納していてもよい。本実施形態では、1命令分のネイティブコードを格納している。

【0049】

図3は、変換テーブル13及び後述する命令テーブル14の一例を示す。図3に示されるとおり、一例としての変換テーブル13の各エントリは、Opフィールドと、Eフィールドと、Instフィールドと、NEXTフィールドと、を含む。

【0050】

Opフィールドには、当該エントリに対応付けられたDalvikバイトコードのオペコードが格納される。

【0051】

Eフィールドには、Dalvikバイトコードのオペコードに対応づけられた1又は複数のネイティブコードのひな形が変換テーブル13又は命令テーブル14に存在するかどうかを示すフラグが格納される。本実施形態では、Eフィールドには、オペコードに対応付けられた1又は複数のネイティブコードのひな形が変換テーブル13又は命令テーブル14に存在する場合に「1」が格納され、存在しない場合に「0」が格納される。

【0052】

Instフィールドには、1命令分のネイティブコードのひな形が格納される。なお、図3では、説明をわかり易くするため自然言語を用いてネイティブコードを表現している

(図5及び図6、以下の説明においても同様)。

【0053】

NEXTフィールドには、当該ネイティブコードのひな形の次に続く命令(ネイティブコード)のひな形を格納する命令テーブルに含まれる所定のエントリへのポインタが格納される。なお、次に続く命令のひな形が存在しない場合、NEXTフィールドには、このようなポインタは格納されていない。つまり、次に続く命令のひな形が存在しない場合、当該NEXTフィールドには何も格納されていない。

【0054】

<命令テーブル14>

命令テーブル14は、例えば、SRAMにより構成される。命令テーブル14は、Dalvikバイトコードのオペコードに対応づけられた1又は複数のネイティブコードのひな形を格納する。例えば、命令テーブル14は、Dalvikバイトコードのオペコードに対応づけられた複数のネイティブコードのひな形を1つ1つのネイティブコードのひな形毎に実行される順にポインタでつないで格納する。

【0055】

図3に示されるとおり、一例としての命令テーブル14の各エントリは、1命令分のネイティブコードのひな形(図中のInstフィールド)と、当該ネイティブコードのひな形の次に続く命令のひな形を格納する命令テーブルの所定のデータへのポインタ(図中のNEXTフィールド)と、を格納する。上述の変換テーブル13と同様に、次に続く命令のひな形が存在しない場合、当該NEXTフィールドには、このようなポインタは格納されていない。

【0056】

<DRMT15>

DRMT15は、Dalvikレジスタと物理レジスタ(本実施形態では、物理レジスタ6)との対応関係を管理する。

【0057】

Dalvikバイトコードでは、すべてのDalvikレジスタのデータがメモリ上の所定の領域に存在するため、同一のDalvikレジスタに対するロード命令が頻繁に生じうる。このDRMT15は、主に、このような頻発するロード命令を削減するために用いられる。つまり、後述するように、このDRMT15により、命令作成部12は、一部のロード命令の作成を省略する。これにより、メモリアクセスが削減される。

【0058】

言い換えると、DRMT15は、不要なネイティブコードの作成を防止するため、既に行われたメモリアクセスを管理する。具体的には、DRMT15は、既に行われたメモリアクセスの管理するため、Dalvikレジスタがどの物理レジスタに対応づけられているかを示す情報を格納する。

【0059】

図4は、DRMT15の一例を示す。DRMT15は、Dalvikレジスタがどの物理レジスタに対応づけられているかを示す情報として、図4に示される各情報を格納する。DRMT15は、図4に示されるとおり、DMフィールド、Validフィールド、Dirtyフィールド、Timeフィールドを含む。

【0060】

DMフィールドには、エントリに対応するDalvikレジスタの番号が格納される。命令作成部12は、Dalvikレジスタがどの物理レジスタに対応づけられているかを示す情報をDRMT15から検索するため、当該DMフィールドに格納されたDalvikレジスタの番号を用いる。

【0061】

Validフィールドには、エントリが有効であるか否かを示すValidビットが格納される。Validビットは、当該エントリが有効であることを「1」で示し、当該エントリが無効で

あることを「0」で示す。

【0062】

Dirtyフィールドには、物理レジスタに格納されている値が、対応するDalvikレジスタ

に格納されている値よりも新しいか否かを示すDirtyビットが格納される。Dirtyビットは、物理レジスタに格納されているデータが、対応するDalvikレジスタに格納されているデータよりも新しいことを「1」で示す。また、Dirtyビットは、物理レジスタに格納され

ているデータが対応するDalvikレジスタに格納されているデータよりも新しくない(例えば、同一である)ことを「0」で示す。なお、物理レジスタに格納されているデータが、対応するDalvikレジスタに格納されているデータよりも新しいとは、Dalvikレジスタに格納されているデータが物理レジスタにロードされた後に、所定の演算処理が行われることで、物理レジスタに格納されているデータがDalvikレジスタに格納されているデータと異なった状態を指す。本実施形態では、命令作成部12が、ストア命令に関するネイティブコードの作成を省略した時に、当該ストア命令に関するDalvikレジスタと同一の番号をDMフィールドに格納するエントリの当該Dirtyフィールドに格納される値を「1」に置き換

える。

【0063】

Timeフィールドには、DMフィールドに格納された番号のDalvikレジスタに関する処理を命令作成部12が行った時刻を記録するタイムスタンプを格納する。なお、本実施形態では、当該Timeフィールドに格納される値は、その値が大きいほど新しい時間を表す。

【0064】

DRフィールドには、DMフィールドに格納された番号のDalvikレジスタに対応する物理レジスタの番号が格納される。

【0065】

命令作成部12は、このDRMT15を用いて、Dalvikレジスタと物理レジスタの対応関係を認識する。つまり、命令作成部12は、DRMT15により、物理レジスタが割り当てられているDalvikレジスタの番号を、割り当てられている物理レジスタの番号と共に認識する。

【0066】

なお、Dalvikレジスタに割り当てる物理レジスタは、例えば、オペレーティングシステムや所定のアプリケーションのために保持されておらず、自由に用いることができる物理レジスタから選ばれてもよい。

【0067】

また、Dalvikレジスタに割り当てる物理レジスタの数は任意でよい。本実施形態では、Dalvikレジスタに割り当てることができる物理レジスタの数は12個であるとする。そして、物理レジスタの番号は、0番から11番までであるとする。このため、DRMT15は12のエントリを格納する記憶部である。

【0068】

<まとめ>

変換器1は、Dalvikバイトコードから1又は複数のネイティブコードを作成する。この時、変換器1は、一部のロード命令に関するネイティブコードについては、その作成を実行しない。

【0069】

なお、バイトコードバッファ11は、本発明に係る「保持部」に相当する。また、変換テーブル13及び命令テーブル14は、本発明に係る「第1記憶部」に相当する。さらに、DRMT15は、本発明に係る「第2記憶部」に相当する。

【0070】

§3 動作例

以下、図5及び図6を用いて、本実施形態に係る変換器1の動作例を説明する。図5及び図6は、本実施形態に係る変換器1の動作例を示す。以下、Dalvikレジスタを「Mx(x

は自然数であり、Dalvikレジスタの番号を示す)」で表す。物理レジスタを「Rx(xは自

然数であり、物理レジスタの番号を示す)」で表す。仮の物理レジスタを「DRx(xは自然数であり、仮の物理レジスタの番号を示す)」で表す。仮のDalvikレジスタを「DMy(yは

自然数、但し、yは、Dalvikバイトコードのオペランドの番号)」で表す。加算命令を「add」で表す。ロード命令を「load」で表す。ストア命令を「store」で表す。ただし、こ

れらは、より具体的には、それぞれのコードにおける所定の方法で指定される。

【0071】

なお、簡単に説明するため、本動作例では、2つの連続する加算命令のDalvikバイトコードを、変換器1がネイティブコードに変換する例を示す。2つの連続する加算命令とは、1つ目が「M0, add, M1, M2」(M0 = M1 + M2)であり、2つ目が「M3, add, M2, M0」(M3 = M2 + M0)である。

【0072】

また、本動作例では、当初DRMT15には何も格納されていないものとして、当該2つの加算命令のネイティブコードが作成される処理手順の一例を説明する。図5は、命令作成部12が1つ目の加算命令「M0, add, M1, M2」のネイティブコードを作成する時の処理

手順の一例を示す。また、図6は、命令作成部12が2つ目の加算命令「M3, add, M2, M0」のネイティブコードを作成する時の処理手順の一例を示す。なお、以下ではネイティ

ブコードを1サイクルに1命令ずつ作成および出力することを想定して説明しているが、同一サイクルに複数の命令を作成および出力してもよい。

【0073】

<1つ目の加算命令>

図5に示されるとおり、まず、命令作成部12は、バイトコードバッファ11からDalvikバイトコードを1つ分取得する(S100)。当該取得したDalvikバイトコードは、加算命令「M0, add, M1, M2」である。

【0074】

次に、命令作成部12は、取得したDalvikバイトコードのオペコード(add)を参照し

て、Opフィールドに当該オペコードを格納するエントリが変換テーブル13に存在するかどうかを検索する(S101)。本実施形態では、図5に示されるとおり、エントリが検索される。なお、命令作成部12は、取得したDalvikバイトコードのオペコードに対応するエントリが変換テーブル13から検索できなかった場合、上記ステータスレジスタ3の格納する識別子をネイティブコードによる命令実行モードを示す識別子に所定の方法によって書き換えてもよい。

【0075】

次に、命令作成部12は、変換テーブル13から検索したエントリのEフィールドに格納される値を参照し、当該オペコード(add)に対応する1又は複数のネイティブコード

のひな形が変換テーブル13又は命令テーブル14に存在するかを判定する(S102)。本実施形態では、図5に示されるとおり、Eフィールドには「1」が格納されているので、オペコード(add)に対応する1又は複数のネイティブコードのひな形が変換テーブ

ル13又は命令テーブル14に存在すると判定される。

【0076】

次に、命令作成部12は、変換テーブル13から検索したエントリのInstフィールドに格納されている1命令分のネイティブコードのひな形「load DR0, DM2」(ロード命

令)を取得する(S103)。

【0077】

次に、命令作成部12は、取得したひな形である「load DR0, DM2」の仮のオペランド

の置き換えを行う(S104、S105)。ここで、「load DR0, DM2」の仮のオペラン

ドは、「DR0」と「DM2」である。

【0078】

まず、命令作成部12は、「DM2」に置き換えるオペランドを1つ目の加算命令であるDalvikバイトコード(M0, add, M1, M2)より取得する。「DM2」は、Dalvikバイトコード

の2番目のオペランドを指すため、命令作成部12は、「DM2」を、Dalvikバイトコード

の2番目のオペランドである「M1」(Dalvikレジスタの1番)に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「1」(置き換えたオペラ

ンドのDalvikレジスタの番号)を格納したエントリを検索する(S104)。

【0079】

この時点では、DRMT15には何も格納されていないので、命令作成部12は、DMフィールドに「1」(Dalvikレジスタの1番)を格納したエントリを検索することはできない。この場合、命令作成部12は、Dalvikレジスタの割り当てに用いられていない物理レジスタを所定の方法で割り当てる。例えば、本実施形態のように、命令作成部12は、Dalvikレジスタに割り当てられていない物理レジスタの中から番号の一番小さい物理レジスタを割り当てる。具体的には、命令作成部12は、「DR0」を「R0」に置き換える。これによ

り、命令作成部12は、ネイティブコード「load R0, M1」の作成を完了し、当該作成し

たネイティブコードをネイティブデコーダ4へ出力する(S105)。

【0080】

次に、命令作成部12は、作成したネイティブコード「load R0, M1」に基づいて、DRMT15にエントリを登録する(S106)。これは、当該ネイティブコード「load R0, M1」が実行されることにより、メモリアクセスが行われ、Dalvikレジスタの1番が物理レジスタの0番に割り当てられることによる。命令作成部12は、例えば、DMフィールドに「1」、Validフィールドに「1」、Dirtyフィールドに「0」、Timeフィールドに「1」、DRフィールドに「0」を格納したエントリをDRMT15に登録する。

【0081】

S104〜S106の処理により変換テーブル13から取得したひな形である「load DR0, DM2」に関する処理が完了する。

【0082】

次に、命令作成部12は、変換テーブル13から検索したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S107)。

【0083】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「load DR1, DM3」(ロード命令)の仮のオペラ

ンドの置き換えを行う(S108、S109)。ここで、「load DR1, DM3」の仮のオペ

ランドは、「DR1」と「DM3」である。

【0084】

まず、命令作成部12は、「DM3」に置き換えるオペランドを1つ目の加算命令であるDalvikバイトコード(M0 add, M1, M2)より取得する。「DM3」は、Dalvikバイトコードの3番目のオペランドを指すため、命令作成部12は、「DM3」を、Dalvikバイトコードの

3番目のオペランドである「M2」に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「2」を格納したエントリを検索する(S108)。

【0085】

この時点では、DRMT15には、DMフィールドに「1」を格納したエントリしか登録されていないので、上記と同様、命令作成部12は、DMフィールドに「2」を格納したエントリを検索することはできない。この場合、命令作成部12は、「DR1」を「R1」に置き換

える。これにより、命令作成部12は、ネイティブコード「load R1, M2」の作成を完了

し、当該作成したネイティブコードをネイティブデコーダ4へ出力する(S109)。

【0086】

次に、命令作成部12は、作成したネイティブコード「load R1, M2」に基づいて、DRMT15にエントリ登録をする(S110)。これは、当該ネイティブコード「load R1, M2」が実行されることにより、メモリアクセスが行われ、Dalvikレジスタの2番が物理レジスタの1番に割り当てられることによる。命令作成部12は、例えば、DMフィールドに「2」、Validフィールドに「1」、Dirtyフィールドに「0」、Timeフィールドに「2」、DRフィールドに「1」を格納したエントリをDRMT15に登録する。

【0087】

S108〜S110の処理により命令テーブル14から取得したひな形である「load D

R1, DM3」に関する処理が完了する。

【0088】

次に、命令作成部12は、S107で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S111)。

【0089】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「add DR2, DR0, DR1」(加算命令)の仮のオペ

ランドの置き換えを行う(S112、S113)。ここで、「add DR2, DR0, DR1」の仮

のオペランドは、「DR2」、「DR0」、「DR1」である。また、当該エントリのInstフ

ィールドには、Dalvikバイトコードの先頭のオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令であることを示すデータフラグが存在する(不図示)。

【0090】

命令作成部12は、当該データフラグの存在により、まずはDalvikバイトコードの先頭のオペランド「M0」を取得する。そして、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「0」を格納したエントリを検索する(S112)。これは、当該命令が、Dalvikバイトコードの先頭のオペランド(M0)に物理レジスタ(「DR2」に置き換

えられる物理レジスタ)を割り当てる命令であることによる。したがって、命令作成部12は、DRMT15のDMフィールドに「0」を格納したエントリを検索することにより、Dalvikレジスタ「M0」にすでに割り当てられた物理レジスタが存在するか否かを判定する。

【0091】

この時点では、DRMT15には、DMフィールドに「0」を格納したエントリは登録されていないので、上記と同様、命令作成部12は、DMフィールドに「0」を格納したエントリを検索することはできない。この場合、Dalvikレジスタ「M0」にすでに割り当てられた物理レジスタが存在しないので、仮のオペランド「DR2」を適当な物理レジスタの番号に置

き換える。この場合、命令作成部12は、「DR2」を「R2」に置き換える。なお、DRMT1

5からエントリが検索された場合、命令作成部12は、「DR2」を、検索されたエントリ

のDRフィールドに格納された物理レジスタの番号に置き換える。

【0092】

また、命令作成部12は、例えば、同一バイトコード内の別のネイティブコードと共通の番号が割り当てられている仮の物理レジスタを、当該別のネイティブコードにおいて割り当てた物理レジスタにより置き換える。つまり、命令作成部12は、「DR0」を「R0」

(1番目のネイティブコードのひな形を参照)と置き換え、「DR1」を「R1」(2番目の

ネイティブコードのひな形を参照)と置き換える。これにより、命令作成部12は、ネイティブコード「add R2, R0, R1」の作成を完了し、当該完成したネイティブコードをネイティブデコーダ4へ出力する(S113)。なお、これらの仮の物理レジスタと物理レジスタとの対応関係(上記の「DR0」と「R0」との対応関係、および、「DR1」と「R1」との対応関係)は命令作成部12内のテーブル(不図示)によって管理される。

【0093】

次に、命令作成部12は、作成したネイティブコード「add R2, R0, R1」に基づいて、DRMT15にエントリ登録をする(S114)。当該命令は、上述のとおり、Dalvikバイトコードの先頭のオペランド(M0)に物理レジスタ(R2)を割り当てる命令であることによる。命令作成部12は、例えば、DMフィールドに「0」、Validフィールドに「1」、Dirtyフィールドに「1」、Timeフィールドに「3」、DRフィールドに「2」を格納したエントリをDRMT15に登録する。なお、上述までのエントリと異なりDirtyフィールドに「1

」を格納する理由は、この時点において、当該add命令によりR2(物理レジスタ)に格納

されるデータがDalvikレジスタ(M0)にストアされていないからである。つまり、Dalvikレジスタ(M0)よりも、当該Dalvikレジスタ(M0)に割り当てられた物理レジスタ(R2)の方が新しいデータを格納しているからである。

【0094】

S112〜S114の処理により命令テーブル14から取得したひな形である「add DR2, DR0, DR1」に関する処理が完了する。

【0095】

次に、命令作成部12は、S111で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S115)。

【0096】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「store DR2, DM1」(ストア命令)の仮のオペランドの置き換えを行う。ここで、「store DR2, DM1」の仮のオペランドは、「DR2」と「DM1」である。ただし、当該ネイティブコードのひな形は、Dalvikレジスタに対するストア命令に関するネイティブコードのひな形であるため、ネイティブコードの作成は省略される。

【0097】

この時、命令作成部12は、ネイティブコードの作成については実行しないが、「DM1

」に置き換えるはずであったオペランドを1つ目の加算命令であるDalvikバイトコード(M0 add, M1, M2)より取得する。「DM1」は、Dalvikバイトコードの1番目のオペランド

を指すため、命令作成部12は、「DM1」に置き換えるはずであったオペランドとして、

「M0」(Dalvikレジスタの0番)を取得する。そして、命令作成部12は、当該Dalvikレジスタの番号「0」をDMフィールドに格納したエントリを検索する(S116)。図5に示されるとおり、DMフィールドに「0」を格納したエントリが検索される。命令作成部12は、検索したエントリのDirtyフィールドに格納された値を「1」に置き換える。なお

、この時点においてすでに当該エントリのDirtyフィールドに格納された値は「1」であ

るため、命令作成部12は、当該処理を省略してもよい。

【0098】

以上までのS100〜S116の処理により、命令作成部12は、1つ目の加算命令「M0, add, M1, M2」のネイティブコードの作成を完了する。具体的に、命令作成部12は

、1つ目の加算命令「M0, add, M1, M2」に対して、「load R0, M1」、「load R1, M2」

、「add R2, R0, R1」の3つのネイティブコードを作成する。

【0099】

<2つ目の加算命令>

次に、図6を用いて、2つ目の加算命令「M3, add, M2, M0」(M3 = M2 + M0)のネイ

ティブコードを作成するときの処理手順について説明する。

【0100】

図6に示されるとおり、まず、命令作成部12は、バイトコードバッファ11からDalvikバイトコードを1つ分取得する(S200)。当該取得したDalvikバイトコードは、加算命令「M3, add, M2, M0」である。

【0101】

次に、命令作成部12は、取得したDalvikバイトコードのオペコード(add)を参照し

て、変換テーブル3のOpフィールドに当該オペコードを格納するエントリが変換テーブル13に存在するかどうかを検索する(S201)。本実施形態では、図6に示されるとおり、エントリが検索される。

【0102】

次に、命令作成部12は、変換テーブル13から検索したエントリのEフィールドに格納される値を参照し、当該オペコード(add)に対応する1又は複数のネイティブコード

のひな形が変換テーブル13又は命令テーブル14に存在するかを判定する(S202)。本実施形態では、図6に示されるとおり、Eフィールドには「1」が格納されているので、オペコード(add)に対応する1又は複数のネイティブコードのひな形が変換テーブ

ル13又は命令テーブル14に存在すると判定される。

【0103】

次に、命令作成部12は、変換テーブル13から検索したエントリのInstフィールドに格納されている1命令分のネイティブコードのひな形「load DR0, DM2」(ロード命

令)を取得する(S203)。

【0104】

次に、命令作成部12は、取得したひな形である「load DR0, DM2」の仮のオペランド

の置き換えを行う。ここで、「load DR0, DM2」の仮のオペランドは、「DR0」と「DM2」

である。

【0105】

まず、命令作成部12は、「DM2」に置き換えるオペランドを2つ目の加算命令であるDalvikバイトコード(M3, add, M2, M0)より取得する。「DM2」は、Dalvikバイトコード

の2番目のオペランドを指すため、命令作成部12は、「DM2」を、Dalvikバイトコード

の2番目のオペランドである「M2」(Dalvikレジスタの2番)に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「2」(置き換えたオペランドのDalvikレジスタの番号)を格納したエントリを検索する(S204)。

【0106】

この時点において、DRMT15にはDMフィールドに「2」(Dalvikレジスタの2番)を格納したエントリが検索される。したがって、この時、命令作成部12は、当該ロード命令のネイティブコードの作成は省略される。つまり、命令作成部12は、仮のオペランドの置き換えを実行せず、ネイティブコードの作成を実行しない。この時点で、「load DR0, DM2」に関する処理が完了する。

【0107】

次に、命令作成部12は、変換テーブル13から検索したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S205)。

【0108】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「load DR1, DM3」(ロード命令)の仮のオペラ

ンドの置き換えを行う。ここで、「load DR1, DM3」の仮のオペランドは、「DR1」と「DM3」である。

【0109】

まず、命令作成部12は、「DM3」に置き換えるオペランドを2つ目の加算命令であるDalvikバイトコード「M3, add, M2, M0」より取得する。「DM3」は、Dalvikバイトコード

の3番目のオペランドを指すため、命令作成部12は、「DM3」を、Dalvikバイトコード

の3番目のオペランドである「M0」に置き換える。次に、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「0」を格納したエントリを検索する(S206)。

【0110】

この時点において、DRMT15にはDMフィールドに「0」(Dalvikレジスタの0番)を格納したエントリが検索される。したがって、この時、命令作成部12は、当該ロード命令のネイティブコードの作成は省略される。つまり、命令作成部12は、仮のオペランドの置き換えを実行せず、ネイティブコードの作成を実行しない。この時点で、「load DR1, DM3」に関する処理が完了する。

【0111】

次に、命令作成部12は、S205で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S207)。

【0112】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「add DR2, DR0, DR1」(加算命令)の仮のオペ

ランドの置き換えを行う。ここで、「add DR2, DR0, DR1」の仮のオペランドは、「DR2」、「DR0」、「DR1」である。また、当該エントリのInstフィールドには、Dalvikバイ

トコードの先頭のオペランド(Dalvikレジスタ)に物理レジスタを割り当てる命令であることを示すデータフラグが存在する(不図示)。

【0113】

命令作成部12は、当該データフラグの存在により、まずはDalvikバイトコードの先頭のオペランド「M3」を取得する。そして、命令作成部12は、DRMT15から、当該DRMT15のDMフィールドに「3」を格納したエントリを検索する(S208)。以上のS112と同様の処理である。

【0114】

この時点では、DRMT15には、DMフィールドに「3」を格納したエントリは登録されていないので、上記と同様、命令作成部12は、DMフィールドに「3」を格納したエントリを検索することはできない。この場合、Dalvikレジスタ「M3」にすでに割り当てられた物理レジスタが存在しないので、仮のオペランド「DR2」を適当な物理レジスタの番号に置

き換える。この場合、命令作成部12は、「DR2」を「R3」に置き換える。

【0115】

また、命令作成部12は、例えば、同一バイトコード内の別のネイティブコードと共通の番号が割り当てられている仮の物理レジスタを、当該別のネイティブコードにおいて割り当てた物理レジスタにより置き換える。つまり、命令作成部12は、「DR0」を「R1」

(1番目のネイティブコードのひな形を参照)と置き換え、「DR1」を「R2」(2番目の

ネイティブコードのひな形を参照)と置き換える。なお、1番目及び2番目のネイティブコードは作成されていない。命令作成部12は、これらをDRMT15から取得する。命令作成部12は、1番目のネイティブコードのひな形「load DR0, DM2」に対する処理(S2

04)の際、検索されたエントリ(DMフィールドに「2」を格納したエントリ)のDRフィールドから「1」を取得する。これにより、命令作成部12は、「DR0」と置き換える物

理レジスタの番号を取得する。また、命令作成部12は、2番目のネイティブコードのひな形「load DR1, DM3」に対する処理(S206)の際、検索されたエントリ(DMフィー

ルドに「0」を格納したエントリ)のDRフィールドから「2」を取得する。これにより、命令作成部12は、「DR1」と置き換える物理レジスタの番号を取得する。なお、これら

の仮の物理レジスタ「DRx」と物理レジスタ「Rx」との対応関係は、命令作成部12内に

存在するテーブル(不図示)によって管理されている。

【0116】

これにより、命令作成部12は、ネイティブコード「add R3, R1, R2」の作成を完了し、当該完成したネイティブコードをネイティブデコーダ4へ出力する(S209)。

【0117】

次に、命令作成部12は、作成したネイティブコード「add R3, R1, R2」に基づいて、DRMT15にエントリを登録する(S210)。当該命令は、上述のとおり、Dalvikバイトコードの先頭のオペランド(M3)に物理レジスタ(R3)を割り当てる命令であることによる。命令作成部12は、例えば、DMフィールドに「3」、Validフィールドに「1」、Dirtyフィールドに「1」、Timeフィールドに「4」、DRフィールドに「3」を格納したエントリをDRMT15に登録する。この時点で「add DR2, DR0, DR1」に関する処理が完了する

。

【0118】

次に、命令作成部12は、S207で取得したエントリのNEXTフィールドに格納されるポインタを用いて、当該ネイティブコードの次に続く命令のひな形を格納する命令テーブル14の所定のエントリを取得する(S211)。

【0119】

次に、命令作成部12は、命令テーブル14から取得したエントリのInstフィールドからネイティブコードのひな形である「store DR2, DM1」の仮のオペランドの置き換えを行う。ここで、「store DR2, DM1」の仮のオペランドは、「DR2」と「DM1」である。ただし、当該ネイティブコードのひな形は、Dalvikレジスタに関するストア命令に関するネイティブコードのひな形であるため、ネイティブコードの作成は省略される。

【0120】

この時、命令作成部12は、ネイティブコードの作成については実行しないが、「DM1

」に置き換えるはずであったオペランドを2つ目の加算命令であるDalvikバイトコード「M3, add, M2, M0」より取得する。「DM1」は、Dalvikバイトコードの1番目のオペランドを指すため、命令作成部12は、「DM1」に置き換えるはずであったオペランドとして、

「M3」(Dalvikレジスタの3番)を取得する。そして、命令作成部12は、当該Dalvikレジスタの番号「3」をDMフィールドに格納したエントリを検索する(S212)。図6に示されるとおり、DMフィールドに「3」を格納したエントリが検索される。命令作成部12は、検索したエントリのDirtyフィールドに格納された値を「1」に置き換える。なお

、この時点においてすでに当該エントリのDirtyフィールドに格納された値は「1」であ

るため、命令作成部12は、当該処理を省略してもよい。

【0121】

以上までのS200〜S212の処理により、命令作成部12は、2つ目の加算命令「M3, add, M2, M0」のネイティブコードの作成を完了する。具体的に、命令作成部12は

、2つ目の加算命令「M3, add, M2, M0」に対して、「add DR2, DR0, DR1」の1つのネイティブコードを作成する。

【0122】

<その他>

以上のようにして、命令作成部12は、Dalvikバイトコードからネイティブコードを作成する。また、以上のようにして、DRMT15にエントリが追加されていく。このように追加されるエントリについて、命令作成部12は、所定のタイミングでエントリの削除を行う。所定のタイミングとは、例えば、DRMT15のエントリが一杯で命令作成部12によるエントリの追加が出来ない時である。この時、命令作成部12は、DRMT15から所定のエントリを削除し、当該エントリの追加を実行する。また、所定のタイミングの他の例として、バイトコードによる命令実行モードからネイティブコードによる命令実行モードに遷移する時が挙げられる。この時、命令作成部12はDRMT15の全エントリを削除する。

【0123】

なお、所定のエントリとは、例えば、登録されてから一番時間が経っているエントリである。命令作成部12は、このようなエントリをTimeフィールドに格納されている時刻から判断する。またその他の例として、所定のエントリとは、例えば、命令作成部12がランダムに選択したエントリである。

【0124】

また、命令作成部12が削除するエントリの数は任意でよい。例えば、命令作成部12は、DRMT15のエントリを削除する時、一度に3つのエントリを削除してもよい。

【0125】

なお、このようなDRMT15のエントリを削除する時、命令作成部12は、削除する対象のエントリのDirtyフィールドの値(Dirtyビット)を確認する。

【0126】

削除する対象のエントリのDirtyフィールドに「0」が格納されている場合、当該エン

トリに含まれた番号の物理レジスタに格納されているデータは、当該エントリに含まれた番号のDalvikレジスタに格納されているデータと同一である。すなわち、対応関係にあるDalvikレジスタと物理レジスタとは同一のデータを格納しているため、物理レジスタに格納されているデータをDalvikレジスタにストアする必要はない。したがって、この時、命令作成部12は、何らネイティブコードを作成しない。

【0127】

他方、削除するエントリのDirtyフィールドに「1」が格納されている場合、当該エン

トリに含まれた番号の物理レジスタに格納されているデータは、更新されているため、当該エントリに含まれた番号のDalvikレジスタに格納されているデータと異なる。すなわち、対応関係にあるDalvikレジスタと物理レジスタとは異なるデータを格納しているため、物理レジスタに格納されているデータをDalvikレジスタにストアする必要がある。命令作

成部12は、当該物理レジスタに格納されるデータを当該Dalvikレジスタにストアする命令に関するネイティブコードを作成する。例えば、命令作成部12は、命令テーブル14等に格納されたストア命令に関するネイティブコードのひな形を取得する。そして、命令作成部12は、当該取得したネイティブコードのひな形に含まれた仮のオペランドを、当該削除する対象のエントリに含まれたDMフィールド及びDRフィールドに格納されている値で置き換える。このようにして、命令作成部12は、削除する対象のエントリに含まれた番号の物理レジスタとDalvikレジスタとに関するストア命令のネイティブコードを作成する。これにより、物理レジスタに格納されている新しいデータがDalvikレジスタ(メモリ)に格納される前に、当該新しいデータを格納する物理レジスタに別のDalvikレジスタが割り当てられることを防ぐことができる。

【0128】

§4 実施の形態に係る作用及び効果

以上によれば、本実施形態に係る変換器は、Dalvikバイトコードに対応するネイティブコードを作成する。この時、命令作成部12は、DRMT15を参照して、一部のロード命令のネイティブコードの作成を省略する。また、命令作成部12は、DRMT15からエントリを削除する時にのみDalvikレジスタに対するストア命令のネイティブコードの作成を行い、それ以外の時はDalvikレジスタに対するストア命令のネイティブコードの作成を省略する。これにより、本実施形態に係る変換器によれば、ロード命令及びストア命令の発行を抑えることができ、メモリアクセスを削減することができる。

【0129】

§5 補足

以上、本発明の実施の形態を詳細に説明してきたが、前述までの説明はあらゆる点において本発明の例示に過ぎず、その範囲を限定しようとするものではない。本発明の範囲を逸脱することなく種々の改良や変形を行うことができることは言うまでもない。本発明は、特許請求の範囲によってのみその範囲が解釈される。また、当業者は、上記本実施形態の記載から、特許請求の範囲の記載および技術常識に基づいて等価な範囲を実施することができる。また、本明細書において使用される用語は、特に言及しない限り、当該分野で通常用いられる意味で用いられる。したがって、他に定義されない限り、本明細書中で使用される全ての専門用語および技術用語は、本発明の属する分野の当業者によって一般的に理解される意味と同じ意味を有する。両者が矛盾する場合、本明細書において使用される用語は、本明細書(定義を含めて)に記載された意味において理解される。

【符号の説明】

【0130】

1 変換器

2 フェッチャ

3 ステータスレジスタ

4 ネイティブデコーダ

5 演算装置

6 物理レジスタ

7 メモリ

11 バイトコードバッファ

12 命令作成部

13 変換テーブル

14 命令テーブル

15 DRMT(Dalvik Register Map Table)

100 プロセッサ

【特許請求の範囲】

【請求項1】

メモリからフェッチしたレジスタ形式のバイトコードを保持する保持部と、

バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部と、

保持部に保持されているバイトコードを取り出し、第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成する命令作成部と、

物理レジスタの番号と、命令作成部が作成したネイティブコードにより当該番号の物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタとの対応関係を示すデータを格納する第2記憶部と、を備え、

命令作成部は、作成するネイティブコードが、第2記憶部に格納されたデータに含まれるメモリ上のレジスタに関するロード命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする変換器。

【請求項2】

命令作成部は、ネイティブコードに格納される物理レジスタの番号を、第2記憶部に格納されたデータに含まれる物理レジスタの番号を用いて特定することを特徴とする請求項1に記載の変換器。

【請求項3】

命令作成部は、作成するネイティブコードがメモリ上のレジスタに関するストア命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする請求項1または2に記載の変換器。

【請求項4】

命令作成部は、物理レジスタを割り当てるネイティブコードのひな形を第1記憶部から取得した時、バイトコードに含まれるメモリ上のレジスタの番号と、当該レジスタに割り当てる物理レジスタの番号との対応関係を示すデータを作成し、当該データを第2記憶部に格納することを特徴とする請求項1から3のいずれか1項に記載の変換器。

【請求項5】

命令作成部は、所定の時点において、第2記憶部に格納されているデータを削除し、当該削除するデータに含まれる番号の物理レジスタに格納されたデータを、当該削除するデータに含まれるメモリ上のレジスタに書き込むストア命令のネイティブコードを作成することを特徴とする請求項4に記載の変換器。

【請求項6】

メモリからフェッチしたレジスタ形式のバイトコードを保持するステップと、

保持したバイトコードを取り出し、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成するネイティブコード作成ステップと、

物理レジスタの番号と、ネイティブコード作成ステップにより作成されたネイティブコードにより物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタとの対応関係を示すデータを第2記憶部に格納する記憶ステップと、を含み、

ネイティブコード作成ステップでは、作成するネイティブコードが、第2記憶部に格納されたメモリ上のレジスタに関するロード命令またはストア命令であると判定される場合、当該ネイティブコードの作成が省略されることを特徴とする変換方法。

【請求項1】

メモリからフェッチしたレジスタ形式のバイトコードを保持する保持部と、

バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部と、

保持部に保持されているバイトコードを取り出し、第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成する命令作成部と、

物理レジスタの番号と、命令作成部が作成したネイティブコードにより当該番号の物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタとの対応関係を示すデータを格納する第2記憶部と、を備え、

命令作成部は、作成するネイティブコードが、第2記憶部に格納されたデータに含まれるメモリ上のレジスタに関するロード命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする変換器。

【請求項2】

命令作成部は、ネイティブコードに格納される物理レジスタの番号を、第2記憶部に格納されたデータに含まれる物理レジスタの番号を用いて特定することを特徴とする請求項1に記載の変換器。

【請求項3】

命令作成部は、作成するネイティブコードがメモリ上のレジスタに関するストア命令であると判定した場合、当該ネイティブコードの作成を省略することを特徴とする請求項1または2に記載の変換器。

【請求項4】

命令作成部は、物理レジスタを割り当てるネイティブコードのひな形を第1記憶部から取得した時、バイトコードに含まれるメモリ上のレジスタの番号と、当該レジスタに割り当てる物理レジスタの番号との対応関係を示すデータを作成し、当該データを第2記憶部に格納することを特徴とする請求項1から3のいずれか1項に記載の変換器。

【請求項5】

命令作成部は、所定の時点において、第2記憶部に格納されているデータを削除し、当該削除するデータに含まれる番号の物理レジスタに格納されたデータを、当該削除するデータに含まれるメモリ上のレジスタに書き込むストア命令のネイティブコードを作成することを特徴とする請求項4に記載の変換器。

【請求項6】

メモリからフェッチしたレジスタ形式のバイトコードを保持するステップと、

保持したバイトコードを取り出し、バイトコードの命令コードに対応したネイティブコードのひな形を格納する第1記憶部に格納されているネイティブコードのひな形を用いて、当該バイトコードに対応する1または複数のネイティブコードを作成するネイティブコード作成ステップと、

物理レジスタの番号と、ネイティブコード作成ステップにより作成されたネイティブコードにより物理レジスタに格納されたデータに対応するデータを格納するメモリ上のレジスタとの対応関係を示すデータを第2記憶部に格納する記憶ステップと、を含み、

ネイティブコード作成ステップでは、作成するネイティブコードが、第2記憶部に格納されたメモリ上のレジスタに関するロード命令またはストア命令であると判定される場合、当該ネイティブコードの作成が省略されることを特徴とする変換方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−88909(P2012−88909A)

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願番号】特願2010−234673(P2010−234673)

【出願日】平成22年10月19日(2010.10.19)

【出願人】(504132881)国立大学法人東京農工大学 (595)

【Fターム(参考)】

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願日】平成22年10月19日(2010.10.19)

【出願人】(504132881)国立大学法人東京農工大学 (595)

【Fターム(参考)】

[ Back to top ]