外部メディアインタフェース装置、テスト方法

【課題】正当性確認テストを行う際の時間を短縮する外部メディアインタフェース装置を提供すること。

【解決手段】記憶手段アクセス制御手段45と、外部メディアアクセス手段41、52と、暗号器43と、を有する外部メディアインタフェース装置100であって、前記暗号器のテストモードである場合、前記記憶手段アクセス制御手段と前記外部メディアアクセス手段との間にテスト用のパスを構築するパス構築手段53と、前記記憶手段アクセス制御手段が読み出したテストデータを取得してテストデータの送信先を振り分けるデータ振り分け手段44、60と、前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するデータ比較手段51と、を有する。

【解決手段】記憶手段アクセス制御手段45と、外部メディアアクセス手段41、52と、暗号器43と、を有する外部メディアインタフェース装置100であって、前記暗号器のテストモードである場合、前記記憶手段アクセス制御手段と前記外部メディアアクセス手段との間にテスト用のパスを構築するパス構築手段53と、前記記憶手段アクセス制御手段が読み出したテストデータを取得してテストデータの送信先を振り分けるデータ振り分け手段44、60と、前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するデータ比較手段51と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアインタフェース装置に関し、特に、暗号化又は復号が可能な暗号器を備えた外部メディアインタフェース装置に関する。

【背景技術】

【0002】

デジタルデータを記憶する多様な記憶媒体が安価に利用できるようになっている。しかし、記憶媒体が外部に流出すると膨大なデジタルデータが漏洩してしまうおそれがある。このため、セキュリティ対策として、デジタルデータを暗号化して記憶することが行われている(例えば、特許文献1参照。)。特許文献1には、入力されたデータを任意の数の記憶装置に分散して、転送途中のデータブロックを、記憶装置毎に異なる暗号鍵を用いて暗号化するRAIDコントローラが開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0003】

CPU等が脱着可能な外部記憶メディアにデジタルデータを記録する場合も、同様に、デジタルデータを暗号化することが考えられる。

【0004】

図1は、従来の外部メディアI/F100の一例を示す。図1において外部メディアI/F100は画像形成装置に搭載されることが想定されているが、外部メディアI/F以外の機能ブロックについて後に詳述する。

【0005】

外部メディアI/F100は外部記憶メディア200へのアクセス制御を行う。外部メディアI/F100は、リードライト兼用のDMAコントローラ(以下、RW−DMAC104)、暗号器103、メディアアクセス制御部102、SRAM105、及び、外部メディア用のIP(Intellectual Property)101、を有する。RW−DMAC104はCPU11を介さずに外部記憶メディア200からのデータ読み出し又はデータの書き込みを行う。暗号器103はRW−DMAC104から受け取ったデジタルデータの暗号化を行ったり、外部記憶メディア200から読み込まれた暗号化データを復号してRW−DMAC104に渡したりする。

【0006】

メディアアクセス制御部102はIP101を制御する。IP101は外部記憶メディア200にアクセスを行う専用の回路である。SRAM105は外部記憶メディア200へ転送する際、及び、外部記憶メディア200からの読み込み時に、一次バッファとして利用される。

【0007】

例えば、暗号化モジュールに関するセキュリティ要件を規定した規格としてFIPS140-2がある。FIPS140-2(FEDERAL INFORMATION PROCESSING STANDARDS PUBLICATION )は、「暗号モジュールが(電源OFF、リセット、リブート等の後で)電源投入された時、その暗号モジュールによって必ず暗号器の自己テスト(正当性確認テスト)を実行されなければならない」と定められている。

【0008】

図2は、FIPS140-2に対応した正当性確認テストの手順を説明する図の一例である。図2の矢印線106に示すように、暗号器103はメモリ12のINPUTデータを暗号化して外部記憶メディア200へ一度出力し、それをRW−DMAC104が再度メモリ12へ読み込む。CPU11が実行するソフトウェアは予め用意されている期待値データと読み出した暗号化されているINPUTデータが一致するか否かにより暗号器103の正当性を確認する。

【0009】

図3は、この正当性確認テストを模式的に説明する図の一例である。画像形成装置のメーカ等は、ソフトウェアや不揮発の記憶装置に予め期待値データと暗号器103へ入力するためのINPUTデータを記憶させておく。

(i) RW−DMAC104はINPUTデータを暗号器103に入力する。

(ii) 暗号器103はINPUTデータを暗号化し、メディアアクセス制御部102に入力する。この時、メディアアクセス制御部102は、外部記憶メディア200の起動処理が完了するまで、ASIC内のSRAM105で保持する。

(iii) 外部記憶メディア200が起動するとメディアアクセス制御部102はIP101を利用して一度外部記憶メディア200へ蓄積する。

(iv) メディアアクセス制御部102は、暗号化されたINPUTデータを読み出す。この過程では、暗号器103を介さずにINPUTデータがRW−DMAC104に出力され、RW−DMAC104は暗号化されたINPUTデータをメモリ12に記憶する。

(v) CPU11は、予め用意されていた期待値データと、暗号化されたINPUTデータとを比較し、暗号器103の正当性を確認する。

【0010】

ここで、(ii)に示すように、外部記憶メディア200によっては駆動系が安定動作するまで若干の時間を要するものがある。また、外部記憶メディア200によっては動作前に初期化を行う必要があるものもある。これらの処理には比較的時間がかかることが知られており、起動時にこの処理を行うと、ユーザが利用開始できるまでの時間(起動時間)が大幅に長くなってしまい、ユーザの利便性を損なうといった問題があった。

【0011】

本発明は、上記課題に鑑み、正当性確認テストを行う際の時間を短縮する外部メディアインタフェース装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、記憶手段からデータを読み出し、また、記憶手段へデータを書き込む記憶手段アクセス制御手段と、外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアアクセス手段と、前記外部メディアアクセス手段が前記外部記憶メディアに書き込むデータを暗号化し、前記外部メディアアクセス手段が前記外部記憶メディアから読み出したデータを復号する暗号器と、を有する外部メディアインタフェース装置であって、前記暗号器の暗号化機能と復号機能のどちらかのテストモードの設定を受け付けるテストモード設定受付手段と、前記テストモード設定受付手段が前記暗号器の暗号化機能のテストモードを受け付けた場合、前記記憶手段アクセス制御手段が読み出したテストデータの送信先を前記データ比較手段又は前記暗号器に振り分けるデータ振り分け手段と、前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するデータ比較手段と、前記記憶手段アクセス制御手段と前記データ振り分け手段、前記データ振り分け手段と前記データ比較手段、前記データ振り分け手段と前記暗号器、及び、前記暗号器と前記データ比較手段、の間にデータパスを構築するパス構築手段と、を有する。

【発明の効果】

【0013】

正当性確認テストを行う際の時間を短縮する外部メディアインタフェース装置を提供することができる。

【図面の簡単な説明】

【0014】

【図1】従来の外部メディアI/Fの一例を示す図である。

【図2】FIPS140-2に対応した生成性確認テストの手順を説明する図の一例である。

【図3】正当性確認テストを模式的に説明する図の一例である。

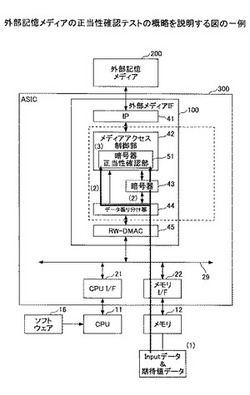

【図4】外部記憶メディアの正当性確認テストの概略を説明する図の一例である。

【図5】画像形成装置の概略構成図の一例である。

【図6】メディアアクセス制御部の機能ブロック図の一例である。

【図7】テストデータを模式的に説明する図の一例である。

【図8】期待値データとINPUTデータが振り分けられる様子を説明する図の一例である。

【図9】暗号器正当性確認部による期待値データとINPUTデータの比較を説明する図の一例である。

【図10】ソフトウェアが外部メディアI/Fの暗号器の正当性を確認する手順を示すフローチャート図の一例である。

【図11】テスト回路の動作手順を示すフローチャート図の一例である。

【図12】画像形成装置の構成図から、要部として外部メディアI/Fを取り出した図の一例である。

【図13】復号時におけるテスト回路の動作手順を示すフローチャート図の一例である。

【図14】暗号化テスト及び復号テストの際のデータフローとデータ間の関係を説明する図の一例である。

【図15】メディアアクセス制御部の機能ブロック図の一例である。

【図16】暗号化テストにおけるデータの流れを模式的に示す図の一例である。

【図17】ソフトウェアが外部メディアI/Fの暗号器の正当性を確認する手順を示すフローチャート図の一例である。

【図18】復号テストにおけるデータの流れを模式的に示す図の一例である。

【図19】ソフトウェアが外部メディアI/Fの暗号器の正当性を確認する手順を示すフローチャート図の一例である。

【発明を実施するための形態】

【0015】

以下、本発明を実施するための形態について図面を参照しながら説明する。

【実施例1】

【0016】

図4は、本実施形態の外部記憶メディア200の正当性確認テストの概略を説明する図の一例である。本実施形態の外部メディアI/F100は、新たに、暗号器正当性確認部51、及び、データ振り分け器44を有する。

(1)データ振り分け器44はメモリに記憶されているINPUTデータと期待値データ(暗号化結果or復号結果)のデータパスを切り換える。詳細は後述するが、暗号化機能のテストを例に説明する。

(2)データ振り分け器44は、暗号器43を介せずに、INPUTデータを暗号器43に入力する。同様に、期待値データを暗号器正当性確認部51に入力する。暗号器43は例えばINPUTデータを暗号化して暗号器正当性確認部51に入力する。

(3)暗号器正当性確認部51は、暗号器43が暗号化したINPUTデータと期待値データを比較する。

【0017】

したがって、暗号器正当性確認部51は、暗号器43が暗号化したINPUTデータをメモリに書き込む必要性をなくし、暗号器43が正当か否かを判定できるようになっている。

【0018】

図4のような正当性確認テストによれば、暗号器43を通過した直後に暗号器正当性確認部51が正当性を確認可能となるので、ユーザの待ち時間を短縮できる。

【0019】

なお以下では、INPUTデータと期待値データの組を「テストデータ」という。

【0020】

〔構成例〕

図5は、画像形成装置の概略構成図の一例を示す。画像形成装置は、プロッタ31、スキャナ32、ASIC300、HDD16、CPU11、メモリ12、ネットワーク装置13、及び、FAX装置14を有する。

【0021】

プロッタ31は、例えば、電子写真方式の印刷装置であり、CMYKの画像データに基づき、トナー画像を用紙に定着することで画像データを出力する。なお、白黒のプロッタでもよいし、液滴を塗布することで用紙に画像を形成するインクジェット型のプロッタでもよい。

【0022】

スキャナ32は、例えば、CCD(Charge Coupled Device )を利用したカラーラインセンサにより原稿を1ライン毎主走査方向に読み取り、原稿を副走査方向に移動して、RGB毎に所定の階調を備えた画像データを生成する。

【0023】

HDD16は、画像データを記憶するストレージとして使用され、また、プログラムやフォントデータなどの静的なデータを記憶している。HDD16はASIC300内の暗号器43の正当性を確認する処理を行うプログラムを記憶しており、図ではソフトウェア16として示されている。

【0024】

CPU11は、CPU11以外のブロックを支配して画像形成装置の全体を制御する。CPU11が実行する制御はプログラムを実行することで行われ、暗号器43の正当性の確認もCPU11がソフトウェア16を実行することで開始される。

【0025】

メモリ12は例えば、RAMやNVRAMであり、CPU11がソフトウェア16の実行時に作業用のメモリとして使用する。ネットワーク装置13は、例えば、NIC(Network Interface Card)であり、不図示のLANと接続し、他の機器と通信することを可能にする。なお、TCP/IP、FTP、HTTP等の処理はOSやプログラムが行う。

【0026】

FAX装置14は、電話回線からのファクシミリデータを復調して画像データを生成しメモリ12に記憶したり、スキャナ32が読み取った画像データをファクシミリ用に変調して電話回線から出力する。電話回線でなくIPネットワークを使用してFAXを送受信することもできる。

【0027】

ASIC300は、プロッタ31、スキャナ32、CPU11、メモリ12、ネットワーク装置13、及び、FAX装置14と不図示のバスを介して接続されている。ASIC300は、内部バス29を介して接続されたプロッタ出力部25、回転器26、外部メディアI/F100、暗号器27、スキャナ入力部28、CPU I/F21、メモリI/F22、ネットワークI/F23及びFAX I/F24を有する。

【0028】

スキャナ入力部28は、予め取得しているスキャナ32のCCD特性に基づき、シェーディング補正処理、γ補正、フィルタ処理、RGB→RGB色変換処理等の各種の画像処理を画像データに施す。

【0029】

暗号器27は、画像データを暗号化・復号するICであり、本実施形態が対象とする暗号器43とは別に存在する。

【0030】

回転器26は、スキャナ32が読み取った画像データ又はプロッタ31へ転送される画像データに対して回転処理を施す。すなわち、読み取り時に傾いた画像の傾きを検出し、画素の配置を換えるなどして傾きを補正する。

【0031】

プロッタ出力部25は、HDD16に記憶されている画像データを読み出し、RGB→CMYKの画像データに変換し、また、ディザ処理を行いCMYK各色の2値化データをプロッタ31に転送する。

【0032】

CPU I/F21はCPU11とASIC300間で周波数の違いを吸収したり、データの入出力を行うバッファとして機能したり、ASIC300の各ブロック間でCPU11とデータの送受信を行う。

【0033】

メモリI/F22はメモリ12にアクセスするもので、例えばRW−DMAC45からメモリ12のデータの読み出し要求を受け付けると、メモリ12からデータを読み出しRW−DMAC45に出力し、RW−DMAC45からデータの書き込み要求を受け付けると、メモリ12にデータを書き込み、その結果をRW−DMAC45に通知する。

【0034】

ネットワークI/F23はLAN等のネットワークにアクセスし、ネットワーク上を流れるデータの宛先のMACアドレスを監視して、自機へのデータを選択的に取り込み、CPU等に割り込みして通知する。また、CPU11からデータの送信要求を受け付けると、自機と宛先のMACアドレスを追加してネットワークに出力する。

【0035】

FAX I/F24はFAX装置14がデータを受信するとCPU等に割り込みして通知する。また、CPU11からデータの送信要求があるとFAX番号等を指定してFAX装置14に出力する。

【0036】

外部メディアI/F100は、外部記憶メディア200にデータを書き込み、また、外部記憶メディア200からデータを読み出す装置である。外部記憶メディア200はフラッシュメモリ、FeRAM、MRAM、ReRAMなど不揮発メモリにより構成され、具体的にはUSBメモリ、SDメモリ、メモリースティック(登録商標)、スマートメディア、コンパクトフラッシュ(登録商標)等がある。

【0037】

外部メディアI/F100は、RW−DMAC45、データ振り分け器44、暗号器43、メディアアクセス制御部42、SRAM46、及び、IP41を有し、メディアアクセス制御部42は暗号器正当性確認部51を有する。

【0038】

RW−DMAC45は、CPU11を介さずに外部記憶メディア200からのデータの読み出し又はデータの書き込みを行う。

【0039】

読み出し:CPU11からRW−DMAC45に対し、例えばメモリ12に記憶されたデータのアドレスと書き込み対象のバイト数が設定される。RW−DMAC45は指定されたアドレスのデータを指定されたバイト数だけメモリ12から読み出し、暗号器43に入力する。ここで、データ振り分け器44は、正当性確認テスト(後述の暗号化テスト又は復号テスト)以外では作動しない(データパスがつながっていない)。暗号器43はデータを暗号化してメディアアクセス制御部42に入力するので、メディアアクセス制御部42はIP41を介して暗号化されたデータを外部記憶メディア200に記憶する。

【0040】

読み出し:CPU11からRW−DMAC45に対し、外部記憶メディア200のアドレスとバイト数(又はファイル名)が設定される。RW−DMAC45はメディアアクセス制御部42とIP41を利用して外部記憶メディア200から指定されたデータを読み出し、暗号器43に入力する。暗号器43は、暗号化されたデータを復号してRW−DMAC45に入力する(正当性確認テスト以外ではデータ振り分け器44は使用されない)。RW−DMAC45はメモリI/F22を介してデータをメモリ12に記憶する。RW−DMAC45はデータを読み出すとCPU11に割り込みして通知する。

【0041】

このように、外部メディアI/F100は原則的に全てのデータを暗号化し、また、読み出したデータを復号するが、CPU11からの制御により暗号化しないようにすることも可能になっている。

【0042】

メディアアクセス制御部42はSRAM46をバッファとして利用しながら、IP41の書き込み状況に基づきデータをIP41に入力する。IP41は決まった単位で外部記憶メディア200にデータを書き込んでいく。また、メディアアクセス制御部42はIP41が外部記憶メディア200から読み出したデータを暗号器43に出力し、暗号器43が復号している間、SRAMにデータを保持しておく。SRAMに空きがなくなるとIP41に読み出しを停止させる。なお、IP41は機能名ではないが、外部記憶メディア200への書き込みと読み出しを行うICである。

【0043】

図5では、外部メディアI/F100は画像形成装置に搭載されているが、画像形成装置に搭載されている必要はなく、情報処理装置や組み込み機器などに搭載されてもよい。

【0044】

〔メディアアクセス制御部〕

図6は、メディアアクセス制御部42の機能ブロック図の一例を示す。メディアアクセス制御部42は、I/F制御モジュール52、暗号器正当性確認部51、及び、テスト回路50を有する。

【0045】

テスト回路50は、モード選択部58、I/F制御部53、暗号器制御部55、正当性確認制御部54、テストデータサイズ記憶部59、完了通知部57、テストデータサイズカウンタ56、データ振り分け器制御部60、及び、DMAC制御部61を有している。

【0046】

モード選択部58は、暗号器テストを行うか否かを選択するスイッチの役割を有し、「通常動作」モード又は「暗号器テスト」モードを選択できる。「通常動作」モードは暗号器43の正当性確認テストを行なわない通常の転送を行うモードである。「暗号器テスト」モードは、さらに「暗号化テストモード」と「復号テストモード」がある。「暗号化テストモード」は、暗号器43の暗号化機能の正当性確認テストが行われるモードである。「復号テストモード」は、暗号器43の復号機能の正当性確認テストが行われるモードである。これらのモードの設定はソフトウェア16が行う。モード選択部58のモードによって、テスト回路50はパスの切換タイミングなどを制御する。

【0047】

I/F制御部53はモード選択部58が「暗号器テスト」モードを選択すると、I/F制御モジュール52を停止し、暗号器テストを動作させるためのパスを構築する。「通常動作」モードでは、RW−DMAC45と暗号器43、暗号器43とI/F制御モジュール52がそれぞれデータパスで接続されている。これに対し「暗号器テスト」モードになると、I/F制御部53は、RW−DMAC45とデータ振り分け部44、データ振り分け部44と暗号器43、データ振り分け部44と暗号器正当性確認部51、暗号器43と暗号器正当性確認部51、をそれぞれデータパスで接続する。

【0048】

なお、暗号器43を経由しないデータ振り分け部44と暗号器正当性確認部51のデータパスをスルーパス47という。データ振り分け部44は、スルーパス47とパス48を択一的に選択してデータの送信先を切り換える。

【0049】

暗号器制御部55は、暗号器43の動作モードを選択する機能で、「暗号化」モード、「復号」モード、又は、「スルー」モードの3つの動作モードを選択できる。

【0050】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を読み込むか否かを制御する。また、正当性確認制御部54は暗号器正当性確認部51のスルー設定をON・OFFに制御する。

【0051】

テストデータサイズ記憶部59はソフトウェア16を実行するCPU11により設定され、テストデータのサイズを保持する。

【0052】

完了通知部57は、テスト回路50の動作が完了したことをCPU11に通知する。

【0053】

テストデータサイズカウンタ56は、期待値データと暗号化又は復号されたINPUTデータとの比較が終わったデータ数を累積して保持する。テストデータサイズカウンタ56とテストデータサイズ記憶部59の値が同じになることが、正当性確認テストの終了条件になる。

【0054】

データ振り分け器制御部60は、データ振り分け器44と暗号器正当性確認部51のスルーパス47と、データ振り分け器44と暗号器43のパス48のどちらを有効にするかを切り換える(暗号器を通らないパス、暗号器を通るパスを切り換える)。

【0055】

DMAC制御部61は、RW−DMACの起動と、RW−DMAC45がデータを書き込むのか、データを読み出すのかを切り換える。

【0056】

図7は、テストデータを模式的に説明する図の一例である。本実施形態ではテストデータに任意のデータ量ずつ期待値データとINPUTデータを交互に配置する。従来は、INPUTデータは最初から最後まで連続しており、期待値データも最初から最後まで連続していた。本実施例では、期待値データとINPUTデータを従来のようにそれぞれ独立して持たせず、例えば1つのファイルのように保持する。

【0057】

図では128ビットずつ交互に配置されているが、期待値データとINPUTデータでビット数が同じであり、かつ、最初から最後まで期待値データとINPUTデータのビット数が一定であればよい。

【0058】

また、期待値データとINPUTデータは、期待値データの方がINPUTデータよりも先のアドレスに記憶されている。したがって、期待値データ→INPUTデータの順に読み出される。

【0059】

期待値データとINPUTデータの配置は逆にすることも可能であるが、この場合、後述するデータパスの制御を期待値データとINPUTデータの配置に合わせて修正する。

【0060】

〔比較手順〕

図8は、期待値データとINPUTデータが振り分けられる様子を説明する図の一例である。

RW−DMAC45はメモリ12から期待値データとINPUTデータをアドレス順に読み出す。したがって、決まったデータ長毎に期待値データとINPUTデータが順番に読み出される。

【0061】

データ振り分け器44にはこのデータ長が設定されている。データ振り分け器44は、RW−DMAC45が読み出した期待値データとINPUTデータから、データ長毎に出力先を振り分ける。例えば、最初の128ビットは暗号器正当性確認部51に、次の128ビットは暗号器43に、次の128ビットは暗号器正当性確認部51に、次の128ビットは暗号器43に…、のように振り分ける。こうすることで、暗号器正当性確認部51には期待値データのみがアドレス順に連続して供給され、暗号器43にはINPUTデータのみがアドレス順に連続して供給される。

【0062】

暗号器43は、予め決まったデータ量をブロックにして、ブロック単位(例えば256ビット)で暗号化を行う。図では「結果1」と記されたブロックが暗号化されたデータである。暗号器正当性確認部51は、期待値データと暗号化されたINPUTデータをブロック単位で比較する。

【0063】

図9は、暗号器正当性確認部51による期待値データと暗号化されたINPUTデータの比較を説明する図の一例である。

【0064】

暗号器43はINPUTデータを暗号化するための時間が必要なので、期待値データの方が先に暗号器正当性確認部51に入力される。このため、暗号器正当性確認部51は、期待値データをラッチする。この後、暗号器43がINPUTデータを暗号化すると、暗号化されたINPUTデータが暗号器正当性確認部51に入力される。したがって、暗号器正当性確認部51には、図9に示すように期待値データ、暗号化されたINPUTデータの順番で、1ブロックずつ入力される。

【0065】

暗号器正当性確認部51は1ブロック分の期待値データをラッチしておき、その後、暗号器43から暗号化されたINPUTデータが入力されると、両者のEX-OR(排他的論理和)を取る。排他的論理和は、2つの入力値が異なる場合に1を出力し、それ

以外の場合(入力値が同じとき)には0を出力する。したがって、EX-ORの結果が全て0の場合、そのブロックの正当性が確認されたと判断され、暗号器正当性確認部51は次のブロックの処理に移ることができる。

【0066】

期待値データ、暗号化されたINPUTデータが交互に入力されるが、期待値データが暗号器正当性確認部51に入力されてから、暗号器43が暗号化されたINPUTデータを入力するまでにレイテンシーが発生する。このため、図9の比較において期待値データの入力→暗号化されたINPUTデータの入力、の順番は崩れることはなく比較することが可能である。

【0067】

〔動作手順〕

図10は、暗号器43の正当性確認テストの全体手順を示すフローチャート図の一例である。本実施例では画像形成装置の電源オンの際、正当性が確認されるものとする。

【0068】

例えば、ユーザが画像形成装置の電源をオンにする(S10)。CPU11はIPL(Initial Program Loader)を実行して、IPLが予め定められソフトウェア16をCPU11に実行させる。本実施例ではこのソフトウェア16が正当性を確認する処理を行う。

【0069】

ソフトウェア16はモード選択部58を「暗号器テスト」モードに設定する(S20)。

【0070】

ソフトウェア16は、交互に配置されているテストデータをメモリ12に用意する(S30)。具体的には、テストデータはソフトウェア16と一体にコード化されているか又はテーブル状にHDD16に記憶されている。ソフトウェア16は変数名などを介して指定するアドレスからテストデータをHDD16等から読み出しメモリ12に記憶させる。

【0071】

ソフトウェア16は、メモリ12上に用意した期待値データとINPUTデータの合計のデータサイズをテストデータサイズ記憶部59に設定する(S40)。

【0072】

この後、暗号器正当性確認部51はテスト回路50を起動し、テスト回路50は起動すると、暗号器43の正当性のテストを開始する(S50)。暗号器43の正当性のテストについて詳細な手順は後述する。

【0073】

暗号器正当性確認部51は期待値データと暗号器43からの入力されたINPUTデータの比較を、完了通知部57から完了通知が行われるまで行う(S60)。暗号器43が交換されていたり、暗号器43が故障していなければ、暗号器正当性確認部51は期待値データと暗号化されたINPUTデータが一致したと判定する(S70)。

【0074】

暗号器正当性確認部51が、期待値データと暗号化されたINPUTデータの比較の結果が不一致であると判定すると(S70のYes)、ソフトウェア16がエラー処理を行う(S80)。エラー処理の内容は、例えば、再度のテストを行うこと、再度のテストを行っても不一致の場合はエラーメッセージを表示すること等であるが、詳細は省略する。

【0075】

図の処理は、暗号器43の暗号化テストと復号テストの両方が完了すると終了する(S90)。例えば、復号テストがまだ完了していない場合、ソフトウェア16は、テスト回路50の完了通知部57から完了通知(暗号化完了)を受けると、暗号器43のテストモードを復号に設定し(S100)、再度、テストデータの準備、データサイズの設定を行い、テスト回路50に処理を実行させる。

【0076】

復号の正当性確認テストが完了すると、テスト回路50は復号の正当性確認テストの完了通知をソフトウェア16に通知する。テスト回路50から完了通知(復号完了)を受けると、暗号器43が正常に動作していると判断できるため、図10の正当性確認テストは終了する。

【0077】

<暗号化テスト>

図11は、テスト回路50の動作手順を詳細な示すフローチャート図の一例である。

【0078】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「暗号化テスト」モードが選択されているか否かを判定する(S110)。

【0079】

モード選択部58が暗号化テストモードに設定されていない場合(S110のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図11の処理は終了する。

【0080】

モード選択部58が暗号化テストモードに設定されている場合(S110のYes)、テスト回路50は暗号化テストを行う。暗号化テストは次の手順で行われる。

【0081】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S120)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0082】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S130)。また、暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、DMAC制御部61はRW−DMAC45に転送サイズを設定する(S140)。

【0083】

暗号器制御部55は、暗号器43を暗号化モードに設定する(S150)。

【0084】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S160)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0085】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S170)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44と暗号器正当性確認部51を結ぶスルーパス47、データ振り分け器44と暗号器43を結ぶパス48、及び、暗号器43から暗号器正当性確認部51へのパス、を構築する。また、使用しないI/F制御モジュール52を停止させる。

【0086】

次に、DMAC制御部61はRW−DMAC45を起動する(S180)。これにより、RW−DMAC45はデータサイズカウンタがテストデータサイズ記憶部59に記憶されたデータサイズを読み出すまでメモリ12からテストデータの読み出しを繰り返す。

【0087】

まず、データ振り分け器44は、データ振り分け制御部60の制御により、パス48をスルーパス47へ変更する(S190)。スルーパス47は暗号器43でなく暗号器正当性確認部51に出力するパスである。

【0088】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S200)。1ブロックには、期待値データとINPUTデータが含まれている。

【0089】

データ振り分け器44は、期待値データのみをスルーパス47へ出力する(S210)。これにより、暗号器正当性確認部51に1ブロック分の期待値データが記憶される(S220)。

【0090】

1ブロック分の期待値データを転送すると、データ振り分け器44はデータ振り分け制御部60の制御により、スルーパス47をパス48に切り替える(S230)。データ振り分け器44は1ブロック分のINPUTデータを暗号器43へ入力する(S240)。

【0091】

暗号器43は転送されたINPUTデータを暗号化する(S250)。暗号器43は、暗号化したINPUTデータを暗号器正当性確認部51に入力する(S260)。ここで、暗号器正当性確認部51は上記のように排他的論理和を取る。

【0092】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分の暗号化されたINPUTデータが転送されたことを検出して、データ比較フラグをONにする(S270)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0093】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S280)。どれか1bitでも1が出力されていた場合(S280のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S290)。

【0094】

ALLゼロの場合(S280のYes)、比較が正常に完了したので、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S300)。

【0095】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S310)。

【0096】

以上のように、テスト回路50は、テストデータの読み込み、パスの設定、比較結果の判定、データサイズの加算を、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになるまで繰り返す。完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、暗号化テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S320)。これにより暗号化テストが完了する。

【0097】

<復号テスト>

図12は、画像形成装置の構成図から、要部として外部メディアI/F100を取り出した図の一例である。図12において図5と同一部の説明は省略する。外部メディアI/F100の構成は暗号化の場合と同様だが、データパスが異なる。

(1)復号テストの場合、データ振り分け器44はテストデータの期待値データを、スルーパス47を介して暗号器正当性確認部51に入力する。

(2)次に、データ振り分け器44はテストデータのうちINPUTデータ(暗号器への入力される復号対象のデータ)を、スルーパス47を介して暗号器正当性確認部51に転送する。暗号器正当性確認部51はそのままINPUTデータを暗号器43に入力する。

(3)暗号器43は、INPUTデータを復号してデータ振り分け器44に入力する。

(4)データ振り分け器44は再度、スルーパス47を介して復号されたINPUTデータを暗号器正当性確認部51に入力する。

(5)暗号器正当性確認部51は、期待値データと復号されたINPUTデータを比較する。

【0098】

メモリ12から読み出したINPUTデータを直接、暗号器43に入力しないのは、暗号器43はメディアアクセス制御部42から受け取ったデータを復号するように設計されているためである。このようにスルーパス47を利用することで、復号テストも可能になる。

【0099】

〔復号時の動作手順〕

図13は、復号テストにおけるテスト回路50の動作手順を示すフローチャート図の一例である。復号時には、正当性確認制御部54が暗号器正当性確認部51のスルー設定をON・OFFする。暗号器正当性確認部51のスルー設定がOFFの場合、暗号器正当性確認部51はデータを保持し、暗号器正当性確認部51のスルー設定がONの場合、暗号器正当性確認部51はデータを保持することなく暗号器正当性確認部51と暗号器43を直結する。

【0100】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「復号テスト」モードが選択されているか否かを判定する(S410)。

【0101】

モード選択部58が復号テストモードに設定されていない場合(S410のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図13の処理は終了する。

【0102】

モード選択部58が復号テストモードに設定されている場合(S410のYes)、テスト回路50は復号テストを行う。復号テストは次の手順で行われる。

【0103】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S420)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0104】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S430)。暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、RW−DMAC45に転送サイズを設定する(S440)。

【0105】

暗号器制御部55は、暗号器43を復号モードに設定する(S450)。

【0106】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S460)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0107】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S470)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44から暗号器正当性確認部51へのスルーパス47、暗号器正当性確認部51から暗号器43へのパス、暗号器43からデータ振り分け器44へのパスを構築し、I/F制御モジュール52を停止させる。

【0108】

次に、DMAC制御部61はRW−DMAC45を起動する(S480)。

【0109】

正当性確認制御部54は、暗号器正当性確認部51のスルー設定をOFFに設定する(S490)。これにより、暗号器正当性確認部51はデータを保持することができる。

【0110】

RW−DMAC45はデータサイズカウンタがテストデータサイズ記憶部59に記憶されたデータサイズを読み出すまでメモリ12からテストデータの読み出しを繰り返す。

【0111】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S500)。1ブロックには、期待値データとINPUTデータが含まれている。

【0112】

データ振り分け器44は、期待値データのみをスルーパス47へ出力する(S510)。これにより、暗号器正当性確認部51に1ブロック分の期待値データが記憶される(S520)。

【0113】

1ブロック分の期待値データを転送すると、正当性確認制御部54は暗号器正当性確認部51のスルー設定をONに設定する(S530)。

【0114】

次に、データ振り分け器44は1ブロック分のINPUTデータを、スルーパス47を介して暗号器正当性確認部51に入力する(S540)。暗号器正当性確認部51はスルー設定がONなので、INPUTデータは暗号器43に入力される(S550)。

【0115】

暗号器43は転送されたINPUTデータを復号する(S560)。暗号器43は、復号されたINPUTデータをデータ振り分け器44に入力する。

【0116】

正当性確認制御部54は、復号されたINPUTデータを蓄積するため暗号器正当性確認部51のスルー設定をOFFに設定する(S570)。

【0117】

データ振り分け器44は、復号されたINPUTデータを暗号器正当性確認部51に入力する(S580)。暗号器正当性確認部51は復号されたINPUTデータを蓄積する(S590)。ここで、暗号器正当性確認部51は上記のように排他的論理和を取る。

【0118】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分の復号されたINPUTデータが転送されたことを検出して、データ比較フラグをONにする(S600)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0119】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S610)。どれか1bitでも1が出力されていた場合(S610のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S620)。

【0120】

ALLゼロの場合(S610のYes)、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S630)。

【0121】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S640)。

【0122】

完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、復号テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S650)。これにより復号データが完了する。

【0123】

以上説明したように、本実施例の外部メディアI/F100は、暗号器43を通過した直後に暗号器正当性確認部51が正当性を確認でき、外部記憶メディア200に書き込む必要がないので、ユーザの待ち時間を短縮できる。また、復号時も外部記憶メディア200に書き込む必要がないので暗号器43の正当性を確認する時間を短縮できる。

【実施例2】

【0124】

実施例1にて説明したように、暗号化テスト用のテストデータ、復号テスト用のテストデータを用意することが好ましいが、必ずしも二種類のテストデータを用意する必要はない。本実施例では、いずれか一方のテストデータにより暗号化テストと復号テストの両方が可能な外部メディアI/F100について説明する。

【0125】

こうすることで、メモリ領域を節約できたり、何らかの理由で暗号化テスト又は復号テストのどちらかのテストデータのみしか用意できない場合にも暗号化テストと復号テストの両方が可能になる。

【0126】

図14は、暗号化テスト及び復号テストの際のデータフローとデータ間の関係を説明する図の一例である。

【0127】

中央に暗号器43があり、暗号器43が出力した暗号化したデータは「暗号データ」、暗号器43が復号したデータは「復号データ」である。

(1)暗号器43は、「復号データ」の入力値を暗号化する。これにより暗号化期待値が得られる。

(2)暗号器43は、「暗号データ」の入力値を復号する。これにより復号期待値が得られる。

【0128】

暗号器43が暗号化したデータは、同じ暗号器43が復号することで、元の入力値に戻る。したがって、「復号データ」の入力値と復号期待値とは同じものであり、「暗号データ」の暗号化期待値と入力値とは同じものである。

【0129】

実施例1では、「復号データ」の入力値と「暗号データ」の暗号化期待値が暗号化テストのテストデータであり、「暗号データ」の入力値と「復号データ」の復号期待値が復号テストのテストデータである。したがって、暗号化テストと復号テストにおいて、期待値データとINPUTデータの関係を逆にするだけで、暗号化テストと復号テストの両方が可能になる。

【0130】

〔構成例〕

図15は、メディアアクセス制御部42の機能ブロック図の一例を示す。図15において図6と同一部の説明は省略する。

【0131】

図15のメディアアクセス制御部42は、データ振り分け器44がテストデータ保持部62を有し、テスト回路50がテストデータ状態通知部63を有する。テストデータ保持部62は、暗号器43に出力するデータを一時的に保持する。テストデータ状態通知部63は、暗号用又は復号用のテストデータの有無をデータ振り分け器44に通知する。

【0132】

ソフトウェア16は、暗号化用のテストデータと復号用のテストデータのうち、どちらを用意しているかをテストデータ状態通知部63に設定しておく。

【0133】

〔動作手順 暗号化テスト〕

まず、暗号化時の手順について説明するが、復号時の手順から実行することも可能である。

【0134】

図16は、データの流れを模式的に示す図の一例を、図17は、ソフトウェア16が外部メディアI/F100の暗号器43の暗号機能の正当性を確認する手順を示すフローチャート図の一例をそれぞれ示す。図16の矢印線のステップ番号は図17のステップ番号と対応している。

【0135】

図16に示すように、データ振り分け器が期待値データをいったん保持しておき、先にIUPUTデータを暗号器正当性確認部51に入力する。そして、データ振り分け器は保持している期待値データを暗号器にて暗号化した後、暗号器正当性確認部51に入力する。こうすることで、復号テスト用のテストデータで暗号化テストが可能になる。

【0136】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「暗号化テスト」モードが選択されているか否かを判定する(S710)。

【0137】

モード選択部58が暗号化テストモードに設定されていない場合(S710のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図17の処理は終了する。

【0138】

モード選択部58が暗号化テストモードに設定されている場合(S710のYes)、テスト回路50は暗号化テストを行う。

【0139】

テスト回路50はまず、テストデータ状態通知部63に暗号化テストのテストデータが用意されているか否かを問い合わせる(S720)。暗号化テストのテストデータが用意されている場合(S730のYes)、すでに説明した図11の暗号化テストが実行される(S740)。

【0140】

復号テストのテストデータしか用意されていない場合(S730のNo)、暗号化テスト用のデータが用意されていない場合の暗号化テストを実施する。暗号化テストのテストデータが用意されていない場合の暗号化テストは次の手順で行われる。

【0141】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S750)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0142】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S760)。暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、RW−DMAC45に転送サイズを設定する(S770)。

【0143】

暗号器制御部55は、暗号器43を暗号化モードに設定する(S780)。

【0144】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S790)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0145】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S800)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44と暗号器正当性確認部51を結ぶスルーパス47、データ振り分け器44と暗号器43を結ぶパス48、及び、暗号器正当性確認部51から暗号器43へのパス、を構築する。また、使用しないI/F制御モジュール52を停止させる。

【0146】

次に、DMAC制御部61はRW−DMAC45を起動する(S810)。

【0147】

データ振り分け器44は、パス48をスルーパス47へ切り換える(S820)。

【0148】

また、データ振り分け器44はテストデータ保持部62のデータ蓄積モードをONに設定する(S830)。

【0149】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S840)。1ブロックには、期待値データとINPUTデータが含まれているが、これらは復号テスト用のテストデータである。まず、復号テスト用の期待値データのみをデータ振り分け器44のテストデータ保持部62に蓄積させていく(S850)。

【0150】

データ振り分け器44は、1ブロック分の期待値データが蓄積された後、データ蓄積モードをOFFに切り替える(S860)。

【0151】

次に、データ振り分け器44は、復号テスト用のテストデータのINPUTデータを1ブロック分、スルーパス47へ転送する(S870)。暗号器正当性確認部51はINPUTデータを蓄積する(S880)。復号用テストデータのINPUTデータは、暗号化された状態である。

【0152】

データ蓄積完了後、データ振り分け器44がスルーパス47をパス48(暗号器側)に切り替える(S890)。

【0153】

データ振り分け器44はテストデータ保持部62に蓄積された復号用テストデータの期待値データを暗号器43へ入力する(S900)。

【0154】

暗号器43は期待値データを暗号化する(S910)。復号用のテストデータの期待値データが暗号化されるので、このデータは暗号化された状態である。

【0155】

暗号器43は、暗号化した復号用テストデータの期待値データを暗号器正当性確認部51に入力する(S920)。暗号器正当性確認部51は上記のように2つのデータの排他的論理和を取る。

【0156】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分の暗号化された期待値データが転送されたことを検出して、データ比較フラグをONにする(S930)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0157】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S940)。どれか1bitでも1が出力されていた場合(S940のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S950)。

【0158】

ALLゼロの場合(S940のYes)、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S960)。

【0159】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S970)。

【0160】

完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、復号テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S980)。

【0161】

以上のように、ソフトウェア16が復号用のテストデータしか有していなくても、テストデータ保持部62がテストデータを保持しておき、復号テスト用の期待値データを暗号器43に、復号テスト用のINPUTデータを暗号器正当性確認部51に入力することで、暗号器43の暗号化テストが可能になる。

【0162】

〔動作手順 復号テスト〕

図18は、復号テストにおけるデータの流れを模式的に示す図の一例を、図19は、ソフトウェア16が外部メディアI/F100の暗号器43の復号機能の正当性を確認する手順を示すフローチャート図の一例である。

【0163】

図18に示すように、期待値データは暗号器正当性確認部51をスルーして暗号器により復号された後、データ振り分け器にいったん保持される。次に、データ振り分け器はIUPUTデータを暗号器正当性確認部51に入力する。そして、データ振り分け器は保持している復号された期待値データを暗号器正当性確認部51に入力する。こうすることで、暗号テスト用のテストデータで復号テストが可能になる。

【0164】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「復号テスト」モードが選択されているか否かを判定する(S1010)。

【0165】

モード選択部58が復号テストモードに設定されていない場合(S1010のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図19の処理は終了する。

【0166】

モード選択部58が暗号化テストモードに設定されている場合(S1010のYes)、テスト回路50は復号のテストを行う。テスト回路50は、まず、テストデータ状態通知部63に復号テスト用のテストデータが用意されているか否かを問い合わせる(S1020)。

【0167】

復号テストのテストデータが用意されている場合(S1030のYes)、すでに説明した図13の復号テストを実行すればよい(S1040)。

【0168】

暗号化用のテストデータしか用意されていない場合(S1030のNo)、テスト回路50は復号用のテストデータが用意されていない場合の復号テストを実行する。復号用のテストデータが用意されていない場合の復号テストは次の手順で行われる。

【0169】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S1050)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0170】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S1060)。暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、RW−DMAC45に転送サイズを設定する(S1070)。

【0171】

暗号器制御部55は、暗号器43を復号モードに設定する(S1080)。

【0172】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S1090)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0173】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S1100)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44から暗号器正当性確認部51へのスルーパス47、暗号器正当性確認部51から暗号器43へのパス、暗号器43からデータ振り分け器44へのパスを構築し、I/F制御モジュール52を停止させる。

【0174】

次に、DMAC制御部61はRW−DMAC45を起動する(S1110)。

【0175】

正当性確認制御部54は、暗号器正当性確認部51のスルー設定をONに設定する(S1120)。

【0176】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S1130)。1ブロックには、期待値データとINPUTデータが含まれているが、これらは暗号化用のテストデータである。

【0177】

まず、データ振り分け器44は暗号化テストのテストデータの期待値データのみをスルーパス47へ出力する(S1140)。暗号化テストのテストデータの期待値データは、暗号化された状態である。

【0178】

暗号器正当性確認部51のスルー設定はONなので、期待値データは暗号器43にそのまま入力される(S1150)。

【0179】

暗号器43は期待値データを復号する(S1160)。暗号化テストのテストデータの期待値データは暗号化されているので、復号により暗号化されていない状態になる。

【0180】

データ振り分け器44は、復号された期待値データをテストデータ保持部62に蓄積させていく(S1170)。

【0181】

次に、正当性確認制御部54は、暗号器正当性確認部51のスルー設定をOFFに設定する(S1180)。

【0182】

データ振り分け器44は、暗号化テストのテストデータのINPUTデータを暗号器正当性確認部51に入力する(S1190)。暗号化テストのテストデータのINPUTデータは暗号化される前の状態である。

【0183】

暗号器正当性確認部51は、INPUTデータを保持する(S1200)。

【0184】

次に、データ振り分け器44は、テストデータ保持部62に記憶している復号された期待値データを、スルーパス47を介して暗号器正当性確認部51に入力する(S1210)。

【0185】

暗号器正当性確認部51は、復号された期待値データを取得する(S1220)。

【0186】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分のデータが転送されたことを検出して、データ比較フラグをONにする(S1230)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0187】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S1240)。どれか1bitでも1が出力されていた場合(S1240のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S1250)。

【0188】

ALLゼロの場合(S1240のYes)、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S1260)。

【0189】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S1270)。

【0190】

完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、復号テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S1280)。

【0191】

以上のように、ソフトウェア16が暗号化テストのテストデータしか有していなくても、復号テストが可能である。テストデータ保持部62が暗号化テスト用の期待値データを暗号器正当性確認部51経由で暗号器に復号させテストデータ保持部62で保持しておく。暗号化テスト用のINPUTデータを暗号器正当性確認部51に出力し、次に、テストデータ保持部62で保持している復号された期待値データを暗号器正当性確認部51に入力することで、暗号器43の復号テストが可能になる。

【符号の説明】

【0192】

11 CPU

12 メモリ

16 ソフトウェア

41 IP

42 メディアアクセス制御部

43 暗号器

44 データ振り分け部

45 RW−DMAC

51 暗号器正当性確認部

52 I/F制御モジュール

53 I/F制御部

54 正当性確認制御部

55 暗号器制御部

56 データサイズカウンタ

57 完了通知部

58 モード選択部

59 テストデータサイズ記憶部

60 データ振り分け制御部

61 DMAC制御部

100 外部メディアI/F

200 外部記憶メディア

【先行技術文献】

【特許文献】

【0193】

【特許文献1】特開2007−215028号公報

【技術分野】

【0001】

本発明は、外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアインタフェース装置に関し、特に、暗号化又は復号が可能な暗号器を備えた外部メディアインタフェース装置に関する。

【背景技術】

【0002】

デジタルデータを記憶する多様な記憶媒体が安価に利用できるようになっている。しかし、記憶媒体が外部に流出すると膨大なデジタルデータが漏洩してしまうおそれがある。このため、セキュリティ対策として、デジタルデータを暗号化して記憶することが行われている(例えば、特許文献1参照。)。特許文献1には、入力されたデータを任意の数の記憶装置に分散して、転送途中のデータブロックを、記憶装置毎に異なる暗号鍵を用いて暗号化するRAIDコントローラが開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0003】

CPU等が脱着可能な外部記憶メディアにデジタルデータを記録する場合も、同様に、デジタルデータを暗号化することが考えられる。

【0004】

図1は、従来の外部メディアI/F100の一例を示す。図1において外部メディアI/F100は画像形成装置に搭載されることが想定されているが、外部メディアI/F以外の機能ブロックについて後に詳述する。

【0005】

外部メディアI/F100は外部記憶メディア200へのアクセス制御を行う。外部メディアI/F100は、リードライト兼用のDMAコントローラ(以下、RW−DMAC104)、暗号器103、メディアアクセス制御部102、SRAM105、及び、外部メディア用のIP(Intellectual Property)101、を有する。RW−DMAC104はCPU11を介さずに外部記憶メディア200からのデータ読み出し又はデータの書き込みを行う。暗号器103はRW−DMAC104から受け取ったデジタルデータの暗号化を行ったり、外部記憶メディア200から読み込まれた暗号化データを復号してRW−DMAC104に渡したりする。

【0006】

メディアアクセス制御部102はIP101を制御する。IP101は外部記憶メディア200にアクセスを行う専用の回路である。SRAM105は外部記憶メディア200へ転送する際、及び、外部記憶メディア200からの読み込み時に、一次バッファとして利用される。

【0007】

例えば、暗号化モジュールに関するセキュリティ要件を規定した規格としてFIPS140-2がある。FIPS140-2(FEDERAL INFORMATION PROCESSING STANDARDS PUBLICATION )は、「暗号モジュールが(電源OFF、リセット、リブート等の後で)電源投入された時、その暗号モジュールによって必ず暗号器の自己テスト(正当性確認テスト)を実行されなければならない」と定められている。

【0008】

図2は、FIPS140-2に対応した正当性確認テストの手順を説明する図の一例である。図2の矢印線106に示すように、暗号器103はメモリ12のINPUTデータを暗号化して外部記憶メディア200へ一度出力し、それをRW−DMAC104が再度メモリ12へ読み込む。CPU11が実行するソフトウェアは予め用意されている期待値データと読み出した暗号化されているINPUTデータが一致するか否かにより暗号器103の正当性を確認する。

【0009】

図3は、この正当性確認テストを模式的に説明する図の一例である。画像形成装置のメーカ等は、ソフトウェアや不揮発の記憶装置に予め期待値データと暗号器103へ入力するためのINPUTデータを記憶させておく。

(i) RW−DMAC104はINPUTデータを暗号器103に入力する。

(ii) 暗号器103はINPUTデータを暗号化し、メディアアクセス制御部102に入力する。この時、メディアアクセス制御部102は、外部記憶メディア200の起動処理が完了するまで、ASIC内のSRAM105で保持する。

(iii) 外部記憶メディア200が起動するとメディアアクセス制御部102はIP101を利用して一度外部記憶メディア200へ蓄積する。

(iv) メディアアクセス制御部102は、暗号化されたINPUTデータを読み出す。この過程では、暗号器103を介さずにINPUTデータがRW−DMAC104に出力され、RW−DMAC104は暗号化されたINPUTデータをメモリ12に記憶する。

(v) CPU11は、予め用意されていた期待値データと、暗号化されたINPUTデータとを比較し、暗号器103の正当性を確認する。

【0010】

ここで、(ii)に示すように、外部記憶メディア200によっては駆動系が安定動作するまで若干の時間を要するものがある。また、外部記憶メディア200によっては動作前に初期化を行う必要があるものもある。これらの処理には比較的時間がかかることが知られており、起動時にこの処理を行うと、ユーザが利用開始できるまでの時間(起動時間)が大幅に長くなってしまい、ユーザの利便性を損なうといった問題があった。

【0011】

本発明は、上記課題に鑑み、正当性確認テストを行う際の時間を短縮する外部メディアインタフェース装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、記憶手段からデータを読み出し、また、記憶手段へデータを書き込む記憶手段アクセス制御手段と、外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアアクセス手段と、前記外部メディアアクセス手段が前記外部記憶メディアに書き込むデータを暗号化し、前記外部メディアアクセス手段が前記外部記憶メディアから読み出したデータを復号する暗号器と、を有する外部メディアインタフェース装置であって、前記暗号器の暗号化機能と復号機能のどちらかのテストモードの設定を受け付けるテストモード設定受付手段と、前記テストモード設定受付手段が前記暗号器の暗号化機能のテストモードを受け付けた場合、前記記憶手段アクセス制御手段が読み出したテストデータの送信先を前記データ比較手段又は前記暗号器に振り分けるデータ振り分け手段と、前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するデータ比較手段と、前記記憶手段アクセス制御手段と前記データ振り分け手段、前記データ振り分け手段と前記データ比較手段、前記データ振り分け手段と前記暗号器、及び、前記暗号器と前記データ比較手段、の間にデータパスを構築するパス構築手段と、を有する。

【発明の効果】

【0013】

正当性確認テストを行う際の時間を短縮する外部メディアインタフェース装置を提供することができる。

【図面の簡単な説明】

【0014】

【図1】従来の外部メディアI/Fの一例を示す図である。

【図2】FIPS140-2に対応した生成性確認テストの手順を説明する図の一例である。

【図3】正当性確認テストを模式的に説明する図の一例である。

【図4】外部記憶メディアの正当性確認テストの概略を説明する図の一例である。

【図5】画像形成装置の概略構成図の一例である。

【図6】メディアアクセス制御部の機能ブロック図の一例である。

【図7】テストデータを模式的に説明する図の一例である。

【図8】期待値データとINPUTデータが振り分けられる様子を説明する図の一例である。

【図9】暗号器正当性確認部による期待値データとINPUTデータの比較を説明する図の一例である。

【図10】ソフトウェアが外部メディアI/Fの暗号器の正当性を確認する手順を示すフローチャート図の一例である。

【図11】テスト回路の動作手順を示すフローチャート図の一例である。

【図12】画像形成装置の構成図から、要部として外部メディアI/Fを取り出した図の一例である。

【図13】復号時におけるテスト回路の動作手順を示すフローチャート図の一例である。

【図14】暗号化テスト及び復号テストの際のデータフローとデータ間の関係を説明する図の一例である。

【図15】メディアアクセス制御部の機能ブロック図の一例である。

【図16】暗号化テストにおけるデータの流れを模式的に示す図の一例である。

【図17】ソフトウェアが外部メディアI/Fの暗号器の正当性を確認する手順を示すフローチャート図の一例である。

【図18】復号テストにおけるデータの流れを模式的に示す図の一例である。

【図19】ソフトウェアが外部メディアI/Fの暗号器の正当性を確認する手順を示すフローチャート図の一例である。

【発明を実施するための形態】

【0015】

以下、本発明を実施するための形態について図面を参照しながら説明する。

【実施例1】

【0016】

図4は、本実施形態の外部記憶メディア200の正当性確認テストの概略を説明する図の一例である。本実施形態の外部メディアI/F100は、新たに、暗号器正当性確認部51、及び、データ振り分け器44を有する。

(1)データ振り分け器44はメモリに記憶されているINPUTデータと期待値データ(暗号化結果or復号結果)のデータパスを切り換える。詳細は後述するが、暗号化機能のテストを例に説明する。

(2)データ振り分け器44は、暗号器43を介せずに、INPUTデータを暗号器43に入力する。同様に、期待値データを暗号器正当性確認部51に入力する。暗号器43は例えばINPUTデータを暗号化して暗号器正当性確認部51に入力する。

(3)暗号器正当性確認部51は、暗号器43が暗号化したINPUTデータと期待値データを比較する。

【0017】

したがって、暗号器正当性確認部51は、暗号器43が暗号化したINPUTデータをメモリに書き込む必要性をなくし、暗号器43が正当か否かを判定できるようになっている。

【0018】

図4のような正当性確認テストによれば、暗号器43を通過した直後に暗号器正当性確認部51が正当性を確認可能となるので、ユーザの待ち時間を短縮できる。

【0019】

なお以下では、INPUTデータと期待値データの組を「テストデータ」という。

【0020】

〔構成例〕

図5は、画像形成装置の概略構成図の一例を示す。画像形成装置は、プロッタ31、スキャナ32、ASIC300、HDD16、CPU11、メモリ12、ネットワーク装置13、及び、FAX装置14を有する。

【0021】

プロッタ31は、例えば、電子写真方式の印刷装置であり、CMYKの画像データに基づき、トナー画像を用紙に定着することで画像データを出力する。なお、白黒のプロッタでもよいし、液滴を塗布することで用紙に画像を形成するインクジェット型のプロッタでもよい。

【0022】

スキャナ32は、例えば、CCD(Charge Coupled Device )を利用したカラーラインセンサにより原稿を1ライン毎主走査方向に読み取り、原稿を副走査方向に移動して、RGB毎に所定の階調を備えた画像データを生成する。

【0023】

HDD16は、画像データを記憶するストレージとして使用され、また、プログラムやフォントデータなどの静的なデータを記憶している。HDD16はASIC300内の暗号器43の正当性を確認する処理を行うプログラムを記憶しており、図ではソフトウェア16として示されている。

【0024】

CPU11は、CPU11以外のブロックを支配して画像形成装置の全体を制御する。CPU11が実行する制御はプログラムを実行することで行われ、暗号器43の正当性の確認もCPU11がソフトウェア16を実行することで開始される。

【0025】

メモリ12は例えば、RAMやNVRAMであり、CPU11がソフトウェア16の実行時に作業用のメモリとして使用する。ネットワーク装置13は、例えば、NIC(Network Interface Card)であり、不図示のLANと接続し、他の機器と通信することを可能にする。なお、TCP/IP、FTP、HTTP等の処理はOSやプログラムが行う。

【0026】

FAX装置14は、電話回線からのファクシミリデータを復調して画像データを生成しメモリ12に記憶したり、スキャナ32が読み取った画像データをファクシミリ用に変調して電話回線から出力する。電話回線でなくIPネットワークを使用してFAXを送受信することもできる。

【0027】

ASIC300は、プロッタ31、スキャナ32、CPU11、メモリ12、ネットワーク装置13、及び、FAX装置14と不図示のバスを介して接続されている。ASIC300は、内部バス29を介して接続されたプロッタ出力部25、回転器26、外部メディアI/F100、暗号器27、スキャナ入力部28、CPU I/F21、メモリI/F22、ネットワークI/F23及びFAX I/F24を有する。

【0028】

スキャナ入力部28は、予め取得しているスキャナ32のCCD特性に基づき、シェーディング補正処理、γ補正、フィルタ処理、RGB→RGB色変換処理等の各種の画像処理を画像データに施す。

【0029】

暗号器27は、画像データを暗号化・復号するICであり、本実施形態が対象とする暗号器43とは別に存在する。

【0030】

回転器26は、スキャナ32が読み取った画像データ又はプロッタ31へ転送される画像データに対して回転処理を施す。すなわち、読み取り時に傾いた画像の傾きを検出し、画素の配置を換えるなどして傾きを補正する。

【0031】

プロッタ出力部25は、HDD16に記憶されている画像データを読み出し、RGB→CMYKの画像データに変換し、また、ディザ処理を行いCMYK各色の2値化データをプロッタ31に転送する。

【0032】

CPU I/F21はCPU11とASIC300間で周波数の違いを吸収したり、データの入出力を行うバッファとして機能したり、ASIC300の各ブロック間でCPU11とデータの送受信を行う。

【0033】

メモリI/F22はメモリ12にアクセスするもので、例えばRW−DMAC45からメモリ12のデータの読み出し要求を受け付けると、メモリ12からデータを読み出しRW−DMAC45に出力し、RW−DMAC45からデータの書き込み要求を受け付けると、メモリ12にデータを書き込み、その結果をRW−DMAC45に通知する。

【0034】

ネットワークI/F23はLAN等のネットワークにアクセスし、ネットワーク上を流れるデータの宛先のMACアドレスを監視して、自機へのデータを選択的に取り込み、CPU等に割り込みして通知する。また、CPU11からデータの送信要求を受け付けると、自機と宛先のMACアドレスを追加してネットワークに出力する。

【0035】

FAX I/F24はFAX装置14がデータを受信するとCPU等に割り込みして通知する。また、CPU11からデータの送信要求があるとFAX番号等を指定してFAX装置14に出力する。

【0036】

外部メディアI/F100は、外部記憶メディア200にデータを書き込み、また、外部記憶メディア200からデータを読み出す装置である。外部記憶メディア200はフラッシュメモリ、FeRAM、MRAM、ReRAMなど不揮発メモリにより構成され、具体的にはUSBメモリ、SDメモリ、メモリースティック(登録商標)、スマートメディア、コンパクトフラッシュ(登録商標)等がある。

【0037】

外部メディアI/F100は、RW−DMAC45、データ振り分け器44、暗号器43、メディアアクセス制御部42、SRAM46、及び、IP41を有し、メディアアクセス制御部42は暗号器正当性確認部51を有する。

【0038】

RW−DMAC45は、CPU11を介さずに外部記憶メディア200からのデータの読み出し又はデータの書き込みを行う。

【0039】

読み出し:CPU11からRW−DMAC45に対し、例えばメモリ12に記憶されたデータのアドレスと書き込み対象のバイト数が設定される。RW−DMAC45は指定されたアドレスのデータを指定されたバイト数だけメモリ12から読み出し、暗号器43に入力する。ここで、データ振り分け器44は、正当性確認テスト(後述の暗号化テスト又は復号テスト)以外では作動しない(データパスがつながっていない)。暗号器43はデータを暗号化してメディアアクセス制御部42に入力するので、メディアアクセス制御部42はIP41を介して暗号化されたデータを外部記憶メディア200に記憶する。

【0040】

読み出し:CPU11からRW−DMAC45に対し、外部記憶メディア200のアドレスとバイト数(又はファイル名)が設定される。RW−DMAC45はメディアアクセス制御部42とIP41を利用して外部記憶メディア200から指定されたデータを読み出し、暗号器43に入力する。暗号器43は、暗号化されたデータを復号してRW−DMAC45に入力する(正当性確認テスト以外ではデータ振り分け器44は使用されない)。RW−DMAC45はメモリI/F22を介してデータをメモリ12に記憶する。RW−DMAC45はデータを読み出すとCPU11に割り込みして通知する。

【0041】

このように、外部メディアI/F100は原則的に全てのデータを暗号化し、また、読み出したデータを復号するが、CPU11からの制御により暗号化しないようにすることも可能になっている。

【0042】

メディアアクセス制御部42はSRAM46をバッファとして利用しながら、IP41の書き込み状況に基づきデータをIP41に入力する。IP41は決まった単位で外部記憶メディア200にデータを書き込んでいく。また、メディアアクセス制御部42はIP41が外部記憶メディア200から読み出したデータを暗号器43に出力し、暗号器43が復号している間、SRAMにデータを保持しておく。SRAMに空きがなくなるとIP41に読み出しを停止させる。なお、IP41は機能名ではないが、外部記憶メディア200への書き込みと読み出しを行うICである。

【0043】

図5では、外部メディアI/F100は画像形成装置に搭載されているが、画像形成装置に搭載されている必要はなく、情報処理装置や組み込み機器などに搭載されてもよい。

【0044】

〔メディアアクセス制御部〕

図6は、メディアアクセス制御部42の機能ブロック図の一例を示す。メディアアクセス制御部42は、I/F制御モジュール52、暗号器正当性確認部51、及び、テスト回路50を有する。

【0045】

テスト回路50は、モード選択部58、I/F制御部53、暗号器制御部55、正当性確認制御部54、テストデータサイズ記憶部59、完了通知部57、テストデータサイズカウンタ56、データ振り分け器制御部60、及び、DMAC制御部61を有している。

【0046】

モード選択部58は、暗号器テストを行うか否かを選択するスイッチの役割を有し、「通常動作」モード又は「暗号器テスト」モードを選択できる。「通常動作」モードは暗号器43の正当性確認テストを行なわない通常の転送を行うモードである。「暗号器テスト」モードは、さらに「暗号化テストモード」と「復号テストモード」がある。「暗号化テストモード」は、暗号器43の暗号化機能の正当性確認テストが行われるモードである。「復号テストモード」は、暗号器43の復号機能の正当性確認テストが行われるモードである。これらのモードの設定はソフトウェア16が行う。モード選択部58のモードによって、テスト回路50はパスの切換タイミングなどを制御する。

【0047】

I/F制御部53はモード選択部58が「暗号器テスト」モードを選択すると、I/F制御モジュール52を停止し、暗号器テストを動作させるためのパスを構築する。「通常動作」モードでは、RW−DMAC45と暗号器43、暗号器43とI/F制御モジュール52がそれぞれデータパスで接続されている。これに対し「暗号器テスト」モードになると、I/F制御部53は、RW−DMAC45とデータ振り分け部44、データ振り分け部44と暗号器43、データ振り分け部44と暗号器正当性確認部51、暗号器43と暗号器正当性確認部51、をそれぞれデータパスで接続する。

【0048】

なお、暗号器43を経由しないデータ振り分け部44と暗号器正当性確認部51のデータパスをスルーパス47という。データ振り分け部44は、スルーパス47とパス48を択一的に選択してデータの送信先を切り換える。

【0049】

暗号器制御部55は、暗号器43の動作モードを選択する機能で、「暗号化」モード、「復号」モード、又は、「スルー」モードの3つの動作モードを選択できる。

【0050】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を読み込むか否かを制御する。また、正当性確認制御部54は暗号器正当性確認部51のスルー設定をON・OFFに制御する。

【0051】

テストデータサイズ記憶部59はソフトウェア16を実行するCPU11により設定され、テストデータのサイズを保持する。

【0052】

完了通知部57は、テスト回路50の動作が完了したことをCPU11に通知する。

【0053】

テストデータサイズカウンタ56は、期待値データと暗号化又は復号されたINPUTデータとの比較が終わったデータ数を累積して保持する。テストデータサイズカウンタ56とテストデータサイズ記憶部59の値が同じになることが、正当性確認テストの終了条件になる。

【0054】

データ振り分け器制御部60は、データ振り分け器44と暗号器正当性確認部51のスルーパス47と、データ振り分け器44と暗号器43のパス48のどちらを有効にするかを切り換える(暗号器を通らないパス、暗号器を通るパスを切り換える)。

【0055】

DMAC制御部61は、RW−DMACの起動と、RW−DMAC45がデータを書き込むのか、データを読み出すのかを切り換える。

【0056】

図7は、テストデータを模式的に説明する図の一例である。本実施形態ではテストデータに任意のデータ量ずつ期待値データとINPUTデータを交互に配置する。従来は、INPUTデータは最初から最後まで連続しており、期待値データも最初から最後まで連続していた。本実施例では、期待値データとINPUTデータを従来のようにそれぞれ独立して持たせず、例えば1つのファイルのように保持する。

【0057】

図では128ビットずつ交互に配置されているが、期待値データとINPUTデータでビット数が同じであり、かつ、最初から最後まで期待値データとINPUTデータのビット数が一定であればよい。

【0058】

また、期待値データとINPUTデータは、期待値データの方がINPUTデータよりも先のアドレスに記憶されている。したがって、期待値データ→INPUTデータの順に読み出される。

【0059】

期待値データとINPUTデータの配置は逆にすることも可能であるが、この場合、後述するデータパスの制御を期待値データとINPUTデータの配置に合わせて修正する。

【0060】

〔比較手順〕

図8は、期待値データとINPUTデータが振り分けられる様子を説明する図の一例である。

RW−DMAC45はメモリ12から期待値データとINPUTデータをアドレス順に読み出す。したがって、決まったデータ長毎に期待値データとINPUTデータが順番に読み出される。

【0061】

データ振り分け器44にはこのデータ長が設定されている。データ振り分け器44は、RW−DMAC45が読み出した期待値データとINPUTデータから、データ長毎に出力先を振り分ける。例えば、最初の128ビットは暗号器正当性確認部51に、次の128ビットは暗号器43に、次の128ビットは暗号器正当性確認部51に、次の128ビットは暗号器43に…、のように振り分ける。こうすることで、暗号器正当性確認部51には期待値データのみがアドレス順に連続して供給され、暗号器43にはINPUTデータのみがアドレス順に連続して供給される。

【0062】

暗号器43は、予め決まったデータ量をブロックにして、ブロック単位(例えば256ビット)で暗号化を行う。図では「結果1」と記されたブロックが暗号化されたデータである。暗号器正当性確認部51は、期待値データと暗号化されたINPUTデータをブロック単位で比較する。

【0063】

図9は、暗号器正当性確認部51による期待値データと暗号化されたINPUTデータの比較を説明する図の一例である。

【0064】

暗号器43はINPUTデータを暗号化するための時間が必要なので、期待値データの方が先に暗号器正当性確認部51に入力される。このため、暗号器正当性確認部51は、期待値データをラッチする。この後、暗号器43がINPUTデータを暗号化すると、暗号化されたINPUTデータが暗号器正当性確認部51に入力される。したがって、暗号器正当性確認部51には、図9に示すように期待値データ、暗号化されたINPUTデータの順番で、1ブロックずつ入力される。

【0065】

暗号器正当性確認部51は1ブロック分の期待値データをラッチしておき、その後、暗号器43から暗号化されたINPUTデータが入力されると、両者のEX-OR(排他的論理和)を取る。排他的論理和は、2つの入力値が異なる場合に1を出力し、それ

以外の場合(入力値が同じとき)には0を出力する。したがって、EX-ORの結果が全て0の場合、そのブロックの正当性が確認されたと判断され、暗号器正当性確認部51は次のブロックの処理に移ることができる。

【0066】

期待値データ、暗号化されたINPUTデータが交互に入力されるが、期待値データが暗号器正当性確認部51に入力されてから、暗号器43が暗号化されたINPUTデータを入力するまでにレイテンシーが発生する。このため、図9の比較において期待値データの入力→暗号化されたINPUTデータの入力、の順番は崩れることはなく比較することが可能である。

【0067】

〔動作手順〕

図10は、暗号器43の正当性確認テストの全体手順を示すフローチャート図の一例である。本実施例では画像形成装置の電源オンの際、正当性が確認されるものとする。

【0068】

例えば、ユーザが画像形成装置の電源をオンにする(S10)。CPU11はIPL(Initial Program Loader)を実行して、IPLが予め定められソフトウェア16をCPU11に実行させる。本実施例ではこのソフトウェア16が正当性を確認する処理を行う。

【0069】

ソフトウェア16はモード選択部58を「暗号器テスト」モードに設定する(S20)。

【0070】

ソフトウェア16は、交互に配置されているテストデータをメモリ12に用意する(S30)。具体的には、テストデータはソフトウェア16と一体にコード化されているか又はテーブル状にHDD16に記憶されている。ソフトウェア16は変数名などを介して指定するアドレスからテストデータをHDD16等から読み出しメモリ12に記憶させる。

【0071】

ソフトウェア16は、メモリ12上に用意した期待値データとINPUTデータの合計のデータサイズをテストデータサイズ記憶部59に設定する(S40)。

【0072】

この後、暗号器正当性確認部51はテスト回路50を起動し、テスト回路50は起動すると、暗号器43の正当性のテストを開始する(S50)。暗号器43の正当性のテストについて詳細な手順は後述する。

【0073】

暗号器正当性確認部51は期待値データと暗号器43からの入力されたINPUTデータの比較を、完了通知部57から完了通知が行われるまで行う(S60)。暗号器43が交換されていたり、暗号器43が故障していなければ、暗号器正当性確認部51は期待値データと暗号化されたINPUTデータが一致したと判定する(S70)。

【0074】

暗号器正当性確認部51が、期待値データと暗号化されたINPUTデータの比較の結果が不一致であると判定すると(S70のYes)、ソフトウェア16がエラー処理を行う(S80)。エラー処理の内容は、例えば、再度のテストを行うこと、再度のテストを行っても不一致の場合はエラーメッセージを表示すること等であるが、詳細は省略する。

【0075】

図の処理は、暗号器43の暗号化テストと復号テストの両方が完了すると終了する(S90)。例えば、復号テストがまだ完了していない場合、ソフトウェア16は、テスト回路50の完了通知部57から完了通知(暗号化完了)を受けると、暗号器43のテストモードを復号に設定し(S100)、再度、テストデータの準備、データサイズの設定を行い、テスト回路50に処理を実行させる。

【0076】

復号の正当性確認テストが完了すると、テスト回路50は復号の正当性確認テストの完了通知をソフトウェア16に通知する。テスト回路50から完了通知(復号完了)を受けると、暗号器43が正常に動作していると判断できるため、図10の正当性確認テストは終了する。

【0077】

<暗号化テスト>

図11は、テスト回路50の動作手順を詳細な示すフローチャート図の一例である。

【0078】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「暗号化テスト」モードが選択されているか否かを判定する(S110)。

【0079】

モード選択部58が暗号化テストモードに設定されていない場合(S110のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図11の処理は終了する。

【0080】

モード選択部58が暗号化テストモードに設定されている場合(S110のYes)、テスト回路50は暗号化テストを行う。暗号化テストは次の手順で行われる。

【0081】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S120)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0082】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S130)。また、暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、DMAC制御部61はRW−DMAC45に転送サイズを設定する(S140)。

【0083】

暗号器制御部55は、暗号器43を暗号化モードに設定する(S150)。

【0084】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S160)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0085】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S170)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44と暗号器正当性確認部51を結ぶスルーパス47、データ振り分け器44と暗号器43を結ぶパス48、及び、暗号器43から暗号器正当性確認部51へのパス、を構築する。また、使用しないI/F制御モジュール52を停止させる。

【0086】

次に、DMAC制御部61はRW−DMAC45を起動する(S180)。これにより、RW−DMAC45はデータサイズカウンタがテストデータサイズ記憶部59に記憶されたデータサイズを読み出すまでメモリ12からテストデータの読み出しを繰り返す。

【0087】

まず、データ振り分け器44は、データ振り分け制御部60の制御により、パス48をスルーパス47へ変更する(S190)。スルーパス47は暗号器43でなく暗号器正当性確認部51に出力するパスである。

【0088】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S200)。1ブロックには、期待値データとINPUTデータが含まれている。

【0089】

データ振り分け器44は、期待値データのみをスルーパス47へ出力する(S210)。これにより、暗号器正当性確認部51に1ブロック分の期待値データが記憶される(S220)。

【0090】

1ブロック分の期待値データを転送すると、データ振り分け器44はデータ振り分け制御部60の制御により、スルーパス47をパス48に切り替える(S230)。データ振り分け器44は1ブロック分のINPUTデータを暗号器43へ入力する(S240)。

【0091】

暗号器43は転送されたINPUTデータを暗号化する(S250)。暗号器43は、暗号化したINPUTデータを暗号器正当性確認部51に入力する(S260)。ここで、暗号器正当性確認部51は上記のように排他的論理和を取る。

【0092】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分の暗号化されたINPUTデータが転送されたことを検出して、データ比較フラグをONにする(S270)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0093】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S280)。どれか1bitでも1が出力されていた場合(S280のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S290)。

【0094】

ALLゼロの場合(S280のYes)、比較が正常に完了したので、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S300)。

【0095】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S310)。

【0096】

以上のように、テスト回路50は、テストデータの読み込み、パスの設定、比較結果の判定、データサイズの加算を、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになるまで繰り返す。完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、暗号化テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S320)。これにより暗号化テストが完了する。

【0097】

<復号テスト>

図12は、画像形成装置の構成図から、要部として外部メディアI/F100を取り出した図の一例である。図12において図5と同一部の説明は省略する。外部メディアI/F100の構成は暗号化の場合と同様だが、データパスが異なる。

(1)復号テストの場合、データ振り分け器44はテストデータの期待値データを、スルーパス47を介して暗号器正当性確認部51に入力する。

(2)次に、データ振り分け器44はテストデータのうちINPUTデータ(暗号器への入力される復号対象のデータ)を、スルーパス47を介して暗号器正当性確認部51に転送する。暗号器正当性確認部51はそのままINPUTデータを暗号器43に入力する。

(3)暗号器43は、INPUTデータを復号してデータ振り分け器44に入力する。

(4)データ振り分け器44は再度、スルーパス47を介して復号されたINPUTデータを暗号器正当性確認部51に入力する。

(5)暗号器正当性確認部51は、期待値データと復号されたINPUTデータを比較する。

【0098】

メモリ12から読み出したINPUTデータを直接、暗号器43に入力しないのは、暗号器43はメディアアクセス制御部42から受け取ったデータを復号するように設計されているためである。このようにスルーパス47を利用することで、復号テストも可能になる。

【0099】

〔復号時の動作手順〕

図13は、復号テストにおけるテスト回路50の動作手順を示すフローチャート図の一例である。復号時には、正当性確認制御部54が暗号器正当性確認部51のスルー設定をON・OFFする。暗号器正当性確認部51のスルー設定がOFFの場合、暗号器正当性確認部51はデータを保持し、暗号器正当性確認部51のスルー設定がONの場合、暗号器正当性確認部51はデータを保持することなく暗号器正当性確認部51と暗号器43を直結する。

【0100】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「復号テスト」モードが選択されているか否かを判定する(S410)。

【0101】

モード選択部58が復号テストモードに設定されていない場合(S410のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図13の処理は終了する。

【0102】

モード選択部58が復号テストモードに設定されている場合(S410のYes)、テスト回路50は復号テストを行う。復号テストは次の手順で行われる。

【0103】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S420)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0104】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S430)。暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、RW−DMAC45に転送サイズを設定する(S440)。

【0105】

暗号器制御部55は、暗号器43を復号モードに設定する(S450)。

【0106】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S460)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0107】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S470)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44から暗号器正当性確認部51へのスルーパス47、暗号器正当性確認部51から暗号器43へのパス、暗号器43からデータ振り分け器44へのパスを構築し、I/F制御モジュール52を停止させる。

【0108】

次に、DMAC制御部61はRW−DMAC45を起動する(S480)。

【0109】

正当性確認制御部54は、暗号器正当性確認部51のスルー設定をOFFに設定する(S490)。これにより、暗号器正当性確認部51はデータを保持することができる。

【0110】

RW−DMAC45はデータサイズカウンタがテストデータサイズ記憶部59に記憶されたデータサイズを読み出すまでメモリ12からテストデータの読み出しを繰り返す。

【0111】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S500)。1ブロックには、期待値データとINPUTデータが含まれている。

【0112】

データ振り分け器44は、期待値データのみをスルーパス47へ出力する(S510)。これにより、暗号器正当性確認部51に1ブロック分の期待値データが記憶される(S520)。

【0113】

1ブロック分の期待値データを転送すると、正当性確認制御部54は暗号器正当性確認部51のスルー設定をONに設定する(S530)。

【0114】

次に、データ振り分け器44は1ブロック分のINPUTデータを、スルーパス47を介して暗号器正当性確認部51に入力する(S540)。暗号器正当性確認部51はスルー設定がONなので、INPUTデータは暗号器43に入力される(S550)。

【0115】

暗号器43は転送されたINPUTデータを復号する(S560)。暗号器43は、復号されたINPUTデータをデータ振り分け器44に入力する。

【0116】

正当性確認制御部54は、復号されたINPUTデータを蓄積するため暗号器正当性確認部51のスルー設定をOFFに設定する(S570)。

【0117】

データ振り分け器44は、復号されたINPUTデータを暗号器正当性確認部51に入力する(S580)。暗号器正当性確認部51は復号されたINPUTデータを蓄積する(S590)。ここで、暗号器正当性確認部51は上記のように排他的論理和を取る。

【0118】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分の復号されたINPUTデータが転送されたことを検出して、データ比較フラグをONにする(S600)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0119】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S610)。どれか1bitでも1が出力されていた場合(S610のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S620)。

【0120】

ALLゼロの場合(S610のYes)、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S630)。

【0121】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S640)。

【0122】

完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、復号テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S650)。これにより復号データが完了する。

【0123】

以上説明したように、本実施例の外部メディアI/F100は、暗号器43を通過した直後に暗号器正当性確認部51が正当性を確認でき、外部記憶メディア200に書き込む必要がないので、ユーザの待ち時間を短縮できる。また、復号時も外部記憶メディア200に書き込む必要がないので暗号器43の正当性を確認する時間を短縮できる。

【実施例2】

【0124】

実施例1にて説明したように、暗号化テスト用のテストデータ、復号テスト用のテストデータを用意することが好ましいが、必ずしも二種類のテストデータを用意する必要はない。本実施例では、いずれか一方のテストデータにより暗号化テストと復号テストの両方が可能な外部メディアI/F100について説明する。

【0125】

こうすることで、メモリ領域を節約できたり、何らかの理由で暗号化テスト又は復号テストのどちらかのテストデータのみしか用意できない場合にも暗号化テストと復号テストの両方が可能になる。

【0126】

図14は、暗号化テスト及び復号テストの際のデータフローとデータ間の関係を説明する図の一例である。

【0127】

中央に暗号器43があり、暗号器43が出力した暗号化したデータは「暗号データ」、暗号器43が復号したデータは「復号データ」である。

(1)暗号器43は、「復号データ」の入力値を暗号化する。これにより暗号化期待値が得られる。

(2)暗号器43は、「暗号データ」の入力値を復号する。これにより復号期待値が得られる。

【0128】

暗号器43が暗号化したデータは、同じ暗号器43が復号することで、元の入力値に戻る。したがって、「復号データ」の入力値と復号期待値とは同じものであり、「暗号データ」の暗号化期待値と入力値とは同じものである。

【0129】

実施例1では、「復号データ」の入力値と「暗号データ」の暗号化期待値が暗号化テストのテストデータであり、「暗号データ」の入力値と「復号データ」の復号期待値が復号テストのテストデータである。したがって、暗号化テストと復号テストにおいて、期待値データとINPUTデータの関係を逆にするだけで、暗号化テストと復号テストの両方が可能になる。

【0130】

〔構成例〕

図15は、メディアアクセス制御部42の機能ブロック図の一例を示す。図15において図6と同一部の説明は省略する。

【0131】

図15のメディアアクセス制御部42は、データ振り分け器44がテストデータ保持部62を有し、テスト回路50がテストデータ状態通知部63を有する。テストデータ保持部62は、暗号器43に出力するデータを一時的に保持する。テストデータ状態通知部63は、暗号用又は復号用のテストデータの有無をデータ振り分け器44に通知する。

【0132】

ソフトウェア16は、暗号化用のテストデータと復号用のテストデータのうち、どちらを用意しているかをテストデータ状態通知部63に設定しておく。

【0133】

〔動作手順 暗号化テスト〕

まず、暗号化時の手順について説明するが、復号時の手順から実行することも可能である。

【0134】

図16は、データの流れを模式的に示す図の一例を、図17は、ソフトウェア16が外部メディアI/F100の暗号器43の暗号機能の正当性を確認する手順を示すフローチャート図の一例をそれぞれ示す。図16の矢印線のステップ番号は図17のステップ番号と対応している。

【0135】

図16に示すように、データ振り分け器が期待値データをいったん保持しておき、先にIUPUTデータを暗号器正当性確認部51に入力する。そして、データ振り分け器は保持している期待値データを暗号器にて暗号化した後、暗号器正当性確認部51に入力する。こうすることで、復号テスト用のテストデータで暗号化テストが可能になる。

【0136】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「暗号化テスト」モードが選択されているか否かを判定する(S710)。

【0137】

モード選択部58が暗号化テストモードに設定されていない場合(S710のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図17の処理は終了する。

【0138】

モード選択部58が暗号化テストモードに設定されている場合(S710のYes)、テスト回路50は暗号化テストを行う。

【0139】

テスト回路50はまず、テストデータ状態通知部63に暗号化テストのテストデータが用意されているか否かを問い合わせる(S720)。暗号化テストのテストデータが用意されている場合(S730のYes)、すでに説明した図11の暗号化テストが実行される(S740)。

【0140】

復号テストのテストデータしか用意されていない場合(S730のNo)、暗号化テスト用のデータが用意されていない場合の暗号化テストを実施する。暗号化テストのテストデータが用意されていない場合の暗号化テストは次の手順で行われる。

【0141】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S750)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0142】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S760)。暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、RW−DMAC45に転送サイズを設定する(S770)。

【0143】

暗号器制御部55は、暗号器43を暗号化モードに設定する(S780)。

【0144】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S790)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0145】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S800)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44と暗号器正当性確認部51を結ぶスルーパス47、データ振り分け器44と暗号器43を結ぶパス48、及び、暗号器正当性確認部51から暗号器43へのパス、を構築する。また、使用しないI/F制御モジュール52を停止させる。

【0146】

次に、DMAC制御部61はRW−DMAC45を起動する(S810)。

【0147】

データ振り分け器44は、パス48をスルーパス47へ切り換える(S820)。

【0148】

また、データ振り分け器44はテストデータ保持部62のデータ蓄積モードをONに設定する(S830)。

【0149】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S840)。1ブロックには、期待値データとINPUTデータが含まれているが、これらは復号テスト用のテストデータである。まず、復号テスト用の期待値データのみをデータ振り分け器44のテストデータ保持部62に蓄積させていく(S850)。

【0150】

データ振り分け器44は、1ブロック分の期待値データが蓄積された後、データ蓄積モードをOFFに切り替える(S860)。

【0151】

次に、データ振り分け器44は、復号テスト用のテストデータのINPUTデータを1ブロック分、スルーパス47へ転送する(S870)。暗号器正当性確認部51はINPUTデータを蓄積する(S880)。復号用テストデータのINPUTデータは、暗号化された状態である。

【0152】

データ蓄積完了後、データ振り分け器44がスルーパス47をパス48(暗号器側)に切り替える(S890)。

【0153】

データ振り分け器44はテストデータ保持部62に蓄積された復号用テストデータの期待値データを暗号器43へ入力する(S900)。

【0154】

暗号器43は期待値データを暗号化する(S910)。復号用のテストデータの期待値データが暗号化されるので、このデータは暗号化された状態である。

【0155】

暗号器43は、暗号化した復号用テストデータの期待値データを暗号器正当性確認部51に入力する(S920)。暗号器正当性確認部51は上記のように2つのデータの排他的論理和を取る。

【0156】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分の暗号化された期待値データが転送されたことを検出して、データ比較フラグをONにする(S930)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0157】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S940)。どれか1bitでも1が出力されていた場合(S940のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S950)。

【0158】

ALLゼロの場合(S940のYes)、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S960)。

【0159】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S970)。

【0160】

完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、復号テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S980)。

【0161】

以上のように、ソフトウェア16が復号用のテストデータしか有していなくても、テストデータ保持部62がテストデータを保持しておき、復号テスト用の期待値データを暗号器43に、復号テスト用のINPUTデータを暗号器正当性確認部51に入力することで、暗号器43の暗号化テストが可能になる。

【0162】

〔動作手順 復号テスト〕

図18は、復号テストにおけるデータの流れを模式的に示す図の一例を、図19は、ソフトウェア16が外部メディアI/F100の暗号器43の復号機能の正当性を確認する手順を示すフローチャート図の一例である。

【0163】

図18に示すように、期待値データは暗号器正当性確認部51をスルーして暗号器により復号された後、データ振り分け器にいったん保持される。次に、データ振り分け器はIUPUTデータを暗号器正当性確認部51に入力する。そして、データ振り分け器は保持している復号された期待値データを暗号器正当性確認部51に入力する。こうすることで、暗号テスト用のテストデータで復号テストが可能になる。

【0164】

テスト回路50が起動されると、暗号器制御部55はモード選択部58に「復号テスト」モードが選択されているか否かを判定する(S1010)。

【0165】

モード選択部58が復号テストモードに設定されていない場合(S1010のNo)、テスト回路50は暗号器43の正当性確認テストを行わない。このため、図19の処理は終了する。

【0166】

モード選択部58が暗号化テストモードに設定されている場合(S1010のYes)、テスト回路50は復号のテストを行う。テスト回路50は、まず、テストデータ状態通知部63に復号テスト用のテストデータが用意されているか否かを問い合わせる(S1020)。

【0167】

復号テストのテストデータが用意されている場合(S1030のYes)、すでに説明した図13の復号テストを実行すればよい(S1040)。

【0168】

暗号化用のテストデータしか用意されていない場合(S1030のNo)、テスト回路50は復号用のテストデータが用意されていない場合の復号テストを実行する。復号用のテストデータが用意されていない場合の復号テストは次の手順で行われる。

【0169】

正当性確認制御部54は、暗号器正当性確認部51の現在の状態を確認するかどうかを指定するデータ比較フラグをOFFにする(S1050)。データ比較フラグがOFFの場合、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認しない。

【0170】

次に、DMAC制御部61は、RW−DMAC45にメモリリード設定を行う(S1060)。暗号器正当性確認部51で比較できるデータサイズ分の転送が行われるように、RW−DMAC45に転送サイズを設定する(S1070)。

【0171】

暗号器制御部55は、暗号器43を復号モードに設定する(S1080)。

【0172】

また正当性確認制御部54は、暗号器正当性確認部51をクリアする(S1090)。クリアとは初期化の意味であり暗号器正当性確認部51にゼロが設定される。

【0173】

またI/F制御部53は暗号器テストを動作させるためのパスを構築する(S1100)。具体的には、RW−DMAC45がメモリ12から読み出したデータをデータ振り分け器44に出力するパス、データ振り分け器44から暗号器正当性確認部51へのスルーパス47、暗号器正当性確認部51から暗号器43へのパス、暗号器43からデータ振り分け器44へのパスを構築し、I/F制御モジュール52を停止させる。

【0174】

次に、DMAC制御部61はRW−DMAC45を起動する(S1110)。

【0175】

正当性確認制御部54は、暗号器正当性確認部51のスルー設定をONに設定する(S1120)。

【0176】

RW−DMAC45は設定された転送サイズ分のデータ(1ブロック)をメモリ12から読み込む(S1130)。1ブロックには、期待値データとINPUTデータが含まれているが、これらは暗号化用のテストデータである。

【0177】

まず、データ振り分け器44は暗号化テストのテストデータの期待値データのみをスルーパス47へ出力する(S1140)。暗号化テストのテストデータの期待値データは、暗号化された状態である。

【0178】

暗号器正当性確認部51のスルー設定はONなので、期待値データは暗号器43にそのまま入力される(S1150)。

【0179】

暗号器43は期待値データを復号する(S1160)。暗号化テストのテストデータの期待値データは暗号化されているので、復号により暗号化されていない状態になる。

【0180】

データ振り分け器44は、復号された期待値データをテストデータ保持部62に蓄積させていく(S1170)。

【0181】

次に、正当性確認制御部54は、暗号器正当性確認部51のスルー設定をOFFに設定する(S1180)。

【0182】

データ振り分け器44は、暗号化テストのテストデータのINPUTデータを暗号器正当性確認部51に入力する(S1190)。暗号化テストのテストデータのINPUTデータは暗号化される前の状態である。

【0183】

暗号器正当性確認部51は、INPUTデータを保持する(S1200)。

【0184】

次に、データ振り分け器44は、テストデータ保持部62に記憶している復号された期待値データを、スルーパス47を介して暗号器正当性確認部51に入力する(S1210)。

【0185】

暗号器正当性確認部51は、復号された期待値データを取得する(S1220)。

【0186】

正当性確認制御部54は、暗号器正当性確認部51に1ブロック分のデータが転送されたことを検出して、データ比較フラグをONにする(S1230)。データ比較フラグがONになると、正当性確認制御部54は、暗号器正当性確認部51の比較結果を確認する。

【0187】

正当性確認制御部54は、暗号器正当性確認部51の比較結果を監視して、ALLゼロか否かを判定する(S1240)。どれか1bitでも1が出力されていた場合(S1240のNo)、正当性確認制御部54は暗号器43の正当性が保たれていないとしてエラー処理を行う(S1250)。

【0188】

ALLゼロの場合(S1240のYes)、正当性確認制御部54はデータ比較フラグを再びOFFに設定する(S1260)。

【0189】

次に、正当性確認制御部54は1ブロックの比較が完了したことを検出して、データサイズカウンタに1ブロック分のデータサイズを上乗せしていく(S1270)。

【0190】

完了通知部57は、テストデータサイズ記憶部59に保持された値とデータサイズカウンタが同じになると、復号テストの完了通知をCPU11に割り込むことでソフトウェア16に対し通知する(S1280)。

【0191】

以上のように、ソフトウェア16が暗号化テストのテストデータしか有していなくても、復号テストが可能である。テストデータ保持部62が暗号化テスト用の期待値データを暗号器正当性確認部51経由で暗号器に復号させテストデータ保持部62で保持しておく。暗号化テスト用のINPUTデータを暗号器正当性確認部51に出力し、次に、テストデータ保持部62で保持している復号された期待値データを暗号器正当性確認部51に入力することで、暗号器43の復号テストが可能になる。

【符号の説明】

【0192】

11 CPU

12 メモリ

16 ソフトウェア

41 IP

42 メディアアクセス制御部

43 暗号器

44 データ振り分け部

45 RW−DMAC

51 暗号器正当性確認部

52 I/F制御モジュール

53 I/F制御部

54 正当性確認制御部

55 暗号器制御部

56 データサイズカウンタ

57 完了通知部

58 モード選択部

59 テストデータサイズ記憶部

60 データ振り分け制御部

61 DMAC制御部

100 外部メディアI/F

200 外部記憶メディア

【先行技術文献】

【特許文献】

【0193】

【特許文献1】特開2007−215028号公報

【特許請求の範囲】

【請求項1】

記憶手段からデータを読み出し、また、記憶手段へデータを書き込む記憶手段アクセス制御手段と、

外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアアクセス手段と、

前記外部メディアアクセス手段が前記外部記憶メディアに書き込むデータを暗号化し、前記外部メディアアクセス手段が前記外部記憶メディアから読み出したデータを復号する暗号器と、を有する外部メディアインタフェース装置であって、

前記暗号器の暗号化機能又は復号機能のテストモードの設定を受け付けるテストモード設定受付手段と、

前記テストモード設定受付手段が前記暗号器の暗号化機能のテストモードを受け付けた場合、前記記憶手段アクセス制御手段が読み出したテストデータの送信先を前記データ比較手段又は前記暗号器に振り分けるデータ振り分け手段と、

前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するデータ比較手段と、

前記記憶手段アクセス制御手段と前記データ振り分け手段、前記データ振り分け手段と前記データ比較手段、前記データ振り分け手段と前記暗号器、及び、前記暗号器と前記データ比較手段、の間にデータパスを構築するパス構築手段と、

を有する外部メディアインタフェース装置。

【請求項2】

前記テストモード設定受付手段が前記暗号器の復号機能のテストモードを受け付けた場合、前記データ振り分け手段は、常にテストデータを前記データ比較手段に出力し、

前記データ比較手段は、前記データ振り分け手段から取得したデータを保持する第一のモードと、前記データ振り分け手段と前記暗号器を直結して前記データ振り分け手段から取得したデータを前記暗号器に転送する第二のモードを有し、

前記データ比較手段は、前記第一のモードにおいて前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記第二のモードにおいて前記データ振り分け手段が振り分けた第二のデータを前記暗号器に出力し、

前記第一のモードにおいて保持している前記第一のデータと、前記第二のモードにおいて前記暗号器が復号し前記データ振り分け手段が振り分けた前記第二のデータとを比較する、

ことを特徴とする請求項1記載の外部メディアインタフェース装置。

【請求項3】

前記データ振り分け手段が前記第一のデータを前記データ比較手段に入力する前に、前記第一のモードに、

前記データ振り分け手段が前記第一のデータを前記データ比較手段に出力した後、前記第二のモードに、

前記データ振り分け手段が前記暗号器が復号した前記第二のデータを、再度、前記データ比較手段に入力する前に、前記第一のモードに、

それぞれ切り換える比較手段制御手段、を有することを特徴とする請求項2記載の外部メディアインタフェース装置。

【請求項4】

前記テストデータが、前記暗号器の暗号化機能をテストするデータか、復号機能をテストするデータかを示すテストデータ情報が登録されたテストデータ情報記憶手段と、

前記記憶手段アクセス制御手段が前記記憶手段から読み出したテストデータを保持するテストデータ保持手段と、を有し、

前記テストモード設定受付手段が前記暗号器の暗号化機能をテストするテストモードの設定を受け付け、前記テストデータ情報記憶手段が、前記テストデータが復号機能をテストするデータであるというテストデータ情報を記憶している場合、

前記データ振り分け手段は、前記第一のデータを前記テストデータ保持手段に記憶しておき、

前記第二のデータを前記データ比較手段に出力し、

前記テストデータ保持手段に記憶されている前記第一のデータを前記暗号器に出力し、

前記データ比較手段は、前記第二のデータと、前記暗号器が暗合化した前記第一のデータを比較する、

ことを特徴とする請求項1記載の外部メディアインタフェース装置。

【請求項5】

前記テストデータが、前記暗号器の暗号化機能をテストするデータか、復号機能をテストするデータかを示すテストデータ情報が登録されたテストデータ情報記憶手段と、

前記記憶手段アクセス制御手段が前記記憶手段から読み出したテストデータを保持するテストデータ保持手段と、を有し、

前記テストモード設定受付手段が前記暗号器の復号機能をテストするテストモードの設定を受け付け、前記テストデータ情報記憶手段が、前記テストデータが暗号化機能をテストするデータであるというテストデータ情報を記憶している場合、

前記データ振り分け手段は、前記第二のモードの前記データ比較手段に前記第一のデータを送信することで前記第一のデータを前記暗号器に出力し、

前記暗号器が復号した前記第一のデータを前記テストデータ保持手段に記憶しておき、

前記第二のデータを、前記第一のモードの前記データ比較手段に出力し、

前記テストデータ保持手段に記憶されている復号された前記第一のデータを前記第一のモードの前記暗号器に前記データ比較手段に出力し、

前記データ比較手段は、前記第二のデータと、前記暗号器が復号した前記第一のデータを比較する、

ことを特徴とする請求項2又は3記載の外部メディアインタフェース装置。

【請求項6】

前記テストデータは、所定のデータ長毎に、前記第一のデータと前記第二のデータが交互に格納されており、

前記データ振り分け手段は、前記データ長毎に、前記第一のデータを前記データ比較手段に、前記第二のデータを前記暗号器に、それぞれ入力する、

ことを特徴とする請求項1記載の外部メディアインタフェース装置。

【請求項7】

前記テストデータは、所定のデータ長毎に、前記第一のデータと前記第二のデータが交互に格納されており、

前記データ振り分け手段は、前記第一のモードにおいて前記データ長の前記第一のデータを前記データ比較手段に出力し、

前記第二のモードにおいて前記データ長の前記第二のデータを前記データ比較手段に入力する、

ことを特徴とする請求項2又は3記載の外部メディアインタフェース装置。

【請求項8】

記憶手段の指示されたアドレスからデータを読み出し、また、記憶手段へデータを書き込む記憶手段アクセス制御手段と、

外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアアクセス手段と、

前記外部メディアアクセス手段が前記外部記憶メディアに書き込むデータを暗号化し、前記外部メディアアクセス手段が前記外部記憶メディアから読み出したデータを復号する暗号器と、を有する外部メディアインタフェース装置のテスト方法であって、

テストモード設定受付手段が、前記暗号器の暗号化機能又は復号機能のテストモードの設定を受け付けるステップと、

パス構築手段が、前記記憶手段アクセス制御手段と前記データ振り分け手段、前記データ振り分け手段と前記データ比較手段、前記データ振り分け手段と前記暗号器、及び、前記暗号器と前記データ比較手段、の間にデータパスを構築するステップと、

前記テストモード設定受付手段が前記暗号器の暗号化機能のテストモードを受け付けた場合、データ振り分け手段が、前記記憶手段アクセス制御手段が読み出したテストデータの送信先を前記データ比較手段又は前記暗号器に振り分けるステップと、

データ比較手段が、前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するステップと、

を有するテスト方法。

【請求項1】

記憶手段からデータを読み出し、また、記憶手段へデータを書き込む記憶手段アクセス制御手段と、

外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアアクセス手段と、

前記外部メディアアクセス手段が前記外部記憶メディアに書き込むデータを暗号化し、前記外部メディアアクセス手段が前記外部記憶メディアから読み出したデータを復号する暗号器と、を有する外部メディアインタフェース装置であって、

前記暗号器の暗号化機能又は復号機能のテストモードの設定を受け付けるテストモード設定受付手段と、

前記テストモード設定受付手段が前記暗号器の暗号化機能のテストモードを受け付けた場合、前記記憶手段アクセス制御手段が読み出したテストデータの送信先を前記データ比較手段又は前記暗号器に振り分けるデータ振り分け手段と、

前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するデータ比較手段と、

前記記憶手段アクセス制御手段と前記データ振り分け手段、前記データ振り分け手段と前記データ比較手段、前記データ振り分け手段と前記暗号器、及び、前記暗号器と前記データ比較手段、の間にデータパスを構築するパス構築手段と、

を有する外部メディアインタフェース装置。

【請求項2】

前記テストモード設定受付手段が前記暗号器の復号機能のテストモードを受け付けた場合、前記データ振り分け手段は、常にテストデータを前記データ比較手段に出力し、

前記データ比較手段は、前記データ振り分け手段から取得したデータを保持する第一のモードと、前記データ振り分け手段と前記暗号器を直結して前記データ振り分け手段から取得したデータを前記暗号器に転送する第二のモードを有し、

前記データ比較手段は、前記第一のモードにおいて前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記第二のモードにおいて前記データ振り分け手段が振り分けた第二のデータを前記暗号器に出力し、

前記第一のモードにおいて保持している前記第一のデータと、前記第二のモードにおいて前記暗号器が復号し前記データ振り分け手段が振り分けた前記第二のデータとを比較する、

ことを特徴とする請求項1記載の外部メディアインタフェース装置。

【請求項3】

前記データ振り分け手段が前記第一のデータを前記データ比較手段に入力する前に、前記第一のモードに、

前記データ振り分け手段が前記第一のデータを前記データ比較手段に出力した後、前記第二のモードに、

前記データ振り分け手段が前記暗号器が復号した前記第二のデータを、再度、前記データ比較手段に入力する前に、前記第一のモードに、

それぞれ切り換える比較手段制御手段、を有することを特徴とする請求項2記載の外部メディアインタフェース装置。

【請求項4】

前記テストデータが、前記暗号器の暗号化機能をテストするデータか、復号機能をテストするデータかを示すテストデータ情報が登録されたテストデータ情報記憶手段と、

前記記憶手段アクセス制御手段が前記記憶手段から読み出したテストデータを保持するテストデータ保持手段と、を有し、

前記テストモード設定受付手段が前記暗号器の暗号化機能をテストするテストモードの設定を受け付け、前記テストデータ情報記憶手段が、前記テストデータが復号機能をテストするデータであるというテストデータ情報を記憶している場合、

前記データ振り分け手段は、前記第一のデータを前記テストデータ保持手段に記憶しておき、

前記第二のデータを前記データ比較手段に出力し、

前記テストデータ保持手段に記憶されている前記第一のデータを前記暗号器に出力し、

前記データ比較手段は、前記第二のデータと、前記暗号器が暗合化した前記第一のデータを比較する、

ことを特徴とする請求項1記載の外部メディアインタフェース装置。

【請求項5】

前記テストデータが、前記暗号器の暗号化機能をテストするデータか、復号機能をテストするデータかを示すテストデータ情報が登録されたテストデータ情報記憶手段と、

前記記憶手段アクセス制御手段が前記記憶手段から読み出したテストデータを保持するテストデータ保持手段と、を有し、

前記テストモード設定受付手段が前記暗号器の復号機能をテストするテストモードの設定を受け付け、前記テストデータ情報記憶手段が、前記テストデータが暗号化機能をテストするデータであるというテストデータ情報を記憶している場合、

前記データ振り分け手段は、前記第二のモードの前記データ比較手段に前記第一のデータを送信することで前記第一のデータを前記暗号器に出力し、

前記暗号器が復号した前記第一のデータを前記テストデータ保持手段に記憶しておき、

前記第二のデータを、前記第一のモードの前記データ比較手段に出力し、

前記テストデータ保持手段に記憶されている復号された前記第一のデータを前記第一のモードの前記暗号器に前記データ比較手段に出力し、

前記データ比較手段は、前記第二のデータと、前記暗号器が復号した前記第一のデータを比較する、

ことを特徴とする請求項2又は3記載の外部メディアインタフェース装置。

【請求項6】

前記テストデータは、所定のデータ長毎に、前記第一のデータと前記第二のデータが交互に格納されており、

前記データ振り分け手段は、前記データ長毎に、前記第一のデータを前記データ比較手段に、前記第二のデータを前記暗号器に、それぞれ入力する、

ことを特徴とする請求項1記載の外部メディアインタフェース装置。

【請求項7】

前記テストデータは、所定のデータ長毎に、前記第一のデータと前記第二のデータが交互に格納されており、

前記データ振り分け手段は、前記第一のモードにおいて前記データ長の前記第一のデータを前記データ比較手段に出力し、

前記第二のモードにおいて前記データ長の前記第二のデータを前記データ比較手段に入力する、

ことを特徴とする請求項2又は3記載の外部メディアインタフェース装置。

【請求項8】

記憶手段の指示されたアドレスからデータを読み出し、また、記憶手段へデータを書き込む記憶手段アクセス制御手段と、

外部記憶メディアにデータを書き込み、また、外部記憶メディアからデータを読み出す外部メディアアクセス手段と、

前記外部メディアアクセス手段が前記外部記憶メディアに書き込むデータを暗号化し、前記外部メディアアクセス手段が前記外部記憶メディアから読み出したデータを復号する暗号器と、を有する外部メディアインタフェース装置のテスト方法であって、

テストモード設定受付手段が、前記暗号器の暗号化機能又は復号機能のテストモードの設定を受け付けるステップと、

パス構築手段が、前記記憶手段アクセス制御手段と前記データ振り分け手段、前記データ振り分け手段と前記データ比較手段、前記データ振り分け手段と前記暗号器、及び、前記暗号器と前記データ比較手段、の間にデータパスを構築するステップと、

前記テストモード設定受付手段が前記暗号器の暗号化機能のテストモードを受け付けた場合、データ振り分け手段が、前記記憶手段アクセス制御手段が読み出したテストデータの送信先を前記データ比較手段又は前記暗号器に振り分けるステップと、

データ比較手段が、前記データ振り分け手段が振り分けた第一のデータを保持すると共に、前記データ振り分け手段が前記暗号器に振り分け、前記暗号器が暗号化した第二のデータを取得し、比較するステップと、

を有するテスト方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−21451(P2013−21451A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−152053(P2011−152053)

【出願日】平成23年7月8日(2011.7.8)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月8日(2011.7.8)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]