多層プリント配線板

【課題】従来に比して動作時における不要輻射雑音の発生が低減される多層プリント配線板を提供。

【解決手段】絶縁された不連続部分が設けられることによって導体パターン14、16、18に分割され、実装される電子部品に対して導体パターン14、16、18ごとにそれぞれ異なる駆動電圧を供給する電源層24を内層に有し、内層のうち不連続部分が設けられた面に対して垂直方向に平行移動された面上には、導体パターン14、16、18同士を高周波的に接続する複数の電源間バイパスコンデンサ12が、および/または導体パターン14、16、18の周縁部に対して垂直方向に平行移動された内層面上には、導体パターン14、16、18とGND層36を高周波的に接続する電源グランド間バイパスコンデンサ52が実装される。

【解決手段】絶縁された不連続部分が設けられることによって導体パターン14、16、18に分割され、実装される電子部品に対して導体パターン14、16、18ごとにそれぞれ異なる駆動電圧を供給する電源層24を内層に有し、内層のうち不連続部分が設けられた面に対して垂直方向に平行移動された面上には、導体パターン14、16、18同士を高周波的に接続する複数の電源間バイパスコンデンサ12が、および/または導体パターン14、16、18の周縁部に対して垂直方向に平行移動された内層面上には、導体パターン14、16、18とGND層36を高周波的に接続する電源グランド間バイパスコンデンサ52が実装される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多層プリント配線板、より具体的には、機能モジュールとして使用される多層プリント配線板に関する。

【背景技術】

【0002】

近年、多層プリント配線板(プリント回路板、プリント基板)に実装する中央処理装置(CPU)、ディジタル信号処理装置(DSP)等といった半導体集積回路の小型高速動作化が求められる中で、回路素子の発熱対策として半導体集積回路を駆動する電源の低電圧化が進められている。また、外部インターフェースとの整合を取るため、回路素子駆動電圧は、例えば5V、3.3V、2.5V、1.8Vなど多種電源電圧の併用が求められている。一方で、多層プリント配線板を内蔵する製品の小型化要求に伴い、多層プリント配線板も小型化、高密度化が求められている。

【0003】

駆動電源の多種電源電圧化に伴い、従来は均一のプレーンで構成されていた多層プリント配線板内層の電源層は、電源電圧ごとに細切れに分割された島パターン状で構成されるようになった。その結果、内層電源層の導体パターン間に不連続部分が生じ、この不連続部分により、均一なプレーンである内層グランド層(GND層)と同等の高速信号線の最短リターン電流経路が確保できなくなっている。

【0004】

また、半導体集積回路素子自体の小型化、高密度化に伴い、回路素子のフットパターンもボールグリッドアレイ(BGA)等の高密度仕様が一般化し、表層のみでの信号配線引き回しが難しくなり、スルーホールを多用して、内層を利用して配線せざるを得なくなっている。このように信号線用のスルーホールが増大すると、当該スルーホールが内層の電源層/GND層を横切る際、絶縁用の逃げ(クリアランス)が必要となるが、このクリアランスにより内層電源層/GND層に非導通部分であるスリット(均一導体パターンでの不連続部分)が生成される。このスリットがあることで、高速信号のリターン電流経路は遠回りを余儀なくされる。

【0005】

ところで、半導体集積回路の高速動作化に伴い、各回路素子間を接続する信号線上を高速信号が伝播する際、電磁妨害(EMI)等の不要輻射雑音が問題となる。また、多層プリント配線板そのものの共振による不要輻射雑音も無視できない要因となっている。これは、電子部品の高機能化や高速化に伴い、電子回路から発生する電磁波が、通信障害や電子回路の相互干渉による誤作動などを生じさせるものとして大きな問題となっている。

【0006】

一般に多層プリント配線板において、回路の高速動作に起因するEMIに対しては、高速信号線のリターン電流経路を高速信号線に一番近い内層均一プレーン上に最短経路で確保する必要があった。しかし、上述したような多種電源駆動電圧の採用により、内層電源層は均一プレーンと見なすことができなくなった。その対策として電圧の異なる導体パターン間の不連続部分にリターン電流経路を確保する場合、特許文献1では、信号線を配線した反対側の表層部品実装面の不連続部分を横断する位置に、少なくとも1個のコンデンサを実装する構造を提案している。

【0007】

また、多層プリント配線板の共振に起因するEMIに対しては、特許文献2において多層プリント配線板周辺の表層部品実装面で電源層とグランド層を接続するためのコンデンサを並べて実装する構造を提案している。

【特許文献1】特許第3610228号公報

【特許文献2】特許第3036629号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、以上で述べたいずれの方法であっても、多層プリント配線板の高密度実装化に伴う、実装部品配置および信号配線引き回しの制約があり、半導体集積回路素子の高速化に伴う動作電源電圧の多電源化に対応して、適切な位置に適切な数量のコンデンサを実装することができないため、EMI等の不要輻射雑音に対して十分な効果が得られていなかった。特に、信号線用スルーホールのクリアランスによるスリットは最短リターン電流経路形成の阻害要因であるが、根本的な対策が提案されるには至っていない。

【0009】

また、多層プリント配線板の表層に電子部品を実装する際に、通常は多層プリント配線板の端5mm程度をガイドなどで挟む等の必要があることから、電子部品を多層プリント配線板の端から5mm以内の位置に実装することは不可能であった。すなわち、特許文献2のような従来の方法では、コンデンサを多層プリント配線板の端から5mm超離して実装する必要があり、多層プリント配線板内層の電源層/GND層の外周端に相当する位置に配置することは不可能であった。したがって、コンデンサの実装位置より外側の多層プリント配線板周辺部に、内層の電源層/GND層の開放端が残り、当該部分がEMI不要輻射雑音の放射源(アンテナ)として作用するため、やはりEMI対策としては十分な効果が得られていなかった。

【0010】

さらに、内層電源層のある導体パターンの開放端で発生した不要輻射雑音は、不連続部分を隔てた先にある他の導体パターンに伝播してしまい、電子機器の誤動作の原因ともなってきた。

【0011】

本発明はこのような課題に鑑み、従来に比して動作時における不要輻射雑音の発生が低減される多層プリント配線板を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は上述の課題を解決するために、絶縁された不連続部分が設けられることによって複数の導体パターンに分割され、実装される電子部品に対してそれぞれ異なる駆動電圧を導体パターンごとに供給する電源層を内層に有し、さらに多層プリント配線板の内層のうち不連続部分が設けられた面に対して垂直方向に平行移動された面上には、複数の導体パターン同士を高周波的に接続する複数のコンデンサが実装される構成をとる。

【0013】

また、本発明は上述の課題を解決するために、絶縁された不連続部分が設けられることによって複数の導体パターンに分割され、実装される電子部品に対してそれぞれ異なる駆動電圧を導体パターンごとに供給する電源層と、基準電位を電子部品に供給するグランド層を内層に有するとともに、さらに内層に電子部品を実装することが可能な内層実装層を有し、内層実装層のうち導体パターンの周縁部に対して垂直方向に平行移動された面上には、導体パターンのいずれかとグランド層を高周波的に接続する複数のコンデンサが実装される構成をとる。

【発明の効果】

【0014】

本発明によれば、電源層の複数の導体パターン同士を高周波的に接続することによって高速信号線のリターン電流経路を最短距離で確保できるため、高速信号線により発生する高次高調波の不要輻射雑音を低減することが可能となる。

【0015】

また、電源層の導体パターンとグランド層を導体パターンの周縁部で高周波的に接続することによって、不要輻射雑音の外部への放射を抑えるので、実装された電子部品を含んで構成される電子回路の高速動作により発生する高次高調波の不要輻射雑音を低減することが可能となる。

【図面の簡単な説明】

【0016】

【図1】本発明に係る多層プリント配線板の実施例において、層を形成する面に対して垂直方向に分断した断面を示す図である。

【図2】図1に示す多層プリント配線板において、内層上における電源間バイパスコンデンサの配置を示す平面図である。

【図3】同実施例において、電源間バイパスコンデンサの配置を示す斜視図である。

【図4】図1に示す多層プリント配線板の変形例を示す、層を形成する面に対して垂直方向に分断した断面を示す図である。

【図5】本発明に係る多層プリント配線板の別の実施例において、内層上における電源グランド間バイパスコンデンサの配置を示す平面図である。

【図6】図5に示す多層プリント配線板において、層を形成する面に対して垂直方向に分断した断面を示す図である。

【図7】図5の実施例において、図6とは異なる角度で分断した断面を示す図である。

【図8】図5の実施例において、図6とは異なる場所を垂直方向に分断した断面を示す図である。

【発明を実施するための最良の形態】

【0017】

次に添付図面を参照して本発明による多層プリント配線板の実施例を詳細に説明する。図1は、全6層からなる多層プリント配線板10のうち、異種電源電圧の導体パターンを高周波的に接続する電源間バイパスコンデンサ12の1つが設けられている部分を示す断面図である。

【0018】

図2は、逐次積層法で多層プリント配線板10を製造したと仮定して、電子部品を実装する内層である内層部品実装層(L4)まで完成した段階における平面図である。この図は、多層プリント配線板10の内層に設けられている複数の電源間バイパスコンデンサ12の配置の一例を把握することを容易にするために示す図である。

【0019】

図2では説明の便宜上、第4層の下層に位置する電源層である第5層(L5)に設けられた、異種の駆動電源電圧を供給する各導体パターン14、16、18の配置を破線で示している。また、図2で表示されている一点鎖線I−Iは、図1で示す断面図の切断方向を示すためのものであり、実際の図1には、第4層から第6層のみならず、多層プリント配線板10の第1層から第6層まですべての層についての断面図が示されている。

【0020】

本実施例に係る多層プリント配線板10は、例えば中央処理装置(CPU)、ディジタル信号処理装置(DSP)等の高速動作素子駆動用として異種電源電圧を必要とする様々な電子機器等に内蔵され得る。電子機器等に内蔵された多層プリント配線板10には半導体集積回路等各種の電子部品が実装され、さらにこれらの電子部品間に高速信号を伝播可能な配線が設置されることによって、それぞれの半導体集積回路が電気的に接続され、実装された回路の駆動により電子機器等を作動させる。多層プリント配線板10に実装された電子部品の駆動電源電圧は、駆動電圧の低電圧化などの観点から各部品によって異なり、本実施例の場合、3種類の駆動電源電圧(5V、3.3V、2.5V)をそれぞれ供給する導体パターン14、16、18が設けられ、これらの導体パターン間は複数個の電源間バイパスコンデンサ12で高周波的に接続されている。

【0021】

なお、以下に述べる多層プリント配線板10の実施例は6層からなる構造である。しかし、全6層の構造に限られず、電源間バイパスコンデンサ12を実装する層がどこであるかに応じて、4層または5層以上の多層プリント配線板であれば、8層、10層、さらにそれ以上の層を有する本発明に係る多層プリント配線板を実現することも可能である。すなわち、表層部品実装層2層、電源層およびGND層の合計4層、またはさらに少なくとも1つの内層部品実装層を加えた合計5層が備わっていれば本発明を実施することが可能である。

【0022】

6層を超える多層プリント配線板としては、内層部品実装層と電源層もしくはGND層の間に信号層が追加されている多層プリント配線板、および/または内層部品実装層を多数段備えるように設計された多層プリント配線板などが考えられる。

【0023】

以下において、多層プリント配線板10の構成についてさらに詳細に説明する。多層プリント配線板10の最下層である第6層(L6)には、その表面に高速信号を出力する電子部品の実装、およびこれらの電子部品間で信号を伝播する高速信号線の配線が可能な表層部品実装層22が設けられている。電子部品の駆動電圧の値は部品によって異なる。この表層部品実装層22は、多層プリント配線板10の一方の表面を構成し、多層プリント配線板10の内側の面上には、例えばプリプレグのような絶縁材料P5が積層されている。

【0024】

絶縁材料P5上には、第5層(L5)として、多層プリント配線板10に実装される半導体集積回路等の電子部品にそれぞれ異なる駆動電源電圧を供給するための5V導体パターン14、3.3V導体パターン16、2.5V導体パターン18が配置され、第5層全体として内層電源層24が構成されている。当然のことながら、各導体パターンが供給する電圧の値は上記の値に限られず、また導体パターンの配置位置や形状、電源層全体に設置される導体パターンの個数は適宜に定め得る。

【0025】

各導体パターンの間には、異なる導体パターンとの絶縁を確保するための不連続部分が形成されている。すなわち、絶縁された不連続部分が設けられることによって電源層24は複数の導体パターン14、16、18に分割されている。また、本実施例の場合、導体パターン14、16、18から構成される電源層24の配線板端20側周縁部は、それぞれ多層プリント配線板10の配線板端20から1mm分だけ内側の位置に配置されている。かかる配置によって、電源層24のクリアランスが構成される。

【0026】

L6層上と同様に、電源層(L5)上にもプリプレグなどの絶縁材料P4が積層され、絶縁層が形成されている。絶縁材料P4には、第5層上にある各導体パターンと第4層上にある電源間バイパスコンデンサ12を最短距離で導通させるためのインナービアが形成されている。その一例として、図1では3.3V導体パターン16と電源間バイパスコンデンサ12を接続するためのインナービア26および 2.5V導体パターン18と電源間バイパスコンデンサ12を接続するためのインナービア28が示されている。最短距離による接続を実現するために、インナービア26、28は多層プリント配線板10の各層を形成する面に対して垂直方向に孔をあけられている。

【0027】

インナービア26、28は、例えば、レーザによって絶縁材料P4を貫く孔をあけた後、形成された孔を銅、銀などの導体でめっき被覆する方法、また、初めにL5層上に銀ペーストのような材料からなる円錐状の突起物(バンプ)を形成しておき、圧力をかけバンプを貫通させて絶縁材料P4にビアを形成する方法など、公知のあらゆる形成方法によって形成され得る。なお、図1で示される本実施例においては、放熱効果を高めるために、あけられた孔の全体を導電材料で充填する設計を採用している。しかしインナービア26、28は、形成された孔の壁部分のみを後述するランド30、32と接触するように銅、銀等の導電体でめっき被覆されることによって導通を図っても良い。

【0028】

絶縁材料P4上は、第4層(L4)である、各種電子部品を実装することが可能な内層部品実装層を構成している。本実施例においては、内層部品実装層のうちインナービア26、28の開口部が形成された位置の直上には、接合材料用銅箔であるランド30、32のような導電体が、インナービア26、28と電気的に接合されるように定着されている。ランド30、32は銅箔からエッチングによって形成してもよいし、銅ペースト等を印刷することによって形成してもよい。また、ランド30、32を用いる代わりに銅めっきなどを積層することによってインナービア26、28と電源間バイパスコンデンサ12を接続してもよい。

【0029】

さらに第4層上には、ランド30、32と接続されるようにして、複数個の電源間バイパスコンデンサ12が実装されている。電源間バイパスコンデンサ12は1個につき、電圧の異なる導体パターン14−16間、14−18間、16−18間のいずれかをインナービアを介して高周波的に接続する。このように各導体パターン間をそれぞれ複数個の電源間バイパスコンデンサ12で接続することによって、電源層24を全体として均一のリターンプレーンとしてみなすことができるようになる。また必要に応じて、第4層上には多層プリント配線板10の表層に実装できない他の電子部品や信号線も実装、配線され得る。

【0030】

本実施例では図2に示すとおり、電源間バイパスコンデンサ12が実装されるL4上の位置は、第5層に配置された各導体パターンの間にある不連続部分が設けられた面に対して垂直方向に平行移動された面上、すなわち不連続部分の垂直上方にあたる位置に沿っている。

【0031】

さらに、電源間バイパスコンデンサ12は、多層プリント配線板10の表層もしくは内層に配線されている高速信号線の本数および経路に合わせて、その垂直上方または下方に配置されるのが最も望ましい。この位置関係を簡略化して図示したものが図3である。第6層の表層部品実装層22に配線されている信号線22A、22B、22Cは、多層プリント配線板10の製造段階では破線で示す銅箔220を多層プリント配線板10に定着させた後、エッチングなどを行うこと等によって形成される。なお、多層プリント配線板10自体の製造段階もしくは多層プリント配線板10が内蔵される電子機器の製造時等には、表層22にはCPU、DSPといった半導体集積回路等のような電子部品40、42が実装され、形成された信号線22A、22B、22Cを介して接続される。信号線22B以外については実装される電子部品の図示を省略しているが、同様に実装接続される。また図3には、多層プリント配線板10が動作するとき、信号線22A、22B、22Cを流れる信号がそれぞれ矢印23a、23b、23cのように電子部品間を伝わるとした場合における、信号線22A、22B、22Cの垂直上方に生じるリターン電流123a、123b、123cの例が表されている。電源間バイパスコンデンサ12A、12B、12Cは、各導体パターンの間にある不連続部分の垂直上方に沿った位置、かつ信号線22A、22B、22Cの配線位置に対して垂直方向に平行移動された線上、すなわちリターン電流の生じる線上の垂直上方に実装される。このように電源間バイパスコンデンサ12A、12B、12Cが配置されることによって、最短距離に抑えられたリターン電流123a、123b、123cの経路が確保される。

【0032】

なお、高速信号線がない場合であっても、各導体パターン間に3個以上の電源間バイパスコンデンサ12を実装することが望ましい。集積回路等から発生するリプルなどのノイズのリターン電流経路となり得る電源間バイパスコンデンサ12を多数用意しておくことにより、特定の電源間バイパスコンデンサ12にノイズが集中するのを防ぎ、共振による誤動作の影響を低減させるためである。

【0033】

不連続部分に沿って電源間バイパスコンデンサ12が実装される間隔は、例えば10mmから30mmの間隔である。もっとも、電源間バイパスコンデンサ12の実装間隔は、多層プリント配線板10の大きさにより決定されるものであり、位置間隔は常に一定の値で特定されるというわけではない。

【0034】

また、使用される電源間バイパスコンデンサ12の容量は、1000pF以上の大容量品が望ましい。しかし、用いられる電源間バイパスコンデンサ12の容量はすべて一定の値に特定されるものでなく、また1000pFの電源間バイパスコンデンサ12と1mFの電源間バイパスコンデンサ12を1つおきに内層部品実装層(L4)に実装するなど、種々の組み合わせが可能である。

【0035】

ランド30、32を介しての電源間バイパスコンデンサ12とインナービア26、28との接続、ひいては電源間バイパスコンデンサ12を介しての第5層に配置された各導体パターン同士の電気的接続は、はんだ、導電性ペースト等の公知の接合材料34を用いてランド30、32と電源間バイパスコンデンサ12の端子が互いに接合されることにより実現されている。

【0036】

このように電源間バイパスコンデンサ12は多層プリント配線板10の内層に実装されるので、多層プリント配線板10の表層(L1、L6)回路実装設計の制約を受けることがない。また、電源間バイパスコンデンサ12を表層実装した場合に比べて、少なくとも多層プリント配線板10の板厚相当分だけ電気長を短くすることができる。さらに、インナービア技術を用いることで、内層間で完結して接続することで、電源間バイパスコンデンサ12を表層実装した場合に必須となるスルーホールを形成しなくてすむため、スルーホールにより生成される内層クリアランスによるスリットの影響を排除できる。

【0037】

電源間バイパスコンデンサ12などが実装された内層部品実装層(L4層)上には、プリプレグのような絶縁材料P3が積層されている。このことによって、電源間バイパスコンデンサ12と他の電子部品および配線に対する絶縁ならびに電源間バイパスコンデンサ12のより強固な定着が図られている。

【0038】

絶縁材料P3上には、L3層たる内層部品実装層があり、電子部品の実装および信号線の配線が可能である。ただし、本発明に直接関係のない要素であるため、図示および詳細な説明は省略する。

【0039】

L3層上にはさらにプリプレグのような絶縁材料P2が積層され、絶縁材料P2上にはL2層として、グランド層36(GND層36)が設けられている。GND層36は、L2層にわたって均一のプレーンであり、多層プリント配線板10に実装された電子部品(40、42など)に電位の基準を与える。

【0040】

GND層36上には、他の層間と同様、プリプレグのような絶縁材料P1が積層され、さらに絶縁材料P1上には、最上層の第1層(L1)として、駆動電圧のそれぞれ異なる高速信号を出力する電子部品の実装、またこれらの電子部品間で信号を伝播する高速信号線の配線が可能な表層部品実装層38が設けられている。電子部品等が実装される表層部品実装層38の表面は、多層プリント配線板10自体の表面の一方でもある。

【0041】

ここまで述べてきた多層プリント配線板10の断面的構成は、図1を参照して説明してきた関係上、3.3V導体パターン16と2.5V導体パターン18の間を電源間バイパスコンデンサ12で高周波的に接続する構成が主であった。しかし言うまでもなく、5V導体パターン14と3.3V導体パターン16の間、および5V導体パターン14と2.5V導体パターン18の間を電源間バイパスコンデンサ12で高周波的に接続する構成についても同様の構成をとる。

【0042】

なお、多層プリント配線板10の内層に実装される電子部品が電源間バイパスコンデンサ12のみである場合には、電源間バイパスコンデンサ12を内層部品実装層(L4)に実装し、インナービア26、28を介して異なる導体パターン同士を接続するのではなく、その代わりに、電源層24の不連続部分の近傍にある導体パターン14、16、18の周縁部に電源間バイパスコンデンサ12用のランド30、32を設け、ランド30、32上に電源間バイパスコンデンサ12を接続する、すなわちL5層の電源層24上に直接電源間バイパスコンデンサ12を実装することも可能である。その場合の断面図を図4で示す。図4の切断方向は図1と同様であり、また図1で示されている構成要素と同一の要素は同一の参照符号で表している。かかる構成をとった場合には、表層部品実装層22、38、電源層24およびGND層36の全4層からなる多層プリント配線板10を提供することも可能となる。

【0043】

続いて、本実施例に係る多層プリント配線板10の動作について述べる。多層プリント配線板10が内蔵された電子機器等が作動すると、例えば表層部品実装層22に実装される電子部品(図3参照)は電源層24からそれぞれの駆動電圧を受け取り、例えば矢印23a、23b、23cのような高速信号(高速スイッチング信号)を出力する。

【0044】

高速信号の伝播に対応して、例えば高速信号線22A、22B、22Cが配線されている表面実装層22に最も近い内層の電源層24には123a、123b、123cのようなリターン電流が誘起される。このとき、電源層24は電圧の異なる導体パターン14、16、18が配置されていることに伴う絶縁された不連続部分を有しているものの、信号線の配置に合わせて電源間バイパスコンデンサ12が備えられているために、電源層24には図1の矢印123で示すような最短経路のリターン電流経路が確保される。

【0045】

電源間バイパスコンデンサ12は従来の多層プリント配線板のように表層で実装されているのではなく、内層部品実装層(L4層)に実装されているので、多層プリント配線板10のリターン電流経路は従来の多層プリント配線板と比較して少なくとも多層プリント配線板の板厚相当分だけ電気長が短い。

【0046】

また、従来の基板とは異なり、表層部品実装層22、38に電源間バイパスコンデンサ12を実装して貫通スルーホールを設ける必要がないので、均一導体パターンであるGND層36にクリアランスのための不連続部分が形成されることもない。したがって、表面部品実装層38上に配線された信号線を伝播する信号に起因してGND層36に生じるリターン電流について、最短経路を形成する妨げとなるものはなくなる。

【0047】

このような動作の下で、高速信号線により発生する高次高調波の不要輻射に関して約10dBの低減効果が認められ、EMI特性が向上する。

【0048】

続いて、図5〜8を参照しつつ、本発明に係る他の実施例に関する説明を行う。図5〜8のいずれにおいても、先の実施例で使用された要素と同じ構成要素については、同一の参照符号で表す。

【0049】

図5は、逐次積層法で多層プリント配線板50を製造したと仮定して、内層部品実装層(L4)まで完成した段階における平面図である。この図によって、多層プリント配線板50の内層に設けられている複数の電源グランド間バイパスコンデンサ52の配置の一例を把握することが容易となる。なお、以後述べる実施例においても、電源層24の各導体パターン14、16、18の間の絶縁を確保する不連続部分の垂直上方には先の実施例で述べた電源間バイパスコンデンサ12が配置され得るが、本図面においてはその図示を省略している。

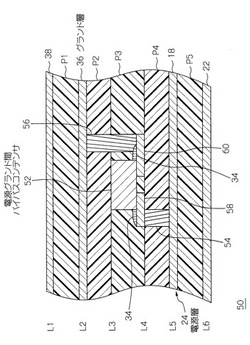

【0050】

図6ないし図8は、電源層とGND層を最短距離で接続する電源グランド間バイパスコンデンサ52を内層部品実装層(第3層/4層間)に備えた、全6層からなる多層プリント配線板50の一部を示す断面図である。図5で表示されている一点鎖線VI−VI、二点鎖線VII−VII、および一点鎖線VIII−VIIIは、それぞれ図6、図7、図8で示す断面図の切断方向を示すためのものであり、実際の図6〜8には、第4層から第6層のみならず、多層プリント配線板50の第1層から第6層まですべての層についての断面図が示されている。

【0051】

本実施例に係る多層プリント配線板50も、先述した実施例に係る多層プリント配線板10と同様、様々な電子機器等に内蔵されている。また、半導体集積回路等各種の電子部品が実装され、さらにこれらの電子部品間をつなぐ高速信号線(例えば、信号線22A、22B、22C)が配線されることによって、それぞれの電子部品が電気的に接続され、電子機器等を作動させる。

【0052】

以下において、電源グランド間バイパスコンデンサ52を備えた多層プリント配線板50の構成について詳細に説明する。ただし、先の実施例に係る多層プリント配線板10の構成と同様の部分については、省略もしくは簡略化する場合がある。

【0053】

本実施例の場合、第5層である電源層24に配置されている導体パターン14、16、18はそれぞれ、他の導体パターンとの間で所定の不連続部分を確保しつつ、多層プリント配線板50の配線板端20から1mm分だけ内側の位置に配置されている。配線板端20から各導体パターン周縁部までに存在する隙間は、電源層24のクリアランスを構成する。同様にGND層36、表層部品実装層22および38の周縁部についても、多層プリント配線板50の配線板端20から1mm分だけ内側に配置されるようにしている。

【0054】

内層部品実装層(L4)には、導体パターン14、16、18の周縁端部に対して垂直方向に平行移動された面上、すなわち垂直上方に沿って、一定の間隔をあけて複数個の電源グランド間バイパスコンデンサ52が実装されている。もっとも、本実施例において電源グランド間バイパスコンデンサ52は導体パターン14、16、18の周縁端部の垂直上方に実装されているが、多層プリント配線板50外周部においては導体パターン周縁端部の垂直上方から5mm以内の範囲で内側に実装されてもよい。EMIの低減の観点からは、導体パターン周縁端部が望ましいものの、製造あるいは配線の都合によって、導体パターン周縁端部に電源グランド間バイパスコンデンサ52を実装できない場合もある。しかし、配線板端20から5mm以内であれば低減効果の低下は少ないからである。

【0055】

このように、電源グランド間バイパスコンデンサ52が実装される位置は、内層部品実装層である第4層上であるため、電源グランド間バイパスコンデンサ52の実装について、多層プリント配線板50表面の表層回路実装設計および製造の制約を受けることはない。

【0056】

電源グランド間バイパスコンデンサ52の実装間隔は例えば10mm〜30mmである。もっとも、電源グランド間バイパスコンデンサ52の実装間隔は、多層プリント配線板50の寸法により決定されるものであり、位置間隔は常に一定の値で特定されるというわけではない。

【0057】

また、使用される電源グランド間バイパスコンデンサ52の容量は、1000pF以上の大容量品が望ましい。しかし、用いられる電源グランド間バイパスコンデンサ52の容量はすべて一定の値に特定されるものでなく、また1000pFの電源グランド間バイパスコンデンサ52と1mFの電源グランド間バイパスコンデンサ52を1つおきに配置するなど、種々の組み合わせが可能である。

【0058】

電源グランド間バイパスコンデンサ52と電源層24およびGND層36の高周波的な接続は、以下のような構成によってなされる。まず、絶縁材料P4には、第5層上にある各導体パターンの端部と第4層上にある電源グランド間バイパスコンデンサ52の端子の一方を最短距離で導通させるためのインナービア54が形成されている。最短距離による電気的接続を実現するために、インナービア54は多層プリント配線板50の各層を形成する面に対して垂直方向に孔をあけられている。

【0059】

また、絶縁材料P3からP2にかけて、第4層上にある電源グランド間バイパスコンデンサ52の端子の残る一方と第2層にあるGND層36を最短距離で導通させるためのインナービア56が形成されている。最短距離による電気的接続を実現するために、インナービア56は多層プリント配線板50の各層を形成する面に対して垂直方向に孔をあけられている。

【0060】

本実施例の場合、第4層(L4)の内層部品実装層のうち、インナービア54の開口部が形成された位置の直上には、接合材料用銅箔であるランド58のような導電体が定着されている。同様に、第4層のうちインナービア56の開口部が形成された位置の直下には、ランド60のような導電体が定着されている。

【0061】

ランド58、60を介しての電源グランド間バイパスコンデンサ52とインナービア54、56の電気的接続は、はんだ、導電性ペースト等、公知の接合材料34を用いてランド58、60と電源グランド間バイパスコンデンサ52の端子を互いに導通接合することにより実現されている。また、ランド58、60を用いる代わりに銅めっきなどを積層することによってインナービア54、56と電源グランド間バイパスコンデンサ52を接続してもよい。

【0062】

このように電源グランド間バイパスコンデンサ52を内層(L4層)に実装し、電源グランド間バイパスコンデンサ52および導体パターン18、GND層36それぞれをインナービア54、56を用いて接続すると、電源グランド間バイパスコンデンサ52を表層に実装した場合に比べて、電源層24の導体パターン端部最適位置に電源グランド間バイパスコンデンサ52を置くことができ、さらに多層プリント配線板50の板厚相当分だけ電気長を短くすることができる。また、インナービア技術を用いて内層間で接続することで、電源グランド間バイパスコンデンサ52を表層実装した場合に必須となるスルーホールおよびスルーホール周辺の内層クリアランスは不要となり、電源層24およびGND層36でのリターン電流発生時におけるスリットの影響、すなわちリターン電流経路の迂回を防止できる。

【0063】

このような構成による結果、電源グランド間バイパスコンデンサ52は、導体パターン14、16、18の周縁端部の垂直上方に沿って内層部品実装層(L4)に実装され、垂直下方または上方に延びるインナービア54、56にて電源層24およびGND層36と接続されている。そのため、図7で示すとおり、導体パターン14、16、18およびGND層36の多層プリント配線板50周縁部には、不要輻射放射源(アンテナ)となり得る開放端は残らない。もしくは、各導体パターン14、16、18およびGND層36の残余開放端を5mm以内に抑えれば、従来のプリント回路版と比べ不要輻射雑音は低減される。

【0064】

続いて、本実施例に係る多層プリント配線板50に各種の電子部品を実装した場合の動作の一例について述べる。多層プリント配線板50が内蔵された電子機器等が作動すると、電源層24やGND層36のような内層プレーンが共振を起こし、不要輻射雑音が発生する。しかし、図7で示すように、電源層24およびGND層36の端部には不要輻射雑音のアンテナとなり得る残余開放端が形成されることなく、電源グランド間バイパスコンデンサ52、インナービア54、56、および電源層24とGND層36によって、多層プリント配線板50の外周縁を囲い覆うようにしてリターン電流経路124が確保される。このように電源グランド間バイパスコンデンサ52により不要輻射雑音を外部に漏らさないことが可能となる。

【0065】

また、図8で示すように、導体パターン14、16、18の端部(多層プリント配線板50外周以外)においても、不要輻射雑音のアンテナとなり得る残余開放端が形成されることなく、電源グランド間バイパスコンデンサ52およびインナービア54、56によってリターン電流経路124が確保されるので、不要輻射雑音は不連続部分を隔てて隣接する導体パターンに伝播しない。すなわち、多層プリント配線板50外周だけでなく内側においても電源グランド間バイパスコンデンサ52を設けることによって不要輻射雑音が低減される。

【0066】

さらに、電源グランド間バイパスコンデンサ52は従来の多層プリント配線板のように表層で実装されているのではなく、内層部品実装層(L4層)に実装されているので、多層プリント配線板50のリターン経路は従来の多層プリント配線板と比較して電気長が短くなる。また、表層に電源グランド間バイパスコンデンサ52を実装する従来の基板のように貫通スルーホールを設ける必要がないので、GND層36にクリアランスのための不連続部分が形成されることもない。したがって、電源層24やGND層36に生じるリターン電流について、不連続部分によって最短のリターン経路の確保が妨げられるようなこともなくなる。

【0067】

このような動作の下で、高速信号線により発生する高次高調波の不要輻射に関して約10dBの低減効果が認められ、EMI特性が向上する。

【0068】

以上、電源間バイパスコンデンサ12および/または電源グランド間バイパスコンデンサ52を内層部品実装層に実装した多層プリント配線板10、50について説明したが、本発明の実施形態はこれに限られるものではなく、本発明の実施が可能である限りにおいて適宜に設計の変更をなし得る。もちろん製造方法のいかんを問わず、完成された回路装置が多層プリント配線板10、50と同様の構造を有すれば、本発明に特有の効果が得られる。

【符号の説明】

【0069】

10 多層プリント配線板

12 電源間バイパスコンデンサ

14 5V導体パターン

16 3.3V導体パターン

18 2.5V導体パターン

24 電源層

26、28 インナービア

34 GND層

50 多層プリント配線板

52 電源グランド間バイパスコンデンサ

54、56 インナービア

【技術分野】

【0001】

本発明は、多層プリント配線板、より具体的には、機能モジュールとして使用される多層プリント配線板に関する。

【背景技術】

【0002】

近年、多層プリント配線板(プリント回路板、プリント基板)に実装する中央処理装置(CPU)、ディジタル信号処理装置(DSP)等といった半導体集積回路の小型高速動作化が求められる中で、回路素子の発熱対策として半導体集積回路を駆動する電源の低電圧化が進められている。また、外部インターフェースとの整合を取るため、回路素子駆動電圧は、例えば5V、3.3V、2.5V、1.8Vなど多種電源電圧の併用が求められている。一方で、多層プリント配線板を内蔵する製品の小型化要求に伴い、多層プリント配線板も小型化、高密度化が求められている。

【0003】

駆動電源の多種電源電圧化に伴い、従来は均一のプレーンで構成されていた多層プリント配線板内層の電源層は、電源電圧ごとに細切れに分割された島パターン状で構成されるようになった。その結果、内層電源層の導体パターン間に不連続部分が生じ、この不連続部分により、均一なプレーンである内層グランド層(GND層)と同等の高速信号線の最短リターン電流経路が確保できなくなっている。

【0004】

また、半導体集積回路素子自体の小型化、高密度化に伴い、回路素子のフットパターンもボールグリッドアレイ(BGA)等の高密度仕様が一般化し、表層のみでの信号配線引き回しが難しくなり、スルーホールを多用して、内層を利用して配線せざるを得なくなっている。このように信号線用のスルーホールが増大すると、当該スルーホールが内層の電源層/GND層を横切る際、絶縁用の逃げ(クリアランス)が必要となるが、このクリアランスにより内層電源層/GND層に非導通部分であるスリット(均一導体パターンでの不連続部分)が生成される。このスリットがあることで、高速信号のリターン電流経路は遠回りを余儀なくされる。

【0005】

ところで、半導体集積回路の高速動作化に伴い、各回路素子間を接続する信号線上を高速信号が伝播する際、電磁妨害(EMI)等の不要輻射雑音が問題となる。また、多層プリント配線板そのものの共振による不要輻射雑音も無視できない要因となっている。これは、電子部品の高機能化や高速化に伴い、電子回路から発生する電磁波が、通信障害や電子回路の相互干渉による誤作動などを生じさせるものとして大きな問題となっている。

【0006】

一般に多層プリント配線板において、回路の高速動作に起因するEMIに対しては、高速信号線のリターン電流経路を高速信号線に一番近い内層均一プレーン上に最短経路で確保する必要があった。しかし、上述したような多種電源駆動電圧の採用により、内層電源層は均一プレーンと見なすことができなくなった。その対策として電圧の異なる導体パターン間の不連続部分にリターン電流経路を確保する場合、特許文献1では、信号線を配線した反対側の表層部品実装面の不連続部分を横断する位置に、少なくとも1個のコンデンサを実装する構造を提案している。

【0007】

また、多層プリント配線板の共振に起因するEMIに対しては、特許文献2において多層プリント配線板周辺の表層部品実装面で電源層とグランド層を接続するためのコンデンサを並べて実装する構造を提案している。

【特許文献1】特許第3610228号公報

【特許文献2】特許第3036629号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、以上で述べたいずれの方法であっても、多層プリント配線板の高密度実装化に伴う、実装部品配置および信号配線引き回しの制約があり、半導体集積回路素子の高速化に伴う動作電源電圧の多電源化に対応して、適切な位置に適切な数量のコンデンサを実装することができないため、EMI等の不要輻射雑音に対して十分な効果が得られていなかった。特に、信号線用スルーホールのクリアランスによるスリットは最短リターン電流経路形成の阻害要因であるが、根本的な対策が提案されるには至っていない。

【0009】

また、多層プリント配線板の表層に電子部品を実装する際に、通常は多層プリント配線板の端5mm程度をガイドなどで挟む等の必要があることから、電子部品を多層プリント配線板の端から5mm以内の位置に実装することは不可能であった。すなわち、特許文献2のような従来の方法では、コンデンサを多層プリント配線板の端から5mm超離して実装する必要があり、多層プリント配線板内層の電源層/GND層の外周端に相当する位置に配置することは不可能であった。したがって、コンデンサの実装位置より外側の多層プリント配線板周辺部に、内層の電源層/GND層の開放端が残り、当該部分がEMI不要輻射雑音の放射源(アンテナ)として作用するため、やはりEMI対策としては十分な効果が得られていなかった。

【0010】

さらに、内層電源層のある導体パターンの開放端で発生した不要輻射雑音は、不連続部分を隔てた先にある他の導体パターンに伝播してしまい、電子機器の誤動作の原因ともなってきた。

【0011】

本発明はこのような課題に鑑み、従来に比して動作時における不要輻射雑音の発生が低減される多層プリント配線板を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は上述の課題を解決するために、絶縁された不連続部分が設けられることによって複数の導体パターンに分割され、実装される電子部品に対してそれぞれ異なる駆動電圧を導体パターンごとに供給する電源層を内層に有し、さらに多層プリント配線板の内層のうち不連続部分が設けられた面に対して垂直方向に平行移動された面上には、複数の導体パターン同士を高周波的に接続する複数のコンデンサが実装される構成をとる。

【0013】

また、本発明は上述の課題を解決するために、絶縁された不連続部分が設けられることによって複数の導体パターンに分割され、実装される電子部品に対してそれぞれ異なる駆動電圧を導体パターンごとに供給する電源層と、基準電位を電子部品に供給するグランド層を内層に有するとともに、さらに内層に電子部品を実装することが可能な内層実装層を有し、内層実装層のうち導体パターンの周縁部に対して垂直方向に平行移動された面上には、導体パターンのいずれかとグランド層を高周波的に接続する複数のコンデンサが実装される構成をとる。

【発明の効果】

【0014】

本発明によれば、電源層の複数の導体パターン同士を高周波的に接続することによって高速信号線のリターン電流経路を最短距離で確保できるため、高速信号線により発生する高次高調波の不要輻射雑音を低減することが可能となる。

【0015】

また、電源層の導体パターンとグランド層を導体パターンの周縁部で高周波的に接続することによって、不要輻射雑音の外部への放射を抑えるので、実装された電子部品を含んで構成される電子回路の高速動作により発生する高次高調波の不要輻射雑音を低減することが可能となる。

【図面の簡単な説明】

【0016】

【図1】本発明に係る多層プリント配線板の実施例において、層を形成する面に対して垂直方向に分断した断面を示す図である。

【図2】図1に示す多層プリント配線板において、内層上における電源間バイパスコンデンサの配置を示す平面図である。

【図3】同実施例において、電源間バイパスコンデンサの配置を示す斜視図である。

【図4】図1に示す多層プリント配線板の変形例を示す、層を形成する面に対して垂直方向に分断した断面を示す図である。

【図5】本発明に係る多層プリント配線板の別の実施例において、内層上における電源グランド間バイパスコンデンサの配置を示す平面図である。

【図6】図5に示す多層プリント配線板において、層を形成する面に対して垂直方向に分断した断面を示す図である。

【図7】図5の実施例において、図6とは異なる角度で分断した断面を示す図である。

【図8】図5の実施例において、図6とは異なる場所を垂直方向に分断した断面を示す図である。

【発明を実施するための最良の形態】

【0017】

次に添付図面を参照して本発明による多層プリント配線板の実施例を詳細に説明する。図1は、全6層からなる多層プリント配線板10のうち、異種電源電圧の導体パターンを高周波的に接続する電源間バイパスコンデンサ12の1つが設けられている部分を示す断面図である。

【0018】

図2は、逐次積層法で多層プリント配線板10を製造したと仮定して、電子部品を実装する内層である内層部品実装層(L4)まで完成した段階における平面図である。この図は、多層プリント配線板10の内層に設けられている複数の電源間バイパスコンデンサ12の配置の一例を把握することを容易にするために示す図である。

【0019】

図2では説明の便宜上、第4層の下層に位置する電源層である第5層(L5)に設けられた、異種の駆動電源電圧を供給する各導体パターン14、16、18の配置を破線で示している。また、図2で表示されている一点鎖線I−Iは、図1で示す断面図の切断方向を示すためのものであり、実際の図1には、第4層から第6層のみならず、多層プリント配線板10の第1層から第6層まですべての層についての断面図が示されている。

【0020】

本実施例に係る多層プリント配線板10は、例えば中央処理装置(CPU)、ディジタル信号処理装置(DSP)等の高速動作素子駆動用として異種電源電圧を必要とする様々な電子機器等に内蔵され得る。電子機器等に内蔵された多層プリント配線板10には半導体集積回路等各種の電子部品が実装され、さらにこれらの電子部品間に高速信号を伝播可能な配線が設置されることによって、それぞれの半導体集積回路が電気的に接続され、実装された回路の駆動により電子機器等を作動させる。多層プリント配線板10に実装された電子部品の駆動電源電圧は、駆動電圧の低電圧化などの観点から各部品によって異なり、本実施例の場合、3種類の駆動電源電圧(5V、3.3V、2.5V)をそれぞれ供給する導体パターン14、16、18が設けられ、これらの導体パターン間は複数個の電源間バイパスコンデンサ12で高周波的に接続されている。

【0021】

なお、以下に述べる多層プリント配線板10の実施例は6層からなる構造である。しかし、全6層の構造に限られず、電源間バイパスコンデンサ12を実装する層がどこであるかに応じて、4層または5層以上の多層プリント配線板であれば、8層、10層、さらにそれ以上の層を有する本発明に係る多層プリント配線板を実現することも可能である。すなわち、表層部品実装層2層、電源層およびGND層の合計4層、またはさらに少なくとも1つの内層部品実装層を加えた合計5層が備わっていれば本発明を実施することが可能である。

【0022】

6層を超える多層プリント配線板としては、内層部品実装層と電源層もしくはGND層の間に信号層が追加されている多層プリント配線板、および/または内層部品実装層を多数段備えるように設計された多層プリント配線板などが考えられる。

【0023】

以下において、多層プリント配線板10の構成についてさらに詳細に説明する。多層プリント配線板10の最下層である第6層(L6)には、その表面に高速信号を出力する電子部品の実装、およびこれらの電子部品間で信号を伝播する高速信号線の配線が可能な表層部品実装層22が設けられている。電子部品の駆動電圧の値は部品によって異なる。この表層部品実装層22は、多層プリント配線板10の一方の表面を構成し、多層プリント配線板10の内側の面上には、例えばプリプレグのような絶縁材料P5が積層されている。

【0024】

絶縁材料P5上には、第5層(L5)として、多層プリント配線板10に実装される半導体集積回路等の電子部品にそれぞれ異なる駆動電源電圧を供給するための5V導体パターン14、3.3V導体パターン16、2.5V導体パターン18が配置され、第5層全体として内層電源層24が構成されている。当然のことながら、各導体パターンが供給する電圧の値は上記の値に限られず、また導体パターンの配置位置や形状、電源層全体に設置される導体パターンの個数は適宜に定め得る。

【0025】

各導体パターンの間には、異なる導体パターンとの絶縁を確保するための不連続部分が形成されている。すなわち、絶縁された不連続部分が設けられることによって電源層24は複数の導体パターン14、16、18に分割されている。また、本実施例の場合、導体パターン14、16、18から構成される電源層24の配線板端20側周縁部は、それぞれ多層プリント配線板10の配線板端20から1mm分だけ内側の位置に配置されている。かかる配置によって、電源層24のクリアランスが構成される。

【0026】

L6層上と同様に、電源層(L5)上にもプリプレグなどの絶縁材料P4が積層され、絶縁層が形成されている。絶縁材料P4には、第5層上にある各導体パターンと第4層上にある電源間バイパスコンデンサ12を最短距離で導通させるためのインナービアが形成されている。その一例として、図1では3.3V導体パターン16と電源間バイパスコンデンサ12を接続するためのインナービア26および 2.5V導体パターン18と電源間バイパスコンデンサ12を接続するためのインナービア28が示されている。最短距離による接続を実現するために、インナービア26、28は多層プリント配線板10の各層を形成する面に対して垂直方向に孔をあけられている。

【0027】

インナービア26、28は、例えば、レーザによって絶縁材料P4を貫く孔をあけた後、形成された孔を銅、銀などの導体でめっき被覆する方法、また、初めにL5層上に銀ペーストのような材料からなる円錐状の突起物(バンプ)を形成しておき、圧力をかけバンプを貫通させて絶縁材料P4にビアを形成する方法など、公知のあらゆる形成方法によって形成され得る。なお、図1で示される本実施例においては、放熱効果を高めるために、あけられた孔の全体を導電材料で充填する設計を採用している。しかしインナービア26、28は、形成された孔の壁部分のみを後述するランド30、32と接触するように銅、銀等の導電体でめっき被覆されることによって導通を図っても良い。

【0028】

絶縁材料P4上は、第4層(L4)である、各種電子部品を実装することが可能な内層部品実装層を構成している。本実施例においては、内層部品実装層のうちインナービア26、28の開口部が形成された位置の直上には、接合材料用銅箔であるランド30、32のような導電体が、インナービア26、28と電気的に接合されるように定着されている。ランド30、32は銅箔からエッチングによって形成してもよいし、銅ペースト等を印刷することによって形成してもよい。また、ランド30、32を用いる代わりに銅めっきなどを積層することによってインナービア26、28と電源間バイパスコンデンサ12を接続してもよい。

【0029】

さらに第4層上には、ランド30、32と接続されるようにして、複数個の電源間バイパスコンデンサ12が実装されている。電源間バイパスコンデンサ12は1個につき、電圧の異なる導体パターン14−16間、14−18間、16−18間のいずれかをインナービアを介して高周波的に接続する。このように各導体パターン間をそれぞれ複数個の電源間バイパスコンデンサ12で接続することによって、電源層24を全体として均一のリターンプレーンとしてみなすことができるようになる。また必要に応じて、第4層上には多層プリント配線板10の表層に実装できない他の電子部品や信号線も実装、配線され得る。

【0030】

本実施例では図2に示すとおり、電源間バイパスコンデンサ12が実装されるL4上の位置は、第5層に配置された各導体パターンの間にある不連続部分が設けられた面に対して垂直方向に平行移動された面上、すなわち不連続部分の垂直上方にあたる位置に沿っている。

【0031】

さらに、電源間バイパスコンデンサ12は、多層プリント配線板10の表層もしくは内層に配線されている高速信号線の本数および経路に合わせて、その垂直上方または下方に配置されるのが最も望ましい。この位置関係を簡略化して図示したものが図3である。第6層の表層部品実装層22に配線されている信号線22A、22B、22Cは、多層プリント配線板10の製造段階では破線で示す銅箔220を多層プリント配線板10に定着させた後、エッチングなどを行うこと等によって形成される。なお、多層プリント配線板10自体の製造段階もしくは多層プリント配線板10が内蔵される電子機器の製造時等には、表層22にはCPU、DSPといった半導体集積回路等のような電子部品40、42が実装され、形成された信号線22A、22B、22Cを介して接続される。信号線22B以外については実装される電子部品の図示を省略しているが、同様に実装接続される。また図3には、多層プリント配線板10が動作するとき、信号線22A、22B、22Cを流れる信号がそれぞれ矢印23a、23b、23cのように電子部品間を伝わるとした場合における、信号線22A、22B、22Cの垂直上方に生じるリターン電流123a、123b、123cの例が表されている。電源間バイパスコンデンサ12A、12B、12Cは、各導体パターンの間にある不連続部分の垂直上方に沿った位置、かつ信号線22A、22B、22Cの配線位置に対して垂直方向に平行移動された線上、すなわちリターン電流の生じる線上の垂直上方に実装される。このように電源間バイパスコンデンサ12A、12B、12Cが配置されることによって、最短距離に抑えられたリターン電流123a、123b、123cの経路が確保される。

【0032】

なお、高速信号線がない場合であっても、各導体パターン間に3個以上の電源間バイパスコンデンサ12を実装することが望ましい。集積回路等から発生するリプルなどのノイズのリターン電流経路となり得る電源間バイパスコンデンサ12を多数用意しておくことにより、特定の電源間バイパスコンデンサ12にノイズが集中するのを防ぎ、共振による誤動作の影響を低減させるためである。

【0033】

不連続部分に沿って電源間バイパスコンデンサ12が実装される間隔は、例えば10mmから30mmの間隔である。もっとも、電源間バイパスコンデンサ12の実装間隔は、多層プリント配線板10の大きさにより決定されるものであり、位置間隔は常に一定の値で特定されるというわけではない。

【0034】

また、使用される電源間バイパスコンデンサ12の容量は、1000pF以上の大容量品が望ましい。しかし、用いられる電源間バイパスコンデンサ12の容量はすべて一定の値に特定されるものでなく、また1000pFの電源間バイパスコンデンサ12と1mFの電源間バイパスコンデンサ12を1つおきに内層部品実装層(L4)に実装するなど、種々の組み合わせが可能である。

【0035】

ランド30、32を介しての電源間バイパスコンデンサ12とインナービア26、28との接続、ひいては電源間バイパスコンデンサ12を介しての第5層に配置された各導体パターン同士の電気的接続は、はんだ、導電性ペースト等の公知の接合材料34を用いてランド30、32と電源間バイパスコンデンサ12の端子が互いに接合されることにより実現されている。

【0036】

このように電源間バイパスコンデンサ12は多層プリント配線板10の内層に実装されるので、多層プリント配線板10の表層(L1、L6)回路実装設計の制約を受けることがない。また、電源間バイパスコンデンサ12を表層実装した場合に比べて、少なくとも多層プリント配線板10の板厚相当分だけ電気長を短くすることができる。さらに、インナービア技術を用いることで、内層間で完結して接続することで、電源間バイパスコンデンサ12を表層実装した場合に必須となるスルーホールを形成しなくてすむため、スルーホールにより生成される内層クリアランスによるスリットの影響を排除できる。

【0037】

電源間バイパスコンデンサ12などが実装された内層部品実装層(L4層)上には、プリプレグのような絶縁材料P3が積層されている。このことによって、電源間バイパスコンデンサ12と他の電子部品および配線に対する絶縁ならびに電源間バイパスコンデンサ12のより強固な定着が図られている。

【0038】

絶縁材料P3上には、L3層たる内層部品実装層があり、電子部品の実装および信号線の配線が可能である。ただし、本発明に直接関係のない要素であるため、図示および詳細な説明は省略する。

【0039】

L3層上にはさらにプリプレグのような絶縁材料P2が積層され、絶縁材料P2上にはL2層として、グランド層36(GND層36)が設けられている。GND層36は、L2層にわたって均一のプレーンであり、多層プリント配線板10に実装された電子部品(40、42など)に電位の基準を与える。

【0040】

GND層36上には、他の層間と同様、プリプレグのような絶縁材料P1が積層され、さらに絶縁材料P1上には、最上層の第1層(L1)として、駆動電圧のそれぞれ異なる高速信号を出力する電子部品の実装、またこれらの電子部品間で信号を伝播する高速信号線の配線が可能な表層部品実装層38が設けられている。電子部品等が実装される表層部品実装層38の表面は、多層プリント配線板10自体の表面の一方でもある。

【0041】

ここまで述べてきた多層プリント配線板10の断面的構成は、図1を参照して説明してきた関係上、3.3V導体パターン16と2.5V導体パターン18の間を電源間バイパスコンデンサ12で高周波的に接続する構成が主であった。しかし言うまでもなく、5V導体パターン14と3.3V導体パターン16の間、および5V導体パターン14と2.5V導体パターン18の間を電源間バイパスコンデンサ12で高周波的に接続する構成についても同様の構成をとる。

【0042】

なお、多層プリント配線板10の内層に実装される電子部品が電源間バイパスコンデンサ12のみである場合には、電源間バイパスコンデンサ12を内層部品実装層(L4)に実装し、インナービア26、28を介して異なる導体パターン同士を接続するのではなく、その代わりに、電源層24の不連続部分の近傍にある導体パターン14、16、18の周縁部に電源間バイパスコンデンサ12用のランド30、32を設け、ランド30、32上に電源間バイパスコンデンサ12を接続する、すなわちL5層の電源層24上に直接電源間バイパスコンデンサ12を実装することも可能である。その場合の断面図を図4で示す。図4の切断方向は図1と同様であり、また図1で示されている構成要素と同一の要素は同一の参照符号で表している。かかる構成をとった場合には、表層部品実装層22、38、電源層24およびGND層36の全4層からなる多層プリント配線板10を提供することも可能となる。

【0043】

続いて、本実施例に係る多層プリント配線板10の動作について述べる。多層プリント配線板10が内蔵された電子機器等が作動すると、例えば表層部品実装層22に実装される電子部品(図3参照)は電源層24からそれぞれの駆動電圧を受け取り、例えば矢印23a、23b、23cのような高速信号(高速スイッチング信号)を出力する。

【0044】

高速信号の伝播に対応して、例えば高速信号線22A、22B、22Cが配線されている表面実装層22に最も近い内層の電源層24には123a、123b、123cのようなリターン電流が誘起される。このとき、電源層24は電圧の異なる導体パターン14、16、18が配置されていることに伴う絶縁された不連続部分を有しているものの、信号線の配置に合わせて電源間バイパスコンデンサ12が備えられているために、電源層24には図1の矢印123で示すような最短経路のリターン電流経路が確保される。

【0045】

電源間バイパスコンデンサ12は従来の多層プリント配線板のように表層で実装されているのではなく、内層部品実装層(L4層)に実装されているので、多層プリント配線板10のリターン電流経路は従来の多層プリント配線板と比較して少なくとも多層プリント配線板の板厚相当分だけ電気長が短い。

【0046】

また、従来の基板とは異なり、表層部品実装層22、38に電源間バイパスコンデンサ12を実装して貫通スルーホールを設ける必要がないので、均一導体パターンであるGND層36にクリアランスのための不連続部分が形成されることもない。したがって、表面部品実装層38上に配線された信号線を伝播する信号に起因してGND層36に生じるリターン電流について、最短経路を形成する妨げとなるものはなくなる。

【0047】

このような動作の下で、高速信号線により発生する高次高調波の不要輻射に関して約10dBの低減効果が認められ、EMI特性が向上する。

【0048】

続いて、図5〜8を参照しつつ、本発明に係る他の実施例に関する説明を行う。図5〜8のいずれにおいても、先の実施例で使用された要素と同じ構成要素については、同一の参照符号で表す。

【0049】

図5は、逐次積層法で多層プリント配線板50を製造したと仮定して、内層部品実装層(L4)まで完成した段階における平面図である。この図によって、多層プリント配線板50の内層に設けられている複数の電源グランド間バイパスコンデンサ52の配置の一例を把握することが容易となる。なお、以後述べる実施例においても、電源層24の各導体パターン14、16、18の間の絶縁を確保する不連続部分の垂直上方には先の実施例で述べた電源間バイパスコンデンサ12が配置され得るが、本図面においてはその図示を省略している。

【0050】

図6ないし図8は、電源層とGND層を最短距離で接続する電源グランド間バイパスコンデンサ52を内層部品実装層(第3層/4層間)に備えた、全6層からなる多層プリント配線板50の一部を示す断面図である。図5で表示されている一点鎖線VI−VI、二点鎖線VII−VII、および一点鎖線VIII−VIIIは、それぞれ図6、図7、図8で示す断面図の切断方向を示すためのものであり、実際の図6〜8には、第4層から第6層のみならず、多層プリント配線板50の第1層から第6層まですべての層についての断面図が示されている。

【0051】

本実施例に係る多層プリント配線板50も、先述した実施例に係る多層プリント配線板10と同様、様々な電子機器等に内蔵されている。また、半導体集積回路等各種の電子部品が実装され、さらにこれらの電子部品間をつなぐ高速信号線(例えば、信号線22A、22B、22C)が配線されることによって、それぞれの電子部品が電気的に接続され、電子機器等を作動させる。

【0052】

以下において、電源グランド間バイパスコンデンサ52を備えた多層プリント配線板50の構成について詳細に説明する。ただし、先の実施例に係る多層プリント配線板10の構成と同様の部分については、省略もしくは簡略化する場合がある。

【0053】

本実施例の場合、第5層である電源層24に配置されている導体パターン14、16、18はそれぞれ、他の導体パターンとの間で所定の不連続部分を確保しつつ、多層プリント配線板50の配線板端20から1mm分だけ内側の位置に配置されている。配線板端20から各導体パターン周縁部までに存在する隙間は、電源層24のクリアランスを構成する。同様にGND層36、表層部品実装層22および38の周縁部についても、多層プリント配線板50の配線板端20から1mm分だけ内側に配置されるようにしている。

【0054】

内層部品実装層(L4)には、導体パターン14、16、18の周縁端部に対して垂直方向に平行移動された面上、すなわち垂直上方に沿って、一定の間隔をあけて複数個の電源グランド間バイパスコンデンサ52が実装されている。もっとも、本実施例において電源グランド間バイパスコンデンサ52は導体パターン14、16、18の周縁端部の垂直上方に実装されているが、多層プリント配線板50外周部においては導体パターン周縁端部の垂直上方から5mm以内の範囲で内側に実装されてもよい。EMIの低減の観点からは、導体パターン周縁端部が望ましいものの、製造あるいは配線の都合によって、導体パターン周縁端部に電源グランド間バイパスコンデンサ52を実装できない場合もある。しかし、配線板端20から5mm以内であれば低減効果の低下は少ないからである。

【0055】

このように、電源グランド間バイパスコンデンサ52が実装される位置は、内層部品実装層である第4層上であるため、電源グランド間バイパスコンデンサ52の実装について、多層プリント配線板50表面の表層回路実装設計および製造の制約を受けることはない。

【0056】

電源グランド間バイパスコンデンサ52の実装間隔は例えば10mm〜30mmである。もっとも、電源グランド間バイパスコンデンサ52の実装間隔は、多層プリント配線板50の寸法により決定されるものであり、位置間隔は常に一定の値で特定されるというわけではない。

【0057】

また、使用される電源グランド間バイパスコンデンサ52の容量は、1000pF以上の大容量品が望ましい。しかし、用いられる電源グランド間バイパスコンデンサ52の容量はすべて一定の値に特定されるものでなく、また1000pFの電源グランド間バイパスコンデンサ52と1mFの電源グランド間バイパスコンデンサ52を1つおきに配置するなど、種々の組み合わせが可能である。

【0058】

電源グランド間バイパスコンデンサ52と電源層24およびGND層36の高周波的な接続は、以下のような構成によってなされる。まず、絶縁材料P4には、第5層上にある各導体パターンの端部と第4層上にある電源グランド間バイパスコンデンサ52の端子の一方を最短距離で導通させるためのインナービア54が形成されている。最短距離による電気的接続を実現するために、インナービア54は多層プリント配線板50の各層を形成する面に対して垂直方向に孔をあけられている。

【0059】

また、絶縁材料P3からP2にかけて、第4層上にある電源グランド間バイパスコンデンサ52の端子の残る一方と第2層にあるGND層36を最短距離で導通させるためのインナービア56が形成されている。最短距離による電気的接続を実現するために、インナービア56は多層プリント配線板50の各層を形成する面に対して垂直方向に孔をあけられている。

【0060】

本実施例の場合、第4層(L4)の内層部品実装層のうち、インナービア54の開口部が形成された位置の直上には、接合材料用銅箔であるランド58のような導電体が定着されている。同様に、第4層のうちインナービア56の開口部が形成された位置の直下には、ランド60のような導電体が定着されている。

【0061】

ランド58、60を介しての電源グランド間バイパスコンデンサ52とインナービア54、56の電気的接続は、はんだ、導電性ペースト等、公知の接合材料34を用いてランド58、60と電源グランド間バイパスコンデンサ52の端子を互いに導通接合することにより実現されている。また、ランド58、60を用いる代わりに銅めっきなどを積層することによってインナービア54、56と電源グランド間バイパスコンデンサ52を接続してもよい。

【0062】

このように電源グランド間バイパスコンデンサ52を内層(L4層)に実装し、電源グランド間バイパスコンデンサ52および導体パターン18、GND層36それぞれをインナービア54、56を用いて接続すると、電源グランド間バイパスコンデンサ52を表層に実装した場合に比べて、電源層24の導体パターン端部最適位置に電源グランド間バイパスコンデンサ52を置くことができ、さらに多層プリント配線板50の板厚相当分だけ電気長を短くすることができる。また、インナービア技術を用いて内層間で接続することで、電源グランド間バイパスコンデンサ52を表層実装した場合に必須となるスルーホールおよびスルーホール周辺の内層クリアランスは不要となり、電源層24およびGND層36でのリターン電流発生時におけるスリットの影響、すなわちリターン電流経路の迂回を防止できる。

【0063】

このような構成による結果、電源グランド間バイパスコンデンサ52は、導体パターン14、16、18の周縁端部の垂直上方に沿って内層部品実装層(L4)に実装され、垂直下方または上方に延びるインナービア54、56にて電源層24およびGND層36と接続されている。そのため、図7で示すとおり、導体パターン14、16、18およびGND層36の多層プリント配線板50周縁部には、不要輻射放射源(アンテナ)となり得る開放端は残らない。もしくは、各導体パターン14、16、18およびGND層36の残余開放端を5mm以内に抑えれば、従来のプリント回路版と比べ不要輻射雑音は低減される。

【0064】

続いて、本実施例に係る多層プリント配線板50に各種の電子部品を実装した場合の動作の一例について述べる。多層プリント配線板50が内蔵された電子機器等が作動すると、電源層24やGND層36のような内層プレーンが共振を起こし、不要輻射雑音が発生する。しかし、図7で示すように、電源層24およびGND層36の端部には不要輻射雑音のアンテナとなり得る残余開放端が形成されることなく、電源グランド間バイパスコンデンサ52、インナービア54、56、および電源層24とGND層36によって、多層プリント配線板50の外周縁を囲い覆うようにしてリターン電流経路124が確保される。このように電源グランド間バイパスコンデンサ52により不要輻射雑音を外部に漏らさないことが可能となる。

【0065】

また、図8で示すように、導体パターン14、16、18の端部(多層プリント配線板50外周以外)においても、不要輻射雑音のアンテナとなり得る残余開放端が形成されることなく、電源グランド間バイパスコンデンサ52およびインナービア54、56によってリターン電流経路124が確保されるので、不要輻射雑音は不連続部分を隔てて隣接する導体パターンに伝播しない。すなわち、多層プリント配線板50外周だけでなく内側においても電源グランド間バイパスコンデンサ52を設けることによって不要輻射雑音が低減される。

【0066】

さらに、電源グランド間バイパスコンデンサ52は従来の多層プリント配線板のように表層で実装されているのではなく、内層部品実装層(L4層)に実装されているので、多層プリント配線板50のリターン経路は従来の多層プリント配線板と比較して電気長が短くなる。また、表層に電源グランド間バイパスコンデンサ52を実装する従来の基板のように貫通スルーホールを設ける必要がないので、GND層36にクリアランスのための不連続部分が形成されることもない。したがって、電源層24やGND層36に生じるリターン電流について、不連続部分によって最短のリターン経路の確保が妨げられるようなこともなくなる。

【0067】

このような動作の下で、高速信号線により発生する高次高調波の不要輻射に関して約10dBの低減効果が認められ、EMI特性が向上する。

【0068】

以上、電源間バイパスコンデンサ12および/または電源グランド間バイパスコンデンサ52を内層部品実装層に実装した多層プリント配線板10、50について説明したが、本発明の実施形態はこれに限られるものではなく、本発明の実施が可能である限りにおいて適宜に設計の変更をなし得る。もちろん製造方法のいかんを問わず、完成された回路装置が多層プリント配線板10、50と同様の構造を有すれば、本発明に特有の効果が得られる。

【符号の説明】

【0069】

10 多層プリント配線板

12 電源間バイパスコンデンサ

14 5V導体パターン

16 3.3V導体パターン

18 2.5V導体パターン

24 電源層

26、28 インナービア

34 GND層

50 多層プリント配線板

52 電源グランド間バイパスコンデンサ

54、56 インナービア

【特許請求の範囲】

【請求項1】

絶縁された不連続部分が設けられることによって複数の導体パターンに分割され、実装される電子部品に対してそれぞれ異なる駆動電圧を前記導体パターンごとに供給する電源層と、

基準電位を前記電子部品に供給するグランド層を内層に有する多層プリント配線板において、

該多層プリント配線板はさらに内層に前記電子部品を実装することが可能な内層実装層を有し、該内層実装層のうち前記導体パターンの周縁部に対して垂直方向に平行移動された面上には、前記導体パターンと前記グランド層を高周波的に接続する複数のコンデンサが実装されることを特徴とする多層プリント配線板。

【請求項2】

請求項1に記載の多層プリント配線板において、前記コンデンサは、前記内層実装層の面上のうち、前記導体パターンの端部から内側5mm以内の面に対して垂直方向に平行移動された面上に実装されていることを特徴とする多層プリント配線板。

【請求項3】

請求項1または2に記載の多層プリント配線板において、前記内層実装層と前記電源層および前記グランド層の間には絶縁体からなる絶縁層が設けられ、該絶縁体層には前記導体パターンのいずれかおよび前記グランド層と前記コンデンサを導通させるインナービアが形成されていることを特徴とする多層プリント配線板。

【請求項1】

絶縁された不連続部分が設けられることによって複数の導体パターンに分割され、実装される電子部品に対してそれぞれ異なる駆動電圧を前記導体パターンごとに供給する電源層と、

基準電位を前記電子部品に供給するグランド層を内層に有する多層プリント配線板において、

該多層プリント配線板はさらに内層に前記電子部品を実装することが可能な内層実装層を有し、該内層実装層のうち前記導体パターンの周縁部に対して垂直方向に平行移動された面上には、前記導体パターンと前記グランド層を高周波的に接続する複数のコンデンサが実装されることを特徴とする多層プリント配線板。

【請求項2】

請求項1に記載の多層プリント配線板において、前記コンデンサは、前記内層実装層の面上のうち、前記導体パターンの端部から内側5mm以内の面に対して垂直方向に平行移動された面上に実装されていることを特徴とする多層プリント配線板。

【請求項3】

請求項1または2に記載の多層プリント配線板において、前記内層実装層と前記電源層および前記グランド層の間には絶縁体からなる絶縁層が設けられ、該絶縁体層には前記導体パターンのいずれかおよび前記グランド層と前記コンデンサを導通させるインナービアが形成されていることを特徴とする多層プリント配線板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−38451(P2013−38451A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2012−231648(P2012−231648)

【出願日】平成24年10月19日(2012.10.19)

【分割の表示】特願2008−223251(P2008−223251)の分割

【原出願日】平成20年9月1日(2008.9.1)

【出願人】(591020663)長野沖電気株式会社 (9)

【出願人】(592258937)沖プリンテッドサーキット株式会社 (18)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成24年10月19日(2012.10.19)

【分割の表示】特願2008−223251(P2008−223251)の分割

【原出願日】平成20年9月1日(2008.9.1)

【出願人】(591020663)長野沖電気株式会社 (9)

【出願人】(592258937)沖プリンテッドサーキット株式会社 (18)

【Fターム(参考)】

[ Back to top ]