多層基板およびDC−DCコンバータ

【課題】昇降圧動作に対するノイズ対策を施すことで、昇圧型、降圧型または昇降圧型コンバータの何れにも用いることができる多層基板、およびそれを備えたDC−DC−コンバータを提供する。

【解決手段】DC−DCコンバータ1は、磁性体が複数積層された積層体11を備え、積層体11の表面には部品搭載電極11A,11Bが設けられている。また、積層体11の内部にはコイルLが形成されている。コイルLは、積層体11の中間層から裏面までに形成された第1コイルL1と、表面から中間層までに形成された第2コイルL2とを有している。第1コイルL1の中間層側の端部は部品搭載電極11Aに接続し、第2コイルL2の中間層側の端部は部品搭載電極11Bに接続し、第1コイルL1の裏面側の端部は、第2コイルL2の表面側の端部に接続している。

【解決手段】DC−DCコンバータ1は、磁性体が複数積層された積層体11を備え、積層体11の表面には部品搭載電極11A,11Bが設けられている。また、積層体11の内部にはコイルLが形成されている。コイルLは、積層体11の中間層から裏面までに形成された第1コイルL1と、表面から中間層までに形成された第2コイルL2とを有している。第1コイルL1の中間層側の端部は部品搭載電極11Aに接続し、第2コイルL2の中間層側の端部は部品搭載電極11Bに接続し、第1コイルL1の裏面側の端部は、第2コイルL2の表面側の端部に接続している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、内部にコイルが形成された多層基板、およびそれを備えるDC−DCコンバータに関する。

【背景技術】

【0002】

携帯機器等の電源回路では、リニアレギュレータ方式やスイッチングレギュレータ方式の超小型のレギュレータモジュールが用いられている。リニアレギュレータ方式のモジュールでは電圧変動成分を全て熱に変換させるため電源回路の変換効率が低く、スイッチングレギュレータ方式のモジュールではスイッチングノイズなどにより一般的にリニアレギュレータ方式に比べてノイズ特性が劣る。そのため、小型で電圧変換効率が高くノイズ特性に優れるスイッチングレギュレータ方式のDC−DCコンバータを、携帯機器等の電源回路に利用可能にすることが提案されている。

【0003】

DC−DCコンバータの小型化を目的として、磁性体を積層した多層基板にDC−DCコンバータが構成されることがある(例えば特許文献1参照)。従来構成のDC−DCコンバータモジュールは、磁性体基板、スイッチングICおよびコンデンサ部品を備える。磁性体基板の下面には入出力端子およびグランド端子が形成され、上面にはスイッチングICおよびコンデンサ部品が搭載され、基板内部にはコイルが設けられる。そして、コイルにスイッチングICなどが接続される構成となる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第4325747号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来構成のDC−DCコンバータモジュールを昇降圧型コンバータとして用いる場合、スイッチングICは、降圧時と昇圧時とでコイルの前段(入力側)または後段(出力側)に接続され、異なる構成となる。このため、スイッチングICから生じるスイッチングノイズによる影響が高くなるコイル端子は降圧時と昇圧時とで異なる。従って、DC−DCコンバータを昇降圧型として用いる場合、コイルの両端子に対してノイズ対策を施す必要があるため、特許文献1に記載の従来構成のDC−DCコンバータモジュールの積層型インダクタの構造をそのまま用いることができない。

【0006】

そこで本発明の目的は、昇降圧動作に対するノイズ対策を施すことで、昇圧型、降圧型または昇降圧型コンバータの何れにも用いることができる多層基板、およびそれを備えたDC−DC−コンバータを提供することにある。

【課題を解決するための手段】

【0007】

本発明は、磁性体が複数積層され、積層方向を法線方向とする第1面および第2面を有する積層体と、前記積層体の前記第1面に設けられた第1端子および第2端子と、前記積層方向を巻回軸方向として前記積層体内部に形成され、前記第1端子および前記第2端子を入出力端子とするコイルと、を備え、前記コイルは、前記積層体の中間層から前記第2面までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続されて形成された第1コイルと、前記第1面から前記中間層までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続され、かつ、前記第1コイルと巻回方向が同じに形成された第2コイルと、を有し、前記第1コイルの前記中間層側の端部は前記第1端子に導通し、前記第2コイルの前記中間層側の端部は前記第2端子に導通し、前記第1コイルの前記第2面側の端部は、前記第2コイルの前記第1面側の端部に導通していることを特徴とする。

【0008】

この構成では、コイルの入出力端子が積層体の中間層に位置するため、コイルの入出力端子は、積層体の第1面または第2面から離れ、かつ、第1コイルおよび第2コイルで挟まれることとなる。このため、例えば、積層体の第1面または第2面にグランド電極パターンを形成した場合であっても、コイルの両端子の何れかから混入したノイズがグランド電極パターンに伝わり難くなる。この結果、グランド電極パターンを介したノイズの回り込みを防止できる。また、コイルの何れかの端子から流れ込んだノイズは、積層体の中間層から外側(第1面側または第2面側)に向けて第1コイルまたは第2コイルを流れる間に波形振幅が小さくなる。このため、第1面または第2面に近くづく際にはノイズが小さくなっているため、グランド電極パターンへのノイズの伝搬を抑制できる。さらに、異なる層のコイル巻線(電極パターン)によって、輻射されたノイズを遮ることができるため、外部へのノイズの流出を抑制できる。

【0009】

本発明に係る多層基板において、前記積層体の前記第1面または前記第2面と前記コイルとの間にグランド電極層が形成されている構成が好ましい。

【0010】

この構成では、積層体の第1面または第2面に回路素子を実装した場合に、コイルとの間に形成されたグランド電極層によって、回路素子からコイル側に輻射されるノイズを遮蔽することができる。

【0011】

本発明に係る多層基板において、前記積層体は、積層方向において複数の前記磁性体を挟持する非磁性体層を最外層に有し、前記グランド電極層は、積層された前記磁性体および前記非磁性体層の境界面に形成されている構成でもよい。

【0012】

この構成では、最外層にグランド電極層を設けることで、磁性体に形成されたコイルと積層体の第1面または第2面との間にグランド電極層が介在することになる。これにより、コイルから放射されるノイズがグランド電極層により遮られ、積層体の第1面または第2面に搭載される回路素子にノイズが伝わることを防止できる。

【発明の効果】

【0013】

本発明によれば、コイルの何れの端子からノイズが流れ込んでも、ノイズを低減することができる。このため、多層基板を昇圧型、降圧型または昇降圧型コンバータの何れに用いても、ノイズによる影響を抑制することができる。

【図面の簡単な説明】

【0014】

【図1】実施形態1に係るDC−DCコンバータの模式断面図。

【図2】実施形態1に係るDC−DCコンバータの別の例の模式断面図。

【図3】実施形態1に係るDC−DCコンバータの等価回路図。

【図4】DC−DCコンバータが降圧動作する場合の等価回路を示す図。

【図5】DC−DCコンバータが昇圧動作する場合の等価回路を示す図。

【図6】実施形態2に係るDC−DCコンバータの模式断面図。

【発明を実施するための形態】

【0015】

(実施形態1)

以下、本発明に係るDC−DCコンバータについて説明する。以下に説明するDC−DCコンバータは、コイルを内蔵した本発明に係る多層基板を備え、その多層基板にスイッチングICおよびコンデンサが実装された昇降圧型DC-DCコンバータモジュールとして説明する。

【0016】

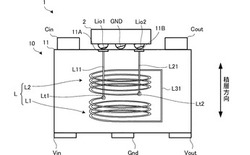

図1は、実施形態1に係るDC−DCコンバータの模式断面図である。DC−DCコンバータ1は多層基板10を備えている。多層基板10は、複数の磁性体層が積層されてなる積層体11を有している。積層体11の各磁性体層は、例えば高透磁率のフェライト(Ni−Zn−CuフェライトまたはNi−Znフェライト等)から構成されるシートである。この積層体11において、回路素子が搭載される面を表面(第1面)とし、不図示の回路基板に実装される面を裏面(第2面)とする。積層体11の表面に搭載される回路素子としては、スイッチングIC2およびコンデンサCin,Coutなどが挙げられる。

【0017】

積層体11は、表面に複数の部品搭載電極(第1端子および第2端子)11A,11Bなどが形成されている。この部品搭載電極11A,11Bには、スイッチングIC2などの回路素子が実装される。また、積層体11は、裏面に外部接続端子としての入力端子電極Vin、出力端子電極Voutおよびグランド端子電極Gndが形成されている。積層体11の表裏面に形成される各電極は、例えばAg等からなる。積層体11の裏面に形成された入力端子電極Vinおよび出力端子電極Voutと、表面に形成された部品搭載電極とは、図示しない積層体11に形成された配線部によって接続されている。

【0018】

以下の説明では、積層体11の表裏面の法線方向を積層方向とし、積層方向における積層体11の表面方向を上方、裏面方向を下方とする。

【0019】

積層体11には積層方向を巻回軸方向とするコイルLが形成されている。コイルLは、積層体11のフェライトシートに形成された環状の電極パターンが、フェライトシートを貫通するビア電極を介して異なる層の電極パターンと導通するよう形成されている。フェライトシートに形成された電極パターンは、例えばAg等からなる。このコイルLは、入出力端子Lt1,Lt2が積層体11の略中央層(中間層)に位置するように形成されている。ここで、入出力端子Lt1,Lt2とは、コイルLの巻き始め端および巻き終わり端をいう。

【0020】

以下、コイルLについて詳述する。コイルLは、積層体11の積層方向の略中央層から下方の領域に形成された第1コイルL1と、積層体11の積層方向の略中央層から上方の領域に形成された第2コイルL2とから構成されている。第1コイルL1および第2コイルL2は巻回方向が同方向である。

【0021】

表面から略中央層までの積層体11の各磁性体層には、積層方向に沿ったビア電極L11,L21が形成されている。ビア電極L11,L21は、積層体11の表面に形成された部品搭載電極11A,11Bと導通している。積層体11の表面から下方に延びるビア電極L11の端部が入出力端子Lt1であり、ビア電極L12の端部が入出力端子Lt2である。この入出力端子Lt1から下方に向けて螺旋状に巻下げられて形成されたコイル巻線が第1コイルL1である。また、入出力端子Lt2から上方に向けて螺旋状に巻上げられて形成されたコイル巻線が第2コイルL2である。そして、第1コイルL1の巻き終わり端と、第2コイルL2の巻き終わり端とは、積層方向に沿って形成されたビア電極L31により接続されている。これにより、入出力端子Lt1,Lt2が積層体11の略中央層に位置したコイルLを形成することができる。なお、第1コイルL1および第2コイルL2は、巻線数がそれぞれコイルLの総巻数の略半分である。

【0022】

スイッチングIC2は、入力端子および出力端子(不図示)とグランド端子GNDとを備え、入力端子から入力された電圧をスイッチングして出力端子から出力する。このスイッチングIC2の入力端子は、部品搭載電極を介して、積層体11の裏面に形成された入力端子電極Vinに導通し、出力端子は積層体11の裏面に形成された出力端子電極Voutに導通している。また、グランド端子GNDは積層体11の裏面に形成されたグランド端子電極Gndに積層体11の内部で導通している。

【0023】

また、スイッチングIC2は、コイル用接続端子Lio1,Lio2を備えている。コイル用接続端子Lio1は部品搭載電極11Aを介して接続ビア電極L11に導通している。コイル用接続端子Lio2は部品搭載電極11Bを介して接続ビア電極L21に導通している。

【0024】

コンデンサCinは、部品搭載電極を介して積層体11の裏面に形成された入力端子電極Vinおよびグランド端子電極Gndに接続されている。コンデンサCinは、入力端子電極Vinから入力される電圧のノイズ成分の除去等を行う。コンデンサCoutは、積層体11の裏面に形成された出力端子電極Voutおよびグランド端子電極Gndに接続されている。コンデンサCoutは、スイッチングIC2の出力端子から出力される電圧を平滑する。

【0025】

図2は、実施形態1に係るDC−DCコンバータの別の例の模式断面図である。図1に示した図面との相違点は、積層体11は、複数の磁性体層が積層され、その両側が非磁性体層12で挟持されてなる構造を有している点、および積層体11の内部で、磁性体層と非磁性体層12の境界面に、グランド電極パターン(グランド電極層)Gが形成されている点である。積層体11の各磁性体層は、例えば高透磁率のフェライト(Ni−Zn−CuフェライトまたはNi−Znフェライト等)から構成されるシートであり、非磁性体層12は比透磁率が1〜10程度の非磁性または低透磁率のフェライト(例えばZn−Cuフェライト等)から構成されるシートである。グランド電極パターンGは、積層された積層体11の磁性体および非磁性体層12の境界面に形成されている。

【0026】

図1と同様に、積層体11には積層方向を巻回軸方向とするコイルLが形成されている。このコイルLは、グランド電極パターンGより下方の層に形成されている。すなわち、積層体11の表面に実装されたスイッチングIC2などの回路素子とコイルLとの間にはグランド電極パターンGが介在している。このグランド電極パターンGにより、コイルから放射されるノイズが回路素子に伝わることを防止している。また、グランド電極パターンGを磁性体層と非磁性体層との境界面に形成することで、積層体の焼成時に、磁性体層と非磁性体層が互いに浸食することを防止できる。また、グランド端子GNDはグランド電極パターンGと電気的に接続されており、積層体11の内部でグランド端子電極Gndに電気的に接続されている。

【0027】

図3は本実施形態に係るDC−DCコンバータの等価回路図である。

【0028】

DC−DCコンバータ1の入力端子電極Vinには、コンデンサCinおよびスイッチングIC2の入力端子INが接続されている。出力端子電極Voutには、コンデンサCoutおよびスイッチングIC2の出力端子OUTが接続されている。また、図1で説明したように、コンデンサCin,CoutおよびスイッチングIC2は、グランド電極パターンG、すなわち、グランドラインに接続されている。

【0029】

スイッチングIC2は、p型MOS−FET21,23およびn型MOS−FET22,24と、各FET21〜24のスイッチング制御を行うドライバ25とを備えている。FET21は、ソースを入力端子IN、ドレインをコイル用接続端子Lio1、ゲートをドライバ25に接続している。FET22は、ソースをグランドライン、ドレインをコイル用接続端子Lio1、ゲートをドライバ25に接続している。FET23は、ドレインをコイル用接続端子Lio2、ソースを出力端子OUT、ゲートをドライバ25に接続している。FET24は、ソースをグランドライン、ドレインをコイル用接続端子Lio2、ゲートをドライバ25に接続している。

【0030】

また、スイッチングIC2のコイル用接続端子Lio1,Lio2には、コイルLが接続されている。具体的には、コイル用接続端子Lio1は、ビア電極L11を介してコイルLの入出力端子Lt1に接続している。コイル用接続端子Lio2は、ビア電極L21を介してコイルLの入出力端子Lt2に接続している。

【0031】

以下に、本実施形態に係るDC−DCコンバータ1の昇降圧動作について説明する。

【0032】

図4は、DC−DCコンバータ1が降圧動作する場合の等価回路を示す図である。図4では、FET23およびFET24を簡易なスイッチ素子で表している。

【0033】

出力端子電極Voutの電圧を入力端子電極Vinの電圧よりも高くする場合、ドライバ25は、FET23を常時オン、FET24を常時オフにする。ドライバ25は、FET21をオン、FET22をオフすることでコイルLに電流を流して励磁させ、エネルギーを蓄積する。その後、ドライバ25は、FET21をオフ、FET22をオンして、コイルLに蓄積したエネルギーを転流させる。この動作を繰り返して、DC−DCコンバータ1は、入力電圧よりも低い電圧を出力端子電極Voutから出力する降圧動作を行う。

【0034】

図5は、DC−DCコンバータ1が昇圧動作する場合の等価回路を示す図である。図5では、FET21およびFET22を簡易なスイッチ素子で表している。

【0035】

出力端子電極Voutの電圧を入力端子電極Vinの電圧よりも低くする場合、ドライバ25は、FET21を常時オン、FET22を常時オフにする。ドライバ25は、FET24をオン、FET24をオフすることでコイルLに電流を流して励磁させ、エネルギーを蓄積する。その後、ドライバ25は、FET24をオフ、FET23をオンして、コイルLに蓄積したエネルギーを放出させる。このとき、コイルLに蓄積されたエネルギーが誘導電圧として入力電圧に加算され、コンデンサCoutによって平滑化される。これにより、DC−DCコンバータ1は入力電圧よりも高い出力電圧を出力する昇圧動作を行う。

【0036】

図4に示す降圧動作の場合、FET21およびFET22をオンオフ制御するため、コイル用接続端子Lio1側は、コイル用接続端子Lio2側よりスイッチングノイズが大きい。一方、図5に示す昇圧動作の場合、FET23およびFET24をオンオフ制御するため、コイル用接続端子Lio2側は、コイル用接続端子Lio1側よりスイッチングノイズが大きい。従って、ノイズの影響を抑えてDC−DCコンバータ1を昇降圧動作するためには、コイル用接続端子Lio1,Lio2の両端子においてノイズ対策が必要となる。

【0037】

本実施形態に係るDC−DCコンバータ1では、コイル用接続端子Lio1,Lio2に接続している入出力端子Lt1,Lt2は積層体11の略中央層に位置し、積層体11の表面近傍に形成されたグランド電極パターンGから離れている。これにより、スイッチングノイズが大きい入出力端子Lt1または入出力端子Lt2がグランド電極パターンGとカップリングして、スイッチングノイズがグランド電極パターンGに伝わることを抑制できる。

【0038】

また、コイル用接続端子Lio1,Lio2から入出力端子Lt1,Lt2へ流れたスイッチングノイズは、第1コイルL1または第2コイルを流れることにより波形振幅が小さくなる。従って、グランド電極パターンGに最も近くなるコイルLの部分に流れるスイッチングノイズは、第1コイルL1または第2コイルを流れた後であるため、入出力端子Lt1,Lt2よりも小さい。この結果、グランド電極パターンGへ伝わるノイズを低減できる。

【0039】

さらに、コイルLは、ある層の電極パターンから輻射されたノイズが、異なる層の電極パターンによりシールドされる構造となっている。このため、入出力端子Lt1,Lt2からノイズが混入した場合でも、積層体11の表面に達するノイズは低減される。この結果、グランド電極パターンGへ伝わるノイズを低減できる。

【0040】

以上のように、グランド電極パターンGに伝わるノイズを低減させることで、グランド電極パターンGを介してDC−DCコンバータ1の外部に流出するノイズを抑制できる。また、グランド電極パターンGを積層体11の表面近傍の層に形成しているため、スイッチングIC2などの回路素子とグランド電極パターンGとの距離を短くでき、その結果、回路素子が発生するノイズはグランド電極パターンGにより抑制することができる。

【0041】

(実施形態2)

本実施形態では、DC−DCコンバータが備えるスイッチングICおよびコンデンサなどの回路素子が多層基板に実装されていない点で実施形態1と相違する。

【0042】

図6は、実施形態2に係るDC−DCコンバータの模式断面図である。本実施形態に係るDC−DCコンバータ5は多層基板6を備えている。多層基板6は、複数の磁性体層が積層されてなる積層体7を備え、積層体7の内部にはコイルLが形成されている。積層体7の裏面には入力端子電極Vinと出力端子電極Voutとが形成されている。入力端子電極Vinと出力端子電極Voutは回路基板30に実装されている。この回路基板30には、スイッチングICおよびコンデンサなどの回路素子40が実装されている。すなわち、本実施形態の場合、回路素子40は多層基板6の表面に実装されておらず、DC−DCコンバータ5は、多層基板6および回路素子40が一体形成されたモジュールとなっていない。

【0043】

なお、回路素子40は回路基板30に形成された配線部31などによって、実施形態1と同様に接続されている。また、回路基板30にはグランド電極パターンGが形成されており、配線部31からのノイズがグランド電極パターンGにより遮蔽されて、回路基板30から外部へ輻射されないようにしてある。

【0044】

積層体7の内部に形成されたコイルLは、実施形態1と同様に、第1コイルL1および第2コイルL2とから構成され、積層体7の積層方向の略中央層に、コイルの巻き始め端および巻き終わり端が位置するよう形成されている。

【0045】

以上のように形成された実施形態2に係るDC−DCコンバータ5であっても、実施形態1と同様に、コイルLからグランド電極パターンGに伝わるノイズを低減させることで、グランド電極パターンGを介してDC−DCコンバータ5の外部に流出するノイズを抑制できる。また、スイッチングICなどの回路素子40は積層体7の表面に実装されていないため、回路素子40のノイズが積層体7のコイルLに及ぼす影響は軽微である。

【0046】

なお、DC−DCコンバータの具体的構成などは、適宜設計変更可能であり、上述の実施形態に記載された作用及び効果は、本発明から生じる最も好適な作用及び効果を列挙したに過ぎず、本発明による作用及び効果は、上述の実施形態に記載されたものに限定されるものではない。

【0047】

本発明に係る多層基板は昇降圧型のDC−DCコンバータ以外に用いてもよく、例えば、昇圧型または降圧型のDC−DCコンバータに用いてもよい。また、多層基板は、DC−DCコンバータ以外の素子に用いてもよいし、単にコイル素子として用いてもよい。

【符号の説明】

【0048】

1−DC−DCコンバータ

2−スイッチングIC

10−多層基板

11−積層体

11A,11B−部品搭載電極(第1端子、第2端子)

21,23−p型MOS−FET

22,24−n型MOS−FET

L−コイル

L1−第1コイル

L2−第2コイル

G−グランド電極パターン

Cin,Cout−コンデンサ

【技術分野】

【0001】

本発明は、内部にコイルが形成された多層基板、およびそれを備えるDC−DCコンバータに関する。

【背景技術】

【0002】

携帯機器等の電源回路では、リニアレギュレータ方式やスイッチングレギュレータ方式の超小型のレギュレータモジュールが用いられている。リニアレギュレータ方式のモジュールでは電圧変動成分を全て熱に変換させるため電源回路の変換効率が低く、スイッチングレギュレータ方式のモジュールではスイッチングノイズなどにより一般的にリニアレギュレータ方式に比べてノイズ特性が劣る。そのため、小型で電圧変換効率が高くノイズ特性に優れるスイッチングレギュレータ方式のDC−DCコンバータを、携帯機器等の電源回路に利用可能にすることが提案されている。

【0003】

DC−DCコンバータの小型化を目的として、磁性体を積層した多層基板にDC−DCコンバータが構成されることがある(例えば特許文献1参照)。従来構成のDC−DCコンバータモジュールは、磁性体基板、スイッチングICおよびコンデンサ部品を備える。磁性体基板の下面には入出力端子およびグランド端子が形成され、上面にはスイッチングICおよびコンデンサ部品が搭載され、基板内部にはコイルが設けられる。そして、コイルにスイッチングICなどが接続される構成となる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第4325747号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来構成のDC−DCコンバータモジュールを昇降圧型コンバータとして用いる場合、スイッチングICは、降圧時と昇圧時とでコイルの前段(入力側)または後段(出力側)に接続され、異なる構成となる。このため、スイッチングICから生じるスイッチングノイズによる影響が高くなるコイル端子は降圧時と昇圧時とで異なる。従って、DC−DCコンバータを昇降圧型として用いる場合、コイルの両端子に対してノイズ対策を施す必要があるため、特許文献1に記載の従来構成のDC−DCコンバータモジュールの積層型インダクタの構造をそのまま用いることができない。

【0006】

そこで本発明の目的は、昇降圧動作に対するノイズ対策を施すことで、昇圧型、降圧型または昇降圧型コンバータの何れにも用いることができる多層基板、およびそれを備えたDC−DC−コンバータを提供することにある。

【課題を解決するための手段】

【0007】

本発明は、磁性体が複数積層され、積層方向を法線方向とする第1面および第2面を有する積層体と、前記積層体の前記第1面に設けられた第1端子および第2端子と、前記積層方向を巻回軸方向として前記積層体内部に形成され、前記第1端子および前記第2端子を入出力端子とするコイルと、を備え、前記コイルは、前記積層体の中間層から前記第2面までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続されて形成された第1コイルと、前記第1面から前記中間層までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続され、かつ、前記第1コイルと巻回方向が同じに形成された第2コイルと、を有し、前記第1コイルの前記中間層側の端部は前記第1端子に導通し、前記第2コイルの前記中間層側の端部は前記第2端子に導通し、前記第1コイルの前記第2面側の端部は、前記第2コイルの前記第1面側の端部に導通していることを特徴とする。

【0008】

この構成では、コイルの入出力端子が積層体の中間層に位置するため、コイルの入出力端子は、積層体の第1面または第2面から離れ、かつ、第1コイルおよび第2コイルで挟まれることとなる。このため、例えば、積層体の第1面または第2面にグランド電極パターンを形成した場合であっても、コイルの両端子の何れかから混入したノイズがグランド電極パターンに伝わり難くなる。この結果、グランド電極パターンを介したノイズの回り込みを防止できる。また、コイルの何れかの端子から流れ込んだノイズは、積層体の中間層から外側(第1面側または第2面側)に向けて第1コイルまたは第2コイルを流れる間に波形振幅が小さくなる。このため、第1面または第2面に近くづく際にはノイズが小さくなっているため、グランド電極パターンへのノイズの伝搬を抑制できる。さらに、異なる層のコイル巻線(電極パターン)によって、輻射されたノイズを遮ることができるため、外部へのノイズの流出を抑制できる。

【0009】

本発明に係る多層基板において、前記積層体の前記第1面または前記第2面と前記コイルとの間にグランド電極層が形成されている構成が好ましい。

【0010】

この構成では、積層体の第1面または第2面に回路素子を実装した場合に、コイルとの間に形成されたグランド電極層によって、回路素子からコイル側に輻射されるノイズを遮蔽することができる。

【0011】

本発明に係る多層基板において、前記積層体は、積層方向において複数の前記磁性体を挟持する非磁性体層を最外層に有し、前記グランド電極層は、積層された前記磁性体および前記非磁性体層の境界面に形成されている構成でもよい。

【0012】

この構成では、最外層にグランド電極層を設けることで、磁性体に形成されたコイルと積層体の第1面または第2面との間にグランド電極層が介在することになる。これにより、コイルから放射されるノイズがグランド電極層により遮られ、積層体の第1面または第2面に搭載される回路素子にノイズが伝わることを防止できる。

【発明の効果】

【0013】

本発明によれば、コイルの何れの端子からノイズが流れ込んでも、ノイズを低減することができる。このため、多層基板を昇圧型、降圧型または昇降圧型コンバータの何れに用いても、ノイズによる影響を抑制することができる。

【図面の簡単な説明】

【0014】

【図1】実施形態1に係るDC−DCコンバータの模式断面図。

【図2】実施形態1に係るDC−DCコンバータの別の例の模式断面図。

【図3】実施形態1に係るDC−DCコンバータの等価回路図。

【図4】DC−DCコンバータが降圧動作する場合の等価回路を示す図。

【図5】DC−DCコンバータが昇圧動作する場合の等価回路を示す図。

【図6】実施形態2に係るDC−DCコンバータの模式断面図。

【発明を実施するための形態】

【0015】

(実施形態1)

以下、本発明に係るDC−DCコンバータについて説明する。以下に説明するDC−DCコンバータは、コイルを内蔵した本発明に係る多層基板を備え、その多層基板にスイッチングICおよびコンデンサが実装された昇降圧型DC-DCコンバータモジュールとして説明する。

【0016】

図1は、実施形態1に係るDC−DCコンバータの模式断面図である。DC−DCコンバータ1は多層基板10を備えている。多層基板10は、複数の磁性体層が積層されてなる積層体11を有している。積層体11の各磁性体層は、例えば高透磁率のフェライト(Ni−Zn−CuフェライトまたはNi−Znフェライト等)から構成されるシートである。この積層体11において、回路素子が搭載される面を表面(第1面)とし、不図示の回路基板に実装される面を裏面(第2面)とする。積層体11の表面に搭載される回路素子としては、スイッチングIC2およびコンデンサCin,Coutなどが挙げられる。

【0017】

積層体11は、表面に複数の部品搭載電極(第1端子および第2端子)11A,11Bなどが形成されている。この部品搭載電極11A,11Bには、スイッチングIC2などの回路素子が実装される。また、積層体11は、裏面に外部接続端子としての入力端子電極Vin、出力端子電極Voutおよびグランド端子電極Gndが形成されている。積層体11の表裏面に形成される各電極は、例えばAg等からなる。積層体11の裏面に形成された入力端子電極Vinおよび出力端子電極Voutと、表面に形成された部品搭載電極とは、図示しない積層体11に形成された配線部によって接続されている。

【0018】

以下の説明では、積層体11の表裏面の法線方向を積層方向とし、積層方向における積層体11の表面方向を上方、裏面方向を下方とする。

【0019】

積層体11には積層方向を巻回軸方向とするコイルLが形成されている。コイルLは、積層体11のフェライトシートに形成された環状の電極パターンが、フェライトシートを貫通するビア電極を介して異なる層の電極パターンと導通するよう形成されている。フェライトシートに形成された電極パターンは、例えばAg等からなる。このコイルLは、入出力端子Lt1,Lt2が積層体11の略中央層(中間層)に位置するように形成されている。ここで、入出力端子Lt1,Lt2とは、コイルLの巻き始め端および巻き終わり端をいう。

【0020】

以下、コイルLについて詳述する。コイルLは、積層体11の積層方向の略中央層から下方の領域に形成された第1コイルL1と、積層体11の積層方向の略中央層から上方の領域に形成された第2コイルL2とから構成されている。第1コイルL1および第2コイルL2は巻回方向が同方向である。

【0021】

表面から略中央層までの積層体11の各磁性体層には、積層方向に沿ったビア電極L11,L21が形成されている。ビア電極L11,L21は、積層体11の表面に形成された部品搭載電極11A,11Bと導通している。積層体11の表面から下方に延びるビア電極L11の端部が入出力端子Lt1であり、ビア電極L12の端部が入出力端子Lt2である。この入出力端子Lt1から下方に向けて螺旋状に巻下げられて形成されたコイル巻線が第1コイルL1である。また、入出力端子Lt2から上方に向けて螺旋状に巻上げられて形成されたコイル巻線が第2コイルL2である。そして、第1コイルL1の巻き終わり端と、第2コイルL2の巻き終わり端とは、積層方向に沿って形成されたビア電極L31により接続されている。これにより、入出力端子Lt1,Lt2が積層体11の略中央層に位置したコイルLを形成することができる。なお、第1コイルL1および第2コイルL2は、巻線数がそれぞれコイルLの総巻数の略半分である。

【0022】

スイッチングIC2は、入力端子および出力端子(不図示)とグランド端子GNDとを備え、入力端子から入力された電圧をスイッチングして出力端子から出力する。このスイッチングIC2の入力端子は、部品搭載電極を介して、積層体11の裏面に形成された入力端子電極Vinに導通し、出力端子は積層体11の裏面に形成された出力端子電極Voutに導通している。また、グランド端子GNDは積層体11の裏面に形成されたグランド端子電極Gndに積層体11の内部で導通している。

【0023】

また、スイッチングIC2は、コイル用接続端子Lio1,Lio2を備えている。コイル用接続端子Lio1は部品搭載電極11Aを介して接続ビア電極L11に導通している。コイル用接続端子Lio2は部品搭載電極11Bを介して接続ビア電極L21に導通している。

【0024】

コンデンサCinは、部品搭載電極を介して積層体11の裏面に形成された入力端子電極Vinおよびグランド端子電極Gndに接続されている。コンデンサCinは、入力端子電極Vinから入力される電圧のノイズ成分の除去等を行う。コンデンサCoutは、積層体11の裏面に形成された出力端子電極Voutおよびグランド端子電極Gndに接続されている。コンデンサCoutは、スイッチングIC2の出力端子から出力される電圧を平滑する。

【0025】

図2は、実施形態1に係るDC−DCコンバータの別の例の模式断面図である。図1に示した図面との相違点は、積層体11は、複数の磁性体層が積層され、その両側が非磁性体層12で挟持されてなる構造を有している点、および積層体11の内部で、磁性体層と非磁性体層12の境界面に、グランド電極パターン(グランド電極層)Gが形成されている点である。積層体11の各磁性体層は、例えば高透磁率のフェライト(Ni−Zn−CuフェライトまたはNi−Znフェライト等)から構成されるシートであり、非磁性体層12は比透磁率が1〜10程度の非磁性または低透磁率のフェライト(例えばZn−Cuフェライト等)から構成されるシートである。グランド電極パターンGは、積層された積層体11の磁性体および非磁性体層12の境界面に形成されている。

【0026】

図1と同様に、積層体11には積層方向を巻回軸方向とするコイルLが形成されている。このコイルLは、グランド電極パターンGより下方の層に形成されている。すなわち、積層体11の表面に実装されたスイッチングIC2などの回路素子とコイルLとの間にはグランド電極パターンGが介在している。このグランド電極パターンGにより、コイルから放射されるノイズが回路素子に伝わることを防止している。また、グランド電極パターンGを磁性体層と非磁性体層との境界面に形成することで、積層体の焼成時に、磁性体層と非磁性体層が互いに浸食することを防止できる。また、グランド端子GNDはグランド電極パターンGと電気的に接続されており、積層体11の内部でグランド端子電極Gndに電気的に接続されている。

【0027】

図3は本実施形態に係るDC−DCコンバータの等価回路図である。

【0028】

DC−DCコンバータ1の入力端子電極Vinには、コンデンサCinおよびスイッチングIC2の入力端子INが接続されている。出力端子電極Voutには、コンデンサCoutおよびスイッチングIC2の出力端子OUTが接続されている。また、図1で説明したように、コンデンサCin,CoutおよびスイッチングIC2は、グランド電極パターンG、すなわち、グランドラインに接続されている。

【0029】

スイッチングIC2は、p型MOS−FET21,23およびn型MOS−FET22,24と、各FET21〜24のスイッチング制御を行うドライバ25とを備えている。FET21は、ソースを入力端子IN、ドレインをコイル用接続端子Lio1、ゲートをドライバ25に接続している。FET22は、ソースをグランドライン、ドレインをコイル用接続端子Lio1、ゲートをドライバ25に接続している。FET23は、ドレインをコイル用接続端子Lio2、ソースを出力端子OUT、ゲートをドライバ25に接続している。FET24は、ソースをグランドライン、ドレインをコイル用接続端子Lio2、ゲートをドライバ25に接続している。

【0030】

また、スイッチングIC2のコイル用接続端子Lio1,Lio2には、コイルLが接続されている。具体的には、コイル用接続端子Lio1は、ビア電極L11を介してコイルLの入出力端子Lt1に接続している。コイル用接続端子Lio2は、ビア電極L21を介してコイルLの入出力端子Lt2に接続している。

【0031】

以下に、本実施形態に係るDC−DCコンバータ1の昇降圧動作について説明する。

【0032】

図4は、DC−DCコンバータ1が降圧動作する場合の等価回路を示す図である。図4では、FET23およびFET24を簡易なスイッチ素子で表している。

【0033】

出力端子電極Voutの電圧を入力端子電極Vinの電圧よりも高くする場合、ドライバ25は、FET23を常時オン、FET24を常時オフにする。ドライバ25は、FET21をオン、FET22をオフすることでコイルLに電流を流して励磁させ、エネルギーを蓄積する。その後、ドライバ25は、FET21をオフ、FET22をオンして、コイルLに蓄積したエネルギーを転流させる。この動作を繰り返して、DC−DCコンバータ1は、入力電圧よりも低い電圧を出力端子電極Voutから出力する降圧動作を行う。

【0034】

図5は、DC−DCコンバータ1が昇圧動作する場合の等価回路を示す図である。図5では、FET21およびFET22を簡易なスイッチ素子で表している。

【0035】

出力端子電極Voutの電圧を入力端子電極Vinの電圧よりも低くする場合、ドライバ25は、FET21を常時オン、FET22を常時オフにする。ドライバ25は、FET24をオン、FET24をオフすることでコイルLに電流を流して励磁させ、エネルギーを蓄積する。その後、ドライバ25は、FET24をオフ、FET23をオンして、コイルLに蓄積したエネルギーを放出させる。このとき、コイルLに蓄積されたエネルギーが誘導電圧として入力電圧に加算され、コンデンサCoutによって平滑化される。これにより、DC−DCコンバータ1は入力電圧よりも高い出力電圧を出力する昇圧動作を行う。

【0036】

図4に示す降圧動作の場合、FET21およびFET22をオンオフ制御するため、コイル用接続端子Lio1側は、コイル用接続端子Lio2側よりスイッチングノイズが大きい。一方、図5に示す昇圧動作の場合、FET23およびFET24をオンオフ制御するため、コイル用接続端子Lio2側は、コイル用接続端子Lio1側よりスイッチングノイズが大きい。従って、ノイズの影響を抑えてDC−DCコンバータ1を昇降圧動作するためには、コイル用接続端子Lio1,Lio2の両端子においてノイズ対策が必要となる。

【0037】

本実施形態に係るDC−DCコンバータ1では、コイル用接続端子Lio1,Lio2に接続している入出力端子Lt1,Lt2は積層体11の略中央層に位置し、積層体11の表面近傍に形成されたグランド電極パターンGから離れている。これにより、スイッチングノイズが大きい入出力端子Lt1または入出力端子Lt2がグランド電極パターンGとカップリングして、スイッチングノイズがグランド電極パターンGに伝わることを抑制できる。

【0038】

また、コイル用接続端子Lio1,Lio2から入出力端子Lt1,Lt2へ流れたスイッチングノイズは、第1コイルL1または第2コイルを流れることにより波形振幅が小さくなる。従って、グランド電極パターンGに最も近くなるコイルLの部分に流れるスイッチングノイズは、第1コイルL1または第2コイルを流れた後であるため、入出力端子Lt1,Lt2よりも小さい。この結果、グランド電極パターンGへ伝わるノイズを低減できる。

【0039】

さらに、コイルLは、ある層の電極パターンから輻射されたノイズが、異なる層の電極パターンによりシールドされる構造となっている。このため、入出力端子Lt1,Lt2からノイズが混入した場合でも、積層体11の表面に達するノイズは低減される。この結果、グランド電極パターンGへ伝わるノイズを低減できる。

【0040】

以上のように、グランド電極パターンGに伝わるノイズを低減させることで、グランド電極パターンGを介してDC−DCコンバータ1の外部に流出するノイズを抑制できる。また、グランド電極パターンGを積層体11の表面近傍の層に形成しているため、スイッチングIC2などの回路素子とグランド電極パターンGとの距離を短くでき、その結果、回路素子が発生するノイズはグランド電極パターンGにより抑制することができる。

【0041】

(実施形態2)

本実施形態では、DC−DCコンバータが備えるスイッチングICおよびコンデンサなどの回路素子が多層基板に実装されていない点で実施形態1と相違する。

【0042】

図6は、実施形態2に係るDC−DCコンバータの模式断面図である。本実施形態に係るDC−DCコンバータ5は多層基板6を備えている。多層基板6は、複数の磁性体層が積層されてなる積層体7を備え、積層体7の内部にはコイルLが形成されている。積層体7の裏面には入力端子電極Vinと出力端子電極Voutとが形成されている。入力端子電極Vinと出力端子電極Voutは回路基板30に実装されている。この回路基板30には、スイッチングICおよびコンデンサなどの回路素子40が実装されている。すなわち、本実施形態の場合、回路素子40は多層基板6の表面に実装されておらず、DC−DCコンバータ5は、多層基板6および回路素子40が一体形成されたモジュールとなっていない。

【0043】

なお、回路素子40は回路基板30に形成された配線部31などによって、実施形態1と同様に接続されている。また、回路基板30にはグランド電極パターンGが形成されており、配線部31からのノイズがグランド電極パターンGにより遮蔽されて、回路基板30から外部へ輻射されないようにしてある。

【0044】

積層体7の内部に形成されたコイルLは、実施形態1と同様に、第1コイルL1および第2コイルL2とから構成され、積層体7の積層方向の略中央層に、コイルの巻き始め端および巻き終わり端が位置するよう形成されている。

【0045】

以上のように形成された実施形態2に係るDC−DCコンバータ5であっても、実施形態1と同様に、コイルLからグランド電極パターンGに伝わるノイズを低減させることで、グランド電極パターンGを介してDC−DCコンバータ5の外部に流出するノイズを抑制できる。また、スイッチングICなどの回路素子40は積層体7の表面に実装されていないため、回路素子40のノイズが積層体7のコイルLに及ぼす影響は軽微である。

【0046】

なお、DC−DCコンバータの具体的構成などは、適宜設計変更可能であり、上述の実施形態に記載された作用及び効果は、本発明から生じる最も好適な作用及び効果を列挙したに過ぎず、本発明による作用及び効果は、上述の実施形態に記載されたものに限定されるものではない。

【0047】

本発明に係る多層基板は昇降圧型のDC−DCコンバータ以外に用いてもよく、例えば、昇圧型または降圧型のDC−DCコンバータに用いてもよい。また、多層基板は、DC−DCコンバータ以外の素子に用いてもよいし、単にコイル素子として用いてもよい。

【符号の説明】

【0048】

1−DC−DCコンバータ

2−スイッチングIC

10−多層基板

11−積層体

11A,11B−部品搭載電極(第1端子、第2端子)

21,23−p型MOS−FET

22,24−n型MOS−FET

L−コイル

L1−第1コイル

L2−第2コイル

G−グランド電極パターン

Cin,Cout−コンデンサ

【特許請求の範囲】

【請求項1】

磁性体が複数積層され、積層方向を法線方向とする第1面および第2面を有する積層体と、

前記積層体の前記第1面に設けられた第1端子および第2端子と、

前記積層方向を巻回軸方向として前記積層体内部に形成され、前記第1端子および前記第2端子を入出力端子とするコイルと、

を備え、

前記コイルは、

前記積層体の中間層から前記第2面までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続されて形成された第1コイルと、

前記第1面から前記中間層までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続され、かつ、前記第1コイルと巻回方向が同じに形成された第2コイルと、

を有し、

前記第1コイルの前記中間層側の端部は前記第1端子に導通し、

前記第2コイルの前記中間層側の端部は前記第2端子に導通し、

前記第1コイルの前記第2面側の端部は、前記第2コイルの前記第1面側の端部に導通している、

多層基板。

【請求項2】

前記積層体の前記第1面または前記第2面と前記コイルとの間にグランド電極層が形成されている請求項1に記載の多層基板。

【請求項3】

前記積層体は、

積層方向において複数の前記磁性体を挟持する非磁性体層を最外層に有し、

前記グランド電極層は、

積層された前記磁性体および前記非磁性体層の境界面に形成されている、

請求項2に記載の多層基板。

【請求項4】

磁性体が複数積層され、積層方向を法線方向とする第1面および第2面を有する積層体と、

前記積層体の第1面に設けられた第1端子および第2端子と、

前記積層方向を巻回軸方向として前記積層体内部に形成され、前記第1端子および前記第2端子を入出力端子とするコイルと、

前記積層体の第1面に設けられ、前記第1端子または前記第2端子を介して前記コイルに接続されたスイッチングICおよびコンデンサと、

を備え、

前記コイルは、

前記積層体の中間層から前記第2面までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続されて形成された第1コイルと、

前記第1面から前記中間層までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続され、かつ、前記第1コイルと巻回方向が同じに形成された第2コイルと、

を有し、

前記第1コイルの前記中間層側の端部は前記第1端子に導通し

前記第2コイルの前記中間層側の端部は前記第2端子に導通し、

前記第1コイルの前記第2面側の端部は、前記第2コイルの前記第1面側の端部に導通している、

DC−DCコンバータ。

【請求項1】

磁性体が複数積層され、積層方向を法線方向とする第1面および第2面を有する積層体と、

前記積層体の前記第1面に設けられた第1端子および第2端子と、

前記積層方向を巻回軸方向として前記積層体内部に形成され、前記第1端子および前記第2端子を入出力端子とするコイルと、

を備え、

前記コイルは、

前記積層体の中間層から前記第2面までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続されて形成された第1コイルと、

前記第1面から前記中間層までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続され、かつ、前記第1コイルと巻回方向が同じに形成された第2コイルと、

を有し、

前記第1コイルの前記中間層側の端部は前記第1端子に導通し、

前記第2コイルの前記中間層側の端部は前記第2端子に導通し、

前記第1コイルの前記第2面側の端部は、前記第2コイルの前記第1面側の端部に導通している、

多層基板。

【請求項2】

前記積層体の前記第1面または前記第2面と前記コイルとの間にグランド電極層が形成されている請求項1に記載の多層基板。

【請求項3】

前記積層体は、

積層方向において複数の前記磁性体を挟持する非磁性体層を最外層に有し、

前記グランド電極層は、

積層された前記磁性体および前記非磁性体層の境界面に形成されている、

請求項2に記載の多層基板。

【請求項4】

磁性体が複数積層され、積層方向を法線方向とする第1面および第2面を有する積層体と、

前記積層体の第1面に設けられた第1端子および第2端子と、

前記積層方向を巻回軸方向として前記積層体内部に形成され、前記第1端子および前記第2端子を入出力端子とするコイルと、

前記積層体の第1面に設けられ、前記第1端子または前記第2端子を介して前記コイルに接続されたスイッチングICおよびコンデンサと、

を備え、

前記コイルは、

前記積層体の中間層から前記第2面までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続されて形成された第1コイルと、

前記第1面から前記中間層までの複数の磁性体に形成された環状の電極パターンが螺旋状に接続され、かつ、前記第1コイルと巻回方向が同じに形成された第2コイルと、

を有し、

前記第1コイルの前記中間層側の端部は前記第1端子に導通し

前記第2コイルの前記中間層側の端部は前記第2端子に導通し、

前記第1コイルの前記第2面側の端部は、前記第2コイルの前記第1面側の端部に導通している、

DC−DCコンバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−98187(P2013−98187A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−236569(P2011−236569)

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]