多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多層膜構造体及びその形成方法に関する。

【背景技術】

【0002】

従来、超々大規模集積回路(ULSI)の基本構成素子である金属-酸化物-半導体電界効果トランジスタ(MOSFET)の性能向上は、素子の微細化によって達成されるところが大きかった。しかし、近年、微細化が極限まで発展した結果、素子のサイズはナノメートルの領域に達しており、その継続は技術的、経済的に困難に直面している。そこで、微細化だけに依存しないMOSFETの性能向上技術として、従来の主流であったシリコン(Si)あるいは歪Siによるチャネル材料に代わって、歪ゲルマニウム(Ge)材料の適用が注目されている。

【0003】

Geは元来、Siよりも高い電子および正孔移動度を有する材料であり、これを用いることは電子素子の高速化、省電力化に有効である。これに加えて、圧縮あるいは伸張歪の加わったGeは、無歪のGeに比較してもさらに正孔および電子移動度が高くなることが知られている。例えば、Fischettiらの理論計算によると1.3%の二軸性の伸張歪をGeに印加した場合、無歪Geの場合に比較して、電子の移動度が10倍以上となることが期待される(非特許文献1参照)。また、同様にGeに二軸性圧縮歪を印加した場合、無歪Geに比べて正孔の移動度の向上が予測されており、1.3%の圧縮歪を印加した場合、正孔移動度は2倍以上となる。このような移動度向上技術の併用によって、電子素子の電流駆動能力のさらなる向上が期待できる。

【0004】

歪Geの作製のためには、シリコンゲルマニウム(Si1-xGex)、ゲルマニウム錫(Ge1-xSnx)(非特許文献2参照)、インジウムガリウム砒素(InxGa1-xAs)(非特許文献3参照)などのGeとは格子定数の異なる歪印加層(ストレッサ)が必要である。例えば、SiはGeよりも原子半径が小さく、Si1-xGexの格子定数はGeのそれよりも小さくなる。そのため、Si1-xGex層上にGe層を格子整合した状態でエピタキシャル成長させると、そのGe層には二軸性の圧縮歪を加えることが可能となる。

【0005】

続いて、ストレッサとなるバッファ層の形成手法について述べる。近年、歪印加バッファ層とSi on insulator(SOI)基板を融合した技術、つまり薄膜かつ歪緩和した歪印加バッファ層を埋め込み酸化(Buried oxide: BOX)層上に形成する技術が注目されている。TakagiらのグループはSOI基板上にエピタキシャル成長させたSi1-xGex層を1000℃以上の高温によって熱酸化することで、Si1-xGex on insulator(SGOI)構造およびGe on insulator(GOI)構造を実現させた(非特許文献4または非特許文献5参照)。一方、TaokaらはSi基板上およびSOI基板上にエピタキシャル成長させたGe層に、酸化Si膜キャップ層を形成後、950℃および1100℃の高温において熱処理することで、SGOI構造を形成する手法について報告している(非特許文献6参照)。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】M. V. Fischetti, and S. E. Laux, J. Appl. Phys. 80, 2234 (1996).

【非特許文献2】S. Takeuchi, Y. Shimura, O. Nakatsuka, S. Zaima, M. Ogawa, and A. Sakai, Appl. Phys. Lett. 92, 231916 (2008).

【非特許文献3】Y. Bai, K.E. Lee, C. Cheng, M.L. Lee and E.A. Fitzgerald, J. Appl. Phys. 104, 084518 (2008).

【非特許文献4】T. Tezuka, N. Sugiyama, T. Mizuno, M. Suzuki and S. Takagi, J. Appl. Phys. 40, 2866 (2001)

【非特許文献5】S. Nakaharai, T. Tezuka, N. Sugiyama, Y. Moriyama, and S. Takagi. Appl. Phys. Lett. 83, 3516 (2003).

【非特許文献6】N. Taoka, A. Sakai, S. Mochizuki, O. Nakatsuka, M. Ogawa, S. Zaima, Thin Solid Films 508, 147 (2006).

【発明の概要】

【発明が解決しようとする課題】

【0007】

非特許文献4〜6記載の手法は、バッファ層としてのSi1-xGex層の形成プロセスや条件が非常に複雑になりがちである。また、Si層とGe層との固相反応を生じさせるのに1000℃前後の高温熱処理が不可欠であるため、その実現には大きなエネルギーが必要であり、生産性、経済性的な観点からの課題が残されている。

【0008】

一方、MOSFETチャネルへの歪印加にバッファ層を用いる場合、素子性能の向上のためにはチャネル層からバッファ層へのリーク電流の抑制が重要となる。リーク電流抑制のためには伝導帯、価電子帯ともに、チャネル層に対するバッファ層のバンドオフセットが大きいことが重要である。

【0009】

しかしながら、Geチャネルに伸張ひずみを加えることを考える際、Ge1-xSnxのような材料をバッファ層として用いることには、そのエネルギーバンドアライメントの関係から、問題がある。Ge1-xSnxはGeと同等かあるいは、Geよりもエネルギーバンドギャップが小さく、また相互のバンドオフセットも小さいため、本来チャネル領域を流れるべき電子や正孔が、Ge1-xSnxに容易に流入し、本来期待する電気伝導が実現できない懸念がある。

【0010】

本発明は以上の点に鑑みなされたものであり、上述した課題のいずれかを解決できる多層膜構造体及びその形成方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の多層膜構造体の形成方法は、

半導体素子用の多層膜構造体の形成方法であって、

シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、

前記半導体層上に表面保護層を形成する表面保護層形成工程と、

前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、

前記表面保護層を除去する除去工程と、

前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする。

【0012】

本発明の多層膜構造体の形成方法によれば、ゲルマニウム層への錫の添加、および表面保護層の形成という理由により、シリコンを含む基板とゲルマニウム層との反応温度の低減という効果を奏する。

【0013】

前記歪半導体層は、ゲルマニウム層であることが好ましい。ゲルマニウム層であることにより、シリコンゲルマニウム錫を含む半導体歪印加層から歪を印加できるという効果がある。

【0014】

前記半導体層に熱処理を施す工程は、400℃以上950℃以下の熱処理であることが好ましい。この温度範囲であることにより、従来よりも低温の熱処理でシリコンとゲルマニウム錫混晶層との反応を誘起し、シリコンゲルマニウム錫混晶層を形成できるという効果がある。

【0015】

前記ゲルマニウム錫混晶の錫組成は、3%以上であってかつ12%以下であることが好ましい。この範囲内であることにより、950℃以下の温度であってもシリコンを含む層とゲルマニウム錫混晶層との反応を生じさせることができる効果が得られる。

【0016】

前記基板は、絶縁膜上に形成されたシリコン層を含む構造であることが好ましい。このような構造であることにより、ゲルマニウム錫層との反応によってシリコンゲルマニウム錫層を形成できる効果が得られる。

前記表面保護層は、酸化シリコン層、窒化シリコン層、窒化チタン層、またはグラファイト層であることが好ましい。上記のものであることにより、シリコンとゲルマニウム錫との反応を促進できる効果が得られる。

【0017】

本発明の多層膜構造体は、

半導体素子用の多層膜構造体であって、

基板の上方に形成された錫を含む歪緩和した半導体歪印加層と、

その上方に形成された歪を有する歪半導体層を含むことを特徴とする。

【0018】

本発明の多層膜構造体は、歪半導体層を含むという理由により、従来の無歪半導体と比較して、高い電子および正孔移動度を実現するという効果を奏する。

前記半導体歪印加層がシリコンゲルマニウム錫混晶層であり、前記歪半導体層がゲルマニウム層であることが好ましい。上記のものであることにより、ゲルマニウム層にはシリコンゲルマニウム錫層から歪が印加される。その結果として、歪半導体層である歪ゲルマニウム層は、無歪ゲルマニウムと比較して、高い電子および正孔移動度を実現するという効果を奏する。

【図面の簡単な説明】

【0019】

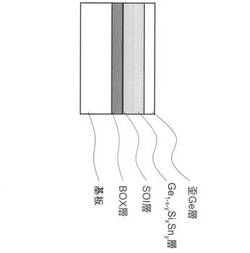

【図1】多層膜構造体の形成方法に関する各工程における試料断面図(1)。SOI基板の構成を表す断面図。

【図2】多層膜構造体の形成方法に関する各工程における試料断面図(2)。表面保護層形成工程後の酸化Si層/Ge1-zSnz層/SOI基板構造の断面図。

【図3】多層膜構造体の形成方法に関する各工程における試料断面図(3)。半導体歪印加層形成工程における熱処理に伴うGezSn1-z層とSOI層との界面固相反応進行後の断面図。

【図4】多層膜構造体の形成方法に関する各工程における試料断面図(4)。表面保護層の除去工程後、積層工程において歪印加層上に歪Ge層のエピタキシャル成長した後の断面図。

【図5】Ge1-zSnz層の成膜直後の試料Aの断面SEM像。

【図6】試料AのGe1-zSnz層の成膜直後の状態におけるGe224逆格子点周辺のX線回折二次元逆格子マップ(XRD-2DRSM)の測定結果。

【図7】試料R(Sn含有なし)のGe層成膜直後の状態におけるGe224逆格子点周辺のX線回折二次元逆格子マップ(XRD-2DRSM)の測定結果。

【図8】400℃、60分間熱処理を施した試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果。

【図9】400℃の熱処理前後の試料Aに対するSi004逆格子点周辺のXRD out-of-plane測定(2θ-ω測定)結果。

【図10】試料AにおけるXRD out-of-plane測定(2θ-ω測定)結果から見積もられた、エピタキシャル層の面直方向の格子定数の熱処理時間依存性。

【図11】400℃、60分間熱処理を施した後の試料Aの断面TEM像。

【図12】300℃、60分間の熱処理後の試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果。

【図13】試料Aを300℃、60分間熱処理した後の断面TEM像。

【図14】試料BにおけるXRD out-of-plane測定(2θ-ω測定)結果から見積もられるエピタキシャル層の面直方向の格子定数の熱処理時間依存性。300℃、および400℃熱処理後の結果。

【図15】試料CにおけるXRD out-of-plane測定(2θ-ω測定)結果から見積もられる、エピタキシャル層の面直方向の格子定数の熱処理時間依存性。400℃および500℃熱処理後の結果。

【図16】500℃で180分間の熱処理を施した試料Cにおいて、表面の酸化Si膜を除去した後の平面SEM像。

【図17】400℃、60分間の熱処理を施した試料Rに対する224逆格子点周辺のXRD-2DRSMの測定結果。

【図18】試料RにおけるXRD out-of-Plane測定(2θ-ω測定)から見積もられるエピタキシャル層の面直方向の格子定数の熱処理時間依存性。

【図19】400℃、30分間の熱処理を施した試料Dの断面SEM像。

【図20】400℃、30分間の熱処理を施した試料Eの断面SEM像。

【図21】試料Dおよび試料Eにおける、XRD out-of-Plane測定(2θ-ω測定)結果から見積もられたエピタキシャル層の面直方向の格子定数の熱処理時間依存性。

【図22】XRD-2DRSMにおける回折パターンの対称性評価方法の模式図。

【図23】各試料において、エピタキシャル層のXRD-2DRSM逆格子回折パターンの対称性を評価した結果。

【発明を実施するための形態】

【0020】

1.多層膜構造体の形成方法

多層膜構造体の形成方法について述べる。図1〜図4に各工程における試料の断面構造を示す。SOI基板として、SIMOX(separation by implanted oxygen)基板を用いた(図1)。ここでは、BOX層上に形成されたSOI層が存在すればよく、例えば、貼り合わせ法やSmart cut等の他の既存の手法を用いて作製したSOI基板を用いても構わない。

【0021】

SOI上のGe1-x-ySixSny層形成のために次に示すような手順で試料作製を行った。SOI層の膜厚は44 nmであった。また、BOX層の膜厚は110 nmであった。始めにアルカリ洗浄および超高真空中で850℃、15分間の熱処理を施してSOI基板を清浄化した。次に、固体ソース分子線エピタキシー法(MBE)法を用いて成長温度150℃で膜厚100〜320 nmのゲルマニウム錫混晶(GezSn1-z)層をエピタキシャル成長させた(半導体層積層工程)。このときGezSn1-z層の成長温度は、GezSn1-z層からのSnの析出を抑えながら、エピタキシャル成長させるために150℃と低温に設定した。SOI上にGezSn1-z層をエピタキシャル成長できればよく、その形成手法は化学気相成長(CVD)法、スパッタリング法など他の既存の手法でも構わない。

【0022】

GezSn1-z/SOI多層構造の形成後、試料を大気中に取り出し、続いてスパッタリング装置を用いて膜厚14〜140 nmの酸化Si(SiO2)層を表面保護層として形成した(表面保護層積層工程、図2)。表面保護層としての酸化Si層の形成には、他のCVD法、スピンコーティング法などの他の既存の手法を用いても構わない。また、表面保護層としては、酸化Si層以外にも、窒化Si層、窒化チタン層、グラファイト層などを用いることができる。

【0023】

その後、窒素雰囲気中において、300〜500℃で1〜180分間の後熱処理を行い、GezSn1-z層とSOI層との固相反応を進行させる(半導体歪印加層形成工程、図3)。この後、フッ酸溶液を用いて表面保護層である酸化Si層を剥離する(表面保護層の除去工程)。この除去工程は化学溶液を用いる他にも、エッチングガスを用いたドライエッチング法や物理的研磨法など、既存の他の技術を用いるものでも構わない。続いて、試料に表面洗浄を施した後に、歪印加層上に歪Ge層のエピタキシャル成長を行うことで、歪Ge層を形成できる(歪半導体層の積層工程、図4)。

【0024】

なお、GezSn1-z層と反応するSiの量を制限する場合、上述のようにSOI基板を用いたが、その制限を設けず、GezSn1-z層とSi層との反応を行う場合は、基板にSi基板を用いても構わない。

【0025】

2.多層膜構造体が奏する効果を確かめるための試験

清浄化したSIMOX基板上に膜厚200 nm、Sn組成10.8%のGezSn1-z層を成長させ、その後、膜厚140 nmの酸化Si膜を形成した試料を試料Aと定める。試料Aと同様に、SIMOX基板上に膜厚200nm、Sn組成6.7%のGezSn1-z層をエピタキシャル成長し、その後膜厚140 nmの酸化Si膜を形成した試料を試料Bとした。また、SIMOX基板上に膜厚320 nm 、Sn組成3.0%のGezSn1-z層をエピタキシャル成長し、その後膜厚140 nmの酸化Si膜を形成した試料を試料Cとした。膜厚100nm、Sn組成6.7%のGezSn1-z層をエピタキシャル成長し、その後膜厚14および140 nmの酸化Si膜を形成した試料を、それぞれ試料Dおよび試料Eとした。さらに、Snの有無の効果を確かめるために、SIMOX基板上にSnを含まないGe層をエピタキシャル成長し、膜厚140 nmの酸化Si膜を形成した試料Rも作製した。

【0026】

試料Aおよび試料Bに対しては、それぞれ300℃および400℃において1〜60分間の熱処理を行った。同様に試料Rに対しては、400℃において1〜60分間の熱処理を行った。また、試料Cに対しては、400℃および500℃において1〜180分間の熱処理を行った。試料Dおよび試料Eに関しては400℃において1〜30分間の熱処理を行った。

【0027】

(低温熱処理によるSOI層とのミキシング)

図5に試料A(Sn組成10.8%)成膜直後の断面走査電子顕微鏡(SEM)像を示す。また、図6および図7に、それぞれ試料A、試料R(Sn含有なし)の成膜直後の状態におけるGe224逆格子点周辺のX線回折二次元逆格子マップ(XRD-2DRSM)の測定結果を示す。XRD-2DRSM図中に示された横軸Qxに垂直な実線は、Siを基準として歪緩和の生じていないpseudomorphicな状態を表す。この実線上に回折ピークが存在する場合、SOI層に対して上層のエピタキシャル層がpseudomorphicに成長していることを示す。また、斜めの実線は完全歪緩和の状態を表す。つまり、この直線上に回折ピークが存在する場合、エピタキシャル層の歪緩和率は100%と判断できる。

【0028】

図5のSEM像よりこのGe0.892Sn0.108はSOI層の上に分離する形で形成されていることがわかる。一方、図6より、試料Aにおける回折ピーク位置から、歪緩和率92%、Sn組成10.8%のGe0.892Sn0.108のエピタキシャル成長が確認できる。一方、試料Rにおいては、図7に示した回折ピーク位置からほぼ完全に歪緩和したGe層が形成されていることが確認できる。

【0029】

次に、試料Aに対して、窒素雰囲気において400℃、1〜60分間の熱処理を施した。400℃、60分間熱処理した試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果を図8に示す。また、400℃の熱処理前後の試料Aに対するSi004逆格子点周辺のXRD out-of-plane測定(2θ-ω測定)結果を図9に示す。さらに、図9に示したXRD out-of-plane測定(2θ-ω測定)結果から見積もられた、試料Aのエピタキシャル層における面直方向の格子定数の熱処理時間依存性を図10に示す。縦軸は面直方向の格子定数、横軸は熱処理時間を表わしている。また点線はバルクGeの格子定数を示している。

【0030】

図6と図8とを比較すると、熱処理の前後においてエピタキシャル層に起因する回折ピークの位置が大きく変化していることがわかる。熱処理後はGeの逆格子点よりもSiの逆格子点により近い位置に回折ピークが確認される。この結果は熱処理によって本来のエピタキシャル層がGeよりも格子定数の小さい結晶を形成していることを示している。

【0031】

また、図10より熱処理前における試料Aの格子定数は5.77ÅとバルクGeの格子定数である5.67Åに比べて大きな値を示している。しかし、400℃、1分間の熱処理を施すと格子定数がバルクGeの格子定数よりも小さな5.63Å程度にまで急激に減少しており、この後、熱処理時間を長くしても試料Aの格子定数はほとんど変わらない。

【0032】

図11に試料Aを60分間熱処理した後の断面透過電子顕微鏡(TEM)像を示す。SOI層とGe0.892Sn0.108層の界面は明瞭には確認できない。従って、熱処理によってSOI層とGe0.892Sn0.108層とが固相反応し、新たな単一結晶層が形成されたものとみなせる。

【0033】

もしも、400℃の熱処理過程によってSOI層とのミキシングと共にGezSn1-z層のSn原子がすべて析出してしまい、SOI層とGeのみが反応しSi1-wGew層が形成されたと仮定すると、そのSi1-wGew層のGe組成比は89.2%と見積もられる。しかし、熱処理前に形成された膜厚200nmのGe0.892Sn0.108層に含まれるGeが膜厚44nmのSOI層と完全に反応した場合、そのSi1-wGew層のGe組成比は78.2%と予想される。これら2つのGe組成の間には食い違いがある。つまり、前述の観測されたエピタキシャル層の格子定数は後述の予想値よりも大きい。これは実際には一定量のSnが格子位置に存在するため、Ge組成の見積もりを誤ってしまったことを示唆している。つまり熱処理過程においてGe0.892Sn0.108層のSnは析出せず、ある程度のSn原子が格子置換位置にとどまり、新たにGe1-x-ySixSny層を形成していると推測できる。ここで新たに形成されたGe1-x-ySixSny層の組成比をXRD-2DRSMの測定結果より考える。SOI層が全て消費されGe0.892Sn0.108層と完全にミキシングしたと仮定すると、XRD-2DRSM測定のピーク位置からその組成比はSiおよびSn組成はそれぞれ21.3%および2.9%と推測される。

【0034】

(固相反応に対する熱処理温度、Sn組成の影響)

試料A(Sn組成10.8%)に対して300℃、60分間の熱処理を施した。同熱処理後の試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果を図12に示す。また、図13に試料Aを300℃、60分間熱処理した後の断面TEM像を示す。図12に示した試料Aを300℃で60分間熱処理した224逆格子点周辺のXRD-2DRSMの測定結果と、図6に示した熱処理前の試料AのXRD-2DRSMの測定結果とを比べると、300℃、60分間の熱処理を施すことでGezSn1-zの224ピーク位置がSiの224ピーク位置に近づいていることが確認できる。しかし、図13からわかるように、熱処理後もSOI層は残留しており、エピタキシャル層とSOI層との間には300℃熱処理後も固相反応は生じていない。すなわち、エピタキシャル層の224ピーク位置の変化、すなわち格子定数の変化はSnの析出のみによって起こっていると結論づけられる。つまり、400℃以下の熱処理によってはSnの析出のみが生じ、400℃以上の熱処理によってSnの析出およびエピタキシャル層とSOI層との固相反応が生じたものと考えられる。

【0035】

さらに、試料B(Sn組成6.7%)に対して、試料A(Sn組成10.8%)と同様に300℃および400℃で1〜60分の熱処理を行った。XRD out-of-plane測定(2θ-ω測定)結果から見積もられる面直方向の格子定数の熱処理時間依存性を図14に示す。300℃における熱処理後の試料Aの測定結果と同様に300℃熱処理後の試料Bにおいても Snの析出による格子定数の変化が見られる。しかし、SOI層とエピタキシャル層との間に固相反応は起こっておらず、Ge1-x-ySixSny層の面直方向の格子定数がバルクGeの格子定数より小さくなることはない。一方、400℃熱処理後の試料Bに関しては400℃熱処理後の試料Aの面直方向の格子定数と同様にGeより小さな格子定数をもつエピタキシャル層の形成が確認できる。これはSOI層とエピタキシャル層との間で固相反応が起こり、Ge1-x-ySixSnyが形成されていることを示している。注目すべきことは400℃における熱処理において、試料A(Sn組成10.8%)の熱処理時間に対する面直方向の格子定数の減少に比べて試料B(Sn組成6.7%)の熱処理時間に対する面直方向の格子定数の減少が緩やかな点である。

【0036】

試料Aおよび試料BよりもSn組成を小さくした試料C(Sn組成3.0%)について400℃および500℃で1〜180分間の熱処理を行った。XRD out-of-plane測定(2θ-ω測定)結果から見積もられる、400℃および500℃において1、30、60および180分間熱処理を施した試料Cの面直方向の格子定数の熱処理時間依存性を図15に示す。400℃熱処理温度の場合、熱処理時間が増加しても面直方向の格子定数は変化しない。一方、500℃熱処理温度の場合、熱処理時間が30分間まで面直方向の格子定数はほとんど変化しないが、それ以降は減少を始めることがわかる。一方で、500℃、180分間の熱処理後の試料CにおけるXRD-2DRSM測定の回折ピーク位置から、Ge1-x-ySixSny層のSiおよびSn組成が、それぞれ14%および1.1%であると見積もられ、若干のSnの析出が示唆される。

【0037】

500℃で180分間の熱処理後の試料Cに対してフッ酸溶液処理を行い、表面の酸化Si膜を除去した後の平面SEM像を図16に示す。一部の領域に析出したSnがエッチングされた結果によるピットが見られるが、概ね均一で平坦な表面が実現できていることがわかる。

【0038】

比較のために試料R(Ge層)を400℃で熱処理を行った。400℃、60分間の熱処理を施した試料Rに対する224逆格子点周辺のXRD-2DRSMの測定結果を図17に示す。また、試料RのXRD out-of-Plane測定(2θ-ω測定)から見積もられるエピタキシャル層の面直方向の格子定数の熱処理時間依存性を図18に示す。熱処理時間の増加にともなって、Ge層内の歪緩和による面直方向の格子定数の減少は確認できる。しかし、その値はバルクGeの格子定数より小さくなることはなく、GeとSiとの固相反応は生じていない。SiとGeを熱処理することで固相反応させ結晶性のよいSi1-wGew層を形成するには、従来、950℃以上の高温が必要である[田岡則之, 博士学位論文, 名古屋大学 (2005).]。また、Si基板上にGeを成長させる場合においても、成長温度400℃程度ではSiとGeとの間に固相反応は起こらない。一方、SOI上に形成したGezSn1-z層に対して400℃の熱処理を施した場合、SOI層とエピタキシャル層との間で固相拡散が起こっていることが確認された。

【0039】

以上の結果より、GeへのSnの導入によってSOI層とGezSn1-z層との固相反応が促進されることは明らかである。このとき、固相反応のための熱処理温度を従来の950℃よりも十分低い400℃程度まで低減できることもわかった。さらに、Sn組成が高いほど、熱処理温度を低減できる。SOI層とGezSn1-z層との固相反応の結果、Geよりも格子定数が小さく、結晶性、均一性の高いGe1-x-ySixSnyをBOX上に形成できる。

(固相拡散に対するSiO2キャップ層の膜厚依存性)

Nakatsukaらは表面酸化Si層を形成していないGezSn1-z/SOI構造の試料に対して、500℃、60分間熱処理を施しているが、GezSn1-z層とSOI層との固相反応は報告されていない。つまり、GezSn1-z層とSOI層との固相反応の促進に対して、酸化Si層が一定の効果を持つと考えられる。

【0040】

そこで、固相反応に対する酸化Si層の効果および膜厚依存性を明らかにするため、Sn組成は一定で酸化Si層膜厚の異なる試料D (GezSn1-z層膜厚100 nm、Sn組成6.7%、酸化Si膜厚14 nm)および試料E (GezSn1-z層膜厚100 nm、Sn組成6.7%、酸化Si膜厚140 nm)に対して、400℃、1〜30分間の熱処理を施して、その格子定数の変化を調べた結果を次に示す。

【0041】

400℃、30分間の熱処理を施した試料Dおよび試料Eの断面SEM像をそれぞれ図19および図20に示す。SiO2キャップ層の膜厚に依らず、GezSn1-z層とSOI層との間に固相反応が生じ、BOX層上に単一層が形成されていることが確認できる。

400℃において1、3、10および30分間の熱処理を施した試料Dおよび試料Eにおける、XRD out-of-Plane測定(2θ-ω測定)結果から見積もられたエピタキシャル層の面直方向の格子定数の熱処理時間依存性を図21に示す。酸化Si層の膜厚が140 nmの試料Dにおいて、熱処理時間が1分間を超えると面直方向の格子定数が急激に減少していることがわかる。一方、SiO2キャップ層の膜厚が14 nmの試料Eにおいては、1分間の熱処理では面直方向の格子定数 はほとんど減少していない。試料Eにおいては、熱処理時間が3分間を超えると、試料Dと同様に格子定数は急激に減少する。つまり酸化Si層の膜厚が大きいほど、より効率的にGezSn1-z層とSOI層との間の固相反応が促進されることがわかる。

【0042】

また、これまで酸化Si層を形成していないSiおよびGe基板上の歪GezSn1-z層を熱処理したときには、転位の導入やSnの析出による歪緩和が優先的に起こることが報告されている。このとき、400℃程度の低温熱処理によるGezSn1-z層と基板SiあるいはGeとの間の固相反応は報告されていない。一方で、前述の結果からは、酸化Si層の膜厚が大きいほど固相拡散が促進されることがわかった。つまり酸化Si層はGezSn1-z層とSOI層との間の固相拡散に必要であり、その膜厚も重要な要素であることがわかる。

(Ge1-x-ySixSnyのモザイシティの評価)

図8に示したように低温熱処理による固相拡散によって形成されたGe1-x-ySixSny層のXRD-2DRSMの224回折パターンは、およそ円形となり、非常に対称性の良い形状をしている。224回折パターンの広がりはGe1-x-ySixSnyの結晶性の乱れ、モザイシティを反映している。このモザイシティを224回折パターンの対称性から評価した。対称性は回折パターン224面に垂直方向および平行方向の半値幅の比から評価し、対称性がいいほどその値は1に近くなる。

【0043】

XRD-2DRSMにおける回折パターンの対称性評価方法の模式図を図22に示す。また、各試料において、エピタキシャル層のXRD-2DRSM逆格子回折パターンの対称性を評価した結果を図23にまとめる。固相拡散によって形成されたGe1-x-ySixSny層はGe層に比べて半値幅の比が0.77から0.92と1に近いことがわかる。一方、Snを含まない試料Rにおいては、その比は1.31と1からの差が比較的大きい。すなわち、SOI層とGezSn1-z層との間で固相反応が生じた試料のモザイシティは比較的小さく、結晶性に優れていることがわかる。結果として、SOI層とGezSn1-z層との固相拡散によるGe1-x-ySixSny層の形成手法はモザイシティの低減に有効であることを示している。

【0044】

以上の結果より、SOI基板上に形成したGezSn1-z層に表面保護層としての酸化Si層を形成し、400℃程度の低温熱処理を施すことで、SOI層とGezSn1-z層との固相反応を生じさせ、Ge1-x-ySixSny層を形成できることが明らかになった。400℃においてGe層とSOI層との固相反応を生じさせるにはSnの存在が必要不可欠であることが示された。また、SOI層とGezSn1-z層との固相反応を促進するには表面保護層が必要であることが明らかになった。さらに、今回形成されたGe1-x-ySixSny層はエピタキシャル成長したGe層と比較してもモザイシティが低く、結晶性が優れていることが明らかになった。このGe1-x-ySixSnyは、バルクのGe層とは異なる格子定数を持つため、Ge層に二軸歪を印加するための歪印加層として利用が可能である。

【技術分野】

【0001】

本発明は、多層膜構造体及びその形成方法に関する。

【背景技術】

【0002】

従来、超々大規模集積回路(ULSI)の基本構成素子である金属-酸化物-半導体電界効果トランジスタ(MOSFET)の性能向上は、素子の微細化によって達成されるところが大きかった。しかし、近年、微細化が極限まで発展した結果、素子のサイズはナノメートルの領域に達しており、その継続は技術的、経済的に困難に直面している。そこで、微細化だけに依存しないMOSFETの性能向上技術として、従来の主流であったシリコン(Si)あるいは歪Siによるチャネル材料に代わって、歪ゲルマニウム(Ge)材料の適用が注目されている。

【0003】

Geは元来、Siよりも高い電子および正孔移動度を有する材料であり、これを用いることは電子素子の高速化、省電力化に有効である。これに加えて、圧縮あるいは伸張歪の加わったGeは、無歪のGeに比較してもさらに正孔および電子移動度が高くなることが知られている。例えば、Fischettiらの理論計算によると1.3%の二軸性の伸張歪をGeに印加した場合、無歪Geの場合に比較して、電子の移動度が10倍以上となることが期待される(非特許文献1参照)。また、同様にGeに二軸性圧縮歪を印加した場合、無歪Geに比べて正孔の移動度の向上が予測されており、1.3%の圧縮歪を印加した場合、正孔移動度は2倍以上となる。このような移動度向上技術の併用によって、電子素子の電流駆動能力のさらなる向上が期待できる。

【0004】

歪Geの作製のためには、シリコンゲルマニウム(Si1-xGex)、ゲルマニウム錫(Ge1-xSnx)(非特許文献2参照)、インジウムガリウム砒素(InxGa1-xAs)(非特許文献3参照)などのGeとは格子定数の異なる歪印加層(ストレッサ)が必要である。例えば、SiはGeよりも原子半径が小さく、Si1-xGexの格子定数はGeのそれよりも小さくなる。そのため、Si1-xGex層上にGe層を格子整合した状態でエピタキシャル成長させると、そのGe層には二軸性の圧縮歪を加えることが可能となる。

【0005】

続いて、ストレッサとなるバッファ層の形成手法について述べる。近年、歪印加バッファ層とSi on insulator(SOI)基板を融合した技術、つまり薄膜かつ歪緩和した歪印加バッファ層を埋め込み酸化(Buried oxide: BOX)層上に形成する技術が注目されている。TakagiらのグループはSOI基板上にエピタキシャル成長させたSi1-xGex層を1000℃以上の高温によって熱酸化することで、Si1-xGex on insulator(SGOI)構造およびGe on insulator(GOI)構造を実現させた(非特許文献4または非特許文献5参照)。一方、TaokaらはSi基板上およびSOI基板上にエピタキシャル成長させたGe層に、酸化Si膜キャップ層を形成後、950℃および1100℃の高温において熱処理することで、SGOI構造を形成する手法について報告している(非特許文献6参照)。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】M. V. Fischetti, and S. E. Laux, J. Appl. Phys. 80, 2234 (1996).

【非特許文献2】S. Takeuchi, Y. Shimura, O. Nakatsuka, S. Zaima, M. Ogawa, and A. Sakai, Appl. Phys. Lett. 92, 231916 (2008).

【非特許文献3】Y. Bai, K.E. Lee, C. Cheng, M.L. Lee and E.A. Fitzgerald, J. Appl. Phys. 104, 084518 (2008).

【非特許文献4】T. Tezuka, N. Sugiyama, T. Mizuno, M. Suzuki and S. Takagi, J. Appl. Phys. 40, 2866 (2001)

【非特許文献5】S. Nakaharai, T. Tezuka, N. Sugiyama, Y. Moriyama, and S. Takagi. Appl. Phys. Lett. 83, 3516 (2003).

【非特許文献6】N. Taoka, A. Sakai, S. Mochizuki, O. Nakatsuka, M. Ogawa, S. Zaima, Thin Solid Films 508, 147 (2006).

【発明の概要】

【発明が解決しようとする課題】

【0007】

非特許文献4〜6記載の手法は、バッファ層としてのSi1-xGex層の形成プロセスや条件が非常に複雑になりがちである。また、Si層とGe層との固相反応を生じさせるのに1000℃前後の高温熱処理が不可欠であるため、その実現には大きなエネルギーが必要であり、生産性、経済性的な観点からの課題が残されている。

【0008】

一方、MOSFETチャネルへの歪印加にバッファ層を用いる場合、素子性能の向上のためにはチャネル層からバッファ層へのリーク電流の抑制が重要となる。リーク電流抑制のためには伝導帯、価電子帯ともに、チャネル層に対するバッファ層のバンドオフセットが大きいことが重要である。

【0009】

しかしながら、Geチャネルに伸張ひずみを加えることを考える際、Ge1-xSnxのような材料をバッファ層として用いることには、そのエネルギーバンドアライメントの関係から、問題がある。Ge1-xSnxはGeと同等かあるいは、Geよりもエネルギーバンドギャップが小さく、また相互のバンドオフセットも小さいため、本来チャネル領域を流れるべき電子や正孔が、Ge1-xSnxに容易に流入し、本来期待する電気伝導が実現できない懸念がある。

【0010】

本発明は以上の点に鑑みなされたものであり、上述した課題のいずれかを解決できる多層膜構造体及びその形成方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の多層膜構造体の形成方法は、

半導体素子用の多層膜構造体の形成方法であって、

シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、

前記半導体層上に表面保護層を形成する表面保護層形成工程と、

前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、

前記表面保護層を除去する除去工程と、

前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする。

【0012】

本発明の多層膜構造体の形成方法によれば、ゲルマニウム層への錫の添加、および表面保護層の形成という理由により、シリコンを含む基板とゲルマニウム層との反応温度の低減という効果を奏する。

【0013】

前記歪半導体層は、ゲルマニウム層であることが好ましい。ゲルマニウム層であることにより、シリコンゲルマニウム錫を含む半導体歪印加層から歪を印加できるという効果がある。

【0014】

前記半導体層に熱処理を施す工程は、400℃以上950℃以下の熱処理であることが好ましい。この温度範囲であることにより、従来よりも低温の熱処理でシリコンとゲルマニウム錫混晶層との反応を誘起し、シリコンゲルマニウム錫混晶層を形成できるという効果がある。

【0015】

前記ゲルマニウム錫混晶の錫組成は、3%以上であってかつ12%以下であることが好ましい。この範囲内であることにより、950℃以下の温度であってもシリコンを含む層とゲルマニウム錫混晶層との反応を生じさせることができる効果が得られる。

【0016】

前記基板は、絶縁膜上に形成されたシリコン層を含む構造であることが好ましい。このような構造であることにより、ゲルマニウム錫層との反応によってシリコンゲルマニウム錫層を形成できる効果が得られる。

前記表面保護層は、酸化シリコン層、窒化シリコン層、窒化チタン層、またはグラファイト層であることが好ましい。上記のものであることにより、シリコンとゲルマニウム錫との反応を促進できる効果が得られる。

【0017】

本発明の多層膜構造体は、

半導体素子用の多層膜構造体であって、

基板の上方に形成された錫を含む歪緩和した半導体歪印加層と、

その上方に形成された歪を有する歪半導体層を含むことを特徴とする。

【0018】

本発明の多層膜構造体は、歪半導体層を含むという理由により、従来の無歪半導体と比較して、高い電子および正孔移動度を実現するという効果を奏する。

前記半導体歪印加層がシリコンゲルマニウム錫混晶層であり、前記歪半導体層がゲルマニウム層であることが好ましい。上記のものであることにより、ゲルマニウム層にはシリコンゲルマニウム錫層から歪が印加される。その結果として、歪半導体層である歪ゲルマニウム層は、無歪ゲルマニウムと比較して、高い電子および正孔移動度を実現するという効果を奏する。

【図面の簡単な説明】

【0019】

【図1】多層膜構造体の形成方法に関する各工程における試料断面図(1)。SOI基板の構成を表す断面図。

【図2】多層膜構造体の形成方法に関する各工程における試料断面図(2)。表面保護層形成工程後の酸化Si層/Ge1-zSnz層/SOI基板構造の断面図。

【図3】多層膜構造体の形成方法に関する各工程における試料断面図(3)。半導体歪印加層形成工程における熱処理に伴うGezSn1-z層とSOI層との界面固相反応進行後の断面図。

【図4】多層膜構造体の形成方法に関する各工程における試料断面図(4)。表面保護層の除去工程後、積層工程において歪印加層上に歪Ge層のエピタキシャル成長した後の断面図。

【図5】Ge1-zSnz層の成膜直後の試料Aの断面SEM像。

【図6】試料AのGe1-zSnz層の成膜直後の状態におけるGe224逆格子点周辺のX線回折二次元逆格子マップ(XRD-2DRSM)の測定結果。

【図7】試料R(Sn含有なし)のGe層成膜直後の状態におけるGe224逆格子点周辺のX線回折二次元逆格子マップ(XRD-2DRSM)の測定結果。

【図8】400℃、60分間熱処理を施した試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果。

【図9】400℃の熱処理前後の試料Aに対するSi004逆格子点周辺のXRD out-of-plane測定(2θ-ω測定)結果。

【図10】試料AにおけるXRD out-of-plane測定(2θ-ω測定)結果から見積もられた、エピタキシャル層の面直方向の格子定数の熱処理時間依存性。

【図11】400℃、60分間熱処理を施した後の試料Aの断面TEM像。

【図12】300℃、60分間の熱処理後の試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果。

【図13】試料Aを300℃、60分間熱処理した後の断面TEM像。

【図14】試料BにおけるXRD out-of-plane測定(2θ-ω測定)結果から見積もられるエピタキシャル層の面直方向の格子定数の熱処理時間依存性。300℃、および400℃熱処理後の結果。

【図15】試料CにおけるXRD out-of-plane測定(2θ-ω測定)結果から見積もられる、エピタキシャル層の面直方向の格子定数の熱処理時間依存性。400℃および500℃熱処理後の結果。

【図16】500℃で180分間の熱処理を施した試料Cにおいて、表面の酸化Si膜を除去した後の平面SEM像。

【図17】400℃、60分間の熱処理を施した試料Rに対する224逆格子点周辺のXRD-2DRSMの測定結果。

【図18】試料RにおけるXRD out-of-Plane測定(2θ-ω測定)から見積もられるエピタキシャル層の面直方向の格子定数の熱処理時間依存性。

【図19】400℃、30分間の熱処理を施した試料Dの断面SEM像。

【図20】400℃、30分間の熱処理を施した試料Eの断面SEM像。

【図21】試料Dおよび試料Eにおける、XRD out-of-Plane測定(2θ-ω測定)結果から見積もられたエピタキシャル層の面直方向の格子定数の熱処理時間依存性。

【図22】XRD-2DRSMにおける回折パターンの対称性評価方法の模式図。

【図23】各試料において、エピタキシャル層のXRD-2DRSM逆格子回折パターンの対称性を評価した結果。

【発明を実施するための形態】

【0020】

1.多層膜構造体の形成方法

多層膜構造体の形成方法について述べる。図1〜図4に各工程における試料の断面構造を示す。SOI基板として、SIMOX(separation by implanted oxygen)基板を用いた(図1)。ここでは、BOX層上に形成されたSOI層が存在すればよく、例えば、貼り合わせ法やSmart cut等の他の既存の手法を用いて作製したSOI基板を用いても構わない。

【0021】

SOI上のGe1-x-ySixSny層形成のために次に示すような手順で試料作製を行った。SOI層の膜厚は44 nmであった。また、BOX層の膜厚は110 nmであった。始めにアルカリ洗浄および超高真空中で850℃、15分間の熱処理を施してSOI基板を清浄化した。次に、固体ソース分子線エピタキシー法(MBE)法を用いて成長温度150℃で膜厚100〜320 nmのゲルマニウム錫混晶(GezSn1-z)層をエピタキシャル成長させた(半導体層積層工程)。このときGezSn1-z層の成長温度は、GezSn1-z層からのSnの析出を抑えながら、エピタキシャル成長させるために150℃と低温に設定した。SOI上にGezSn1-z層をエピタキシャル成長できればよく、その形成手法は化学気相成長(CVD)法、スパッタリング法など他の既存の手法でも構わない。

【0022】

GezSn1-z/SOI多層構造の形成後、試料を大気中に取り出し、続いてスパッタリング装置を用いて膜厚14〜140 nmの酸化Si(SiO2)層を表面保護層として形成した(表面保護層積層工程、図2)。表面保護層としての酸化Si層の形成には、他のCVD法、スピンコーティング法などの他の既存の手法を用いても構わない。また、表面保護層としては、酸化Si層以外にも、窒化Si層、窒化チタン層、グラファイト層などを用いることができる。

【0023】

その後、窒素雰囲気中において、300〜500℃で1〜180分間の後熱処理を行い、GezSn1-z層とSOI層との固相反応を進行させる(半導体歪印加層形成工程、図3)。この後、フッ酸溶液を用いて表面保護層である酸化Si層を剥離する(表面保護層の除去工程)。この除去工程は化学溶液を用いる他にも、エッチングガスを用いたドライエッチング法や物理的研磨法など、既存の他の技術を用いるものでも構わない。続いて、試料に表面洗浄を施した後に、歪印加層上に歪Ge層のエピタキシャル成長を行うことで、歪Ge層を形成できる(歪半導体層の積層工程、図4)。

【0024】

なお、GezSn1-z層と反応するSiの量を制限する場合、上述のようにSOI基板を用いたが、その制限を設けず、GezSn1-z層とSi層との反応を行う場合は、基板にSi基板を用いても構わない。

【0025】

2.多層膜構造体が奏する効果を確かめるための試験

清浄化したSIMOX基板上に膜厚200 nm、Sn組成10.8%のGezSn1-z層を成長させ、その後、膜厚140 nmの酸化Si膜を形成した試料を試料Aと定める。試料Aと同様に、SIMOX基板上に膜厚200nm、Sn組成6.7%のGezSn1-z層をエピタキシャル成長し、その後膜厚140 nmの酸化Si膜を形成した試料を試料Bとした。また、SIMOX基板上に膜厚320 nm 、Sn組成3.0%のGezSn1-z層をエピタキシャル成長し、その後膜厚140 nmの酸化Si膜を形成した試料を試料Cとした。膜厚100nm、Sn組成6.7%のGezSn1-z層をエピタキシャル成長し、その後膜厚14および140 nmの酸化Si膜を形成した試料を、それぞれ試料Dおよび試料Eとした。さらに、Snの有無の効果を確かめるために、SIMOX基板上にSnを含まないGe層をエピタキシャル成長し、膜厚140 nmの酸化Si膜を形成した試料Rも作製した。

【0026】

試料Aおよび試料Bに対しては、それぞれ300℃および400℃において1〜60分間の熱処理を行った。同様に試料Rに対しては、400℃において1〜60分間の熱処理を行った。また、試料Cに対しては、400℃および500℃において1〜180分間の熱処理を行った。試料Dおよび試料Eに関しては400℃において1〜30分間の熱処理を行った。

【0027】

(低温熱処理によるSOI層とのミキシング)

図5に試料A(Sn組成10.8%)成膜直後の断面走査電子顕微鏡(SEM)像を示す。また、図6および図7に、それぞれ試料A、試料R(Sn含有なし)の成膜直後の状態におけるGe224逆格子点周辺のX線回折二次元逆格子マップ(XRD-2DRSM)の測定結果を示す。XRD-2DRSM図中に示された横軸Qxに垂直な実線は、Siを基準として歪緩和の生じていないpseudomorphicな状態を表す。この実線上に回折ピークが存在する場合、SOI層に対して上層のエピタキシャル層がpseudomorphicに成長していることを示す。また、斜めの実線は完全歪緩和の状態を表す。つまり、この直線上に回折ピークが存在する場合、エピタキシャル層の歪緩和率は100%と判断できる。

【0028】

図5のSEM像よりこのGe0.892Sn0.108はSOI層の上に分離する形で形成されていることがわかる。一方、図6より、試料Aにおける回折ピーク位置から、歪緩和率92%、Sn組成10.8%のGe0.892Sn0.108のエピタキシャル成長が確認できる。一方、試料Rにおいては、図7に示した回折ピーク位置からほぼ完全に歪緩和したGe層が形成されていることが確認できる。

【0029】

次に、試料Aに対して、窒素雰囲気において400℃、1〜60分間の熱処理を施した。400℃、60分間熱処理した試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果を図8に示す。また、400℃の熱処理前後の試料Aに対するSi004逆格子点周辺のXRD out-of-plane測定(2θ-ω測定)結果を図9に示す。さらに、図9に示したXRD out-of-plane測定(2θ-ω測定)結果から見積もられた、試料Aのエピタキシャル層における面直方向の格子定数の熱処理時間依存性を図10に示す。縦軸は面直方向の格子定数、横軸は熱処理時間を表わしている。また点線はバルクGeの格子定数を示している。

【0030】

図6と図8とを比較すると、熱処理の前後においてエピタキシャル層に起因する回折ピークの位置が大きく変化していることがわかる。熱処理後はGeの逆格子点よりもSiの逆格子点により近い位置に回折ピークが確認される。この結果は熱処理によって本来のエピタキシャル層がGeよりも格子定数の小さい結晶を形成していることを示している。

【0031】

また、図10より熱処理前における試料Aの格子定数は5.77ÅとバルクGeの格子定数である5.67Åに比べて大きな値を示している。しかし、400℃、1分間の熱処理を施すと格子定数がバルクGeの格子定数よりも小さな5.63Å程度にまで急激に減少しており、この後、熱処理時間を長くしても試料Aの格子定数はほとんど変わらない。

【0032】

図11に試料Aを60分間熱処理した後の断面透過電子顕微鏡(TEM)像を示す。SOI層とGe0.892Sn0.108層の界面は明瞭には確認できない。従って、熱処理によってSOI層とGe0.892Sn0.108層とが固相反応し、新たな単一結晶層が形成されたものとみなせる。

【0033】

もしも、400℃の熱処理過程によってSOI層とのミキシングと共にGezSn1-z層のSn原子がすべて析出してしまい、SOI層とGeのみが反応しSi1-wGew層が形成されたと仮定すると、そのSi1-wGew層のGe組成比は89.2%と見積もられる。しかし、熱処理前に形成された膜厚200nmのGe0.892Sn0.108層に含まれるGeが膜厚44nmのSOI層と完全に反応した場合、そのSi1-wGew層のGe組成比は78.2%と予想される。これら2つのGe組成の間には食い違いがある。つまり、前述の観測されたエピタキシャル層の格子定数は後述の予想値よりも大きい。これは実際には一定量のSnが格子位置に存在するため、Ge組成の見積もりを誤ってしまったことを示唆している。つまり熱処理過程においてGe0.892Sn0.108層のSnは析出せず、ある程度のSn原子が格子置換位置にとどまり、新たにGe1-x-ySixSny層を形成していると推測できる。ここで新たに形成されたGe1-x-ySixSny層の組成比をXRD-2DRSMの測定結果より考える。SOI層が全て消費されGe0.892Sn0.108層と完全にミキシングしたと仮定すると、XRD-2DRSM測定のピーク位置からその組成比はSiおよびSn組成はそれぞれ21.3%および2.9%と推測される。

【0034】

(固相反応に対する熱処理温度、Sn組成の影響)

試料A(Sn組成10.8%)に対して300℃、60分間の熱処理を施した。同熱処理後の試料Aに対する224逆格子点周辺のXRD-2DRSMの測定結果を図12に示す。また、図13に試料Aを300℃、60分間熱処理した後の断面TEM像を示す。図12に示した試料Aを300℃で60分間熱処理した224逆格子点周辺のXRD-2DRSMの測定結果と、図6に示した熱処理前の試料AのXRD-2DRSMの測定結果とを比べると、300℃、60分間の熱処理を施すことでGezSn1-zの224ピーク位置がSiの224ピーク位置に近づいていることが確認できる。しかし、図13からわかるように、熱処理後もSOI層は残留しており、エピタキシャル層とSOI層との間には300℃熱処理後も固相反応は生じていない。すなわち、エピタキシャル層の224ピーク位置の変化、すなわち格子定数の変化はSnの析出のみによって起こっていると結論づけられる。つまり、400℃以下の熱処理によってはSnの析出のみが生じ、400℃以上の熱処理によってSnの析出およびエピタキシャル層とSOI層との固相反応が生じたものと考えられる。

【0035】

さらに、試料B(Sn組成6.7%)に対して、試料A(Sn組成10.8%)と同様に300℃および400℃で1〜60分の熱処理を行った。XRD out-of-plane測定(2θ-ω測定)結果から見積もられる面直方向の格子定数の熱処理時間依存性を図14に示す。300℃における熱処理後の試料Aの測定結果と同様に300℃熱処理後の試料Bにおいても Snの析出による格子定数の変化が見られる。しかし、SOI層とエピタキシャル層との間に固相反応は起こっておらず、Ge1-x-ySixSny層の面直方向の格子定数がバルクGeの格子定数より小さくなることはない。一方、400℃熱処理後の試料Bに関しては400℃熱処理後の試料Aの面直方向の格子定数と同様にGeより小さな格子定数をもつエピタキシャル層の形成が確認できる。これはSOI層とエピタキシャル層との間で固相反応が起こり、Ge1-x-ySixSnyが形成されていることを示している。注目すべきことは400℃における熱処理において、試料A(Sn組成10.8%)の熱処理時間に対する面直方向の格子定数の減少に比べて試料B(Sn組成6.7%)の熱処理時間に対する面直方向の格子定数の減少が緩やかな点である。

【0036】

試料Aおよび試料BよりもSn組成を小さくした試料C(Sn組成3.0%)について400℃および500℃で1〜180分間の熱処理を行った。XRD out-of-plane測定(2θ-ω測定)結果から見積もられる、400℃および500℃において1、30、60および180分間熱処理を施した試料Cの面直方向の格子定数の熱処理時間依存性を図15に示す。400℃熱処理温度の場合、熱処理時間が増加しても面直方向の格子定数は変化しない。一方、500℃熱処理温度の場合、熱処理時間が30分間まで面直方向の格子定数はほとんど変化しないが、それ以降は減少を始めることがわかる。一方で、500℃、180分間の熱処理後の試料CにおけるXRD-2DRSM測定の回折ピーク位置から、Ge1-x-ySixSny層のSiおよびSn組成が、それぞれ14%および1.1%であると見積もられ、若干のSnの析出が示唆される。

【0037】

500℃で180分間の熱処理後の試料Cに対してフッ酸溶液処理を行い、表面の酸化Si膜を除去した後の平面SEM像を図16に示す。一部の領域に析出したSnがエッチングされた結果によるピットが見られるが、概ね均一で平坦な表面が実現できていることがわかる。

【0038】

比較のために試料R(Ge層)を400℃で熱処理を行った。400℃、60分間の熱処理を施した試料Rに対する224逆格子点周辺のXRD-2DRSMの測定結果を図17に示す。また、試料RのXRD out-of-Plane測定(2θ-ω測定)から見積もられるエピタキシャル層の面直方向の格子定数の熱処理時間依存性を図18に示す。熱処理時間の増加にともなって、Ge層内の歪緩和による面直方向の格子定数の減少は確認できる。しかし、その値はバルクGeの格子定数より小さくなることはなく、GeとSiとの固相反応は生じていない。SiとGeを熱処理することで固相反応させ結晶性のよいSi1-wGew層を形成するには、従来、950℃以上の高温が必要である[田岡則之, 博士学位論文, 名古屋大学 (2005).]。また、Si基板上にGeを成長させる場合においても、成長温度400℃程度ではSiとGeとの間に固相反応は起こらない。一方、SOI上に形成したGezSn1-z層に対して400℃の熱処理を施した場合、SOI層とエピタキシャル層との間で固相拡散が起こっていることが確認された。

【0039】

以上の結果より、GeへのSnの導入によってSOI層とGezSn1-z層との固相反応が促進されることは明らかである。このとき、固相反応のための熱処理温度を従来の950℃よりも十分低い400℃程度まで低減できることもわかった。さらに、Sn組成が高いほど、熱処理温度を低減できる。SOI層とGezSn1-z層との固相反応の結果、Geよりも格子定数が小さく、結晶性、均一性の高いGe1-x-ySixSnyをBOX上に形成できる。

(固相拡散に対するSiO2キャップ層の膜厚依存性)

Nakatsukaらは表面酸化Si層を形成していないGezSn1-z/SOI構造の試料に対して、500℃、60分間熱処理を施しているが、GezSn1-z層とSOI層との固相反応は報告されていない。つまり、GezSn1-z層とSOI層との固相反応の促進に対して、酸化Si層が一定の効果を持つと考えられる。

【0040】

そこで、固相反応に対する酸化Si層の効果および膜厚依存性を明らかにするため、Sn組成は一定で酸化Si層膜厚の異なる試料D (GezSn1-z層膜厚100 nm、Sn組成6.7%、酸化Si膜厚14 nm)および試料E (GezSn1-z層膜厚100 nm、Sn組成6.7%、酸化Si膜厚140 nm)に対して、400℃、1〜30分間の熱処理を施して、その格子定数の変化を調べた結果を次に示す。

【0041】

400℃、30分間の熱処理を施した試料Dおよび試料Eの断面SEM像をそれぞれ図19および図20に示す。SiO2キャップ層の膜厚に依らず、GezSn1-z層とSOI層との間に固相反応が生じ、BOX層上に単一層が形成されていることが確認できる。

400℃において1、3、10および30分間の熱処理を施した試料Dおよび試料Eにおける、XRD out-of-Plane測定(2θ-ω測定)結果から見積もられたエピタキシャル層の面直方向の格子定数の熱処理時間依存性を図21に示す。酸化Si層の膜厚が140 nmの試料Dにおいて、熱処理時間が1分間を超えると面直方向の格子定数が急激に減少していることがわかる。一方、SiO2キャップ層の膜厚が14 nmの試料Eにおいては、1分間の熱処理では面直方向の格子定数 はほとんど減少していない。試料Eにおいては、熱処理時間が3分間を超えると、試料Dと同様に格子定数は急激に減少する。つまり酸化Si層の膜厚が大きいほど、より効率的にGezSn1-z層とSOI層との間の固相反応が促進されることがわかる。

【0042】

また、これまで酸化Si層を形成していないSiおよびGe基板上の歪GezSn1-z層を熱処理したときには、転位の導入やSnの析出による歪緩和が優先的に起こることが報告されている。このとき、400℃程度の低温熱処理によるGezSn1-z層と基板SiあるいはGeとの間の固相反応は報告されていない。一方で、前述の結果からは、酸化Si層の膜厚が大きいほど固相拡散が促進されることがわかった。つまり酸化Si層はGezSn1-z層とSOI層との間の固相拡散に必要であり、その膜厚も重要な要素であることがわかる。

(Ge1-x-ySixSnyのモザイシティの評価)

図8に示したように低温熱処理による固相拡散によって形成されたGe1-x-ySixSny層のXRD-2DRSMの224回折パターンは、およそ円形となり、非常に対称性の良い形状をしている。224回折パターンの広がりはGe1-x-ySixSnyの結晶性の乱れ、モザイシティを反映している。このモザイシティを224回折パターンの対称性から評価した。対称性は回折パターン224面に垂直方向および平行方向の半値幅の比から評価し、対称性がいいほどその値は1に近くなる。

【0043】

XRD-2DRSMにおける回折パターンの対称性評価方法の模式図を図22に示す。また、各試料において、エピタキシャル層のXRD-2DRSM逆格子回折パターンの対称性を評価した結果を図23にまとめる。固相拡散によって形成されたGe1-x-ySixSny層はGe層に比べて半値幅の比が0.77から0.92と1に近いことがわかる。一方、Snを含まない試料Rにおいては、その比は1.31と1からの差が比較的大きい。すなわち、SOI層とGezSn1-z層との間で固相反応が生じた試料のモザイシティは比較的小さく、結晶性に優れていることがわかる。結果として、SOI層とGezSn1-z層との固相拡散によるGe1-x-ySixSny層の形成手法はモザイシティの低減に有効であることを示している。

【0044】

以上の結果より、SOI基板上に形成したGezSn1-z層に表面保護層としての酸化Si層を形成し、400℃程度の低温熱処理を施すことで、SOI層とGezSn1-z層との固相反応を生じさせ、Ge1-x-ySixSny層を形成できることが明らかになった。400℃においてGe層とSOI層との固相反応を生じさせるにはSnの存在が必要不可欠であることが示された。また、SOI層とGezSn1-z層との固相反応を促進するには表面保護層が必要であることが明らかになった。さらに、今回形成されたGe1-x-ySixSny層はエピタキシャル成長したGe層と比較してもモザイシティが低く、結晶性が優れていることが明らかになった。このGe1-x-ySixSnyは、バルクのGe層とは異なる格子定数を持つため、Ge層に二軸歪を印加するための歪印加層として利用が可能である。

【特許請求の範囲】

【請求項1】

半導体素子用の多層膜構造体の形成方法であって、

シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、

前記半導体層上に表面保護層を形成する表面保護層工程と、

前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層工程と、

前記表面保護層を除去する除去工程と、

前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

【請求項2】

前記半導体層がゲルマニウム層であることを特徴とする請求項1に記載の多層膜構造体の形成方法。

【請求項3】

前記半導体層に熱処理を施す工程が400℃以上950℃以下の熱処理であることを特徴とする請求項1又は2に記載の多層膜構造体の形成方法。

【請求項4】

前記ゲルマニウム錫混晶の錫組成が3%以上であってかつ12%以下であることを特徴とする請求項1〜3のいずれか1項に記載の多層膜構造体の形成方法。

【請求項5】

前記基板が絶縁膜上に形成されたシリコン層を含む構造であることを特徴とする請求項1〜4のいずれか1項に記載の多層膜構造体の形成方法。

【請求項6】

前記表面保護層が酸化シリコン層、窒化シリコン層、窒化チタン層、またはグラファイト層であることを特徴とする請求項1〜5のいずれか1項に記載の多層膜構造体の形成方法。

【請求項7】

半導体素子用の多層膜構造体であって、

基板の上方に形成された錫を含む歪緩和した半導体歪印加層と、

その上方に形成された歪を有する歪半導体層を含むことを特徴とする多層膜構造体。

【請求項8】

前記半導体歪印加層がシリコンゲルマニウム錫混晶層であり、

前記歪半導体層がゲルマニウム層であることを特徴とする請求項7に記載の多層膜構造体。

【請求項1】

半導体素子用の多層膜構造体の形成方法であって、

シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、

前記半導体層上に表面保護層を形成する表面保護層工程と、

前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層工程と、

前記表面保護層を除去する除去工程と、

前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

【請求項2】

前記半導体層がゲルマニウム層であることを特徴とする請求項1に記載の多層膜構造体の形成方法。

【請求項3】

前記半導体層に熱処理を施す工程が400℃以上950℃以下の熱処理であることを特徴とする請求項1又は2に記載の多層膜構造体の形成方法。

【請求項4】

前記ゲルマニウム錫混晶の錫組成が3%以上であってかつ12%以下であることを特徴とする請求項1〜3のいずれか1項に記載の多層膜構造体の形成方法。

【請求項5】

前記基板が絶縁膜上に形成されたシリコン層を含む構造であることを特徴とする請求項1〜4のいずれか1項に記載の多層膜構造体の形成方法。

【請求項6】

前記表面保護層が酸化シリコン層、窒化シリコン層、窒化チタン層、またはグラファイト層であることを特徴とする請求項1〜5のいずれか1項に記載の多層膜構造体の形成方法。

【請求項7】

半導体素子用の多層膜構造体であって、

基板の上方に形成された錫を含む歪緩和した半導体歪印加層と、

その上方に形成された歪を有する歪半導体層を含むことを特徴とする多層膜構造体。

【請求項8】

前記半導体歪印加層がシリコンゲルマニウム錫混晶層であり、

前記歪半導体層がゲルマニウム層であることを特徴とする請求項7に記載の多層膜構造体。

【図22】

【図23】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図23】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−244069(P2012−244069A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−115089(P2011−115089)

【出願日】平成23年5月23日(2011.5.23)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成23年3月9日 社団法人応用物理学会発行の「2011年春季 第58回応用物理学関係連合講演会「講演予稿集」(DVD−ROM)」に発表

【出願人】(504139662)国立大学法人名古屋大学 (996)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月23日(2011.5.23)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成23年3月9日 社団法人応用物理学会発行の「2011年春季 第58回応用物理学関係連合講演会「講演予稿集」(DVD−ROM)」に発表

【出願人】(504139662)国立大学法人名古屋大学 (996)

【Fターム(参考)】

[ Back to top ]